공개특허 10-2020-0034604

(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2020-0034604

(43) 공개일자 2020년03월31일

(51) 국제특허분류(Int. Cl.)

*G05F 3/26* (2006.01) *G05F 3/24* (2006.01)

(71) 출원인

에이블릭 가부시키가이샤

일본국 치바켄 치바시 미하마구 나카세 1쵸메 8반

지

(52) CPC특허분류

*G05F 3/262* (2013.01)

*G05F 3/24* (2013.01)

(72) 발명자

사노 미노루

일본국 치바켄 치바시 미하마구 나카세 1쵸메 8반

지 에이블릭 가부시키가이샤 나이

(21) 출원번호 10-2019-0111283

(74) 대리인

특허법인코리아나

(22) 출원일자 2019년09월09일

심사청구일자 없음

(30) 우선권주장

JP-P-2018-177359 2018년09월21일 일본(JP)

전체 청구항 수 : 총 3 항

(54) 발명의 명칭 정전류 회로

### (57) 요 약

(과제) 전원 전압이 높은 경우라도, 기동시에 과대한 전류가 흐르지 않는 정전류 회로를 제공한다.

(해결수단) 정전류 발생 회로와, 정전류 발생 회로의 기동을 검출하는 기동 검출 회로와, 정전류 발생 회로에 기동 전압을 출력하는 클램프 회로를 구비하고, 클램프 회로가 출력하는 기동 전압은 정전류 발생 회로의 커런트 미러 회로를 구성하는 트랜지스터가 동작하고 있을 때의 게이트 전압보다 높은 게이트 전압의 근방의 전압인 것을 특징으로 한다.

대 표 도 - 도1

## 명세서

### 청구범위

#### 청구항 1

접지 단자에 접속된 저항과, 상기 접지 단자와 상기 저항에 접속된 제 1 커런트 미러 회로와, 전원 단자와 상기 제 1 커런트 미러 회로 사이에 접속된 제 2 커런트 미러 회로를 구비한 정전류 발생 회로와,

상기 정전류 발생 회로의 기동을 검출하고, 검출 신호를 출력하는 기동 검출 회로와,

상기 정전류 발생 회로에 기동 전압을 출력하는 클램프 회로와,

상기 전원 단자에 전원 전압이 투입된 것을 검출하면 상기 클램프 회로를 기동하고, 상기 기동 검출 회로의 검출 신호를 받으면 상기 클램프 회로를 정지하는, 전원 검출 회로를 구비하고,

상기 클램프 회로가 출력하는 상기 기동 전압은, 상기 정전류 발생 회로가 동작하고 있을 때의 상기 제 1 커런트 미러 회로를 구성하는 트랜지스터의 게이트 전압보다 높은 상기 게이트 전압의 근방의 전압인 것을 특징으로 하는 정전류 회로.

#### 청구항 2

제 1 항에 있어서,

상기 기동 검출 회로는, 정전류 인버터로 구성되는, 정전류 회로.

#### 청구항 3

제 2 항에 있어서,

상기 전원 검출 회로는,

상기 정전류 인버터의 상기 검출 신호를 받는 논리 회로와,

상기 전원 단자와 상기 정전류 인버터의 출력 단자 사이에 형성된 콘덴서와,

상기 논리 회로가 출력 신호를 반전할 때에 발생하는 관통 전류를 상기 콘덴서에 흘리는 커런트 미러 회로를 구비하는, 정전류 회로.

## 발명의 설명

### 기술 분야

[0001]

본 발명은 정전류 회로에 관한 것이다.

### 배경 기술

[0002]

전자 회로의 저소비화 기술로서, 미사용시에 회로를 슬리프 상태로 함으로써 전력 소비를 삐감하는 간헐 동작 기술이 알려져 있다. 정전류 회로는, 간헐 동작에 있어서, 단시간에 안정적으로 기동하는 것이 요구된다.

[0003]

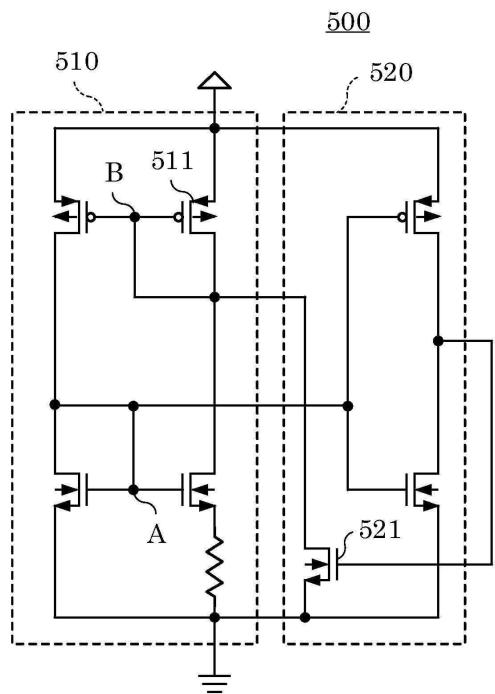

도 5 는, 기동 회로를 구비한, 종래의 정전류 회로의 일례인 정전류 회로 (500) 의 회로도이다. 정전류 회로 (500) 는, 정전류 회로부 (510) 와 기동 회로부 (520) 를 구비하고 있다.

[0004]

정전류 회로 (500) 는, 정전류 회로부 (510) 가 노드 (A) 의 전압이 낮으면 기동하지 않기 때문에, 기동 회로부 (520) 를 구비하고 있다. 기동 회로부 (520) 는, 노드 (A) 의 전압이 낮으면 NMOS 트랜지스터 (521) 를 온 하여, PMOS 트랜지스터 (511) 로부터 기동 전류를 인발함으로써, 정전류 회로부 (510) 를 기동시킨다 (예를 들어, 특허문현 1 참조).

## 신행기술문헌

## 특허문헌

[0005] (특허문헌 0001) 일본 공개특허공보 2011-118532호

### 발명의 내용

#### 해결하려는 과제

- [0006] PMOS 트랜지스터 (511) 의 게이트 · 소스간 전압은 전원 전압에 의존하여 변화된다. 따라서, 종래의, 기동 회로를 구비한 정전류 회로 (500) 에서는, 전원 전압이 높은 경우, PMOS 트랜지스터 (511) 로부터 NMOS 트랜지스터 (521) 로 과대한 기동 전류가 흘러 베린다.

- [0007] 본 발명은 전원 전압이 높은 경우라도, 기동시에 과대한 전류가 흐르지 않는 정전류 회로를 제공하는 것을 목적으로 한다.

#### 과제의 해결 수단

- [0008] 본 발명의 일 양태에 관련된 정전류 회로는,

- [0009] 접지 단자에 접속된 저항과, 상기 접지 단자와 상기 저항에 접속된 제 1 커런트 미러 회로와, 전원 단자와 상기 제 1 커런트 미러 회로 사이에 접속된 제 2 커런트 미러 회로를 구비한 정전류 발생 회로와,

- [0010] 상기 정전류 발생 회로의 기동을 검출하고, 검출 신호를 출력하는 기동 검출 회로와,

- [0011] 상기 정전류 발생 회로에 기동 전압을 출력하는 클램프 회로와,

- [0012] 상기 전원 단자에 전원 전압이 투입된 것을 검출하면 상기 클램프 회로를 기동하고, 상기 기동 검출 회로의 검출 신호를 받으면 상기 클램프 회로를 정지하는, 전원 검출 회로를 구비하고,

- [0013] 상기 클램프 회로가 출력하는 상기 기동 전압은, 상기 정전류 발생 회로가 동작하고 있을 때의 상기 제 1 커런트 미러 회로를 구성하는 트랜지스터의 게이트 전압보다 높은 상기 게이트 전압의 근방의 전압인 것을 특징으로 한다.

### 발명의 효과

- [0014] 본 발명의 정전류 회로에 의하면, 클램프 회로 (30) 에서 발생시킨 클램프 전압으로 정전류 발생 회로 (10) 를 기동하고 있기 때문에, 전원 전압이 높은 경우라도, 기동시에 과대한 전류가 흐르는 것을 방지할 수 있다.

#### 도면의 간단한 설명

- [0015] 도 1 은 본 발명의 실시형태의 정전류 회로의 구성예를 나타내는 블록도이다.

- 도 2 는 본 실시형태의 정전류 회로의 제 1 예를 나타내는 회로도이다.

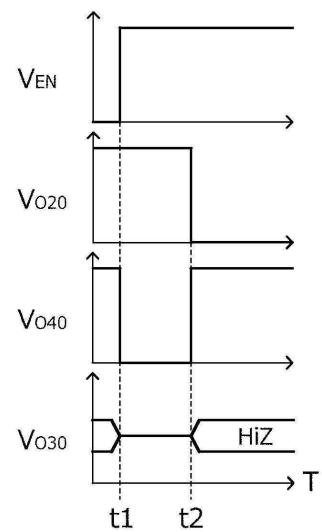

- 도 3 은 도 2 의 정전류 회로의 동작을 나타내는 타이밍도이다.

- 도 4 는 본 실시형태의 정전류 회로의 제 2 예를 나타내는 회로도이다.

- 도 5 는 종래의 정전류 회로를 나타내는 회로도이다.

### 발명을 실시하기 위한 구체적인 내용

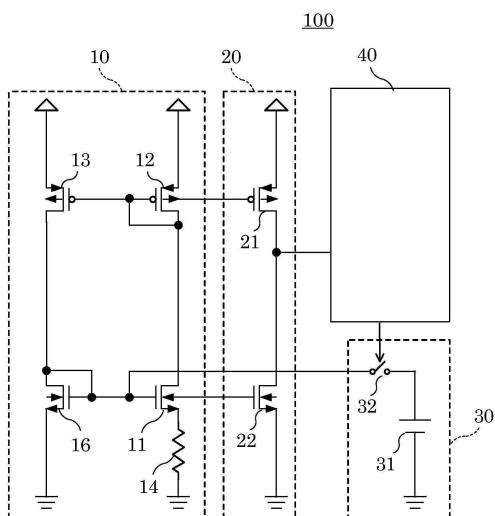

- [0016] 도 1 은, 본 발명의 실시형태의 정전류 회로 (100) 의 구성예를 나타내는 블록도이다. 정전류 회로 (100) 는, 정전류 발생 회로 (10) 와, 기동 검출 회로 (20) 와, 클램프 회로 (30) 와, 전원 검출 회로 (40) 를 구비하고 있다.

- [0017] 정전류 발생 회로 (10) 는, 제 1 커런트 미러 회로를 구성하는 NMOS 트랜지스터 (11, 16) 와, 제 2 커런트 미러 회로를 구성하는 PMOS 트랜지스터 (12, 13) 와, 저항 (14) 을 구비하고 있다. 기동 검출 회로 (20) 는, PMOS 트랜지스터 (21) 와 NMOS 트랜지스터 (22) 를 구비하고, 정전류 인버터를 구성하고 있다. 클램프 회로 (30) 는, 전압원 (31) 과 스위치 장치 (32) 를 구비하고 있다.

- [0018] 정전류 발생 회로 (10) 에서는, NMOS 트랜지스터 (11, 16) 의 게이트에 클램프 회로 (30) 의 출력 단자 (030) 가 접속되어 있다. 기동 검출 회로 (20) 에서는, PMOS 트랜지스터 (21) 의 게이트에 PMOS 트랜지스터 (13) 의 게이트가 접속되고, NMOS 트랜지스터 (22) 의 게이트에 NMOS 트랜지스터 (11) 의 게이트가 접속되어 있다.

- 전원 검출 회로 (40) 에서는, 입력 단자에 기동 검출 회로 (20) 의 출력 단자 (020) 가 접속되어 있다. 클램프 회로 (30) 는, 전압원 (31) 이 스위치 장치 (32) 를 개재하여 클램프 회로 (30) 의 출력 단자 (030) 에 접속되고, 스위치 장치 (32) 의 제어 단자에 전원 검출 회로 (40) 의 출력 단자 (040) 가 접속되어 있다.

- [0019] 전원이 투입된 직후에 있어서, 정전류 발생 회로 (10) 가 기동되어 있지 않으면, 기동 검출 회로 (20) 는, PMOS 트랜지스터 (21) 와 NMOS 트랜지스터 (22) 는 함께 오프되어 있기 때문에, 출력 단자 (020) 는 하이·임피던스로 되어 있다. 전원 검출 회로 (40) 는, 전원 전압이 입력되어 있어, 기동 검출 회로 (20) 의 출력 단자 (020) 가 하이·임피던스일 때에는, 정전류 발생 회로 (10) 가 기동되어 있지 않다고 판단하여, 전원 검출 회로 (40) 의 출력 단자 (040) 로부터 기동 신호를 출력한다. 클램프 회로 (30) 는, 전원 검출 회로 (40) 의 출력 단자 (040) 로부터 기동 신호를 받으면, 스위치 장치 (32) 를 온하여 전압원 (31) 의 전압을 출력한다. 여기서, 전압원 (31) 의 전압은, 정전류 발생 회로 (10) 가 통상 동작하고 있을 때의 NMOS 트랜지스터 (11, 16) 의 게이트 전압 (이하, 「통상 게이트 전압」으로 한다) 보다 높으며, 또한 정전류 발생 회로 (10) 의 기동 전류가 과대해지지 않을 정도로 낮은 전압, 즉 정전류 발생 회로 (10) 의 기동 전류가 과대해지는 최소 전압보다 낮은 전압으로 설정된다. 이 실시예에서는, 전압원 (31) 의 전압은, 가능한 한 낮은 것이 바람직하기 때문에, NMOS 트랜지스터 (11, 16) 의 통상 게이트 전압보다 높은, 통상 게이트 전압의 근방의 전압으로 설정되어 있다.

- [0020] 정전류 발생 회로 (10) 는, NMOS 트랜지스터 (11, 16) 의 게이트에 클램프 회로 (30) 의 전압원 (31) 의 전압이 인가됨으로써 기동 전류가 발생하여, 기동한다. 기동 검출 회로 (20) 는, 정전류 발생 회로 (10) 가 기동된 것을 검지하여, 예를 들어, NMOS 트랜지스터 (22) 가 온되어 Low 레벨의 검출 신호를 출력한다. 전원 검출 회로 (40) 는, 기동 검출 회로 (20) 로부터 검출 신호를 받으면 기동 신호의 출력을 정지하여, 클램프 회로 (30) 의 동작을 정지시킨다.

- [0021] 이상 설명한 바와 같이, 본 실시형태의 정전류 회로 (100) 는, 클램프 회로 (30) 가 NMOS 트랜지스터 (11, 16) 의 게이트에 상기 서술한 전압을 인가하여 정전류 발생 회로 (10) 를 기동하기 때문에, 과잉의 기동 전류가 흐르지 않고 신속하게 기동할 수 있다.

- [0022] 또, 기동 검출 회로 (20) 는, 전원 전압 의존성이 없는 정전류 인버터로 구성하였기 때문에, 전원 전압에 상관없이 정전류 발생 회로 (10) 의 기동을 검출할 수 있다는 효과도 있다.

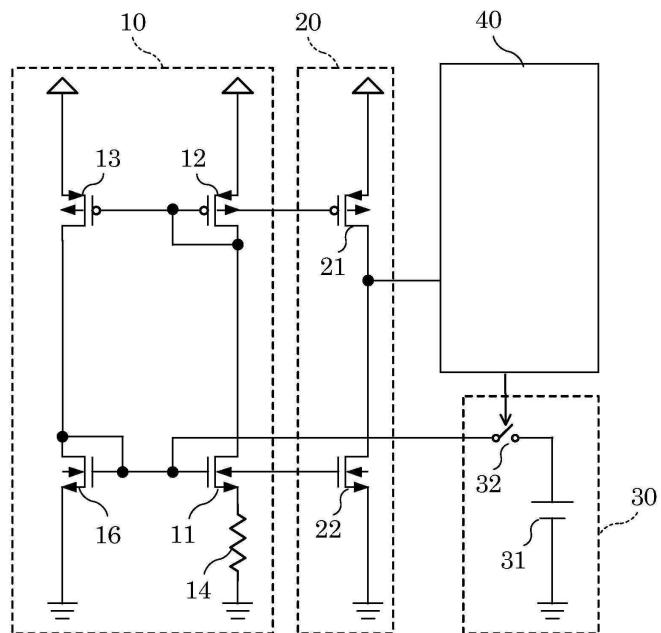

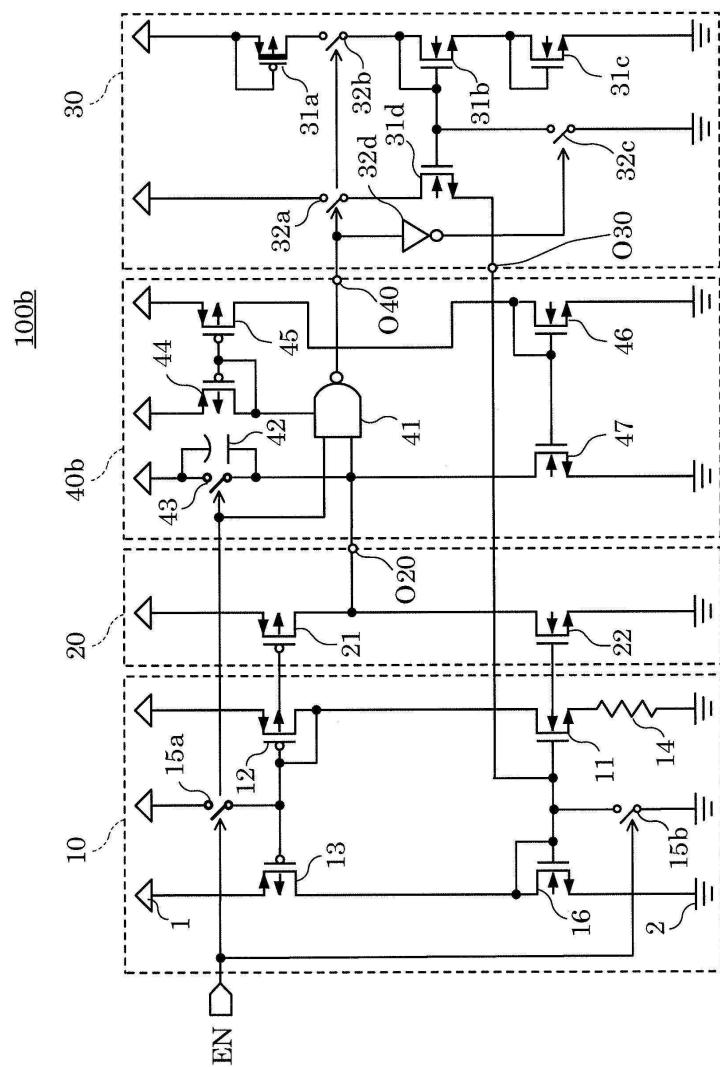

- [0023] 도 2 는, 정전류 회로 (100) 의 제 1 예인 정전류 회로 (100a) 의 구성예를 나타내는 회로도이다. 정전류 회로 (100a) 에서는, 이네이블 단자 (EN) 를 구비하고, 외부로부터의 이네이블 신호 (VEN) 에 의해 간헐 동작을 가능하게 한 회로예를 나타내고 있다.

- [0024] 정전류 발생 회로 (10) 는, NMOS 트랜지스터 (11, 16) 의 게이트와 접지 단자 (2) 사이에 스위치 (15a) 와, PMOS 트랜지스터 (12, 13) 의 게이트와 전원 단자 (1) 사이에 스위치 (15b) 를, 추가로 구비하고 있다. 스위치 (15a) 와 스위치 (15b) 의 제어 단자는, 이네이블 단자 (EN) 에 접속되어 있다.

- [0025] 클램프 회로 (30) 는, 다이오드 결선 (結線) 된, 디프레션형의 PMOS 트랜지스터 (31a), NMOS 트랜지스터 (31b) 및 NMOS 트랜지스터 (31c) 와, NMOS 트랜지스터 (31d) 를 전압원 (31) 으로서 구비하고 있다. 또, 클램프 회로 (30) 는, 스위치 (32a, 32b 및 32c) 와, NOT 회로 (32d) 를 스위치 장치 (32) 로서 구비하고 있다. 스위치 (32a 및 32b) 의 제어 단자는, 전원 검출 회로 (40a) 의 출력 단자 (040) 가 접속되어 있다. 스위치 (32c) 의 제어 단자는, 전원 검출 회로 (40a) 의 출력 단자 (040) 가 NOT 회로 (32d) 를 개재하여 접속되어 있다.

- [0026] 전원 검출 회로 (40a) 는, 논리 회로로서의 NAND 회로 (41) 와, 콘텐서 (42) 와, 스위치 (43) 를 구비하고 있다. NAND 회로 (41) 는, 일방의 입력 단자에 이네이블 단자 (EN) 가 접속되고, 타방의 입력 단자에 기동 검출 회로 (20) 의 출력 단자 (020) 가 접속되고, 출력 단자에 전원 검출 회로 (40a) 의 출력 단자 (040) 가 접속되어 있다. 콘텐서 (42) 와 스위치 (43) 는, 전원 단자 (1) 와 NAND 회로 (41) 의 타방의 입력 단자 사이에 병렬로 접속되어 있다.

- [0027] 여기서, 스위치 (15a, 15b, 32a, 32b, 32c, 43) 는, 제어 신호가 Low 레벨에서 온되고, High 레벨에서 오프되도록 구성하고 있다.

- [0028] 다음으로, 정전류 회로 (100a) 의 동작에 대해 설명한다. 도 3 은, 정전류 회로 (100a) 의 동작을 나타내는 타이밍도이다.

- [0029] 시각 t1 보다 앞에서는, 이네이블 신호 (VEN) 가 Low 레벨로 되어 있기 때문에, 스위치 (15a, 15b) 가 온되어 있으므로, 정전류 발생 회로 (10) 는 동작을 정지하고 있다. 또, 기동 검출 회로 (20) 에 있어서의 PMOS 트랜지스터 (21) 와 NMOS 트랜지스터 (22) 가 오프되어 있는 한편, 스위치 (43) 가 온되어 있기 때문에, 기동 검출 회로 (20) 의 출력 단자 (020) 의 전압 (이하, 「출력 전압 (VO20)」으로 한다) 은 High 레벨로 되어 있다. 전원 검출 회로 (40a) 는, NAND 회로 (41) 에 출력 전압 (VO20) 의 High 레벨과 이네이블 신호 (VEN) 의 Low 레벨이 입력되어 있기 때문에, 전원 검출 회로 (40a) 의 출력 단자 (040) 의 전압 (이하, 「출력 전압 (VO40)」으로 한다) 은 High 레벨로 되어 있다.

- [0030] 클램프 회로 (30) 에는, High 레벨의 출력 전압 (VO40) 이 입력되어 있기 때문에, 스위치 (32a, 32b) 는 오프, 스위치 (32c) 가 온되어 있다. 스위치 (32a, 32b) 가 오프되어 있고, 스위치 (32c) 가 온되어 있기 때문에, 클램프 회로 (30) 는 동작을 정지하고, 클램프 회로 (30) 의 출력 단자 (030) 는 하이 · 임피던스로 되어 있다.

- [0031] 시각 t1 에서 이네이블 신호 (VEN) 가 High 레벨이 되면, 스위치 (15a, 15b) 가 오프되지만, 정전류 발생 회로 (10) 가 기동되지 않으면 PMOS 트랜지스터 (21) 와 NMOS 트랜지스터 (22) 가 오프되어 있다. NAND 회로 (41) 의 입력 단자의 전압은, 스위치 (43) 가 오프되지만, 콘덴서 (42) 에 의해 High 레벨로 유지된다. NAND 회로 (41) 는, 출력 전압 (VO20) 의 High 레벨과 이네이블 신호 (VEN) 의 High 레벨이 입력되기 때문에, 전원 검출 회로 (40a) 의 출력 전압 (VO40) 은 Low 레벨이 된다.

- [0032] 따라서, 클램프 회로 (30) 는, 스위치 (32a, 32b) 가 온, 스위치 (32c) 가 오프되기 때문에, 동작을 개시한다. 스위치 (32a, 32b) 가 온, 스위치 (32c) 가 오프인 스위칭 상태에서는, 디프레션형의 PMOS 트랜지스터 (31a) 의 전류가 NMOS 트랜지스터 (31b) 및 NMOS 트랜지스터 (31c) 에 흐른다. 또, NMOS 트랜지스터 (31b) 의 게이트에는 전압이 발생한다. 클램프 회로 (30) 는, NMOS 트랜지스터 (31b) 의 게이트에 발생하는 전압에 기초하여, NMOS 트랜지스터 (31d) 의 소스로부터 출력 단자 (030) 를 개재하여 정전류 발생 회로 (10) 가 기동되기 위한 전압을 출력한다.

- [0033] 출력 단자 (030) 의 전압 (이하, 「출력 전압 (VO30)」으로 한다) 은, NMOS 트랜지스터 (31b), NMOS 트랜지스터 (31c), NMOS 트랜지스터 (31d) 의 각각의 게이트 · 소스간 전압을 VGS31b, VGS31c, VGS31d 로 하면, 이하의 식으로 나타내어진다.

- [0034]

$$VO30 = VGS31b + VGS31c - VGS31d$$

- [0035] 여기서, 클램프 회로 (30) 의 출력 전압 (VO30) 을, 전압 (VGS31b, VGS31c, VGS31d) 을 조정함으로써, NMOS 트랜지스터 (16 및 11) 의 통상 게이트 전압보다 높은 전압, 또한 통상 게이트 전압의 근방의 전압으로 설정한다. 이와 같이 함으로써, 정전류 회로 (100a) 는, 정전류 발생 회로 (10) 의 기동 전류가 정상시 (定常時) 의 전류의 전류값의 근방에 발생하기 때문에, 과잉의 기동 전류가 흐르지 않고, 신속하게 기동할 수 있다. 바꾸어 말하면, 설정되는 출력 전압 (VO30) 은, NMOS 트랜지스터 (16 및 11) 의 통상 게이트 전압을 V1 로 하고, 과잉의 기동 전류를 발생시키는 최소 전압을 V2 로 하면,  $V1 < VO30 < V2$  를 만족하는 전압이다. NMOS 트랜지스터 (16 및 11) 의 통상 게이트 전압의 근방의 전압의 범위는,  $V1 < VO30 < V2$  의 범위 중, V2 보다 V1 에 보다 가까운 전압을 취하는 범위이다.

- [0036] 시각 t2 에 있어서, 정전류 발생 회로 (10) 가 기동되면, 기동 검출 회로 (20) 는, NMOS 트랜지스터 (16 및 11) 의 게이트 전압의 상승에 의해 그 기동을 검지한다. 그리고, PMOS 트랜지스터 (21) 와 NMOS 트랜지스터 (22) 로 구성되는 정전류 인버터가 출력 전압 (VO20) 을 Low 레벨로 천이시킨다. NAND 회로 (41) 는 전압 (VO20) 의 Low 레벨이 입력되기 때문에 출력 전압이 High 레벨이 되고, 클램프 회로 (30) 는 동작을 정지한다. 그리고, 정전류 회로 (100a) 는, 기동 동작이 완료된다.

- [0037] 이상 설명한 바와 같이, 정전류 회로 (100a) 는, 클램프 회로 (30) 가 NMOS 트랜지스터 (16 및 11) 의 게이트에 상기 서술한 전압을 인가하여 정전류 발생 회로 (10) 를 기동하기 때문에, 과잉의 기동 전류가 흐르지 않고 신속하게 기동할 수 있다.

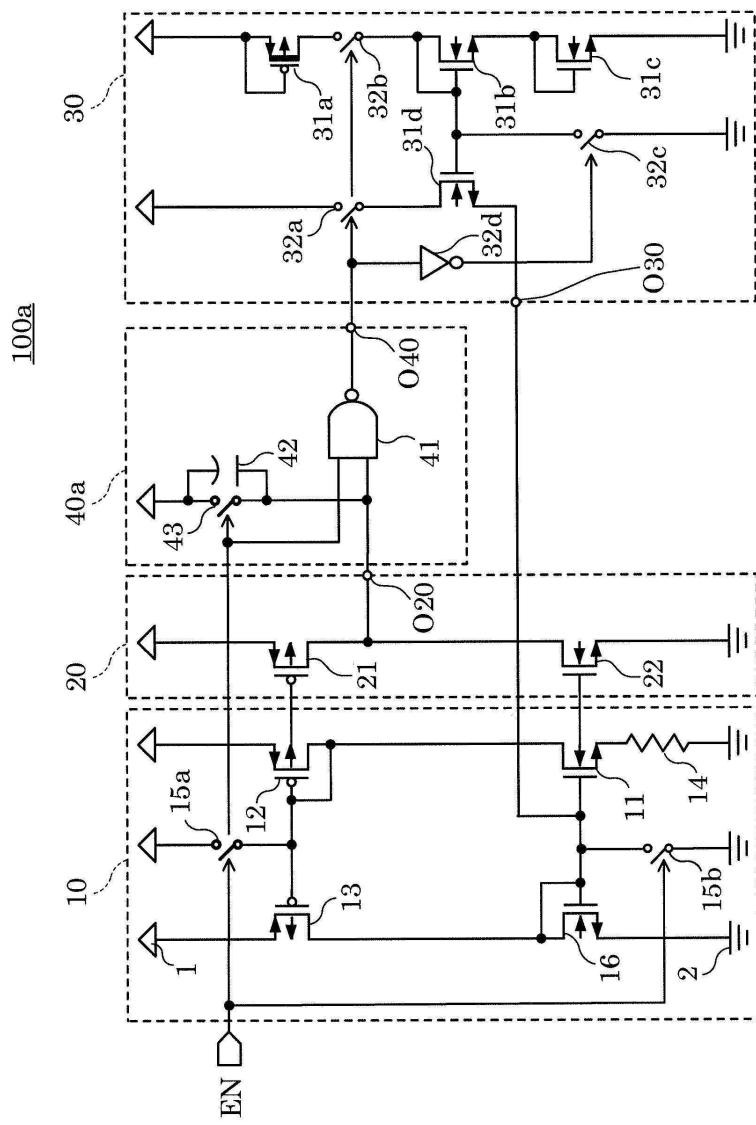

- [0038] 도 4 는, 정전류 회로 (100) 의 제 2 예인 정전류 회로 (100b) 의 구성예를 나타내는 회로도이다. 정전류 회로 (100b) 의 전원 검출 회로 (40b) 는, 정전류 회로 (100a) 의 전원 검출 회로 (40a) 에 제 3 커런트 미러 회로를 구성하는 PMOS 트랜지스터 (44, 45) 와, 제 4 커런트 미러 회로를 구성하는 NMOS 트랜지스터 (46, 47)

를 추가로 구비하고 있다. 또한, 정전류 회로 (100b) 의 다른 회로 구성은, 정전류 회로 (100a) 와 동일하기 때문에, 동일한 구성 요소에는 동일한 부호를 붙여 그 설명은 생략한다.

[0039] 기동 검출 회로 (20) 가 출력 전압 (VO20) 을 Low 레벨로 할 때, 정전류 인버터가 콘덴서 (42) 의 전하를 방전하기 때문에, High 레벨에서 Low 레벨로 반전하는 데에 시간을 필요로 한다. 즉, NAND 회로 (41) 는, 입력 단자의 전압이 반전되는 데에 시간을 필요로 하기 때문에, 그 사이에 관통 전류가 발생해 버린다. 그래서, 전원 검출 회로 (40b) 는, NAND 회로 (41) 의 동작 전류를 콘덴서 (42) 의 방전 전류로 하는 제 3 커런트 미러 회로와 제 4 커런트 미러 회로를 구비하고 있다.

[0040] 콘덴서 (42) 의 전하를 방전할 때에, NAND 회로 (41) 에 관통 전류가 발생하면, 제 3 커런트 미러 회로와 제 4 커런트 미러 회로는, 그 관통 전류에 의해 콘덴서 (42) 의 전하를 방전한다. 따라서, 기동 검출 회로 (20) 가 정전류 발생 회로 (10) 의 기동을 검출하였을 때, 기동 검출 회로 (20) 의 출력 전압 (VO20) 을 급속히 Low 레벨로 반전하는 것이 가능해진다.

[0041] 이상, 본 발명의 실시형태에 대해 설명하였지만, 본 발명은 상기 실시형태에 한정되지 않고, 본 발명의 취지를 일탈하지 않는 범위에 있어서 다양한 변경이 가능하다.

[0042] 예를 들어, 전압원 (31) 은, NMOS 트랜지스터 (11 및 16) 의 통상 게이트 전압보다 높으며, 또한 통상 게이트 전압의 근방의 전압을 출력하면 되고, 도시한 회로에 한정되지 않는다. 또, 기동 검출 회로 (20) 는, 정전류 발생 회로 (10) 가 기동된 것을 검출할 수 있는 회로이면 되고, 도시한 정전류 인버터에 한정되지 않는다.

또, 정전류 회로의 구체예에서는, 이네이블 단자 (EN) 를 구비한 예에 의해 설명하였지만, 그것에 한정되는 것은 아니다. 전원 검출 회로 (40) 는, 이네이블 신호에 상관없이, 전원이 기동된 것을 검출하여 클램프 회로 (30) 를 기동하는 회로여도 된다. 또, 논리 회로는 상기 회로에 한정되지 않는다.

### 부호의 설명

10 : 정전류 발생 회로

20 : 기동 검출 회로

30 : 클램프 회로

31 : 전압원

40, 40a, 40b : 전원 검출 회로

EN : 이네이블 단자

도면

도면1

100

## 도면2

## 도면3

## 도면4

## 도면5