(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2015년04월13일

(11) 등록번호 10-1511648

(24) 등록일자 2015년04월07일

(51) 국제특허분류(Int. Cl.)

*H01L 21/301* (2006.01)

(21) 출원번호 10-2012-7028305

(22) 출원일자(국제) 2011년06월20일

심사청구일자 2014년06월18일

(85) 번역문제출일자 2012년10월29일

(65) 공개번호 10-2013-0083381

(43) 공개일자 2013년07월22일

(86) 국제출원번호 PCT/US2011/041126

(87) 국제공개번호 WO 2011/163149

국제공개일자 2011년12월29일

(30) 우선권주장

13/160,713 2011년06월15일 미국(US)

61/357,468 2010년06월22일 미국(US)

(56) 선행기술조사문헌

KR1020090115039 A

US20040259329 A1

US20070272555 A1

US20050274702 A1

(73) 특허권자

어플라이드 머티어리얼스, 인코포레이티드

미국 95054 캘리포니아 산타 클라라 바우어스 애브뉴 3050

(72) 발명자

레이, 웨이-셍

미국 캘리포니아 95130 산호세 듀발 드라이브 1786

이튼, 브래드

미국 캘리포니아 94025 멘로 파크 에이트 애비뉴 563

(뒷면에 계속)

(74) 대리인

특허법인에이아이피

전체 청구항 수 : 총 11 항

심사관 : 김정진

(54) 발명의 명칭 페토초-기반의 레이저를 이용한 웨이퍼 다이싱 및 플라즈마 식각

**(57) 요약**

복수의 집적 회로들을 각각 갖는 반도체 웨이퍼들을 다이싱(dicing)하는 방법들이 설명된다. 방법은 반도체 웨이퍼 위에 마스크를 형성하는 단계를 포함한다. 마스크는 집적 회로들을 퍼복 및 보호하는 층으로 구성된다. 마스크는 갭(gap)들을 갖는 패터닝된 마스크를 제공하기 위하여 페토초-기반의 레이저 스크라이빙 프로세스(femtosecond-based laser scribing process)로 패터닝된다. 패터닝은 집적 회로들 사이의 반도체 웨이퍼의 영역들을 노출한다. 다음으로, 집적 회로들을 싱글레이팅하기 위하여, 반도체 웨이퍼는 패터닝된 마스크 내의 갭(gap)들을 통해 식각된다.

**대 표 도** - 도9b

(72) 발명자

**알라만칠리, 마드하바 라오**

미국 캘리포니아 95037 모간 힐 아베니다 드 로스

파드레스 1660

**싱호, 사라브지트**

미국 캘리포니아 95051 산타클라라 #74 퀄리 블러

바드 1000

---

**쿠마르, 아제이**

미국 캘리포니아 95014 쿠퍼티노 만자나타 코트

10457

**홀덴, 제임스 엠.**

미국 캘리포니아 95129 산호세 골든 드라이브 5088

## 명세서

### 청구범위

#### 청구항 1

복수의 집적 회로들을 포함하는 반도체 웨이퍼를 다이싱(dicing)하는 방법으로서, 상기 집적 회로들을 피복 및 보호하는 층을 포함하는 마스크를 상기 반도체 웨이퍼 위에 형성하는 단계; 각각이 폭을 갖는 스크라이브 라인들을 갖는 레이저-스크라이빙된 마스크를 제공하기 위하여 펨토초-기반의 레이저 스크라이빙 프로세스(femtosecond-based laser scribing process)로 상기 마스크를 패터닝하는 단계로서, 상기 스크라이브 라인들은 상기 집적 회로들 사이의 반도체 웨이퍼의 영역들을 노출하는, 상기 마스크를 패터닝하는 단계; 및 상기 집적 회로들을 싱글레이팅(singulating)하기 위하여 트렌치들을 상기 반도체 웨이퍼 내에 플라즈마 식각하는 단계로서, 상기 트렌치들 각각은 상기 폭과 동일한 폭을 갖는, 상기 플라즈마 식각하는 단계를 포함하는, 복수의 집적 회로들을 포함하는 반도체 웨이퍼를 다이싱하는 방법.

#### 청구항 2

청구항 1에 있어서,

상기 펨토초-기반의 레이저 스크라이빙 프로세스로 상기 마스크를 패터닝하는 단계는, 상기 집적 회로들 사이의 상기 반도체 웨이퍼의 영역들 내에 레이저-스크라이빙된 트렌치들을 형성하는 단계를 포함하고, 상기 폭을 갖는 상기 트렌치들을 상기 반도체 웨이퍼 내에 플라즈마 식각하는 단계는, 상기 집적 회로들을 싱글레이팅하기 위하여 상기 레이저-스크라이빙된 트렌치들을 연장하는 단계를 포함하는, 복수의 집적 회로들을 포함하는 반도체 웨이퍼를 다이싱하는 방법.

#### 청구항 3

청구항 1에 있어서,

상기 펨토초-기반의 레이저 스크라이빙 프로세스로 상기 마스크를 패터닝하는 단계는, 400 펨토초보다 크지 않은 레이저 펄스 폭을 가지며 540 나노미터보다 크지 않은 파장을 갖는 레이저를 이용하는 단계를 포함하는, 복수의 집적 회로들을 포함하는 반도체 웨이퍼를 다이싱하는 방법.

#### 청구항 4

삭제

#### 청구항 5

청구항 1에 있어서,

상기 마스크를 형성하는 단계는 포토-레지스트 층 및 I-라인 패터닝(I-line patterning) 층으로 구성된 그룹으로부터 선택된 층을 형성하는 단계를 포함하는, 복수의 집적 회로들을 포함하는 반도체 웨이퍼를 다이싱하는 방법.

#### 청구항 6

청구항 1에 있어서,

상기 복수의 집적 회로들은 디바이스 층/기판 계면에서 측정되는 바와 같이 10 마이크론보다 크지 않은 폭을 갖는 스트리트들에 의해 분리되는, 복수의 집적 회로들을 포함하는 반도체 웨이퍼를 다이싱하는 방법.

#### 청구항 7

청구항 1에 있어서,

상기 복수의 집적 회로들은 비-제한적인 레이아웃을 가지는, 복수의 집적 회로들을 포함하는 반도체 웨이퍼를 다이싱하는 방법.

#### 청구항 8

복수의 집적 회로들을 포함하는 반도체 웨이퍼를 다이싱하는 방법으로서,

실리콘 기판 상에 배치된 집적 회로들을 피복 및 보호하는 폴리머 마스크 층을 상기 실리콘 기판 위에 형성하는 단계로서, 상기 집적 회로들은 로우 K 재료(low K material)의 층 및 구리(copper)의 층 위에 배치된 실리콘 디옥사이드(silicon dioxide)의 층을 포함하는, 상기 폴리머 마스크 층을 형성하는 단계;

스크라이브 라인들이 상기 집적 회로들 사이의 상기 실리콘 기판의 영역들을 노출하는, 각각이 폭을 갖는 상기 스크라이브 라인들을 갖는 레이저 스크라이빙된 폴리머 마스크를 제공하기 위하여, 펨토초-기반의 레이저 스크라이빙 프로세스로 상기 폴리머 마스크 층, 상기 실리콘 디옥사이드의 층, 상기 로우 K 재료의 층, 및 상기 구리의 층을 패터닝하는 단계; 및

상기 집적 회로들을 싱글레이팅하기 위하여 트렌치들을 상기 실리콘 기판 내에 플라즈마 식각하는 단계로서, 상기 트렌치들 각각은 상기 폭과 동일한 폭을 갖는, 상기 플라즈마 식각하는 단계를 포함하는, 복수의 집적 회로들을 포함하는 반도체 웨이퍼를 다이싱하는 방법.

#### 청구항 9

청구항 8에 있어서,

상기 펨토초-기반의 레이저 스크라이빙 프로세스로 상기 실리콘 디옥사이드의 층, 상기 로우 K 재료의 층, 및 상기 구리의 층을 패터닝하는 단계는, 상기 로우 K 재료의 층 및 상기 구리의 층을 어블레이팅하기 전에 상기 실리콘 디옥사이드의 층을 어블레이팅하는 단계를 포함하는, 복수의 집적 회로들을 포함하는 반도체 웨이퍼를 다이싱하는 방법.

#### 청구항 10

청구항 8에 있어서,

상기 펨토초-기반의 레이저 스크라이빙 프로세스로 패터닝하는 단계는 상기 집적 회로들 사이의 상기 실리콘 기판의 영역들 내에 레이저-스크라이빙된 트렌치들을 형성하는 더 단계를 포함하고, 상기 폭을 갖는 상기 트렌치들을 상기 실리콘 기판 내에 플라즈마 식각하는 단계는 상기 집적 회로들을 싱글레이팅하기 위하여 상기 레이저-스크라이빙된 트렌치들을 연장하는 단계를 포함하는, 복수의 집적 회로들을 포함하는 반도체 웨이퍼를 다이싱하는 방법.

#### 청구항 11

청구항 8에 있어서,

상기 펨토초-기반의 레이저 스크라이빙 프로세스로 패터닝하는 단계는 400 펨토초보다 크지 않은 레이저 펄스 폭을 가지며 530 나노미터보다 크지 않은 파장을 가지는 레이저를 이용하는 단계를 포함하는, 복수의 집적 회로들을 포함하는 반도체 웨이퍼를 다이싱하는 방법.

#### 청구항 12

삭제

#### 청구항 13

청구항 8에 있어서,

상기 집적 회로들은 10 마이크론보다 크지 않은 폭을 갖는 스트리트들에 의해 분리되는, 복수의 집적 회로들을 포함하는 반도체 웨이퍼를 다이싱하는 방법.

#### 청구항 14

삭제

## 청구항 15

삭제

### 발명의 설명

#### 기술 분야

##### 관련 출원들에 대한 상호 참조

[0001] 본 출원은 그 전체 내용들이 본 명세서에 참조를 위해 통합되는, 2010년 6월 22일자로 출원된 미국 특허 가출원 제61/357,468호의 이익을 주장한다.

#### 기술 분야

[0004] 본 발명의 실시예들은 반도체 프로세싱(semiconductor processing)의 분야에 관한 것으로, 특히, 복수의 접적 회로들을 그 위에 각각 가지는 반도체 웨이퍼들을 다이싱(dicing)하는 방법들에 관한 것이다.

### 배경 기술

[0005] 반도체 웨이퍼 프로세싱에서는, 접적 회로들이 실리콘(silicon) 또는 다른 반도체 재료로 구성된 웨이퍼(또는 기판이라고도 지칭됨) 상에 형성된다. 일반적으로, 반전도성(semiconducting), 전도성(conducting) 또는 절연성(insulating)인 다양한 재료들의 층들은 접적 회로들을 형성하기 위해 사용된다. 접적 회로들을 형성하기 위하여, 이 재료들은 다양한 잘 알려진 프로세스(process)들을 이용하여 도핑, 증착 및 식각된다. 각각의 웨이퍼는 다이들(dice)로서 알려진 접적 회로들을 갖는 다수의 개별적인 영역들을 형성하도록 프로세싱된다.

[0006] 접적 회로 형성 프로세스 후에, 웨이퍼는 패키징을 위하여 또는 더 큰 회로들 내에서 패키징되지 않은 형태로 이용하기 위하여 개별적인 다이(die)를 서로로부터 분리하기 위하여 "다이싱(diced)" 된다. 웨이퍼 다이싱을 위하여 이용되는 2개의 주요 기술들은 스크라이빙(scribing) 및 소잉(sawing)이다. 스크라이빙으로, 다이아몬드가 박혀있는 스크라이브(diamond tipped scribe)는 미리 형성된 스크라이브 라인들을 따라 웨이퍼 표면을 가로질러 이동된다. 이 스크라이브 라인들은 다이들 사이의 공간들을 따라 연장된다. 이 공간들은 통상적으로 "스트리트(street)"이라고 지칭된다. 다이아몬드 스크라이브는 스트리트들을 따라 웨이퍼 표면에서 얇은 스크래치(shallow scratch)들을 형성한다. 롤러(roller)와 같은 것으로 압력을 가하면, 웨이퍼는 스크라이브 라인들을 따라 분리된다. 웨이퍼에서의 파손(break)들은 웨이퍼 기판의 결정 격자 구조(crystal lattice structure)를 따른다. 스크라이빙은 두께가 약 10 밀(mil : 1/1000 인치) 이하인 웨이퍼들을 위해 이용될 수 있다. 더 두꺼운 웨이퍼들을 위해서는, 소잉이 다이싱을 위한 현재의 바람직한 방법이다.

[0007] 소잉(sawing)으로, 높은 분당 회전수(rpm : revolution per minute)로 회전하는 다이아몬드가 박혀있는 소우(saw)는 웨이퍼 표면과 접촉하고, 스트리트들을 따라 웨이퍼를 소잉한다. 웨이퍼는 필름 프레임을 가로질러 늘어져 있는 접착제 필름과 같은 지지 부재(supporting member) 상에 장착되고, 소우는 수직 및 수평 스트리들을 모두에 반복적으로 가해진다. 스크라이빙 또는 소잉에 있어서의 하나의 문제는 다이들의 절단된 에지(edge)들을 따라 이가 빠진 자국(chip)들 및 둥글게 잘린 자국(gouge)들이 형성될 수 있다는 점이다. 또한, 크랙(crack)들이 형성될 수 있고 다이들의 에지들로부터 기판으로 전파될 수 있고, 접적 회로를 동작 불능으로 할 수 있다. 정사각형 또는 직사각형 다이의 하나의 측면(side)만이 결정질 구조의 <110> 방향에서 스크라이빙될 수 있으므로, 칩핑(chipping) 및 크래킹(cracking)은 특히, 스크라이빙에 있어서 문제이다. 그 결과, 다이의 다른 측면의 클리빙(cleaving)은 들쭉날쭉한(jagged) 분리선으로 귀착된다. 칩핑 및 크래킹으로 인해, 접적 회로들에 대한 손상을 방지하기 위하여 웨이퍼 상의 다이들 사이에 추가적인 간격 설정(spacing)이 요구되고, 예를 들어, 칩들 및 크랙들은 실제적인 접적 회로들로부터 거리를 두고 유지된다. 간격 설정 요건들의 결과로서, 많은 다이들이 표준적인 크기의 웨이퍼 상에 형성될 수 없으며, 그렇지 않을 경우에 회로로 이용될 수 있는 웨이퍼 자원(real estate)이 낭비된다. 소우(saw)의 이용은 반도체 웨이퍼 상의 면적의 낭비를 악화시킨다. 소우의 블레이드(blade)는 대략 15 마이크론(micron) 두께이다. 이와 같이, 소우에 의해 행해지는 절단부(cut)를 둘러싸는 크래킹 및 다른 손상이 접적 회로들에 피해를 주지 않음을 보장하기 위하여, 종종 다이들 각각의 회로를 3백 내지 5백 마이크론 분리해야 한다. 또한, 절단 후에, 각각의 다이는 소잉 프로세스로부터 발생하는 입자들 및 다른 오염물들을 제거하기 위하여 상당한 세정을 요구한다.

[0008] 또한, 플라즈마 다이싱이 이용되었지만, 마찬가지로 제한들을 가질 수 있다. 예를 들어, 플라즈마 다이싱의 구

현을 방해하는 하나의 제한은 비용일 수 있다. 레지스트(resist)를 패터닝하기 위한 표준적인 리소그래피(lithography) 동작은 구현 비용을 엄청나게 비싸게 만들 수 있다. 플라즈마 다이싱의 구현을 방해할 가능성이 있는 또 다른 제한은 스트리트들을 따른 다이싱 시에 통상적으로 마주치는 금속들(예를 들어, 구리)의 플라즈마 프로세싱이 생산의 문제들 또는 스루풋(throughput) 한계들을 만들 수 있다는 것이다.

## 발명의 내용

### 과제의 해결 수단

[0009] 본 발명의 실시예들은 반도체 웨이퍼들을 다이싱하는 방법들을 포함하고, 각각의 웨이퍼는 그 웨이퍼 상에 복수의 집적 회로들을 가진다.

[0010] 일 실시예에서, 복수의 집적 회로들을 갖는 반도체 웨이퍼를 다이싱하는 방법은 상기 반도체 웨이퍼 위에 마스크를 형성하는 단계를 포함하고, 상기 마스크는 상기 집적 회로들을 피복 및 보호하는 층으로 구성된다. 다음으로, 캡들을 갖는 패터닝된 마스크를 제공하기 위하여, 상기 마스크는 펨토초-기반의 레이저 스크라이빙 프로세스(femtosecond-based scribing process)로 패터닝되어, 상기 집적 회로들 사이의 상기 반도체 웨이퍼의 영역들을 노출한다. 다음으로, 상기 집적 회로들을 싱귤레이팅하기 위하여, 상기 반도체 웨이퍼는 상기 패터닝된 마스크 내의 캡들을 통해 식각된다.

[0011] 또 다른 실시예에서, 반도체 웨이퍼를 다이싱하기 위한 시스템은 팩토리 인터페이스(factory interface)를 포함한다. 레이저 스크라이브 장치는 팩토리 인터페이스와 결합되고, 펨토초-기반의 레이저를 포함한다. 또한, 플라즈마 식각 캠버는 상기 팩토리 인터페이스와 결합된다.

[0012] 또 다른 실시예에서, 복수의 집적 회로들을 갖는 반도체 웨이퍼를 다이싱하는 방법은 실리콘 기판 위에 폴리머 층을 형성하는 단계를 포함한다. 상기 폴리머 층은 상기 실리콘 기판 상에 배치된 집적 회로들을 피복 및 보호 한다. 상기 집적 회로들은 로우 K 재료(low K material)의 층 및 구리(copper)의 층 위에 배치된 실리콘 디옥사이드(silicon dioxide)의 층으로 구성된다. 상기 집적 회로들 사이의 상기 실리콘 기판의 영역들을 노출하기 위하여, 폴리머 층, 실리콘 디옥사이드의 층, 로우 K 재료의 층, 및 구리의 층은 펨토초-기반의 레이저 스크라이빙 프로세스로 패터닝된다. 다음으로, 상기 집적 회로들을 싱귤레이팅하기 위하여, 실리콘 기판은 캡들을 통해 식각된다.

### 도면의 간단한 설명

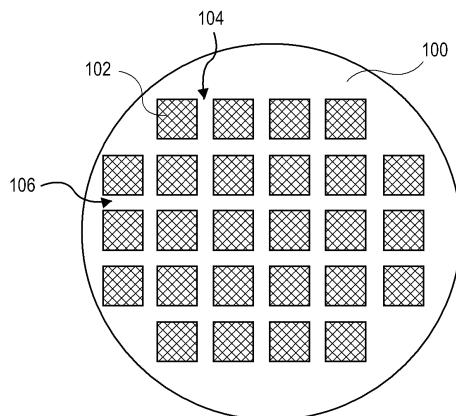

[0013] 도 1은 본 발명의 실시예에 따라, 다이싱될 반도체 웨이퍼의 상단 평면도를 예시한다.

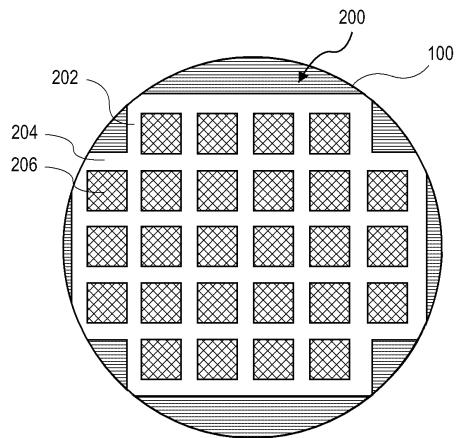

도 2는 본 발명의 실시예에 따라, 그 위에 형성되는 다이싱 마스크를 가지는 다이싱될 반도체 웨이퍼의 상단 평면도를 예시한다.

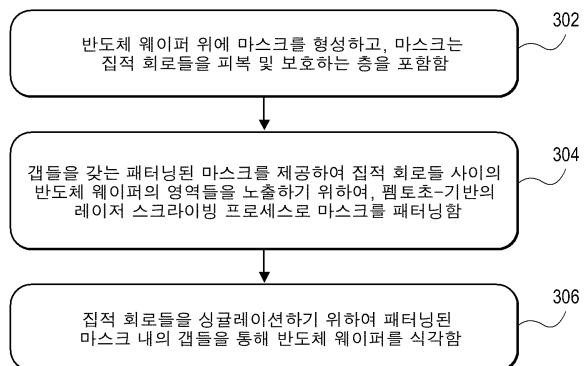

도 3은 본 발명의 실시예에 따라, 복수의 집적 회로들을 포함하는 반도체 웨이퍼를 다이싱하는 방법에서의 동작들을 나타내는 순서도이다.

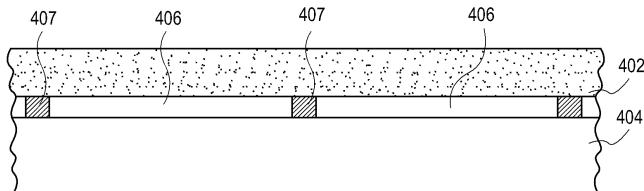

도 4a는 본 발명의 실시예에 따라, 도 3의 순서도의 동작(302)에 대응하는, 반도체 웨이퍼를 다이싱하는 방법을 수행하는 중인 복수의 집적 회로들을 포함하는 반도체 웨이퍼의 단면도를 예시한다.

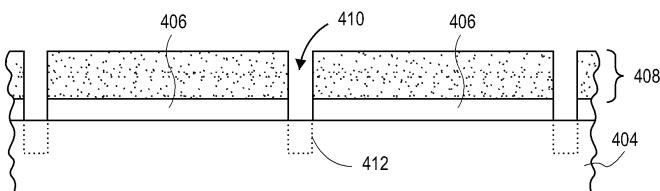

도 4b는 본 발명의 실시예에 따라, 도 3의 순서도의 동작(304)에 대응하는, 반도체 웨이퍼를 다이싱하는 방법을 수행하는 중인 복수의 집적 회로들을 포함하는 반도체 웨이퍼의 단면도를 예시한다.

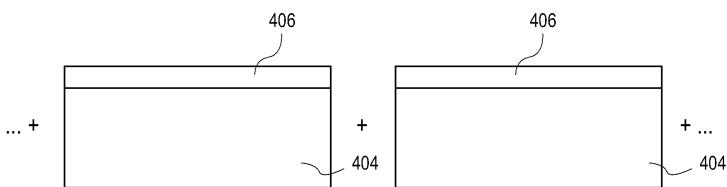

도 4c는 본 발명의 실시예에 따라, 도 3의 순서도의 동작(306)에 대응하는, 반도체 웨이퍼를 다이싱하는 방법을 수행하는 중인 복수의 집적 회로들을 포함하는 반도체 웨이퍼의 단면도를 예시한다.

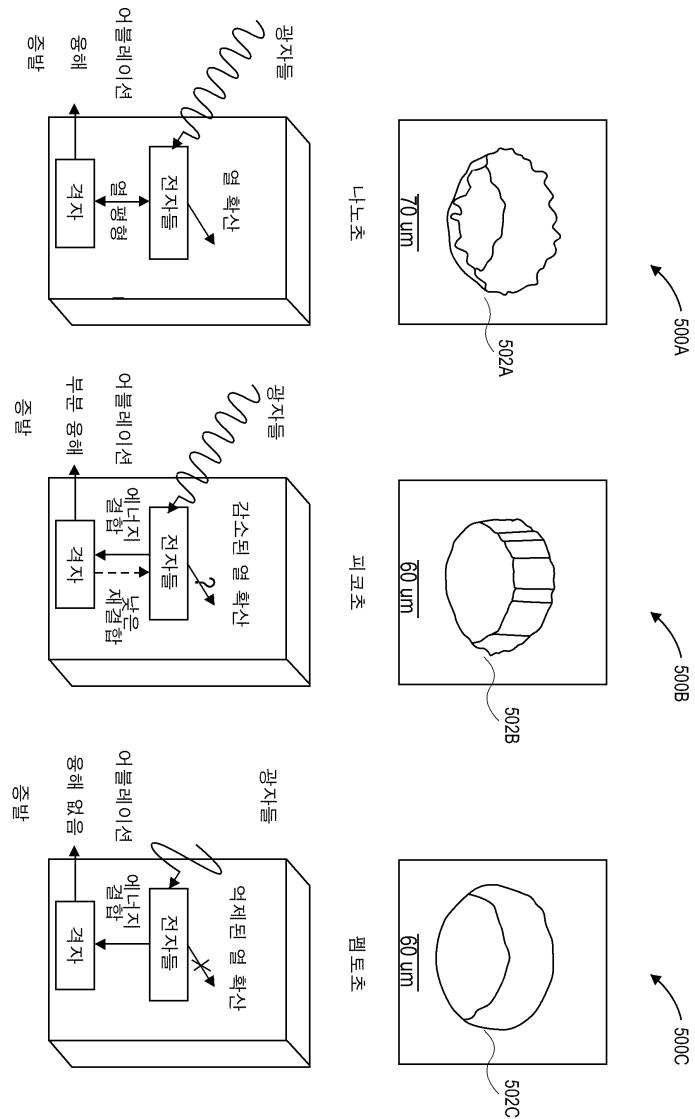

도 5는 본 발명의 실시예에 따라, 펨토초(femtosecond) 범위 대(versus) 더 긴 펄스 시간들에서 레이저 펄스를 이용하는 효과들을 예시한다.

도 6은 본 발명의 실시예에 따라, 반도체 웨이퍼 또는 기판의 스트리트 영역에서 이용될 수 있는 재료들의 적층체(stack)의 단면도를 예시한다.

도 7은 본 발명의 실시예에 따라, 결정질 실리콘(c-Si), 구리(Cu), 결정질 실리콘 디옥사이드(c-SiO<sub>2</sub>), 및 비정질 실리콘 디옥사이드(a-SiO<sub>2</sub>)에 대한 광자 에너지의 함수로서의 흡수 계수의 플롯(plot)을 포함한다.

도 8은 레이저 펄스 에너지, 레이저 펄스 폭, 및 레이저 빔 반경의 함수로서 주어진 레이저에 대한 레이저 강도

의 관계를 도시하는 수학식이다.

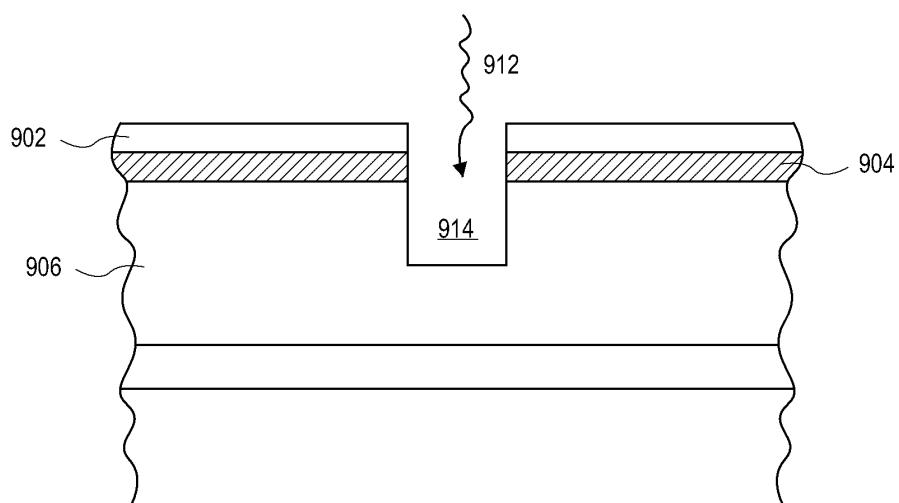

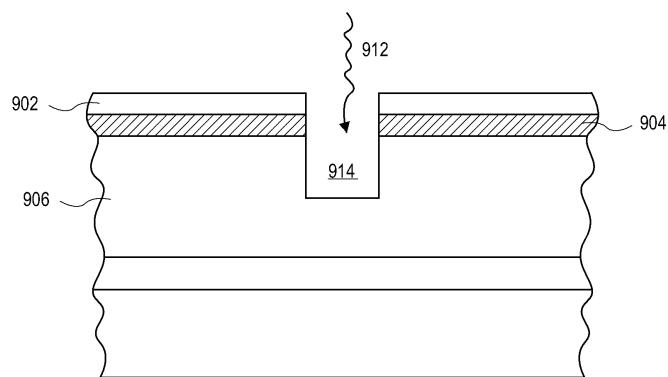

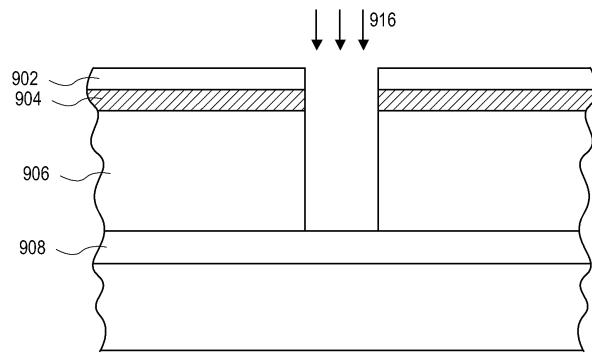

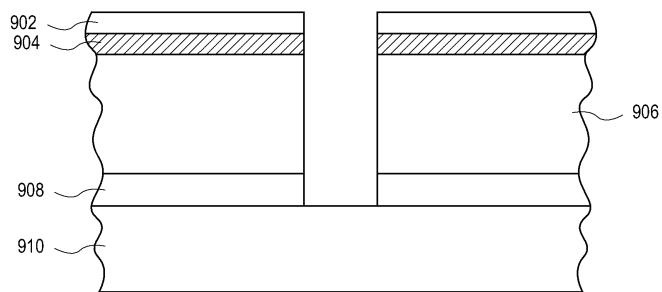

도 9a 내지 도 9d는 본 발명의 실시예에 따라, 반도체 웨이퍼를 다이싱하는 방법에서의 다양한 동작들의 단면도들을 예시한다.

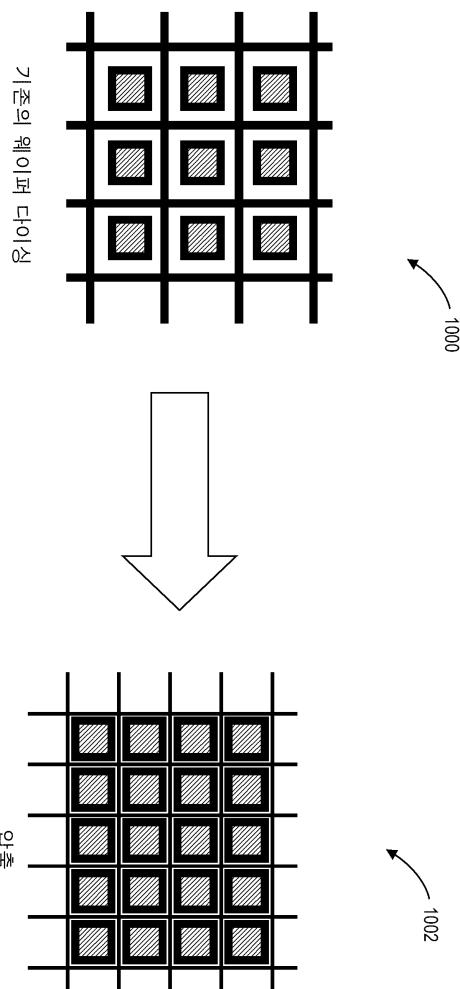

도 10은 본 발명의 실시예에 따라, 최소 폭으로 제한될 수 있는 더 좁은 스트리트들 대 기존의 다이싱을 이용함으로써 달성되는 반도체 웨이퍼 상의 압축을 예시한다.

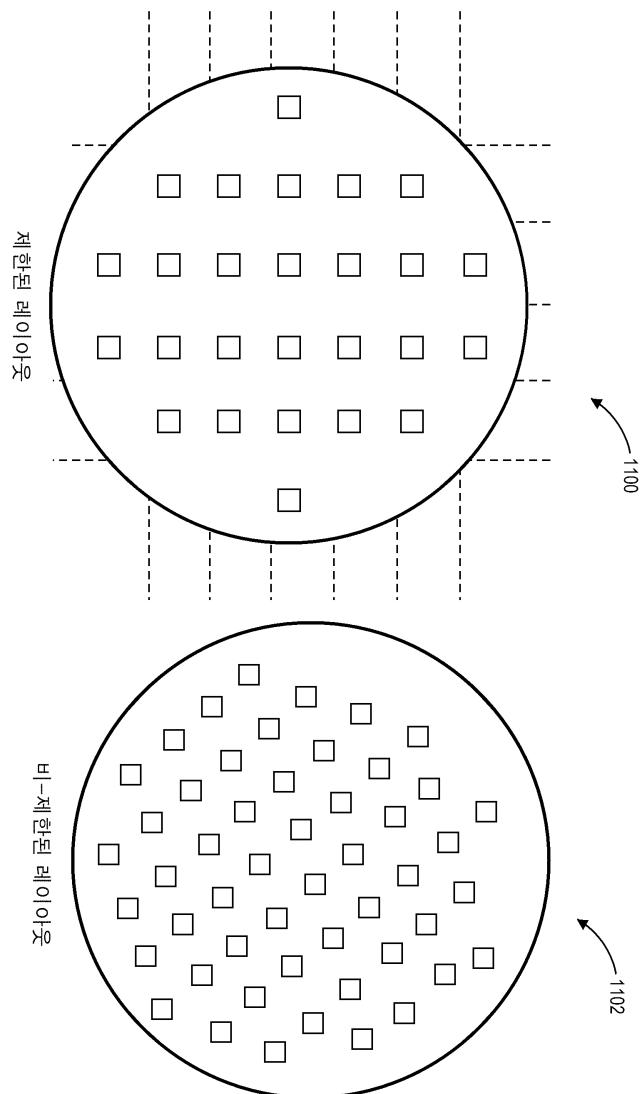

도 11은 본 발명의 실시예에 따라, 더욱 밀도 높은 실장(packing) 및 이에 따라 웨이퍼 당 더 많은 다이를 가능하게 하는 프리폼(preform) 집적 회로 배열 대 격자 배열 방법들을 예시한다.

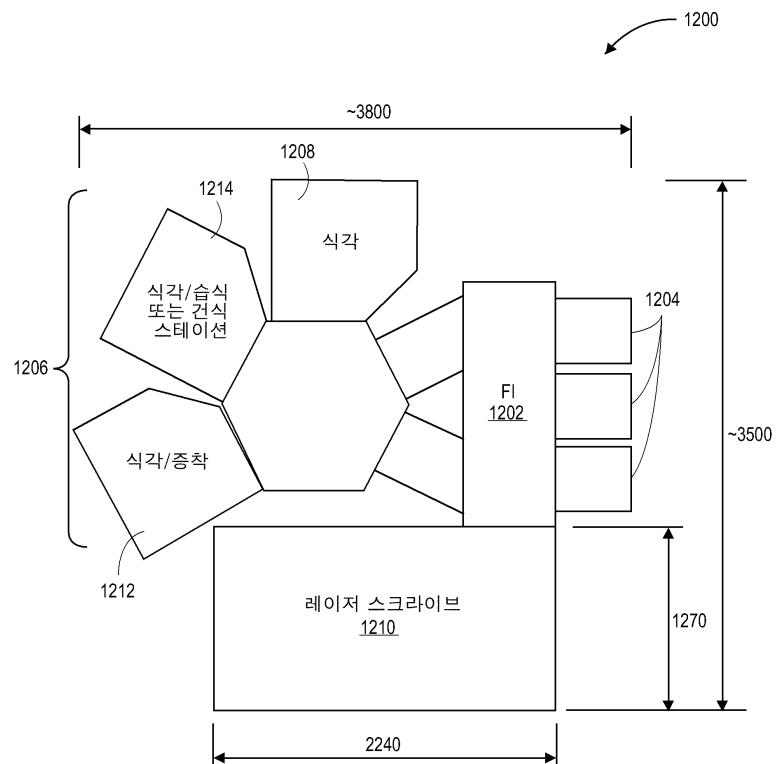

도 12는 본 발명의 실시예에 따라, 웨이퍼들 또는 기판들의 레이저 및 플라즈마 다이싱을 위한 도구 레이아웃의 블록도를 예시한다.

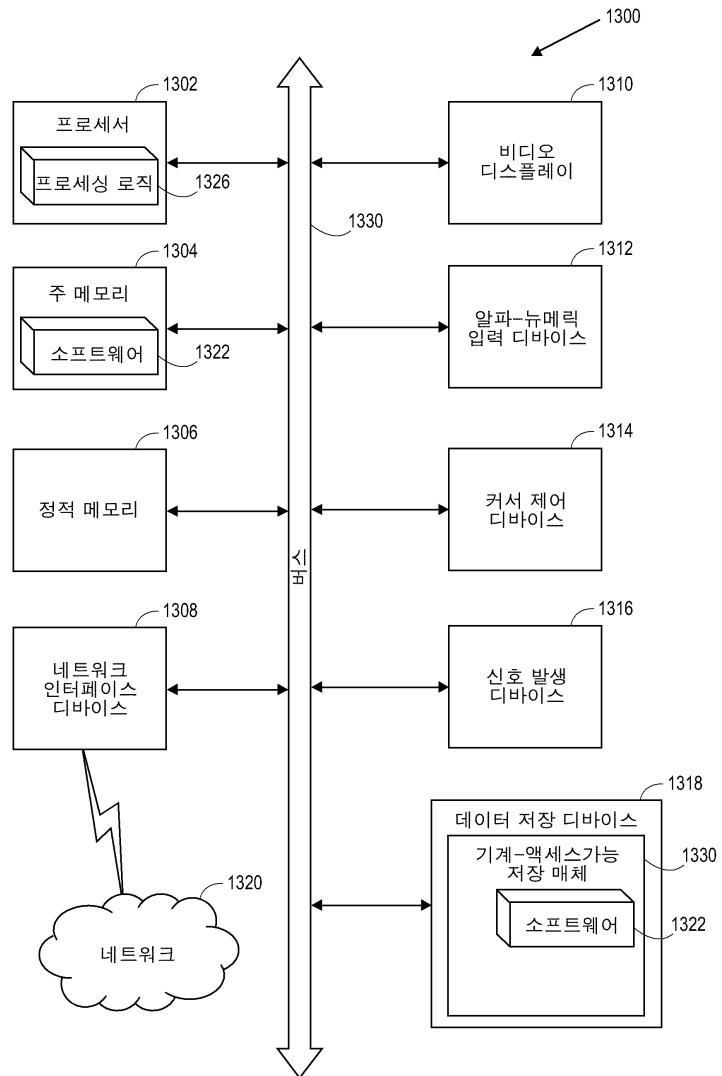

도 13은 본 발명의 실시예에 따라, 예시적인 컴퓨터 시스템의 블록도를 예시한다.

### 발명을 실시하기 위한 구체적인 내용

**[0014]** 각각의 웨이퍼가 그 웨이퍼 상에 복수의 집적 회로들을 가지는 반도체 웨이퍼들을 다이싱하는 방법들이 설명된다. 다음의 설명에서는, 본 발명의 실시예들의 철저한 이해를 제공하기 위하여, 펨토초-기반 레이저 스크라이빙 및 플라즈마 식각 조건들 및 재료 체제(regime)들과 같은 여러 특정한 세부사항들이 기술된다. 본 발명의 실시예들이 이 특정한 세부사항들 없이 실시될 수 있다는 것은 당업자에게 명백할 것이다. 다른 사례들에서, 집적 회로 제조와 같은 잘 알려진 측면들은 본 발명의 실시예들을 불필요하게 모호하게 하지 않기 위하여 상세하게 설명되지 않는다. 또한, 도면들에서 도시된 다양한 실시예들은 예시적인 표면이며 반드시 축척을 조정하도록 도시되어야 하는 것은 아니라는 것을 이해해야 한다.

**[0015]** 초기 레이저 스크라이브(laser scribe) 및 후속 플라즈마 식각(plasma etch)에 관여하는 하이브리드(hybrid) 웨이퍼 또는 기판 다이싱 프로세스는 다이 싱글레이션(die singulation)을 위해 구현될 수 있다. 레이저 스크라이브 프로세스는 마스크 층, 유기 및 무기 유전체 층들, 및 디바이스 층(device layer)들을 깨끗하게 제거하기 위해 이용될 수 있다. 다음으로, 웨이퍼 또는 기판의 노출 또는 부분적인 식각 후에 레이저 식각 프로세스가 종료될 수 있다. 다음으로, 다이싱 프로세스의 플라즈마 식각 부분은 다이 또는 칩 싱글레이션 또는 다이싱을 초래하기 위하여, 별크 단결정(bulk single crystalline) 실리콘 같은 것을 통해, 웨이퍼 또는 기판의 별크(bulk)를 통하여 식각하기 위해 채용될 수 있다.

**[0016]** 기존의 웨이퍼 다이싱 방법들은 순수 기계적 분리에 기초한 다이아몬드 소우 절단, 초기 레이저 스크라이빙 및 후속 다이아몬드 소우 다이싱, 또는 나노초(nanosecond) 또는 피코초(picosecond) 레이저 다이싱을 포함한다. 50 마이크론 두께의 별크 실리콘 싱글레이션과 같은 얇은 웨이퍼 또는 기판 싱글레이션(singulation)을 위하여, 기존의 방법들은 열악한 프로세스 품질만을 산출하였다. 얇은 웨이퍼들 또는 기판들로부터 다이를 싱글레이팅할 때에 직면할 수 있는 과제들 중의 일부는 극소 크랙(microcrack)의 형성이나 상이한 층들 사이의 디라미네이션, 무기 유전체 층들의 침평, 업격한 커프 폭 제어의 유지, 또는 정밀한 어블레이션 깊이 제어를 포함할 수 있다. 본 발명의 실시예들은 상기 과제들을 하나 이상을 해소하기 위해 유용할 수 있는 하이브리드 레이저 스크라이빙(hybrid laser scribing) 및 플라즈마 식각 다이 싱글레이션 방법을 포함한다.

**[0017]** 본 발명의 실시예에 따르면, 반도체 웨이퍼를 개별화된 또는 싱글레이팅된 집적 회로들로 다이싱하기 위하여 펨토초-기반의 레이저 스크라이빙 및 플라즈마 식각의 조합이 이용된다. 하나의 실시예에서, 펨토초-기반의 레이저 스크라이빙은 전체적인 것이 아니라면, 본질적으로 비-열적(non-thermal) 프로세스로서 이용된다. 예를 들어, 펨토초-기반의 레이저 스크라이빙은 전혀 없는 또는 무시할 수 있는 열 손상 구역으로 국소화(localhost) 될 수 있다. 실시예에서, 본 명세서의 방법들은 울트라-로우(ultra-low) k 필름들을 갖는 집적 회로들을 싱글레이팅하기 위해 이용된다. 기존 다이싱에 있어서, 소우(saw)들은 이러한 로우 K 필름들을 수용하기 위하여 느려질 필요가 있을 수 있다. 또한, 반도체 웨이퍼들은 다이싱 이전에 지금은 흔히 박형화(thin)된다. 이와 같이, 실시예에서, 마스크 패터닝, 펨토초-기반의 레이저에 의한 부분적인 웨이퍼 스크라이빙과, 그 후의 플라즈마 식각 프로세스는 이제 실용적이다. 하나의 실시예에서는, 플라즈마 식각 환경에서 다이싱 프로세스를 완료하기 위해 관통-비아 탑입 실리콘 식각이 이용된다.

**[0018]** 따라서, 본 발명의 일 측면에서는, 반도체 웨이퍼를 싱글레이팅된 집적 회로들로 다이싱하기 위하여, 펨토초-기반의 레이저 스크라이빙 및 플라즈마 식각의 조합이 이용될 수 있다. 도 1은 본 발명의 실시예에 따라, 다이싱 될 반도체 웨이퍼의 상단 평면도를 예시한다. 도 2는 본 발명의 실시예에 따라, 반도체 웨이퍼 위에 형성된 다

이상 마스크를 갖는 다이싱될 반도체 웨이퍼의 상단 평면도를 예시한다.

[0019] 도 1을 참조하면, 반도체 웨이퍼(100)는 집적 회로들을 포함하는 복수의 영역(102)들을 가진다. 영역(102)들은 수직 스트리트(204)들 및 수평 스트리트(106)들에 의해 분리된다. 스트리트들(104 및 106)은 집적 회로들을 포함하지 않으며 웨이퍼가 그것을 따라 다이싱될 위치들로서 설계되는 반도체 웨이퍼의 영역들이다. 본 발명의 일부 실시예들은 스트리트들을 따라 반도체 웨이퍼를 통해 트렌치들을 절단하기 위하여 조합된 펌토초-기반의 레이저 스크라이브 및 플라즈마 식각 기술의 이용에 관여하여, 다이들은 개별적인 칩들 또는 다이로 분리된다. 레이저 스크라이브 및 플라즈마 식각 프로세스 둘 모두는 결정 구조의 방위에 독립적이므로, 다이싱될 반도체 웨이퍼의 결정 구조는 웨이퍼를 통해 수직 트렌치를 달성하는 것에 중요하지 않을 수 있다.

[0020] 도 2를 참조하면, 반도체 웨이퍼(100)는 반도체 웨이퍼(100) 상에 증착된 마스크(200)를 가진다. 하나의 실시예에서는, 대략 4 내지 10 마이크론 두께의 층을 달성하기 위하여 마스크가 기존의 방식으로 증착된다. 반도체 웨이퍼(100)가 다이싱될 스트리트들(104 및 106)을 따라 위치들(예를 들어, 캡들(202 및 204))을 정의하기 위하여, 마스크(200) 및 반도체 웨이퍼(100)의 일부는 레이저 스크라이빙 프로세스로 패터닝된다. 반도체 웨이퍼(100)의 집적 회로 영역들은 마스크(200)에 의해 피복 및 보호된다. 마스크(200)의 영역들(206)은, 후속 식각 프로세스 중에, 집적 회로들이 식각 프로세스에 의해 열화되지 않도록 위치된다. 식각 프로세스 중에 식각될 영역들을 정의하여 반도체 웨이퍼(100)를 최종적으로 다이싱하기 위하여, 수평 캡들(204) 및 수직 캡들(202)은 영역들(206) 사이에 형성된다.

[0021] 도 3은 본 발명의 실시예에 따라, 복수의 집적 회로들을 포함하는 반도체 웨이퍼를 다이싱하는 방법에서의 동작들을 나타내는 순서도(300)이다. 도 4a 내지 도 4c는 본 발명의 실시예에 따라, 순서도(300)의 동작들에 대응하는, 반도체 웨이퍼를 다이싱하는 방법을 수행하는 중인 복수의 집적 회로들을 포함하는 반도체 웨이퍼의 단면도들을 예시한다.

[0022] 순서도(300)의 동작(302) 및 대응하는 도 4a를 참조하면, 마스크(402)는 반도체 웨이퍼 또는 기판(204) 위에 형성된다. 마스크(202)는 반도체 웨이퍼(404)의 표면 상에 형성된 집적 회로(406)들을 피복하고 보호하는 층으로 구성된다. 또한, 마스크(402)는 집적 회로(406)들 각각의 사이에 형성된 중간 스트리트(407)들을 피복한다.

[0023] 본 발명의 실시예에 따르면, 마스크(402)를 형성하는 것은 다음으로 한정되지는 않지만, 포토-레지스트 층 또는 I-라인 패터닝(I-line patterning) 층과 같은 층을 형성하는 것을 포함한다. 예를 들어, 포토-레지스트 층과 같은 폴리머 층(polymer layer)은 그렇지 않을 경우에는 리소그래픽 프로세스(lithographic process)에서 이용하기에 적합한 재료로 구성될 수 있다. 하나의 실시예에서, 포토-레지스트 층은 다음으로 한정되지는 않지만, 248 나노미터(nm : nanometer) 레지스트, 193 nm 레지스트, 157 nm 레지스트, 극자외선(EUV : extreme ultraviolet) 레지스트, 또는 디아조나프토퀴논(diazonaphthoquinone) 감광제(sensitizer)를 갖는 폐놀 수지 매트릭스(phenolic resin matrix)와 같은 포지티브(positive) 포토-레지스트 재료로 구성된다. 또 다른 실시예에서, 포토-레지스트 층은 다음으로 한정되지 않지만, 폴리-시스-이소프렌(poly-cis-isoprene) 및 폴리-비닐-신나메이트(poly-vinyl-cinnamate)과 같은 네거티브 포토-레지스트 재료로 구성된다.

[0024] 실시예에서, 반도체 웨이퍼 또는 기판(404)은 제조 프로세스를 견디기에 적합하고 반도체 프로세싱 층들이 그 위에 적합하게 배치될 수 있는 재료로 구성된다. 예를 들어, 하나의 실시예에서, 반도체 웨이퍼 또는 기판(404)은 다음으로 한정되지 않지만, 결정질 실리콘, 게르마늄 또는 실리콘/게르마늄과 같은 IV족-기반(group IV-based) 재료로 구성된다. 특정한 실시예에서, 반도체 웨이퍼(404)를 제공하는 것은 모노결정질(monocrystalline) 실리콘 기판을 제공하는 것을 포함한다. 특정 실시예에서, 단결정질 실리콘 기판은 불순물 원자(impurity atom)들로 도핑된다. 또 다른 실시예에서, 반도체 웨이퍼 또는 기판(404)은 예를 들어, 발광 다이오드(LED)들의 제조 시에 이용되는 III-V족 재료 기판과 같은 III-V족 재료로 구성된다.

[0025] 실시예에서, 반도체 웨이퍼 또는 기판(404)은 집적 회로(406)들의 일부로서, 반도체 디바이스들의 어레이를 그 상부에 또는 그 내부에 배치하였다. 이러한 반도체 디바이스들의 예들은, 다음으로 한정되지는 않지만, 실리콘 기판에서 제조되고 유전체 층에서 감싸는 메모리 디바이스들 또는 상보형 금속-옥사이드-반도체(CMOS : complimentary metal-oxide-semiconductor) 트랜지스터들을 포함한다. 복수의 금속 상호접속부(interconnect)들은 디바이스들 또는 트랜지스터들 위에 그리고 유전체 층들을 둘러쌀 때에 형성될 수 있고, 디바이스들 또는 트랜지스터들을 전기적으로 결합하여 집적 회로(406)들을 형성하기 위해 이용될 수 있다. 스트리트(407)들을 이루는 재료들은 집적 회로(406)들을 형성하기 위해 이용되는 그러한 재료들과 유사하거나 동일할 수 있다. 예를 들어, 스트리트(407)들은 유전체 재료들, 반도체 재료들, 및 금속배선(metallization)의 층들로 구성될 수 있다. 하나의 실시예에서, 스트리트(407)들 중의 하나 이상은 집적 회로(406)들의 실제적인 디바이스들과 유사

한 테스트 디바이스들을 포함한다.

[0026] 순서도(300)의 동작(304)과, 대응하는 도 4b를 참조하면, 갭(gap)(410)들을 갖는 패터닝된 마스크(patterned mask)(408)를 제공하기 위하여, 마스크(402)는 다중-펄스 버스트들을 이용한 펄스 트레인 레이저 스크라이빙 프로세스로 패터닝되어, 집적 회로(406)들 사이의 반도체 웨이퍼 또는 기판(404)의 영역들을 노출한다. 이와 같이, 레이저 스크라이빙 프로세스는 집적 회로(406)들 사이에서 원래 형성되는 스트리트(407)들의 재료를 제거하기 위해 이용된다. 본 발명의 실시예에 따르면, 다중-펄스 버스트들을 이용한 펄스 트레인 레이저 스크라이빙 프로세스로 마스크(402)를 패터닝하는 것은 도 4b에서 도시된 바와 같이, 집적 회로(406)들 사이의 반도체 웨이퍼(404)의 영역들 내로 부분적으로 트렌치(trench)(412)들을 형성하는 것을 포함한다.

[0027] 실시예에서, 레이저 스크라이빙 프로세스로 마스크(406)를 패터닝하는 것은 웨이퍼 위의 펄스 폭을 갖는 레이저를 이용하는 것을 포함한다. 특히, 가시 스펙트럼과, 자외선(UV : ultra-violet) 및 적외선(IR : infra-red) 범위들(총합하여 광대역 광학 스펙트럼)에서의 파장을 갖는 레이저는 웨이퍼 기반의 레이저, 즉, 대략 웨이퍼( $10^{-15}$  초)의 펄스 폭을 갖는 레이저를 제공하기 위하여 이용될 수 있다. 하나의 실시예에서, 어블레이션은 광장 종속적이 아니거나, 본질적으로 광장 종속적이 아니므로, 마스크(402), 스트리트(407), 및 가능하다면, 반도체 웨이퍼 또는 기판(404)의 일부의 필름들과 같은 복합 필름들에 적합하다.

[0028] 도 5는 본 발명의 실시예에 따라, 웨이퍼 위에 더 긴 주파수들의 레이저 펄스를 이용하는 효과들을 예시한다. 도 5를 참조하면, 웨이퍼 위의 펄스 폭을 갖는 레이저를 이용함으로써, 열 손상 문제들은 더 긴 펄스 폭들(예를 들어, 비아(via)(500B)의 피코초 프로세싱에 의한 손상(502B)과 비아(500A)의 나노초 프로세싱에 의한 상당한 손상(502A))에 비해, 열 손상 문제들은 완화되거나 제거될 수 있다(예를 들어, 비아(500C)의 웨이퍼 프로세싱에 의한 손상이 최소 내지 전혀 없음). 비아(500C)의 형성 도중의 손상의 제거 또는 완화는 도 5에 도시된 바와 같이, (피코초 기반의 레이저 어블레이션을 위해 도시되는 바와 같은) 낮은 에너지 재결합(energy recoupling) 또는 (나노초 기반의 레이저 어블레이션을 위해 도시되는 바와 같은) 열 평형의 결여로 인한 것일 수 있다.

[0029] 펄스 폭과 같은 레이저 파라미터들의 선택은 깨끗한 레이저 스크라이브 절단부들을 달성하기 위하여 칩핑, 극소 크랙들 및 디라미네이션을 최소화하는 성공적인 레이저 스크라이빙 및 다이싱 프로세스를 제공하는데 중요할 수 있다. 레이저 스크라이브 절단부가 더 깨끗할수록, 궁극적인 다이싱레이션을 위해 수행될 수 있는 식각 프로세스가 더 유연(smooth)해진다. 반도체 디바이스 웨이퍼들에서, 상이한 재료 유형들(예를 들어, 전도체들, 절연체들, 반전도체들) 및 두께들의 다수의 기능적인 층들은 전형적으로 그 위에 배치된다. 이러한 재료들은 다음으로 한정되지 않지만, 폴리머들과 같은 유기 재료들, 금속들, 또는 실리콘 디옥사이드(silicon dioxide) 및 실리콘 나이트라이드(silicon nitride)와 같은 무기 유전체들을 포함할 수 있다.

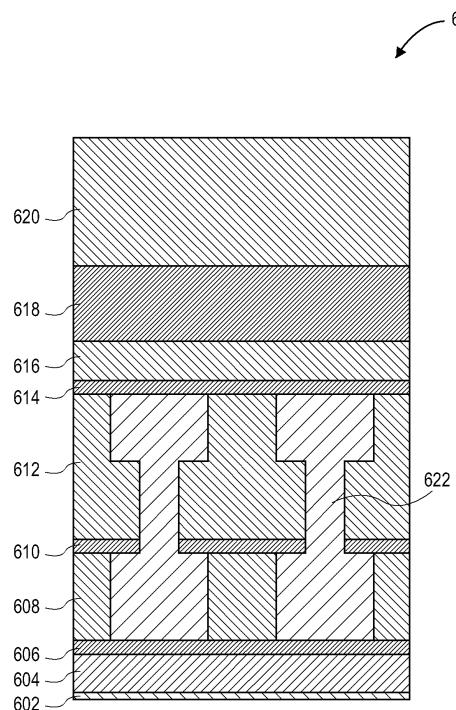

[0030] 웨이퍼 또는 기판 상에 배치된 개별적인 집적 회로들 사이의 스트리트는 집적 회로들 자체와 유사하거나 동일한 층들을 포함할 수 있다. 예를 들어, 도 6은 본 발명의 실시예에 따라, 반도체 웨이퍼 또는 기판의 스트리트 영역에서 이용될 수 있는 재료들의 적층체의 단면도를 예시한다.

[0031] 도 6을 참조하면, 스트리트 영역(600)은, 도시된 상태적인 두께를 갖는, 실리콘 기판의 상단 부분(top portion)(602), 제 1 실리콘 디옥사이드 층(604), 제 1 식각 정지 층(606), 제 1 로우 K(low K) 유전체 층(608)(예를 들어, 실리콘 디옥사이드에 대해 4.0의 유전 상수(dielectric constant)보다 작은 유전 상수를 가짐), 제 2 식각 정지 층(610), 제 2 로우 K 유전체 층(612), 제 3 식각 정지 층(614), 비도팽 실리카 유리(USG : undoped silica glass) 층(616), 제 2 실리콘 디옥사이드 층(618), 및 포토-레지스트의 층(620)을 포함한다. 구리 금속배선(622)은 제 1 및 제 3 식각 정지 층들(606 및 614) 사이에 그리고 제 2 식각 정지 층(610)을 통하여 배치된다. 특정 실시예에서, 제 1, 제 2, 및 제 3 식각 정지 층들(606, 610 및 614)은 실리콘 나이트라이드로 구성되는 반면, 로우 K 유전체 층들(608 및 612)은 탄소 도핑된(carbon-doped) 실리콘 옥사이드 재료로 구성된다.

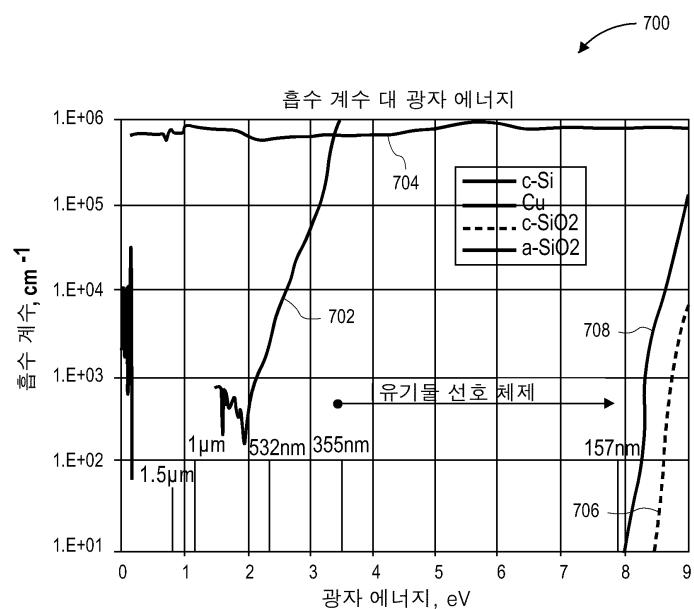

[0032] (나노초-기반 또는 피코초-기반의 레이저 조사와 같은) 기존의 레이저 조사(laser irradiation) 하에서, 스트리트(600)의 재료들은 광학적 흡수 및 어블레이션 메커니즘들의 측면에서 상당히 상이하게 거동한다. 예를 들어, 실리콘 디옥사이드와 같은 유전체 층들은 정상적인 조건들 하에서 모든 상업적으로 이용가능한 레이저 파장들에 대해 본질적으로 투명하다. 이와 대조적으로, 금속들, 유기물들(예를 들어, 로우 K 재료들) 및 실리콘은 광자(photon)들을 매우 용이하게, 특히, 나노초-기반 또는 피코초-기반의 레이저 조사에 응답하여 결합할 수 있다. 예를 들어, 도 7은 본 발명의 실시예에 따라, 결정질 실리콘(c-Si, 702), 구리(Cu, 704), 결정질 실리콘 디옥사이드(c-SiO<sub>2</sub>, 706), 및 비정질 실리콘 디옥사이드(a-SiO<sub>2</sub>, 708)에 대한 광자 에너지의 함수로서의 흡수 계수의

플롯(plot)(700)을 포함한다. 도 8은 레이저 펄스 에너지, 레이저 펄스 폭, 및 레이저 빔 반경의 함수로서 주어진 레이저에 대한 레이저 강도의 관계를 도시하는 수학식(800)이다.

[0033] 수학식(800) 및 흡수 계수들의 플롯(700)을 이용하면, 실시예에서, 펨토초 레이저-기반의 프로세스에 대한 파라미터들은, 이러한 재료들의 일반적인 에너지 흡수 특성들이 특정 조건들 하에서 폭넓게 상이할 수 있더라도, 무기 및 유기 유전체들, 금속들, 및 반도체들에 대한 본질적으로 공통적인 어블레이션 효과를 가지도록 선택될 수 있다. 예를 들어, 실리콘 디옥사이드의 흡수율은 비-선형(non-linear)이고, 적합한 레이저 어블레이션 파라미터들 하에서 유기 유전체들, 반도체들 및 금속들의 흡수율과 더욱 비슷하게 될 수 있다. 이러한 하나의 실시예에서, 높은 강도 및 짧은 펄스 폭의 펨토초-기반의 레이저 프로세스는 실리콘 디옥사이드 충파, 유기 유전체, 반도체, 또는 금속 중의 하나 이상을 포함하는 충돌의 적층체를 어블레이팅하기 위해 이용된다. 특정 실시예에서, 마스크, 스트리트, 및 실리콘 기판의 일부를 제거하기 위하여, 대략 400 펨토초 이하의 펄스들이 펨토초-기반의 레이저 조사 프로세스에서 이용된다.

[0034] 이와 대조적으로, 최적이 아닌 레이저 파라미터들이 선택되면, 무기 유전체, 유기 유전체, 반도체, 또는 금속의 둘 이상과 관여되는 적층들 구조들에서는, 레이저 어블레이션 프로세스가 디라미네이션 문제들을 야기시킬 수 있다. 예를 들어, 레이저는 측정가능한 흡수 없이 (대략 9 eV 밴드갭(bandgap)을 갖는 실리콘 디옥사이드와 같은) 높은 밴드갭 에너지 유전체들을 관통한다. 그러나, 레이저 에너지는 기저 금속 또는 실리콘 충에서 흡수될 수 있고, 이것은 금속 또는 실리콘 충들의 상당한 기화(vaporization)를 야기시킨다. 기화는 위에 놓인 실리콘 디옥사이드 유전체 충을 들어올리기 위한 높은 압력을 발생시킬 수 있고, 이것은 극심한 충간 디라미네이션 및 극소 크랙킹(microcracking)을 잠재적으로 야기시킨다. 실시예에서는, 피코초-기반의 레이저 조사 프로세스들이 복합 적층체들에서의 극소 크랙킹 및 디라미네이팅에 이르게 하지만, 펨토초-기반의 레이저 조사 프로세스들은 동일한 재료의 적층체들의 극소 크랙킹 또는 디라미네이션에 이르게 하지 않음을 증명하였다.

[0035] 유전체 충들을 직접 어블레이팅할 수 있기 위하여, 유전체 재료들의 이온화가 발생할 필요가 있을 수 있어서, 이들은 강하게 흡수하는 광자들에 의해 전도성 재료와 유사하게 거동한다. 흡수는 레이저 에너지가 유전체 충의 궁극적인 어블레이션 전에 레이저 에너지의 대부분이 기저의 실리콘 또는 금속 충들까지 관통하는 것을 차단할 수 있다. 실시예에서는, 레이저 강도가 광자 이온화를 개시시키고 무기 유전체 재료들에서의 이온화에 영향을 줄 정도로 충분히 높을 때, 무기 유전체들의 이온화가 실현 가능하다.

[0036] 본 발명의 실시예에 따르면, 적합한 펨토초-기반의 레이저 프로세스들은 흔히 다양한 재료들에서의 비선형 상호 작용(interaction)들에 이르게 하는 높은 피크 강도(irradiance : 조도)에 의해 특징된다. 이러한 하나의 실시예에서, 펨토초 레이저 소스들은 바람직하게는, 100 펨토초 내지 400 펨토초의 범위이지만, 대략 10 펨토초 내지 500 펨토초의 범위인 펄스 폭을 가진다. 하나의 실시예에서, 펨토초 레이저 소스들은 바람직하게는, 540 나노미터 내지 250 나노미터의 범위이지만, 대략 1570 나노미터 내지 200 나노미터의 범위인 파장을 가진다. 하나의 실시예에서, 레이저 및 대응하는 광학계(optical system)는 바람직하게는, 대략 5 마이크론(micron) 내지 10 마이크론의 범위이지만, 대략 3 마이크론 내지 15 마이크론의 범위인 작업 표면(work surface)에서 초점(focal spot)을 제공한다.

[0037] 작업 표면에서의 공간 빔 프로파일(spacial beam profile)은 단일 모드(가우시안(Gaussian))일 수 있거나, 성형된 텁햇(top-hat) 프로파일을 가질 수 있다. 실시예에서, 레이저 소스는 바람직하게는, 대략 500 kHz 내지 5 MHz의 범위이지만, 대략 200 kHz 내지 10 MHz 범위인 펄스 반복 레이트를 가진다. 실시예에서, 레이저 소스는 바람직하게는, 대략 1 uJ 내지 5 uJ의 범위이지만, 대략 0.5 uJ 내지 100 uJ의 범위인 작업 표면에서 펄스 에너지를 전달한다. 실시예에서, 레이저 스크라이빙 프로세스는 바람직하게는, 대략 600 mm/sec 내지 2 m/sec의 범위이지만, 대략 500 mm/sec 내지 5 m/sec의 범위인 속도로 작업물(work piece) 표면을 따라 행해진다.

[0038] 스크라이빙 프로세스는 오직 단일 경로에서 또는 다수 경로들에서 행해질 수 있지만, 실시예에서, 바람직하게는 1 내지 2 경로들에서 행해질 수 있다. 하나의 실시예에서, 작업물에서의 스크라이빙 깊이는 대략 5 마이크론 내지 50 마이크론 깊이의 범위, 바람직하게는, 대략 10 마이크론 내지 20 마이크론 깊이의 범위이다. 레이저는 주어진 펄스 반복 레이트에서 단일 펄스들의 트레인에서, 또는 펄스 버스트들의 트레인에서 적용될 수 있다. 실시예에서, 발생되는 레이저 빔의 커프 폭(kef width)은 실리콘 웨이퍼 스크라이빙/다이싱에서, 바람직하게는, 디바이스/실리콘 계면에서 측정되는 대략 6 마이크론 내지 10 마이크론의 범위이지만, 대략 2 마이크론 내지 15 마이크론의 범위이다.

[0039] 무기 유전체들의 어블레이션을 지시하기 전에 무기 유전체(예를 들어, 실리콘 디옥사이드)의 이온화를 달성하고 기저층(under layer) 손상에 의해 야기되는 디라미네이션 및 침평을 최소화하기 위하여 충분히 높은 레이저 강도

를 제공하는 것과 같은 이점들 및 장점들로 레이저 파라미터들이 선택될 수 있다. 또한, 정밀하게 제어되는 어블레이션 폭(예를 들어, 커프 폭) 및 깊이를 갖는 공업적 응용들을 위한 의미 있는 프로세스 스루풋을 제공하기 위하여 파라미터들이 선택될 수 있다. 위에서 설명된 바와 같이, 펨토초-기반의 레이저는 피코초-기반 및 나노초-기반의 레이저 어블레이션 프로세스들에 비해, 이러한 장점들을 제공하기에 훨씬 더 적합하다. 그러나, 펨토초-기반의 레이저 어블레이션의 스펙트럼에서도, 특정 파장들은 그 외의 것들보다 양호한 성능을 제공할 수 있다. 예를 들어, 하나의 실시예에서, UV 범위에 근접하거나 UV 범위 내의 파장을 갖는 펨토초-기반의 레이저 프로세스는 IR 범위에 근접하거나 IR 범위 내의 파장을 갖는 펨토초-기반의 레이저 프로세스보다 깨끗한 어블레이션 프로세스를 제공한다. 이러한 특정 실시예에서, 반도체 웨이퍼 또는 기판 스크라이빙에 적합한 펨토초-기반의 레이저 프로세스는 대략 540 나노미터 이하의 파장을 갖는 레이저에 기초하고 있다. 이러한 구체적인 실시예에서, 대략 540 나노미터 이하의 파장을 갖는 레이저의 대략 400 펨토초 이하의 폴스들이 이용된다. 그러나, 대안적인 실시예에서는, 듀얼(dual) 레이저 파장들(예를 들어, IR 레이저 및 UV 레이저의 조합)이 이용된다.

[0040] 순서도(300)의 동작(306)과, 대응하는 도 4c를 참조하면, 집적 회로(406)들을 싱글레이팅하기 위하여, 반도체 웨이퍼(404)는 패터닝된 마스크(408) 내의 캡(410)들을 통하여 식각된다. 본 발명의 실시예에 따르면, 반도체 웨이퍼(404)를 식각하는 것은 도 4c에 도시된 바와 같이, 반도체 웨이퍼(404)를 완전히 통하여 궁극적으로 식각하기 위하여, 펨토초-기반의 레이저 스크라이빙 프로세스로 형성된 트렌치(412)들을 식각하는 것을 포함한다.

[0041] 실시예에서, 반도체 웨이퍼(404)를 식각하는 것은 플라즈마 식각 프로세스를 이용하는 것을 포함한다. 하나의 실시예에서는, 관통-실리콘 비아 타입 식각 프로세스(through-silicon via type etch process)가 이용된다. 예를 들어, 특정 실시예에서, 반도체 웨이퍼(404)의 재료의 식각 레이트는 분당 25 마이크론(25 microns per minute)보다 크다. 초고밀도 플라즈마 소스(ultra-high-density plasma source)는 다이 싱글레이션 프로세스의 플라즈마 식각 부분을 위해 이용될 수 있다. 이러한 플라즈마 식각 프로세스를 수행하기 위해 적합한 프로세스 챔버의 예는 미국, 캘리포니아, 썬니베일(Sunnyvale)의 Applied Materials로부터 입수 가능한 Applied Centura® Silvia™ 식각 시스템이다. Applied Centura® Silvia™ 식각 시스템은 용량성(capacitive) 및 유도성(inductive) RF 결합(RF coupling)을 합성(combine)하고, 이것은 오직 용량성 결합에 의해, 심지어 자기적 강화(magnetic enhancement)에 의해 제공되는 개선사항들에 의해 가능하였던 이온 밀도 및 이온 에너지의 훨씬 더 독립적인 제어를 제공한다. 잠재적으로 손상시키는 높은 DC 바이어스 레벨들을 갖지 않는 상대적으로 고밀도의 플라즈마들을 심지어 매우 낮은 압력들에서 달성하기 위하여, 이 합성은 이온 에너지로부터 이온 밀도의 효과적인 결합해제(decoupling)를 가능하게 한다. 이것은 예외적으로 폭이 넓은 프로세스 윈도우(process window)로 귀착된다. 그러나, 실리콘을 식각할 수 있는 임의의 플라즈마 식각 챔버가 이용될 수 있다. 예시적인 실시예에서는, 본질적으로 정밀한 프로파일 제어 및 사실상 스캐립-제거된(scallop-free) 측벽들을 유지하면서, 기존의 실리콘 식각 레이트들의 대략 40%보다 큰 식각 레이트로 단결정 실리콘 기판 또는 웨이퍼(404)를 식각하기 위하여 딥 실리콘 식각(deep silicon etch)이 이용된다. 특정 실시예에서는, 관통-실리콘 비아 타입 식각 프로세스가 이용된다. 상기 식각 프로세스는 일반적으로 SF<sub>6</sub>, C<sub>4</sub>F<sub>8</sub>, CHF<sub>3</sub>, XeF<sub>2</sub>와 같은 불소기반 가스(Fluorine-based gas) 또는 상대적으로 고속의 식각 레이트로 실리콘을 식각할 수 있는 임의의 다른 반응 가스인 반응성 가스로부터 발생되는 플라즈마에 기초하고 있다. 실시예에서, 마스크 층(408)은 도 4c에 도시된 바와 같이, 싱글레이션 프로세스 후에 제거된다.

[0042] 따라서, 순서도(300) 및 도 4a 내지 도 4c를 다시 참조하면, 마스크 층을 통해, 웨이퍼 스트리트들(금속배선을 포함함)을 통하여, 그리고 부분적으로 실리콘 기판 내로의 초기 레이저 어블레이션에 의해 웨이퍼 다이싱이 수행될 수 있다. 레이저 폴스 폭은 펨토초 범위에서 선택될 수 있다. 다음으로, 다이 싱글레이션은 후속 관통-실리콘 딥 플라즈마 식각에 의해 완료될 수 있다. 본 발명의 실시예에 따르면, 다이싱을 위한 재료 적층체의 특정 예가 도 9a 내지 도 9d에 따라 이하에 설명된다.

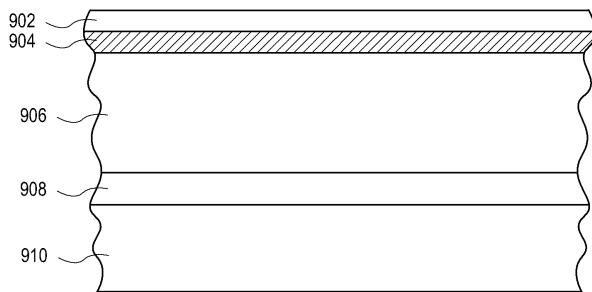

[0043] 도 9a를 참조하면, 하이브리드 레이저 어블레이션 및 플라즈마 식각 다이싱을 위한 재료 적층체는 마스크 층(902), 디바이스 층(904), 및 기판(906)을 포함한다. 마스크 층, 디바이스 층 및 기판은 백킹 테이프(backing tape)(910)에 고착(affix)되는 다이 부착 필름(die attach film)(908) 위에 배치된다. 실시예에서, 마스크 층(902)은 마스크(402)와 연계하여 위에서 설명된 포토-레지스트 층들과 같은 포토-레지스트 층이다. 디바이스 층(904)은 (구리 층들과 같은) 하나 이상의 금속 층들 위에 배치된 (실리콘 디옥사이드와 같은) 무기 유전체 층과, (탄소 도핑된 옥사이드 층들과 같은) 하나 이상의 로우 K 유전체 층들을 포함한다. 또한, 디바이스 층(904)은 집적 회로를 사이에 배열된 스트리트들을 포함하고, 스트리트들은 집적 회로들에 대한 동일하거나 유사한 층들을 포함한다. 기판(906)은 별크 단결정 실리콘 기판이다.

[0044] 실시예에서, 별크 단결정 실리콘 기판(906)은 다이 부착 필름(908)에 고착되기 전에 이면(backside)으로부터 박형화(thin) 된다. 박형화는 이면 그라인드 프로세스(backside grind process)에 의해 수행될 수 있다. 하나의 실시예에서, 별크 단결정 실리콘 기판(906)은 대략 50 내지 100 마이크론의 범위의 두께로 박형화된다. 실시예에서, 박형화는 레이저 어블레이션 및 플라즈마 식각 다이싱 프로세스 이전에 수행되는 것을 주목하는 것이 중요하다. 실시예에서, 포토-레지스트 층(902)은 대략 5 마이크론의 두께를 가지고, 디바이스 층(904)은 대략 2 내지 3 마이크론의 범위의 두께를 가진다. 실시예에서, 다이 부착 필름(908)(또는 박형화된 또는 얇은 웨이퍼 또는 기판을 백킹 테이프(910)에 본딩할 수 있는 임의의 적합한 대체물)은 대략 20 마이크론의 두께를 가진다.

[0045] 도 9b를 참조하면, 기판(906) 내에 트렌치(914)들을 형성하기 위하여, 마스크(902), 디바이스 층(904) 및 기판(906)의 일부가 다중-펄스 버스트(912)들을 이용한 펄스 트레인 레이저 스크라이빙 프로세스로 패터닝된다. 도 9c를 참조하면, 다이 부착 필름(908) 아래로 트렌치(914)를 연장하기 위하여 관통-실리콘 딥 플라즈마 식각 프로세스(916)가 이용되어, 다이 부착 필름(908)의 상단 부분을 노출하고 실리콘 기판(906)을 싱글레이팅한다. 디바이스 층(904)은 관통-실리콘 딥 플라즈마 식각 프로세스(916) 동안에 포토-레지스트 층(902)에 의해 보호된다.

[0046] 도 9d를 참조하면, 싱글레이션 프로세스는 다이 부착 필름(908)을 패터닝하는 것, 백킹 테이프(910)의 상단 부분을 노출하는 것, 및 다이 부착 필름(908)을 싱글레이팅하는 것을 더 포함할 수 있다. 실시예에서, 다이 부착 필름은 레이저 프로세스에 의해 또는 식각 프로세스에 의해 싱글레이팅된다. 추가적인 실시예들은 추후에 백킹 테이프(910)로부터 (예를 들어, 개별적인 집적 회로들로서) 기판(906)의 싱글레이팅된 부분들을 제거하는 것을 포함할 수 있다. 하나의 실시예에서, 싱글레이팅된 다이 부착 필름(908)은 기판(906)의 싱글레이팅된 부분들의 이면들 상에 유지된다. 다른 실시예들은 디바이스 층(904)으로부터 마스킹 포토-레지스트 층(902)을 제거하는 것을 포함할 수 있다. 대안적인 실시예에서, 기판(906)이 대략 50 마이크론보다 더 얇을 경우, 레이저 어블레이션 프로세스(912)는 추가적인 플라즈마 프로세스를 이용하지 않고 기판(906)을 완전히 싱글레이팅하기 위해 이용된다.

[0047] 다이 부착 필름(908)을 싱글레이팅한 이후에, 실시예에서, 마스킹 포토-레지스트 층(902)은 디바이스 층(904)으로부터 제거된다. 실시예에서, 싱글레이팅된 집적 회로들은 패키징(packaging)을 위하여 백킹 테이프(910)로부터 제거된다. 이러한 하나의 실시예에서, 패터닝된 다이 부착 필름(908)은 각각의 집적 회로의 이면 상에 유지되고 최종 패키징 내에 포함된다. 그러나, 또 다른 실시예에서, 패터닝된 다이 부착 필름(908)은 싱글레이션 프로세스 동안에 또는 그 이후에 제거된다.

[0048] 도 4a 내지 도 4c를 다시 참조하면, 복수의 집적 회로(406)들은 대략 10 마이크론 이하의 폭을 갖는 스트리트(407)들에 의해 분리될 수 있다. 레이저의 밀집된 프로파일 제어에 적어도 부분적으로 기인한, 웨이퍼-기반의 레이저 스크라이빙 방법의 이용은 집적 회로들의 레이아웃에서의 이러한 압축(compactation)을 가능하게 할 수 있다. 예를 들어, 도 10은 본 발명의 실시예에 따라, 최소 폭으로 제한될 수 있는 기존의 다이싱 대 더 좁은 스트리트들을 이용함으로써 달성되는 반도체 웨이퍼 또는 기판 상의 압축을 예시한다.

[0049] 도 10을 참조하면, 최소 폭(예를 들어, 레이아웃(1000)에 있어서 대략 70 마이크론 이상인 폭들)으로 제한될 수 있는 기존의 다이싱 대 더 좁은 스트리트들(예를 들어, 레이아웃(1002)에 있어서 대략 10 마이크론 이하인 폭들)을 이용함으로써 반도체 웨이퍼 상에서의 압축이 달성된다. 그러나, 웨이퍼-기반의 레이저 스크라이빙 프로세스에 의해 가능하게 되더라도, 10 마이크론 미만으로 스트리트 폭을 감소시키는 것이 항상 바람직하지는 않을 수 있음을 이해해야 한다. 예를 들어, 일부 응용들은 집적 회로들을 분리하는 스트리트들에서 더미 또는 테스트 디바이스들을 제조하기 위하여 적어도 40 마이크론의 스트리트 폭을 요구할 수 있다.

[0050] 도 4a 내지 도 4c를 다시 참조하면, 복수의 집적 회로(406)들은 비-제한적인 레이아웃에서 반도체 웨이퍼 또는 기판(404) 상에 배열될 수 있다. 예를 들어, 도 11은 밀도가 더 높은 실장을 허용하는 프리폼 집적 회로 배열을 예시한다. 밀도가 더 높은 실장은 본 발명의 실시예에 따라, 웨이퍼 당 더 많은 다이 대 격자 배열 방법들을 제공할 수 있다. 도 11을 참조하면, 프리폼 레이아웃(예를 들어, 반도체 웨이퍼 또는 기판(1102) 상의 비-제한적 레이아웃)은 밀도가 더 높은 실장 및 이에 따라, 웨이퍼 당 더 많은 다이 대 격자 배열 방법들(예를 들어, 반도체 웨이퍼 또는 기판(1100) 상의 제한된 레이아웃)을 가능하게 한다. 실시예에서, 레이저 어블레이션 및 플라즈마 식각 싱글레이션 프로세스의 속도는 다이 크기, 레이아웃, 또는 스트리트들의 수에 독립적이다.

[0051] 단일 프로세스 도구는 하이브리드 웨이퍼-기반의 레이저 어블레이션 및 플라즈마 식각 싱글레이션 프로세스에서의 동작들의 다수 또는 전부를 수행하도록 구성될 수 있다. 예를 들어, 도 12는 본 발명의 실시예에 따라, 웨이

퍼들 또는 기판들의 레이저 및 플라즈마 다이싱을 위한 도구 레이아웃(tool layout)의 블록도를 예시한다.

[0052] 도 12를 참조하면, 프로세스 도구(1200)는 팩토리 인터페이스(1202)(FI : factory interface)와 결합된 복수의 로드락(load lock)(1204)들을 갖는 팩토리 인터페이스(1202)(FI)를 포함한다. 클러스터 도구(cluster tool)(1206)는 팩토리 인터페이스(1202)와 결합된다. 클러스터 도구(1206)는 플라즈마 식각 챔버(1208)와 같은, 하나 이상의 플라즈마 식각 챔버들을 포함한다. 또한, 레이저 스크라이브 장치(1210)는 팩토리 인터페이스(1202)에 결합된다. 하나의 실시예에서, 프로세스 도구(1200)의 전체 차지 면적(footprint)은 도 12에 도시된 바와 같이, 대략 3500 밀리미터(3.5 미터) X 대략 3800 밀리미터(3.8 미터)일 수 있다.

[0053] 실시예에서, 레이저 스크라이브 장치(1210)는 웹토초-기반의 레이저를 수용한다. 웹토초-기반의 레이저는 위에서 설명된 레이저 어블레이션 프로세스들과 같은 하이브리드 레이저 및 식각 싱글레이션 프로세스의 레이저 어블레이션 부분을 수행하기에 적합하다. 하나의 실시예에서는, 가동 스테이지(moveable stage)가 레이저 스크라이브 장치(1210) 내에 또한 포함되고, 가동 스테이지는 웹토초-기반의 레이저에 대해 웨이퍼 또는 기판(또는 그 캐리어(carrier))을 이동하기 위해 구성된다. 특정 실시예에서는, 웹토초-기반의 레이저도 가동성(moveable)이다. 하나의 실시예에서, 레이저 스크라이브 장치(1210)의 전체 차지 면적은 도 12에 도시된 바와 같이, 대략 2240 밀리미터 X 대략 1270 밀리미터일 수 있다.

[0054] 실시예에서, 하나 이상의 플라즈마 식각 챔버(1208)들은 복수의 접적 회로들을 성글레이팅하기 위해 패터닝된 마스크에서 캡(gap)들을 통하여 웨이퍼 또는 기판을 식각하기 위해 구성된다. 이러한 하나의 실시예에서, 하나 이상의 플라즈마 식각 챔버(1208)들은 딥 실리콘 식각 프로세스(deep silicon etch process)를 수행하도록 구성된다. 특정 실시예에서, 하나 이상의 플라즈마 식각 챔버(1208)들은 미국, 캘리포니아, 써니베일(Sunnyvale)의 Applied Materials로부터 이용가능한 Applied Centura® Silvia™ 식각 시스템이다. 식각 챔버는 단결정 실리콘 기판들 또는 웨이퍼들 상에 또는 그 내부에 수용되는 성글레이팅 접적 회로들을 생성하기 위해 이용되는 딥 실리콘 식각을 위하여 특별히 설계될 수 있다. 실시예에서, 고밀도(high-density) 플라즈마 소스는 높은 실리콘 식각 레이트들을 가능하게 하기 위하여 플라즈마 식각 챔버(1208) 내에 포함된다. 실시예에서, 성글레이션 또는 다이싱 프로세스의 높은 제조 스루풋(manufacturing throughput)을 가능하게 하기 위하여, 하나를 초과하는 식각 챔버가 프로세스 도구(1200)의 클러스터 도구(1206) 부분 내에 포함된다.

[0055] 팩토리 인터페이스(1202)는 레이저 스크라이브 장치(1210)를 갖는 외부 제조 설비 및 클러스터 도구(1206) 사이를 인터페이스하기 위한 적합한 대기 포트(atmospheric port)일 수 있다. 팩토리 인터페이스(1202)는 (전방 개방 통합 포드(front opening unified pod)와 같은) 저장 유닛들로부터 클러스터 도구(1206)나 레이저 스크라이브 장치(1210), 또는 이 둘 모두로 웨이퍼들(또는 그 캐리어들)을 이송하기 위한 아암(arm)들 또는 블레이드(blade)들을 갖는 로봇(robot)들을 포함할 수 있다.

[0056] 클러스터 도구(1206)는 성글레이션 방법에서의 기능들을 수행하기에 적합한 다른 챔버들을 포함할 수 있다. 예를 들어, 하나의 실시예에서는, 추가적인 식각 챔버 대신에, 증착 챔버(1212)가 포함된다. 증착 챔버(1212)는 웨이퍼 또는 기판의 레이저 스크라이빙 이전에 웨이퍼 또는 기판의 디바이스 층의 상에 또는 그 위에서의 마스크 증착(mask deposition)을 위해 구성될 수 있다. 이러한 하나의 실시예에서, 증착 챔버(1212)는 포토-레지스트 층을 증착하기에 적합하다. 또 다른 실시예에서는, 추가적인 식각 챔버 대신에, 습식/건식 스테이션(wet/dry station)(1214)이 포함된다. 습식/건식 스테이션은 기판 또는 웨이퍼의 레이저 스크라이브 및 플라즈마 식각 성글레이션 프로세스에 후속하여, 잔류물(residue)들 및 파편(fragment)들을 세정하거나 마스크를 제거하기에 적합할 수 있다. 실시예에서, 계측 스테이션(metrology station)이 프로세스 도구(1200)의 부품으로서 또한 포함된다.

[0057] 본 발명의 실시예들은 본 발명의 실시예들에 따라 프로세스를 수행하기 위하여 컴퓨터 시스템(또는 다른 전자 디바이스들)을 프로그램하도록 이용될 수 있는 명령어(instruction)들을 그 위에 저장한 기계-판독가능 매체(machine-readable medium)를 포함할 수 있는 컴퓨터 프로그램 제품 또는 소프트웨어로서 제공될 수 있다. 하나의 실시예에서, 컴퓨터 시스템은 도 12와 연계하여 설명된 프로세스 도구(1200)와 결합된다. 기계-판독가능 매체는 기계(예를 들어, 컴퓨터)에 의해 판독가능한 형태로 정보를 저장 또는 송신하기 위한 임의의 메커니즘(mechanism)을 포함한다. 예를 들어, 기계-판독가능(예를 들어, 컴퓨터-판독가능) 매체는 기계(예를 들어, 컴퓨터) 판독가능 저장 매체(예를 들어, 판독전용 메모리("ROM"), 랜덤 액세스 메모리("RAM"), 자기 디스크 저장 매체, 광학 저장 매체, 플래시(flash) 메모리 디바이스들 등), 기계(예를 들어, 컴퓨터) 판독가능 송신 매체(전기 광, 음향, 또는 그 외의 형태의 전파된 신호들(예를 들어, 적외선 신호들, 디지털 신호들 등)), 등을 포함한다.

[0058] 도 13은 기계가 본 명세서에서 설명된 방법론들 중의 임의의 하나 이상을 수행하게 하기 위하여, 명령어들의 세

트(set)가 그 내부에서 실행될 수 있는 컴퓨터 시스템(1300)의 예시적인 형태로 기계의 도식적인 표현을 예시한다. 대안적인 실시예들에서, 기계는 로컬 영역 네트워크(LAN : Local Area Network), 인트라넷(intranet), 익스트라넷(extranet), 또는 인터넷(Internet) 내의 다른 기계들로 접속(예를 들어, 네트워크화)될 수 있다. 기계는 클라이언트-서버(client-server) 네트워크 환경 내의 서버 또는 클라이언트 기계의 용량에서, 또는 퍼어-투-퍼어(peer-to-peer)(또는 분산(distributed)) 네트워크 환경에서 퍼어 기계(peer machine)로서 동작할 수 있다. 기계는 개인용 컴퓨터(PC : personal computer), 태블릿 PC(tablet PC), 세톱 박스(STB : set-top box), 개인 정보 단말(PDA : Personal Digital Assistant), 셀룰러 전화, 웹 기기(web appliance), 서버, 네트워크 라우터(network router), 스위치 또는 브릿지(bridge), 또는 기계에 의해 취해져야 할 작동들을 특정하는 명령어들(순차적이거나 그렇지 않음)의 세트를 실행할 수 있는 임의의 기계일 수 있다. 또한, 단일 기계만 예시되어 있지만, 용어 "기계(machine)"는 본 명세서에서 설명된 방법론들 중의 임의의 하나 이상을 수행하기 위하여 명령어들의 세트(또는 다수의 세트들)를 개별적으로 또는 통합하여 실행하는 기계들(예를 들어, 컴퓨터들)의 임의의 집합을 포함하도록 선택될 수도 있을 것이다.

[0059] 예시적인 컴퓨터 시스템(1300)은 프로세서(1302), 주 메모리(main memory)(1304)(예를 들어, 판독전용 메모리(ROM : read-only memory), 플래시 메모리, 동기식 DRAM(SDRAM : synchronous DRAM) 또는 램버스 DRAM(RDRAM : Rambus DRAM)과 같은 동적 랜덤 액세스 메모리(DRAM : dynamic random access memory), 등), 정적 메모리(static memory)(1306)(예를 들어, 플래시 메모리, 정적 랜덤 액세스 메모리(SRAM : static random access memory), 등), 및 보조 메모리(secondary memory)(1318)(예를 들어, 데이터 저장 디바이스)를 포함하고, 이들은 버스(bus)(1330)를 통해 서로 통신한다.

[0060] 프로세서(1302)는 마이크로프로세서, 중앙 프로세싱 유닛, 등과 같은 하나 이상의 범용(general-purpose) 프로세싱 디바이스들을 나타낸다. 더욱 구체적으로, 프로세서(1302)는 복합 명령어 세트 컴퓨팅(CISC : complex instruction set computing) 마이크로프로세서, 감소된 명령어 세트 컴퓨팅(RISC : reduced instruction set computing) 마이크로프로세서, 매우 긴 명령어 워드(VLIW : very long instruction word) 마이크로프로세서, 다른 명령어 세트들을 수행하는 프로세서, 또는 명령어 세트들의 조합을 수행하는 프로세서들일 수 있다. 프로세서(1302)는 특정 용도 집적 회로(ASIC : application specific integrated circuit), 필드 프로그램 가능 게이트 어레이(FPGA : field programmable gate array), 디지털 신호 프로세서(DSP : digital signal processor), 네트워크 프로세서, 등과 같은 하나 이상의 특별목적(special-purpose) 프로세싱 디바이스들일 수도 있다. 프로세서(1302)는 본 명세서에서 설명된 동작들을 수행하기 위한 프로세싱 로직(processsing logic)(1326)을 실행하도록 구성된다.

[0061] 컴퓨터 시스템(1300)은 네트워크 인터페이스 디바이스(1308)를 더 포함할 수 있다. 또한, 컴퓨터 시스템(1300)은 비디오 디스플레이 유닛(1310)(예를 들어, 액정 디스플레이(LCD : liquid crystal display), 발광 다이오드 디스플레이(LED : light emitting diode display), 음극선관(CRT : cathode ray tube)), 알파뉴메릭 입력 디바이스(alphanumeric input device)(1312)(예를 들어, 키보드), 커서 제어 디바이스(cursor control device)(1314)(예를 들어, 마우스(mouse)), 및 신호 발생 디바이스(1316)(예를 들어, 스피커(speaker))를 포함할 수 있다.

[0062] 보조 메모리(1318)는 본 명세서에서 설명된 방법론들 또는 기능들 중의 임의의 하나 이상을 구체화하는 명령어들(예를 들어, 소프트웨어(1322))의 하나 이상의 세트들이 그 위에 저장되는 기계-액세스가능 저장 매체(machine-accessible storage medium)(또는 더욱 구체적으로, 컴퓨터-판독가능 저장 매체)(1331)를 포함할 수 있다. 또한, 소프트웨어(1322)는 컴퓨터 시스템(1300), 주 메모리(1304), 및 기계-판독가능 저장 매체를 또한 구성하는 프로세서(1302)에 의한 실행 동안에 주 메모리(1304) 내에서 및/또는 프로세서(1302) 내에서 완전히 또는 적어도 부분적으로 상주할 수도 있다. 소프트웨어(1322)는 네트워크 인터페이스 디바이스(1308)를 통해 네트워크(1320) 상에서 추가적으로 송신 또는 수신될 수 있다.

[0063] 기계-액세스가능 저장 매체(1331)가 단일 매체인 것으로 예시적인 실시예에서 도시되어 있지만, 용어 "기계-판독가능 저장 매체"는 명령어들의 하나 이상의 세트들을 저장하는 단일 매체 또는 다수 매체(예를 들어, 중앙집중화된 또는 분산된 데이터베이스, 및/또는 연계된 캐시들 및 서버들)를 포함하도록 선택되어야 한다. 또한, 용어 "기계-판독가능 저장 매체"는 기계에 의한 실행을 위하여 명령어들의 세트를 저장 또는 인코딩할 수 있고 기계가 본 발명의 방법론들 중의 임의의 하나 이상을 수행하도록 하는 임의의 매체를 포함하도록 선택될 것이다. 따라서, 용어 "기계-판독가능 저장 매체"는 다음으로 한정되지 않지만, 고체-상태 메모리(solid-state memory)들과, 광학 및 자기 매체를 포함하도록 선택될 것이다.

[0064]

본 발명의 실시예에 따르면, 기계-액세스가능 저장 매체는 데이터 프로세싱 시스템이 복수의 집적 회로들을 갖는 반도체 웨이퍼를 다이싱하는 방법을 수행하도록 하는 그 위에 저장된 명령어들을 가진다. 방법은 반도체 웨이퍼 위에 마스크를 형성하는 것을 포함하고, 마스크는 집적 회로들을 회복하고 보호하는 층으로 구성된다. 다음으로, 캡들을 갖는 패터닝된 마스크를 제공하기 위하여, 마스크는 웨토초-기반의 레이저 스크라이빙 프로세스로 패터닝된다. 반도체 웨이퍼의 영역들은 집적 회로들 사이에 노출된다. 다음으로, 집적 회로들을 싱글레이팅 하기 위하여, 반도체 웨이퍼는 패터닝된 마스크 내의 캡들을 통해 식각된다.

[0065]

따라서, 복수의 집적 회로들을 각각 갖는 반도체 웨이퍼들을 다이싱하는 방법들이 개시되었다. 본 발명의 실시 예에 따르면, 방법은 복수의 집적 회로들을 갖는 반도체 웨이퍼를 다이싱하는 것을 포함하고, 반도체 웨이퍼 위에 마스크를 형성하는 것을 포함하고, 마스크는 집적 회로들을 회복 및 보호하는 층으로 구성된다. 또한, 방법은 캡들을 갖는 패터닝된 마스크를 제공하기 위하여 웨토초-기반의 레이저 스크라이빙 프로세스로 마스크를 패터닝하는 것을 포함하고, 집적 회로들 사이의 반도체 웨이퍼의 영역들을 노출한다. 또한, 방법은 집적 회로들을 싱글레이팅하기 위하여 패터닝된 마스크 내의 캡들을 통해 반도체 웨이퍼를 식각하는 것을 포함한다. 하나의 실시예에서, 웨토초-기반의 레이저 스크라이빙 프로세스로 마스크를 패터닝하는 것은 집적 회로들 사이의 반도체 웨이퍼의 영역들 내에 트렌치들을 형성하는 것을 포함한다. 그 실시예에서, 반도체 웨이퍼를 식각하는 것은 레이저 스크라이빙 프로세스로 형성된 트렌치들을 식각하는 것을 포함한다.

## 도면

### 도면1

### 도면2

**도면3**순서도 300**도면4a****도면4b****도면4c**

## 도면5

도면6

도면7

## 도면8

$$I = \frac{E_p}{\pi \cdot w_0^2 \cdot \tau}$$

펄스 에너지

┌─────────┐

강도 ─────────── E\_p ──────────┐

└─────────┘

┌─────────┐

π · w\_0^2 · τ ──────────┐

└─────────┘

빔 반경

## 도면9a

## 도면9b

도면9c

도면9d

도면10

도면11

도면12

## 도면13