(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5645543号

(P5645543)

(45) 発行日 平成26年12月24日(2014.12.24)

(24) 登録日 平成26年11月14日(2014.11.14)

(51) Int.Cl.

H04N 5/378 (2011.01)

F 1

H04N 5/335 780

請求項の数 5 (全 14 頁)

(21) 出願番号 特願2010-185421 (P2010-185421)

(22) 出願日 平成22年8月20日 (2010.8.20)

(65) 公開番号 特開2012-44549 (P2012-44549A)

(43) 公開日 平成24年3月1日 (2012.3.1)

審査請求日 平成25年8月9日 (2013.8.9)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100090273

弁理士 國分 孝悦

(72) 発明者 桜木 孝正

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

審査官 松永 隆志

最終頁に続く

(54) 【発明の名称】撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

各々が光電変換素子を有し、行列状に配列される複数の画素と、

前記複数の画素の各列に対応して設けられ、前記画素の信号を増幅する複数のアンプと、

信号を蓄積する複数のホールド容量と、

前記複数のアンプの出力端子及び前記複数のホールド容量の間にそれぞれ接続される複数のスイッチとを有し、

前記複数のアンプは、それぞれ、1つのオペアンプを有し、

前記複数のアンプの出力端子に対してそれぞれ前記1つのオペアンプの出力端子のみが接続され、

前記各列のアンプは、並列に動作し、

前記スイッチがオンの状態で前記アンプは第1の信号帯域幅で増幅し、その後、前記スイッチがオンの状態で前記アンプは前記第1の信号帯域幅より狭い第2の信号帯域幅で増幅し、その後、前記スイッチがオフの状態で前記アンプは第2の信号帯域幅で増幅することを特徴とする撮像装置。

## 【請求項 2】

前記アンプは、第1のバイアス電流の供給を受けることにより前記第1の信号帯域幅で増幅し、前記第1のバイアス電流より小さい第2のバイアス電流の供給を受けることにより前記第2の信号帯域幅で増幅することを特徴とする請求項1記載の撮像装置。

**【請求項 3】**

前記アンプは、容量及び可変抵抗の直列接続回路を有する位相補償回路を有する負帰還アンプであり、前記可変抵抗を第1の抵抗値にすることにより前記第1の信号帯域幅で増幅し、前記可変抵抗を前記第1の抵抗値より低い第2の抵抗値にすることにより前記第2の信号帯域幅で増幅することを特徴とする請求項1記載の撮像装置。

**【請求項 4】**

前記アンプは、負帰還アンプであることを特徴とする請求項1又は2記載の撮像装置。

**【請求項 5】**

前記アンプは、ソースフォロワーアンプであることを特徴とする請求項1又は2記載の撮像装置。

10

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、撮像装置に関する。

**【背景技術】****【0002】**

特許文献1には、撮像素子に用いられる2重サンプリング回路が開示されている。最近のアナログ信号処理回路には、ほとんどの場合、スイッチと容量を用いたサンプルホールド回路が使用されている。撮像素子のみならず、ほとんど全ての電子機器は高速動作が求められ、信号処理回路内のサンプルホールド回路も高速動作が必要になる。サンプルホールド回路を高速動作させるには、サンプルホールド回路の入力端子を駆動するバッファの信号帯域幅を広くすることが必要である。バッファの信号帯域幅は、通常そのバイアス電流に依存し、バイアス電流を大きくするほど広帯域になる。

20

**【先行技術文献】****【特許文献】****【0003】**

【特許文献1】特開2006-345280号公報

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

30

しかし、バッファのゲインはバッファのバイアス電流に依存し、バイアス電流が大きいほど帯域が広くなるので、サンプルホールド回路を高速化するために、バッファのバイアス電流を増加し広帯域化すると、バッファの出力端子におけるノイズも増大してしまう。

**【0005】**

本発明の目的は、サンプルホールドの高速化と低ノイズ化を両立させることができる撮像装置を提供することである。

**【課題を解決するための手段】****【0006】**

本発明の撮像装置は、各々が光電変換素子を有し、行列状に配列される複数の画素と、前記複数の画素の各列に対応して設けられ、前記画素の信号を増幅する複数のアンプと、信号を蓄積する複数のホールド容量と、前記複数のアンプの出力端子及び前記複数のホールド容量の間にそれぞれ接続される複数のスイッチとを有し、前記複数のアンプは、それぞれ、1つのオペアンプを有し、前記複数のアンプの出力端子に対してそれぞれ前記1つのオペアンプの出力端子のみが接続され、前記各列のアンプは、並列に動作し、前記スイッチがオンの状態で前記アンプは第1の信号帯域幅で増幅し、その後、前記スイッチがオンの状態で前記アンプは前記第1の信号帯域幅より狭い第2の信号帯域幅で増幅し、その後、前記スイッチがオフの状態で前記アンプは第2の信号帯域幅で増幅することを特徴とする。

40

**【発明の効果】****【0007】**

50

サンプルホールドの高速化と低ノイズ化を両立させることができる。

【図面の簡単な説明】

【0008】

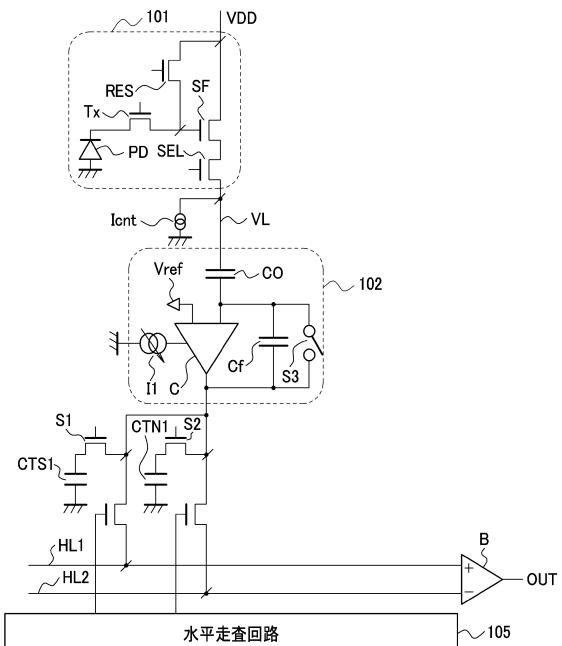

【図1】第1の実施形態におけるサンプルホールド回路の概略構成を示す図である。

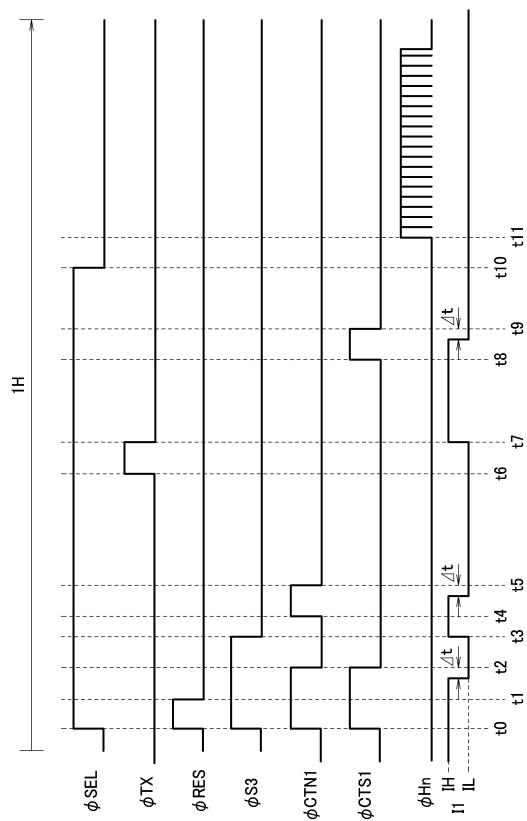

【図2】第1の実施形態のサンプルホールド回路のタイミング図である。

【図3】第2の実施形態におけるサンプルホールド回路の概略構成を示す図である。

【図4】第2の実施形態のサンプルホールド回路のタイミング図である。

【図5】バッファーアンプの回路例を表す図である。

【図6】バッファーアンプにおける電圧ゲイン - 周波数特性を表す図である。

【図7】第3の実施形態におけるバッファーアンプの回路図である。 10

【図8】第4の実施形態におけるバッファーアンプの概略構成を示す図である。

【図9】第4の実施形態におけるバッファーアンプのゲイン - 周波数特性図である。

【図10】可変電流源の具体例を示す図である。

【図11】第2の実施形態における可変抵抗の具体例を示す図である。

【図12】第4の実施形態におけるサンプルホールド回路の構成例を示す図である。

【図13】図12のサンプルホールド回路のタイミング図である。

【図14】第5の実施形態における撮像装置の構成例を示す図である。

【図15】図14の撮像装置のタイミング図である。

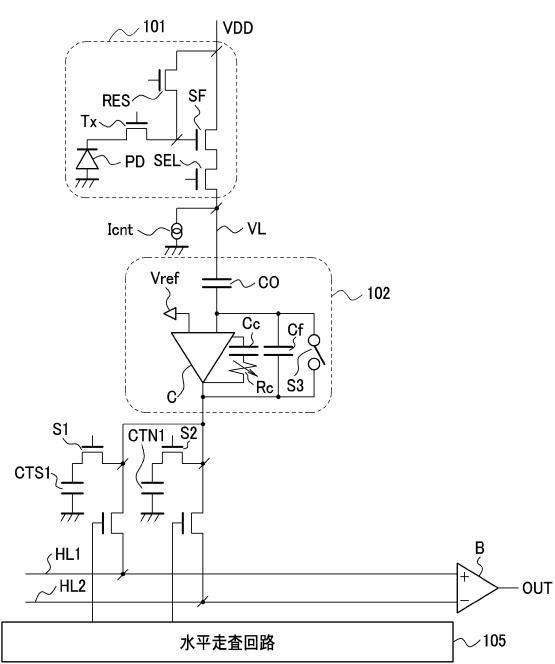

【図16】第6の実施形態における撮像装置の構成例を示す図である。

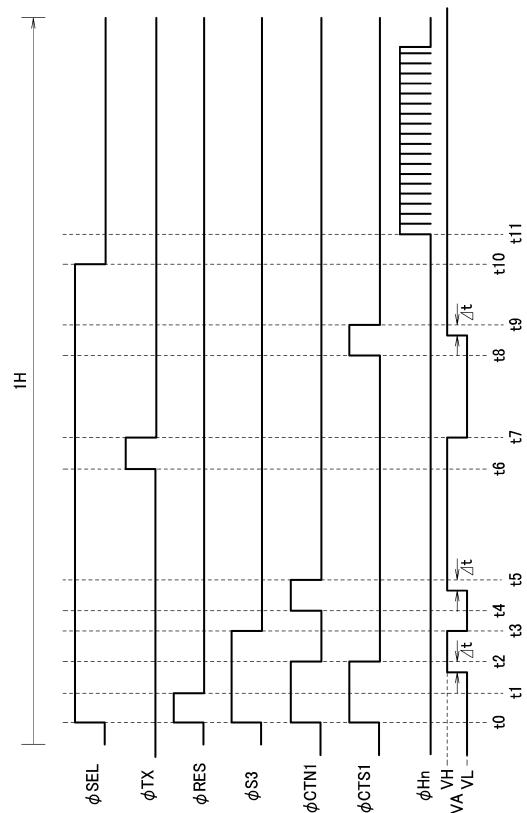

【図17】図16の撮像装置のタイミング図である。 20

【発明を実施するための形態】

【0009】

(第1の実施形態)

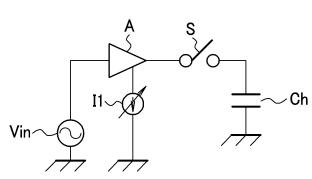

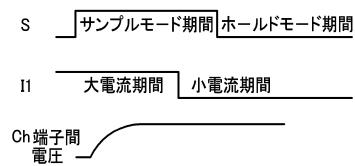

図1は、本発明の第1の実施形態によるサンプルホールド回路の構成例を示す図であり、図2はそのサンプルホールド回路のタイミング図である。図中、Aは、スイッチSとホールド容量Chで形成されるサンプルホールド回路の入力を駆動するバッファーアンプであり、I1はバッファーアンプAのバイアス電流源、VinはバッファーアンプAの入力に印加される信号源である。バッファーアンプCは、信号源Vinの信号を増幅する。ホールド容量Chは、信号を蓄積する。スイッチSは、バッファーアンプAの出力端子及びホールド容量Chの間に接続される。 30

【0010】

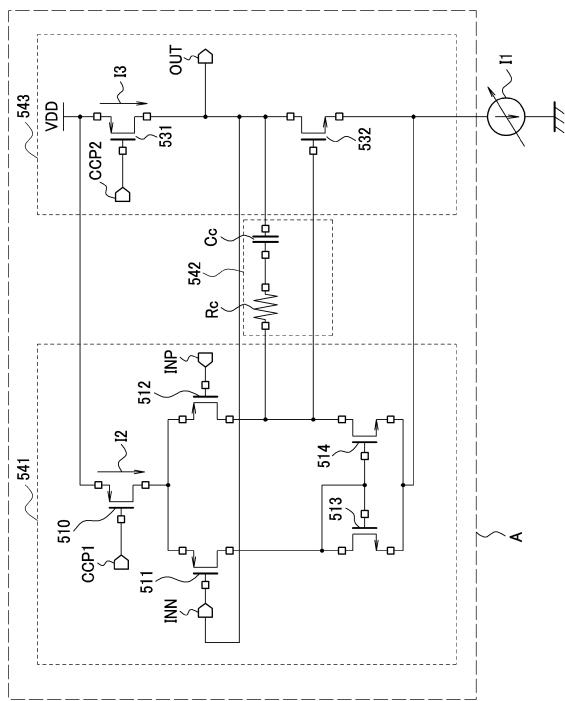

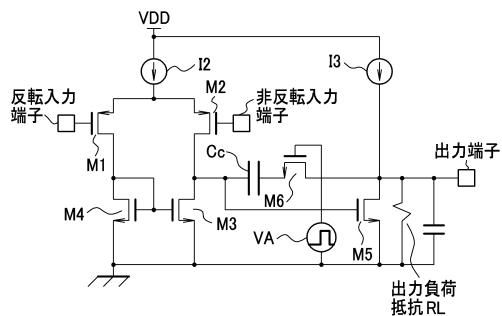

図5は、バッファーアンプA及び電流源I1の構成例を示す図である。バッファーアンプAは、差動増幅回路541と、ソース接地増幅回路543と、発振を防止するための位相補償回路542とを有する負帰還アンプである。差動増幅回路541の反転入力端子INNには、ソース接地増幅回路543の出力端子OUTが接続されている。差動増幅回路541は、端子CCP1から入力される電圧によってバイアス電流I2が制御されるMOS電界効果トランジスタ(MOSトランジスタ)510と、MOSトランジスタ511～514とを有する。差動増幅回路541において、端子INNは反転入力端子、端子INPは入力端子である。位相補償回路542は、抵抗Rc及び容量Ccの直列接続回路を有し、差動増幅回路541及びソース接地増幅回路543間に接続されている。ソース接地増幅回路543は、端子CCP2から入力される電圧によってバイアス電流I3が制御されるMOSトランジスタ531と、MOSトランジスタ532とを有する。バッファーアンプAは、入力端子INPから入力した信号源Vinの信号を増幅し、出力端子OUTから出力する。 40

【0011】

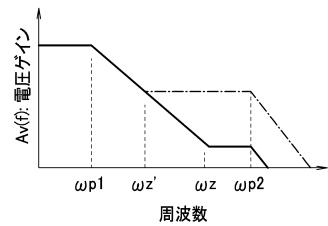

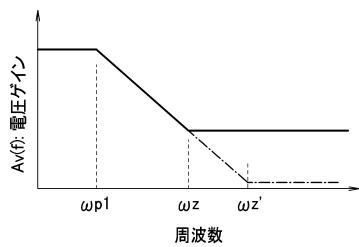

図6は、図5のバッファーアンプAの電圧ゲイン - 周波数特性を示す図である。図中、zはゼロ点、p1は第1のポール周波数、p2は第2のポール周波数を示している。第2のポール周波数p2は、およそ次式(1)で表わされる。

【0012】

$$p_1 = 1 / (g_m \times R_1 \times R_L \times C_c) \quad (1)$$

## 【0013】

$g_m$  は M O S ランジスタ 5 3 2 の相互コンダクタンス、 $R_1$  及び  $R_L$  はそれぞれ差動增幅回路 5 4 1 の出力インピーダンス及び出力負荷抵抗である。

## 【0014】

$R_1$  は M O S ランジスタ 5 1 2 、 5 1 4 のドレイン抵抗  $R_{ds}$  に並列したものに等しく、ドレイン抵抗  $R_{ds}$  はドレイン電流  $I_d$  に反比例する ( $R_{ds} = 1 / I_d$ )。一方、 $g_m$  は  $g_m = I_d$  の関係にある。

## 【0015】

また、ドレイン電流  $I_d$  はバイアス電流  $I_2$  の  $1 / 2$  に等しいので、結局、第 1 のポール周波数  $p_1$  は、 $p_1 = I_2 / C_c$  と表され、バイアス電流  $I_2$  の  $f$  に比例する。第 1 のポール  $p_1$  以降、電圧ゲインは  $-6 \text{dB} / \text{oct}$  で変化するので、図 6 に示すように、第 1 のポール周波数  $p_1$  と帯域幅は基本的に比例関係にある。したがって、帯域幅は、バイアス電流  $I_2$  の  $f$  に比例する。さらに、第 2 のポール周波数  $p_2$  とゼロ周波数  $z$  は次式 (2) 及び (3) のように表される。ここで、 $C_2$  は出力端子の負荷容量である。10

## 【0016】

$$p_2 = g_m / C_2 \quad (2)$$

$$z = 1 / C_c (1 / g_m - R_c) \quad (3)$$

## 【0017】

式 (3) から抵抗  $R_c$  の値によって、 $z$  の周波数が変化し、 $R_c > > 1 / g_m$  とすると、 $z$  は小さい値 ( $z'$ ) となるので、図 6 内の破線で示したゲイン特性のようになる。高周波領域でのゲインが増加し広帯域化され、逆に抵抗  $R_c$  を小さくすると帯域は狭くなる。20

## 【0018】

バッファーアンプ A の出力端子におけるランダムノイズ  $V_o(f)$  は、次式 (4) で表わされる。ここで、バッファーアンプ A の入力換算ノイズ電圧を  $V_1(f)$  、該バッファーアンプ A の入力端子に印加される信号源  $V_{in}$  のノイズ電圧を  $V_2(f)$  とし、さらにバッファーアンプ A の電圧ゲインを  $A_v(f)$  とする。

## 【0019】

$$V_o(f) = A_v(f) \times (V_1(f)^2 + V_2(f)^2) \quad (4)$$

## 【0020】

ここで、 $A_v(f)$  は、図 6 で示したように、電圧ゲインが周波数  $f$  の関数であることを示している。出力端子のノイズは、次式 (5) で表わされるので、バッファーアンプ A が広帯域になるほど、バッファーアンプ A から出力されるノイズは大きくなる。

## 【0021】

$$V_o(f) df = \{ A_v(f) \times \{ (V_1(f)^2 + V_2(f)^2) \} df \} \quad (5)$$

## 【0022】

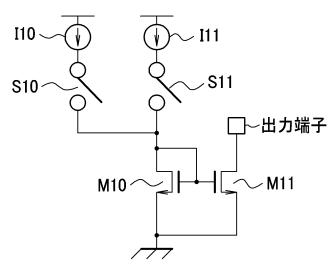

本実施形態では、電流源  $I_1$  は、バッファーアンプ A 及びグランド電位ノード間に接続され、サンプルモード及びホールドモードのタイミングに応じて、電流を可変できる。可変電流源  $I_1$  の具体例を図 10 に示す。 $I_{10}$  及び  $I_{11}$  は定電流源、 $S_{10}$  及び  $S_{11}$  はスイッチ、 $M_{10}$  及び  $M_{11}$  は M O S ランジスタである。M O S ランジスタ  $M_{10}$  及び  $M_{11}$  はそれぞれのゲートが接続されてカレントミラー回路を構成している。40

## 【0023】

図 2 のタイミング図と共に動作を説明すると、電流源  $I_1$  の大電流期間において図 10 のスイッチ  $S_{10}$  及び  $S_{11}$  が共にオンし、定電流源  $I_{10}$  及び  $I_{11}$  の電流は M O S ランジスタ  $M_{10}$  のドレイン端子に流入する。M O S ランジスタ  $M_{10}$  及び  $M_{11}$  は、前述のようにカレントミラー回路を構成しているので、M O S ランジスタ  $M_{11}$  のドレイン電流は電流源  $I_{10}$  及び  $I_{11}$  の電流を足した値になる。次に、図 2 の電流源  $I_1$  の小電流期間では、図 10 のスイッチ  $S_{10}$  はオフに、スイッチ  $S_{11}$  はオンにすることに50

より、MOSトランジスタM10のドレインに流れ込む電流は電流源I11の電流になる。よって、MOSトランジスタM11のドレイン電流も電流源I11の電流になる。

#### 【0024】

図1において、スイッチSをオンにして、サンプルホールド回路をサンプルモードにすると、バッファーアンプAはホールド容量Chを充電し、Chの端子間電圧は変化する。この変化する速度を向上させることはサンプルホールド回路の高速動作に直結するので、バッファーアンプAの信号帯域は広くなくてはならない。そのために、バッファーアンプAのバイアス電流源I1の電流を、容量Chの端子間電圧が変化している間は大きい値に設定する。容量Chの端子間電圧の遷移が終了した後、バッファーアンプAのバイアス電流源I1の電流を小さい値に設定し、バッファーアンプAを狭帯域、低ノイズモードにすることで、容量Chに保存される信号電圧も低ノイズになる。スイッチSがオンしてサンプルモードになった後バイアス電流源I1の電流を大電流に設定する時間幅は、バッファーアンプAが扱う信号振幅の最大値に対する、容量Chを負荷にした場合のセトリング時間を目安にすればよい。10

#### 【0025】

以上のように、スイッチSがオンの状態（サンプルモード）でバッファーアンプAは第1の信号帯域幅（広帯域）で増幅する。その後、スイッチSがオフの状態（ホールドモード）でバッファーアンプAは第1の信号帯域幅（広帯域）より狭い第2の信号帯域幅（狭帯域）で増幅する。その後、スイッチSがオフの状態（ホールドモード）でバッファーアンプAは第2の信号帯域幅（狭帯域）で増幅する。バッファーアンプAは、第1のバイアス電流（大電流）の供給を受けることにより第1の信号帯域幅（広帯域）で増幅し、第1のバイアス電流（大電流）より小さい第2のバイアス電流（小電流）の供給を受けることにより第2の信号帯域幅（狭帯域）で増幅する。20

#### 【0026】

信号源Vinは、サンプルホールド回路の入力端子を駆動するバッファーアンプAの入力信号源である。信号源Vinの信号が変化し、それに応答してバッファーアンプAの出力が変化し、サンプルホールドスイッチSをオンさせて該出力電圧がサンプルホールド容量Chに印加される。その期間は、バッファーアンプAのバイアス電流源I1の電流を大きい値に設定して高速駆動モードとし、バッファーアンプAの出力電圧の遷移が終了した後にバッファーアンプAのバイアス電流源I1の電流を小さい値に設定することで低速、低ノイズモードにする。その後サンプルホールドスイッチSをオフさせてホールド状態にすることで、サンプルホールドの高速化と低ノイズ化の両立が可能になる。30

#### 【0027】

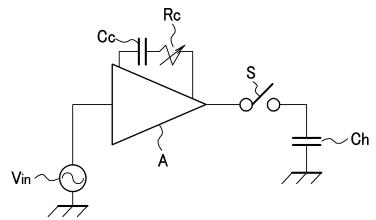

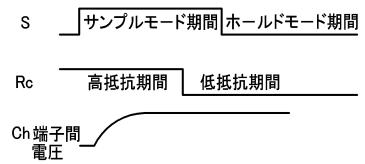

##### （第2の実施形態）

図3は、本発明の第2の実施形態によるサンプルホールド回路の構成例を示す図である。本実施形態は、図1と同様であるが、バッファーアンプAに搭載される位相補償容量（又は帯域制限のための容量）Ccに直列に、サンプルモード、ホールドモードのタイミングに応じて可変できる可変抵抗Rcを接続し、電流源I1を削除している点が異なる。バッファーアンプAは、容量Cc及び可変抵抗Rcの直列接続回路を有する位相補償回路542（図5）を有する負帰還アンプである。抵抗Rcの値を、図4のタイミング図のようにスイッチSがオンしてサンプルモードになっているある期間に、可変抵抗Rcを高抵抗に設定し、該バッファーアンプAを広帯域、高速モードにする。その後、容量Chの端子間電圧の遷移が終了するところで抵抗Rcを低い値に設定し、バッファーアンプAを狭帯域、低ノイズモードにする。上記回路動作によってサンプルホールド回路を高速、低ノイズで動作させることが可能になる。以上のように、可変抵抗Rcを第1の抵抗値（高抵抗）にすることにより第1の信号帯域幅（広帯域）で増幅し、可変抵抗Rcを第1の抵抗値（高抵抗）より低い第2の抵抗値（低抵抗）にすることにより第2の信号帯域幅（狭帯域）で増幅する。40

#### 【0028】

サンプルホールド回路の入力端子を駆動するバッファーアンプAの入力信号が変化し、

50

それに応答してバッファーアンプAの出力が変化し、サンプルホールドスイッチSをオンさせて該出力電圧がサンプルホールド容量C<sub>h</sub>に印加される。その期間は、該バッファーアンプA内の位相補償容量C<sub>c</sub>に直列に接続された抵抗R<sub>c</sub>の値を高い値に設定することで高速駆動モードとする。そして、該バッファーアンプAの出力電圧の遷移が終了した後に該バッファーアンプA内の位相補償容量C<sub>c</sub>に直列に接続された抵抗R<sub>c</sub>の値を低い値に設定することで低速、低ノイズモードにすることでサンプルホールドの高速化と低ノイズ化の両立が可能になる。

#### 【0029】

図11は抵抗R<sub>c</sub>を変化させるバッファーアンプAの具体例である。電流源I<sub>2</sub>は図5のMOSトランジスタ510に対応し、電流源I<sub>3</sub>は図5のMOSトランジスタ531に対応する。MOSトランジスタM1は図5のMOSトランジスタ511に対応し、MOSトランジスタM2は図5のMOSトランジスタ512に対応する。MOSトランジスタM3は図5のMOSトランジスタ514に対応し、MOSトランジスタM4は図5のMOSトランジスタ513に対応する。MOSトランジスタM6は図5の抵抗R<sub>c</sub>に対応し、MOSトランジスタM5は図5のMOSトランジスタ532に対応する。可変抵抗R<sub>c</sub>は、MOSトランジスタM6のドレイン及びソース間抵抗であり、MOSトランジスタM6のゲート電圧に応じて抵抗値が変化する。図4のタイミング図と共に説明する。図4中の抵抗R<sub>c</sub>の高抵抗期間では図11内のパルス電圧源V<sub>A</sub>の値のある低電圧V<sub>L</sub>に設定することでMOSトランジスタM6のゲート-ソース間電圧が小さい値になるため、nチャネルMOSトランジスタM6のオン抵抗R<sub>c</sub>はある高い値になる。したがって、図5の帯域幅に関して前述したようにバッファーアンプAの帯域幅は広がり動作は高速になる。図4中の抵抗R<sub>c</sub>の低抵抗期間では図11のパルス電圧源V<sub>A</sub>の値のある高電圧V<sub>H</sub>に設定することで、MOSトランジスタM6のゲート-ソース間電圧はある高い値になり、nチャネルMOSトランジスタM6のオン抵抗R<sub>c</sub>はある低い値になる。したがって、前記と同様の理由でバッファーアンプAの信号帯域幅は狭くなる。なお、可変抵抗R<sub>c</sub>は、複数のスイッチとその複数のスイッチのそれぞれに直列に接続された抵抗を用い、その複数のスイッチをオン/オフ制御することにより、抵抗値をえるようにしてもよい。

#### 【0030】

##### (第3の実施形態)

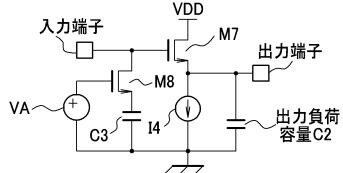

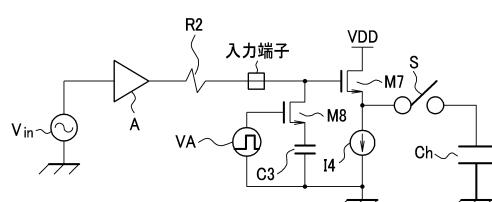

図7は、本発明の第3の実施形態によるバッファーアンプAの構成例を示す図である。本実施形態のバッファーアンプAは、図1のバッファーアンプA及び電流源I<sub>1</sub>の代わりに設けられる。バッファーアンプAがN MOSソースフォロワーアンプであり、負帰還を掛けた演算増幅器ではない場合である。まず図7を用いて簡単に説明する。図中、M7はソースフォロワーアンプを構成するMOSトランジスタ、I<sub>4</sub>はMOSトランジスタM7のバイアス電流源、C<sub>2</sub>は出力負荷容量である。M8はMOSトランジスタ、V<sub>A</sub>はMOSトランジスタM8のゲートを駆動する電圧源、C<sub>3</sub>は容量である。

#### 【0031】

サンプルホールド回路を駆動する駆動回路としてMOSソースフォロワーアンプを用いた場合、そのゲイン-周波数特性におけるポール周波数pは次式(6)で表わされ、MOSトランジスタM7の相互コンダクタンスg<sub>m</sub>に比例する。ここで、相互コンダクタンスg<sub>m</sub>は、次式(7)で表わされる。

#### 【0032】

$$p = g_m / C_2 \quad (6)$$

$$g_m = (2k \times I_d \times W / L) \quad (7)$$

#### 【0033】

ここで、I<sub>d</sub>はドレイン電流、kは定数、W及びLはそれぞれMOSトランジスタのゲート幅及びゲート長であるので、ドレイン電流I<sub>d</sub>を大きくするほどポール周波数pは大きく、つまり広帯域化される。

#### 【0034】

本実施形態は、負帰還を用いた増幅回路に対して上述したのと同様の処理を行う。サン

10

20

30

40

50

プルホールド回路の入力端子を駆動するソースフォローアンプの入力信号が変化し、それに応答してソースフォローアンプの出力が変化し、サンプルホールドスイッチSをオンさせて該出力電圧がサンプルホールド容量C<sub>h</sub>に印加される。その期間では、ソースフォローアンプのバイアス電流源I<sub>4</sub>の電流を大きい値に設定して高速駆動モードとする。そして、ソースフォローアンプの出力電圧の遷移が終了した後に、ソースフォローアンプのバイアス電流源I<sub>4</sub>の電流を小さい値に設定することにより、低速、低ノイズモードにする。その後、サンプルホールドスイッチSをオフさせてホールド状態にすることで、サンプルホールドの高速化と低ノイズ化の両立が可能になる。可変電流源I<sub>4</sub>の具体例は前述した図10を用いることができる。バイアス電流源I<sub>4</sub>の電流を大きい値に設定する場合は、図10におけるスイッチS<sub>10</sub>及びS<sub>11</sub>を共にオンさせ、カレントミラーレ<sup>10</sup>回路を構成するMOSトランジスタM<sub>11</sub>のドレイン電流をI<sub>10</sub>+I<sub>11</sub>にする。バイアス電流源I<sub>4</sub>の電流を小さい値に設定する場合は、図10中のスイッチS<sub>10</sub>のみオンさせ、スイッチS<sub>11</sub>はオフとすることで、カレントミラー回路を構成するMOSトランジスタM<sub>11</sub>のドレイン電流はI<sub>10</sub>となる。

## 【0035】

(第4の実施形態)

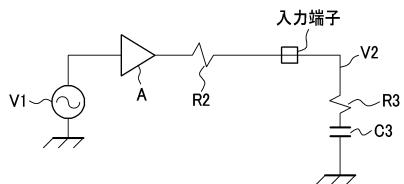

図8は、本発明の第4の実施形態によるバッファーアンプを説明する図である。本実施形態では、図7内のMOSトランジスタM<sub>8</sub>と、MOSトランジスタM<sub>8</sub>のゲートを駆動する電圧源V<sub>A</sub>、容量C<sub>3</sub>を用いることで、ソースフォローアンプの帯域を制御することが可能になる。前述と同様にして、サンプルホールド回路のスイッチSがオン オフするタイミングの前後にソースフォローアンプの信号帯域幅を変化させることで、サンプルホールドの高速化と低ノイズ化の両立が可能になる。<sup>20</sup>

## 【0036】

上記事柄を、図8を用いて本実施形態の原理を詳細に説明する。図8中Aはソースフォローアンプの入力部を駆動する駆動回路(電圧ゲイン=1を仮定)、R<sub>2</sub>は該駆動回路の出力抵抗、R<sub>3</sub>は図7中のMOSトランジスタM<sub>8</sub>のオン抵抗である。信号源V<sub>1</sub>は図1の信号源V<sub>in</sub>に対応する。信号源V<sub>1</sub>と、抵抗R<sub>2</sub>を介してソースフォローアンプの入力部に現れる電圧V<sub>2</sub>の比(電圧ゲイン)は次式(8)で表される。

## 【0037】

$$V_2 / V_1 = (1 + C_3 \times R_3) / \{ (R_2 + R_3) \times C_3 + 1 \} \quad (8) \quad 30$$

## 【0038】

R<sub>3</sub> >> R<sub>2</sub>の関係にある時は、V<sub>2</sub> / V<sub>1</sub> = 1となるが、R<sub>3</sub> << R<sub>2</sub>の時は、次式(9)になり、ボード線図で表すと図9のようになる。

## 【0039】

$$V_2 / V_1 = (1 + C_3 \times R_3) / (R_2 \times C_3 + 1) \quad (9)$$

## 【0040】

図中 p<sub>1</sub>はポール周波数、zはゼロ点である。ポール周波数 p<sub>1</sub>及びゼロ点 zは、それぞれ次式(10)及び(11)となる。

## 【0041】

$$p_1 = 1 / (C_3 \times R_2) \quad (10) \quad 40$$

$$z = 1 / (C_3 \times R_3) \quad (11)$$

## 【0042】

抵抗R<sub>3</sub>の値を変えると、図9の z から z' のようにゼロ点の位置が変化するため、抵抗R<sub>3</sub>の値を大きくするほど広帯域になることが分かる。

## 【0043】

図7のMOSトランジスタM<sub>8</sub>のゲートを駆動する電圧源V<sub>A</sub>の電圧値を変えることでのMOSトランジスタM<sub>8</sub>のオン抵抗が変化し、上述した信号帯域が変化する。したがって、サンプルホールド回路のスイッチSがオン オフするタイミングの前後に電圧源V<sub>A</sub>の電圧値を制御すればサンプルホールドの高速化と低ノイズ化の両立が可能になることが分かる。<sup>50</sup>

## 【0044】

図12は、本実施形態によるサンプルホールド回路の構成例を示す図であり、可変電圧源VAを有し、サンプルホールド回路の動作モードに応じて電圧源VAの電圧変化を行う具体例を示す。図13は、図12のサンプルホールド回路のタイミング図である。図中の符号は図7、図8にならう。図12内のスイッチSをオンさせてサンプルホールド回路がサンプルモードになっているとき、電圧源VAの電圧をある低電位VLにする。その電圧は図12のMOSトランジスタM8のゲートに印加されるので、nチャネルMOSトランジスタM8のオン抵抗R3はある高い値になる。前述した理由によってゼロ点周波数 $\omega$ は低い値になるので、MOSトランジスタM7のソースフォロワーアンプは広帯域になる。

10

## 【0045】

図13に示したように、図12のスイッチSをオフにし、サンプルホールド回路がホールドモードになる以前に、図12の電圧源VAの電圧をある高い値VHにする。これにより、MOSトランジスタM8のオン抵抗R3の値がある低い値になり、MOSトランジスタM7のソースフォロワーアンプは狭帯域になる。

## 【0046】

## (第5の実施形態)

図14は、本発明の第5の実施形態による撮像装置の構成例を示す図である。第1の実施形態のサンプルホールド回路は、列アンプ部102に適用されている。同図の構成と、その動作タイミングを図15も併用して簡単に説明する。なお、図14では、画素部101は1つしか記載されていないが、2次元的に複数配列された形式のものも当然含まれる。

20

## 【0047】

画素101は、光電変換により信号を生成する光電変換素子であるフォトダイオードPDと、フォトダイオードPDに蓄積された電荷を、画素出力部SFを構成するMOSトランジスタのゲート端子に転送する転送部TXを含む。画素出力部SFの入力部であるゲート端子は、リセット部RESを介して電源VDDと接続されている。さらに、画素出力部SFのソース端子は画素選択部SELを介して列アンプ102の入力容量C0の一方の端子と接続されると共に、定電流源ICntにも接続される。

## 【0048】

30

列アンプ102は、オペアンプCを備え、画素101の出力信号を増幅する。オペアンプCの反転入力端子は入力容量C0の他方の端子と接続される。オペアンプCの反転入力端子と出力端子間に、帰還容量Cfが接続されている。さらに、オペアンプCの反転入力端子と出力端子とを短絡するスイッチS3が設けられている。オペアンプCの非反転入力端子には電源Vrefが与えられる。画素101から垂直信号線VLに出力された信号に対しては、オペアンプCの帰還経路に接続される帰還容量Cfの容量値と、入力容量C0の容量値との比で決定されるゲインがかかるて増幅される。後述するが、画素101に起因するノイズが入力容量C0で低減される。ここでは入力容量C0、オペアンプCを含めて第1のCDS(Correlated Double Sampling; 相関二重サンプリング)回路とする。

40

## 【0049】

列アンプ102で増幅された信号は、スイッチS1、S2を介して、保持容量(ホールド容量)CTS1、CTN1に選択的に伝達されて保持される。保持容量CTS1には、フォトダイオードPDで光電変換されることで得られる電荷に基づく信号が蓄積され、保持容量CTN1には、画素出力部SFをリセットしたことに基づく信号が蓄積される。保持容量CTS1、CTN1はそれぞれ異なる水平信号線HLn(nは1~2)に接続される。保持容量CTS1及びCTN1に保持された信号は、それぞれスイッチを介して差動増幅器Bの異なる入力端子に接続される。水平走査回路105から信号H1、H2、...が入力されると、保持容量CTS1、CTN1に保持された信号が水平信号線HLnを介して対応する差動増幅器Bに入力される。差動増幅器Bからは、保持容量CTS1

50

及び C T N 1 で保持された信号の差分が出力される。ここで、保持容量 C T S 1 , C T N 1 と差動増幅器 B を含めて第 2 の C D S 回路とする。第 2 の C D S 回路によって列アンプ 1 0 2 に起因するオフセットが低減される。

#### 【 0 0 5 0 】

図 15 を用いて、本実施形態に係る動作を説明する。図 14 において、T X 、 R E S 、 S E L 、スイッチ S 3 に入力される信号をそれぞれ T X 、 R E S 、 S E L 、 S 3 で表し、信号がハイレベルである時にスイッチが導通するものとする。保持容量 C T S 1 、 C T N 1 と列アンプ 1 0 2 の出力端子との間にあるスイッチ S 1 , S 2 に与えられる信号をそれぞれ C T S 1 、 C T N 1 と表し、信号がハイレベルである時にスイッチが導通するものとする。

10

#### 【 0 0 5 1 】

まず、時刻 t 0 において信号 T X 及び H n を除く信号がハイレベルに遷移する。信号 S E L がハイレベルになると画素選択部 S E L が導通するので、画素出力部 S F のソース端子と定電流源 I c n t とが電気的に接続されてソースフォローアンプが形成される。これにより画素出力部 S F のゲート端子の電位に応じたレベルが信号として垂直信号線 V L に現れる。このタイミングで信号 R E S がハイレベルであるので、垂直信号線 V L には、画素出力部 S F のゲート端子をリセットしている状態に対応するレベルが現れる。また、信号 S 3 がハイレベルになることでオペアンプ C の反転入力端子と出力端子とが短絡されると共に、帰還容量 C f がリセットされる。オペアンプ C の仮想接地により、帰還容量 C f の両端子の電位は電源 V r e f と同電位とみなせる。信号 C T N 1 、 C T S 1 がハイレベルであるので、オペアンプ C の出力によって保持容量 C T N 1 、 C T S 1 がリセットされる。

20

#### 【 0 0 5 2 】

時刻 t 1 に信号 R E S がローレベルに遷移し、画素出力部 S F のゲート端子のリセット状態が解除される。時刻 t 2 において信号 S 3 、 C T N 1 、 C T S 1 がローレベルになり、それぞれに対応するスイッチが非導通状態になる。

#### 【 0 0 5 3 】

その後、時刻 t 3 において信号 S 3 がローレベルに遷移することで、オペアンプ C の入出力端子の短絡状態が解除される。入力容量 C 0 では、画素出力部 S F のゲート端子をリセットしたことに対応するレベルが、電源 V r e f によりクランプされる。

30

#### 【 0 0 5 4 】

時刻 t 4 に信号 C T N 1 がハイレベルになり、時刻 t 5 に信号 C T N 1 がローレベルになることで、この時の列アンプ 1 0 2 の出力が保持容量 C T N 1 に保持される。すなわち、保持容量 C T N 1 に保持される信号には、列アンプ 1 0 2 に起因するオフセット成分が含まれる。

#### 【 0 0 5 5 】

時刻 t 6 に信号 T X がハイレベルに遷移すると、フォトダイオード P D に蓄積されていた電荷が画素出力部 S F のゲート端子へと転送される。これにより画素出力部 S F のゲート端子の電位が変化するので、垂直信号線 V L に現れるレベルも変化する。このとき入力容量 C 0 は浮遊状態にあるので、時刻 t 1 でクランプされた垂直信号線 V L のレベルからの電位の変動分のみがオペアンプ C の反転入力端子に入力される。これにより光電変換に基づく信号がオペアンプ C に入力される。

40

#### 【 0 0 5 6 】

時刻 t 8 から信号 C T S 1 がハイレベルになり、これがローレベルに遷移すると、垂直信号線 V L に現れたレベルを増幅した信号が保持容量 C T S 1 に保持される。ここで保持容量 C T S 1 に保持される信号には、保持容量 C T N 1 と同様に、列アンプ 1 0 2 に起因するオフセットが含まれる。

#### 【 0 0 5 7 】

この後、信号 S E L がローレベルになることで、画素 1 0 1 の選択状態が解除される。各保持容量 C T S 1 , C T N 1 に保持される信号には、列アンプ 1 0 2 に起因するオフ

50

セットが含まれるので、差動増幅器 B により差分を取ることでオフセット成分を低減することが可能となる。

#### 【0058】

その後、水平走査回路 105 から信号  $H_n$  が出力され、容量 CTS1, CTN1 から水平信号線 HL1, HL2 に信号が転送され、差動増幅器（出力アンプ）B から信号が出力される。

#### 【0059】

次に、本実施形態の動作を、上記の信号読み出し動作に絡めて説明する。オペアンプ C は図 1 のバッファーアンプ A に対応し、スイッチ S1, S2 は図 1 のスイッチ S に対応し、容量 CTS1 及び CTN1 は図 1 のホールド容量 Ch に対応する。図 14 の容量 CTS1, CTN1 に画素 101 の信号を高速に、かつ低ノイズで保存するため、列アンプ C が前記容量 CTS1, CTN1 を駆動する際に該アンプ C のバイアス電流源 I1 の値を第 1 の実施形態と同様に変化させる。具体的には、図 15 のタイミング図で、CTS1, CTN1 がハイレベルからロー・レベルへ遷移するある時間以前（図中 t と記述）に該バイアス電流源 I1 の電流をある大電流 IH からある小電流 IL へ変化させる。容量 CTS1, CTN1 に該アンプ C から信号電荷を充放電する際には高速に行う。そして、充放電が終了し該容量 CTS1, CTN1 の電位が定常状態に達した後に、該バイアス電流源 I1 の電流を IL と小さくすることでアンプ C は低ノイズで両容量 CTS1, CTN1 を駆動する。図 15 中の時間 t は、該アンプ C のセトリング時間を鑑み、CTS1, CTN1 のパルス幅から決定する。

10

20

#### 【0060】

##### （第 6 の実施形態）

アンプ C を高速モードから低ノイズモードへ変化させる手段は、上記手段以外に第 2 の実施形態で示した、アンプ C 内の位相補償容量に直列に接続された抵抗 Rc を変化させることも当然用いることができる。

#### 【0061】

図 16 は、本発明の第 6 の実施形態による撮像装置の構成例を示す図である。オペアンプ C は図 1 のバッファーアンプ A に対応し、スイッチ S1, S2 は図 1 のスイッチ S に対応し、容量 CTS1 及び CTN1 は図 1 のホールド容量 Ch に対応する。オペアンプ C の可変抵抗 Rc の実施形態として、前記した図 11 の MOS ランジスタ M6 と、MOS ランジスタ M6 のゲート端子を駆動するパルス電圧源 VA を用いることができる。図 17 は、図 16 の撮像装置の動作タイミングである。読み出しに関しては、前記図 15 とほぼ同様で、図 15 における電流源 I1 の代わりにパルス電圧源 VA の電圧の変化タイミングを記述している。すなわち、図 17 のタイミング図で、信号 CTS1, CTN1 がハイレベルからロー・レベルへ遷移するある時間以前（図中 t と記述）に該電圧源 VA の電圧をある低電圧 VL からある高電圧 VH へ変化させる。こうすることで、該容量 CTS1, CTN1 に該アンプ C から信号電荷を充放電する際には高速に行い、充放電が終了し該容量 CTS1, CTN1 の電位が定常状態に達した後に、該電圧源 VA の電圧を VH と高くすることで該アンプ C は低ノイズで両容量を駆動する。なお、第 5 及び第 6 の実施形態と同様に、第 3 及び第 4 の実施形態のサンプルホールド回路も撮像装置の列アンプ 102 に適用することができる。

30

40

#### 【0062】

なお、上記実施形態は、何れも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されなければならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

#### 【符号の説明】

#### 【0063】

$V_{in}$  信号源、A バッファーアンプ、I1 バイアス電流源、S スイッチ、Ch ホールド容量

50

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 10】

【図 9】

【図 11】

【図 12】

【図 13】

S サンプルモード期間 ホールドモード期間

VH -----

VA VH

VL -----

VL

【図 14】

【図15】

【図16】

【図17】

---

フロントページの続き

(56)参考文献 特開2009-273148(JP,A)

特開2003-060934(JP,A)

特開平11-150683(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 04 N 5 / 378