(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2014년09월03일

(11) 등록번호 10-1437701

(24) 등록일자 2014년08월28일

(51) 국제특허분류(Int. Cl.)

H01L 29/78 (2006.01) H01L 21/336 (2006.01)

(21) 출원번호 10-2008-7030499

(22) 출원일자(국제) 2007년05월21일

심사청구일자 2012년05월21일

(85) 번역문제출일자 2008년12월15일

(65) 공개번호 10-2009-0018638

(43) 공개일자 2009년02월20일

(86) 국제출원번호 PCT/US2007/069329

(87) 국제공개번호 WO 2007/149666

국제공개일자 2007년12월27일

(30) 우선권주장

11/471,279 2006년06월19일 미국(US)

(56) 선행기술조사문헌

JP2002110984 A\*

KR1020040111710 A\*

JP2006324570 A

US20050167742 A1\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

페어차일드 세미컨덕터 코포레이션

미국 95134 캘리포니아주 산 호세 오차드 파크웨이 3030

(72) 발명자

크래프트 네이든

미국 펜실베니아 17901 포츠빌 포츠빌 스트리트 1243

코콘 크리스토퍼 보그슬러

미국 펜실베니아 18707 마운틴탑 와일드우드 레인 5

쏘렵 폴

미국 유타 84088 웨스트 조단 사우쓰 3850 웨스트 7991

(74) 대리인

오병석

전체 청구항 수 : 총 27 항

심사관 : 최정민

(54) 발명의 명칭 실드 전극과 게이트 전극이 접속된 실드 게이트 트랜치 전계효과 트랜지스터를 형성하는 구조물 및 방법

### (57) 요 약

전계효과 트랜지스터(FFT)는, 반도체 영역으로 연장되는 복수의 트랜치를 포함한다. 각각의 트랜치는 게이트 전극 및 실드 전극을 포함하고, 상기 게이트 전극과 상기 실드 전극의 사이에는 전극간 유전체가 존재하며, 상기 실드 전극과 상기 게이트 전극은 전기적으로 접속한다.

대 표 도 - 도2H

## 특허청구의 범위

### 청구항 1

전계효과 트랜지스터(field effect transistor; FET)에 있어서,

반도체 영역 내로 연장되고, 활성 영역에 배치된 트랜치;

상기 트랜치의 하부에 배치되고, 실드 유전체에 의해 상기 반도체 영역으로부터 절연되는 실드 전극;

상기 실드 전극 위에 배치된 전극간 유전체(inter-electrode dielectric; IED);

상기 전극간 유전체 위의 상기 트랜치의 상부에 배치된 게이트 전극 - 상기 게이트 전극은 게이트 유전체에 의해 상기 반도체 영역으로부터 절연되고, 상기 실드 전극과 상기 게이트 전극은 상기 트랜치를 넘어 비활성 영역으로 연장됨 - ; 및

상기 비활성 영역에 배치되고, 상기 게이트 전극을 상기 실드 전극과 전기적으로 접속하는 게이트 상호접속층을 포함하는 전계효과 트랜지스터.

### 청구항 2

제1항에 있어서,

상기 반도체 영역은,

제1 도전성 타입의 드리프트(drift) 영역;

상기 드리프트 영역 위에 배치된 제2 도전성 타입의 본체 영역; 및

상기 트랜치에 인접하여 상기 본체 영역 내에 배치된 제1 도전성 타입의 소스 영역을 포함하는, 전계효과 트랜지스터.

### 청구항 3

제2항에 있어서,

상기 트랜치 내에서 상기 게이트 전극에 상기 반도체 영역의 최상면의 아래까지 리세스가 형성되고,

상기 전계효과 트랜지스터는,

상기 소스 영역 및 상기 본체 영역과 접속하는 상호접속층; 및

상기 게이트 전극 위에 배치되고, 상기 게이트 전극을 상기 상호접속층으로부터 절연시키는 유전 물질(dielectric material)을 더 포함하는 전계효과 트랜지스터.

### 청구항 4

제2항에 있어서,

제1 도전성 타입의 기판을 더 포함하되,

상기 드리프트 영역은 상기 기판 위에 배치되고, 상기 트랜치는 상기 본체 영역을 통해 연장되고 상기 드리프트 영역 내에서 종단되는 전계효과 트랜지스터.

### 청구항 5

제2항에 있어서,

제1 도전성 타입의 기판을 더 포함하되,

상기 드리프트 영역은 상기 기판 위에 배치되고, 상기 트랜치는 상기 본체 영역 및 상기 드리프트 영역을 통해 연장되고 상기 기판 내에서 종단되는 전계효과 트랜지스터.

### 청구항 6

삭제

### 청구항 7

제1항에 있어서,

상기 게이트 상호접속층은 상기 비활성 영역의 게이트 러너 영역에 주기적으로 배치된 접촉 개구(contact opening)를 통해 형성되는 접촉부를 포함하는 전계효과 트랜지스터.

### 청구항 8

제1항에 있어서,

상기 실드 전극은 상기 트랜치 내의 상기 전극간 유전체를 통한 추가적인 접속에 의하여 상기 게이트 전극에 전기적으로 접속되는 전계효과 트랜지스터.

### 청구항 9

제1항에 있어서,

상기 게이트 전극은 또한, 상기 트랜치 내측의 상기 전극간 유전체의 적어도 하나의 개구를 통해 상기 실드 전극에 전기적으로 접속되는 전계효과 트랜지스터.

### 청구항 10

제1항에 있어서,

상기 전계효과 트랜지스터를 수용하는 다이의 주변을 따라서 연장되는 종단 영역을 더 포함하고,

상기 실드 전극과 상기 게이트 전극은 상기 트랜치를 넘어 상기 종단 영역으로 연장되고, 상기 실드 전극과 상기 게이트 전극이 상기 종단 영역에서 상기 게이트 상호접속층에 의하여 전기적으로 접속되는 전계효과 트랜지스터.

### 청구항 11

제10항에 있어서,

상기 실드 전극과 게이트 전극간의 상기 전기적 접속은 상기 종단 영역에 배치된 하나 또는 그 이상의 접촉 개구를 통해 이루어지는 전계효과 트랜지스터.

### 청구항 12

반도체 다이 내의 전계효과 트랜지스터(FET)에 있어서,

적어도 하나의 활성 셀을 포함하는 활성 영역;

활성 셀을 포함하지 않는 비활성 영역;

제1 도전성 타입의 드리프트 영역;

상기 드리프트 영역 위에 배치된 제2 도전성 타입의 본체 영역; 및

상기 본체 영역을 통해 상기 드리프트 영역 내로 연장되는 트랜치 - 상기 트랜치의 내부에는 실드 전극 및 게이트 전극이 배치되고, 상기 실드 전극은 상기 게이트 전극의 아래에 배치됨 - 을 포함하되,

상기 실드 전극과 상기 게이트 전극은 상기 트랜치를 넘어 상기 비활성 영역으로 연장되고, 상기 실드 전극은 상기 비활성 영역에 배치된 게이트 상호접속층에 의하여 상기 게이트 전극과 전기적으로 접속되는 전계효과 트랜지스터.

### 청구항 13

제12항에 있어서,

상기 트랜치에 인접하여 상기 본체 영역 내에 배치된 제1 도전성 타입의 소스 영역; 및

상기 소스 영역에 인접하여 상기 본체 영역 내에 배치된 제2 도전성 타입의 고농도 본체 영역을 더 포함하는 전계효과 트랜지스터.

#### 청구항 14

제13항에 있어서,

상기 트랜치 내에서 상기 게이트 전극에 상기 소스 영역의 최상면의 아래까지 리세스가 형성되고,

상기 전계효과 트랜지스터는,

상기 소스 영역 및 상기 고농도 본체 영역과 접촉하는 상호접속층; 및

상기 게이트 전극 위에 배치되고, 상기 게이트 전극을 상기 상호접속층으로부터 절연시키는 유전 물질을 더 포함하는 전계효과 트랜지스터.

#### 청구항 15

제12항에 있어서,

제1 도전성 타입의 기판을 더 포함하되,

상기 드리프트 영역은 상기 기판 위에서 연장되고, 상기 트랜치는 상기 본체 영역을 통해 연장되고 상기 드리프트 영역 내에서 종단되는 전계효과 트랜지스터.

#### 청구항 16

제12항에 있어서,

제1 도전성 타입의 기판을 더 포함하되,

상기 드리프트 영역은 상기 기판 위에 배치되고, 상기 트랜치는 상기 본체 영역 및 상기 드리프트 영역을 통해 연장되고 상기 기판 내에서 종단되는 전계효과 트랜지스터.

#### 청구항 17

제12항에 있어서,

상기 실드 전극과 상기 게이트 전극 사이의 배치되는 전극간 유전체(IED)를 더 포함하되,

상기 실드 전극은 또한, 상기 전극간 유전체를 통해 형성된 전기적 접속에 의하여 상기 게이트 전극과 전기적으로 접속되는 전계효과 트랜지스터.

#### 청구항 18

제12항에 있어서,

상기 비활성 영역은 상기 다이의 중앙부를 통해 연장되는 게이트 러너(gate runner) 영역을 포함하고, 상기 실드 전극과 상기 게이트 전극은 상기 트랜치를 넘어 상기 게이트 러너 영역으로 연장되며, 상기 실드 전극과 상기 게이트 전극은 상기 게이트 러너 영역에서 상기 게이트 상호접속층에 의하여 전기적으로 접속되는 전계효과 트랜지스터.

#### 청구항 19

제12항에 있어서,

상기 비활성 영역은 상기 다이의 주변을 따라 연장되는 종단 영역을 포함하고, 상기 실드 전극과 상기 게이트 전극은 상기 트랜치를 넘어 상기 종단 영역으로 연장되며, 상기 실드 전극과 상기 게이트 전극은 상기 종단 영역에서 상기 게이트 상호접속층에 의하여 전기적으로 접속되는 전계효과 트랜지스터.

#### 청구항 20

전계효과 트랜지스터(FET)에 있어서,

반도체 영역으로 연장되는 복수의 트랜치를 포함하되,

각각의 트랜치는 게이트 전극 및 실드 전극을 포함하고, 상기 게이트 전극과 상기 실드 전극의 사이에는 전극간 유전체가 배치되고,

각각의 트랜치의 상기 실드 전극, 상기 전극간 유전체 및 상기 게이트 전극은 상기 전계효과 트랜지스터의 비활성 영역으로 연장되고, 각각의 트랜치의 상기 실드 전극과 상기 게이트 전극은 상기 전계효과 트랜지스터의 상기 비활성 영역의 접촉 개구 내에 배치된 상호접속층을 통해 전기적으로 접속되며,

상기 접촉 개구는 상기 전극간 유전체에 의해 정의되는 제1 부분과 상기 게이트 전극의 측벽에 의해 정의되는 제2 부분을 포함하는,

전계효과 트랜지스터.

## 청구항 21

전계효과 트랜지스터(FET)를 형성하는 방법에 있어서,

반도체 영역에 트랜치를 형성하는 단계;

상기 트랜치의 하부 측벽과 바닥 표면을 덮는 실드 유전체층을 형성하는 단계;

상기 트랜치의 하부에 실드 전극을 형성하는 단계;

상기 실드 전극 위에 상기 트랜치의 상부 측벽을 따라서 유전체층을 형성하는 단계;

상기 트랜치 내에, 상기 실드 전극 위에 게이트 전극을 형성하는 단계 - 상기 실드 전극과 상기 게이트 전극은, 상기 실드 전극과 상기 게이트 전극이 상기 트랜치를 넘어 메사(mesa) 영역 위에서 연장되도록 형성됨 - ;

상기 게이트 전극에 복수의 접촉 개구를 형성하는 단계 - 상기 접촉 개구를 통해 상기 실드 전극의 표면 구역이 노출됨 - ; 및

상기 접촉 개구 내에, 상기 게이트 전극을 상기 실드 전극과 전기적으로 접속하는 상호접속층을 형성하는 단계를 포함하는 전계효과 트랜지스터 형성 방법.

## 청구항 22

삭제

## 청구항 23

제21항에 있어서,

상기 메사 영역은 상기 전계효과 트랜지스터를 수용하는 다이의 비활성 영역에 배치되는, 전계효과 트랜지스터 형성 방법.

## 청구항 24

제21항에 있어서,

상기 유전체층은 실리콘의 산화에 의하여 형성되는 전계효과 트랜지스터 형성 방법.

## 청구항 25

제21항에 있어서,

상기 반도체 영역은 제1 도전성 타입의 기판 위에 배치된 제1 도전성 타입의 에피택시층을 포함하고,

상기 전계효과 트랜지스터 형성 방법은,

상기 에피택시층에 제2 도전성 타입의 본체 영역을 형성하는 단계;

상기 트랜치에 인접하여 상기 본체 영역에 제1 도전성 타입의 소스 영역을 형성하는 단계; 및

상기 소스 영역에 인접하여 상기 본체 영역에 제2 도전성 타입의 고농도 본체 영역을 형성하는 단계를 더 포함하는 전계효과 트랜지스터 형성 방법.

### 청구항 26

제21항에 있어서,

상기 게이트 전극을 형성하기 전에, 상기 실드 전극 위에서 연장되는 상기 유전체층의 일부에 하나 또는 그 이상의 개구를 형성하는 단계를 더 포함하되,

상기 트랜치에 상기 게이트 전극이 형성되면, 상기 하나 또는 그 이상의 개구를 통하여 상기 게이트 전극이 상기 실드 전극에 전기적으로 접촉하는 전계효과 트랜지스터 형성 방법.

### 청구항 27

반도체 다이에 활성 영역 및 비활성 영역을 포함하는 전계효과 트랜지스터(FET)를 형성하는 방법에 있어서,

상기 활성 영역에 반도체 영역으로 연장되는 트랜치를 형성하는 단계;

상기 트랜치 내에 제1 폴리실리콘층을 형성하는 단계 - 상기 제1 폴리실리콘층은 상기 비활성 영역의 메사 영역 위에서 연장되는 부분을 포함함 - ;

상기 트랜치의 바닥부에 실드 전극을 형성하기 위하여 상기 트랜치 내의 상기 제1 폴리실리콘층에 리세스를 형성하는 단계 - 상기 트랜치 내의 상기 실드 전극은 상기 제1 폴리실리콘층의 상기 비활성 영역의 상기 메사 영역 위에서 연장되는 부분과 전기적으로 연속성을 가짐 - ;

(i) 상기 트랜치의 노출된 상부 측벽, (ii) 상기 실드 전극의 상부 표면, 및 (iii) 상기 메사 영역 위의 상기 제1 폴리실리콘층의 상기 부분의 표면 구역의 적어도 일부를 덮는 유전체층을 실리콘의 산화를 사용하여 형성하는 단계;

상기 트랜치 내에 제2 폴리실리콘층을 형성하는 단계 - 상기 제2 폴리실리콘층은 상기 메사 영역에서 상기 유전체층 위에서 연장되는 부분을 포함함 - ;

상기 트랜치의 상부에 게이트 전극을 형성하기 위하여 상기 트랜치 내의 상기 제2 폴리실리콘층에 리세스를 형성하는 단계 - 상기 트랜치 내의 상기 게이트 전극은 상기 제2 폴리실리콘층의 상기 메사 영역 위에서 연장되는 부분과 전기적으로 연속성을 가짐 - ;

상기 제2 폴리실리콘층의 상기 메사 영역 위에서 연장되는 부분 및 상기 유전체층의 상기 메사 영역 위에서 연장되는 부분에 적어도 하나의 접촉 개구를 형성하는 단계 - 상기 적어도 하나의 접촉 개구를 통하여 상기 제1 폴리실리콘층의 표면 구역이 노출됨 - ; 및

상기 적어도 하나의 접촉 개구 내에, 상기 제1 폴리실리콘층을 상기 제2 폴리실리콘층과 전기적으로 접속하는 게이트 상호접속층을 형성하는 단계

를 포함하는 전계효과 트랜지스터 형성 방법.

### 청구항 28

제27항에 있어서,

상기 제1 폴리실리콘층을 형성하기 전에, 상기 트랜치의 측벽과 바닥을 덮고 상기 메사 영역 위에서 연장되는 실드 유전체층을 형성하는 단계; 및

상기 트랜치 내의 상기 제1 폴리실리콘층에 리세스를 형성한 후에, 상기 트랜치의 상부 측벽을 노출시키기 위하여 상기 트랜치 내의 상기 실드 유전체층에 리세스를 형성하는 단계를 더 포함하는 전계효과 트랜지스터 형성 방법.

### 청구항 29

제27항에 있어서,

상기 반도체 영역은 제1 도전성 타입의 기판 위에 배치되는 제1 도전성 타입의 에피택시층을 포함하고,

상기 전계효과 트랜지스터 형성 방법은,

상기 에피택시층에 제2 도전성 타입의 본체 영역을 형성하는 단계;

상기 트랜치에 인접하여 상기 본체 영역 내에 제1 도전성 타입의 소스 영역을 형성하는 단계; 및

상기 소스 영역에 인접하여 상기 본체 영역 내에 제2 도전성 타입의 고농도 본체 영역을 형성하는 단계를 더 포함하는 전계효과 트랜지스터 형성 방법.

### 청구항 30

삭제

### 청구항 31

삭제

### 청구항 32

삭제

### 청구항 33

삭제

### 청구항 34

삭제

### 청구항 35

삭제

## 명세서

### 기술 분야

[0001]

본 발명은 일반적으로 전력 반도체 전계효과 트랜지스터(FETs)에 관한 것이고, 보다 구체적으로는 실드 전극과 게이트 전극이 접속된 실드 게이트 트랜치 전계효과 트랜지스터에 관한 것이다.

### 배경 기술

[0002]

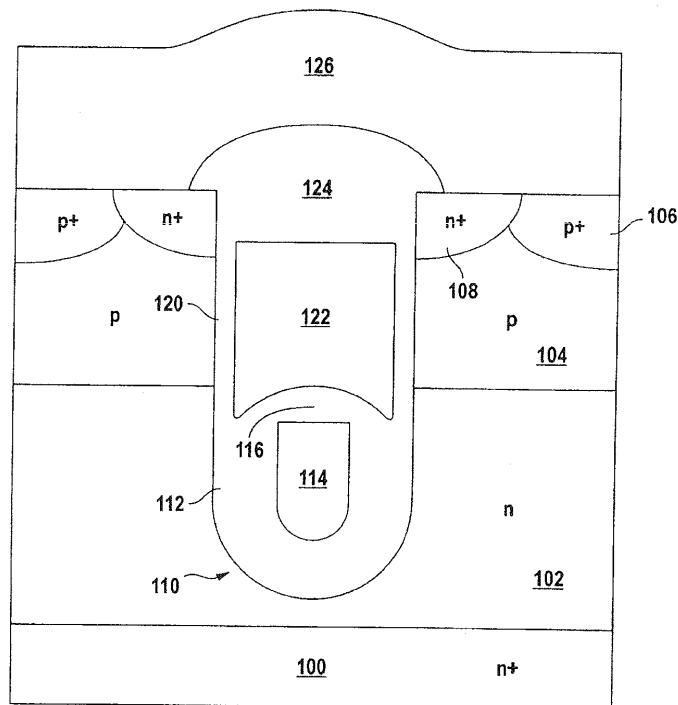

실드 게이트 트랜치 전계효과 트랜지스터(shielded gate trench FETs)는, 실드 전극이 게이트-드레인 용량 (gate-drain capacitance; Cgd)을 감소시키고 트랜지스터의 항복 전압(breakdown voltage)을 향상시킨다는 점에서, 종래의 FET보다 우수하다. 도 1은 종래의 실드 게이트 트랜치 금속산화물 반도체 전계효과 트랜지스터 (MOSFET)의 단순화된 단면도이다. n-타입 에피택시층 102는 n+ 기판 100 위에서 연장된다. N+ 소스 영역 108과 p+ 고농도(heavy) 본체 영역 106은, 에피택시층 102에 형성된 p-타입 본체 영역 104에 형성된다. 트랜치 110은 본체 영역 104를 통해서 연장되고 드리프트 영역에서 종단된다. 트랜치 110은 게이트 전극 122 아래에 실드 전극 114를 포함한다. 게이트 전극 122는 인접한 실리콘 영역으로부터 게이트 유전체 120에 의해 절연되고, 실드 전극 114는 인접한 실리콘 영역으로부터 게이트 유전체 120보다 더 두꺼운 실드 유전체 112에 의해 절연된다.

[0003]

상기 게이트 전극과 실드 전극은 전극간 유전체(inter-electrode dielectric; IED)라고도 불리는 유전체층 116에 의해 서로로부터 절연된다. IED층 116은 실드 전극 114와 게이트 전극 122 사이에 존재할 수 있는 전위 차

이를 견디기에 충분한 품질과 두께를 가져야 한다. 또한, IED층 116 내의 또는 상기 실드 전극 114와 IED층 116 사이의 경계면에서의 경계면 트랩 전하(trap charges) 및 유전체 트랩 전하는 주로 상기 IED층을 형성하는 방법과 연관된다.

[0004] 상기 IED는 일반적으로 다양한 처리 방법에 의해 형성된다. 그러나, 상기의 요구되는 전기적 특성을 제공할 만큼 충분히 강하고 신뢰성 있는 고품질의 IED를 보장하기 위해서는 실드 게이트 트랜치 FET를 형성하는 복잡한 처리 과정이 필요하다. 이에 따라, 온-저항(on-resistance)과 같은 이러한 전기적 특성을 유지하거나 향상시키는 동시에 고품질의 IED에 대한 필요는 제거하는, 실드 게이트 트랜치 FET를 형성하는 구조물 및 방법에 대한 요구가 존재한다.

### 발명의 상세한 설명

[0005] 본 발명의 일 실시예에 의하면, 전계효과 트랜지스터는, 반도체 영역으로 연장되는 복수의 트랜치를 포함한다. 각각의 트랜치는 게이트 전극 및 실드 전극을 포함하고, 상기 게이트 전극과 상기 실드 전극의 사이에는 전극간 유전체가 존재하며, 상기 실드 전극과 상기 게이트 전극은 전기적으로 접속한다.

[0006] 일 실시예에서, 상기 실드 전극은 각각의 트랜치의 하부에 위치하고, 실드 유전체에 의해 상기 반도체 영역으로부터 절연된다. 전극간 유전체(inter-electrode dielectric; IED)는 각각의 실드 전극 위에서 연장된다. 상기 게이트 전극은, 상기 전극간 유전체 위의 각각의 트랜치의 상부에 위치하고, 게이트 유전체에 의해 상기 반도체 영역으로부터 절연된다.

[0007] 다른 실시예에서, 상기 반도체 영역은 제1 도전성 타입의 드리프트(drift) 영역, 상기 드리프트 영역 위에서 연장되는 제2 도전성 타입의 본체 영역, 및 상기 트랜치에 인접한 상기 본체 영역에 위치하는 제1 도전성 타입의 소스 영역을 포함한다.

[0008] 다른 실시예에서, 상기 반도체 영역은 제1 도전성 타입의 기판을 더 포함하고, 상기 드리프트 영역은 상기 기판 위에서 연장되며, 상기 트랜치는 상기 본체 영역을 통해 연장되고 상기 드리프트 영역 내에서 종단된다.

[0009] 다른 실시예에서, 상기 트랜치는 상기 본체 영역 및 상기 드리프트 영역을 통해 연장되고 상기 기판 내에서 종단된다.

[0010] 다른 실시예에서, 상기 전계효과 트랜지스터는, 상기 트랜치가 형성되는 활성 영역 및 비활성 영역을 더 포함한다. 상기 실드 전극과 상기 게이트 전극은 각각의 트랜치를 넘어 상기 비활성 영역으로 연장되고, 상기 비활성 영역에서 상기 실드 전극과 게이트 전극이 게이트 상호접속층에 의하여 전기적으로 접속된다.

[0011] 다른 실시예에서, 상기 실드 전극과 상기 게이트 전극간의 전기적 접속은 상기 비활성 영역의 게이트 러너 영역에 주기적으로 형성된 접촉 개구를 통해 이루어진다.

[0012] 또 다른 실시예에서, 상기 실드 전극은 각각의 트랜치 내의 상기 전극간 유전체를 통한 추가적인 접속에 의하여 상기 게이트 전극에 전기적으로 접속된다.

[0013] 또 다른 실시예에서, 상기 비활성 영역은 상기 전계효과 트랜지스터를 수용하는 다이의 주변을 따라서 연장되는 종단 영역을 포함하고, 상기 실드 전극과 상기 게이트 전극은 각각의 트랜치를 넘어 상기 종단 영역으로 연장되고, 상기 종단 영역에서 상기 실드 전극과 게이트 전극이 게이트 상호접속층에 의하여 전기적으로 접속된다.

[0014] 본 발명의 다른 실시예에 의하면, 전계효과 트랜지스터가 다음과 같이 형성된다. 반도체 영역으로 연장되는 복수의 트랜치가 형성된다. 각각의 트랜치의 바닥부에 실드 전극이 형성된다. 상기 실드 전극 위에서 각각의 트랜치의 상부에 게이트 전극이 형성된다. 상기 실드 전극과 상기 게이트 전극을 전기적으로 접속하는 게이트 상호접속층이 형성된다.

[0015] 일 실시예에서, 상기 실드 전극이 형성되기 전에 각각의 트랜치의 하부 측벽과 바닥 표면을 덮는 실드 유전체층이 형성된다. 상기 게이트 전극이 형성되기 전에 상기 트랜치의 상부 측벽과 상기 실드 전극의 표면을 덮는 유전체층이 형성된다.

[0016] 다른 실시예에서, 상기 실드 전극 및 상기 게이트 전극은 상기 트랜치를 넘어 메사 영역 위로 연장되도록 형성된다. 상기 게이트 전극의 상기 메사 영역 위에서 연장되는 부분에 복수의 접촉 개구가 형성되고, 상기 접촉 개구를 통하여 상기 실드 전극의 표면 구역이 노출된다. 상기 상호접속층은 상기 접촉 개구를 채우도록 형성되

어, 상기 실드 전극과 게이트 전극을 서로 전기적으로 접속한다.

[0017] 다른 실시예에서, 상기 메사 영역은 상기 전계효과 트랜지스터를 수용하는 다이의 비활성 영역에 존재한다.

[0018] 다른 실시예에서, 상기 유전체층은 실리콘의 산화에 의하여 형성된다.

[0019] 다른 실시예에서, 상기 게이트 전극이 형성되기 전에, 상기 유전체층의 상기 실드 전극 위에서 연장되는 부분에 하나 또는 그 이상의 개구가 형성됨으로써, 상기 트랜치에 상기 게이트 전극이 형성되면, 상기 하나 또는 그 이상의 개구를 통하여 상기 게이트 전극이 상기 실드 전극에 전기적으로 접촉한다.

## 실시예

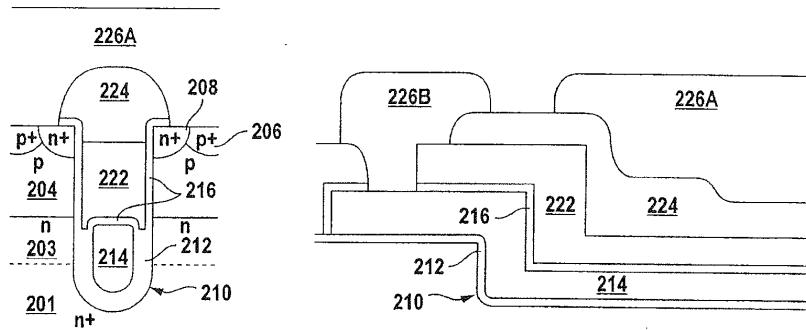

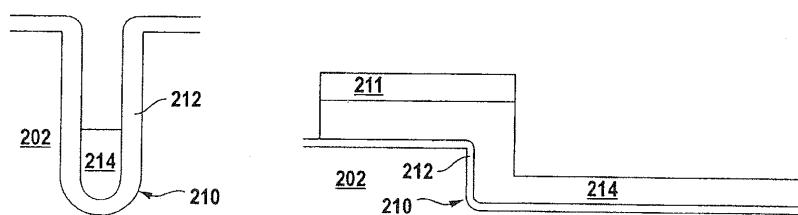

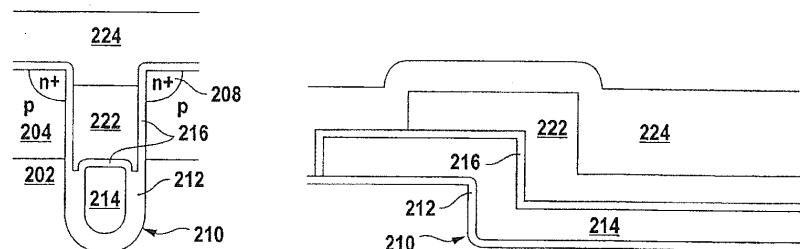

[0023] 도 2A 내지 2H는 본 발명의 일 실시예에 의한 실드 게이트 트랜치 전계효과 트랜지스터를 형성하는 처리 과정의 다양한 단계에서의 단순화된 단면도이다. 도 2A 내지 2H에서, 좌측 단면도는 실드 게이트 트랜치 전계효과 트랜지스터 구조물을 형성하는 단계들의 시퀀스를 활성 영역에서 도시한 것이고, 우측 단면도는 이에 대응되는 활성 영역으로부터 비활성 영역으로의(우로부터 좌로) 천이(transition) 영역에서의 도면이다. 본 명세서에서,

"활성 영역(active region)"은 다이의 활성 셀을 수용하는 구역을 나타내고, "비활성 영역(non-active region)"은 활성 셀을 포함하지 않은 다이의 구역을 나타낸다. 상기 비활성 영역은 상기 다이의 주변을 따라서 연장되는 종단 영역 및 상기 다이의 주변 또는 중앙부를 따라서 또는 상기 다이의 주변과 중앙부의 모두를 따라서 연장되는 게이트 러너를 포함한다.

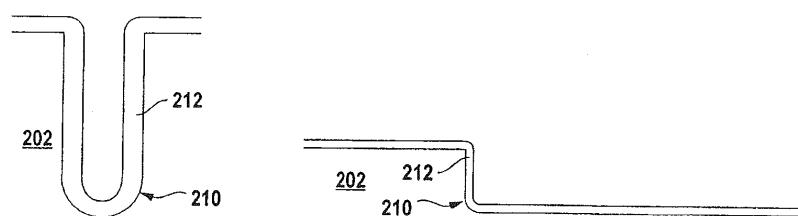

[0024] 도 2A에서, 종래 기술을 사용하여, 반도체 영역 202에 트랜치 210이 형성되고, 상기 트랜치의 측벽과 바닥 표면을 덮고 상기 트랜치에 인접한 메사 영역(mesa regions)으로 연장되도록 실드 유전체 212(예를 들어, 산화물을 포함함)가 형성된다. 도 2A 내지 2H의 각각에서 우측 단면도는, 좌측 단면도에 수직인 방향을 따라서 좌측 단면도에 도시된 트랜치의 중심을 관통한다. 이렇게 해서, 우측 단면도는 좌측 단면도의 트랜치가 활성 영역의 에지에서 종단되는 것을 도시한다. 또한, 상기 단면도들은 일정한 비율로 도시된 것은 아니며, 특히 우측 단면도와 좌측 단면도의 동일한 층 또는 영역의 물리적 치수(예를 들어, 두께)가 동일하지 않은 것처럼 보일 수 있다. 예를 들어, 도 2A에서, 실드 유전체 212는 좌측 단면도보다 우측 단면도에서 더 얇아 보인다.

[0025] 도 2A의 우측 단면도에 도시된 것처럼, 실드 유전체 212는 트랜치 210의 바닥 표면을 따라서 연장되고, 상기 활성 영역의 에지에서 트랜치 210을 넘어 실리콘 영역 202 위로 상승하여 연장된다. 일 실시예에서, 반도체 영역 202는 고농도로 도핑된 n-타입 기판(도시되지 않음) 위에 형성된 n-타입 에피택시층(도시되지 않음)을 포함하고, 트랜치 202는 에피택시층 내로 연장되고 그 내부에서 종단된다. 다른 변형예에서, 트랜치 202는 에피택시층을 통해 연장되고 상기 기판 내에서 종단된다.

[0026] 도 2B에서, 실드 전극 214는 트랜치 210의 바닥부를 따라 형성되고, 다음과 같이 상기 다이의 비활성 영역에서 전기적으로 접근가능하게 된다. 공지 기술을 사용하여, 먼저 도전성 물질(예를 들어, 도핑된 또는 도핑되지 않은 폴리실리콘을 포함함)이 상기 트랜치를 채우고 상기 메사 영역 위에서 연장되도록 형성되고, 이어서 실드 전극 214를 형성하기 위해 상기 도전성 물질에 트랜치 210 내로 깊게 리세스가 형성된다.

[0027] 상기 도전성 물질에 리세스를 형성하는 동안, 상기 다이의 상기 비활성 영역에서 연장되는 상기 도전성 물질의 일부분을 보호하기 위해 마스크 211이 사용된다. 결과적으로, 도 2B의 우측 단면도에 도시된 바와 같이, 실드 전극 214는 상기 다이의 비활성 영역 내의 상기 메사 표면 위에서보다 트랜치 210의 내측에서 더 두껍다. 상기 활성 영역의 에지에서, 상기 실드 전극이 트랜치 210을 넘어 상기 비활성 영역의 메사 표면 위로 연장되도록, 추가적인 마스크 211이 적용된다. 이렇게 해서 트랜치 210 내측의 실드 전극 214가 상기 다이의 비활성 영역에서 전기적 접속에 이용가능하게 된다.

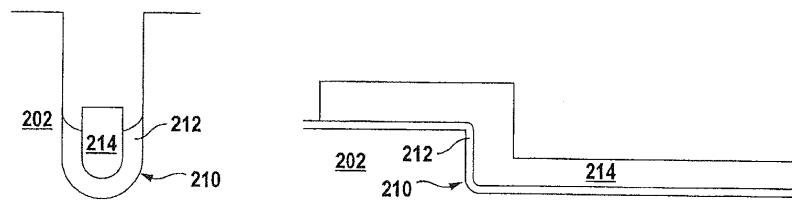

[0028] 도 2C에서, 공지의 방법을 사용하여, 우측 단면도에 도시된 것처럼, 트랜치의 측벽을 따라 그리고 상기 활성 영역의 메사 표면 위에서 실드 유전체 212가 완전히 제거된다. 이렇게 해서 상기 실드 유전체에는 실드 전극 214의 최상면 아래로 리세스가 형성된다. 일 실시예에서는, 실드 전극 214의 최상면이 실드 유전체층 212의 최상면과 동일 평면이 되도록 상기 실드 전극 214에 리세스가 형성된다. 이는 이후의 게이트/전극간 유전체층의 형성을 위한 평평한 표면을 제공한다.

[0029] 도 2D에서, 트랜치의 상부 측벽을 따라서 연장되는 게이트 유전체층 216이 종래의 기술을 사용하여 형성된다. 일 실시예에서, 게이트 유전체 216은 종래의 실리콘 산화를 사용하여 형성된다. 이 처리는 또한 실드 전극 214

의 산화를 일으켜 게이트 전극 214 위에 전극간 유전체(IED) 층을 형성한다. 우측 단면도에 도시된 바와 같이, 활성 및 비활성 영역 내에서 실드 전극 214의 모든 노출된 표면을 따라서 유전체층 216이 연장된다. 이하에서 논의되는 바와 같이, 고품질의 IED를 형성하는데 일반적으로 요구되는 추가적인 처리 단계들이 제거된다.

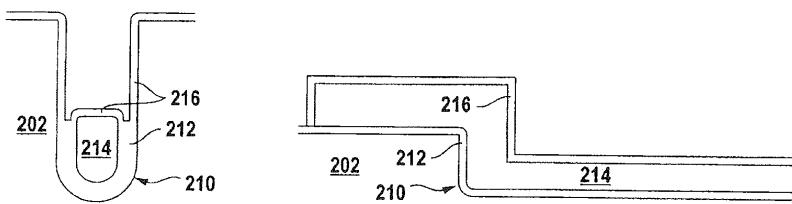

[0030] 도 2E에서, 리세스가 형성된 게이트 전극 222가 트랜치 210 내에 형성되고 다음과 같이 상기 비활성 영역에서 전기적으로 접근가능하게 된다. 종래 기술을 사용하여, 트랜치 210을 채우고 상기 다이의 활성 및 비활성 영역의 메사 표면 위에서 연장되는 제2 도전층(예를 들어, 도핑된 폴리실리콘을 포함함)이 형성된다. 게이트 전극 222를 형성하기 위해 상기 제2 도전층에는 트랜치 210 내로 리세스가 형성된다.

[0031] 상기 제2 도전층에 리세스를 형성하는 동안, 상기 다이의 비활성 영역에서 연장되는 상기 제2 도전성 물질의 일부분을 보호하기 위해 마스크 219가 사용된다. 결과적으로, 도 2B의 우측 단면도에 도시된 것처럼 게이트 전극 222는 상기 다이의 비활성 영역 내의 상기 메사 표면 위에서보다 트랜치 210 내측에서 더 두껍다. 상기 활성 영역의 에지에서, 리세스가 형성된 상기 게이트 전극 222가 트랜치 210을 넘어 상기 비활성 영역의 메사 표면 위로 연장되도록 추가적인 마스크 219가 적용된다. 이렇게 해서 트랜치 210 내측의 게이트 전극 222가 상기 다이의 비활성 영역에서 전기적 접속에 이용가능하게 된다. 마스크 219는 상기 비활성 영역의 전체 실드 전극 214 위에서는 연장되지 않는다는 점에 유의한다. 이하에서 논의되는 바와 같이, 이는 동일한 접촉 개구를 통한 상기 게이트 전극과 상기 실드 전극의 접촉을 용이하게 한다.

[0032] 도 2E에서, 종래의 본체 주입 및 드라이브인(drive-in) 기술을 사용하여 반도체 영역 202에 p-타입 본체 영역 204가 형성된다. 트랜치 210에 인접한 본체 영역 216에는 고농도로 도핑된 n-타입 소스 영역 208이 종래의 소스 주입 기술을 사용하여 형성된다.

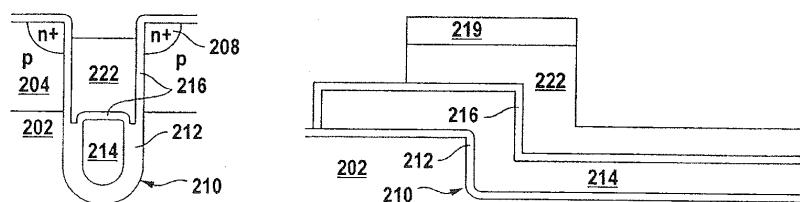

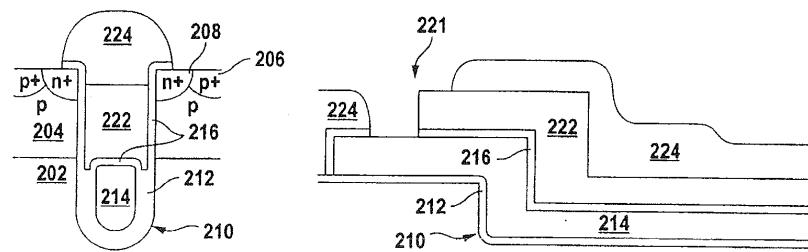

[0033] 도 2F에서, 상기 구조 위에 공지 기술을 사용하여 BPSG와 같은 유전체층 224가 형성된다. 도 2G에서, 상기 활성 영역 내에 소스-본체 접촉 개구를 형성하기 위해 유전체층 224에 패턴이 형성되고 유전체층 224가 식각되며, 다음으로 유전체 유동이 수행된다. 좌측 단면도에 도시된 것처럼, 게이트 전극 222 위의 전체에서 연장되고 소스 영역 208 위의 일부에서 연장되는 유전체 돔(dome) 225가 형성된다. P-타입 고농도 본체 영역 206이 종래의 주입 기술을 사용하여 노출된 반도체 영역 202에 형성된다. 우측 단면도에 도시된 바와 같이, 게이트 전극 222의 표면 영역 및 측벽 그리고 실드 전극 214의 표면 영역을 노출시키기 위하여, 상기 활성 영역 내에 접촉 개구를 형성하는 마스킹 및 식각 처리와 동일한 처리가 상기 비활성 영역의 유전체층 224에 접촉 개구 221을 형성하는데 사용된다.

[0034] 도 2H에서, 상기 구조 위에 상호접속층(예를 들어, 금속을 포함함)이 형성되고 소스-본체 상호접속부 226A 및 게이트 상호접속부 226B를 형성하기 위해 상기 상호접속층에 패턴이 형성된다. 좌측 단면도에 도시된 바와 같이, 소스-본체 상호접속부 226A는 소스 영역 208 및 고농도 본체 영역 206과 접촉하지만 유전체 돔 224에 의해 게이트 전극 222로부터는 절연된다. 우측 단면도에 도시된 바와 같이, 게이트 금속 226B는 실드 전극 214 및 게이트 전극 222와 접촉 개구 221을 통해 접촉하고 이에 따라 상기 두 전극을 서로 단락(short)시킨다.

[0035] 이렇게 해서, 실드 전극이 부유되거나(floating, 즉, 전기적으로 바이어스되지 않음) 또는 소스 전위(예를 들어, 접지 전위)로 바이어스되는 종래의 실드 게이트 전계효과 트랜지스터와 달리, 도 2H에 도시된 전계효과 트랜지스터의 실시예에서는, 실드 전극이 게이트 전극에 접속되고 상기 게이트 전극과 동일한 전위로 바이어스된다. 실드 전극이 부유되거나 접지 전위에 접속되는 종래의 전계효과 트랜지스터에서는, 상기 실드 및 게이트 전극 사이의 전위 차이를 견디기 위해 일반적으로 고품질 IED가 요구된다. 그러나, 실드 전극과 게이트 전극의 전기적 접속은 고품질 IED에 대한 요구를 제거한다. 상기 실드 전극은, 상기 게이트 전위로 바이어스되지만, 여전히 동일한 항복 전압을 위한 온 저항의 감소를 가능하게 하는 전하 균형 구조로서 기능한다. 따라서, 고품질 IED의 형성과 관련된 처리 단계들을 제거하는 동시에, 동일한 항복 전압을 위한 낮은 온 저항이 성취된다. 이론적으로, 이러한 구조는 IED를 필요로 하지 않지만, 게이트 유전체의 형성 중에 IED가 자연적으로 형성된다. 따라서, 단순한 제조 과정을 사용하여 고성능의 트랜지스터가 형성된다.

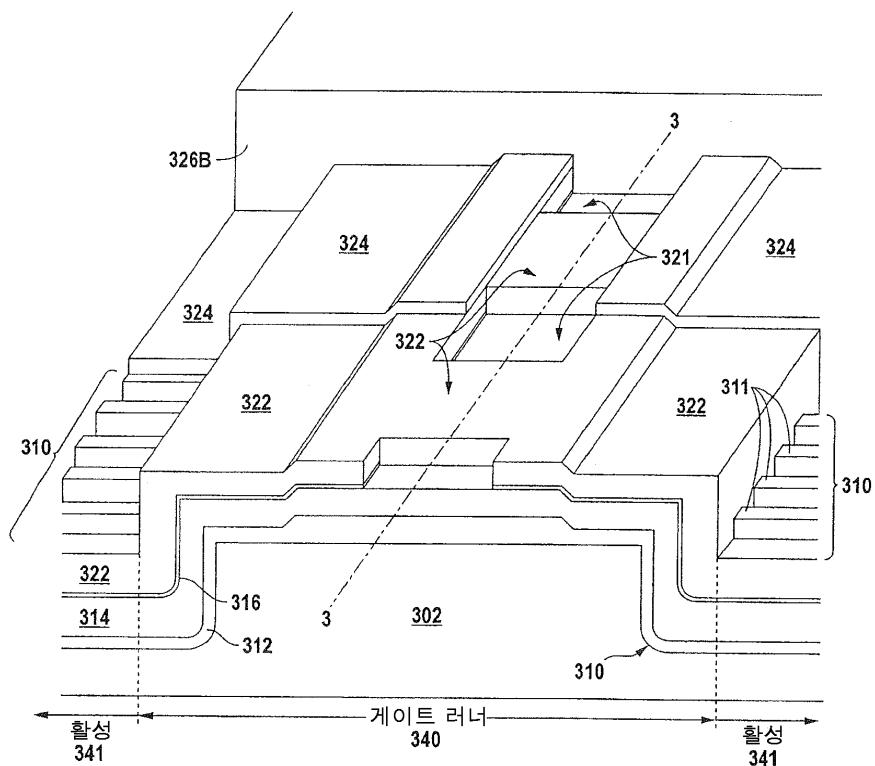

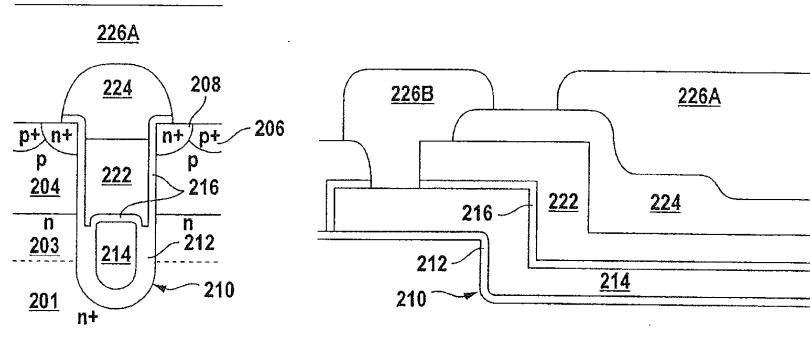

[0036] 게이트 전극과 실드 전극간의 전기적 접속은 다이의 종단 또는 에지 영역, 또는, 도 3에 도시된 것처럼 게이트 러너가 연장되는 다이의 중앙부와 같은 비활성 영역의 어디에나 형성될 수 있다. 도 3은 본 발명의 일 실시예에 의한 실드 게이트 트랜치 전계효과 트랜지스터의 게이트 러너의 일부분의 등각도이다. 상부 층(예를 들어, 게이트 상호접속층 326B와 유전체층 324)은 그 아래에 놓인 구조물을 드러내기 위해 벗겨져 있다. 도시된 바와 같이, 활성 영역 341의 평행하게 연장되는 트랜치 310은 게이트 러너 영역 340의 양측에서 종단된다.

[0037] 게이트 러너 영역 340은 선분 3-3에 대해 구조적으로 대칭적이고 그 절반의 각각은 도 2H에 도시된 것과 구조적

으로 유사하다. 실드 유전체 312는 트랜치의 열 310을 넘어 게이트 러너 영역 340의 메사 표면 위로 연장된다. 마찬가지로, 실드 전극 314, 전극간 유전체 316 및 게이트 전극 322의 각각이 트랜치의 열 310을 넘어 게이트 러너 영역 340의 메사 표면 위로 연장된다. 영역 311은 활성 영역 341의 인접한 트랜치들 사이의 메사를 나타낸다.

[0038] 접촉 개구 321은, 게이트 상호접속층 326B(예를 들어, 금속을 포함함)가 전기적 접촉을 형성하는 실드 전극 314의 표면 구역을 노출시킨다. 또한, 게이트 상호접속층 326B는 유전체층 324를 통해 노출된 게이트 전극 322의 표면 구역 332와 전기적 접촉을 형성한다. 상기 트랜치 내측의 각각의 게이트 전극을 바이어스시킴에 있어서의 지연을 최소화하기 위해서는 게이트 저항을 최소화하는 것이 바람직하다. 동일한 이유로, 상기 트랜치 내측의 각각의 실드 전극을 바이어스시킴에 있어서의 지연을 최소화하는 것이 바람직하다. 이에 따라, 게이트 러너 영역 340 내의 접촉 개구 321의 빈도 및 형상이 저항을 최소화하도록 최적화될 수 있고, 이에 따라 게이트 패드 (gate pad)로부터 게이트 및 실드 전극 각각으로의 지연을 최소화할 수 있다. 상기 실드 및 게이트 전극을 바이어스시킴에 있어서의 지연은 게이트 러너 영역 및 상기 다이의 종단 또는 에지 영역의 양쪽에서 게이트 전극과 실드 전극 간의 접촉을 형성함으로써 더욱 감소될 수 있다.

[0039] 본 발명의 다른 실시예들에 의하면 상기 실드 및 게이트 전극은 다른 방식에 의해 전기적으로 접속될 수 있다. 예를 들어, 각각의 트랜치의 IED 위에 게이트 전극을 형성하기 전에 소정의 위치에서 상기 IED가 식각될 수 있다. 이 실시예에서는, 도 2H 및 3에 도시된 접촉 개구가 필요하지 않고, 각각의 트랜치의 게이트 전극으로의 게이트 상호접속 접촉부 또한 상기 IED 내의 단락을 통해 대응하는 실드 전극에 연결될 것이다. 다른 실시예에 의하면, IED 내의 개구를 통해 그리고 종단 영역과 게이트 러너 영역과 같은 비활성 영역에 형성된 접촉 개구를 통해 게이트과 실드 전극의 접촉이 형성될 수 있다. 고품질의 IED에 대한 요구가 제거됨으로써 드레인-소스간 온 저항  $R_{DSon}$ 이 향상된 실드 게이트 트랜치 MOSFET을 형성하는 처리 과정이 단순하고 좀 더 제어가능하게 된다.

[0040] 본 발명의 원리는, 여하한 목적으로 참조에 의해 본 명세서에 편입된 "전력 반도체 디바이스 및 제조 방법"이라는 명칭의 미국 특허출원 제11/026,276호의 도 3A, 3B, 4A, 4C, 6 내지 8, 9A 내지 9C, 11, 12, 15, 16, 24 및 26A 내지 26C에 도시된 것과 같은 임의의 실드 게이트 전계효과 트랜지스터 구조물에 적용될 수 있다.

[0041] 본 발명의 바람직한 실시예들이 위에서 설명되었지만, 많은 변경, 변형 및 등가물들이 가능하다. 본 발명이 속하는 분야에서 통상의 지식을 가진 자는 동일한 기술이 다른 타입의 초접합(super junction) 구조물 뿐만 아니라 좀 더 넓게는 수평형 디바이스를 포함하는 다른 종류의 디바이스들에도 적용될 수 있다는 것을 인식할 것이다. 예를 들어, 본 발명의 실시예들은 n-채널 MOSFET에 관하여 기술되었지만, 다양한 영역의 도전성 타입을 반전시키는 것만으로 p-채널 MOSFET에 본 발명의 원리가 적용될 수 있다. 따라서, 상기 기재에 의해 본 발명의 영역을 제한해서는 안 되며, 본 발명의 영역은 첨부된 청구범위에 의해 정의되어야 한다.

## 도면의 간단한 설명

[0020] 도 1은 종래의 실드 게이트 트랜치 MOSFET의 단면도이다.

[0021] 도 2A 내지 2H는 본 발명의 일 실시예에 의한 실드 게이트 트랜치 전계효과 트랜지스터를 형성하는 처리 과정의 다양한 단계에서의 단순화된 단면도이다.

[0022] 도 3은 본 발명의 일 실시예에 의한 실드 게이트 트랜치 전계효과 트랜지스터의 게이트 러너(gate runner)의 일 부분의 등각도이다.

도면

도면1

(종래 기술)

도면2A

도면2B

## 도면2C

## 도면2D

## 도면2E

## 도면2F

## 도면2G

## 도면2H

## 도면3