(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-308629

(P2005-308629A)

(43) 公開日 平成17年11月4日(2005.11.4)

(51) Int.Cl.<sup>7</sup>

**G21K 1/06**

**G03F 7/20**

**G21K 5/00**

**G21K 5/02**

**H01L 21/027**

F 1

G21K 1/06

G21K 1/06

G21K 1/06

G03F 7/20

G21K 5/00

テーマコード(参考)

2H097

5FO46

N

503

Z

審査請求 未請求 請求項の数 14 O L (全 21 頁) 最終頁に続く

(21) 出願番号

特願2004-128128 (P2004-128128)

(22) 出願日

平成16年4月23日 (2004.4.23)

(71) 出願人

000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人

100086818

弁理士 高梨 幸雄

(72) 発明者

山本 武

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

(72) 発明者

三宅 明

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

F ターム(参考) 2H097 CA15 LA10

5FO46 GB01

(54) 【発明の名称】ミラーユニット及びその製造方法

## (57) 【要約】

【課題】 基板を変形させる手段とcoating mill in g手段(多層膜を部分的に除去する方法)を適切に組み合わせて使うことで、波面収差が小さく、高反射率で、工程的にも簡単で、高品位のミラーユニットを得ること。

【解決手段】 第1面に多層膜が施されている基板と、該基板の形状を変形させる基板変形手段とを有するミラーユニットであって、前記多層膜の最表層を含む1以上の層の膜が部分的に欠けていること。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

第1面に多層膜が施されている基板と、該基板の形状を変形させる基板変形手段とを有するミラーユニットであって、

前記多層膜の最表層を含む1以上の層の膜が部分的に欠けていることを特徴とするミラーユニット。

**【請求項 2】**

前記基板変形手段は複数のアクチュエータを有しており、該複数のアクチュエータが前記基板の前記第1面と反対側の第2面に連結されていることを特徴とする請求項1記載のミラーユニット。

**【請求項 3】**

前記基板変形手段は、前記基板の一面の大きさと略同程度の周期長の変形を行っており、該基板のそれよりも短い周期長の変形は、前記多層膜の部分的な膜層の削除により補正されていることを特徴とする請求項1又は2のミラーユニット。

**【請求項 4】**

前記基板の一面の大きさの1/2と等しい又は略等しい周期長の形状変化の補正は、前記基板変形手段で行い、該基板の一面の大きさの1/10以下の周期長の形状変化の補正是多層膜の部分的な膜層の削除により補正されていることを特徴とする請求項1又は2に記載のミラーユニット。

**【請求項 5】**

前記基板変形手段は、前記反射面に波長λの光束を前記反射面に入射させたとき、反射光束の波面の誤差がλ/2以上ある領域に対する反射面上の基板の変形の補正を行い、該基板のそれよりも小さい波面の誤差を生ずる領域は、前記多層膜の部分的な膜層の削除により補正されていることを特徴とする請求項1又は2のミラーユニット。

**【請求項 6】**

前記多層膜は60層以上の膜より成り、膜層の削除は最上層から数えて最大20層まであることを特徴とする請求項1から5のいずれか1項のミラーユニット。

**【請求項 7】**

基板の第一面が多層膜が施された反射面であり、該多層膜は最表層を含む最大20層までが部分的に膜除去手段で削除されており、該基板は、該基板の一面と反対側の面に設けた基板変形手段で、形状が変化していることを特徴とするミラーユニット。

**【請求項 8】**

前記基板変形手段によって前記基板の形状を変化させたときに発生する波面収差は、前記多層膜を部分的に除去して補正されていることを特徴とする請求項1から7のいずれか1項のミラーユニット。

**【請求項 9】**

請求項1から8のいずれか1項のミラーユニットを含む光学系を用いて、光源からの光を被露光体に導くことにより、前記被露光体を露光することを特徴とする露光装置。

**【請求項 10】**

光源からの光でレチクルを照明する照明光学系と、請求項1から8のいずれか1項のミラーユニットを含み、前記レチクルからの光を被露光体に導く投影光学系とを有することを特徴とする露光装置。

**【請求項 11】**

請求項9又は10に記載の露光装置を用いて前記被露光体を露光する工程と、前記露光された被露光体を現像する工程とを有することを特徴とするデバイスの製造方法。

**【請求項 12】**

基板の一面に多層膜を施して、反射面とする多層膜形成工程と、該基板の形状を変化させる基板変形工程と、該反射面の多層膜を部分的に除去する多層膜削除工程を含んでいることを特徴とするミラーユニットの製造方法。

**【請求項 13】**

10

20

30

40

50

前記基板変形工程による前記基板の変形の後、前記反射面の波面収差の計測を行い、該計測された結果に基づいて前記多層膜の一部分を削除する工程を含むことを特徴とする請求項12に記載のミラーユニットの製造方法。

**【請求項14】**

前記基板に対する変形を複数のアクチュエータを用いて行う工程を含むことを特徴とする請求項12又は13のミラーユニットの製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、ミラーユニット及びそれを有する露光装置に関し、例えば、X線露光装置、10 EUV露光装置、X線顕微鏡等に用いられる反射鏡に好適なものである。

**【背景技術】**

**【0002】**

従来より、半導体メモリや論理回路などの微細な回路パターンを含む半導体素子を製造するための焼き付け(リソグラフィー)方法(露光方法)として、焼付け用の光に紫外線を用いた縮小投影露光方法が行われている(特許文献1)。

**【0003】**

縮小投影露光で転写できる最小パターンの線幅寸法は、転写に用いる光の波長に比例し、投影光学系の開口数に反比例する。このため微細な回路パターンを転写するためには用いる光は、波長の短い光が用いられている。例えば、水銀ランプから放射されるi線(波長365nm)、KrFエキシマレーザーから放射される波長248nmの光、ArFエキシマレーザーから放射される波長193nmの光が用いられている。このように投影露光に用いる紫外光の波長はより短くなっている。

**【0004】**

近来、半導体素子の回路パターンは急速に微細化しており、紫外光を用いたリソグラフィーでは限界が生じている。特に線幅が0.1μmを下回るような非常に微細な回路パターンを効率よく焼き付けるために、紫外線よりも更に波長が短い波長10~15nm程度の極端紫外光(EUV光)を用いた縮小投影露光装置が提案されている(特許文献2)。

**【0005】**

EUV光領域では物質による吸収が非常に大きくなるので、可視光や紫外光で用いられるような光の屈折を利用したレンズ光学系は実用的ではない。この為、EUV光を用いた露光装置(投影露光装置)では反射光学系が用いられている。この場合、レチクルも反射鏡の上に吸収体によって転写すべきパターンを形成した反射型レチクルが用いられる。

**【0006】**

露光光としてEUV光を用いた露光装置を構成する反射型光学素子としては、光学定数の異なる2種類の物質を交互に積層した多層膜反射鏡が多く用いられる。例えば精密な形状に研磨されたガラス基板の表面にモリブデンとケイ素を交互に積層して多層膜反射鏡を形成している。その層の厚さは、例えばモリブデン層の厚さは2nm、ケイ素層の厚さは5nm程度である。ここでは2種類の物質の層の厚さを加えたものを膜周期とよぶ。上記例では膜周期はおよそ7nmである。

**【0007】**

このような多層膜反射鏡にEUV光が入射すると、特定の波長のEUV光が反射される。

**【0008】**

入射角をθ、EUV光の波長をλ、膜周期をdとすると近似的には、

$$2 \times d \times \cos \theta =$$

の関係を満足するような波長λを中心とした狭いバンド幅のEUV光だけが効率よく反射される。このときのバンド幅は一般に0.6~1nm程度である。

**【0009】**

10

20

30

40

50

反射される E U V 光の反射率は最大で 70 % 程度であり、反射されなかつた光は多層膜中あるいは基板中で吸収され、そのエネルギーの大部分が熱になる。

#### 【 0 0 1 0 】

多層膜反射鏡は光の損失が大きいので、露光装置に用いる多層膜反射鏡の枚数は最小限に抑えることが必要である。少ない枚数の多層膜反射鏡で広い露光領域を実現するには、光軸から一定の距離だけ離れた細い円弧状の領域（リングフィールド）だけを用いて、レチクルとウエハを同時に走査して広い面積を等倍で転写する方法（スキャン露光）が行われている。

#### 【 0 0 1 1 】

このような露光装置においては、高精度に加工された多層膜反射鏡の製造が必須の技術となっている。多層膜反射鏡は一般には基板となる部材を加工・研磨し所定の曲率を持つようにした後、表面に多層膜を成膜する方法が取られる。しかし、後に示すように、E U V 露光装置に搭載される投影光学系の多層膜反射鏡の反射面の面形状は非常に高い精度であることが要求される。そのため、一旦反射面に多層膜を成膜した後に更に精度を向上させる方法が従来から提案してきた（特許文献 3）。

#### 【 0 0 1 2 】

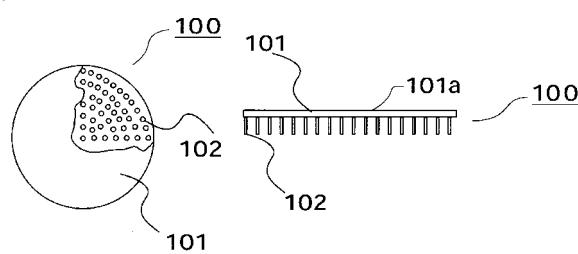

次に特許文献 3 に開示されているアクチュエータを使って基板を変形させる例を図 9 を用いて説明する。図 9において、100 は反射鏡であり、変形可能な基板 101 の表面が反射面 101a となっており、基板 101 の裏面にアクチュエータとして複数個のピエゾ素子 102 が同心円状に配設されている。このピエゾ素子 102 は、中心から同じ半径の円周上にあるものには同じ電圧が印加されるように設定されており、各円周ごとに異なる電圧を印加することによって任意の回転面が形成される。又、各円周上のピエゾ素子 102 に印加する電圧は、要求される反射面 101a の曲率半径を満たすように中心からの距離に対する変化量と、ピエゾ素子 102 の電圧に対する変位量から決定される。決められた電圧がパソコン等の図示されていない制御手段によって制御されながらピエゾ素子 102 に印加され、反射鏡（球面鏡）100 が形成される。形成された球面鏡は、オプティカルスペロメータを用いて曲率半径が、干渉計を用いて形状が測定され、設計値からのズレ分（形状誤差）をピエゾ素子 102 への印加電圧を微調整して補正される。

#### 【 0 0 1 3 】

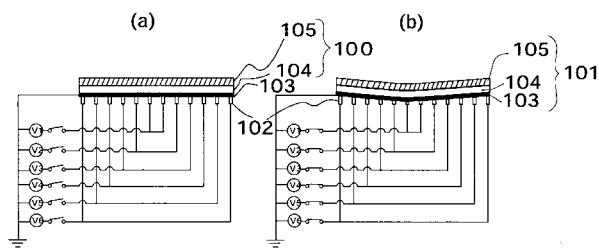

図 10 は図 9 における変形可能な基板 101 状に多層膜 105 を施し、多層膜反射鏡 100 とした場合である。図 9 で説明した方法で多層膜反射鏡 100 を製作している。図 10において、シリコンウエハー 104 の上には多層膜 105 が形成され、裏面にはピエゾ素子 102 の電極となるように導電性物質 103 が付けられている。

#### 【 0 0 1 4 】

図 10 (a) に示すように上記多層膜反射鏡 100 の裏面にピエゾ素子 102 が取り付けられていて決められた電圧が制御手段によって印加されることで図 10 (b) のように反射面の形状が補正されている。

#### 【 0 0 1 5 】

又、個々のミラーに存在する多層膜ミラーの基板面形状の補正方法として、アクチュエータを用いる方法の他に、Coating Milling の手法が提案されている（非特許文献 1）。

【特許文献 1】特開平 05 - 063051 号公報

【特許文献 2】特開 2003 - 224052 号公報

【特許文献 3】特許第 301084 号

【非特許文献 1】「SUB-nm Figure Error Correction of a Multilayer Mirror by Its Surface Milling」（Masaki Yamamoto, Nuclear Instruments and Methods in Physics Research A, 467-468 (2001)）

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【 0 0 1 6 】

露光波長として E U V 光を用いた E U V 露光装置に搭載される投影光学系には、それを

10

20

30

40

50

構成する多層膜反射鏡の反射面の面形状は非常に高い精度であることが要求される。例えば投影光学系を構成する反射鏡の枚数を  $n$ 、EUV光の波長を  $\lambda$  とすると許容される形状誤差 (rms値) はマレシャルの式

【0017】

【数1】

$$\sigma = \lambda / (28 \times \sqrt{n})$$

【0018】

で与えられる。例えば、投影光学系が4枚の反射鏡で構成され、波長 ( $\lambda$ ) が 13 nm の露光装置の場合、 $\sigma = 0.23 \text{ nm}$  となる。又、分解能 30 nm の線幅のパターン転写を行なう場合に、投影光学系全系に許容される波面収差量は 0.4 nm 程度である。

【0019】

しかし、研磨によって反射面の形状誤差を上記許容値内に收めることは製作上非常に困難である。

【0020】

又、自重や取り付け部材に対して装着された際に面形状に変形が生じる場合がある。

【0021】

そのため、自重や取り付けによって生じる変形や、研磨で到達できる限界以上の微小な波面収差を同時に補正できる多層膜反射鏡が要望されている。

【0022】

しかし、例えばアクチュエータを使って基板を変形させる方法では、周期の小さい変形は補正することが難しい。一般に反射鏡の剛性を保つために基板も一定の剛性が必要になるため周期の小さな変形を与えることが困難である。基板の剛性を落とせば周期の小さな変形を与えることも可能だが、反面、研磨や装置に取り付ける際の、あるいは経時的な変形が大きくなり製作が難しい。

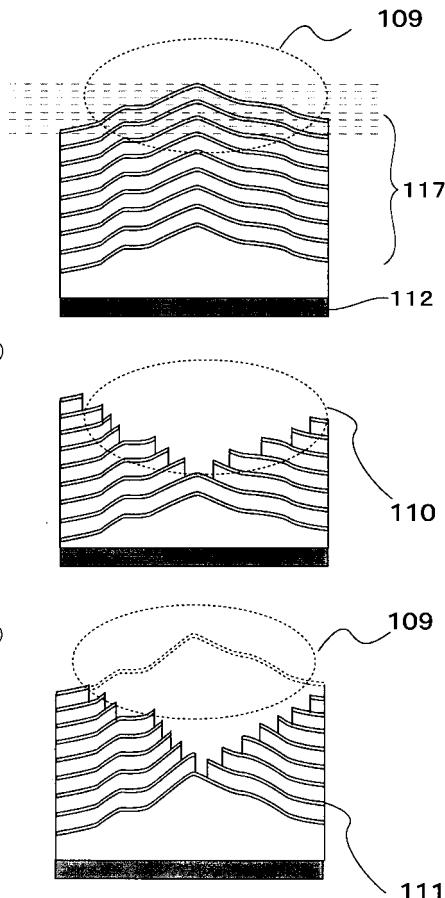

【0023】

又、coating milling手段のみを用いた基板の変形の補正是一層対で補正できる位相差に比べて大きな量の補正を行う場合に非常に不利である。例えば図13(a)~(c)に示すように、基板112上に多層膜117を施した多層膜反射鏡の表面上の領域109に大きな変形があった場合に顕著である。図13(b)の領域110にあるように多くの層に対してcoating millingを行う必要がある。この為、例えば一層対削るごとに、0.2 nmの補正が出来、10 nm分の位相差があった場合、それを補正しようとすると50層対分を削る必要が発生し、coating millingの工程が複雑になる。又、十分な反射率を確保するためにはそれだけ多くの多層膜を予め形成しておく必要があり、工程的にもコスト的にも実施が困難である。例えば、50層対分を削る可能性がある場合には、必要な反射率が得られる多層膜117の総数に予め50層分追加して成膜する必要がある。

【0024】

又、図13(c)のようにさらに基板112の変形が大きくなる部分109があると、必要な反射率が得られる限度の層対(111)を超えてcoating millingを行う必要が発生し、高反射率という多層膜使用の本来の目的を満足できない場合ある。

【0025】

本発明は、基板を変形させる手段とcoating milling手段(多層膜を部分的に除去する方法)を適切に組み合わせて使うことで、波面収差が小さく、高反射率で、工程的にも簡単で、高品位のミラーユニット及びそれを有する露光装置の提供を目的とする。

【課題を解決するための手段】

【0026】

本発明のミラーユニットは、

第1面に多層膜が施されている基板と、該基板の形状を変形させる基板変形手段とを有するミラーユニットであって、前記多層膜の最表層を含む1以上の層の膜が部分的に欠

10

20

30

40

50

けていることを特徴としている。

【0027】

基板の第一面が多層膜が施された反射面であり、該多層膜は最表層を含む最大20層までが部分的に膜除去手段で削除されており、該基板は、該基板の一面と反対側の面に設けた基板変形手段で、形状が変化されていることを特徴としている。

【0028】

又、本発明のミラーユニットの製造方法は、

基板の一面に多層膜を施して、反射面とする多層膜形成工程と、該基板の形状を変化させる基板変形工程と、該反射面の多層膜を部分的に除去する多層膜削除工程を含んでいることを特徴としている。

10

【0029】

又、本発明の露光装置は、前述したミラーユニットを用いてレチクルからの光を被露光体に導くことを特徴としている。

【発明の効果】

【0030】

本発明によれば、基板を変形させる手段とcoating milling手段（多層膜を部分的に除去する方法）を適切に組み合わせて使うことで、波面収差が小さく、高反射率で、工程的にも簡単で、高品位のミラーユニットが得られる。

【発明を実施するための最良の形態】

【0031】

まず、各実施例に関係する変形モードについて説明する。

20

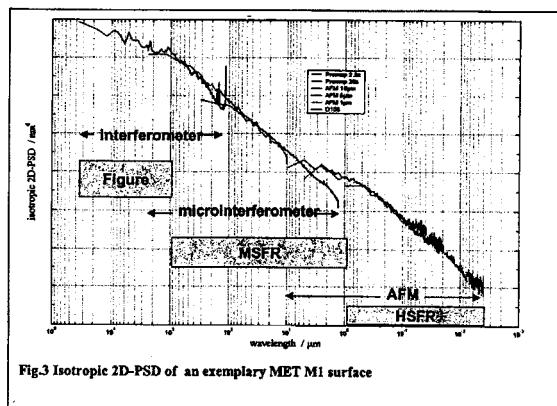

【0032】

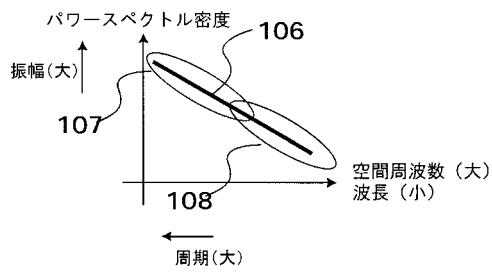

まず、多層膜ミラーの表面形状の変位における周期（波長）と振幅（パワースペクトル密度）の関係は図11の直線106に示すように、周期の大きい（波長が長い）ものは振幅も大きく、周期の小さいものは振幅も小さいという関係にあることが知られている。

【0033】

例えば、「PROCEEDING OF SPIE Vol.4146 , Mirror substrates fr EUV-lithography : progress is metrology and optical fabrication technology , Carl Zeiss(Germany) Fig. 3」によれば、図22に示すように振幅の大きさと波長の大きさには、波長 小（短くなる）、振幅 小（小さくなる）という相関があることが示されている。

30

【0034】

図22は、横軸に波長を、縦軸に二次元のパワースペクトル密度（power spectral density）をプロットしており、ある周期の変形がどの程度含まれているかを示している。横軸を右方向が波長が小さくなる方向であるので、波長が小さくなると含まれる振幅の大きさも小さくなることが示されている。

【0035】

従って図11に示すように、周期も振幅も大きいグループ（107）と周期も振幅も小さいグループ（108）とに分けることができる。ここで、周期も振幅も大きいグループ107を“低次の変形”、周期も振幅も小さいグループ108を“高次の変形”と定義する。

40

【0036】

次に、以下の各実施例において適用しているcoating milling（膜除去手段）について説明する。

【0037】

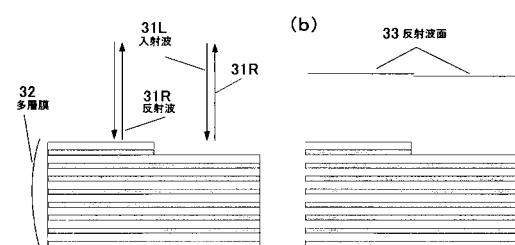

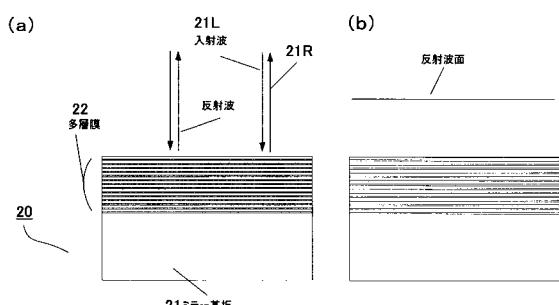

図2(a)に示すようにミラー基板21に全く均一に多層膜22が成膜されている多層膜ミラー20に位相の揃った平行光21Lを入射すると、図2(b)に示すように完全に位相の揃った反射光21Rが得られる。しかし、図3(a)に示すように一層対膜数が異なる部分で反射光の波面の比較をする場合、図3(b)に示すように反射光31Rの反射波面33に位相の違いが生じる。

【0038】

50

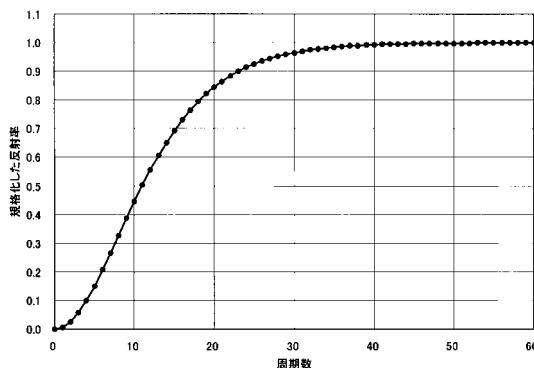

多層膜ミラーの反射率は膜周期数に依存する。図4に多層膜の周期数と最大値で規格化した反射率Rを示す。40層対程度までは膜周期数の増加と共に反射率Rは大きく増加する。しかし40層対以上では反射率Rはほぼ飽和する。反射率Rが飽和した後に十分な膜周期数が積層された状態、例えば60層対程度に積層された状態であれば膜周期数の違いにより生じる現象は波面の違いだけである。

#### 【0039】

以下、材料にMoSiを用いたMoSi多層膜ミラーに波長13.5nmのEUV光を入射角10°で入射した場合を例にとり説明する。

#### 【0040】

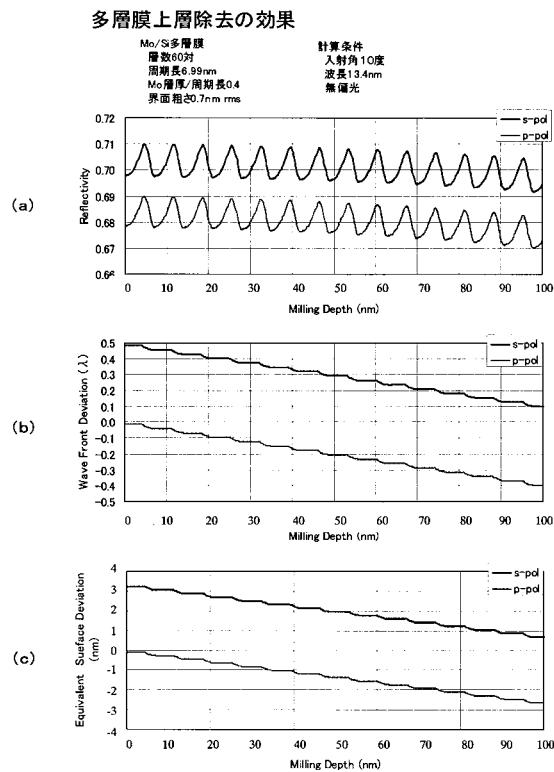

ここで最上層の多層膜を原点とし、最上層から多層膜を削る場合について考える。ここでは、多層膜を削る量をmilling depthと呼ぶ。MoSi多層膜ミラーに波長13.5nmのEUV光を入射角10°で入射した場合についてmilling depthと反射率のグラフを図5(a)、milling depthと波面のずれ量のグラフを図5(b)に示す。通常、Moの酸化の影響を考慮し、Si層を最上層にするため、本計算においてもSi層を最上層として計算を行なった。

#### 【0041】

多層膜を1層対( $=6.99\text{ nm}$ )取り除くことで、反射光の波面が0.025波長程度動くことが分かる。又波面のずれ量を空間的な反射位置のずれに換算したグラフを図5(c)に示す。ここで入射光の波長、波面のずれ量Wと空間的な反射位置のずれLの関係は次式、 $\times W = 2L$ により与えられる。

#### 【0042】

この例であれば多層膜を1層対( $=6.99\text{ nm}$ )削ることは反射位置が0.2nm程度動くことに等しい。図5(a)から分かるようにcoating millingを行なうと屈折率の関係からSi層に比べ、Mo層で大きく反射率および波面が変化する。上述したように、60層対程度積層していれば反射率は膜周期に関して飽和しているので、ちょうど1周期膜厚を取り除くと反射率は変化せずに波面だけが変化する。

#### 【0043】

図2～図5を用いて示した以上の関係を用いれば、多層膜ミラー(ミラーコニット)の基板面形状の0.2nm程度の補正を、多層膜を一層対( $=6.99\text{ nm}$ )と大きく削ることで容易に達成することができる。従来よりこの手法をcoating millingと呼んでいる。

#### 【0044】

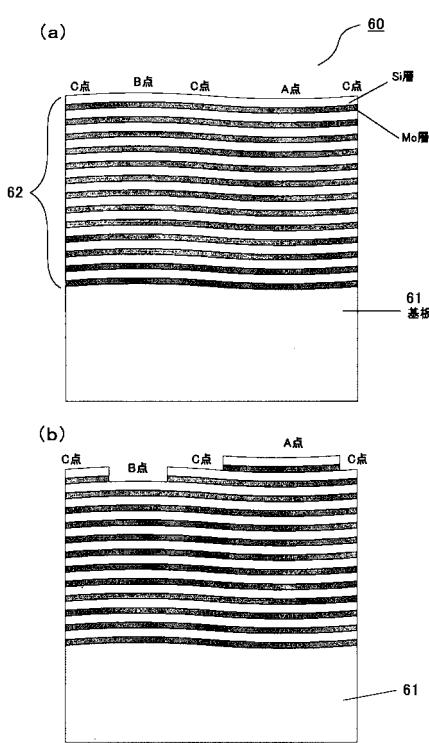

例えば図6(a)のように面が歪んだミラー基板61に均一な多層膜62が成膜された多層膜ミラー60に光が入射する場合を考える。coating millingは位相を遅らせる手法であるので、最も位相の遅れているミラー60の点Aを原点としてcoating millingを行なう。上述したようにSi層で波面の変化はほとんどなく、Mo層で大きく波面が変化するがMo層は酸化に弱い。このため特殊なコーティングをしない場合は、Mo層の中間でcoating millingを終えて連続的に波面を調整するのは困難である。よって、図6(b)のようにMoとSiをあわせた層を1層対ずつ取り除き不連続的に波面を調整する。Si層に関しては波面に大きな影響を及ぼさないためSi層の中間でcoating millingを終えたとしても大きな影響はない。上述したように波長13.5nmのEUV光を入射角10°で入射した場合、膜を1層対(厚さ6.99nm)ずつ取り除くことで0.2nm刻みで、空間的な反射位置すなわちミラー基板61の形状誤差を補正することができる。

#### 【0045】

図6(a)の点Bにおけるミラー基板61の形状が点Aから見て0.4nmの形状誤差を持ち、C点が0.2nmの形状誤差を持つとする。図6(b)の点Bの多層膜を2層対取り除き、さらに点Cの多層膜を1層対取り除くことでミラー基板の形状誤差に起因する波面収差が補正できる。

#### 【0046】

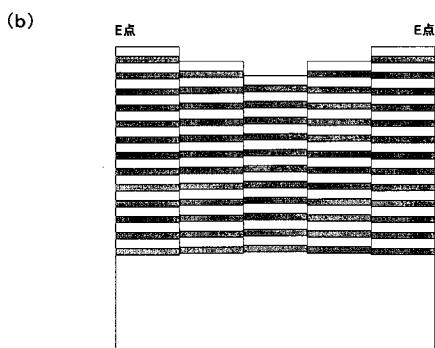

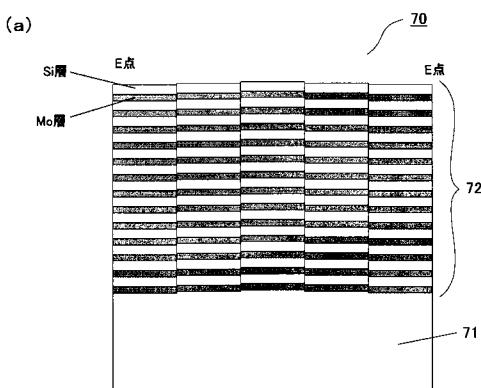

又同様に、例えば図7(a)のように端部に比べ中心部が盛り上がっているミラー基板

10

20

30

40

50

71に均一な多層膜72が成膜された多層膜ミラーに光が入射する場合を考える。ここでは反射ミラーの点Eの位相が相対的に最も遅れているので、点Eを原点としてcoating millingを行なう。反射ミラー70の端部と中心部との形状誤差が0.4nm程度でその間が連続的に変化している場合、中心部の多層膜を2層対取り除く。さらに、その両脇を1層対取り除くことで基板の形状誤差に起因する波面収差を補正している。

#### 【0047】

次に本発明のミラーユニット(多層膜反射鏡)及びそれを有する光学機器について説明する。

#### 【実施例1】

#### 【0048】

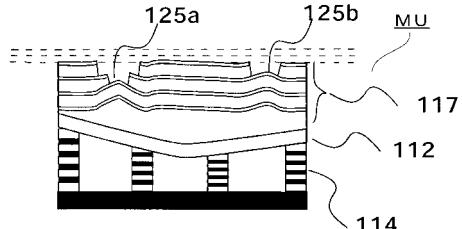

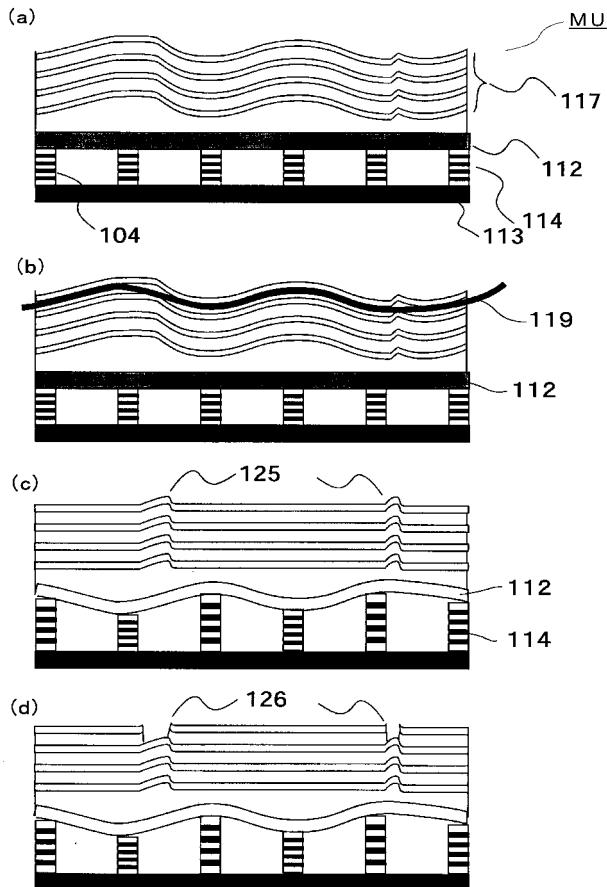

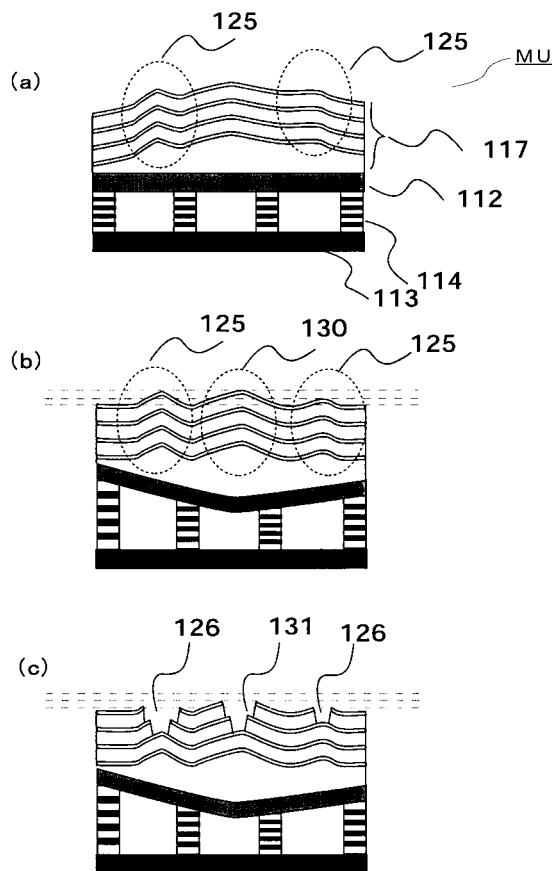

図1は、ミラーユニットMUの実施例1の要部断面図、図14、図15は、本発明の実施例1のミラーユニット(多層膜反射鏡)MUの製造過程における要部断面図である。

#### 【0049】

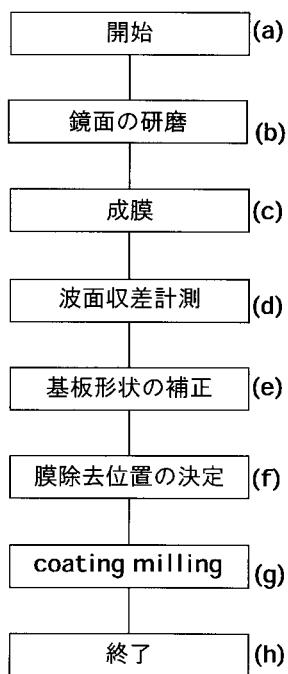

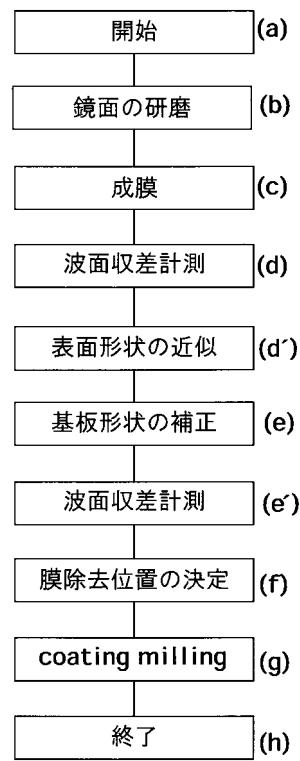

図16は、本発明のミラーユニットの製造方法のフローチャートである。

#### 【0050】

図15は、図16のフローチャートにおけるあるステップのときのミラーユニットMUの要部断面を示している。

#### 【0051】

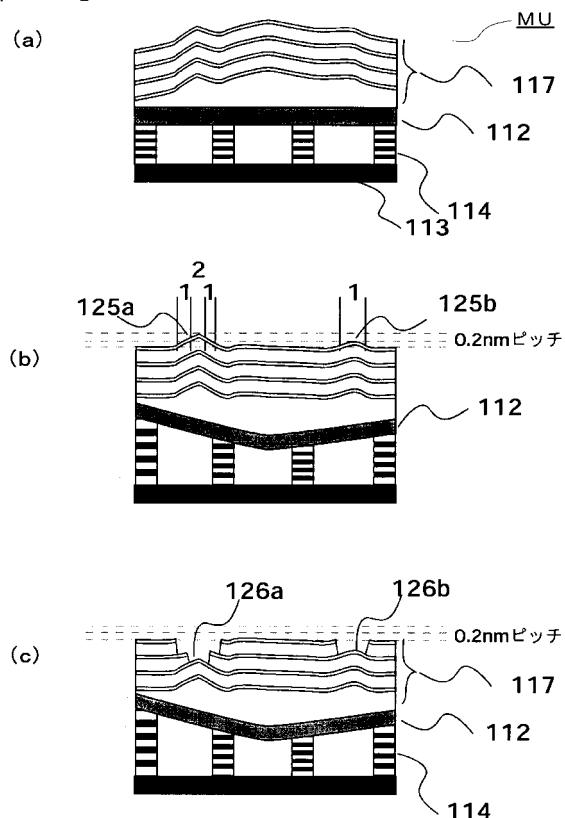

図1と図15(c)のミラーユニットMUは、基板112の変形をアクチュエータ114とcoating milling(膜除去手段)で補正し、それが完了した図を示している。

#### 【0052】

本実施例では、基板112の一面が多層膜117が施された反射面であり、該一面に対向する面には、基板112の形状を部分的に変形させることができる基板変形手段114が設けられている。そして多層膜117を部分的に最表層(反射鏡に施される多層膜の最も表面側の膜の層)から数えて1以上の膜までを削除している。

#### 【0053】

図1、図14、図15において、112は基板、117は基板112上に成膜された多層膜、113は高剛性の部材であり、基板112を保持している。114は基板112を変形させるアクチュエータ(基板変形手段)である。116はアクチュエータの動作をコントロールするコントローラである。

#### 【0054】

部材(113)とアクチュエータ(114)は成膜以前に取り付けてもよいし、成膜後に取り付けてもよい。基板(112)は高剛性の部材(113)からバネ(115)で反射面の反対側から力を加えることで固定されている。

#### 【0055】

図14(a)は基板112の鏡面の研磨が終了して高剛性の部材113に取り付けられた図で、フローチャート図16のステップ(b)に相当する。

#### 【0056】

図14(b)は基板112上に多層膜117の成膜が終了した段階の図で、図16のステップ(c)に相当する。

#### 【0057】

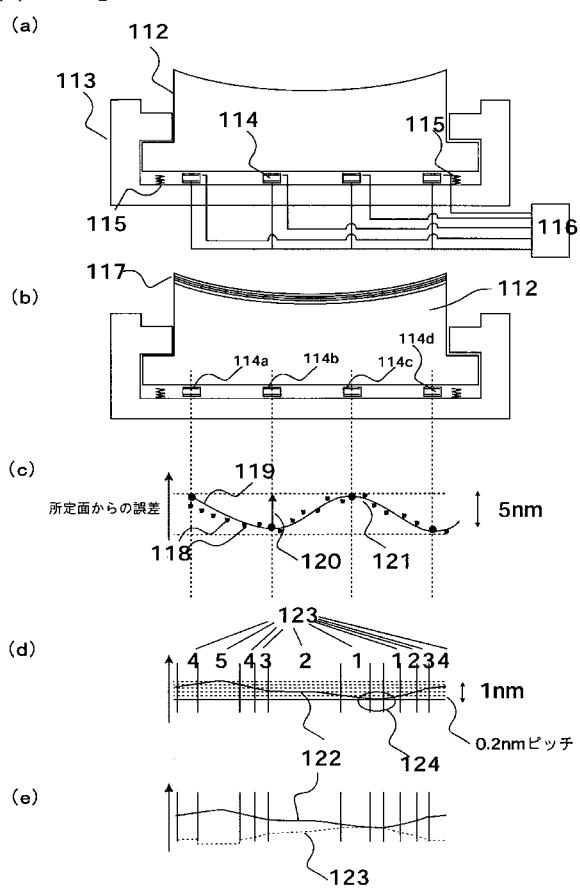

図14(c)は所定面からの成膜の厚さの誤差を求めた段階の図で、図16ステップ(d)に相当する。

#### 【0058】

図14(d)はアクチュエータ114による基板112の形状の補正のみを行い、膜除去位置が決定された段階の図で、図16のステップ(e)、図16のステップ(f)に相当する。

#### 【0059】

図14(e)は膜除去の方法によって多層膜117の一部を除去することにより、波面が補正された段階の図で、図16のステップ(g)に相当する。

10

20

30

40

50

## 【0060】

図15(a)は多層膜117の成膜と波面収差計測が終了した段階の図であり、図16のステップ(c)、(d)に相当する。

## 【0061】

図15(b)は基板変形手段によって基板112の形状が補正された段階の図であり、図16のステップ(e)に相当する。図15(b)において、一部分125a、126bが表層及び表層近傍の膜除去を行うべき部分である。

## 【0062】

図15(c)は膜除去手段(coating milling)によって多層膜117の一部分126a、126b表層及び表層近傍の膜を削除し、波面収差が補正された段階の図である。

10

## 【0063】

基板112には、ZERODURE(登録商標)等の超低膨張材が好適である。部材113には剛性の高い部材としてセラミック製が好適である。アクチュエータ(114)としては、例えばピエゾ素子が好適である。ピエゾ素子を用いると微小な変位を制御可能であるし、スタッカ状に積み上げることで変位量を大きくすることも可能である。その他にも、ピエゾ素子とヒンジバネを組み合わせて微動機構を形成したりしてもよい。

## 【0064】

基板112の鏡面に関しては、部材113への取り付け時の変形を考慮し、部材(113)を取り付け、ピエゾ素子114には電圧を加えない状態で表面を研磨し、設計された面からの凹凸差である誤差が3nm程度となるまで研磨する。誤差が3nm程度までの精度の研磨であれば比較的容易に到達することが可能である。

20

## 【0065】

ピエゾ素子114の個数は、基板112を変形させる次数等で変化し得るが、本実施例ではミラーの大きさと同程度の周期を持つ次数の変形を補正するために、直径方向の断面位置において4つのピエゾ素子を配置してある。実際には曲面全体に配置されているが、図では省略している。

## 【0066】

アクチュエータ104は基板101の変形モードに応じて配置している。例えば、反射鏡全面で一周期長のモードの変位までを基板101の変形で補正しようとなれば、最低4個のアクチュエータで良いが、それより高次の変形モードを補正しようとするならば、その分多くのアクチュエータを配置するのが良い。

30

## 【0067】

多層膜(102)は、MoSi多層膜(一層対6.99nm)を60層程度積層している。これは十分な反射率が得られる40層に追加して20層をcoating millingのために予め成膜するためである。即ち削除する膜層は1以上20以下としている。

40

## 【0068】

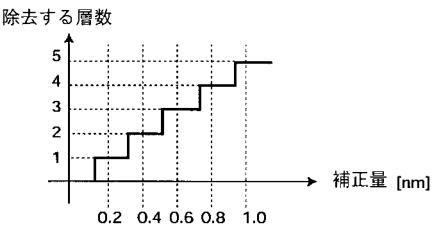

多層膜117の表面の一部を削除するときの補正量(nm)と除去する層数の関係は図12に示すようになっている。この図12は多層膜としてMoSi多層膜(一層対6.99nm)を想定してるので0.2nm毎に1層対を除去するグラフになっているが、この値は具体的な多層膜の種類によって異なる。

## 【0069】

本実施例では、多層膜反射鏡を基板112の一面に多層膜117を施し、反射面とする多層膜形成工程と、基板112の形状を変化させる基板変形工程と、反射鏡表面の多層膜117を部分的に除去する多層膜削除工程を用いて製造している。

## 【0070】

次に低次の変形と高次の変形による具体的な補正の手順等を説明する。

## 【0071】

図14(c)は波面収差計測によって設計面(所定面)からの誤差が計測され、各点における誤差(点118)が得られた状態である。これを基板変形手段で補正が可能な曲線で近似させ、近似曲線(119)を得る。

50

**【 0 0 7 2 】**

次に、近似曲線(119)において最も凸である(突出している)位置(121)を求める。ピエゾ素子は押す方向にのみ力を伝達することができるため、最も凸の位置を基準にそれより凹の部分を押す必要がある。例えばピエゾ素子114bでは、長さ120の大きさだけ補正を行う。ピエゾ素子による補正で波面の誤差は1nm程度にまで小さくなっている。この段階ステップ(f)で基板112を変形させて“低次の変形”を補正している。

**【 0 0 7 3 】**

次に、ステップ(h)、(i)でピエゾ素子による変形でも補正できなかった図14(d)に示す変形量(122)を膜除去手段(coating milling)で補正する。今度は曲線(122)中最も凹となる位置(124)を求め(ステップ(h))、そこから図12のグラフに従って除去する層数を決定し、所定の領域内において膜除去手段により決定された層数の膜を除去する(ステップ(i))。

10

**【 0 0 7 4 】**

図14では除去する層数が大きいので、より簡略化した図15において説明する。

**【 0 0 7 5 】**

図15(b)において、部分125aは、0.2nmピッチで2層対分の補正が必要であり、部分125bは1層対分の補正が必要であるので、図15(c)にあるように、各々の部分について膜除去手段によって膜を除去する。この段階で“高次の変形”が補正される。

20

**【 0 0 7 6 】**

以上のようにすることで、多層膜反射鏡で反射させる光に対して波面収差を補正している。

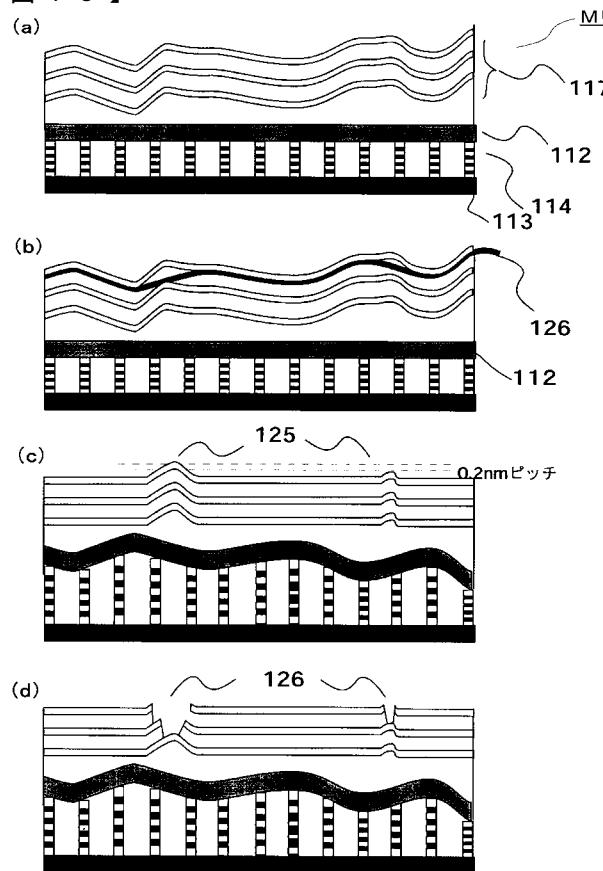

**【 実施例2 】****【 0 0 7 7 】**

図17は、実施例2のミラーユニットMUの要部断面図である。図17(a)は波面収差計測において、多層膜17の変形量が計測された段階の図である。図17(b)は変形量を低次の周期的な関数によって近似させて、近似曲線119を求めた図である。図17(c)は図17(b)で求めた近似曲線119の関数に従って基板112の変形を行った後の図である。この図17(c)では、鏡面の大きさの周期より大きい変形が基板変形手段114によって補正されている。図17(d)は、基板変形手段114で補正しきれなかった残りの変形を膜除去手段によって補正した後の図である。この段階で、基板変形手段114では補正できない大きさの周期を持つ変形が良好に補正されている。

30

**【 0 0 7 8 】**

本実施例によれば少なくとも反射鏡の大きさと等しい又は略等しい周期長の位相の補正是基板変形手段で行い、それより周期長の短い変形は膜除去手段によって補正し、これによって良好に波面収差を補正したミラーユニットを得ている。

**【 実施例3 】****【 0 0 7 9 】**

図18は、実施例3のミラーユニットMUの要部断面図である。本実施例は、反射鏡の径の方向に13個のピエゾ素子114を配置して図17の実施例2に比べてより波長の小さい、反射鏡の大きさの少なくとも1/2より大きい周期長の位相の補正を基板変形手段で行っている。

40

**【 0 0 8 0 】**

本実施例によれば反射鏡の大きさの少なくとも1/2より大きい周期長の位相の補正是基板変形手段で、それより周期長の短い変形(例えば1/10以下の周期長の変形)は膜除去手段によって補正している。

**【 0 0 8 1 】**

図18(a)は波面収差計測において、多層膜17の変形量が計測された段階の図である。図18(b)は変形量を低次の周期的な関数によって近似させて、近似曲線126を

50

求めた図である。図 18 (c) は図 18 (b) で求めた近似曲線 126 の関数に従って基板 112 の変形を行った後の図である。この図 18 (c) では、鏡面の大きさの周期より大きい変形が基板変形手段 114 によって補正されている。図 18 (d) は、基板変形手段 114 で補正しきれなかった残りの変形を膜除去手段によって補正した後の図である。この段階で、基板変形手段 114 では補正できない大きさの周期を持つ変形が良好に補正されている。

#### 【0082】

本実施例によれば少なくとも反射鏡の大きさと等しい又は略等しい周期長の位相の補正是基板変形手段で行い、それより周期長の短い変形は膜除去手段によって補正し、これによって良好に波面収差を補正した多層膜反射鏡を得ている。

10

#### 【0083】

又、本実施例では、基板変形手段 114 は、前記反射面に波長 の光束を反射面に入射させたとき、反射光束の波面の誤差が /2 以上ある領域に対する反射面上の基板 112 の変形の補正を行い、基板 112 のそれよりも小さい波面の誤差を生ずる領域は、多層膜 117 の部分的な膜層の削除より補正している。

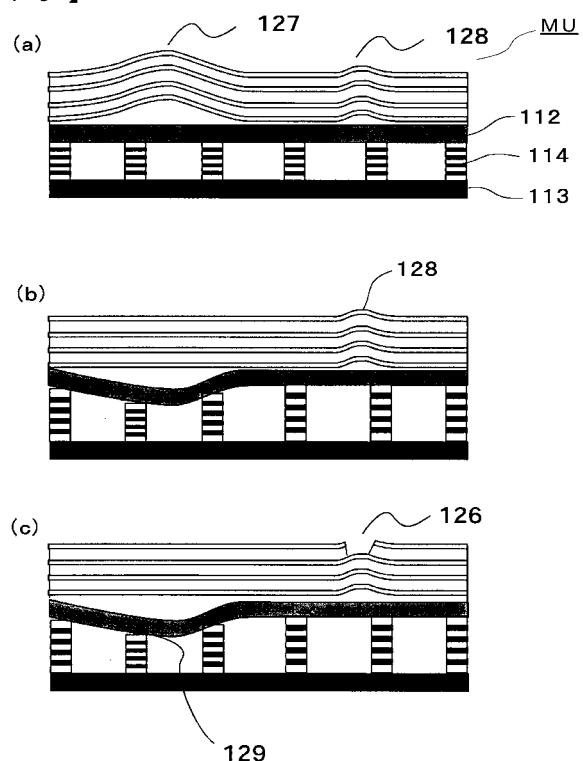

#### 【実施例 4】

#### 【0084】

図 19 は、実施例 4 のミラーユニット MU の要部断面図である。図 19 (a) は波面収差計測によって表面形状が計測された状態である。ここで、部分 127 は変形量が大きい部分、部分 128 は変形量が小さい部分である。図 19 (b) は大きな変形の部分 127 を基板変形手段 114 によって補正した後の図である。図 19 (c) は残りの部分 128 の変形を膜除去手段によって補正した後の図である。

20

#### 【0085】

このような本実施例によれば変形量の大きな変形は基板変形手段で、変形量の小さな変形は膜除去手段によって補正し、これによって良好に波面収差を補正した多層膜反射鏡を得ている。

#### 【0086】

以上のように本実施例では、前記基板変形工程による前記基板の変形の後、波面収差計測を行い、該計測された結果に基づいて前記多層膜の一部分を削除する工程を利用してミラーユニット（多層膜反射鏡）を製造している。

30

#### 【実施例 5】

#### 【0087】

図 20 は、実施例 5 のミラーユニット MU の要部断面図である。図 20 (a) は多層膜 117 の表面形状を基板変形手段による補正を行った段階の図であるが、図 20 (b) に示す部分 130 にあるように、基板 112 の変形によって新たに変形が発生する場合がある。図 20 (c) における部分 131 は変形 (130) が膜除去手段 114 によって補正された部分を示している。この方法によれば基板変形手段による変形のために、もし、新たな変形が起きてもそれを補正することが出来る。

#### 【0088】

基板変形手段で新たに発生する変形は、計算によって求めてもよいし、基板変形手段による変形の後に再度波面収差計測を行うことで求めてもよい。

40

#### 【0089】

以上のように本実施例では、基板変形手段によって基板 112 に生じた形状変化に伴い発生する波面収差も含めて多層膜 117 を部分的に除去して波面収差を補正している。

#### 【0090】

図 21 は、本実施例の以上の手順を示したフローチャートである。図 16 のフローチャートに比べて、ステップ (d) の波面収差の計測の後にステップ (d') の表面形状の近似が入り、ステップ (e) の、ピエゾ素子での補正とステップ (f) の膜除去手段の間にもう一度ステップ (e') の波面収差計測が含まれていることが異なっており、その他は同じである。

50

## 【0091】

以上の各実施例によれば、波面収差が小さくかつ、高反射率で、工程的にも複雑にならないミラーユニットを作成することができる。

## 【実施例6】

## 【0092】

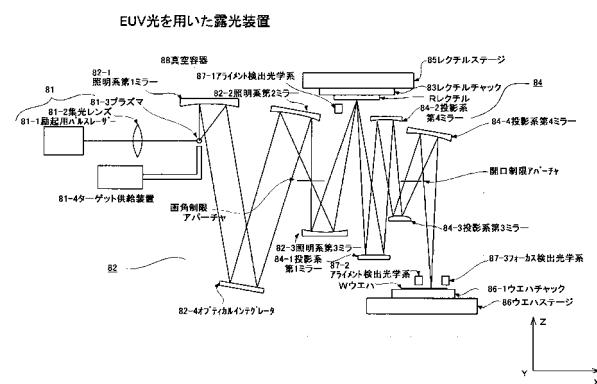

図8は、本発明のミラーユニット（多層膜反射鏡）を用いた露光装置の実施例6の要部概略図である。図8は、EUV光を用いた投影露光装置を示している。

## 【0093】

図8に示すEUV光を用いた縮小投影露光装置は、パルスレーザ81-1、集光レンズ81-2、プリズム81-3、ターゲット供給装置81-4を含むEUV光源81と、第1ミラー82-1、オプティカルインテグレータ82-4、第2ミラー82-2、第3ミラー82-3を含む照明光学系82と、レチクルチャック83に保持された反射型レチクルRと、投影系第1ミラー84-1～投影系第4ミラー84-4を含む投影光学系84、レチクルステージ85、ウエハチャック86-1を保持するウエハステージ86、アライメント検出光学系87-1、87-2、フォーカス検出光学系87-3を含むアライメント光学系87、そして前述の各部材を真空中で保持する真空系88などの部材で構成されている。

## 【0094】

EUV光源は例えばレーザープラズマ光源81-1が用いられる。これは真空容器中のターゲット材81-3に高強度のパルスレーザー光を集光レンズ81-2を介して照射し、高温のプラズマを発生させ、これから放射されるたとえば波長13nm程度のEUV光を利用するものである。ターゲット材81-3としては、金属膜、ガスジェット、液滴などが用いられる。放射されるEUV光の平均強度を高くするためにはパルスレーザーの繰り返し周波数は高い方が良く、通常数kHzの繰り返しで運転される。

## 【0095】

照明光学系は、複数の集光ミラー82-1～82-3とオプティカルインテグレータ82-4等から構成される。集光ミラーはレーザープラズマからほぼ等方的に放射されるEUV光を集め役割を果たす。オプティカルインテグレータ82-4はレクチル（マスク）Rを均一に所定の開口数で照明する役割を持っている。またレチクルRの照明領域を円弧状に限定するためのアーチャ（画角制限アーチャ）が設けられる。

## 【0096】

投影光学系は複数の反射ミラーを用いている。ミラー枚数は4枚から6枚程度である。ミラーの反射面の形状は凸面または凹面の球面または非球面である。開口数NAは0.1～0.2程度である。

## 【0097】

レチクルステージ85とウエハステージ86は縮小倍率に比例した速度比で同期して走査する機構をもつ。ここでレチクルR又はウエハW面内で走査方向をX、それに垂直な方向をY、レチクルR又はウエハW面に垂直な方向をZとする。

## 【0098】

レチクルRは、レチクルステージ83上に保持される。レチクルステージ83はX方向に高速移動する機構をもつ。また、X方向、Y方向、Z方向、および各軸の回りの回転方向に微動機構をもち、レチクル位置決めができるようになっている。レチクルステージ85の位置と姿勢はレーザ干渉計によって計測され、その結果に基づいて、位置と姿勢が制御される。

## 【0099】

ウエハWはウエハチャック86-1によってウエハステージ86に保持される。ウエハステージ86はレチクルステージ85と同様にX方向に高速移動する機構をもつ。また、X方向、Y方向、Z方向、および各軸の回りの回転方向に微動機構をもち、ウエハ位置決めができるようになっている。ウエハステージ86の位置と姿勢はレーザ干渉計によって計測され、その結果に基いて、位置と姿勢が制御される。

10

20

30

40

50

## 【0100】

アライメント検出機構 87-1 ~ 87-3 によってレチクル R の位置と投影光学系 84 の光軸との位置関係、およびウエハ W の位置と投影光学系 84 の光軸との位置関係が計測され、レチクル R の投影像がウエハ W の所定の位置に一致するようにレチクルステージ 85 およびウエハステージ 86 の位置と角度が設定される。

## 【0101】

又、フォーカス位置検出機構 87-3 によってウエハ W 面で Z 方向のフォーカス位置が計測され、ウエハステージ 86 の位置及び角度を制御することによって、露光中は常時ウエハ W 面を投影光学系 84 による結像位置に保つ。

## 【0102】

ウエハ W 上で 1 回のスキャン露光が終わると、ウエハステージ 86 は X、Y 方向にステップ移動して次のショットの走査露光開始位置に移動し、再びレチクルステージ 85 及びウエハステージ 86 が投影光学系 84 の縮小倍率に比例した速度比で X 方向に同期走査する。

## 【0103】

このようにして、レチクル R の縮小投影像がウエハ W 上に結像した状態でそれらを同期走査するという動作が繰り返される（ステップ・アンド・スキャン）。こうして、ウエハ W 全面にレチクル R の転写パターンが転写される。

## 【0104】

本実施例では、図 8 に示す各種の反射ミラーに前述した実施例 1 ~ 5 で示したミラーユニットを用いている。

## 【0105】

これによって良好なる光学性能が得られる露光装置を構成している。

## 【0106】

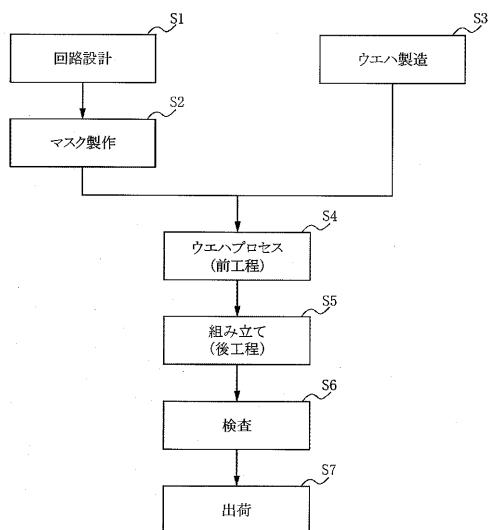

次に、図 23 及び図 24 を参照して、上述の露光装置を利用したデバイス製造方法の実施例を説明する。

## 【0107】

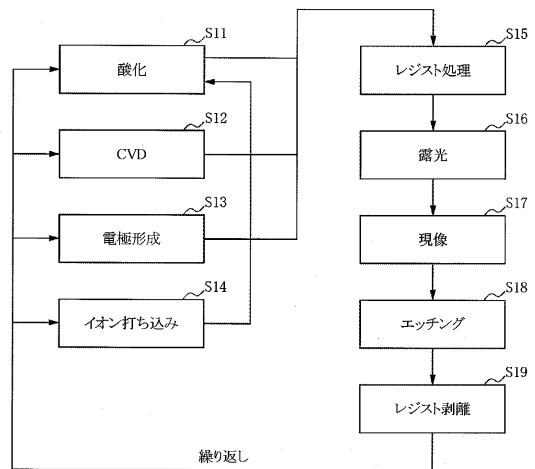

図 23 は、デバイス（ I C や L S I などの半導体チップ、 L C D 、 C C D 等）の製造を説明するためのフローチャートである。本実施形態においては、半導体チップの製造を例に説明する。

## 【0108】

ステップ 1 (回路設計) では、デバイスの回路設計を行う。ステップ 2 (マスク製作) では、設計した回路パターンを形成したマスクを製作する。ステップ 3 (ウェハ製造) では、シリコンなどの材料を用いてウェハを製造する。

## 【0109】

ステップ 4 (ウェハプロセス) は、前工程と呼ばれ、マスクとウェハを用いてリソグラフィー技術によってウェハ上に実際の回路を形成する。ステップ 5 (組み立て) は、後工程と呼ばれ、ステップ 4 によって作成されたウェハを用いて半導体チップ化する工程であり、アッセンブリ工程（ダイシング、ボンディング）、パッケージング工程（チップ封入）等の工程を含む。ステップ 6 (検査) では、ステップ 5 で作成された半導体デバイスの動作確認テスト、耐久性テストなどの検査を行う。

## 【0110】

こうした工程を経て半導体デバイスが完成し、それが出荷（ステップ 7 ）される。

## 【0111】

図 24 は、ステップ 4 のウェハプロセスの詳細なフローチャートである。

## 【0112】

ステップ 11 (酸化) では、ウェハの表面を酸化させる。ステップ 12 ( C V D ) では、ウェハの表面に絶縁膜を形成する。ステップ 13 (電極形成) では、ウェハ上に電極を蒸着などによって形成する。

## 【0113】

10

20

30

40

50

ステップ14(イオン打ち込み)では、ウェハにイオンを打ち込む。ステップ15(レジスト処理)では、ウェハに感光剤を塗布する。ステップ16(露光)では、露光装置によってマスクの回路パターンをウェハに露光する。ステップ17(現像)では、露光したウェハを現像する。ステップ18(エッティング)では、現像したレジスト像以外の部分を削り取る。ステップ19(レジスト剥離)では、エッティングが済んで不要となったレジストを取り除く。

#### 【0114】

これらのステップを繰り返し行うことによってウェハ上に多重に回路パターンが形成される。本実施形態のデバイス製造方法によれば、従来よりも高品位のデバイスを製造することができる。このように、露光装置を使用するデバイス製造方法、並びに結果物としてのデバイスも本発明の一側面を構成する。

10

20

30

40

50

#### 【図面の簡単な説明】

#### 【0115】

【図1】実施例1の要部断面図

【図2】入射波とミラー基板上に成膜された多層膜による反射波の波面の説明図

【図3】一層対膜数が異なる部分で反射光の波面の比較説明図

【図4】多層膜の周期数と規格化した反射率との関係を示したグラフ

【図5】多層膜上層除去の効果を示した説明図

【図6】多層膜上層の除去を模式的に表した説明図

【図7】多層膜上層の除去を模式的に表した説明図

【図8】EUV露光装置の実施例6の概略図

【図9】従来の反射鏡の概略図

【図10】従来の反射鏡の概略図

【図11】反射鏡の周期と振幅の関係を示したグラフ

【図12】補正量と除去する層数の関係を示した説明図

【図13】成膜後の反射鏡を部分的な膜除去方法によってのみ補正した概略図

【図14】実施例に関わる実施形態の概略図

【図15】実施例1に関わる概略図

【図16】実施例1に関わる製造方法の手順を記述したフローチャート

【図17】実施例1に関わる概略図

【図18】実施例2に関わる概略図

【図19】実施例3に関わる概略図

【図20】実施例4に関わる概略図

【図21】実施例5に関わる製造方法の手順を記述したフローチャート

【図22】反射鏡の表面粗さを示した説明図

【図23】デバイス(ICIやLSIなどの半導体チップ、LCD、CCD等)の製造を説明するためのフローチャート

【図24】図23に示すステップ4のウェハプロセスの詳細なフローチャート

#### 【符号の説明】

#### 【0116】

MU：ミラーユニット

100：反射鏡

101：基板

102：アクチュエータ

103：導電性物質

104：基板

105：多層膜

106：空間周波数とパワースペクトル密度の相関

107：低次の変形

108：高次の変形

109 : 大きな変形量

110 : 大きな変形量を coating milling で補正した場合の図

111 : 必要な反射率が得られる層対

112 : 基板

113 : 高剛性部材

114 : アクチュエータ

115 : 基板を部材に取り付けるバネ

116 : アクチュエータコントローラ

117 : 多層膜

118 : 各位置での所定面からのズレ量

119 : ズレ量を近似した曲線

120 : 各アクチュエータ位置での補正量

121 : 近似曲線での一番凸な部分

122 : 基板補正手段によって補正された後の変形

123 : 基板補正手段によって補正された後の変形を膜除去手段によって補正した面

124 : 基板補正手段によって補正された後の変形の一一番凹な部分

125 : 基板補正手段によって補正で残った高次の変形

126 : 膜除去手段によって補正された部分

127 : 变形の絶対量の大きい部分

128 : 变形の絶対量の小さい部分

129 : 基板変形手段による変形

130 : 基板変形手段によって新たに生じた変形

131 : 基板変形手段によって新たに生じた変形を膜除去手段によって補正した部分

10

20

【図 1】

【図 3】

【図 2】

【図 4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図14】

【図13】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

---

フロントページの続き(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

G 2 1 K 5/02 X

H 0 1 L 21/30 5 3 1 A