(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-193621

(P2004-193621A)

(43) 公開日 平成16年7月8日(2004.7.8)

(51) Int.Cl.<sup>7</sup>H01L 21/312

H01L 21/768

F 1

H01L 21/312

H01L 21/90

テーマコード(参考)

C 5FO33

J 5FO58

審査請求 未請求 請求項の数 10 O L 外国語出願 (全 14 頁)

|              |                              |          |                                                                                  |

|--------------|------------------------------|----------|----------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2003-412698 (P2003-412698) | (71) 出願人 | 501229528<br>テキサス インスツルメンツ インコーポ<br>レイテッド<br>アメリカ合衆国、テキサス、ダラス、チャ<br>ーチル ウエイ 7839 |

| (22) 出願日     | 平成15年12月11日 (2003.12.11)     | (74) 代理人 | 100066692<br>弁理士 浅村 皓                                                            |

| (31) 優先権主張番号 | 318309                       | (74) 代理人 | 100072040<br>弁理士 浅村 肇                                                            |

| (32) 優先日     | 平成14年12月12日 (2002.12.12)     | (74) 代理人 | 100107504<br>弁理士 安藤 克則                                                           |

| (33) 優先権主張国  | 米国(US)                       | (74) 代理人 | 100102897<br>弁理士 池田 幸弘                                                           |

最終頁に続く

(54) 【発明の名称】金属バリア接着性が改良された、シリコン-炭素-酸素誘電体を有する半導体デバイス、及びその形成方法

## (57) 【要約】

【課題】OSGと銅の間にバリア層を設ける場合、OSGに対するバリア層の接着性が許容し得ないものであるという従来技術の欠点を改良する代替の実施形態を提供する。

【解決手段】半導体ウェーハ上に形成された電子デバイス(200)を製造する方法(100)。本方法は、ウェーハに対する固定位置に誘電体層(226)を形成する。ここで、前記誘電体層は、シリコン、炭素、及び酸素の各々を有する原子濃度で含む。前記形成ステップの後、本方法は、前記誘電体層の一部における炭素の原子濃度が上昇し、前記誘電体層の一部における酸素の原子濃度が低下するように、前記電子デバイスをプラズマに暴露する(118)。暴露ステップの後、本方法は、前記誘電体層の少なくとも一部に隣接してバリア層を形成する(120)。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

半導体ウェーハ上に形成される電子デバイスの製造方法であって、

前記ウェーハに対する固定位置に誘電体層を形成するステップであって、前記誘電体層

が、シリコン、炭素、及び酸素の各々を有する原子濃度で含むステップと、

前記形成ステップの後、前記誘電体層の一部における炭素の原子濃度が上昇し、前記誘

電体層の一部における酸素の原子濃度が低下するように、前記電子デバイスをプラズマに

暴露するステップと、

前記暴露ステップの後、前記誘電体層の少なくとも一部に隣接してバリア層を形成する

ステップとを含む方法。

10

**【請求項 2】**

前記暴露ステップが、前記電子デバイスをヘリウムと水素を含むプラズマに暴露するス

テップを含む、請求項 1 記載の方法。

**【請求項 3】**

前記暴露ステップが、前記電子デバイスをヘリウムと H<sub>2</sub> を含むプラズマに暴露するス

テップを含む、請求項 1 記載の方法。

**【請求項 4】**

前記プラズマが、ヘリウム約 95 % と H<sub>2</sub> 約 5 % を含む、請求項 3 に記載の方法。

**【請求項 5】**

前記暴露ステップが、

前記ウェーハを支持する台に、少なくとも 100 ワットの電力を印加するステップと、

前記印加ステップと同時に、ヘリウムと水素を含むプラズマに、前記電子デバイスを暴

露するステップとを含む、請求項 1 記載の方法。

20

**【請求項 6】**

前記暴露ステップが、前記ウェーハを支持する台に、100 ~ 500 ワットの範囲の電

力を印加するステップと、

前記印加ステップと同時に、ヘリウムと水素を含むプラズマに、前記電子デバイスを暴

露するステップとを含む、請求項 1 記載の方法。

**【請求項 7】**

誘電体層を形成する前記ステップが、前記ウェーハと前記誘電体層との間に前記導体が

位置するように前記誘電体層を形成するように、誘電体層を形成する前記ステップの前に

、前記ウェーハに対する固定位置に導体を形成するステップと、

前記暴露ステップの前に、前記誘電体層にボイドを形成するステップであって、前記ボ

イドが前記誘電体層を貫通して延びていて、前記導体の一部を露出するステップとをさら

に含む、請求項 1 記載の方法。

30

**【請求項 8】**

ボイドを形成する前記ステップの後、前記電子デバイスをプラズマに暴露する前記ス

テップの前に、前記電子デバイスをアルゴンに暴露するステップをさらに含む、請求項 7 記

載の方法。

**【請求項 9】**

半導体ウェーハ上に形成される電子デバイスの製造方法であって、

前記ウェーハに対する固定位置に誘電体層を形成するステップであって、前記誘電体層

が、シリコン、炭素、及び酸素を含むステップと、

前記形成ステップの後、前記電子デバイスを、ヘリウムと水素を含むプラズマに暴露す

るステップと、

前記暴露ステップの後、前記誘電体層の少なくとも一部に隣接してバリア層を形成する

ステップとを含む方法。

40

**【請求項 10】**

前記暴露ステップが、

前記ウェーハを支持する台に、少なくとも 100 ワットの電力を印加するステップと、

50

前記印加ステップと同時に、ヘリウムと水素を含むプラズマに、前記電子デバイスを暴露する前記ステップとを含む、請求項 9 記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本実施形態は、半導体デバイス及び方法に関し、より詳細には、シリコン・炭素・酸素誘電体層に対する接着性の改良を対象とする。

【背景技術】

【0002】

半導体デバイスは、現代社会の無数の様々な側面で普及している。その結果、こうしたデバイスの市場はかなり急速に進歩し続けている。この進歩は多くの点で明らかであり、直接間接に半導体デバイスに、さらにこうしたデバイスを形成する方法に関係している。たとえば、この進歩は、デバイスの数多くの属性に影響を与えており、デバイスのサイズ、信頼性、収率、及びコストを含む、設計及び製作時のこうした属性に注目する必要性が増大している。これら及びその他の側面は、従来技術の対象となっているが、以下に詳述する好ましい実施形態によってさらに改良された。

【0003】

さらなる背景としては、この好ましい実施形態は、半導体デバイスにおける誘電体層に対する接着性に関するものである。より具体的には、この好ましい実施形態は、シリコン、炭素、及び酸素のすべてを含む誘電体層、並びに、バリア層に対する誘電体層の接着性に関し、バリア層は誘電体層と銅などの金属との間のバリアとして作用する。初めにシリコン、炭素、及び酸素を有する誘電体層に目を向けると、こうした材料は、有機珪素ガラス(「OSG」)として公知のフィルムに組み合わされていることがあり、このフィルムは、Novellus and Applied Materialsから市販されている。OSG層は、好適な(すなわち、比較的低い)誘電率など、当技術分野で公知の様々な理由で魅力がある。次に銅に目を向けると、アルミニウムなど従来から使用されている金属と比べて銅の抵抗は低く、したがって信頼性が高いので、これを使用することが当技術分野で特に配線用金属としてより好まれるようになってきた。

【0004】

上記を想定すると、銅をOSG層と同じデバイスに使用する場合は、通常、銅とOSGの間にバリア層を形成する。このバリア層が、誘電体中へ銅が拡散する望ましくない可能性を防止又は低下させる。しかし、この好ましい実施形態に関連して、本発明の発明者らは、OSGと銅の間にバリア層を設ける場合、OSGに対するバリア層の接着性が許容しえないものであることを確認した。たとえば、いくつかの公知の試験技術を用いてこうした接着性を実験的に評価した。これらの技術は、バリア層がOSGから外れてしまうために、その後形成される銅層/デバイスに対するバリアとして、その本来の目的を果たすことができないことを実証した。たとえば、テープ試験が用いられた。この試験では、OSG層上にバリア層を形成した半導体ウェーハをけがき、このウェーハにテープを貼付し、これを剥がして層が無傷のままかどうかを確認する。こうした試験で、バリア層とOSG層の界面にクラックが形成されたことが分かった。これは、これら2層間の結合が許容しえないことを定性的に実証するものである。別の例として、4点曲げ試験を行った。この試験では、上記と同じタイプの半導体ウェーハの両端に屈曲力を加えた。この力は、ウェーハのより中央部に加えられる他の力と組み合わせて用いた。この試験を用いて定量的な測定を行い、OSGとバリア層の間が破損するとき端部に加えられた力を求めた。こうした破損は、バリア層のクラック又は破断として発生することもあり、バリア層がOSG層から剥離することもある。最後の試験として、上記のウェーハに、化学機械研磨(「CMP」)を施すことができる。この試験は、これが実際の製造ステップであるという点で好ましいことがある。CMPは、追加の加工ステップの前に様々な層を平坦化するために使用されることが多いからである。とにかく、本発明の発明者らは、CMPによって、隣接したOSGとバリア層の間が破損することも確認している。

10

20

30

40

50

**【発明の開示】****【発明が解決しようとする課題】****【0005】**

上記に鑑みて、本発明の発明者らは、従来技術の様々な欠点を改良する代替の実施形態を以下に提供するものである。

**【課題を解決するための手段】****【0006】**

1つの好ましい実施形態には、半導体ウェーハ上に形成された電子デバイスを製造する方法がある。本方法は、前記ウェーハに対する固定位置に誘電体層を形成する。ここで、前記誘電体層は、シリコン、炭素、及び酸素の各々を有する原子濃度で含む。前記形成ステップの後、本方法は、前記誘電体層の一部における炭素の原子濃度が上昇し、前記誘電体層の一部における酸素の原子濃度が低下するように、前記電子デバイスをプラズマに暴露する。前記暴露ステップの後、本方法は、前記誘電体層の少なくとも一部に隣接してバリア層を形成する。10

**【0007】**

他の様様もまた開示され、特許請求されている。

**【発明を実施するための最良の形態】****【0008】**

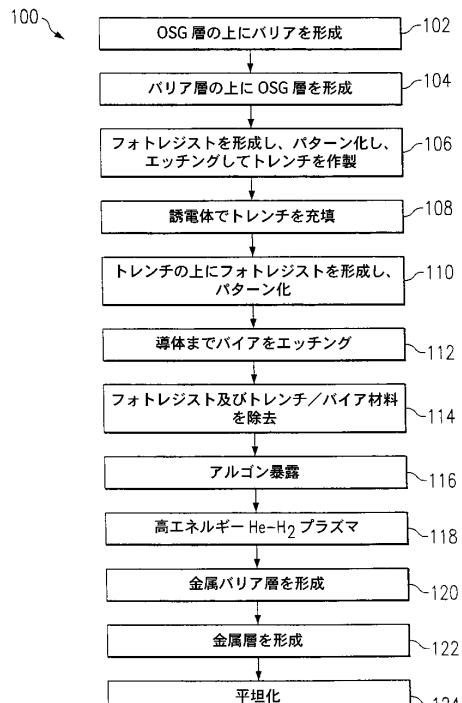

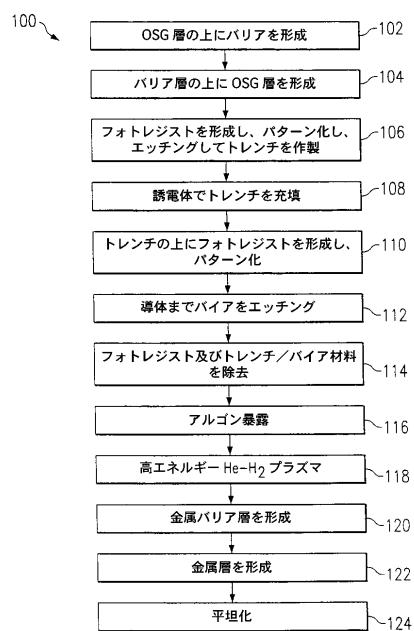

図1は、この好ましい実施形態によるデバイス形成方法100の、1つの好ましい実施形態の流れ図を示す図である。方法100とこの方法で形成されるデバイスをさらに例証するために、本発明の範囲をさらに実証する図2～図11に示した横断面図をさらに参照して、方法100の様々なステップを以下に述べる。20

**【0009】**

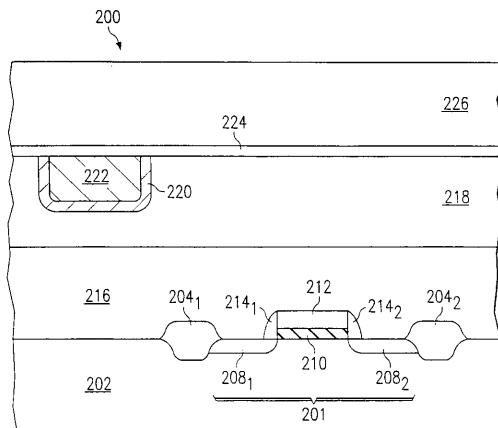

この好ましい実施形態は、1つにはシリコン、炭素、及び酸素を含む誘電体層の処理に関連する。こうした材料は、有機珪素ガラス（「OSG」）として知られるフィルムに組み合わされていることがある。OSG層は、半導体デバイスの種々のレベルで用いることができる。そこで紹介のために、半導体デバイス200を示す図2に関して、以下の説明に使用する一例を次に提供する。さらに、従来技術及び以下に説明する本発明の実施形態のいずれも、図2に示すような構造を用いて実施することができる。ここで、追加の加工ステップのさらなる詳述をこの好ましい実施形態について以下に提供する。さらに、図2～図11を参照して好ましい実施形態の方法を説明するが、これらの方法は、隣接するバリア層に対する接着性改良がOSG層にメリットをもたらす、どんなタイプのデバイス構造（たとえば、金属配線、金属線、金属ゲート、又は他の導電性構造）にも、かつどんなタイプのデバイス（たとえば、メモリデバイス、論理デバイス、パワーデバイス、ディジタル信号プロセッサ、又はマイクロプロセッサ）にも適用することができる。30

**【0010】**

初めに図2のデバイス200に目を向けると、このデバイスは、当分野で公知の技術で形成された各種構成部品を含んでいる。これらの構成部品は、例として示すように、基板202（たとえば、シリコン）に形成された活性エリア201に関連して形成されたトランジスタなどの様々なデバイスを形成することができる。基板202は、デバイス200の基礎を形成する半導体ウェーハの一部であるか、又はこれを代表している。さらに、このウェーハを、以下にさらに説明するように1つ又は複数のツール内に封入して、本明細書記載の様々なステップを遂行することができる。一般に、活性エリア201は、分離領域 $204_1$ 、 $204_2$ の間に画定される。活性エリア201内には、ソース及びドレイン領域 $208_1$ 、 $208_2$ 、ゲート誘電体210、導電性ゲート212、並びに側壁絶縁体 $214_1$ 、 $214_2$ が形成されており、これによりたとえばトランジスタを形成している。誘電体層216を、ここに示すトランジスタの上に重ねて形成し、平坦化する。したがって、誘電体層216は、当分野で公知の技術で形成された能動（ことによると受動）部品を含むデバイス部分の上に重なっている。第2誘電体層218が誘電体層216の上に重なるように示されているが、実際は、層216と218は1層でもよい。40

10

20

30

40

50

## 【0011】

図2とその他の項目について引き続き説明すると、複数レベルの配線構造を形成することができ、この配線構造が互いに、及び基板202と関連して形成された各種の構成要素と接続することができることに留意されたい。こうした配線構造によって実現される接続、及びこの構造が接続することができる構成要素には多くの可能性があるが、当分野の技術者なら容易に確かめることができるので、特定の接続に関する著しい詳細は必要なない。したがって、特定の例だけを以下に提供するが、これは単に状況を実証するだけであり、対象とする本発明の範囲を限定するものではない。この特定の例では、誘電体層218に形成されたトレンチ構造内にライナ／バリア層220を形成する。このライナ／バリア層220は、タンタル、窒化タンタル、窒化チタン、タンゲステン、窒化タンゲステン、その他を含む各種材料の1種とすることができます。さらに、ライナ／バリア層220と整合して導体222を形成し、誘電体層218の上面に沿ってこれを平坦化する。他の導電性材料から形成することもできるが、一例として、導体222は銅を前提とする。その後、誘電体層218の上、したがって導体222の上にもバリア層224を形成する。このバリア層は、しばしばエッチストップ層と呼ばれ、一般に数百オングストロームオーダーの窒化シリコン又はその他の誘電性バリア材料である。

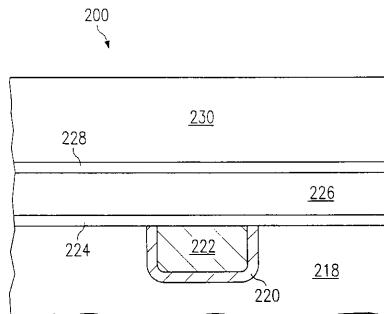

## 【0012】

図2の残りの説明では、この好ましい実施形態に特に関連する様態について紹介する。バリア層224の上に重ねて誘電体層226を形成する。この誘電体層226は、化学気相成長法（「CVD」）、スピノン法、又はその他の堆積法で堆積することができる。誘電体層226の厚みは要求性能によって決まる。さらに、誘電体層226は、誘電率が比較的低く、かつOSGから形成されていることが好ましい。すなわち、少なくともシリコン、炭素、及び酸素の所定の組合せを含んでいる。したがって、話を単純にするために、以下本明細書では、誘電体層226をOSG層226と呼ぶ。以下に詳述するように、この好ましい実施形態は、OSG層226に対する次のバリア層の接着性を改良することに関するものである。さらにこの点に関して以下の図を単純化するために、層218から上を切取った図を示すことによって、図2の詳細の多くを以下の図から除いてある。したがって、焦点は、OSG層226である。しかし、当分野の技術者なら、以下の図に示した構造が、図2のデバイス（又は上記のその他のデバイス）も含むことを意図したものであることを理解するはずである。

## 【0013】

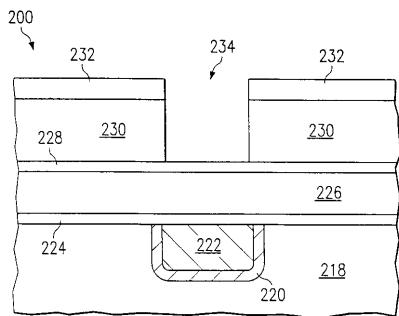

図3に目を向けると、これは、追加の製造ステップ後の図2のデバイス200を図示している。次に図1の方法100に戻ってこの製造ステップをさらに考察する。さらに紹介すると、最新の例として、方法100は、いわゆるデュアルダマシン構造を形成するステップを含むものである。デュアルダマシン構造とは、通常デバイス層内に、2つの部分を含むボイドを形成することを意味する。これらの2つの部分は、異なる名前で呼ばれることがある。たとえば、略垂直のより狭いボイドはバイアと呼ばれることがあり、略水平のしばしばより広いボイドはトレンチと呼ばれることがある。一般的のデュアルダマシン法は当技術分野で公知であり、実際には、異なるステップで、又は順序の異なる類似のステップで、時には特定のバリア層付で、又はこれが無い状態で実施することができる。したがって、デュアルダマシンの様態に関しては、方法100は一例に過ぎない。この背景を前提として、方法100は、OSG層226の上にバリア層228を形成するステップ102で始まる。バリア層228は、たとえばバリア層224と同じ方法又は同様な方法で形成することができ、こうして通常数百オングストロームオーダーの窒化シリコンのエッチストップ層が形成される。ステップ102の後に、ステップ104で、バリア層228の上にもう1つの誘電体層230が形成される。この好ましい実施形態では、誘電体層230は、層226と同じOSG材料で形成される。誘電体層230の厚みは、誘電体層226の厚みと同じでも異なってもよい。これも参考のために、以下の本明細書では誘電体層230をOSG層230と呼ぶ。

## 【0014】

10

20

30

40

50

図4は、当技術分野で公知の技術に従って、追加の製造ステップを行った後の図3のデバイス200を示す。方法100を進むと、次のステップ106でフォトレジスト層232を形成し、パターン化し、エッチングする。したがって、図4の透視図では、3つのステップすべてがフォトレジスト層232に対して行われている。これにより、OSG層230を貫通し、バリア(又はエッチストップ)層228上で止まる第1ボイド234が形成される。これは、トレンチと呼ばれることがある。最後に、以下でより明らかになる理由で、ボイド234を形成するためのパターン化及びエッチングは、このボイドが少なくとも部分的に導体222と垂直にそろっていることが好ましい。

#### 【0015】

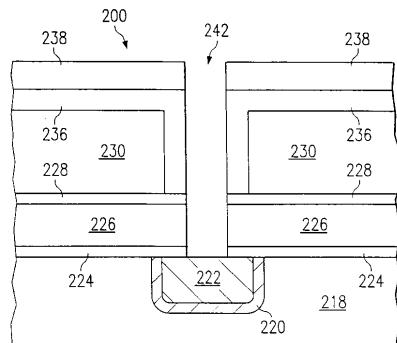

図5は、当技術分野で公知の技術に従って、追加の製造ステップを行った後の図4のデバイス200を示す。方法100を進むと、次のステップ108で、図4のフォトレジスト層232の残りを(所望により、適当な清浄化ステップで)除去し、デバイス200の上に次の誘電体層236を形成する。その結果、この誘電体層が図4に示したボイド234を充填する。次に、ステップ110で、別のフォトレジスト層238を形成しパターン化する。フォトレジスト層238は、以下に説明する次のエッチングでエリア240が除去されるようにパターン化する。さらに、エリア240はまた、導体222及び図4のボイド234を誘電体層236で充填したエリアと少なくとも部分的に垂直にそろっていることが好ましい。

#### 【0016】

図6は、当技術分野で公知の技術に従って、追加の製造ステップを行った後の図5のデバイス200を示す。方法100を進むと、次のステップ112で、フォトレジスト層238をエッチングして、この層の材料を図5に示したエリア240から除去する。そしてエッチングを継続して、誘電体層236、バリア層228、OSG層226、及びバリア層224を貫通して、バリアと呼ばれることがあるボイド242を作り出す。こうして、エッチングは、導体222の上面まで到達する。したがって、以下に示すように、最終的にはトレンチ242のエリアに、導体222への電気的接点を作ることができる。

#### 【0017】

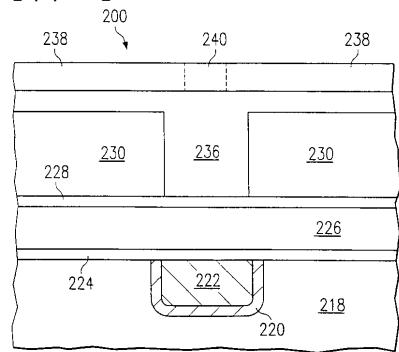

図7は、当技術分野で公知の技術に従って、追加の製造ステップを行った後の図6のデバイス200を示す。方法100を進むと、次のステップ114で、図5に示したフォトレジスト層238と誘電体層236の両方をデバイス200から除去する。これらの2つの層は異なる材料から形成されているので、異なる除去技術を使用することができます。いずれにせよ、これらが除去されると、OSG層230、226を通って導体222の上面まで単一ボイド244が残る。ボイド244は、2つの部分を効果的に含むことに留意されたい。1つの部分は、導体222の近くでOSG層226のエッチング部分の間にありより狭幅の部分であり、他の部分は、導体222から離れたOSG層230のエッチング部分の間にありより広幅の部分である。この2段構造は、典型的なデュアルダマシン法の結果である。

#### 【0018】

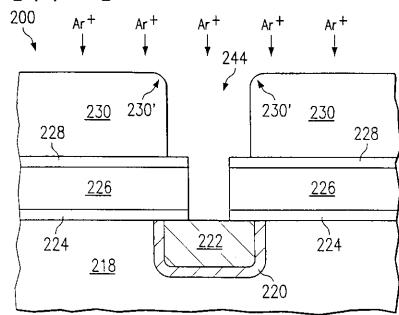

図8は、追加の製造ステップを行った後の図7のデバイス200を示す。しかし、ここで、残りの各種ステップは、従来技術からの離脱を提供するものであり、OSG層230、226の露出した垂直及び水平部分に対して、これらの部分と後で形成されるバリア層間の改良された接着性をさらに提供するものであることに留意されたい。次いで図8に目を向け図1の方法100をさらに進むと、ステップ116で、デバイス200は、好ましくはアルゴンスパッタエッチング法でアルゴンに暴露される。こうしたプロセスは、通常、スパッタエッチングチャンバで行われる。このチャンバでは、デバイス200を形成するウェーハに対してアルゴンイオンを加速させる。ステップ116のアルゴンスパッタリングは、様々な利点があることが認められている。第1に、アルゴンが、方法100の前のステップに由来する、導体222の上面に残りやすい様々な汚染物質を清浄化する。こうした汚染物質としては、エッチング残渣、前のエッチングからのポリマー、及び導体222が銅の場合は酸化銅を挙げることができる。第2に、アルゴンスパッタリングは、O

10

20

30

40

50

S G 層 2 3 0 の内縁部をわずかに丸くする。こうした縁部を図 8 に 2 3 0' として示す。以下に述べる理由で、こうした丸みづけは特定の実施形態で有利な場合がある。最後に、ボイド 2 4 4 の形成後は汚染物質が存在する確率が高いために、ステップ 1 1 6 が大部分の実際の実施において望ましいことに留意されたい。ただし、ステップ 1 1 6 の必要性並びにその継続時間は、ボイドがシングルダマシン法で形成されたのか、又はデュアルダマシン法で形成されたのかを含めて、各種パラメータに基づいて調整することができる。実際、前のステップの後に十分な清浄化操作を行った結果ボイド 2 4 4 の汚染物質が無視できるなら、このような場合には、代替の実施形態においてステップ 1 1 6 を省略することができる。

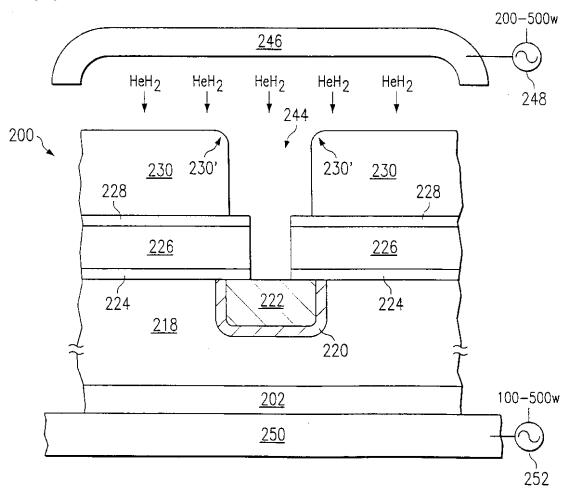

## 【 0 0 1 9 】

10

図 9 は、ステップ 1 1 8 に関する図 1 の方法 1 0 0 に記載したように、追加の製造ステップを行った後の図 8 のデバイス 2 0 0 を示す。ステップ 1 1 8 では、このステップは従来技術からさらに離脱したものであり、デバイス 2 0 0 は He と H<sub>2</sub> を含むプラズマにさらされる。ただし、この 2 つのそれぞれの割合は変化させることができる。たとえば、従来技術では、導体 2 2 2 などの導体の上部にある酸化銅を低減させるために、He が混合物の 9 5 %、H<sub>2</sub> が混合物の 5 % である、He と H<sub>2</sub> を含むプラズマが、App lied Materials によって (10 ワットのオーダーの) 非常に低い台パワーで実施されている。さらに、従来技術の He - H<sub>2</sub> プラズマは、プラズマが形成されるチャンバコイルに対して電源を印加することによってこのプラズマをイオン化することによって実施されており、この電源は、2 0 0 ~ 5 0 0 ワットのオーダーである。ステップ 1 1 8 に戻ると、プラズマをイオン化するために、同等の電力構成及び電源と共に、この同じ He 9 5 % と H<sub>2</sub> 5 % の混合物をステップ 1 1 8 で使用してもよく、又は異なる割合の He と H<sub>2</sub> を使用してもよい。この目的のために、図 9 は、チャンバコイル 2 4 6 と、このコイル 2 4 6 に接続した電源 2 4 8 のブロック図を含んでいる。こうした構成は当技術分野で公知である。さらに、電源 2 4 8 は、2 0 0 ~ 5 0 0 ワットの範囲に設定することが好ましい。これは、従来技術で用いられるものと同等の範囲である。しかし、ステップ 1 1 8 は、この好ましい実施形態の少なくとも 2 つの点で従来技術と異なるものである。第 1 に、好ましい実施形態では、ステップ 1 1 8 の He - H<sub>2</sub> プラズマは、ステップ 1 1 6 のアルゴン処理に加えて行うものである。第 2 に、ステップ 1 1 8 のプラズマは、基板 2 0 2 を支持している台 2 5 0 に対して比較的大きな電力を印加することによって、デバイス 2 0 0 が形成されているウェーハに向かって加速される。この態様を説明するために、図 9 は一般的の台 2 5 0 を示しており、当分野の技術者は、ステップ 1 1 8 を遂行するための適当なプラズマチャンバでこうした装置をよく見かけるはずである。さらにこの点については、台 2 5 0 は電源 2 5 2 と結合しており、ステップ 1 1 8 では、好ましくは電源 2 5 2 は 1 0 0 ~ 5 0 0 ワットの範囲のどんな電力レベルも供給する。ステップ 1 1 8 の継続時間はこの好ましい実施形態に従って変えることができる。好ましくは、こうした持続時間は、O SG 層 2 2 6 、 2 3 0 のそれぞれの露出面からの所定の深さにのみプラズマの影響を与えるような時間とする。たとえば、この影響がこれらの層の約 1 0 オングストロームに及ぶことが好ましく、本発明の発明者らは、1 秒当たり約 1 オングストロームの影響を観察している。したがって、1 0 オングストロームに影響を与えるために、ステップ 1 1 8 のプラズマ加速は 1 0 秒間にわたって行われる。またこの点について、好ましい実施形態では、ステップ 1 1 8 の継続時間の上限についても検討している。具体的には以下に示すように、ステップ 1 1 8 He - H<sub>2</sub> プラズマの影響を受けた O SG 層 2 3 0 のエリアの一部はその後除去されるので、ステップ 1 1 8 のプラズマ浸透深さをこの除去によって打ち消すことができる。しかし、他の暴露エリアではこうした除去は行われないので、O SG がより深く影響を受けるようなレベルに到達するようにステップ 1 1 8 のプラズマを形成することで、これらのエリア並びにその影響（もしも影響があればだが）に注意を払うべきである。たとえば、ステップ 1 1 8 の持続時間をあまり長く延ばすと、導体 2 2 2 と任意の近くの類似の接点（明確には図示せず）との間のキャパシタンスが増大する可能性がある。したがって、こうした影響を避けるために、ステップ 1 1 8 の持続時間及びこ

20

30

40

50

れに対応する影響の深さを監視するべきである。

【0020】

以下のステップに進む前に、ステップ118で得られた結果に関するいくつかの観察に注目すべきである。台250に印加するステップ118の電力を従来技術の電力より増大させたのに応答して、He-H<sub>2</sub> プラズマは、OSG層230、226を含むデバイス200の露出エリアに向かって下方へ加速される。OSG層230、226に関しては、本発明の発明者等は、ステップ118によってこれらの層の露出面（垂直及び水平両方共）近くのシリコン、炭素、及び酸素の原子濃度が変化することを観察している。たとえば、1つの実験的研究では、ステップ118の前のOSG層230、226は元々酸素の原子濃度が比較的高く、炭素の原子濃度が低く、シリコンの原子濃度は炭素と酸素の間の濃度であったが、ステップ118の後は層230、226の露出面近くでこれらの濃度が変化し、このステップ前のそれぞれの濃度と比べて、炭素濃度が上昇し、酸素濃度が低下し、シリコンも上昇している。本発明の発明者等は、以下にさらに評価するように、両OSG層230、226の表面とその後の金属層間の接着が改良されるのは、これらの濃度変化の1つ又は複数が関連していると確信している。さらに、この好ましい実施形態で、ステップ116のアルゴン処理が、金属導体222の上面から酸化銅を除去することが分かったが、この材料の一部はボイド244エリア内のOSG層226の垂直な側壁に沿って残留することが分かった。しかし、ステップ118の処理は、これらの側壁エリアの酸素も低下させると思われ、これにより、下記の追加の金属と組み合わせてこの領域に改良された金属導体を形成する。最後に、ステップ118 プラズマは、導体が銅で形成されている場合、導体222の上面の金属に最小の影響しか与えないことが認められている。10 20

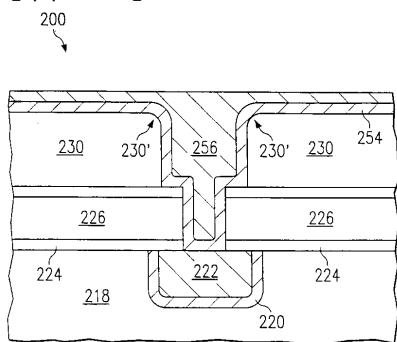

【0021】

図10は、ステップ120に関して図1の方法100に記載したように、追加の製造ステップを行った後の図9のデバイス200を示す。ステップ120では、前の図9でボイド244として示されたものの内部に導電性バリア層254が形成される。バリア層254は、たとえばタンタルなど、様々な材料から作ることができる。好ましい実施形態では、バリア層254の厚みは、250オングストロームのオーダーとすることができます。しかし、デバイスサイズが縮小する傾向が続いているので、業界ではいわゆる「ゼロバリア」状態を達成する目標が表明されている。それまでは、バリア層の厚み低下が目標であり、実際、この好ましい実施形態と関連づけて、バリア層254の厚みも低下させることができると思われる。たとえば、バリア層254の厚みが50オングストロームの薄さで、満足できるデバイス収率が見出されている。より具体的には、上記のようにOSG層226、230の原子濃度の変化によって、本明細書の背景技術の部分で説明したように、こうした接着が壊れてしまう従来技術とは異なり、こうした薄くなった厚みでも、バリア層254とこの層の下の材料との間の十分な接着が確認されている。30

【0022】

図10に進むと、図1の方法100に示したように、ステップ120の後にステップ122が行われる。このステップにおいて、前の図9でボイド244として示されたものの内部に延在する金属層256がデバイス200の上に形成される。好ましい実施形態では、金属層256は銅である。初めにボイド244内のバリア層254上に銅シード層（個別に図示せず）を形成し、この銅シード層の後に銅めっき層を形成することによってこれを形成する。これらの層に関連して、上記のアルゴンステップ116が縁部230'の丸みづけに好都合であると述べたことを思い出されたい。こうした縁部230'が無いと、バリア層254並びに銅シード層の付着は、ボイド244内の垂直開口に集中するか、あるいはこれを剥ぎ取る傾向にあると思われ、その結果、その後の金属層256はこのエリアを完全には充填することができない。こうした結果は、金属層内に空隙を作り出すといわれることがある。しかし、図10を見ると、丸みのついた縁部230'が金属層256によるボイド244の完全な充填を可能にしているので、ボイド244の全体が金属層256で充填されていることが分かる。別の観察としては、図10におけるデバイス200形成の状態を見ると、バリア層254が金属層256とOSG層230、226の間のバ40 50

リアを形成していることがさらに分かる。したがって、金属層 256 が銅である好ましい実施例では、バリア層 254 が金属層 256 から OSG 層 230、226 への銅の拡散を防止している。しかし、ステップ 118 がこれら OSG 層 230、226 の銅と酸素の濃度を変化させることを思い出すと、将来の実施形態では層 254 の厚みをさらに薄くすることができ、一方、変化した濃度自体も金属層 256 による銅の拡散を妨げることができるとと思われる。このようにして、さらにゼロバリアに向けて進歩する。

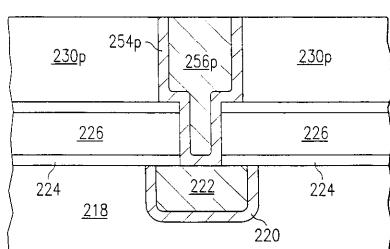

#### 【0023】

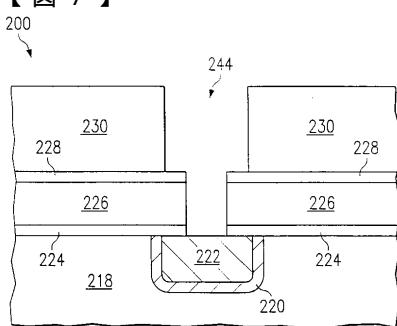

図 11 は、ステップ 124 に関して図 1 の方法 100 に記載したように、追加の製造ステップを行った後の図 10 のデバイス 200 を示す。ステップ 124 では、たとえば化学機械研磨（「CMP」）操作を用いて、デバイス 200 を平坦化する。参考のために、この平坦化によって影響を受ける層は参照符号に下付き文字「P」をつけて示した。こうして、平坦化の後は、OSG 層 230 は OSG 層 230<sub>P</sub> になり、金属バリア層 254 は金属バリア層 254<sub>P</sub> になり、金属層 256 は金属層 256<sub>P</sub> になる。したがって、図 11 の得られたデバイス 200 の構造から、電気的接点を金属層 256<sub>P</sub> に作ることができ、これにより金属導体 222 にも電気的に接続する。最後に、ステップ 118 に関連して、He - H<sub>2</sub> プラズマ暴露の継続時間が、OSG 層 230 の濃度が影響を受ける深さを制御することを上述したことを思い出されたい。好ましい実施形態では、この影響を受けた深さは、ステップ 124 の CMP 操作によって部分的又は全体的に除去され、したがって OSG 層 230 の上水平面に沿ったプラズマ処理のどんな影響も CMP によって効果的に除去される。しかし、表面の下では、OSG 層 230<sub>P</sub> と金属バリア 254<sub>P</sub> の間の改良された接着性は引き続き存在しており、こうした改良は、本明細書に上記した様々な試験方法によって確認されている。

#### 【0024】

上記から、当分野の技術者は、この好ましい実施形態が、金属とシリコン・炭素・酸素誘電体層との間の接着性が改良された半導体デバイス及び方法を提供することを理解するはずである。この改良された接着性は、デバイスの信頼性、収率、及びコストを含めて様々なメリットを提供し、バリア厚みを低下させることによってデバイスのサイズを縮小することができる。さらに、特定の好ましい材料を説明したが、当分野の技術者は、様々な代替物が本発明の教示内でも実施できることを確かめることができる。さらに、前述の実施形態はデュアルダマシン構造の 1 つの型として示したが、多くの変形を有するが依然として本発明の範囲内にある別のデュアルダマシン構造も形成することができる。そして実際に、本発明の範囲は、トレンチとバイアを別々に形成するシングルダマシン構造によって形成された構造も含む。したがって、前述のメリット、並びに、説明され当分野の技術者が確かめることができる様々な代替ステップは、本発明の範囲の柔軟性を実証するものである。また、本実施形態を詳細に説明してきたが、特許請求の範囲によって規定された本発明の範囲を逸脱することなく、上記の説明に様々な置換、修正、又は変更を行うことができることも、これら代替ステップは実証するはずである。

#### 【図面の簡単な説明】

#### 【0025】

【図 1】シリコン、炭素、及び酸素を含む誘電体層に隣接したバリア層を含むデバイスを形成するための 1 つの好ましい実施形態の流れ図を示す。ここに記載の実施形態は、しばしば、デュアルダマシンと呼ばれ、多くのバリエーションで形成することができる。本発明は、トレンチレベルとバイアレベルを別々に形成するシングルダマシン法で形成した構造も含む。

【図 2】内部にトランジスタが形成されており、金属導体が形成された誘電体層がこのトランジスタの上に重なっている基板を含む、好ましい実施形態による半導体デバイスの一部の横断面図を示す。

【図 3】第 1 バリア層によって覆われた金属導体を含む、図 2 のデバイスの一部を示す図である。ここでは、第 1 バリア層は、第 1 シリコン・炭素・酸素含有層によって覆われており、第 1 シリコン・炭素・酸素含有層は、第 2 バリア層と第 2 シリコン・炭素・酸素含有層によって覆われている。

10

20

30

40

50

有層によって覆われている。

【図4】フォトレジスト層の形成ステップと、このフォトレジスト層を通して第2バリア層までエッチングして、第2シリコン・炭素・酸素含有層を貫通するトレンチを形成するステップとを含む、追加の製造ステップ後の図3のデバイスを示す図である。

【図5】フォトレジストの形成を含む、追加の製造ステップ後の図4のデバイスを示す図である。

【図6】エッチングして、第1シリコン・炭素・酸素含有層を貫通して金属接点までバイアを形成するステップを含む、追加の製造ステップ後の図5のデバイスを示す図である。

【図7】フォトレジストと誘電体層の両方を除去した後の図6のデバイスを示す図である。

10

【図8】アルゴンプラズマをあてた図7のデバイスを示す図である。

【図9】高エネルギーHe-H<sub>2</sub>プラズマをあてた図8のデバイスを示す図である。

【図10】金属バリア層及び銅層を形成した後の図9のデバイスを示す図である。

【図11】平坦化ステップ後の図10のデバイスを示す図である。

#### 【符号の説明】

##### 【0026】

|                                    |                                            |    |

|------------------------------------|--------------------------------------------|----|

| 100                                | 好ましい実施形態によるデバイスの形成方法                       |    |

| 102                                | OSG層226の上にバリア層228を形成するステップ                 |    |

| 104                                | バリア層228の上にOSG層230を形成するステップ                 |    |

| 106                                | フォトレジスト層232を形成し、パターン化し、エッチングするステップ         | 20 |

| 108                                | 誘電体層236でボイド234を充填するステップ                    |    |

| 110                                | 別のフォトレジスト層238を形成しパターン化するステップ               |    |

| 112                                | 導体222までフォトレジスト層238をエッチングするステップ             |    |

| 114                                | フォトレジスト層238と誘電体層236の両方を除去するステップ            |    |

| 116                                | アルゴンスパッタリングステップ                            |    |

| 118                                | デバイス200をHeとH <sub>2</sub> を含むプラズマに暴露するステップ |    |

| 120                                | ボイド244内にバリア層254を形成するステップ                   |    |

| 122                                | デバイス200の上に金属層256を形成するステップ                  |    |

| 124                                | デバイス200を平坦化するステップ                          |    |

| 200                                | デバイス                                       | 30 |

| 201                                | 活性エリア                                      |    |

| 202                                | 基板                                         |    |

| 204 <sub>1</sub> 、204 <sub>2</sub> | 分離領域                                       |    |

| 208 <sub>1</sub> 、208 <sub>2</sub> | ソース及びドレイン領域                                |    |

| 210                                | ゲート誘電体                                     |    |

| 212                                | 導電性ゲート                                     |    |

| 214 <sub>1</sub> 、214 <sub>2</sub> | 側壁絶縁体                                      |    |

| 216                                | 誘電体層                                       |    |

| 218                                | 誘電体層                                       |    |

| 220                                | ライナ/バリア層                                   | 40 |

| 222                                | 導体                                         |    |

| 224                                | バリア層                                       |    |

| 226                                | 誘電体層(OSG層)                                 |    |

| 228                                | バリア層                                       |    |

| 230                                | 誘電体層(OSG層)                                 |    |

| 230'                               | 丸められた縁部                                    |    |

| 230 <sub>p</sub>                   | 平坦化された誘電体層(OSG層)                           |    |

| 232                                | フォトレジスト層                                   |    |

| 234                                | 第1ボイド(トレンチ)                                |    |

| 236                                | 誘電体層                                       | 50 |

2 3 8 フォトレジスト層

2 4 0 エリア

2 4 2 ボイド(バイア)

2 4 4 単一ボイド

2 4 6 チャンバコイル

2 4 8 電源

2 5 0 台

2 5 2 電源

2 5 4 導電性バリア層

2 5 4<sub>p</sub> 平坦化された導電性バリア層 10

2 5 6 金属層

2 5 6<sub>p</sub> 平坦化された金属層

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

【図8】

【図10】

【図9】

【図11】

---

フロントページの続き

(72)発明者 リチャード エイ、フォースト

アメリカ合衆国 テキサス、ダラス、ウィントン ストリート 6534

(72)発明者 ノエル エム、ラッセル

アメリカ合衆国 テキサス、ブレイノー、アップランズ ドライブ 1916

(72)発明者 リ チェン

アメリカ合衆国 テキサス、オースティン、セント エドワーズ ドライブ 104

F ターム(参考) 5F033 HH19 KK11 KK19 KK21 KK32 KK33 KK34 MM01 MM02 MM12

MM13 NN06 NN07 QQ00 QQ09 QQ14 QQ25 QQ37 QQ48 QQ92

QQ94 QQ96 RR01 RR06 SS11 SS21 TT02 XX14 XX28

5F058 AA02 AA08 AC03 AD05 AF01 AF04 AG07 AH02 BA04 BA10

BC05 BD07 BF02 BF46 BH16 BJ02

【外國語明細書】

2004193621000001.pdf