(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-294494

(P2005-294494A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>

H01L 31/12

F 1

H01L 31/12

テーマコード(参考)

C

5FO89

審査請求 未請求 請求項の数 5 O L (全 7 頁)

(21) 出願番号

特願2004-106772 (P2004-106772)

(22) 出願日

平成16年3月31日 (2004.3.31)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100081732

弁理士 大胡 典夫

(74) 代理人 100075683

弁理士 竹花 喜久男

(74) 代理人 100084515

弁理士 宇治 弘

(72) 発明者 野口 吉雄

福岡県北九州市小倉北区下到津1丁目10

番1号 株式会社東芝北九州工場内

Fターム(参考) 5F089 AB03 AC21 AC30 EA04

(54) 【発明の名称】光半導体装置及びその製造方法

## (57) 【要約】

**【課題】** パッケージの小型化、及び工程数の削減を図ることが可能な光半導体装置及びその製造方法を提供する。

**【解決手段】** 発光側及び受光側のリードフレーム1と、前記発光側及び受光側のリードフレームの一部及び/又はその近傍で、実質的に同一平面上に形成される発光側及び受光側の素子搭載部2と、発光側の前記素子搭載部2a上の所定位置に載置される発光素子3と、前記発光素子と対向するように設置される受光素子5と、受光側の前記素子搭載部2b上に配置され、前記発光素子3から所定距離となるように、所定面において前記受光素子5を支持する受光素子支持手段6を備える。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

発光側及び受光側のリードフレームと、

前記発光側及び受光側のリードフレームの一部及び／又はその近傍で、実質的に同一平面上に形成される発光側及び受光側の素子搭載部と、

発光側の前記素子搭載部上の所定位置に載置される発光素子と、

前記発光素子と対向するように設置される受光素子と、

受光側の前記素子搭載部上に配置され、前記発光素子から所定距離となるように、所定面において前記受光素子を支持する受光素子支持手段を備えることを特徴とする光半導体装置。

10

**【請求項 2】**

前記受光素子支持手段は、ダミーペレット及び／又は前記受光素子を制御する制御素子ペレットであることを特徴とする請求項1記載の光半導体装置。

**【請求項 3】**

前記受光素子支持手段は、前記受光素子を前記発光素子と対向する面において支持することを特徴とする請求項1又は2に記載の光半導体装置。

**【請求項 4】**

発光側リードフレーム及び受光側リードフレームの一部及び／又はその近傍に形成される発光側及び受光側の素子搭載部を、実質的に同一平面となるように配置する工程と、

発光素子を前記発光側の素子搭載部に載置する工程と、

受光素子支持手段を受光側の素子搭載部に載置する工程と、

受光素子を受光素子支持手段の所定面に設置し、前記発光素子と対向するように配置する工程を備えることを特徴とする光半導体装置の製造方法。

20

**【請求項 5】**

少なくとも前記発光素子及び前記受光素子を樹脂封止する工程と、

樹脂封止の後、前記受光側素子搭載部及び／又は受光素子支持手段の一部を除去する工程を備えることを特徴とする請求項4に記載の光半導体装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

30

本発明は、発光素子と受光素子が対向配置する構造を有する光半導体装置及びその製造方法に関する。

**【背景技術】****【0002】**

一般に、フォトカプラ、フォトリレー等光半導体装置においては、発光素子（発光ダイオード）、受光素子（光起電ダイオード）及び駆動用のMOSFETを夫タリードフレームに搭載し、発光素子と受光素子が対向するように配置して封止する構造が用いられている（例えば特許文献1参照）。

**【0003】**

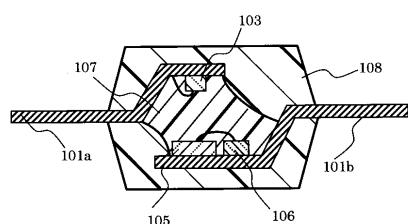

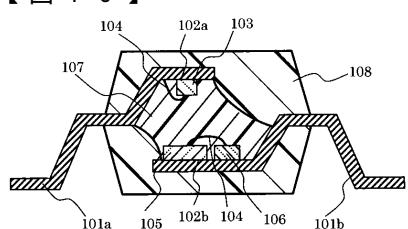

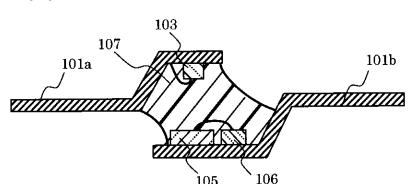

図10に従来の光半導体装置を二重封止構造のフォトリレーを例に挙げて示す。図に示すように、発光側リードフレーム101aに発光素子103が、受光側リードフレーム101bに受光素子105及びMOSFET106が搭載されており、これらが対向するように配置されている。これら素子は光透過性樹脂107で1次封止、光遮断性樹脂108で2次封止されている。発光素子、受光素子は夫タリードフレーム、MOSFETとワイヤー104によりボンディングされている。

40

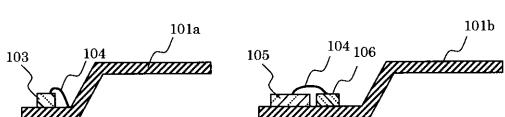

**【0004】**

このようなフォトカプラは、以下のように形成される。先ず、図11に示すように、夫タ押し下げ加工されたリードフレーム101a、101bに、夫タ発光素子103、受光素子105/MOSFET106を搭載する。そして、図12に示すように、これらを対向させた状態に配置する。

50

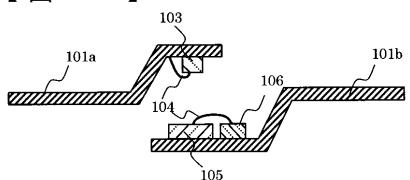

**【0005】**

次に、図13に示すように、これらを光透過性樹脂107により1次封止し、光の伝達経路を形成する。そして、図14に示すように、光を遮断し、素子を保護するために、光遮断性樹脂108により2次封止する。さらに各リードフレーム101a、101bをフォーミングして、図10に示す光半導体素子が形成される。

**【特許文献1】特開2003-8050号公報****【発明の開示】****【発明が解決しようとする課題】****【0006】**

近年、半導体装置の高性能化、実装密度の向上に伴い、光半導体装置の小型化が強く要求されている。しかしながら、このような従来の光半導体装置においては、上述したとおり、受光側リードフレームにおいて、受光素子とMOSFETを平面配置しているため、パッケージの小型化が困難であるという問題があった。

**【0007】**

また、従来の製造工程においては、発光側、受光側のリードフレームを対向させる工程、さらにこれを保持した上で封止する工程をしており、工程数の削減によるリードタイムの短縮やコストの削減が困難であるという問題があった。

**【0008】**

そこで、本発明は、従来の問題を取り除き、パッケージの小型化、及び工程数の削減を図ることが可能な光半導体装置及びその製造方法を提供することを目的とするものである。

**【課題を解決するための手段】****【0009】**

本発明の一態様によれば、発光側及び受光側のリードフレームと、前記発光側及び受光側のリードフレームの一部及び／又はその近傍で、実質的に同一平面上に形成される発光側及び受光側の素子搭載部と、発光側の前記素子搭載部上の所定位置に載置される発光素子と、前記発光素子と対向するように設置される受光素子と、受光側の前記素子搭載部上に配置され、前記発光素子から所定距離となるように、所定面において前記受光素子を支持する受光素子支持手段を備えることを特徴とする光半導体装置が提供される。

**【0010】**

また、本発明の一態様によれば、発光側リードフレーム及び受光側リードフレームの一部及び／又はその近傍に形成される発光側及び受光側の素子搭載部を、実質的に同一平面となるように配置する工程と、発光素子を前記発光側の素子搭載部に載置する工程と、受光素子支持手段を受光側の素子搭載部に載置する工程と、受光素子を受光素子支持手段の所定面に設置し、前記発光素子と対向するように配置する工程を備えることを特徴とする光半導体装置の製造方法が提供される。

**【発明の効果】****【0011】**

本発明の一実施態様によれば、パッケージの小型化、及び工程数の削減を図ることが可能な光半導体装置及びその製造方法を提供することができる。

**【発明を実施するための最良の形態】****【0012】**

以下本発明の実施形態について、図を参照して説明する。

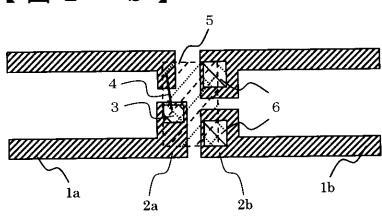

**【0013】****(実施形態1)**

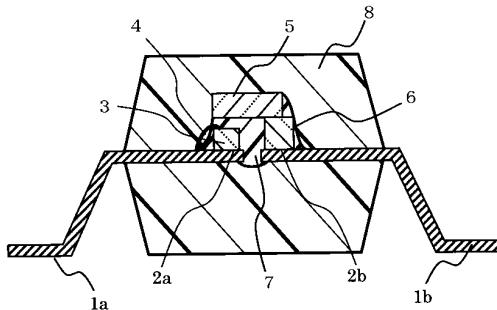

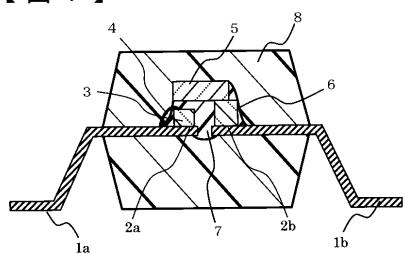

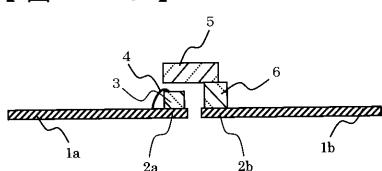

図1に本実施形態の光半導体装置の断面図を示す。図に示すように、発光側リードフレーム1aのベッド2a(発光側素子搭載部)上に発光素子3が載置・接続され、ワイヤー4により他方のリードフレームとボンディングされている。そして、この発光素子3と対向するように受光素子5が配置されている。受光素子5は、受光側リードフレーム1bのベッド2b(受光側素子搭載部)上に載置・接続されたMOSFET6とFCB(フリッ

10

20

30

40

50

プチップボンディング)などにより接続され、これにより支持されている。発光素子3と受光素子5は光透過性の1次封止樹脂7で封止され、光の伝達経路が形成されており、さらに光遮断性の2次封止樹脂8で封止されている。

#### 【0014】

そして、このような光半導体装置において、リードフレーム1aより外部からの電気信号が入力され、発光素子3が発光し、1次封止樹脂7を介して受光素子5に光信号が伝達される。そして、受光素子5において電気信号に変換され、MOSFET6を経て、リードフレーム1bより出力される。

#### 【0015】

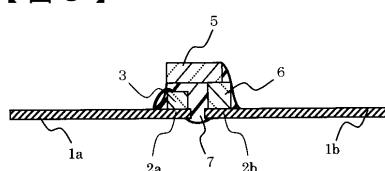

このような光半導体装置は、例えば以下のように形成される。先ず、図2-aに断面図を、図2-bに上面図を示すように、プレス、エッチングなどにより発光側と受光側が所定の間隔となるように形成され、一体化されたリードフレーム1a、1bを用い、ベッド2a上に発光素子3を、ベッド2b上にMOSFET6を夫々載置、接続する。そして、MOSFET6上に、受光素子5をその一部が発光素子3と対向するように載置する。

#### 【0016】

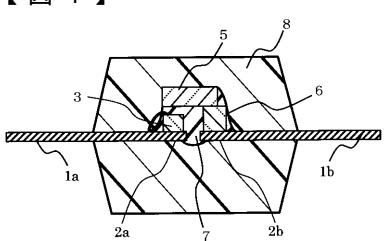

次いで、図3に示すように、発光素子3、受光素子5を光透過性の1次封止樹脂7で封止し、光の伝達経路を形成する。そして、図4に示すように、これらを光遮断性の2次封止樹脂8で封止する。さらに、封止樹脂8から露出したリードフレーム1a、1bを、実装用にフォーミングし、図1に示す光半導体装置が形成される。

#### 【0017】

このような光半導体素子においては、従来平面配置されていた受光素子とMOSFETを立体的に配置することができ、パッケージの小型化を実現することが可能となる。さらに、発光素子と受光素子は、発光側、受光側が同一平面上に配置されたリードフレーム上に搭載されるため、従来の1次封止前の、発光側、受光側リードフレームを対向・保持する接合工程を省略することができ、工程数の削減が可能となる。また、高さ方向の位置制御も容易となり、さらに発光側と受光側が一体化したリードフレームを用いているため、フレーム方向の位置ずれが抑制され、特性のばらつきも抑えられる。

#### 【0018】

##### (実施形態2)

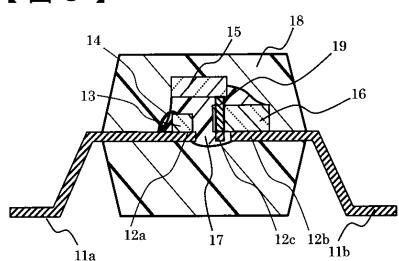

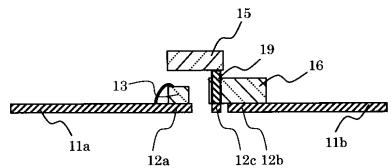

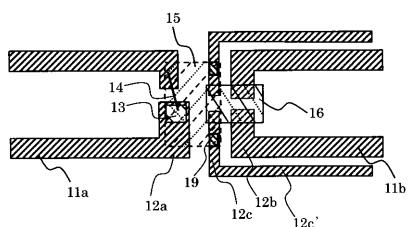

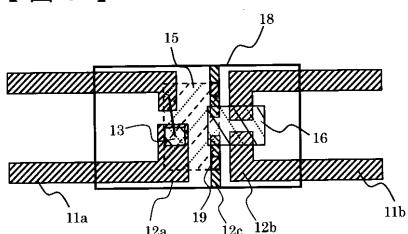

図5に本実施形態の光半導体装置を示す。図に示すように、実施形態1と同様に、発光側リードフレーム11aのベッド12a(発光側素子搭載部)上に発光素子13が載置・接続され、ワイヤー14によりボンディングされている。そしてこの発光素子13と対向するように受光素子15が配置されている。受光素子15は、受光側リードフレーム11bのベッド12b(受光側素子搭載部)上に載置・接続されたMOSFET16上で、ベッド12a、ベッド12b間に設けられた導電性のベッド12c上に載置された導電性のダミーベレット19により支持されている。ベッド12cはMOSFET16と接続されており、ダミーベレット19を経て受光素子15と接続されている。そして、実施形態1と同様に、発光素子13と受光素子15は光透過性の1次封止樹脂17で封止され、さらに光遮断性の2次封止樹脂18で封止されている。

#### 【0019】

このような光半導体装置において、実施形態1と同様に、リードフレーム11aより外部からの電気信号が入力され、発光素子13が発光し、1次封止樹脂17を介して受光素子15に光信号が伝達される。そして、受光素子15において電気信号に変換され、MOSFET16を経て、リードフレーム11bより出力される。

#### 【0020】

このような光半導体装置は、例えば以下のように形成される。先ず、図6-aに断面図を、図6-bに上面図を示すように、実施形態1と同様に、リードフレーム11a、11bの、ベッド12a上に発光素子13を、ベッド12b上にMOSFET16を夫々載置・接続する。一方、受光側リードフレーム11bの外周を囲むように形成されたフレーム12c'のベッド12cと、MOSFET16を接続し、これを挟むように、ベッド12

10

20

30

40

50

c 上にダミーペレット 19 を載置する。そして、ダミーペレット 19 上に、受光素子 15 を載置、接続し、発光素子 13 と対向させる。尚、リードフレーム 11a、11b、フレーム 12c' は、プレス、エッチングなどにより形成され、一体化されている。

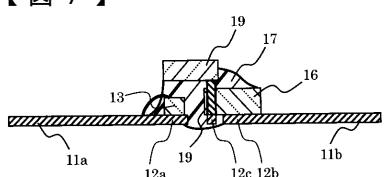

#### 【0021】

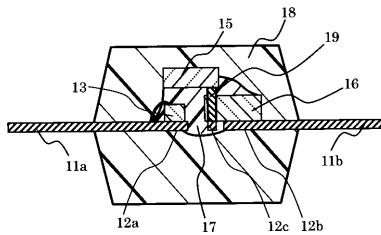

次いで、図 7 に示すように、発光素子 13、受光素子 15 を光透過性の 1 次封止樹脂 17 で封止し、光の伝達経路を形成する。そして、図 8 に示すように、これらを光遮断性の 2 次封止樹脂 18 で封止する。

#### 【0022】

次いで、図 9 に示すように、フレーム 12c' の封止樹脂 18 から露出した部分を切断、除去する。そして、封止樹脂 18 から露出したリードフレーム 11a、11b を、実装用にフォーミングし、図 5 に示す光半導体装置が形成される。

#### 【0023】

本実施形態において、ダミーペレットの材料を特に規定していないが、内部素子のデザインにより、セラミックス系、シリコン系、金属系等、導電性、非導電性の種々の材料を選択することが可能である。

#### 【0024】

尚、これら実施形態において、発光側、受光側が一体化されたリードフレームが用いられているが、必ずしも一体化されていなくてもよく、夫々形成されたものを同一平面上に位置制御して配置しても良い。また、HOPP 状フレームを用いて、連続的に形成することも可能である。

#### 【0025】

また、ベッド上における各素子の接続方法は特に規定されないが、樹脂接合、共晶接合や、FCB 等適宜選択することができる。

#### 【0026】

これら実施形態においては、MOSFET を搭載しているが、MOSFET を有さない光半導体素子においても、ダミーペレット上に受光素子を載置することで、工程数の削減や、特性のばらつきの抑制、パッケージの小型化等の効果を得ることができる。そして、ダミーペレットは、樹脂封止後においても必ずしもベッド上に固定されている必要はなく、樹脂封止後にベッドが除去されていてもよい。

#### 【0027】

尚、本発明は、上述した実施形態に限定されるものではない。その他要旨を逸脱しない範囲で種々変形して実施することができる。

#### 【図面の簡単な説明】

#### 【0028】

【図 1】本発明の一実施態様の光半導体装置を示す図。

【図 2-a】本発明の一実施態様の光半導体装置の製造工程を示す図。

【図 2-b】本発明の一実施態様の光半導体装置の製造工程を示す図。

【図 3】本発明の一実施態様の光半導体装置の製造工程を示す図。

【図 4】本発明の一実施態様の光半導体装置の製造工程を示す図。

【図 5】本発明の一実施態様の光半導体装置を示す図。

【図 6-a】本発明の一実施態様の光半導体装置の製造工程を示す図。

【図 6-b】本発明の一実施態様の光半導体装置の製造工程を示す図。

【図 7】本発明の一実施態様の光半導体装置の製造工程を示す図。

【図 8】本発明の一実施態様の光半導体装置の製造工程を示す図。

【図 9】本発明の一実施態様の光半導体装置の製造工程を示す図。

【図 10】従来の光半導体装置を示す図。

【図 11】従来の光半導体装置の製造工程を示す図。

【図 12】従来の光半導体装置の製造工程を示す図。

【図 13】従来の光半導体装置の製造工程を示す図。

【図 14】従来の光半導体装置の製造工程を示す図。

## 【符号の説明】

## 【0029】

- 1a、1b、11a、11b、101a、101b リードフレーム

2a、2b、12a、12b、12c、102a、102b ベッド

12c' フレーム

3、13、103 発光素子

4、14、104 ワイヤー<sup>10</sup>

5、15、105 受光素子

6、16、106 M O S F E T

7、17、107 一次封止樹脂

8、18、108 二次封止樹脂

19 ダミーペレット

【図1】

【図2-a】

【図2-b】

【図3】

【図4】

【図5】

【図 6 - a】

【図 6 - b】

【図 7】

【図 8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図 14】