(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2013년03월05일

(11) 등록번호 10-1239162

(24) 등록일자 2013년02월26일

- (51) 국제특허분류(Int. Cl.)

*G09G 3/30* (2006.01) *G09G 3/32* (2006.01)

*G09G 3/20* (2006.01) *H05B 33/12* (2006.01)

- (21) 출원번호 10-2007-7013918

- (22) 출원일자(국제) 2005년11월28일

심사청구일자 2010년11월17일

- (85) 번역문제출일자 2007년06월20일

- (65) 공개번호 10-2007-0091146

- (43) 공개일자 2007년09월07일

- (86) 국제출원번호 PCT/JP2005/022228

- (87) 국제공개번호 WO 2006/059737

국제공개일자 2006년06월08일

(30) 우선권주장

JP-P-2004-00347502 2004년11월30일 일본(JP)

(56) 선행기술조사문헌

KR1020040094628 A\*

KR1020030030846 A\*

KR1020010055654 A\*

JP2004325885 A\*

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 16 항

심사관 : 조기덕

(54) 발명의 명칭 표시장치와 그 구동방법, 반도체장치, 및 전자기기

**(57) 요 약**

구동 트랜지스터에 p형 트랜지스터를 채용한 경우, 단극성 트랜지스터만으로 구성되는 표시 패널을 제조하는 것은 곤란하다. 표시 패널에 형성되는 회로를 단극성 트랜지스터로 구성하면 제조 공정을 줄이고, 코스트 다운을 꾀할 수 있다. 본 발명에서는, 발광소자를 구동하는 구동 트랜지스터로서 n형 트랜지스터를 사용하고, 구동 트랜지스터와 발광소자로 소스 폴로워 회로를 구성한다.

**대 표 도**

## 특허청구의 범위

### 청구항 1

삭제

### 청구항 2

삭제

### 청구항 3

삭제

### 청구항 4

삭제

### 청구항 5

발광소자와,

상기 발광소자를 구동하는 구동 트랜지스터와,

용량소자와,

제1 스위치와,

제2 스위치와,

제3 스위치와,

아날로그 전위가 입력되는 신호선과,

전원선을 포함하는 화소를 구비한 반도체장치로서,

상기 구동 트랜지스터의 게이트 단자는 상기 용량소자를 통해 상기 신호선에 접속되고,

상기 구동 트랜지스터의 소스 단자 및 드레인 단자 중의 한쪽은 상기 발광소자의 화소전극에 접속되고,

상기 구동 트랜지스터의 소스 단자 및 드레인 단자 중의 다른 한쪽은 상기 제1 스위치 및 상기 제 3 스위치를 통해 상기 전원선에 접속되고, 상기 제2 스위치 및 상기 제 3 스위치를 통해 상기 게이트 단자에 접속되는 반도체장치.

### 청구항 6

발광소자와,

상기 발광소자를 구동하는 구동 트랜지스터와,

용량소자와,

제1 스위치와,

제2 스위치와,

제3 스위치와,

아날로그 전위가 입력되는 신호선과,

전원선과,

배선을 포함하는 화소를 구비한 반도체장치로서,

상기 구동 트랜지스터의 게이트 단자는 상기 용량소자를 통해 상기 신호선에 접속되고,

상기 제 1 스위치와 상기 제 3 스위치의 양쪽은 상기 발광소자가 발광하는 기간 동안 오프 상태이고,

상기 구동 트랜지스터의 소스 단자 및 드레인 단자 중의 한쪽은 상기 발광소자의 화소전극에 접속되고, 상기 제 3 스위치를 통해 상기 배선에 접속되고,

상기 구동 트랜지스터의 소스 단자 및 드레인 단자 중의 다른 한쪽은 상기 제1 스위치를 통해 상기 전원선에 접속되고, 상기 제2 스위치를 통해 상기 구동 트랜지스터의 게이트 단자에 접속되는 반도체장치.

#### 청구항 7

발광소자와,

상기 발광소자를 구동하는 구동 트랜지스터와,

용량소자와,

제1 스위치와,

제2 스위치와,

제3 스위치와,

아날로그 전위가 입력되는 신호선과,

배선과,

전원선을 포함하는 화소를 구비한 반도체장치로서,

상기 구동 트랜지스터의 게이트 단자는 상기 용량소자의 한쪽 전극에 접속되고, 상기 제 3 스위치를 통해 상기 배선에 접속되며,

상기 용량소자의 다른 쪽 전극은 상기 신호선에 접속되고,

상기 구동 트랜지스터의 소스 단자 및 드레인 단자 중의 한쪽은 상기 발광소자의 화소전극에 접속되고,

상기 구동 트랜지스터의 소스 단자 및 드레인 단자 중의 다른 한쪽은 상기 제1 스위치를 통해 상기 전원선에 접속되고, 상기 제2 스위치를 통해 상기 구동 트랜지스터의 게이트 단자에 접속되는 반도체장치.

#### 청구항 8

제 5항 내지 제 7항 중 어느 한 항에 있어서,

상기 제1 스위치와 상기 제2 스위치는 n형 트랜지스터인 반도체장치.

#### 청구항 9

제 5항 내지 제 7항 중 어느 한 항에 있어서,

상기 제1 스위치는 p형 트랜지스터이고, 상기 제2 스위치는 n형 트랜지스터인 반도체장치.

#### 청구항 10

제 5항 내지 제 7항 중 어느 한 항에 있어서,

상기 전원선에 공급되는 전위는 RGB 각 요소의 화소에 따라 다른 반도체장치.

#### 청구항 11

제 5항 내지 제 7항 중 어느 한 항에 있어서,

복수의 상기 화소는 멘타 배치된 반도체장치.

**청구항 12**

제 5항 내지 제 7항 중 어느 한 항에 따른 반도체장치를 구비한 전자기기.

**청구항 13**

제 12항에 있어서,

상기 전자기기는 디스플레이, 비디오 카메라 등의 카메라, 모바일 컴퓨터 등의 컴퓨터, 화상재생장치, 고글형 디스플레이, 또는 휴대전화기인 전자기기.

**청구항 14**

제 5항 내지 제 7항 중 어느 한 항에 있어서,

상기 전원선의 전위는 상기 발광소자의 대향전극에 공급되는 전위보다 높은 반도체장치.

**청구항 15**

삭제

**청구항 16**

삭제

**청구항 17**

제 5항 내지 제 7항 중 어느 한 항에 있어서,

상기 구동 트랜지스터는 n형 트랜지스터인 반도체장치.

**청구항 18**

삭제

**청구항 19**

삭제

**청구항 20**

용량소자의 한쪽 전극에 접속된 신호선에 아날로그 신호 전위를 공급하는 단계로서, 상기 용량소자의 다른 쪽 전극은 구동 트랜지스터의 게이트 단자에 접속되어 있는 단계와,

상기 구동 트랜지스터의 게이트 단자와 전원선 사이의 부분을 제 1 스위치와 제 2 스위치에 의해 도통으로 하고, 상기 구동 트랜지스터의 소스 단자 및 드레인 단자 중의 한쪽과 상기 전원선 사이의 부분을 제 3 스위치에 의해 비도통으로 하는 단계와,

상기 구동 트랜지스터의 게이트 단자와 상기 전원선 사이의 상기 부분을 상기 제 1 스위치에 의해 비도통으로 하고, 상기 구동 트랜지스터의 게이트 단자와 상기 구동 트랜지스터의 소스 단자 및 드레인 단자 중의 한쪽 사이의 부분을 상기 제 2 스위치 및 상기 제 3 스위치에 의해 도통으로 하는 단계와,

상기 구동 트랜지스터의 게이트 단자와 상기 구동 트랜지스터의 소스 단자 및 드레인 단자 중의 한쪽 사이의 상기 부분을 상기 제 2 스위치에 의해 비도통으로 하는 단계와,

상기 구동 트랜지스터의 게이트 단자의 전위와 상기 아날로그 신호 전위 사이의 전위차를 상기 용량소자에 의해 유지하는 단계와,

상기 구동 트랜지스터의 소스 단자 및 드레인 단자 중의 한쪽과 상기 전원선 사이의 상기 부분을 상기 제 1 스위치 및 상기 제 3 스위치에 의해 도통으로 하고, 발광 기간에 상기 아날로그 신호 전위보다 높은 전위를 상기

신호선에 공급하는 단계를 포함하는 반도체장치의 구동방법.

### 청구항 21

삭제

### 청구항 22

아날로그 신호를 화소에 기록하는 기간에 아날로그 신호 전위를 신호선에 공급하는 반도체 장치의 구동방법으로서,

상기 아날로그 신호의 기록은,

전원선과 구동 트랜지스터의 소스 단자 및 드레인 단자 중의 한쪽 사이에 설치된 제 1 스위치와 상기 구동 트랜지스터의 게이트 단자와 상기 구동 트랜지스터의 소스 단자 및 드레인 단자 중의 한쪽과의 사이에 설치된 제 2 스위치를 오프 상태로 하고, 배선과 상기 구동 트랜지스터의 게이트 단자 사이에 설치된 제 3 스위치를 온 상태로 하는 단계와,

상기 제 1 스위치가 오프 상태인 기간 동안 상기 제 3 스위치를 오프 상태로 하고 상기 제 2 스위치를 온 상태로 하는 단계와,

상기 제 2 스위치를 오프 상태로 하는 단계를 포함하고,

상기 구동 트랜지스터의 소스 단자 및 드레인 단자 중의 다른 한쪽에 발광소자가 접속되고,

상기 신호선과 상기 구동 트랜지스터의 게이트 단자의 사이에 용량소자가 설치되고,

상기 아날로그 신호 전위보다 높은 전위가 상기 발광소자가 발광하는 기간에 상기 신호선에 공급되는 반도체 장치의 구동방법.

### 청구항 23

제 20항 또는 제 22항에 있어서,

상기 아날로그 신호 전위보다 높은 전위는 삼각파 전위인 반도체장치의 구동방법.

### 청구항 24

제 20항 또는 22항에 있어서,

상기 구동 트랜지스터는 n형 트랜지스터인 반도체장치의 구동방법.

### 청구항 25

제 20항 또는 제 22항에 있어서,

상기 반도체장치는 디스플레이, 비디오 카메라 등의 카메라, 모바일 컴퓨터 등의 컴퓨터, 화상재생장치, 고글형 디스플레이, 또는 휴대전화기로 이루어진 군에서 선택된 전자기기에 내장되는 반도체장치의 구동방법.

## 명세서

### 기술 분야

[0001]

본 발명은 부하에 공급하는 전류를 트랜지스터로 제어하는 기능을 구비한 반도체장치에 관한 것으로, 특히 전류에 의해 휘도가 변화되는 전류구동형 표시소자로 형성된 화소와, 그 신호선 구동회로를 포함한 표시장치에 관한 것이다. 또한, 본 발명은 그 구동방법에 관한 것이다. 또한, 본 발명은 그 표시장치를 표시부에 가지는 전자기기에 관한 것이다.

## 배경기술

[0002] 최근, 화소가 발광 다이오드(LED) 등의 표시소자로 구성된 소위 자발광형 표시장치가 주목을 받고 있다. 이러한 자발광형 표시장치에 사용되는 표시소자로는, 유기발광 다이오드(OLED, 유기EL소자, 일렉트로루미네스цен스(electroluminescence:EL)소자 등이라고도 한다)가 주목을 받고 있고, 유기 EL디스플레이 등에 사용되게 되었다. OLED 등의 표시소자는 자발광형이므로, 액정 모니터에 비해 화소의 시인성이 높고, 백라이트를 필요로 하지 않고, 응답 속도가 빠른 이점이 있다. 또한, 표시소자의 회도는, 표시소자를 흐르는 전류치에 의해 제어된다.

[0003] 이러한 표시장치의 발광 계조를 제어하는 구동방식에는, 디지털 방식과 아날로그 방식이 있다. 디지털 방식에서는, 디지털 제어로 표시소자를 온/오프 상태로 하고, 발광 시간을 제어해서 계조를 표현한다. 이 방법에는 각 화소의 회도의 균일성이 뛰어나다는 장점이 있는 반면, 주파수를 높일 필요가 있어 소비 전력이 커지게 된다. 한편, 아날로그 방식에는, 표시소자의 발광 강도를 아날로그 제어하는 방식과, 표시소자의 발광 시간을 아날로그 제어하는 방식이 있다. 발광 강도를 아날로그 제어하는 방식은, 각 화소의 박막 트랜지스터(이하, TFT라고도 한다)의 특성의 편차의 영향을 받기 쉽고, 각 화소의 발광에도 편차가 생긴다. 한편, 발광 시간을 아날로그 제어하여, 각 화소의 발광의 균일성이 우수한 아날로그 시간계조방식, 및 그 아날로그 시간계조방식의 표시장치가 비특허문헌 1에 기재되어 있다(비특허문헌 1 참조).

[0004] 즉, 비특허문헌 1에 기재된 표시장치의 화소에서는, 표시소자와 그 표시소자를 구동하는 트랜지스터로 인버터를 구성한다. 구동 트랜지스터의 게이트 단자는 인버터의 입력 단자에 해당하고, 표시소자의 양극은 인버터의 출력 단자에 해당한다. 화소에 영상신호전압을 기록할 때에는, 인버터를 온과 오프의 중간으로 설정한다. 그리고, 발광 기간에는 화소에 삼각파전압을 입력함으로써 인버터의 출력을 제어한다. 즉, 표시소자의 양극에 공급되는 전위가 되는 인버터의 출력을 제어함으로써, 표시소자의 발광/비발광을 제어한다.

[0005] [비특허문헌 1] SID 04 DIGEST P1394 ~ P1397

### 발명의 상세한 설명

[0006] 전술한 비특허문헌 1에 기재된 표시장치에서는, p형 트랜지스터가 표시소자를 구동하는 구동 트랜지스터로 사용된다.

[0007] 이 경우, p형 트랜지스터는 오프 전류가 커지는 경향이 있으므로, 화소 내의 스위칭용 트랜지스터에는 n형 트랜지스터가 필요해진다. 그러면, p형 트랜지스터만으로 화소를 구성하기는 어려워진다. 따라서 구동 트랜지스터에 p형 트랜지스터를 채용하면, 단극성 트랜지스터만으로 구성되는 표시 패널을 제조하기가 어려워진다.

[0008] 한편, 유기 EL디스플레이나 FED(필드 이미션 디스플레이) 등의 표시장치의 수요는 증가해왔다. 그런데 상당히 많은 수의 TFT를 제조할 필요가 있으므로, 수율 등의 측면으로부터 그 제조 비용을 충분히 낮추기는 어렵다.

[0009] 표시장치의 비용에는 표시 패널의 제조 공정 수가 직접적인 영향을 미치기 때문에, 가능한 한 적은 공정으로 제조하는 것이 바람직하다. 따라서, 표시 패널에 형성되는 TFT를 n형 또는 p형 중 어느 한쪽의 도전형만으로 구성하는 것이 시도되었다. 이 방법에 의해, 이온 도핑 공정의 일부를 생략할 수 있고, 포토마스크의 매수도 더욱 줄일 수 있다. 그 결과, 표시장치의 코스트 다운을 꾀할 수 있다.

[0010] 상기 측면으로부터, 화소를 구성하는 회로가 형성된 반도체장치에 있어서, 그 제조 비용이 절감된 반도체장치를 제공하는 것을 과제로 한다.

[0011] 또한, 화소가 포함된 표시장치에 있어서, 그 제조 비용이 절감된 표시장치를 제공하는 것을 과제로 한다.

[0012] 또한, 그 표시장치의 구동방법을 제공하는 것을 과제로 한다.

[0013] 또한, 상기 표시장치를 표시부에 가지는 전자기기를 제공하는 것을 과제로 한다.

[0014] 화소를 구성하는 회로에 있어서, 상기 회로는 표시소자를 구동하는 구동 트랜지스터와, 아날로그의 전위가 입력되는 신호선과, 구동 트랜지스터의 게이트 단자의 전위와 신호선의 전위 사이의 전위차를 유지하는 유지수단과, 구동 트랜지스터의 드레인 단자와 게이트 단자 사이를 도통 또는 비도통으로 하는 전환 수단을 구비하고, 구동 트랜지스터로서 n형 트랜지스터를 사용한다.

[0015] 화소를 구성하는 회로에 있어서, 상기 회로는 표시소자와, 표시소자를 구동하는 구동 트랜지스터와, 아날로그의 전위가 입력되는 신호선과, 구동 트랜지스터의 게이트 단자의 전위와 신호선의 전위 사이의 전위차를 유지하는

유지 수단과, 구동 트랜지스터의 드레인 단자와 게이트 단자 사이를 도통 또는 비도통으로 하는 전환 수단을 구비하고, 상기 구동 트랜지스터와 상기 표시소자로 소스 풀로워를 구성한다.

[0016] 본 발명의 반도체장치는 화소를 구성하는 회로를 포함하고, 상기 회로는 표시소자를 구동하는 구동 트랜지스터와, 아날로그의 전위가 입력되는 신호선과, 상기 구동 트랜지스터의 게이트-소스간 전압을 역치전압으로 하는 설정 수단과, 상기 신호선에 입력된 전위와 상기 구동 트랜지스터의 게이트 단자의 전위 사이의 전위차를 유지하는 유지 수단을 가지고, 상기 구동 트랜지스터는 n형 트랜지스터다.

[0017] 또한, 본 발명의 반도체장치는 화소를 구성하는 회로를 포함하고, 상기 회로는 표시소자를 구동하는 구동 트랜지스터와, 아날로그의 전위가 입력되는 신호선과, 상기 구동 트랜지스터의 게이트 단자의 전위와 상기 신호선의 전위 사이의 전위차를 유지하는 유지 수단과, 상기 구동 트랜지스터의 드레인 단자와 게이트 단자 사이의 부분을 도통 또는 비도통으로 하는 전환 수단을 가지고, 상기 구동 트랜지스터는 n형 트랜지스터다.

[0018] 또한, 본 발명의 반도체장치는 화소를 구성하는 회로를 포함하고, 상기 회로는 표시소자를 구동하는 구동 트랜지스터와, 용량소자와, 아날로그의 전위가 입력되는 신호선과, 상기 구동 트랜지스터의 드레인 단자와 게이트 단자 사이의 부분을 도통 또는 비도통으로 하는 전환 수단을 가지고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 구동 트랜지스터의 게이트 단자는 용량소자를 통해 상기 신호선에 접속된다.

[0019] 또한, 본 발명의 반도체장치는 화소를 구성하는 회로를 포함하고, 상기 회로는 표시소자를 구동하는 구동 트랜지스터와, 용량소자와, 아날로그의 전위가 입력되는 신호선과, 상기 구동 트랜지스터의 드레인 단자와 게이트 단자 사이의 부분을 도통 또는 비도통으로 하는 전환 수단을 가지고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 구동 트랜지스터의 게이트 단자는 용량소자를 통해 상기 신호선에 접속되고, 상기 구동 트랜지스터의 소스 단자는 상기 표시소자의 양극이 되는 화소전극에 접속된다.

[0020] 또한, 본 발명의 반도체장치는 화소를 구성하는 회로를 포함하고, 상기 회로는 표시소자를 구동하는 구동 트랜지스터와, 용량소자와, 스위치와, 아날로그의 전위가 입력되는 신호선을 가지고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 구동 트랜지스터의 게이트 단자는 용량소자를 통해 상기 신호선에 접속되고, 상기 구동 트랜지스터의 드레인 단자는 상기 게이트 단자와 상기 스위치를 통해 접속된다.

[0021] 또한, 본 발명의 반도체장치는 화소를 구성하는 회로를 포함하고, 상기 회로는 표시소자를 구동하는 구동 트랜지스터와, 용량소자와, 스위치와, 아날로그의 전위가 입력되는 신호선을 가지고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 구동 트랜지스터의 게이트 단자는 용량소자를 통해 상기 신호선에 접속되고, 상기 구동 트랜지스터의 소스 단자는 상기 표시소자의 양극이 되는 화소전극에 접속되고, 상기 구동 트랜지스터의 드레인 단자는 상기 게이트 단자와 상기 스위치를 통해 접속된다.

[0022] 또한, 본 발명의 반도체장치는 화소를 구성하는 회로를 포함하고, 상기 회로는 표시소자를 구동하는 구동 트랜지스터와, 용량소자와, 제1 스위치와, 제2 스위치와, 아날로그의 전위가 입력되는 신호선과, 전원선을 가지고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 구동 트랜지스터의 게이트 단자는 용량소자를 통해 상기 신호선에 접속되고, 상기 구동 트랜지스터의 제1 단자는 상기 표시소자의 화소전극에 접속되고, 상기 구동 트랜지스터의 제2 단자는 상기 전원선과 상기 제1 스위치를 통해 접속되고 상기 게이트 단자와 상기 제2 스위치를 통해 접속된다.

[0023] 또한, 본 발명의 반도체장치는 화소를 구성하는 회로를 포함하고, 상기 회로는 표시소자를 구동하는 구동 트랜지스터와, 용량소자와, 제1 스위치와, 제2 스위치와, 아날로그의 전위가 입력되는 신호선과, 전원선을 가지고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 구동 트랜지스터의 게이트 단자는 용량소자를 통해 상기 신호선에 접속되고, 상기 구동 트랜지스터의 소스 단자는 상기 표시소자의 양극이 되는 화소전극에 접속되고, 상기 구동 트랜지스터의 드레인 단자는 상기 전원선과 상기 제1 스위치를 통해 접속되고 상기 게이트 단자와 상기 제2 스위치를 통해 접속된다.

[0024] 또한, 본 발명의 반도체장치는 화소를 구성하는 회로를 포함하고, 상기 회로는 표시소자를 구동하는 구동 트랜지스터와, 용량소자와, 제1 스위치와, 제2 스위치와, 제3 스위치와, 아날로그의 전위가 입력되는 신호선과, 전원선과, 배선을 가지고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 구동 트랜지스터의 게이트 단자는 용량소자를 통해 상기 신호선에 접속되고, 상기 구동 트랜지스터의 제1 단자는 상기 표시소자의 화소전극에 접속되고 제3 스위치를 통해 상기 배선과 접속되고, 상기 구동 트랜지스터의 제2 단자는 상기 전원선과 상기 제1 스위치를 통해 접속되고 상기 게이트 단자와 상기 제2 스위치를 통해 접속된다.

[0025] 또한, 본 발명의 반도체장치는 화소를 구성하는 회로를 포함하고, 상기 회로는 표시소자를 구동하는 구동 트랜

지스터와, 용량소자와, 제1 스위치와, 제2 스위치와, 제3 스위치와, 제4 스위치와, 아날로그 영상신호전위가 입력되는 제1 신호선과, 규칙적인 패형의 아날로그 전위가 입력되는 제2 신호선과, 전원선을 가지고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 구동 트랜지스터의 게이트 단자는 용량소자의 한쪽 전극과 접속되고, 상기 용량소자의 다른 쪽 전극은 상기 제1 신호선과 상기 제3 스위치를 통해 접속되고 상기 제2 신호선과 상기 제4 스위치를 통해 접속되고, 상기 구동 트랜지스터의 제1 단자는 상기 표시소자의 화소전극에 접속되고, 상기 구동 트랜지스터의 제2 단자는 상기 전원선과 상기 제1 스위치를 통해 접속되고 상기 게이트 단자와 상기 제2 스위치를 통해 접속된다.

[0026] 또한, 본 발명의 반도체장치는 화소를 구성하는 회로를 포함하고, 상기 회로는 표시소자를 구동하는 구동 트랜지스터와, 용량소자와, 제1 스위치와, 제2 스위치와, 제3 스위치와, 제4 스위치와, 아날로그 영상신호전위가 입력되는 제1 신호선과, 규칙적인 패형의 아날로그 전위가 입력되는 제2 신호선과, 전원선을 가지고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 구동 트랜지스터의 게이트 단자는 용량소자의 한쪽 전극과 접속되고, 상기 용량소자의 다른 쪽 전극은 상기 제1 신호선과 상기 제3 스위치를 통해 접속되고 상기 제2 신호선과 상기 제4 스위치를 통해 접속되고, 상기 구동 트랜지스터의 소스 단자는 상기 표시소자의 양극이 되는 화소전극에 접속되고, 상기 구동 트랜지스터의 드레인 단자는 상기 전원선과 상기 제1 스위치를 통해 접속되고 상기 게이트 단자와 상기 제2 스위치를 통해 접속된다.

[0027] 또한, 본 발명의 반도체장치는 상기 구성으로 되어 있고, 상기 제1 스위치 및 제2 스위치는 n형 트랜지스터다.

[0028] 또한, 본 발명의 반도체장치는 상기 구성으로 되어 있고, 상기 제1 스위치는 p형 트랜지스터이며, 상기 제2 스위치는 n형 트랜지스터다.

[0029] 또한, 본 발명의 반도체장치는 상기 구성으로 되어 있고, 상기 화소를 구성하는 회로의 전원선에 공급되는 전위는 RGB 각 요소의 화소에 따라 다르다.

[0030] 또한, 본 발명의 반도체장치는 상기 구성으로 되어 있고, 상기 화소를 구성하는 각 회로는 헬타 배치되어 있다.

[0031] 또한, 표시소자와 표시소자의 구동을 제어하는 구동 트랜지스터를 가지는 화소에 있어서, 구동 트랜지스터로서 n형 트랜지스터를 사용한다.

[0032] 또한, 구동 트랜지스터의 소스 단자를 표시소자의 양극에 접속한다.

[0033] 본 발명의 표시장치는, 표시소자와, 상기 표시소자를 구동하는 트랜지스터와, 용량소자와, 아날로그의 전위가 입력되는 신호선과, 상기 구동 트랜지스터의 드레인 단자와 게이트 단자 사이의 부분을 도통 또는 비도통으로 하는 전환 수단을 구비한 화소를 가지고, 상기 구동 트랜지스터의 게이트 단자는 상기 용량소자를 통해 상기 신호선과 접속되고, 상기 표시소자와 상기 구동 트랜지스터는 소스 폴로워를 구성하고, 상기 구동 트랜지스터의 게이트 단자는 상기 소스 폴로워의 입력 단자이며, 상기 구동 트랜지스터의 소스 단자는 소스 폴로워의 출력 단자다.

[0034] 본 발명의 표시장치는, 표시소자와, 상기 표시소자를 구동하는 구동 트랜지스터와, 아날로그의 전위가 입력되는 신호선과, 상기 구동 트랜지스터의 게이트-소스간 전압을 역치전압으로 하는 설정 수단과, 상기 신호선에 입력된 전위와 상기 구동 트랜지스터의 게이트 단자의 전위 사이의 전위차를 유지하는 유지 수단을 구비한 화소를 가지고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 구동 트랜지스터의 소스 단자는 상기 표시소자의 양극과 접속된다.

[0035] 또한, 본 발명의 표시장치는, 표시소자와, 상기 표시소자를 구동하는 구동 트랜지스터와, 아날로그의 전위가 입력되는 신호선과, 상기 구동 트랜지스터의 게이트 단자의 전위와 상기 신호선의 전위 사이의 전위차를 유지하는 유지 수단과, 상기 구동 트랜지스터의 드레인 단자와 게이트 단자 사이의 부분을 도통 또는 비도통으로 하는 전환 수단을 구비한 화소를 가지고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 구동 트랜지스터의 소스 단자는 상기 표시소자의 양극과 접속된다.

[0036] 또한, 본 발명의 표시장치는, 표시소자와, 상기 표시소자를 구동하는 구동 트랜지스터와, 용량소자와, 아날로그의 전위가 입력되는 신호선과, 상기 구동 트랜지스터의 드레인 단자와 게이트 단자 사이의 부분을 도통 또는 비도통으로 하는 전환 수단을 구비한 화소를 가지고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 구동 트랜지스터의 게이트 단자는 용량소자를 통해 상기 신호선에 접속되고, 상기 구동 트랜지스터의 소스 단자는 상기 표시소자의 양극에 접속된다.

[0037] 또한, 본 발명의 표시장치는, 표시소자와, 상기 표시소자를 구동하는 구동 트랜지스터와, 용량소자와,

스위치와, 아날로그의 전위가 입력되는 신호선을 구비한 화소를 가지고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 구동 트랜지스터의 게이트 단자는 용량소자를 통해 상기 신호선에 접속되고, 상기 구동 트랜지스터의 소스 단자는 상기 표시소자의 양극에 접속되고, 상기 구동 트랜지스터의 드레인 단자는 상기 게이트 단자와 상기 스위치를 통해 접속된다.

[0038] 또한, 본 발명의 표시장치는, 표시소자와, 상기 표시소자를 구동하는 구동 트랜지스터와, 용량소자와, 제1 스위치와, 제2 스위치와, 아날로그의 전위가 입력되는 신호선과, 전원선을 구비한 화소를 가지고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 구동 트랜지스터의 게이트 단자는 용량소자를 통해 상기 신호선에 접속되고, 상기 구동 트랜지스터의 제1 단자는 상기 표시소자의 화소전극에 접속되고, 상기 구동 트랜지스터의 제2 단자는 상기 전원선과 상기 제1 스위치를 통해 접속되고 상기 게이트 단자와 상기 제2 스위치를 통해 접속되고, 상기 전원선에는 상기 표시소자의 대향전극에 공급되는 전위보다 높은 전위가 공급된다.

[0039] 또한, 본 발명의 표시장치는, 표시소자와, 상기 표시소자를 구동하는 구동 트랜지스터와, 용량소자와, 제1 스위치와, 제2 스위치와, 아날로그의 전위가 입력되는 신호선과, 전원선을 구비한 화소를 가지고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 구동 트랜지스터의 게이트 단자는 용량소자를 통해 상기 신호선에 접속되고, 상기 구동 트랜지스터의 소스 단자는 상기 표시소자의 양극에 접속되고, 상기 구동 트랜지스터의 드레인 단자는 상기 전원선과 상기 제1 스위치를 통해 접속되고 상기 게이트 단자와 상기 제2 스위치를 통해 접속된다.

[0040] 또한, 본 발명의 표시장치는, 표시소자와, 상기 표시소자를 구동하는 구동 트랜지스터와, 용량소자와, 제1 스위치와, 제2 스위치와, 제3 스위치와, 아날로그의 전위가 입력되는 신호선과, 전원선과, 배선을 구비한 화소를 가지고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 구동 트랜지스터의 게이트 단자는 용량소자를 통해 상기 신호선에 접속되고, 상기 구동 트랜지스터의 제1 단자는 상기 표시소자의 화소전극과 접속되고 상기 배선과 제3 스위치를 통해 접속되고, 상기 구동 트랜지스터의 제2 단자는 상기 전원선과 상기 제1 스위치를 통해 접속되고 상기 게이트 단자와 상기 제2 스위치를 통해 접속된다.

[0041] 또한, 본 발명의 표시장치는, 표시소자와, 상기 표시소자를 구동하는 구동 트랜지스터와, 용량소자와, 제1 스위치와, 제2 스위치와, 제3 스위치와, 제4 스위치와, 아날로그 영상신호전위가 입력되는 제1 신호선과, 규칙적인 파형의 아날로그 전위가 입력되는 제2 신호선과, 전원선을 구비한 화소를 가지고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 구동 트랜지스터의 게이트 단자는 용량소자의 한쪽 전극과 접속되고, 상기 용량소자의 다른 쪽 전극은 상기 제1 신호선과 상기 제3 스위치를 통해 접속되고 상기 제2 신호선과 상기 제4 스위치를 통해 접속되고, 상기 구동 트랜지스터의 제1 단자는 상기 표시소자의 화소전극에 접속되고, 상기 구동 트랜지스터의 제2 단자는 상기 전원선과 상기 제1 스위치를 통해 접속되고 상기 게이트 단자와 상기 제2 스위치를 통해 접속되고, 상기 전원선에는 상기 표시소자의 대향전극에 공급되는 전위보다 높은 전위가 공급된다.

[0042] 또한, 본 발명의 표시장치는, 표시소자와, 상기 표시소자를 구동하는 구동 트랜지스터와, 용량소자와, 제1 스위치와, 제2 스위치와, 제3 스위치와, 제4 스위치와, 아날로그 영상신호전위가 입력되는 제1 신호선과, 규칙적인 파형의 아날로그 전위가 입력되는 제2 신호선과, 전원선을 구비한 화소를 가지고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 구동 트랜지스터의 게이트 단자는 용량소자의 한쪽 전극과 접속되고, 상기 용량소자의 다른 쪽 전극은 상기 제1 신호선과 상기 제3 스위치를 통해 접속되고 상기 제2 신호선과 상기 제4 스위치를 통해 접속되고, 상기 구동 트랜지스터의 소스 단자는 상기 표시소자의 양극에 접속되고, 상기 구동 트랜지스터의 드레인 단자는 상기 전원선과 상기 제1 스위치를 통해 접속되고 상기 게이트 단자와 상기 제2 스위치를 통해 접속된다.

[0043] 또한, 본 발명의 표시장치는 상기 구성으로 되어 있고, 상기 제1 스위치 및 제2 스위치는 n형 트랜지스터다.

[0044] 또한, 본 발명의 표시장치는 상기 구성으로 되어 있고, 상기 제1 스위치는 p형 트랜지스터이며, 상기 제2 스위치는 n형 트랜지스터다.

[0045] 또한, 본 발명의 표시장치는 상기 구성으로 되어 있고, 상기 화소의 전원선에 공급되는 전위는 RGB 각 요소의 화소에 따라 다르다.

[0046] 또한, 본 발명의 표시장치는, 표시소자와, 아날로그의 전위가 입력되는 신호선과, 구동 트랜지스터의 게이트-소스간 전압을 역치전압으로 하는 설정 수단과, 상기 신호선에 입력된 전위와 상기 구동 트랜지스터의 게이트 단자의 전위 사이의 전위차를 유지하는 유지 수단과, 상기 표시소자에 순방향 전류를 공급하기 위한 제1 경로와, 상기 표시소자에 역방향 전류를 공급하기 위한 제2 경로를 구비한 화소를 가지고, 상기 제1 경로에 상기 표시소자를 구동하는 상기 구동 트랜지스터를 구비하고, 상기 제2 경로에 전류의 공급을 제어하는 제어 수단을 구비하

고, 상기 구동 트랜지스터는 n형 트랜지스터다.

[0047] 또한, 본 발명의 표시장치는, 표시소자와, 아날로그의 전위가 입력되는 신호선과, 구동 트랜지스터의 게이트 단자의 전위와 상기 신호선의 전위 사이의 전위차를 유지하는 유지 수단과, 상기 구동 트랜지스터의 드레인 단자와 게이트 단자 사이의 부분을 도통 또는 비도통으로 하는 전환 수단과, 상기 표시소자에 순방향 전류를 공급하기 위한 제1 경로와, 상기 표시소자에 역방향 전류를 공급하기 위한 제2 경로를 가지고, 상기 제1 경로에 상기 표시소자를 구동하는 상기 구동 트랜지스터를 구비하고, 상기 제2 경로에 전류의 공급을 제어하는 제어 수단을 구비하고, 상기 구동 트랜지스터는 n형 트랜지스터다.

[0048] 또한, 본 발명의 표시장치는 상기 구성으로 되어 있고, 상기 화소는 엘타 배치되어 있다.

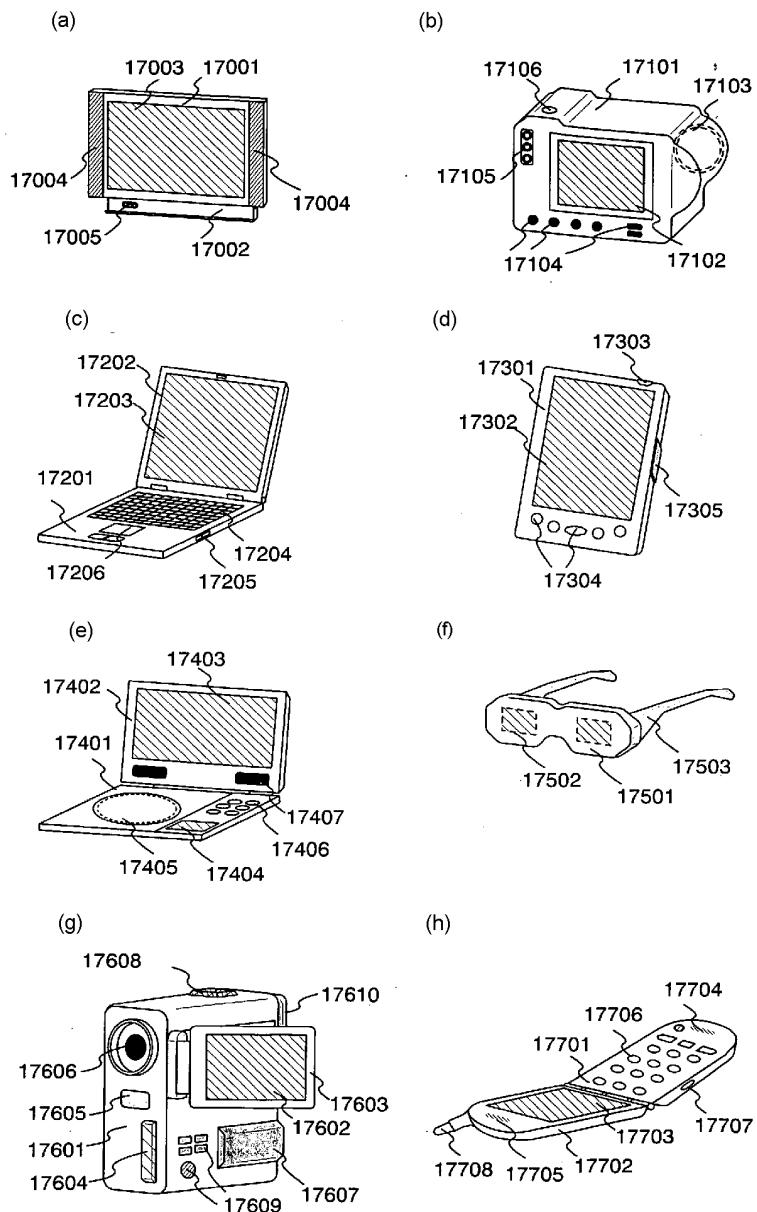

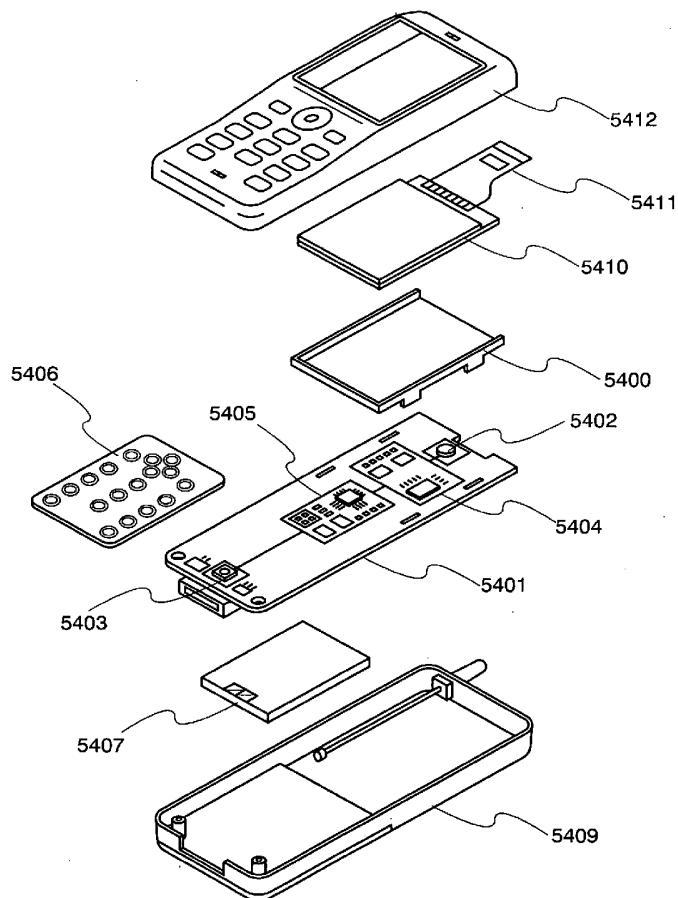

[0049] 또한 본 발명의 전자기기는, 상기 구성의 표시장치를 표시부에 가지는 디스플레이, 카메라, 컴퓨터, 모바일 컴퓨터, 화상재생장치, 고글형 디스플레이, 비디오 카메라 또는 휴대전화기다.

[0050] 본 발명의 표시장치의 구동방법에 있어서, 상기 표시장치는, 표시소자와, 상기 표시소자를 구동하는 구동 트랜지스터와, 아날로그의 전위가 입력되는 신호선과, 상기 구동 트랜지스터의 게이트 단자의 전위와 상기 신호선의 전위 사이의 전위차를 유지하는 유지 수단과, 상기 구동 트랜지스터의 드레인 단자와 게이트 단자 사이의 부분을 도통 또는 비도통으로 하는 전환 수단을 구비한 화소를 가지고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 구동 트랜지스터의 소스 단자는 상기 표시소자의 양극과 접속되고, 기록 기간에는 상기 신호선에 아날로그 신호 전위를 공급해서 상기 화소에 신호를 기록하고, 발광 기간에는 상기 신호선에 상기 아날로그 신호 전위를 공급해서 상기 구동 트랜지스터를 온 상태로 한다.

[0051] 또한, 본 발명의 표시장치의 구동방법에 있어서, 상기 표시장치는, 표시소자와, 상기 표시소자를 구동하는 구동 트랜지스터와, 아날로그의 전위가 입력되는 신호선과, 상기 구동 트랜지스터의 게이트 단자의 전위와 상기 신호선의 전위 사이의 전위차를 유지하는 유지 수단과, 상기 구동 트랜지스터의 드레인 단자와 게이트 단자 사이의 부분을 도통 또는 비도통으로 하는 전환 수단을 구비한 화소를 가지고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 구동 트랜지스터의 소스 단자는 상기 표시소자의 양극과 접속되고, 기록 기간에는, 상기 신호선에 아날로그 신호 전위를 공급하고, 상기 전환 수단에 의해 상기 구동 트랜지스터의 드레인 단자와 게이트 단자 사이의 부분을 도통 상태로 해서 상기 화소에 신호를 기록하고, 상기 전환 수단에 의해 상기 구동 트랜지스터의 드레인 단자와 게이트 단자 사이의 부분을 비도통으로 해서 상기 구동 트랜지스터의 게이트 단자의 전위와 상기 신호선의 전위 사이의 전위차를 상기 유지 수단에 의해 유지시키고, 발광 기간에는, 상기 신호선에 상기 아날로그 신호 전위보다 높은 전위를 공급해서 상기 표시소자를 발광 상태로 하고, 상기 아날로그 신호 전위보다 낮은 전위를 공급해서 비발광 상태로 한다.

[0052] 또한, 본 발명의 표시장치의 구동방법에 있어서, 상기 표시장치는, 표시소자와, 상기 표시소자를 구동하는 구동 트랜지스터와, 아날로그의 전위가 입력되는 신호선과, 상기 구동 트랜지스터의 게이트 단자의 전위와 상기 신호선의 전위 사이의 전위차를 유지하는 유지 수단과, 상기 구동 트랜지스터의 드레인 단자와 게이트 단자 사이의 부분을 도통 또는 비도통으로 하는 전환 수단을 구비한 화소를 가지고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 구동 트랜지스터의 소스 단자는 상기 표시소자의 양극과 접속되고, 기록 기간에는, 상기 신호선에 아날로그 신호 전위를 공급하고, 상기 전환 수단에 의해 상기 구동 트랜지스터의 드레인 단자와 게이트 단자를 도통시켜서 상기 화소에 신호를 기록하고, 상기 전환 수단에 의해 상기 구동 트랜지스터의 드레인 단자와 게이트 단자를 비도통으로 해서, 상기 구동 트랜지스터의 게이트 단자의 전위와 상기 신호선의 전위 사이의 전위차를 상기 유지 수단에 의해 유지하고, 발광 기간에는, 상기 신호선에 삼각파의 전위를 공급하여, 표시소자의 발광, 비발광 상태를 제어한다.

[0053] 또한, 본 발명의 표시장치의 구동방법에 있어서, 상기 표시장치는, 표시소자와, 상기 표시소자를 구동하는 구동 트랜지스터와, 용량소자와, 스위치와, 아날로그의 전위가 입력되는 신호선을 구비한 화소를 가지고, 상기 구동 트랜지스터의 게이트 단자는 용량소자를 통해 상기 신호선에 접속되고, 상기 구동 트랜지스터의 소스 단자는 상기 표시소자의 양극에 접속되고, 상기 구동 트랜지스터의 드레인 단자는 상기 게이트 단자와 상기 스위치를 통해 접속되고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 스위치는, 상기 화소에 신호를 기록할 때에 온 상태로 하고, 발광 기간에는 오프 상태로 하고, 상기 신호선은, 신호의 화소에의 기록 기간에는 아날로그 신호 전위를 공급하고, 발광 기간에는 삼각파의 전위를 공급한다.

[0054] 또한, 본 발명의 표시장치의 구동방법에 있어서, 상기 표시장치는, 표시소자와, 상기 표시소자를 구동하는 구동 트랜지스터와, 용량소자와, 제1 스위치와, 제2 스위치와, 아날로그의 전위가 입력되는 신호선과, 전원선을 구비

한 화소를 가지고, 상기 구동 트랜지스터의 게이트 단자는 용량소자를 통해 상기 신호선에 접속되고, 상기 구동 트랜지스터의 소스 단자는 상기 표시소자의 양극에 접속되고, 상기 구동 트랜지스터의 드레인 단자는, 상기 전원선과 상기 제1 스위치를 통해 접속되고 상기 게이트 단자와 상기 제2 스위치를 통해 접속되고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 제2 스위치는, 상기 화소에 신호를 기록할 때에 온 상태로 하고, 상기 제1 스위치는, 발광 기간에는 온 상태로 하고, 기록 기간에는 상기 제2 스위치가 온 상태인 기간에 온 상태로부터 오프 상태로 하고, 상기 신호선은, 신호의 화소에의 기록 기간에는 아날로그 신호 전위를 공급하고, 발광 기간에는 삼각파의 전위를 공급한다.

[0055] 또한, 본 발명의 표시장치의 구동방법에 있어서, 상기 표시장지는, 표시소자와, 상기 표시소자를 구동하는 구동 트랜지스터와, 용량소자와, 제1 스위치와, 제2 스위치와, 제3 스위치와, 제4 스위치와, 아날로그 영상신호전위가 입력되는 제1 신호선과, 규칙적으로 변화되는 아날로그 전위가 입력되는 제2 신호선과, 전원선을 구비한 화소를 가지고, 상기 구동 트랜지스터의 게이트 단자는 상기 용량소자의 한쪽 전극과 접속되고, 상기 용량소자의 다른 쪽 전극은, 상기 제3 스위치를 통해 상기 제1 신호선과 접속되는 한편, 상기 제4 스위치를 통해 상기 제2 신호선과 접속되고, 상기 구동 트랜지스터의 소스 단자는 상기 표시소자의 양극에 접속되고, 상기 구동 트랜지스터의 드레인 단자는, 상기 전원선과 상기 제1 스위치를 통해 접속되는 한편, 상기 게이트 단자와 상기 제2 스위치를 통해 접속되고, 상기 구동 트랜지스터는 n형 트랜지스터인 것을 특징으로 하는 표시장치의 구동방법이며, 상기 화소에 신호를 기록할 때에는, 상기 제2 스위치 및 상기 제3 스위치를 온 상태로 하고, 상기 제1 스위치는, 상기 제2 스위치 및 상기 제3 스위치가 온 상태인 기간의 일부 기간에는 오프 상태로 하고, 상기 제4 스위치는, 상기 제2 스위치 및 상기 제3 스위치가 온 상태가 아닌 기간에 온 상태로 한다.

[0056] 또한, 본 발명의 표시장치의 구동방법에 있어서, 상기 표시장지는, 표시소자와, 상기 표시소자를 구동하는 구동 트랜지스터와, 용량소자와, 제1 스위치와, 제2 스위치와, 제3 스위치와, 제4 스위치와, 아날로그 신호 전위가 입력되는 제1 신호선과, 삼각파의 전위가 입력되는 제2 신호선과, 전원선을 구비한 화소를 가지고, 상기 구동 트랜지스터의 게이트 단자는 상기 용량소자의 한쪽 전극과 접속되고, 상기 용량소자의 다른 쪽 전극은 상기 제3 스위치를 통해 상기 제1 신호선과 접속되는 한편, 상기 제4 스위치를 통해 상기 제2 신호선과 접속되고, 상기 구동 트랜지스터의 소스 단자는 상기 표시소자의 양극에 접속되고, 상기 구동 트랜지스터의 드레인 단자는, 상기 전원선과 상기 제1 스위치를 통해 접속되는 한편, 상기 게이트 단자와 상기 제2 스위치를 통해 접속되고, 상기 구동 트랜지스터는 n형 트랜지스터이며, 상기 화소에 신호를 기록할 때에는, 상기 제2 스위치 및 상기 제3 스위치를 온 상태로 하고, 상기 제1 스위치는, 상기 제2 스위치 및 상기 제3 스위치가 온 상태인 기간의 일부 기간에는 오프 상태로 하고, 상기 제4 스위치는, 상기 제2 스위치 및 상기 제3 스위치가 온 상태가 아닌 기간에 온 상태로 한다.

[0057] 이때, 본 발명에 있어서 접속되어 있다는 것은, 전기적으로 접속되어 있는 것을 의미한다. 따라서, 사이에 별도의 소자나 스위치 등이 배치되어도 된다.

[0058] 한편, 표시소자의 종류는 특별히 제한되지 않는다. EL소자(유기EL소자, 무기EL소자 또는 유기물 및 무기물을 포함하는 EL소자)나 FED(Field Emission Display)에 사용하는 소자, FED의 일종인 SED(Surface-conduction Electron-emitter Display), 액정 모니터(LCD), 플라즈마 디스플레이(PDP), 전자 페이퍼 디스플레이, DMD(Digital Micromirror Device), 압전 세라믹 디스플레이 등에 사용하는 소자 등, 어떤 표시소자로 해도 상관 없다.

[0059] 본 발명에 있어서, 적용 가능한 트랜지스터의 종류에 한정은 없고, 비정질 실리콘이나 다결정 실리콘로 대표되는 비단결정 반도체막을 사용한 박막 트랜지스터(TFT), 반도체기판이나 SOI기판을 사용해서 형성되는 MOS형 트랜지스터, 접합형 트랜지스터, 바이폴라 트랜지스터, 유기반도체나 카본 나노튜브를 사용한 트랜지스터, 그 외의 트랜지스터를 적용할 수 있다. 또한 트랜지스터가 배치되는 기판의 종류에 한정은 없고, 단결정 기판, SOI기판, 유리기판, 플라스틱 기판 등에 배치할 수 있다.

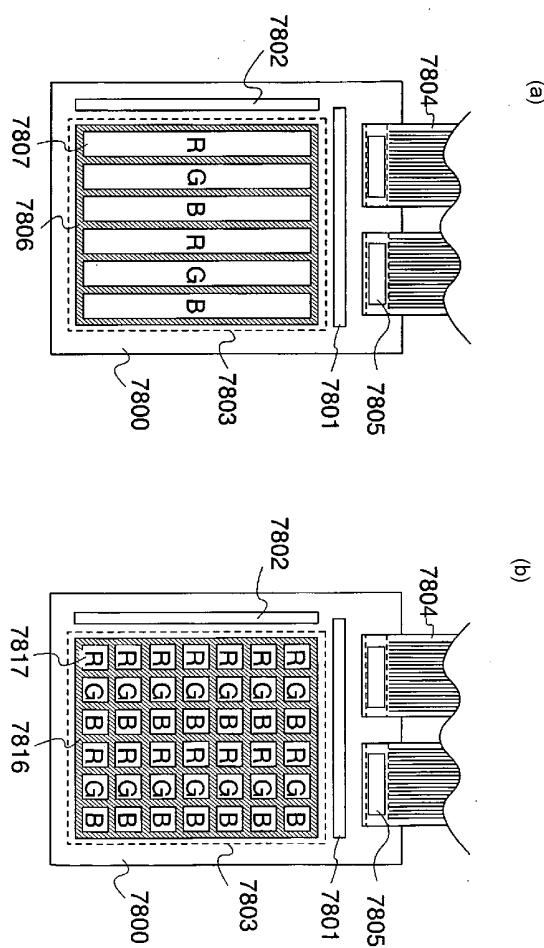

[0060] 본 명세서에 있어서, 하나의 화소는 하나의 색 요소 RGB를 나타내는 것으로 한다. 따라서, R(빨강)G(초록)B(파랑)의 색 요소 RGB로 이루어진 풀 컬러 표시장치의 경우, 하나의 화소는 RGB의 1요소를 의미한다.

[0061] 또한, 본 명세서에 있어서, 화소가 매트릭스로 배치되어 있다는 것은, 세로줄과 가로줄을 조합한 소위 격자 형태로 배치되어 있는 경우에는 물론, 세 개의 색 요소 RGB(예를 들면, RGB)로 풀 컬러 표시를 행할 경우에, 1개의 화상의 최소 요소를 나타내는 세 개의 색 요소 RGB의 화소가 소위 엘타 배치되어 있는 경우도 포함하는 것으로 한다.

[0062] 또한, 본 명세서에 있어서, 반도체장치는 반도체소자(트랜지스터나 다이오드 등)를 포함하는 회로를 가지는 장치를 말한다.

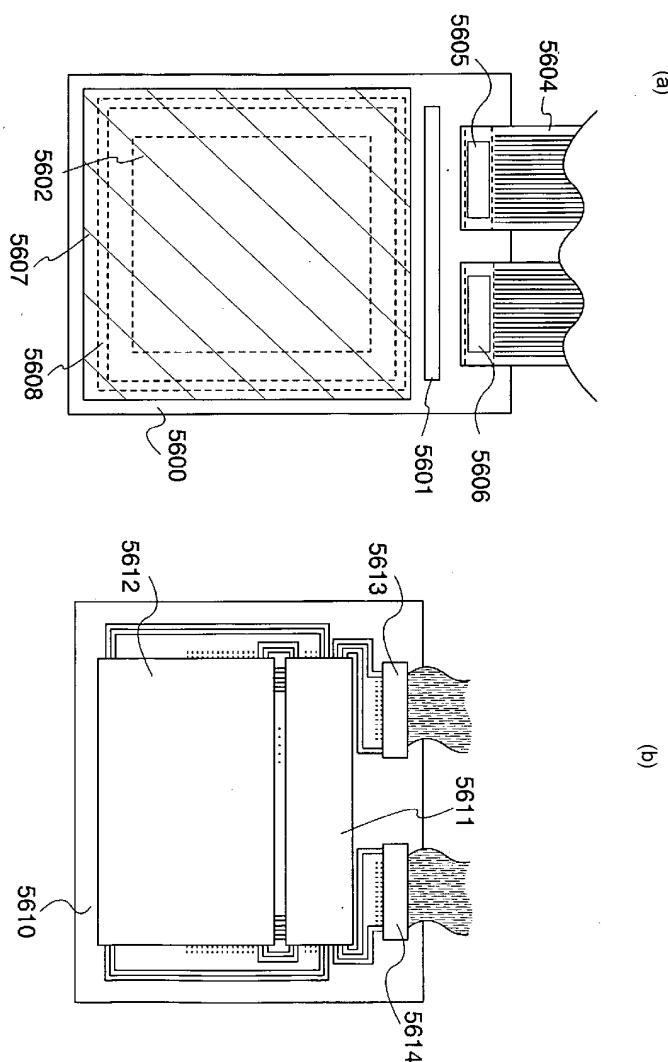

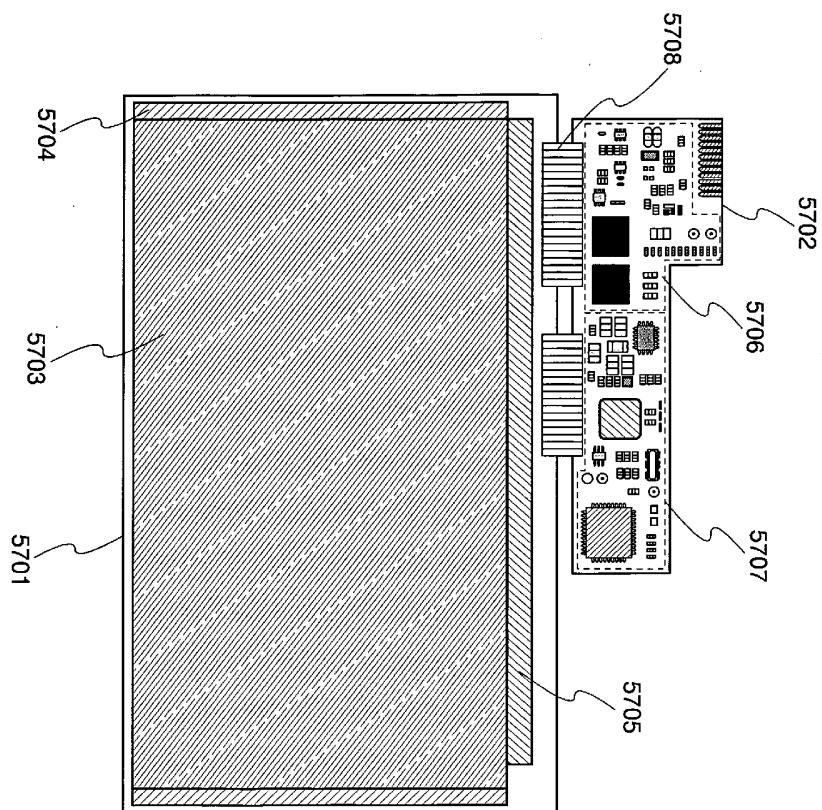

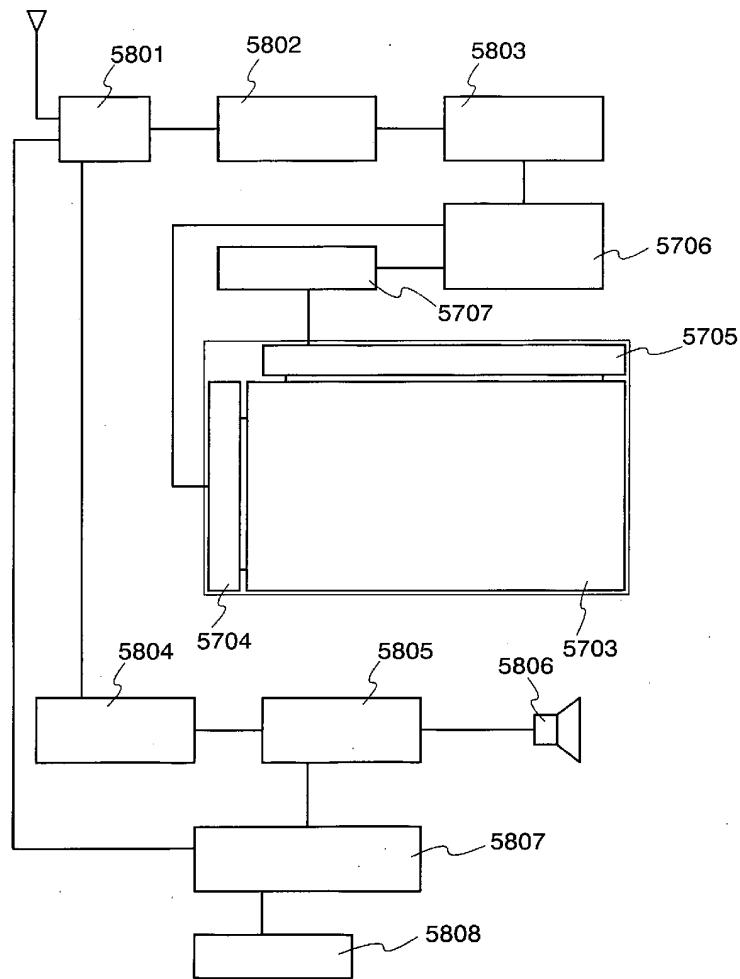

## 실시예

[0145] 이하, 본 발명의 실시예에 대해서 도면을 참조하면서 설명하지만, 본 발명은 다양한 형태로 실시할 수 있으며, 본 발명의 취지 및 그 범위에서 일탈하지 않는 한 그 형태 및 상세한 내용을 다양하게 변경할 수 있다는 것은 당업자라면 용이하게 이해된다. 따라서, 본 실시예의 기재 내용에 한정해서 해석해서는 안 된다.

[0146] (실시예 1)

[0147] 본 실시예에서는 본 발명의 표시장치의 화소 구성과 그 동작 원리에 관하여 설명한다.

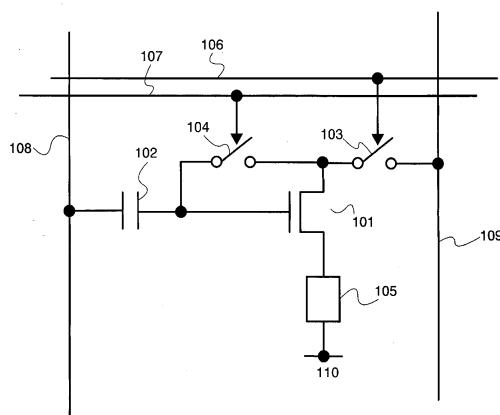

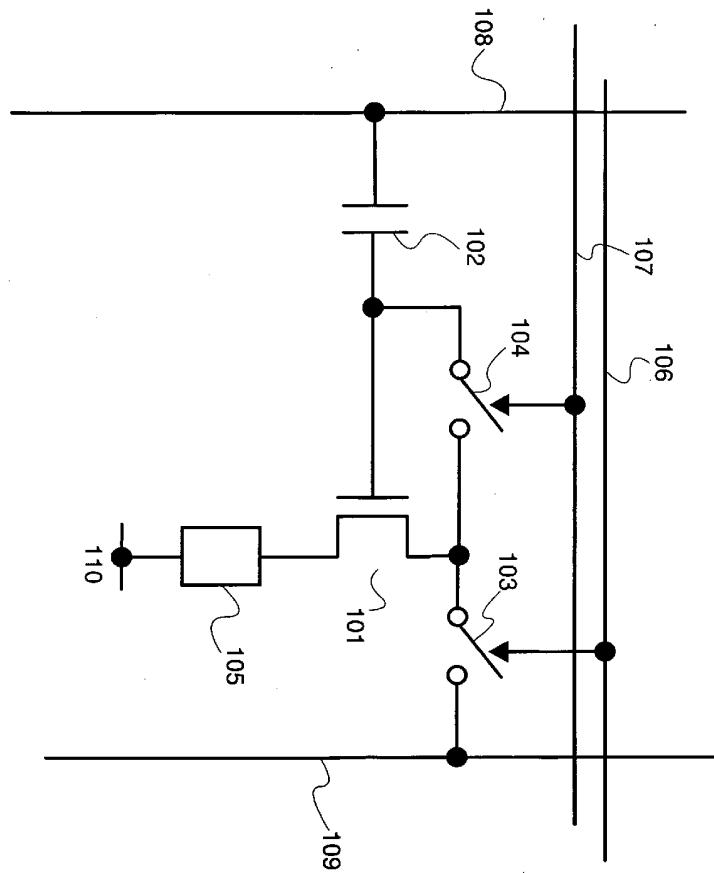

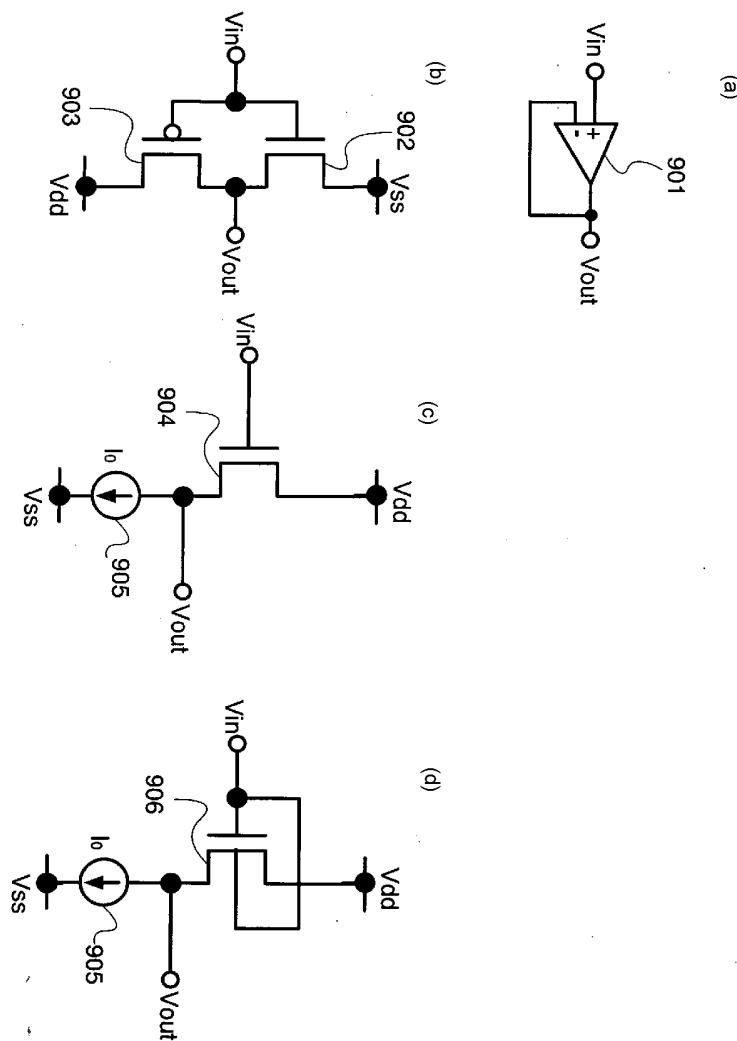

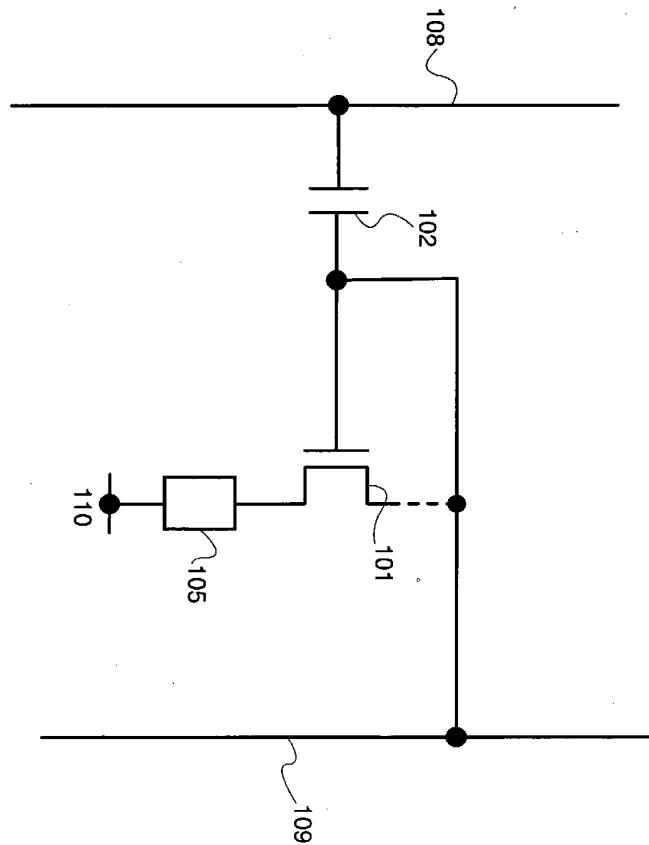

[0148] 우선, 도 1을 참조해서 본 발명의 표시장치의 화소 구성에 대해서 상세히 설명한다. 화소는 구동 트랜지스터(101)와, 용량소자(102)와, 제1 스위치(103)와, 제2 스위치(104)와, 표시소자(105)와, 제1 주사선(G1 line)(106)과, 제2 주사선(G2 line)(107)과, 신호선(Data line)(108)과, 전원선(Supply line)(109)을 구비한다. 이때, 구동 트랜지스터(101)에는 n형 트랜지스터를 사용한다.

[0149] 구동 트랜지스터(101)의 소스 단자는 표시소자(105)의 양극과 접속되고, 게이트 단자는 용량소자(102)를 통해 신호선(108)과 접속되고, 드레인 단자는 제1 스위치(103)를 통해 전원선(109)과 접속된다. 이때, 전원선(109)에는 전원전위 Vdd가 공급된다. 또한 구동 트랜지스터(101)의 게이트 단자와 드레인 단자는 제2 스위치(104)를 통해 접속된다. 따라서 제2 스위치(104)가 온 상태일 때에는 구동 트랜지스터(101)의 게이트 단자와 드레인 단자는 도통한다. 그리고, 제2 스위치(104)가 오프 상태가 되면, 구동 트랜지스터(101)의 게이트 단자와 드레인 단자는 비도통이 되고, 그 순간의 구동 트랜지스터(101)의 게이트 단자(또는 드레인 단자)와 신호선(108) 사이의 전위차(전압)를 용량소자(102)로 유지할 수 있다. 또한 표시소자(105)의 음극은 Vss의 전위가 공급되는 배선(110)과 접속된다. 이때, Vss는 Vss<Vdd를 만족시키는 전위다. 예를 들면, Vss=GND(접지 전위)로 해도 된다.

[0150] 다음으로, 도 1의 화소 구성의 동작 원리에 관하여 설명한다.

[0151] 화소의 신호 기록 기간에, 제1 주사선(106) 및 제2 주사선(107)에 신호를 입력하고, 제1 스위치(103) 및 제2 스위치(104)를 온 상태로 한다. 그러면, 구동 트랜지스터(101)의 드레인 단자와 게이트 단자에 전원선(109)의 전원전위(Vdd)가 공급된다. 그리고, 용량소자(102), 구동 트랜지스터(101) 및 표시소자(105)에 전류가 흘러, 용량소자(102)에서는 전하의 축적 또는 방전이 행해진다. 이때, 화소에의 신호 기록 기간에는, 신호선(108)에는 아날로그 신호 전위가 공급된다. 이 아날로그 신호 전위는 비디오신호에 해당한다.

[0152] 잠시 후, 용량소자(102)에는 전류가 흐르지 않게 된다. 그리고, 구동 트랜지스터(101) 및 표시소자(105)에 전류가 흐른다. 왜냐하면, 이때 구동 트랜지스터(101)의 게이트 단자는, 제2 스위치(104)에 의해 드레인 단자와 도통되어 있기 때문에, 게이트 단자의 전위는, 전원전위(Vdd)가 되어 구동 트랜지스터(101)는 온 상태이기 때문이다.

[0153] 이 상태에서, 제1 스위치(103)를 오프 상태로 한다. 그러면 처음에는, 구동 트랜지스터(101)와 용량소자(102)에 전류가 흐르지만, 잠시 후, 구동 트랜지스터(101) 및 용량소자(102)에 전류가 흐르지 않게 된다. 이렇게 해서, 구동 트랜지스터(101)는 오프 상태가 된다. 이때, 구동 트랜지스터(101)의 게이트-소스간 전압 Vgs는 역치전압 Vth와 대략 동등하다.

[0154] 그리고, 이 상태가 되면 제2 스위치(104)를 오프 상태로 한다. 그러면, 용량소자(102)에는, 트랜지스터를 오프 상태로 하는 구동 트랜지스터(101)의 게이트 단자의 전위와, 제2 스위치(104)를 오프 상태로 한 순간 신호선(108)에 공급되어 있는 아날로그 신호 전위의 전위차(Vp)가 유지된다. 이렇게 해서 화소에 아날로그 신호가 기록된다.

[0155] 이때, 전술한 제1 스위치(103), 및 제2 스위치(104)의 온/오프는, 제1 주사선(106), 및 제2 주사선(107)에 각각 펄스 신호를 입력함으로써 제어한다.

[0156] 화소에 아날로그 신호가 기록되면, 그때 신호선(108)에 공급된 아날로그 신호 전위를 기준으로 해서, 신호선(108)의 전위의 변동에 따라 구동 트랜지스터(101)의 온/오프가 제어되게 된다. 즉, 신호선(108)의 전위가, 신호 기록 기간에 화소에 기록될 때의 아날로그 신호 전위 이하일 때에는 구동 트랜지스터(101)는 오프 상태가 되

고, 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위보다 높아지면 구동 트랜지스터(101)는 온 상태가 된다.

[0157] 즉, 화소에 아날로그 신호가 기록되면, 용량소자(102)가 전위차( $V_p$ )를 유지하므로, 신호선(108)의 전위가, 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위 이하일 때에는, 구동 트랜지스터(101)의 게이트 단자의 전위도, 화소에 아날로그 신호가 기록될 때의 게이트 단자의 전위 이하가 되고, 구동 트랜지스터(101)는 오프 상태가 된다. 한편, 신호선(108)의 전위가, 기록 기간에 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위보다 높아지면, 구동 트랜지스터(101)의 게이트 단자의 전위도, 화소에 아날로그 신호가 기록될 때의 게이트 단자의 전위보다 높아지므로 구동 트랜지스터(101)는 온 상태가 된다.

[0158] 따라서, 화소의 발광 기간에는, 제2 스위치(104)를 오프 상태로 하고, 제1 스위치(103)를 온 상태로 한 상태에서, 신호선(108)에 공급하는 전위를 아날로그적으로 변화시킴으로써 구동 트랜지스터(101)의 온/오프를 제어하고, 표시소자(105)에 전류가 흐르고 있는 시간을 아날로그적으로 제어하여, 계조를 표현할 수 있다.

[0159] 계속해서, 화소의 발광 기간에, 신호선(108)에 공급하는 전위에 관하여 설명한다.

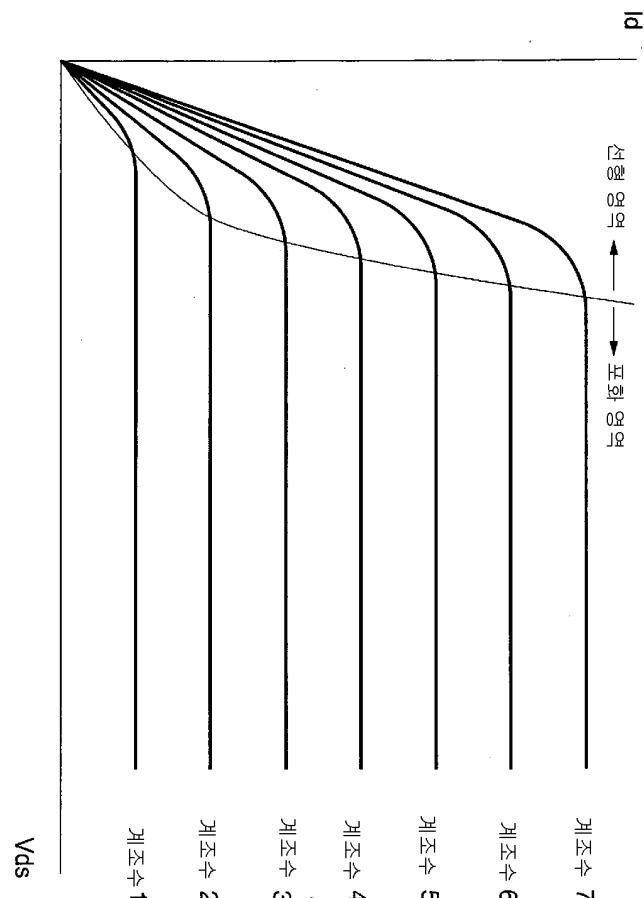

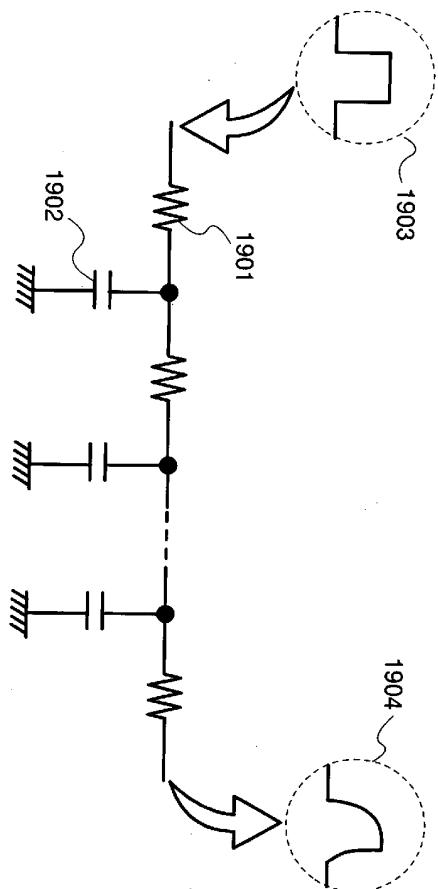

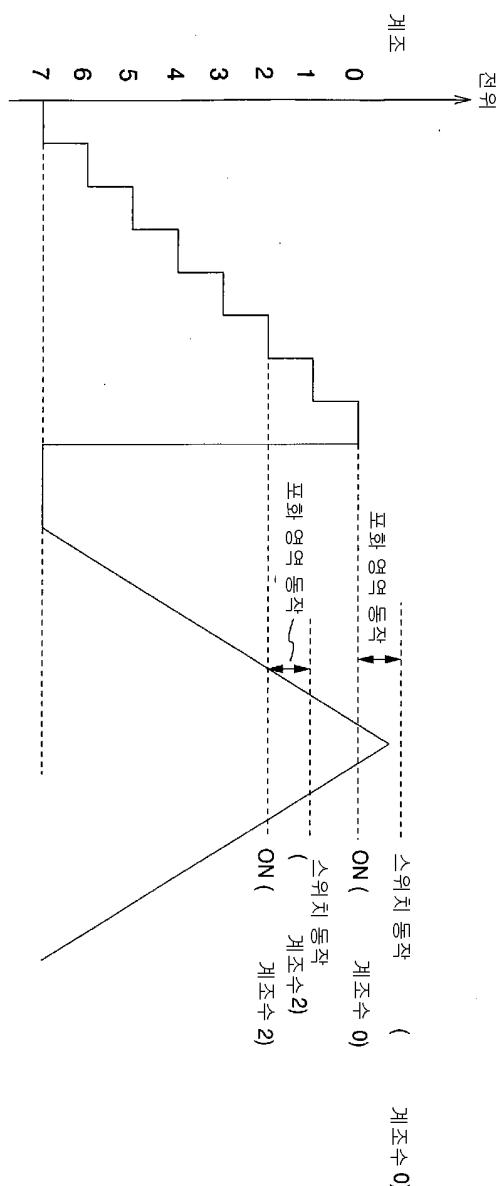

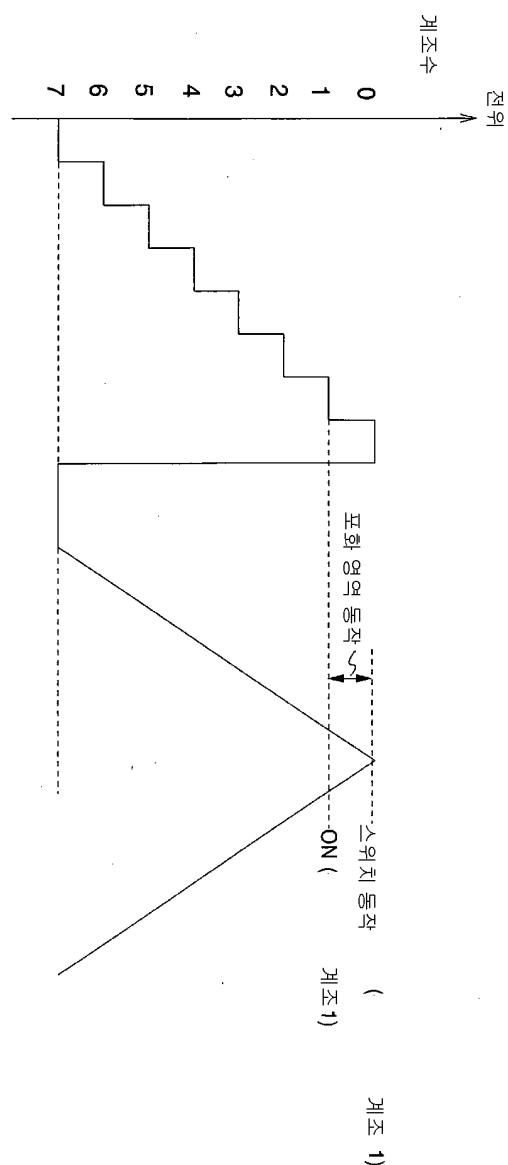

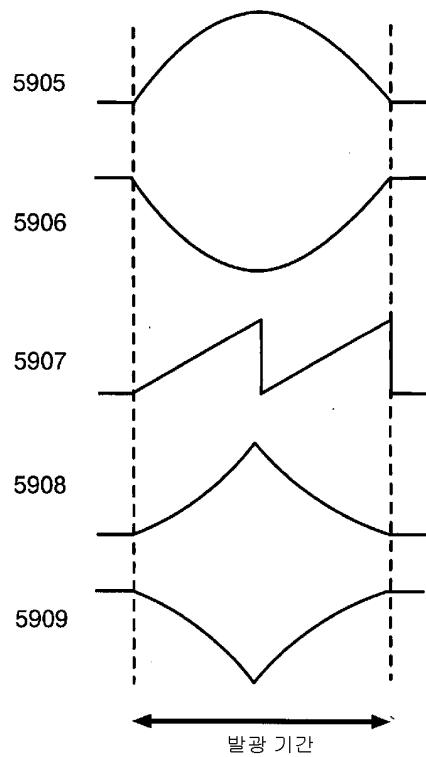

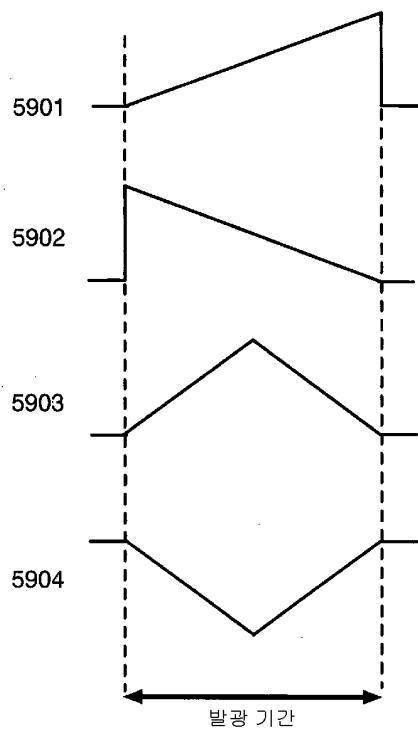

[0160] 예를 들면, 발광 기간에는, 신호선(108)에 저전위로부터 고전위로 아날로그적으로 변화되는 전위를 공급한다. 일례로서, 도 59의 과형(5901)과 같이 직선적으로 전위가 상승하도록 해도 된다.

[0161] 또한 고전위로부터 저전위로 아날로그적으로 변화되는 전위를 공급해도 된다. 예를 들면, 과형(5902)과 같이 직선적으로 전위가 하강하도록 해도 된다.

[0162] 또한 그것들을 조합한 과형으로 해도 된다. 즉, 일례로서, 과형(5903)과 같이 저전위로부터 고전위로 직선적으로 상승하고, 고전위로부터 저전위로 하강하도록 전위를 공급해도 된다. 이때, 이하 이러한 과형(5903)을 삼각과 전위라고 한다. 또는, 과형(5904)과 같이 고전위로부터 저전위로 직선적으로 하강하고, 저전위로부터 고전위로 직선적으로 상승하도록 전위를 공급해도 된다.

[0163] 또한 신호선(108)에 공급하는 전위는 직선적인 변화가 아니어도 된다. 과형(5905)과 같이 전과정류회로의 출력과 형의 1주기에 해당하는 과형의 전위를 공급해도 되고, 그 과형을 상하 반전시킨 과형(5906)의 전위를 공급해도 된다. 또한 과형(5908)이나 과형(5909)과 같은 과형의 전위를 공급해도 된다.

[0164] 이러한 과형으로 함으로써, 비디오신호에 대한 발광 시간을 자유롭게 설정할 수 있다. 따라서, 감마 보정 등을 실행할 수 있다.

[0165] 화소의 발광 기간에 있어서, 상기 과형(5901), 과형(5902), 과형(5903), 과형(5904), 과형(5905), 과형(5906), 과형(5908) 또는 과형(5909)의 펄스를 복수 연속으로 공급해도 된다. 일례로서, 과형(5907)에 나타낸 바와 같이, 과형(5901)의 펄스를 화소의 발광 기간에, 두 번 연속으로 공급해도 된다.

[0166] 이렇게 함으로써, 발광 시간을 1프레임 내에서 분산시킬 수 있다. 그 결과, 프레임 주파수가 외관상 향상되고, 화면의 깜박거림을 방지할 수 있다.

[0167] 또한 화소의 발광 기간에는 제1 스위치(103)를 온 상태로 하여, 구동 트랜지스터(101)의 드레인 단자에 전원선(109)의 전원전위  $V_{dd}$ 를 공급한다. 한편, 제2 스위치(104)는 오프 상태가 된다.

[0168] 이렇게 해서, 화소에 아날로그 신호를 기록할 때에 신호선(108)에 공급되는 아날로그 신호 전위에 의해 화소의 아날로그 시간조표시가 가능해진다. 이때, 계조수가 작을수록 그 아날로그 신호 전위는 높아진다.

[0169] 왜냐하면, 화소의 발광 기간에 공급되는 삼각과 전위와, 화소에의 신호 기록 기간에 화소에 입력한 아날로그 신호 전위의 대소관계에 따라, 구동 트랜지스터(101)의 온/오프가 결정되기 때문이다. 화소에의 신호 기록 기간에 화소에 입력되는 아날로그 신호 전위가, 화소의 발광 기간에 공급되는 삼각과 전위보다 낮은 경우에는, 구동 트랜지스터(101)는 온 상태가 되고, 발광한다. 따라서, 화소에의 신호 기록 기간에 화소에 입력되는 아날로그 신호 전위가 낮을수록, 화소의 발광 기간에 공급되는 삼각과 전위보다 낮은 기간이 길어지고, 발광하는 기간도 길어진다. 따라서, 계조도 높아진다. 반대로, 화소에의 신호 기록 기간에 화소에 입력되는 아날로그 신호 전위가 높을수록, 화소의 발광 기간에 공급되는 삼각과 전위보다 낮은 기간이 짧아지고, 발광하는 기간도 짧아진다. 따라서, 계조도 작아진다.

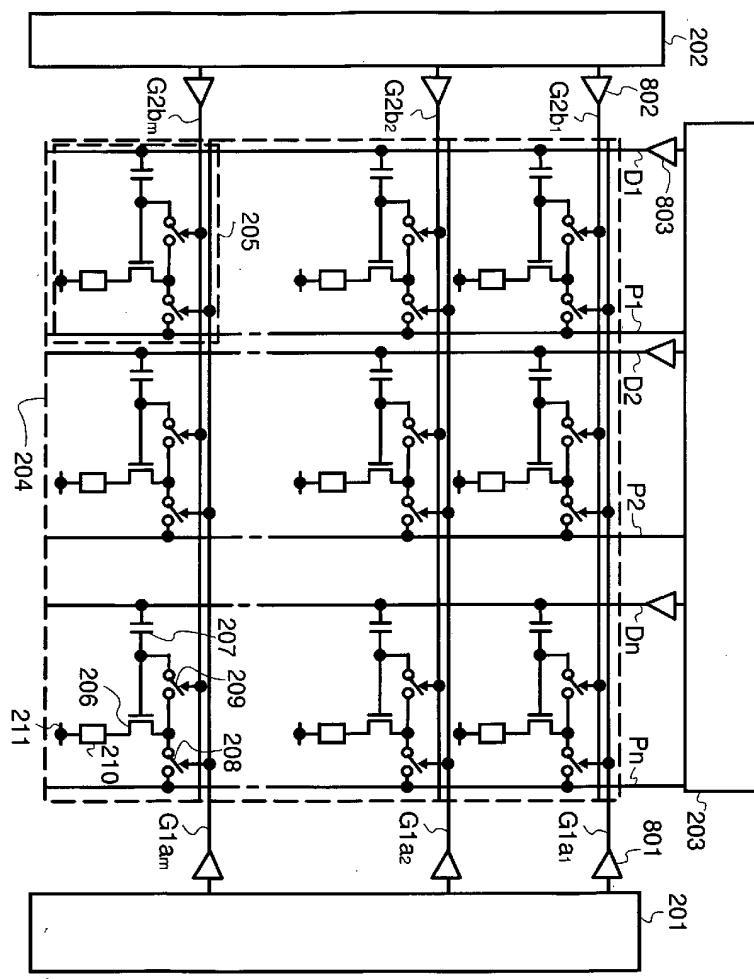

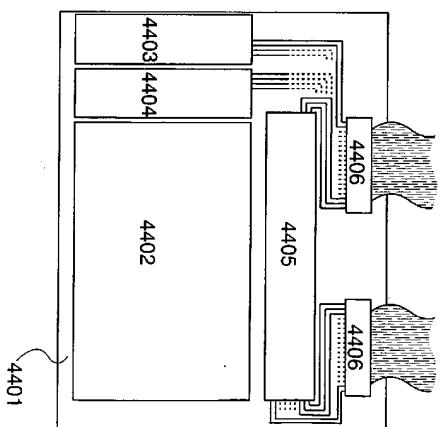

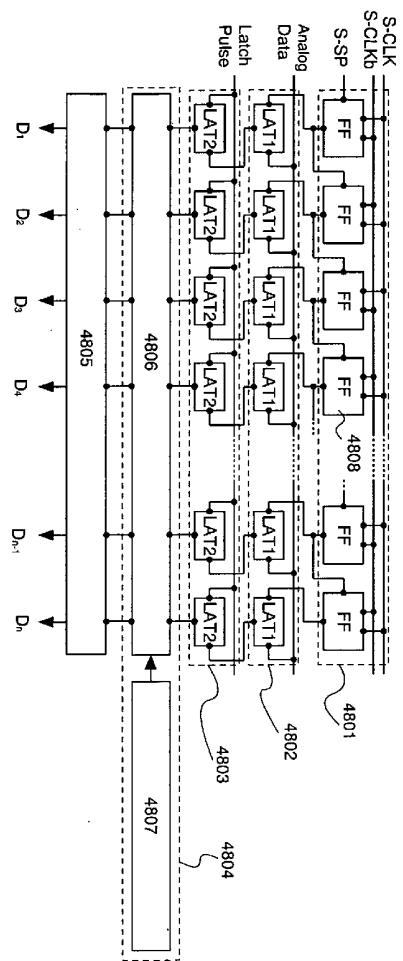

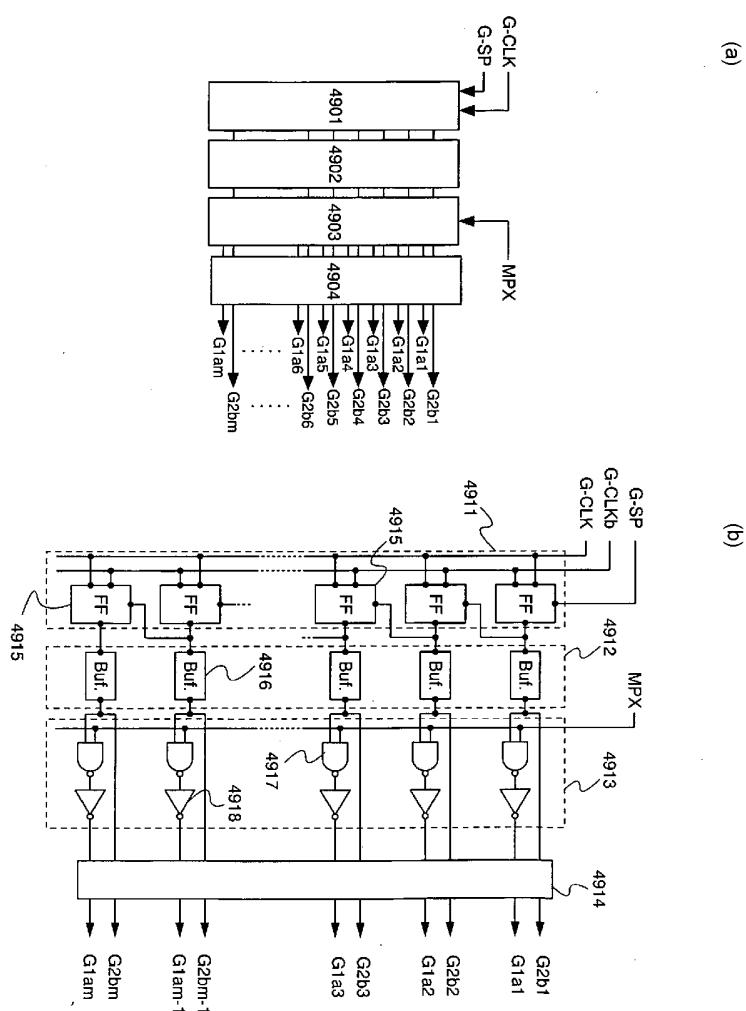

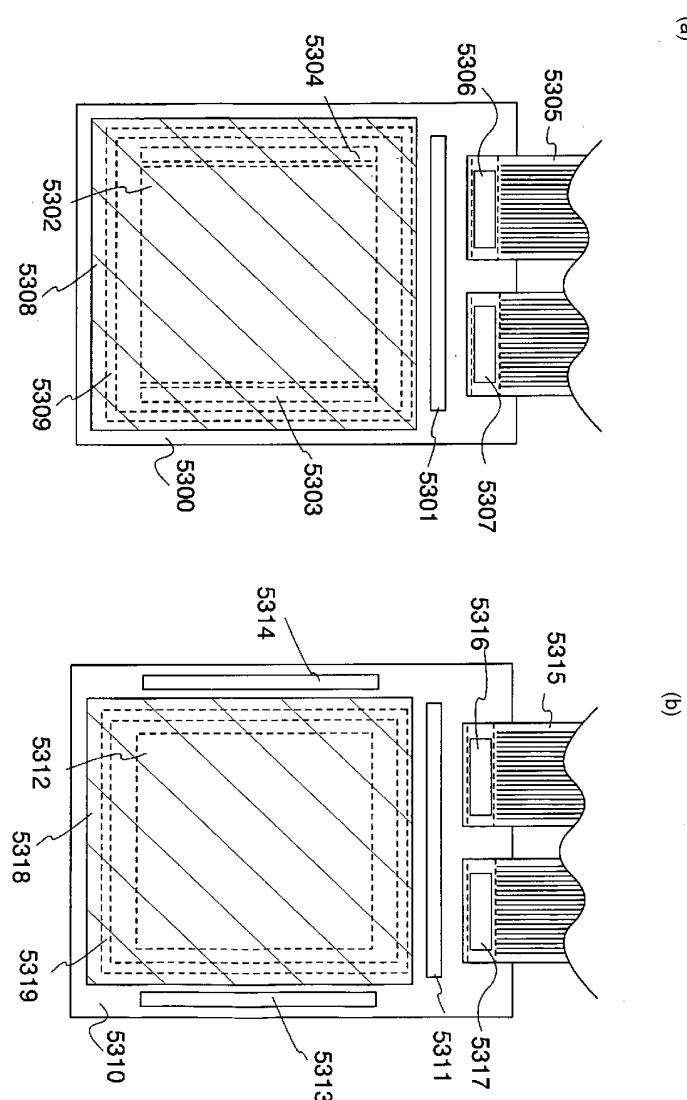

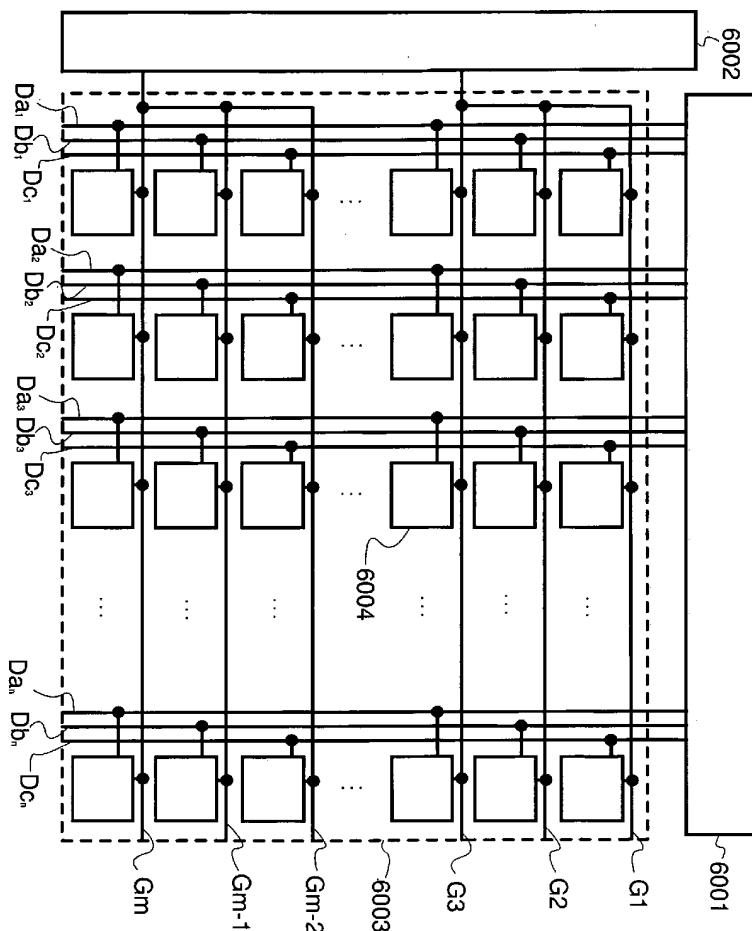

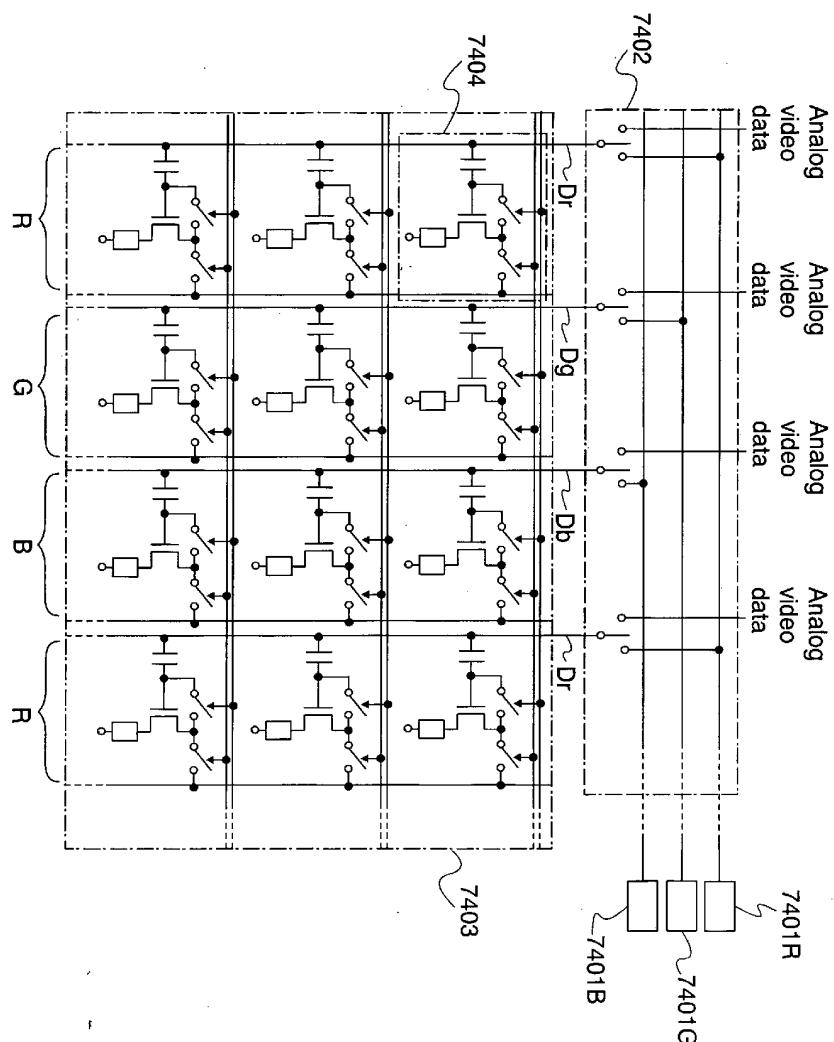

[0170] 계속해서 화소부에 도 1의 화소 구성을 가지는 표시장치에 대해서 도 2를 참조하여 설명한다. 도 2의 표시장치는, 제1 주사선 구동회로(201), 제2 주사선 구동회로(202), 신호선 구동회로(203), 화소부(204)를 가지고, 화소부(204)는 화소(205)를 복수 개 구비한다. 행 방향으로 배치된 제1 주사선(G1 line) G1a1 ~ G1am 및 제2 주사선

(G2 line) G2b1 ~ G2bm과 열 방향으로 배치된 신호선(Data line) D1 ~ Dn 및 전원선(Supply line) P1 ~ Pn에 대응해서 화소(205)가 매트릭스로 배치되어 있다.

[0171] 화소(205)는 구동 트랜지스터(206)와, 용량소자(207)와, 제1 스위치(208)와, 제2 스위치(209)와, 표시소자(210)와, 제1 주사선 G1ai(G1a1 ~ G1am 중 어느 하나)과, 제2 주사선 G2bi(G2b1 ~ G2bm 중 어느 하나)과, 신호선 Dj(D1 ~ Dn 중 어느 하나)과, 전원선 Pj(P1 ~ Pn 중 어느 하나)를 구비한다. 이때, 구동 트랜지스터(206)에는 n형 트랜지스터를 사용한다. 또한, 화소(205)는 화소부(204)에 복수 개 배치된 화소 중 하나의 화소를 나타낸다.

[0172] 구동 트랜지스터(206)의 소스 단자는 표시소자(210)의 양극과 접속되고, 게이트 단자는 용량소자(207)를 통해 신호선 Dj와 접속되고, 드레인 단자는 제1 스위치(208)를 통해 전원선 Pj와 접속된다. 전원선(P1 ~ Pn)에는 전원 전위 Vdd가 공급된다. 이때, 전원선(P1 ~ Pn)에 공급하는 전위는 Vdd에 한정되지 않고, 예를 들면, 색 요소 RGB로 이루어진 풀 컬러 표시의 경우에는, 각 색 요소 RGB의 화소마다 전원전위의 값을 변경해도 된다. 즉, 색 요소 R을 나타내는 화소 열에는 Vdd1, 색 요소 G를 나타내는 화소 열에는 Vdd2, 색 요소 B를 나타내는 화소 열에는 Vdd3로 하도록 공급해도 된다.

[0173] 또한 구동 트랜지스터(206)의 게이트 단자와 드레인 단자는 제2 스위치(209)를 통해 접속된다. 따라서 제2 스위치(209)가 온 상태일 때에는 구동 트랜지스터(206)의 게이트 단자와 드레인 단자는 도통한다. 그리고, 제2 스위치(209)가 오프 상태가 되면, 구동 트랜지스터(206)의 게이트 단자와 드레인 단자는 비도통이 되고, 그 순간의 구동 트랜지스터(206)의 게이트 단자(또는 드레인 단자)와 신호선 Dj 사이의 전위차(전압)를 용량소자(207)는 유지할 수 있다. 또한 표시소자(210)의 음극은 Vss의 전위가 공급된 배선(211)과 접속된다. 이때, Vss는 Vss < Vdd를 만족시키는 전위다. 예를 들면, Vss=GND(접지 전위)로 해도 된다.

[0174] 이때, 주사선 구동회로는 좌우에 배치되어 있지만 이것에 한정되지 않는다. 한쪽에 모두 배치해도 된다.

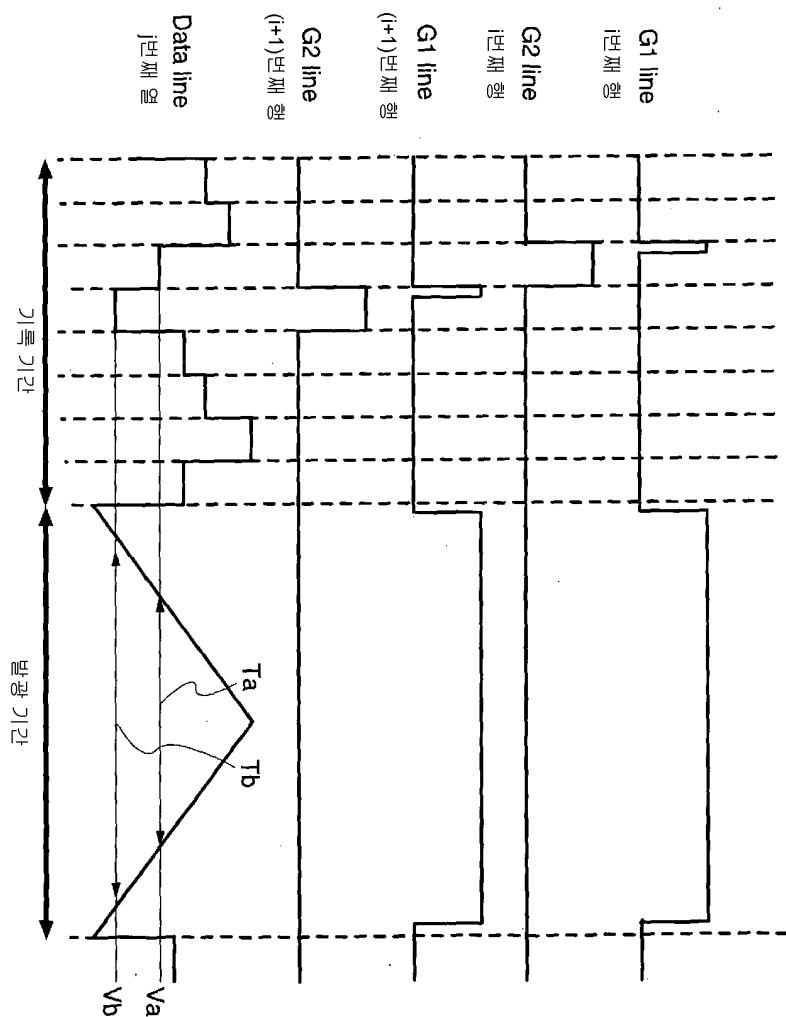

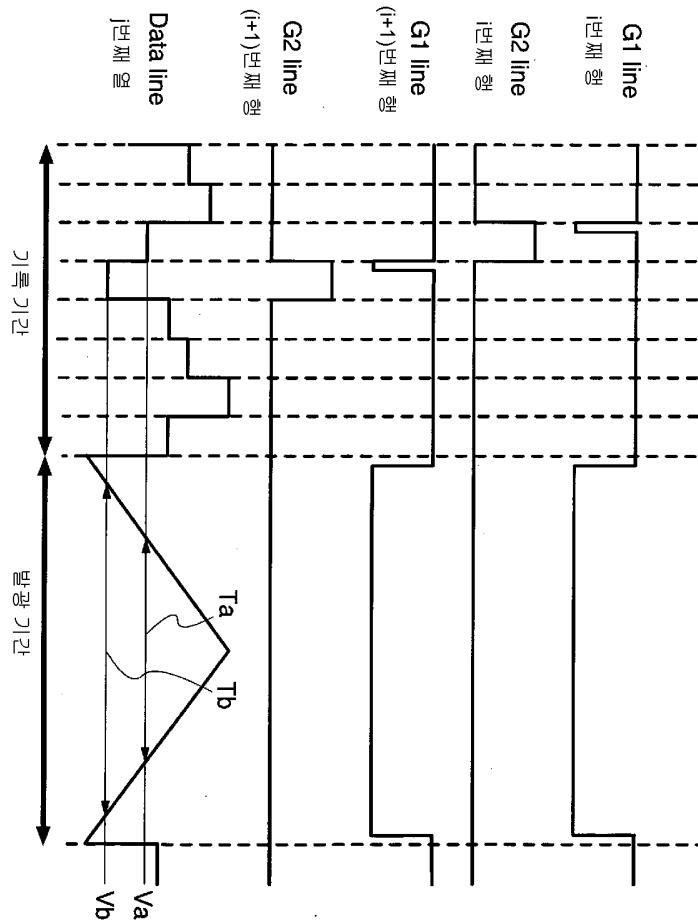

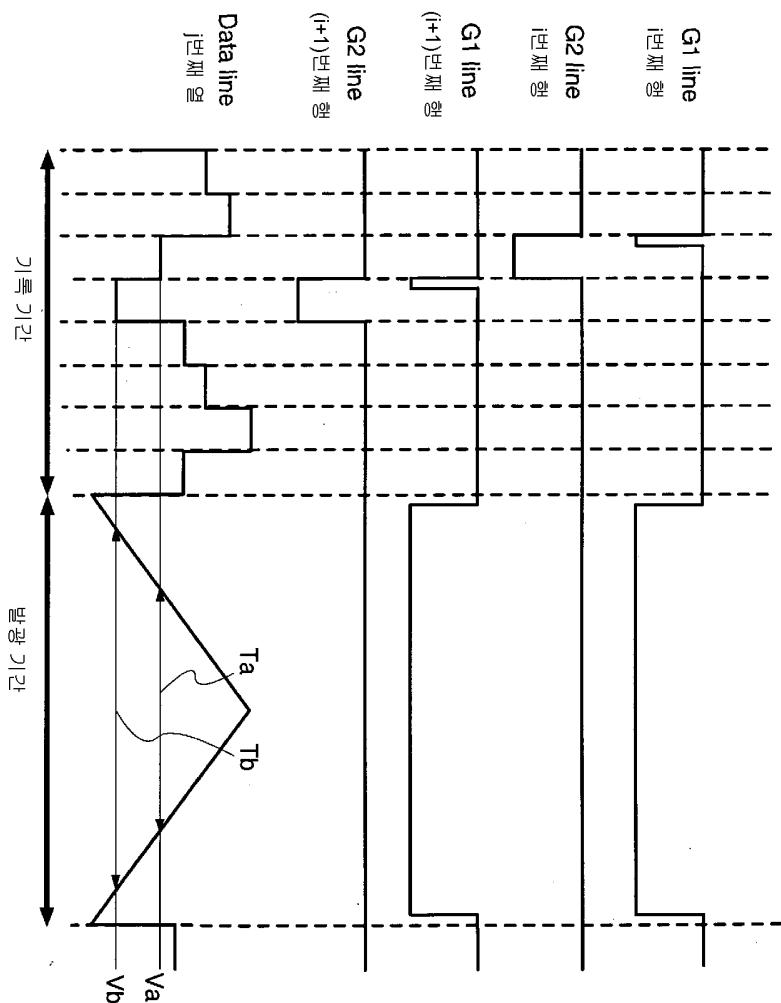

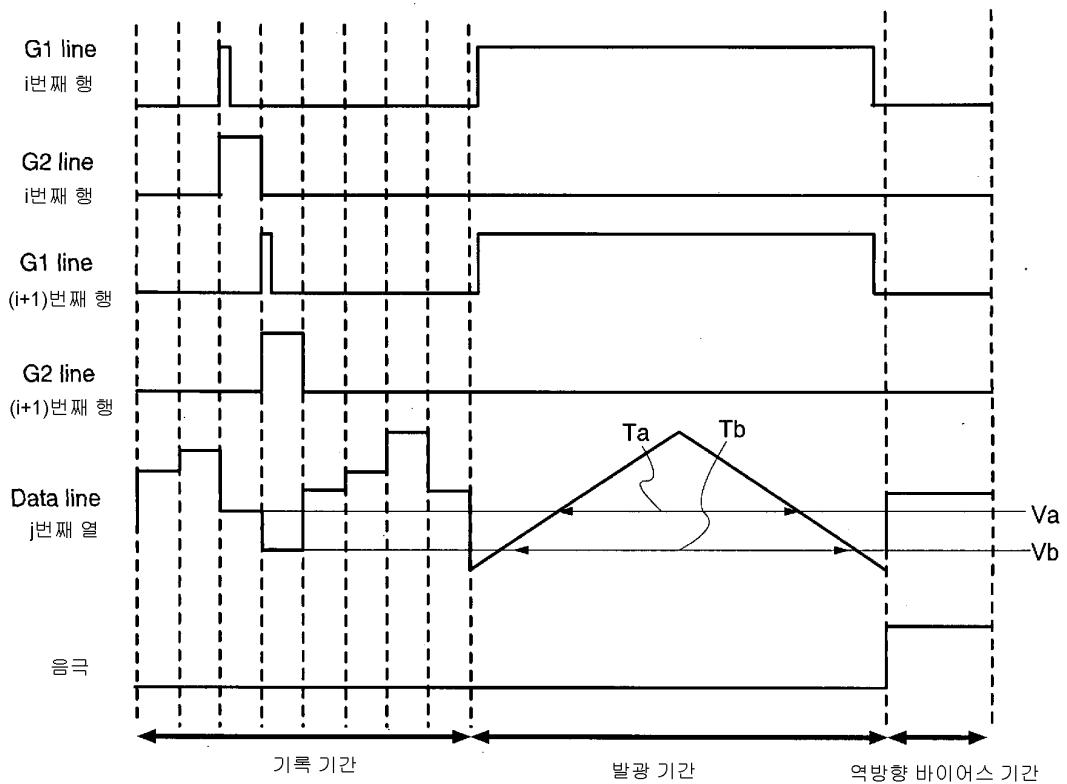

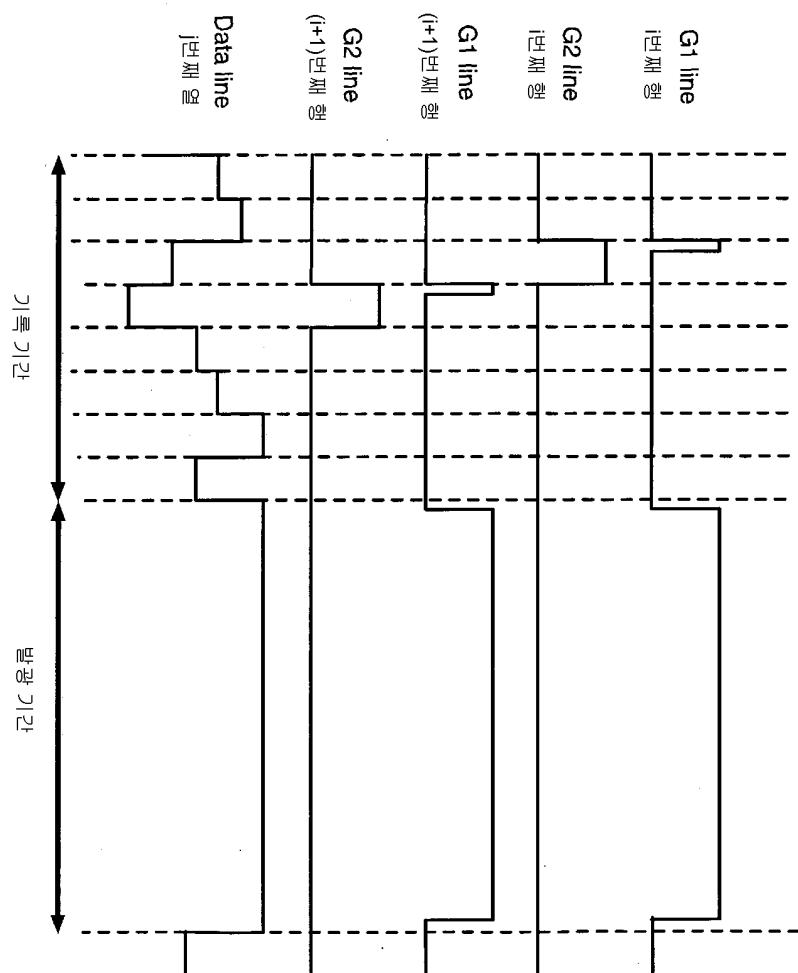

[0175] 다음으로, 도 2 및 도 3을 참조해서 본 발명의 표시장치의 동작 원리에 관하여 설명한다. 도 3은 도 2에 있어서의 표시장치의 화소부(204) 중 어느 화소 열(j번째 열)의 타이밍 차트를 도시한 도면이다. 이때, 화소부(204)에 복수 개 배치된 각각의 화소는, 화소(205)와 동일한 구성이기 때문에, 각각의 화소의 구동 트랜지스터, 용량소자, 제1 스위치, 제2 스위치 및 표시소자는 화소(205)와 같은 부호를 참조하여 설명한다.

[0176] 도 3에 나타낸 바와 같이, 기록 기간에는 j번째 열의 화소의 Data line(신호선 Dj)에 아날로그 신호 전위가 입력된다. i번째 행의 G1 line(제1 주사선 G1ai)과 G2 line(제2 주사선 G2bi)에 펄스 신호가 입력되면, 제1 스위치(208)와 제2 스위치(209)는 온 상태가 되고, i번째 행의 화소의 구동 트랜지스터(206)의 드레인 단자에는 전원선 Pj로부터의 전원전위(Vdd)가 공급되어, 용량소자(207), 구동 트랜지스터(206) 및 표시소자(210)에 전류가 흐른다. 그리고, 용량소자(207)에서는 전하의 축적 혹은 방전이 행해진다. 즉, 용량소자(207)에 원래 축적되어 있던 전하와 Data line(신호선 Dj)에 공급된 전위(Va)의 관계에 따라 전하의 축적 또는 방전이 일어난다. 그리고, 제1 주사선 G1ai에 입력된 펄스 신호의 펄스 폭보다 제2 주사선 G2bi에 입력되는 펄스 신호의 펄스 폭이 길기 때문에, 제2 스위치(209)가 온인 상태에서 제1 스위치(208)는 오프 상태로 한다. 제1 스위치(208)가 오프 상태가 되는 순간에는, 구동 트랜지스터(206)의 게이트 단자는 전원전위(Vdd)가 공급되어 있기 때문에 구동 트랜지스터(206)는 온 상태가 된다. 따라서, 구동 트랜지스터(206), 표시소자(210) 및 용량소자(207)에 전류가 흐른다. 잠시 후, 구동 트랜지스터(206), 표시소자(210) 및 용량소자(207)에 전류가 흐르지 않게 된다. 즉 정상상태가 된다. 이렇게 해서, 구동 트랜지스터(206)는 오프 상태가 된다. 구동 트랜지스터(206)의 게이트-소스간 전압 Vgs는 역치전압 Vth와 대략 동등하다. 이때, 구동 트랜지스터(206)의 온/오프를 제어하는 데에 필요한 게이트 전위를 얻을 수 있으면 완전히 정상상태가 되지 않아도 된다. 그 후에, 제2 스위치(209)는 오프 상태가 되고, 용량소자(207)는 트랜지스터를 오프 상태로 하는 구동 트랜지스터(206)의 게이트 단자의 전위와, 제2 스위치(209)가 오프한 순간의 신호선 Dj에 공급되어 있는 아날로그 신호 전위 사이의 전위차를 유지한다. 이렇게 해서, i번째 행, j번째 열의 화소에 Data line(신호선 Dj)으로부터 아날로그 신호가 기록된다. 한편 이때, 각 화소 열마다 각각의 Data line(신호선 D1 ~ Dn)으로부터 각각의 아날로그 신호 전위가 공급되고, 각 열의 i번째 행의 화소에 아날로그 신호가 기록된다.

[0177] 다음으로, i+1번째 행의 G1 line(제1 주사선 G1ai+1)과 G2 line(제2 주사선 G2bi+1)에 펄스 신호가 입력되면, i+1번째 행, j번째 열의 화소의 Data line(신호선 Dj)에는 전위(Vb)가 입력되고, 화소에 아날로그 신호가 기록된다. 또한, 이때, 각 화소의 열마다 각각의 Data line(신호선 D1 ~ Dn)으로부터 각각의 아날로그 신호 전위가 공급되고, 각 열의 i+1번째 행의 화소에 아날로그 신호가 기록된다.

[0178] 이렇게, 화소의 각 행의 G1 line(제1 주사선 G1a1 ~ G1am)과 G2 line(제2 주사선 G2b1 ~ G2bm)에 펄스 신호가 공

급되고, 각각의 화소에 아날로그 신호가 기록되면 1프레임 기간의 화소부(204)에의 아날로그 신호의 기록 기간이 종료된다.

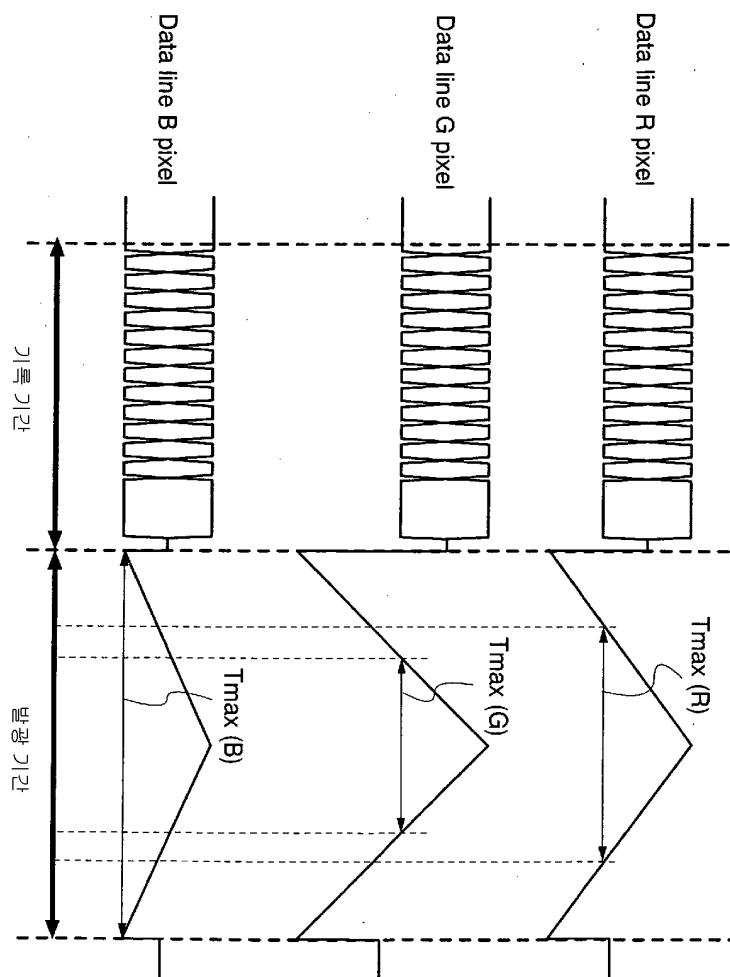

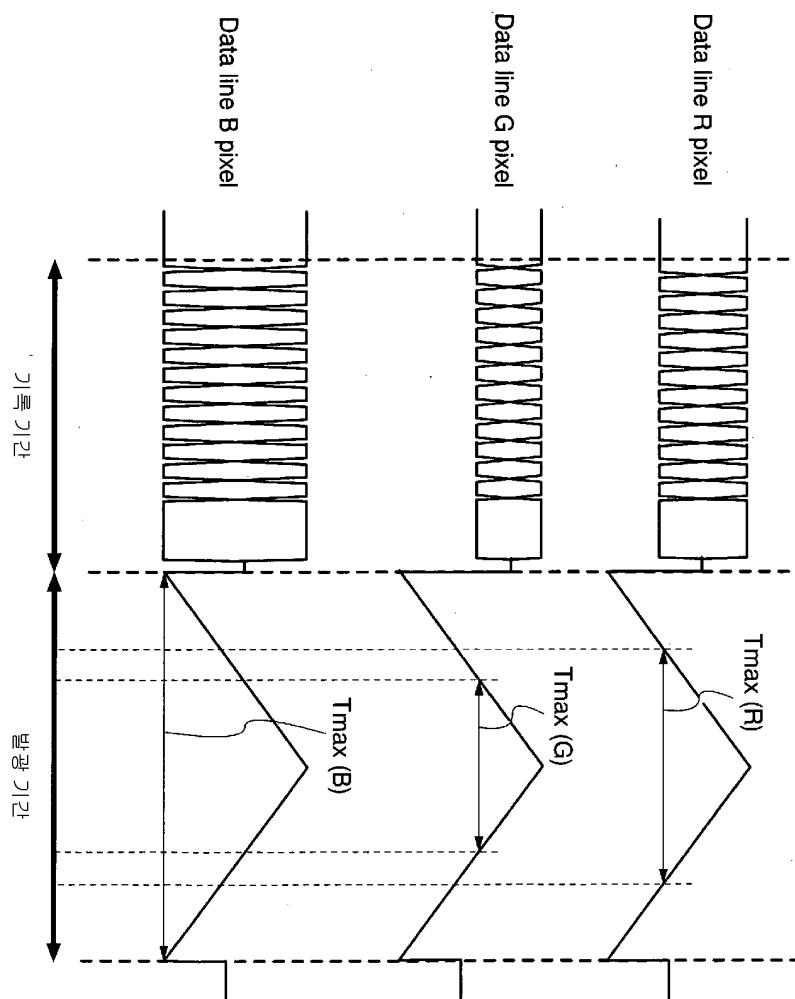

[0179] 계속해서, 모든 행의 화소의 제1 스위치(208)를 온, 제2 스위치(209)를 오프 상태로 하도록, 각각 제1 주사선 G1a1~G1am 및 제2 주사선 G2b1~G2bm에 신호를 공급하고, 도 3에 나타낸 바와 같이 Data line(신호선 D1~Dn)에 삼각파 전위를 공급한다. 그러면, i번째 행, j번째 열의 화소는 Data line가 Va보다 낮은 전위일 때에는 표시소자(210)를 비발광 상태로 유지하고, Data line이 Va보다 높은 기간(Ta)에는 표시소자(210)가 발광한다. 마찬가지로 i+1번째 행, j번째 열의 화소도 마찬가지로, 기간(Tb) 동안에 표시소자(210)는 발광한다.

[0180] 또한, 신호 기록 기간이 종료된 후, 아날로그 신호가 기록될 때 아날로그 신호 전위보다 낮은 전위가 Data line(신호선 D1~Dn)에 공급되는 동안에는 그 화소는 발광하지 않고, 기록된 아날로그 신호 전위보다 높아지면 발광하는 원리에 대해서는, 도 1의 화소 구성을 사용해서 설명한 바와 같으므로 여기에서는 상세한 설명을 생략한다.

[0181] 이렇게, 발광 기간에는, 전체 화소의 신호선 D1~Dn에 삼각파 전위가 공급되고, 각각 기록 기간에 아날로그 신호가 기록될 때의 아날로그 신호 전위에 따라 표시소자(210)의 발광 시간이 설정된다. 이렇게 해서, 아날로그 시간조표시가 가능해진다.

[0182] 이때, 표시소자(210)의 발광/비발광을 제어하는 구동 트랜지스터(206)의 온/오프는, 상기한 바와 같이, 기록 기간에 Data line(신호선 D1~Dn)에 공급된 아날로그 신호 전위가, 발광 기간에 Data line(신호선 D1~Dn)에 입력되는 삼각파 전위보다 높은지 또는 낮은지에 따라 결정되고, 디지털적으로 제어할 수 있다. 따라서, 구동 트랜지스터(206)의 특성의 편차의 영향을 적게 받고 구동 트랜지스터(206)의 온/오프를 제어할 수 있다. 즉, 각 화소의 발광의 편차를 개선할 수 있다.

[0183] 또한 본 발명의 화소 구성은 n형 트랜지스터를, 표시소자의 발광/비발광을 제어하는 구동 트랜지스터에 사용할 수 있다. 일반적으로 p형 트랜지스터보다 n형 트랜지스터의 이동도  $\mu$ 가 크다. 따라서, 같은 전류를 흘려보내는 경우, 트랜지스터 사이즈를 작게 할 수 있다. 따라서, 고화질의 표시장치를 제공할 수 있다. 또한 트랜지스터 사이즈를 작게 할 수 있으므로 화소의 개구율의 향상을 꾀할 수 있다. 따라서, 소비 전력이 저감된 표시장치를 제공할 수 있고, EL소자의 신뢰성도 향상된다.

[0184] 또한 화소부 전체 혹은 주변의 구동회로까지 포함시켜서 n형 트랜지스터만으로 구성되는 회로를 제공할 수 있으므로, 공정 수가 감소한, 저비용의 단극성 표시 패널을 제공할 수 있다.

[0185] 또한 표시장치 패널이 가지는 회로에 사용하는 박막 트랜지스터를 n형 트랜지스터만으로 구성할 수 있으므로, 아모포스 반도체나 세미 아모포스 반도체(혹은 미결정 반도체라고도 한다)를 반도체층에 사용한 박막 트랜지스터로 구성되는 회로를 가지는 표시장치를 제공할 수 있다. 예를 들면, 아모포스 반도체로는, 아모포스 실리콘(a-Si:H)을 들 수 있다. 따라서, 더욱, 비용을 낮출 수 있다. 이때, 도 1이나 도 2등에 나타내는 스위치는, 전기적인 스위치로 해도 되고 기계적인 스위치로 해도 된다. 전류의 흐름을 제어할 수 있으면 된다. 트랜지스터로 해도 되고, 다이오드로 해도 되며, 그것들을 조합한 논리회로로 해도 된다. 따라서, 스위치로서 트랜지스터를 사용할 경우, 그 트랜지스터는, 단순한 스위치로서 동작하므로, 트랜지스터의 도전형은 특별히 한정되지 않는다. 다만, 오프 전류가 적을수록 바람직할 경우, 오프 전류가 적은 쪽의 극성의 트랜지스터를 사용하는 것이 바람직하다. 오프 전류가 적은 트랜지스터로는, LDD영역을 설치한 트랜지스터 등이 있다. 또한 스위치로서 동작시키는 트랜지스터의 소스 단자의 전위가, 저전위측 전원(Vss, GND, 0V 등)에 가까운 상태에서 동작하는 경우에는 n형을, 반대로, 소스 단자의 전위가, 고전위측 전원(Vdd 등)에 가까운 상태에서 동작하는 경우에는 p형을 사용하는 것이 바람직하다. 왜냐하면, 게이트 소스 간 전압의 절대치를 크게 할 수 있어, 스위치로서, 동작하기 쉽기 때문이다. 한편, n형과 p형을 모두 사용하여, CMOS형 스위치로 해도 된다.

[0186] 이때, 본 실시예에 있어서, 표시소자를 구동하는 구동 트랜지스터의 소스 단자 및 드레인 단자, 및 표시소자의 양극 및 음극은, 표시소자에 순방향 전압이 인가될 때의 단자 및 전극을 말한다.

[0187] (실시예 2)

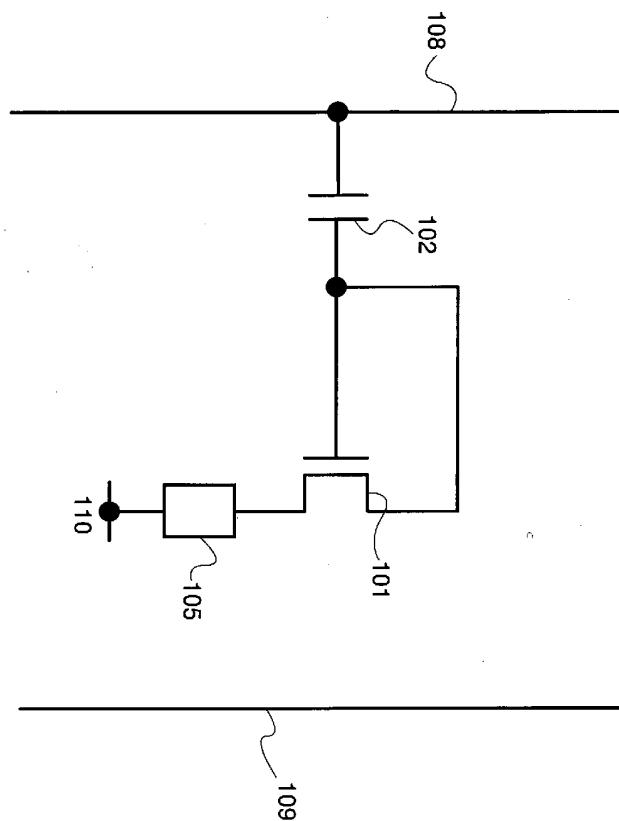

[0188] 본 실시예에서는, 실시예 1의 화소 구성과는 다른 구성을 나타낸다. 본 실시예에 나타내는 화소 구성은, 화소에 아날로그 신호를 기록할 때에 공급되는 아날로그 신호 전위와, 화소의 발광, 비발광을 제어하는 아날로그 신호 전위를 다른 배선에 의해 화소에 공급하는 구성으로 한다.

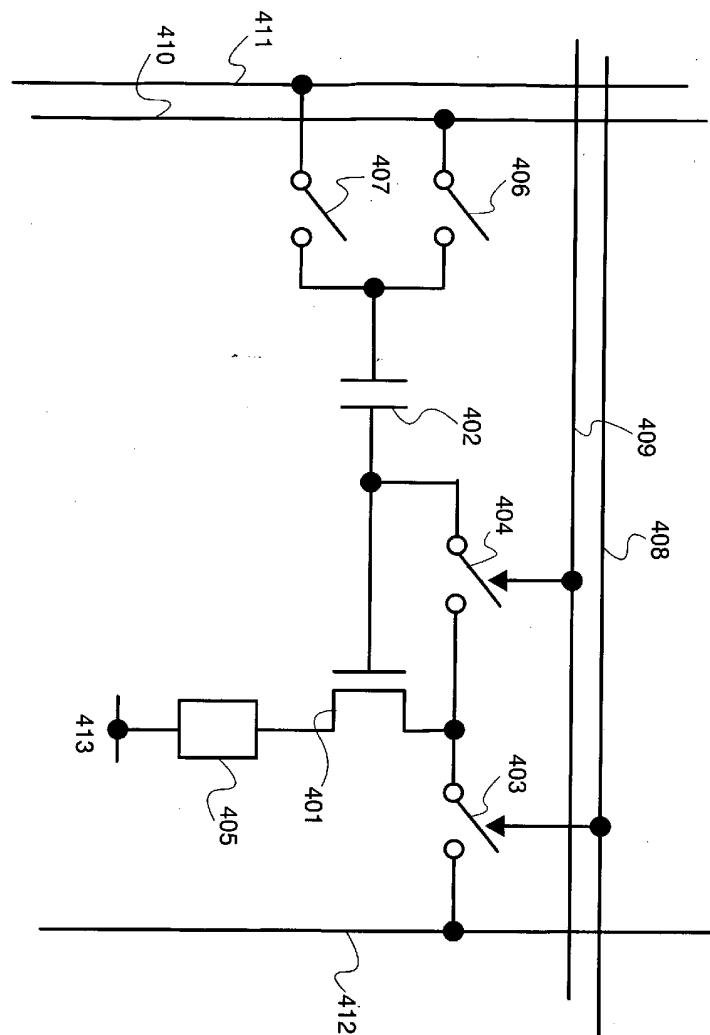

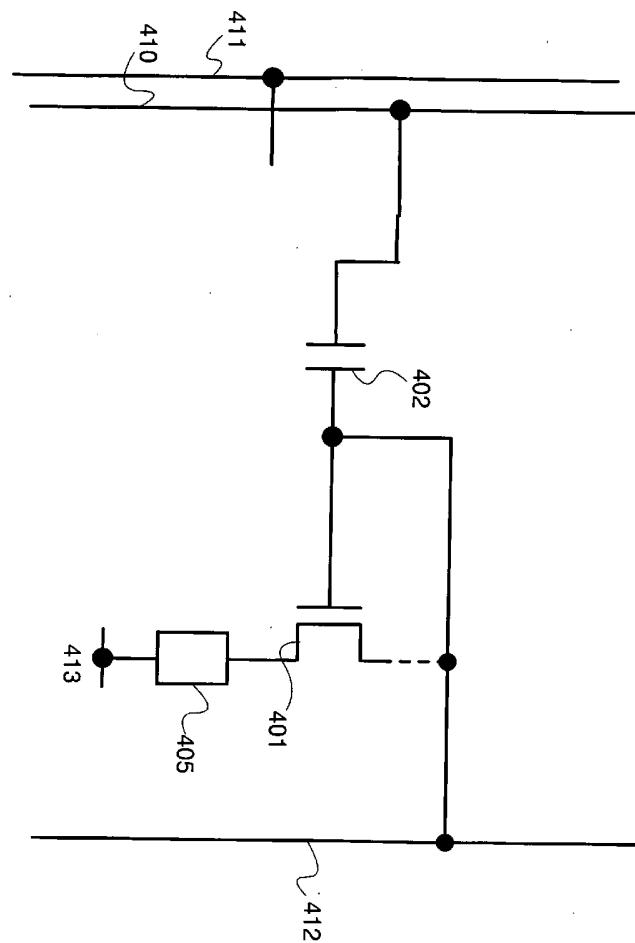

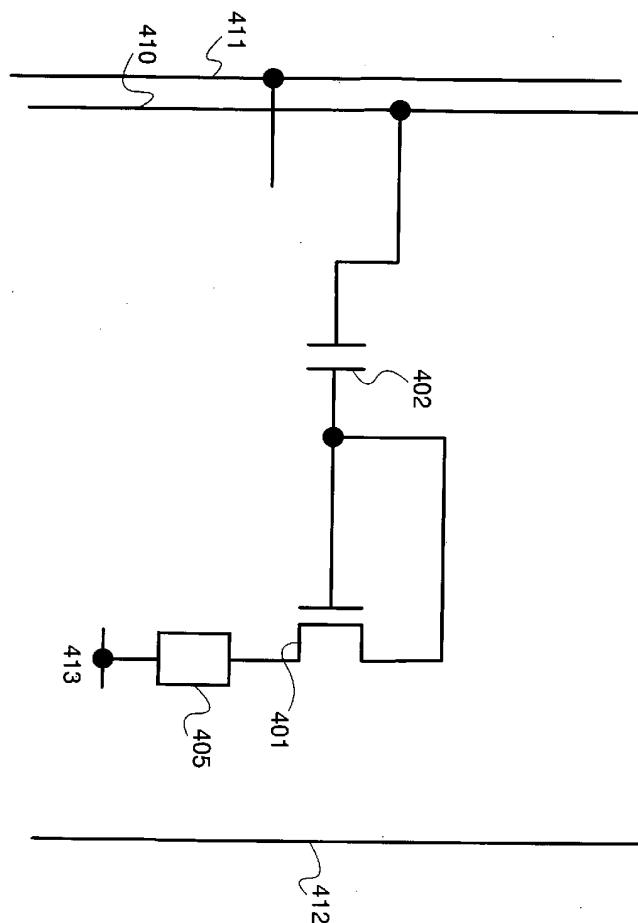

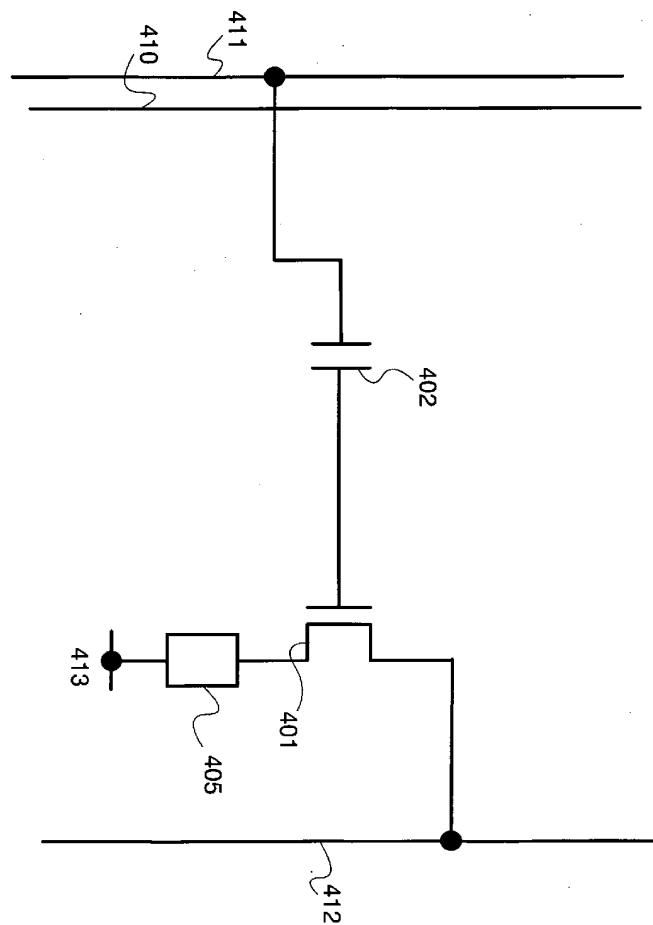

[0189] 우선, 도 4를 사용해서 본 발명의 표시장치의 화소 구성에 대해서 상세히 설명한다. 화소는 구동 트랜지스터

(401)와, 용량소자(402)와, 제1 스위치(403)와, 제2 스위치(404)와, 표시소자(405)와, 제3 스위치(406)와, 제4 스위치(407)와, 제1 주사선(G1 line)(408)과, 제2 주사선(G2 line)(409)과, 제1 신호선(Data1 line)(410)과, 제2 신호선(Data2 line)(411)과, 전원선(Supply line)(412)을 구비한다. 이때, 구동 트랜지스터(401)에는 n형 트랜지스터를 사용한다.

[0190] 구동 트랜지스터(401)의 소스 단자는 표시소자(405)의 양극과 접속되고, 게이트 단자는 용량소자(402)의 한쪽 전극과 접속되고, 용량소자(402)의 다른 쪽 전극은, 제3 스위치(406)를 통해 제1 신호선(410)과, 제4 스위치(407)를 통해 제2 신호선(411)과 접속된다. 구동 트랜지스터(401)의 드레인 단자는 제1 스위치(403)를 통해 전원선(412)과 접속된다. 또한, 전원선(412)에는 전원전위 Vdd가 공급된다. 또한, 전원선에 공급하는 전위는 Vdd에 한정되지 않고, 예를 들면, 색 요소 RGB로 이루어진 폴 컬러 표시의 경우에는, RGB의 각각의 색 요소의 화소마다 전원선의 전위의 값을 변환해도 된다.

[0191] 또한 구동 트랜지스터(401)의 게이트 단자와 드레인 단자는 제2 스위치(404)를 통해 접속된다. 따라서 제2 스위치(404)가 온 상태일 때에는 구동 트랜지스터(401)의 게이트 단자와 드레인 단자는 도통한다. 그리고, 제2 스위치(404)가 오프 상태가 되면, 구동 트랜지스터(401)의 게이트 단자와 드레인 단자는 비도통이 되고, 그 순간의 구동 트랜지스터(401)의 게이트 단자(드레인 단자)와 제1 신호선(410)에 공급되는 아날로그 신호 전위 사이의 전위차(전압)를 용량소자(402)는 유지한다. 또한 표시소자(405)의 음극은 Vss의 전위가 공급된 배선(413)과 접속된다. 이때, Vss는 Vss<Vdd를 만족시키는 전위다. 예를 들면, Vss=GND(접지 전위)로 해도 된다.

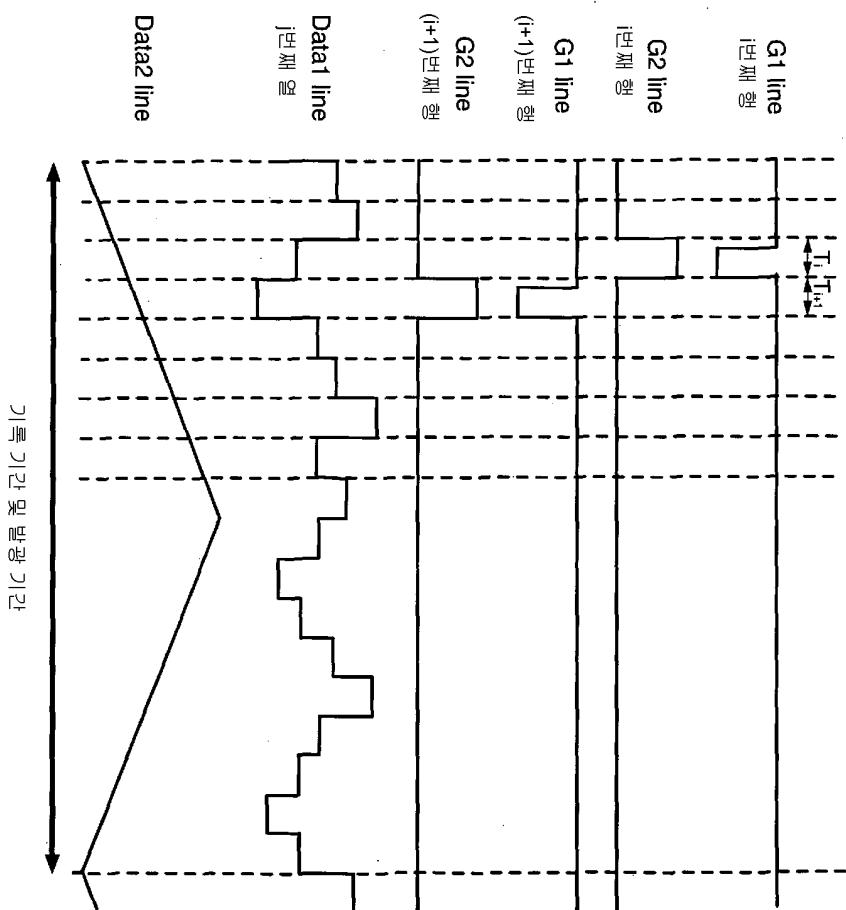

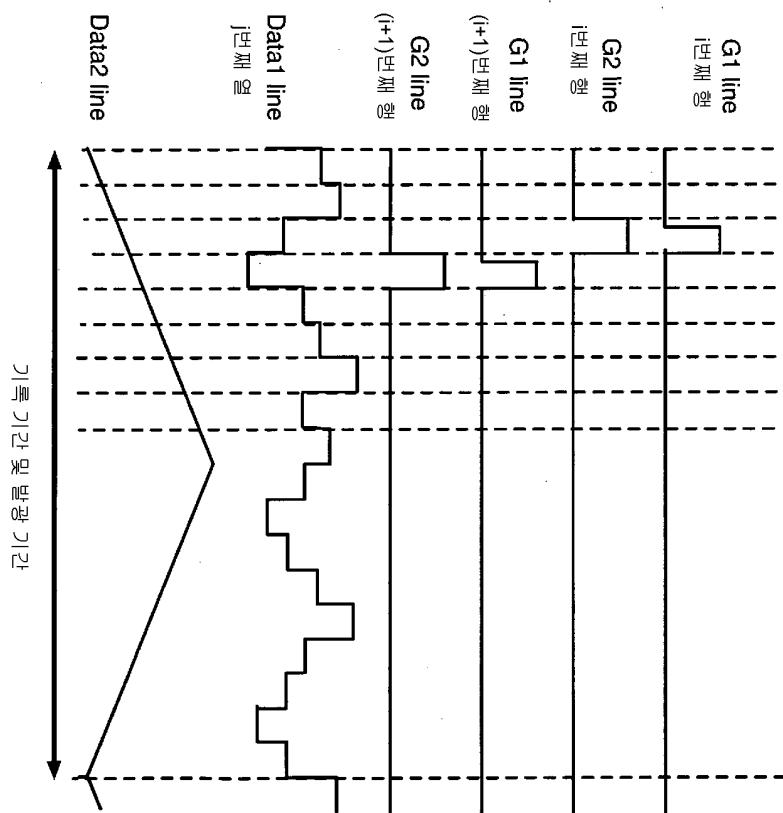

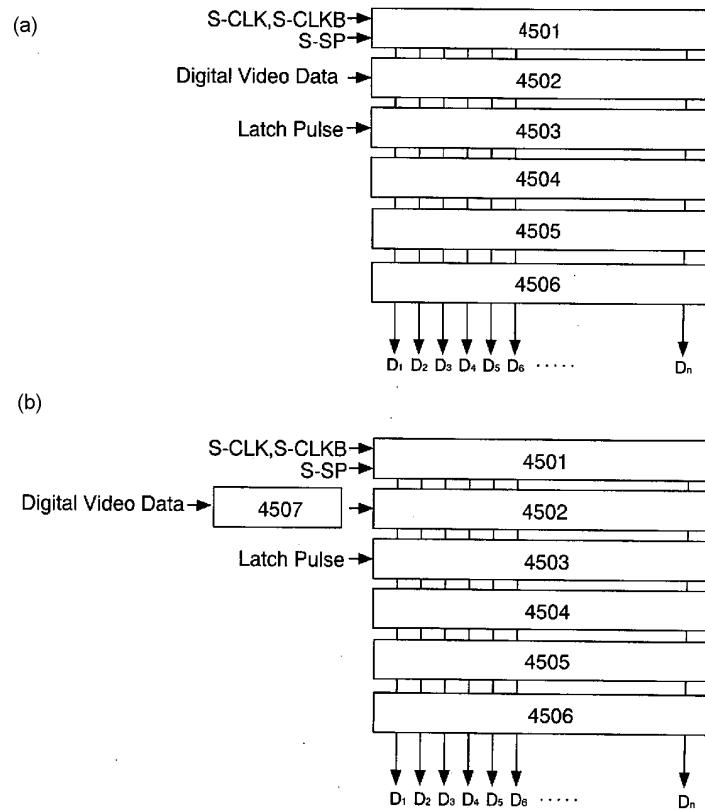

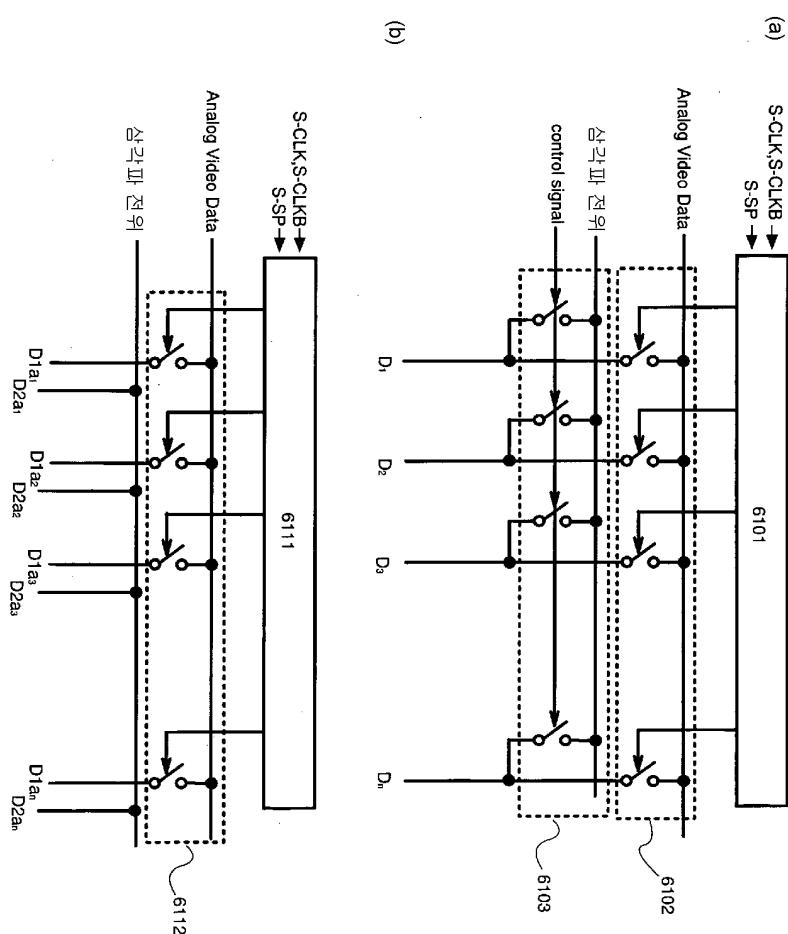

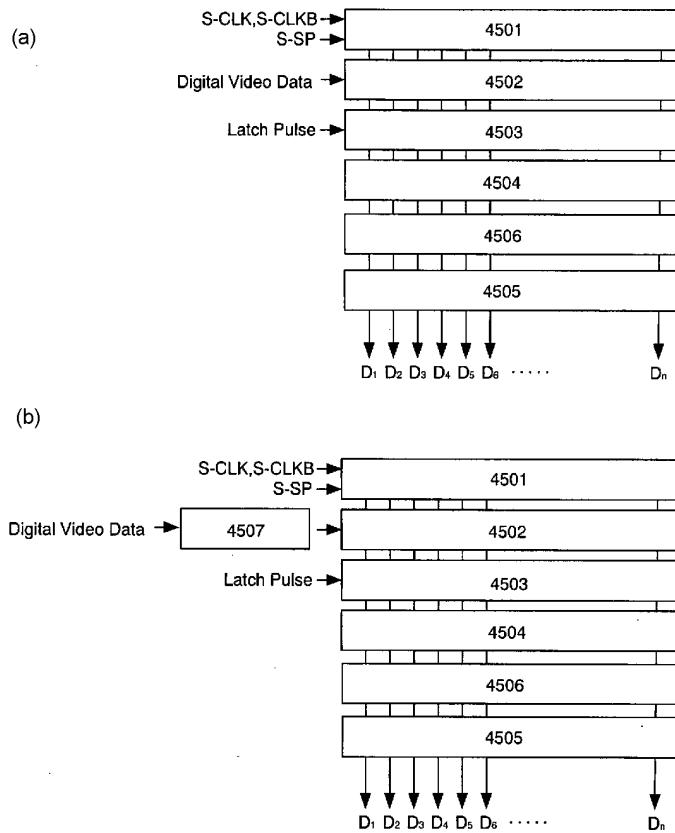

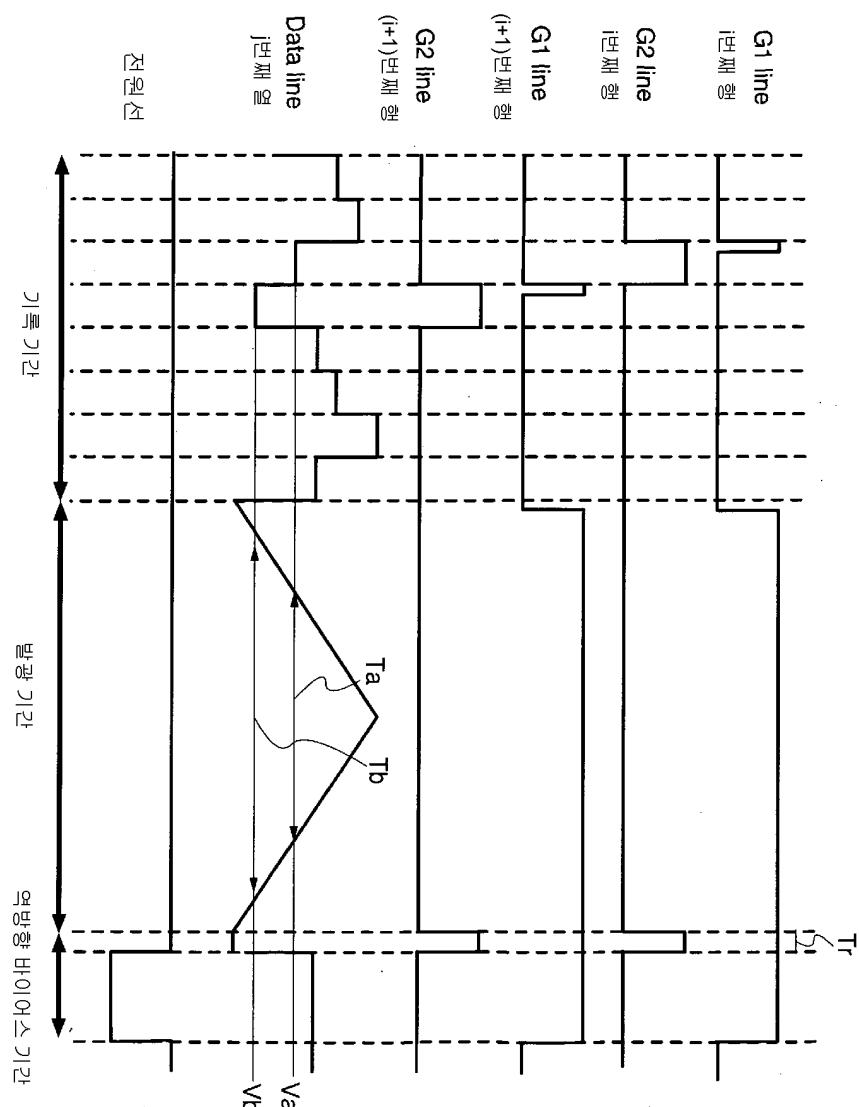

[0192] 다음으로, 도 4의 화소 구성의 동작 원리에 대해서 도 5를 사용해서 간단히 설명한다. 도 5에 나타내는 타이밍 차트는 복수의 도 4에 나타내는 화소가 매트릭스로 배치된 표시장치의 j번째 열의 화소 열의 타이밍 차트를 나타낸다. 또한 도 5에 나타내는 타이밍 차트에 있어서, G1 line(제1 주사선), G2 line(제2 주사선)의 신호가 H레벨일 때에, 각각 제1 스위치(403), 제2 스위치(404)는 온 상태가 되고, L레벨일 때에 오프 상태가 되는 것으로 한다.

[0193] 도 4의 화소에서는, 각 화소의 계조를 결정하는 아날로그 신호 전위가 제1 신호선(410)에 공급되고, 각각 화소의 발광 시간을 제어하는 전위가 제2 신호선(411)에 공급된다.

[0194] 이때, 제2 신호선(411)에 공급되는 전위는, 실시예 1에 나타낸 바와 같이, 과형(5901), 과형(5902), 과형(5903), 과형(5904), 과형(5905), 과형(5906) 혹은 과형(5907), 과형(5908), 과형(5909), 또는 이것들을 복수 개 연속으로 공급해도 된다.

[0195] 연속으로 공급함으로써, 발광 시간을 1프레임 내에서 분산시킬 수 있다. 그 결과, 프레임 주파수가 외형상 향상되게 되고, 화면의 깜박거림을 방지할 수 있다.

[0196] 이때, 본 실시예의 화소 구성을 가지는 표시장치는, 화소부의 행마다 신호 기록 기간과 발광 기간이 설정된다.

[0197] 여기에서, i번째 행의 화소의 신호 기록 기간에 관하여 설명한다. 도 5에 나타내는 Ti기간이 i번째 행의 화소의 신호 기록 시간을 나타낸다. 그리고, Ti기간 이외의 기간에는 i번째 행의 화소는 발광 기간이 된다.

[0198] 우선, 화소의 기록 기간 Ti에는 제3 스위치(406)를 온 상태로 하고, 제4 스위치(407)를 오프 상태로 한다. 그리고, G2 line(제2 주사선(409))은 기록 기간 Ti에는 H레벨의 신호가 입력되고, G1 line(제1 주사선(408))은 기록 기간에, H레벨로부터 L레벨로 내려간다. 즉, 제2 주사선(409) 및 제1 주사선(408)이 H레벨인 기간에는 제2 스위치(404) 및 제1 스위치(403)는 온 상태가 된다. i번째 행의 화소의 구동 트랜지스터(401)의 드레인 단자는 전원선(412)으로부터의 전원전위(Vdd)가 공급되고, 용량소자(402), 구동 트랜지스터(401) 및 표시소자(405)에 전류가 흐른다. 그리고, 용량소자(402)에서는 전하의 축적 혹은 방전이 행해진다. 즉, 용량소자(402)에 원래 축적되어 있던 전하와 Data1 line(제1 신호선(410))에 공급된 전위 사이의 관계에 따라 전하의 축적 또는 방전이 일어난다. 그리고, G1 line(제1 주사선(408))의 신호가 H레벨로부터 L레벨로 하강하면, 제2 스위치(404)는 온인 상태에서, 제1 스위치(403)는 오프 상태가 된다. 제1 스위치(403)가 오프 상태인 순간은, 구동 트랜지스터(401)의 게이트 단자는 전원전위(Vdd)가 공급되어 있기 때문에 구동 트랜지스터(401)는 온 상태가 된다. 따라서, 구동 트랜지스터(401), 표시소자(405) 및 용량소자(402)에 전류가 흐른다. 잠시 후, 구동 트랜지스터(401), 표시소자(405) 및 용량소자(402)에 전류가 흐르지 않게 된다. 즉 정상상태가 된다.

[0199] 이렇게 해서, 구동 트랜지스터(401)는 오프 상태가 된다. 구동 트랜지스터(401)의 온/오프를 제어하는 데에 필요한 게이트 전위를 얻을 수 있으면 완전히 정상상태가 되지 않아도 된다.

[0200] 그 후에 G1 line(제1 주사선(408))에 공급되는 신호는 H레벨로 상승하고, G2 line(제2 주사선(409))에 공급되는

신호는 L레벨로 하강한다. 즉, 제1 스위치(403)는 온 상태가 되고, 제2 스위치(404)는 오프 상태가 된다. 그러면, 용량소자(402)는 트랜지스터를 오프 상태로 하는 구동 트랜지스터(401)의 게이트 단자의 전위와, 제2 스위치(404)가 오프 상태인 순간의 제1 신호선(410)에 공급된 아날로그 신호 전위 사이의 전위차를 유지한다.

[0201] 이렇게 해서, i번째 행, j번째 열의 화소에 Data1 line(제1 신호선(410))으로부터 아날로그 신호가 기록된다. 또한, 이때, 각 화소의 열마다 각각의 Data1 line(제1 신호선(410))으로부터 각각의 아날로그 신호 전위가 입력되고, 각 열의 i번째 행의 화소에 아날로그 신호가 기록된다.

[0202] 이렇게 해서, i번째 행의 화소의 신호 기록 기간  $T_i$ 가 종료되면,  $i+1$ 번째 행의 화소의 신호 기록 기간  $T_{i+1}$ 이 시작되고, i번째 행의 화소는 발광 기간이 된다.

[0203] i번째 행의 화소의 발광 기간에는 i번째 행의 화소의 제3 스위치(406)를 오프 상태로 하고, 제4 스위치(407)를 온 상태로 한다.

[0204] 이때, 도 5에 나타낸 바와 같이 Data2 line(제2 신호선411)에는 삼각파 전위가 공급된다. i번째 행, j번째 열의 화소는 Data2 line(제2 신호선411)이, i번째 행의 화소의 신호 기록 기간  $T_i$ 에 Data1 line(제1 신호선(410))에 공급된 아날로그 신호 전위보다 낮은 전위일 때에는 표시소자(405)는 비발광 상태를 유지하고, Data2 line(제2 신호선411)이, i번째 행의 화소의 신호 기록 기간  $T_i$ 에 Data1 line(제1 신호선(410))에 공급된 아날로그 신호 전위보다 높은 전위인 동안, 표시소자(405)는 발광한다. 따라서, 기록 기간에 아날로그 신호가 기록될 때의 아날로그 신호 전위에 따라 표시소자(405)의 발광 시간이 설정된다. 이렇게 해서, 아날로그 시간계조표시가 가능해진다.

[0205] 이렇게 본 실시예의 화소 구성은 표시장치에서는, 화소 행마다 순차로, 신호 기록 기간이 시작되고, 신호 기록 기간이 종료되면 화소 행마다 발광 기간으로 이어진다. 본 실시예와 같이 선 순차로 신호가 화소에 기록되는 경우에는, 기록 기간에는 하나의 화소만큼의 시간이 요구되므로, 발광 기간을 길게 할 수 있다. 즉, 듀티비(1프레임 기간에 있어서의 발광 기간의 비율)가 높으므로, 표시소자의 순간 휘도를 낮게 할 수 있다. 따라서, 표시소자의 신뢰성을 향상시킬 수 있다.

[0206] 또한 각 행에 있어서 화소의 기록 기간을 길게 할 수 있으므로, Data1 line(제1 신호선(410))에 아날로그 신호 전위를 입력하는 신호선 구동회로의 주파수를 낮출 수 있다. 따라서, 소비 전력을 줄일 수 있다.

[0207] 이때, 표시소자(405)의 발광/비발광을 제어하는 구동 트랜지스터(401)의 온/오프는, 상기한 바와 같이, 기록 기간에 Data1 line(제1 신호선(410))에 공급되는 아날로그 신호 전위가, 발광 기간에 Data2 line(제2 신호선411)에 입력되는 삼각파 전위보다 높은지 또는 낮은지에 따라 결정되고, 디지털적으로 제어할 수 있다. 따라서, 구동 트랜지스터(401)의 특성의 편차의 영향을 적게 받고 구동 트랜지스터(401)의 온/오프를 제어할 수 있다. 즉, 각 화소의 발광의 편차를 개선할 수 있다.

[0208] 또한 본 발명의 화소 구성은 n형 트랜지스터를, 표시소자의 발광/비발광을 제어하는 구동 트랜지스터에 사용할 수 있다. 일반적으로 p형 트랜지스터보다 n형 트랜지스터의 이동도  $\mu$ 가 크다. 따라서, 같은 전류를 흘려보내면서, 트랜지스터 사이즈를 작게 할 수 있다. 따라서, 화소의 개구율이 향상되고, 고화질 표시나 소비 전력이 저감된 표시장치를 제공할 수 있다.

[0209] 또한 화소 영역 전체 혹은 주변의 구동회로까지 포함시켜서 n형 트랜지스터만으로 구성되는 회로를 제공할 수 있으므로, 공정 수가 삭감된, 저비용의 단극성 표시장치 패널을 제공할 수 있다.

[0210] 또한 표시장치 패널이 가지는 회로에 사용하는 박막 트랜지스터를 n형 트랜지스터만으로 구성할 수 있으므로, 아모포스 반도체나 세미 아모포스 반도체(혹은 미결정 반도체라고도 한다)를 반도체층에 사용한 박막 트랜지스터로 구성되는 회로를 가지는 표시장치를 제공할 수 있다. 예를 들면, 아모포스 반도체로는, 아모포스 실리콘(a-Si:H)을 들 수 있다.

[0211] 이때, 본 실시예에 있어서, 표시소자를 구동하는 구동 트랜지스터의 소스 단자 및 드레인 단자, 및 표시소자의 양극 및 음극은, 표시소자에 순방향의 전압이 인가될 때의 단자 및 전극을 말한다.

[0212] (실시예 3)

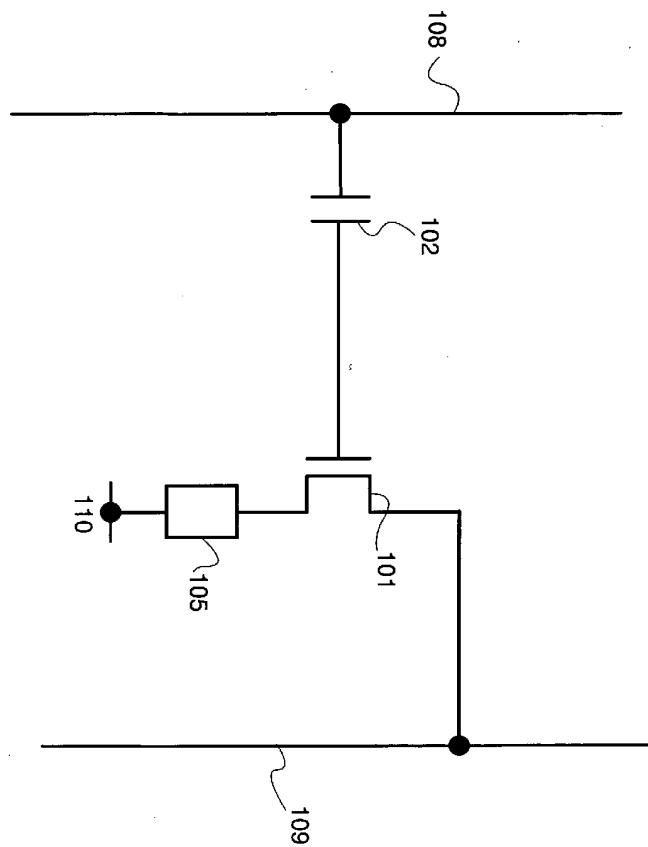

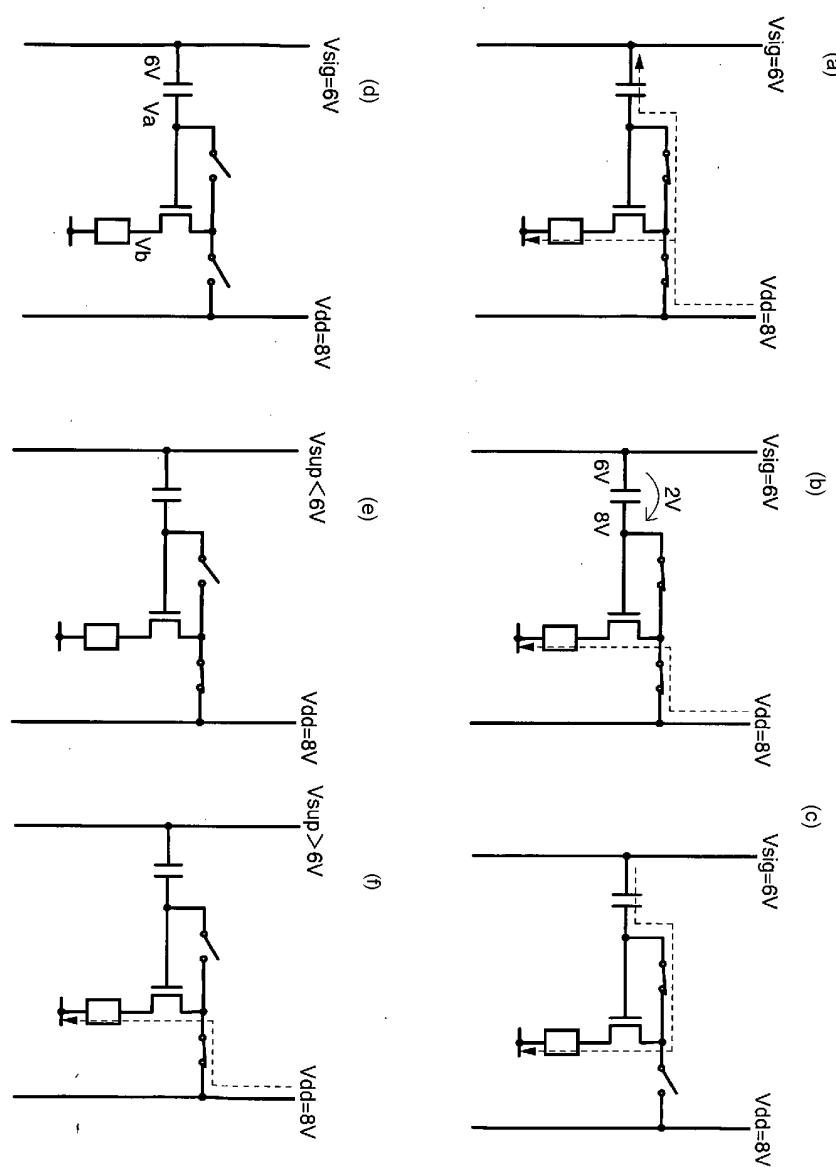

[0213] 본 실시예에서는, 실시예 1 및 실시예 2에 나타낸 화소 구성의 스위치에 n형 트랜지스터를 적용한 경우에 관하여 설명한다.

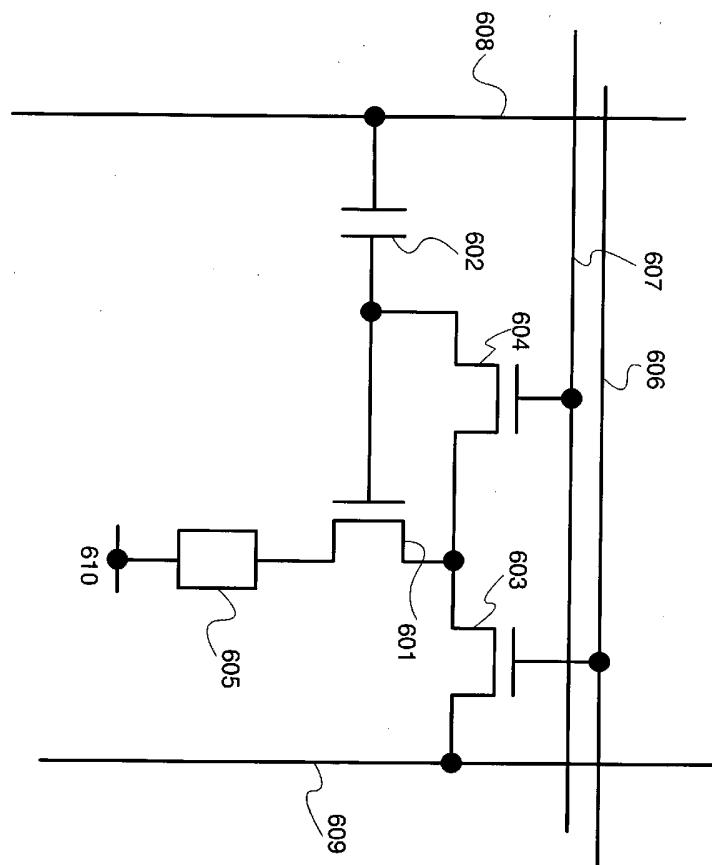

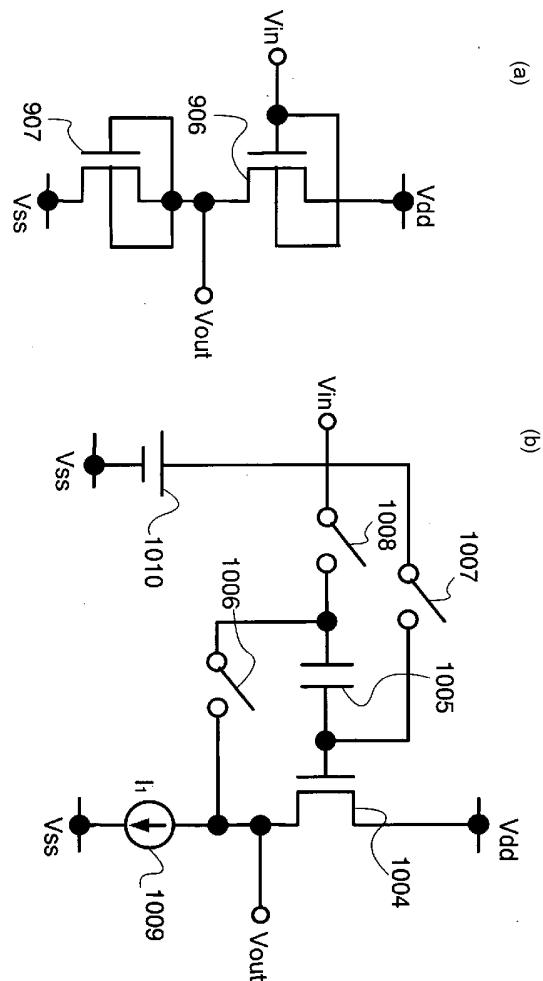

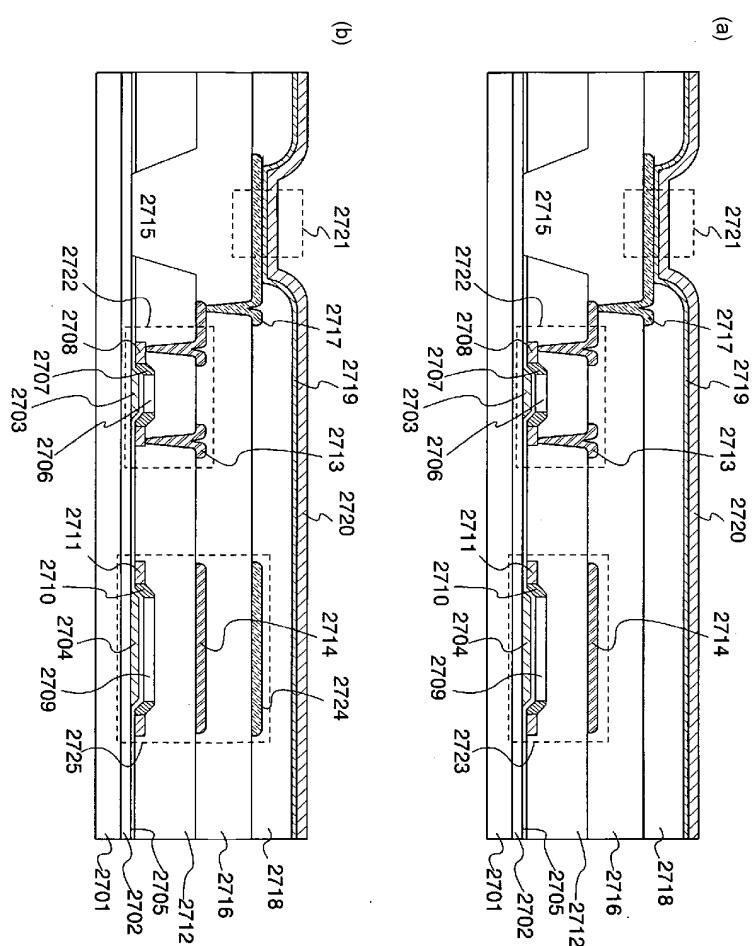

[0214] 우선, 도 6을 사용해서 실시예 1에 나타낸 도 1의 화소 구성의 스위치에 n형 트랜지스터를 적용한 경우에 관하

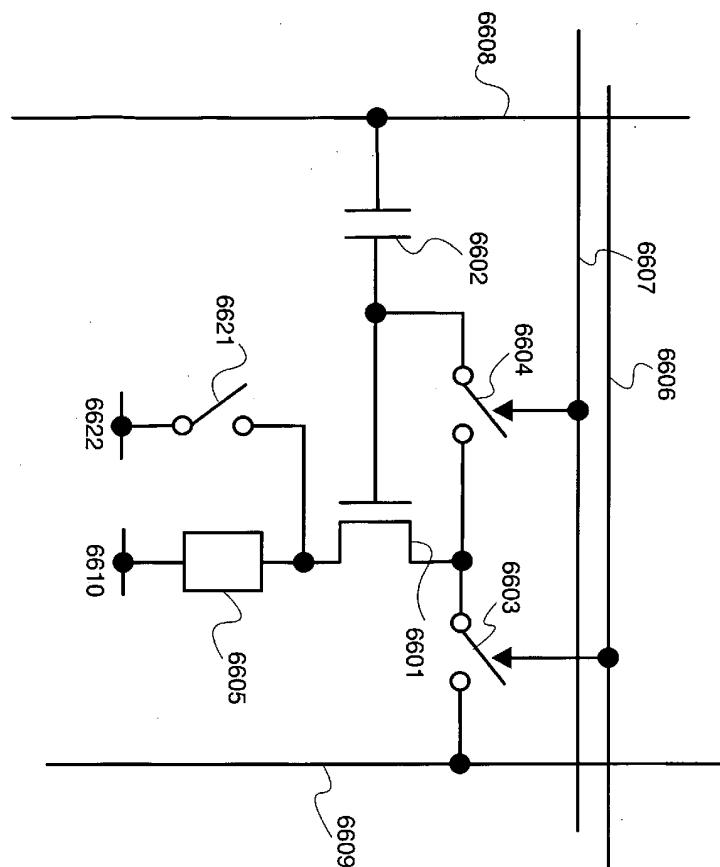

여 설명한다. 화소는 구동 트랜지스터(601)와, 용량소자(602)와, 제1 스위칭용 트랜지스터(603)와, 제2 스위칭용 트랜지스터(604)와, 표시소자(605)와, 제1 주사선(G1 line)(606)과, 제2 주사선(G2 line)(607)과, 신호선(Data line)(608)과, 전원선(Supply line)(609)을 구비한다. 이때, 구동 트랜지스터(601), 제1 스위칭용 트랜지스터(603) 및 제2 스위칭용 트랜지스터(604)에는 n형 트랜지스터를 사용한다.

[0215] 구동 트랜지스터(601)의 소스 단자는 표시소자(605)의 양극과 접속되고, 게이트 단자는 용량소자(602)를 통해 신호선(608)과 접속되고, 드레인 단자는 제1 스위칭용 트랜지스터(603)의 소스 단자 및 제2 스위칭용 트랜지스터(604)의 제1 단자(소스 단자 또는 드레인 단자)와 접속된다. 또한 제1 스위칭용 트랜지스터(603)의 드레인 단자는 전원선(609)과 접속되고, 게이트 단자는 제1 주사선(606)과 접속된다. 따라서, 제1 주사선(606)에 H레벨의 신호를 공급하면 제1 스위칭용 트랜지스터(603)는 온 상태가 되고, 전원선(609)에 공급된 전원전위 Vdd를 구동 트랜지스터(601)의 드레인 단자에 공급할 수 있다. 또한 제2 스위칭용 트랜지스터(604)의 제2 단자(소스 단자 또는 드레인 단자)는 구동 트랜지스터(601)의 게이트 단자와 접속된다. 따라서, 제2 주사선(607)에 H레벨의 신호를 공급하면 제2 스위칭용 트랜지스터(604)는 온 상태가 되고, 구동 트랜지스터(601)의 드레인 단자와 게이트 단자를 도통할 수 있다. 그리고, 제2 스위칭용 트랜지스터(604)가 오프 상태가 되면, 구동 트랜지스터(601)의 게이트 단자와 드레인 단자는 비도통이 되고, 그 순간의 구동 트랜지스터(601)의 게이트 단자(드레인 단자)와 신호선(608) 사이의 전위차(전압)를 용량소자(602)는 유지할 수 있다. 또한 표시소자(605)의 음극은 Vss의 전위가 공급된 배선(610)과 접속된다. 이때, Vss는 Vss<Vdd를 만족시키는 전위다. 예를 들면, Vss=GND(접지 전위)로 해도 된다. 이때, 전원선에 공급하는 전위는 Vdd에 한정되지 않고, 예를 들면, 색 요소 RGB로 이루어진 풀 컬러 표시의 경우에는, RGB의 각각의 색 요소의 화소마다 전원선의 전위의 값을 변환해도 된다.

[0216] 한편, 도 6의 화소 구성의 동작에 대해서는, 도 1의 화소 구성과 같으므로 생략한다.

[0217] 여기에서, 스위칭용 트랜지스터는 리크 전류(오프 전류 및 게이트 리크 전류)가 적은 구성으로 하는 것이 바람직하다고 할 수 있다. 오프 전류는, 트랜지스터가 오프 상태일 때, 소스 드레인 간에 흐르게 되는 전류이며, 게이트 리크 전류는, 게이트 절연막을 통해 게이트와 소스 또는 드레인 간에 전류가 흐르는 전류다.

[0218] 따라서, 제1 스위칭용 트랜지스터(603) 및 제2 스위칭용 트랜지스터(604)로 사용되는 N채널형 트랜지스터는, 저농도 불순물영역(Lightly Doped Drains:LDD영역이라고도 한다)을 설치한 구성으로 하는 것이 바람직하다. LDD영역을 설치한 구성의 트랜지스터는 오프 전류를 저감할 수 있기 때문이다. 혹은 제2 스위칭용 트랜지스터(604)에만 LDD영역을 설치한다. 제2 스위칭용 트랜지스터(604)에 오프 전류가 흐르면, 용량소자(602)의 전하를 보유할 수 없게 되고, 제1 스위칭용 트랜지스터(603)는 표시소자(605)에 전류를 흐르게 할 때에 온 전류를 크게 할 필요가 있기 때문이다.

[0219] 보다 바람직한 형태로는, 제2 스위칭용 트랜지스터(604) 및 제1 스위칭용 트랜지스터(603)에 LDD영역을 설치하고, 적어도 제1 스위칭용 트랜지스터(603)의 LDD영역에는 게이트 전극과 부분적으로 겹치는 영역을 설치한다. 그러면, 제2 스위칭용 트랜지스터(604)는 오프 전류를 저감하고, 제1 스위칭용 트랜지스터(603)는 온 전류를 크게 하고, 핫 일렉트론의 발생을 더욱 저감할 수 있다. 따라서, 제1 스위칭용 트랜지스터(603)의 신뢰성이 향상된다.

[0220] 또한 구동 트랜지스터(601)에도 LDD영역을 설치하고, LDD영역이 게이트 전극과 겹치는 구조로 함으로써 신뢰성이 향상된다.

[0221] 또한 게이트 절연막의 막 두께를 얇게 해도 오프 전류는 저감할 수 있다. 따라서, 구동 트랜지스터(601)의 막 두께보다 제1 스위칭용 트랜지스터(603) 및 제2 스위칭용 트랜지스터(604)의 막 두께를 얇게 하는 것이 바람직하다.

[0222] 또한 제1 스위칭용 트랜지스터(603) 및 제2 스위칭용 트랜지스터(604)를 멀티 게이트 트랜지스터로 함으로써 게이트 리크 전류를 저감할 수 있다.

[0223] 특히, 제2 스위칭용 트랜지스터(604)에 오프 전류가 흐르게 되면, 용량소자(602)는 기록 기간에 기록된 전압을 유지할 수 없게 되므로, 제2 스위칭용 트랜지스터(604)에만 LDD영역을 설치하거나, 게이트 절연막을 얇게 하거나, 멀티 게이트로 해도 된다.

[0224] 이때, 제1 주사선(606)의 H레벨의 전위는, 전원선(609)의 전위보다 제1 스위칭용 트랜지스터(603)의 역치전압 Vth 이상 높은 것이 바람직하다. 또한 마찬가지로, 제2 주사선(607)의 H레벨의 전위도, 전원선(609)의 전위보다 제2 스위칭용 트랜지스터(604)의 역치전압 Vth 이상 높은 것이 바람직하다.

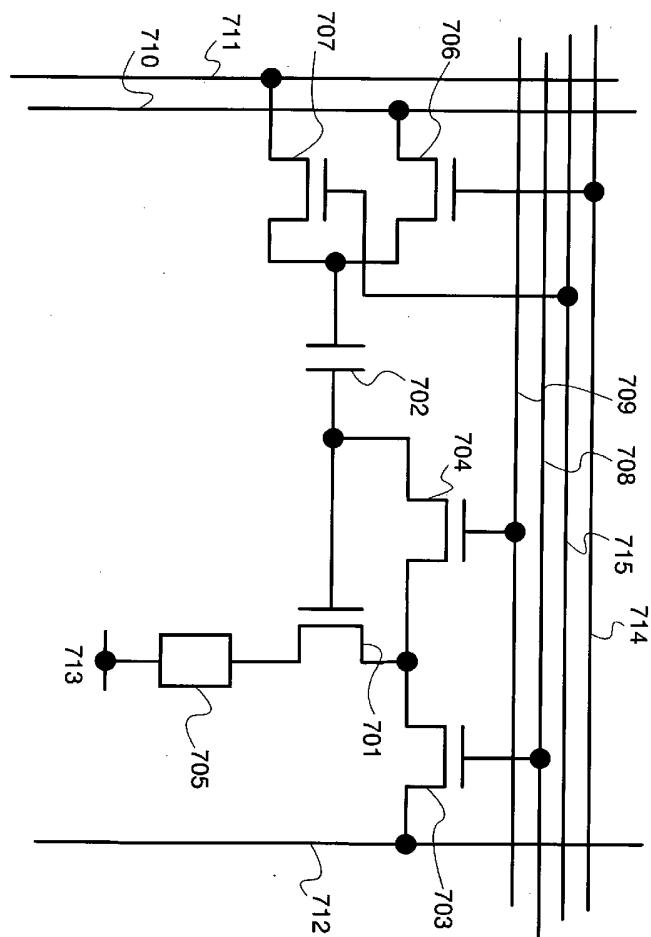

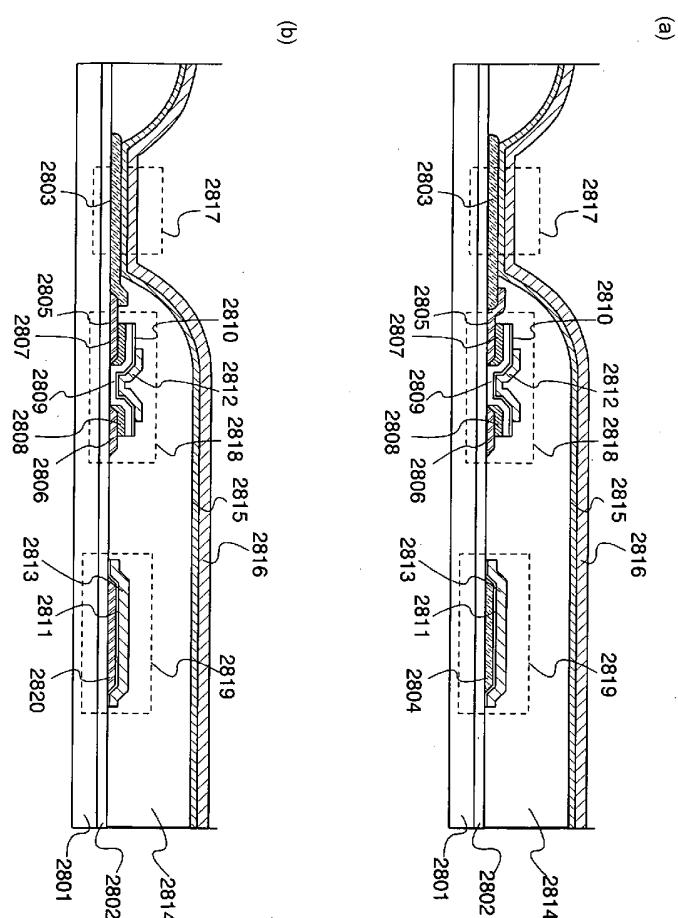

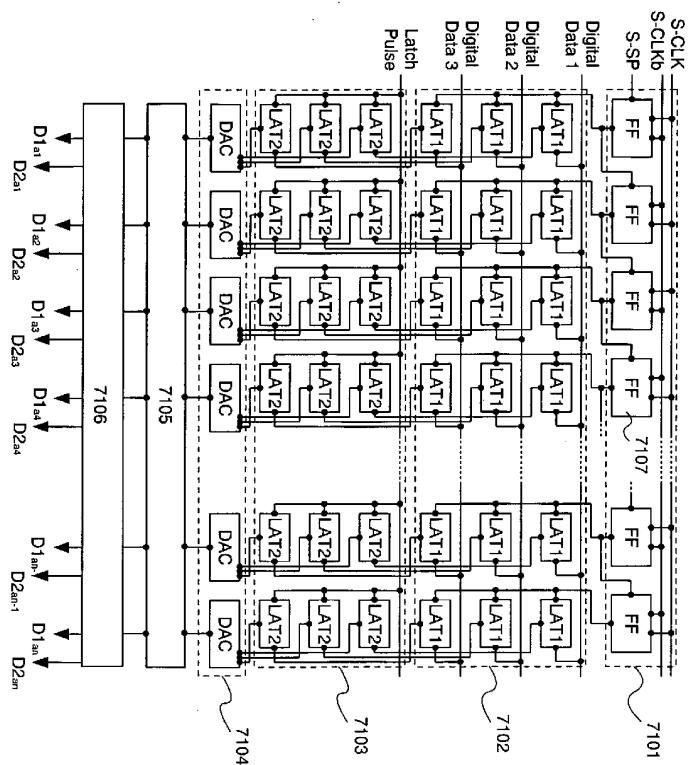

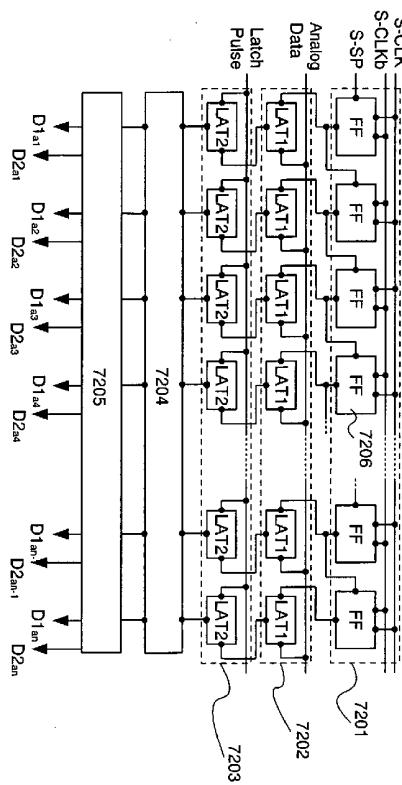

- [0225] 다음으로, 도 7을 사용해서 실시예 2에 나타낸 도 4의 화소 구성의 스위치에 n형 트랜지스터를 적용한 경우에 관하여 설명한다.

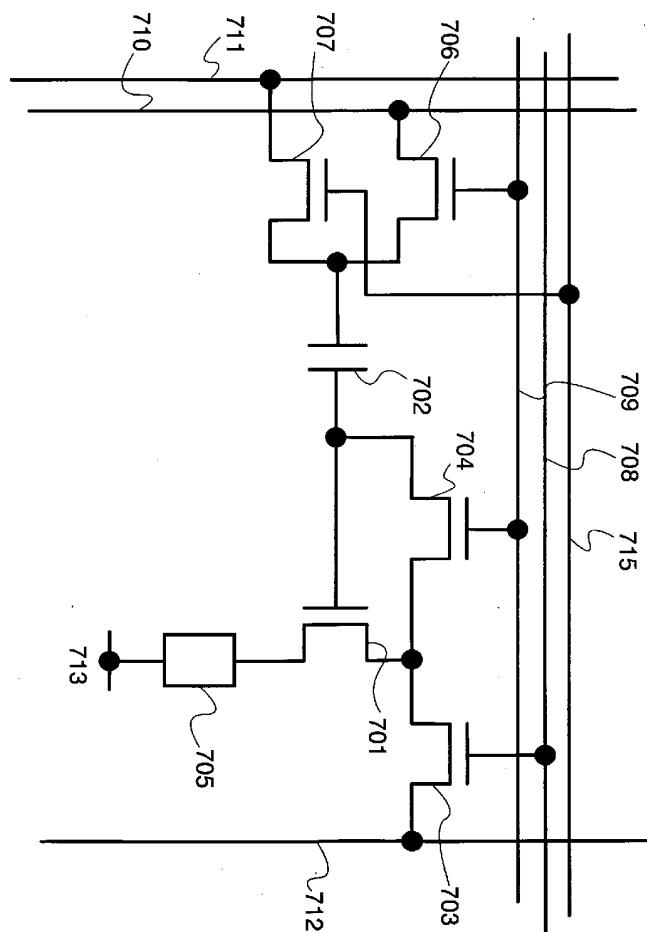

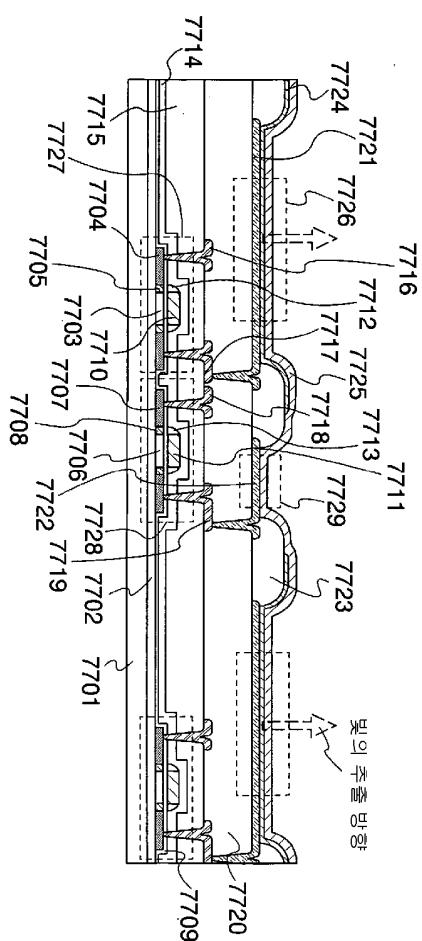

- [0226] 화소는 구동 트랜지스터(701)와, 용량소자(702)와, 제1 스위칭용 트랜지스터(703)와, 제2 스위칭용 트랜지스터(704)와, 표시소자(705)와, 제3 스위칭용 트랜지스터(706)와, 제4 스위칭용 트랜지스터(707)와, 제1 주사선(G1 line)(708)과, 제2 주사선(G2 line)(709)과, 제1 신호선(Data line1)(710)과, 제2 신호선(Data line2)(711)과, 전원선(Supply line)(712)과, 제3 주사선(714)과 제4 주사선(715)을 구비한다. 이때, 구동 트랜지스터(701), 제1 스위칭용 트랜지스터(703), 제2 스위칭용 트랜지스터(704), 제3 스위칭용 트랜지스터(706) 및 제4 스위칭용 트랜지스터(707)에는 n형 트랜지스터를 사용한다.

- [0227] 구동 트랜지스터(701)의 소스 단자는 표시소자(705)의 양극과 접속되고, 게이트 단자는 용량소자(702)의 한쪽 전극과 접속된다. 용량소자(702)의 다른 쪽 전극은, 제3 스위칭용 트랜지스터(706)의 제1 단자(소스 단자 또는 드레인 단자), 및 제4 스위칭용 트랜지스터(707)의 제1 단자(소스 단자 또는 드레인 단자)와 접속된다. 제3 스위칭용 트랜지스터(706)의 제2 단자(소스 단자 또는 드레인 단자)는 제1 신호선(710)과, 제4 스위칭용 트랜지스터(707)의 제2 단자(소스 단자 또는 드레인 단자)는 제2 신호선(711)과 접속된다. 구동 트랜지스터(701)의 드레인 단자는 제1 스위칭용 트랜지스터(703)의 소스 단자 및 제2 스위칭용 트랜지스터(704)의 제1 단자와 접속된다. 그리고, 제1 스위칭용 트랜지스터(703)의 드레인 단자는 전원선(712)과 접속된다. 또한 구동 트랜지스터(701)의 게이트 단자는 제2 스위칭용 트랜지스터(704)의 제2 단자와 접속된다. 따라서 제2 스위칭용 트랜지스터(704)가 온 상태일 때에는 구동 트랜지스터(701)의 게이트 단자와 드레인 단자는 도통된다. 그리고, 제2 스위칭용 트랜지스터(704)가 오프 상태가 되면, 구동 트랜지스터(701)의 게이트 단자와 드레인 단자는 비도통이 되고, 그 순간의 구동 트랜지스터(701)의 게이트 단자(드레인 단자)와 제1 신호선(710)에 의해 공급되는 아날로그 신호 전위 사이의 전위차(전압)를 용량소자(702)는 유지할 수 있다. 또한 표시소자(705)의 음극은 Vss의 전위가 공급된 배선(713)과 접속된다. 이때, Vss는 Vss<Vdd를 만족시키는 전위다. 예를 들면, Vss=GND(접지 전위)로 해도 된다. 이때, 전원선에 공급하는 전위는 Vdd에 한정되지 않고, 예를 들면, 색 요소 RGB로 이루어진 풀 컬러 표시의 경우에는, RGB의 각각의 색 요소의 화소마다 전원선의 전위의 값을 변환해도 된다.

- [0228] 이때, 제1 스위칭용 트랜지스터(703)의 온/오프는 게이트 단자에 접속된 제1 주사선(708)에 입력되는 신호로 제어하고, 제2 스위칭용 트랜지스터(704)의 온/오프는 게이트 단자에 접속된 제2 주사선(709)에 입력되는 신호로 제어하고, 제3 스위칭용 트랜지스터(706)의 온/오프는 게이트 단자에 접속된 제3 주사선(714)에 입력되는 신호로 제어하고, 제4 스위칭용 트랜지스터(707)의 온/오프는 게이트 단자에 접속된 제4 주사선(715)에 입력되는 신호로 제어한다. 자세한 동작에 대해서는, 실시예 1의 도 4에 나타낸 화소 구성과 같으므로 생략한다.

- [0229] 여기에서, 스위칭용 트랜지스터는 리크 전류(오프 전류 및 게이트 리크 전류)가 적은 구성으로 하는 것이 바람직하다고 할 수 있다. 오프 전류는, 트랜지스터가 오프 상태일 때에 소스 드레인 간에 흐르게 되는 전류이며, 게이트 리크 전류는, 게이트 절연막을 통해 게이트와 소스 또는 드레인 간에 흐르게 되는 전류다.

- [0230] 따라서, 제1 스위칭용 트랜지스터(703), 제2 스위칭용 트랜지스터(704), 제3 스위칭용 트랜지스터(706) 및 제4 스위칭용 트랜지스터(707)에 사용되는 N채널형 트랜지스터는, LDD영역을 설치한 구성으로 하는 것이 바람직하다. LDD영역을 설치한 구성의 트랜지스터는 오프 전류를 저감할 수 있기 때문이다. 혹은 제1 스위칭용 트랜지스터(703) 이외의 제2 스위칭용 트랜지스터(704), 제3 스위칭용 트랜지스터(706) 및 제4 스위칭용 트랜지스터(707)에 LDD영역을 설치할 수 있다. 제2 스위칭용 트랜지스터(704)에 오프 전류가 흐르면, 용량소자(702)의 전하를 보유할 수 없게 되고, 제1 스위칭용 트랜지스터(703)는 표시소자(705)에 전류를 흐르게 할 때에 온 전류를 크게 할 필요가 있기 때문이다.

- [0231] 보다 바람직한 형태로는, 제2 스위칭용 트랜지스터(704) 및 제1 스위칭용 트랜지스터(703)에 LDD영역을 설치하고, 적어도 제1 스위칭용 트랜지스터(703)의 LDD영역에는 게이트 전극과 부분적으로 겹치는 영역을 설치한다. 그러면, 제2 스위칭용 트랜지스터(704)는 오프 전류를 저감할 수 있다. 그리고, 제1 스위칭용 트랜지스터(703)는 온 전류를 크게 하고, 핫 일렉트론의 발생을 더욱 저감할 수 있다. 따라서, 제1 스위칭용 트랜지스터(703)의 신뢰성이 향상된다.

- [0232] 또한 구동 트랜지스터(701)에도 LDD영역을 설치하고, LDD영역이 게이트 전극과 겹치는 구조로 함으로써 신뢰성이 향상된다.

- [0233] 또한 게이트 절연막의 막 두께를 얇게 해도 오프 전류는 저감할 수 있다. 따라서, 구동 트랜지스터(701)의 막 두께보다 제1 스위칭용 트랜지스터(703) 및 제2 스위칭용 트랜지스터(704)의 막 두께를 얇게 하는 것이 바람직

하다.

[0234] 또한 제1 스위칭용 트랜지스터(703) 및 제2 스위칭용 트랜지스터(704)를 멀티 게이트 트랜지스터로 함으로써, 게이트 리크 전류를 저감할 수 있다.

[0235] 특히, 제2 스위칭용 트랜지스터(704)에 오프 전류가 흐르게 되면, 용량소자(702)는 기록 기간에 기록된 전압을 유지할 수 없게 되므로, 제2 스위칭용 트랜지스터(704)에만 LDD를 설치하거나, 게이트 절연막을 얇게 하거나, 멀티 게이트로 해도 된다.

[0236] 이때, 제1 주사선(708)의 H레벨의 전위는, 전원선(712)의 전위보다 제1 스위칭용 트랜지스터(703)의 역치전압  $V_{th}$  이상 높은 것이 바람직하다. 또한 마찬가지로, 제2 주사선(709)의 H레벨의 전위는, 전원선(712)의 전위보다 제2 스위칭용 트랜지스터(704)의 역치전압  $V_{th}$  이상 높은 것이 바람직하다. 또한 마찬가지로, 제3 주사선(714)의 H레벨의 전위는, 제1 신호선(710)의 전위보다 제3 스위칭용 트랜지스터(706)의 역치전압  $V_{th}$  이상 높은 것이 바람직하다. 또한 마찬가지로, 제4 주사선(715)의 H레벨의 전위도, 제2 신호선(711)의 전위보다 제4 스위칭용 트랜지스터(707)의 역치전압  $V_{th}$  이상 높은 것이 바람직하다.

[0237] 이때, 제3 스위칭용 트랜지스터(706)와 제2 스위칭용 트랜지스터(704)의 온/오프는 같은 타이밍으로 제어할 수 있기 때문에, 도 18에 나타낸 바와 같이, 제3 스위칭용 트랜지스터(706)의 게이트 단자를 제2 주사선(709)에 접속함으로써 도 7에 있어서의 제3 주사선(714)을 설치하지 않는 구성으로 할 수 있다.

[0238] n형 트랜지스터에는 LDD영역을 용이하게 형성할 수 있다. 따라서, 본 실시예에서 나타낸 바와 같이, n형 트랜지스터를 스위칭용 트랜지스터로서 사용함으로써, 오프 전류가 저감된 스위칭용 트랜지스터를 형성할 수 있다. 또한 이 스위칭용 트랜지스터를 멀티 게이트로 함으로써 게이트 리크 전류를 더욱 저감할 수 있다. 따라서, 스위칭용 트랜지스터의 스위치로서의 기능을 보다 향상시킬 수 있다.

[0239] 또한, 화소 영역 전체 혹은 주변의 구동회로까지 포함시켜서 n형 트랜지스터만으로 구성되는 회로를 제공할 수 있으므로, 공정 수가 절감된, 저비용의 단극성 표시장치 패널을 제공할 수 있다.

[0240] 또한, 표시장치 패널이 가지는 회로에 사용하는 박막 트랜지스터를 n형 트랜지스터만으로 구성할 수 있으므로, 아모포스 반도체나 세미 아모포스 반도체(혹은 미결정 반도체라고도 한다)를 반도체층에 사용한 박막 트랜지스터로 구성되는 회로를 가지는 표시장치를 제공할 수 있다. 예를 들면, 아모포스 반도체로는, 아모포스 실리콘(a-Si:H)을 들 수 있다.

[0241] 이때, 본 실시예에 있어서, 표시소자를 구동하는 구동 트랜지스터의 소스 단자 및 드레인 단자, 및 표시소자의 양극 및 음극은, 표시소자에 순방향의 전압이 인가될 때의 단자 및 전극을 말한다.

[0242] (실시예 4)

[0243] 본 실시예에서는, 실시예 1 및 실시예 2에 나타낸 화소 구성에 있어서 적어도 하나의 스위치에 p형 트랜지스터를 사용한 경우에 관하여 설명한다.

[0244] 우선, 도 1의 화소 구성의 제1 스위치(103)에 p형 트랜지스터, 제2 스위치(104)에 n형 트랜지스터를 적용한 경우의 구성에 대해서 도 20을 참조하여 설명한다.

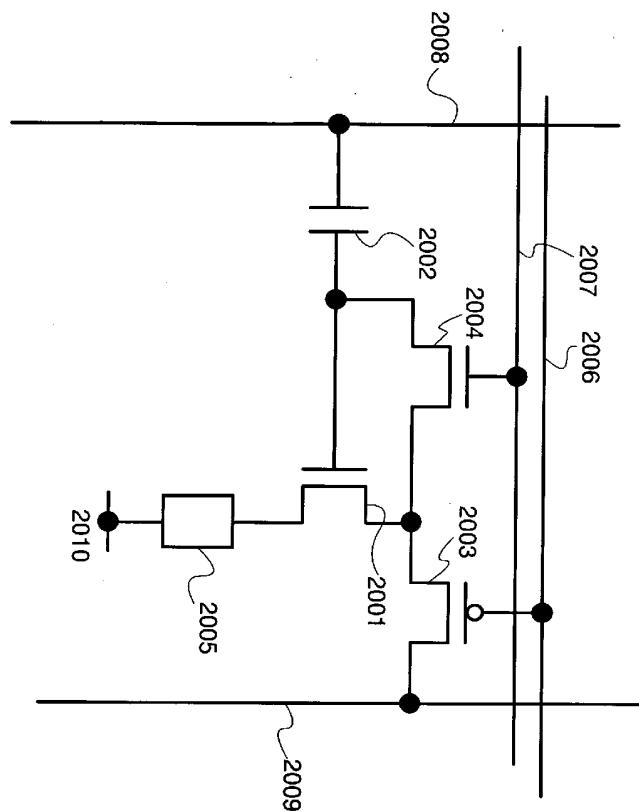

[0245] 화소는 구동 트랜지스터(2001)와, 용량소자(2002)와, p형 트랜지스터인 제1 스위칭용 트랜지스터(2003)와, n형 트랜지스터인 제2 스위칭용 트랜지스터(2004)와, 표시소자(2005)와, 제1 주사선(G1 line)(2006)과, 제2 주사선(G2 line)(2007)과, 신호선(Data line)(2008)과, 전원선(Supply line)(2009)을 구비한다. 이때, 구동 트랜지스터(2001)에는 n형 트랜지스터를 사용한다.

[0246] 구동 트랜지스터(2001)의 소스 단자는 표시소자(2005)의 양극과 접속되고, 게이트 단자는 용량소자(2002)를 통해 신호선(2008)과 접속되고, 드레인 단자는 제1 스위칭용 트랜지스터(2003)의 드레인 단자 및 제2 스위칭용 트랜지스터(2004)의 제1단자(소스 단자 또는 드레인 단자)와 접속된다. 또한 제1 스위칭용 트랜지스터(2003)의 소스 단자는 전원선(2009)과 접속되고, 게이트 단자는 제1 주사선(2006)과 접속된다. 따라서, 제1 주사선(2006)에 L레벨의 신호가 공급되면 제1 스위칭용 트랜지스터(2003)는 온 상태가 되고, 전원선(2009)에 공급된 전원전위  $V_{dd}$ 를 구동 트랜지스터(2001)의 드레인 단자에 공급할 수 있다. 또한 제2 스위칭용 트랜지스터(2004)의 제2 단자(소스 단자 또는 드레인 단자)는 구동 트랜지스터(2001)의 게이트 단자와 접속된다. 따라서, 제2 주사선 2007에 H레벨의 신호를 공급하면 제2 스위칭용 트랜지스터(2004)는 온 상태가 되고, 구동 트랜지스터(2001)의 드레인 단자와 게이트 단자를 도통 할 수 있다. 그리고, 제2 스위칭용 트랜지스터(2004)가 오프 상태가 되면, 구동

트랜지스터(2001)의 게이트 단자와 드레인 단자는 비도통이 되고, 그 순간의 구동 트랜지스터(2001)의 게이트 단자(드레인 단자)와 신호선(2008) 사이의 전위차(전압)를 용량소자(2002)는 유지할 수 있다. 또한 표시소자(2005)의 음극은 Vss의 전위가 공급된 배선(2010)과 접속된다. 이때, Vss는 Vss<Vdd를 만족시키는 전위다. 예를 들면, Vss=GND(접지 전위)로 해도 된다. 또한, 전원선에 공급하는 전위는 Vdd에 한정되지 않고, 예를 들면, 색 요소 RGB로 이루어진 풀 컬러 표시의 경우에는, RGB의 각각의 색 요소의 화소마다 전원선의 전위의 값을 변환해도 된다.

[0247] 계속해서, 본 화소 구성의 타이밍 차트를 도 21에 나타낸다. 도 3의 타이밍 차트와는, 도 21에 나타내는 G1 line(제1 주사선)의 구형파의 H레벨과 L레벨이 반전된다는 점이 다르다. 즉, 도 20의 화소 구성에 있어서, 제1 주사선(2006)이 H레벨로부터 L레벨로 하강하면 제1 스위칭용 트랜지스터(2003)는 온 상태가 된다. 다른 동작에 대해서는, 실시예 1의 도 1의 화소 구성의 설명과 같으므로 생략한다.

[0248] 여기에서, 제1 스위칭용 트랜지스터(2003)는 소스 단자가 전원전위 Vdd가 공급된 전원선(2009)에 접속되어 있기 때문에, 소스 단자의 전위는 고정되어 있다. 따라서, 제1 스위칭용 트랜지스터(2003)의 온/오프를 제어하는 제1 주사선(2006)에 공급하는 신호는, 제1 스위칭용 트랜지스터(2003)의 드레인 단자에 접속되어 있는 부하에 의존하지 않고 결정할 수 있다. 즉, 제1 스위칭용 트랜지스터의 온/오프를 제어하기 위한 신호는 고정 전위인 전원 전위 Vdd와 게이트 단자의 전위 사이의 전위차가 역치전압 이상이면 되기 때문에, 신호의 진폭은 최소한 억제할 수 있어, 소비 전력을 절감할 수 있다.

[0249] 또한, 제1 스위칭용 트랜지스터(2003)의 드레인 단자는 제2 스위칭용 트랜지스터(2004)를 통해 용량소자(2002)와 접속되어 있으므로, 제1 스위칭용 트랜지스터(2003)는 오프 전류가 작지 않아도 그다지 문제는 없다.

[0250] 따라서, 제1 스위칭용 트랜지스터(2003)에는 p형 트랜지스터가 바람직하다.

[0251] 또한, 제2 스위칭용 트랜지스터(2004)는 n형 트랜지스터이기 때문에, LDD영역을 설치하는 것이 용이해서, 오프 전류를 저감할 수 있다. 따라서, 용량소자(2002)의 전압의 유지 능력을 높일 수 있다.

[0252] 다음으로, 도 4의 화소 구성의 스위치 중 적어도 하나에 p형 트랜지스터를 적용한 경우의 구성에 대해서 도 22에 나타낸다.

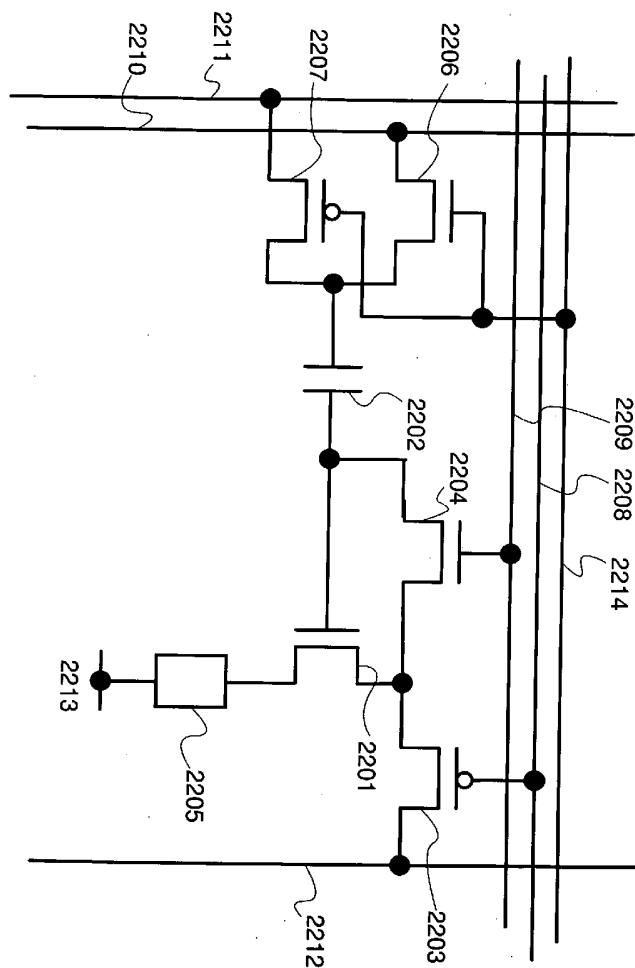

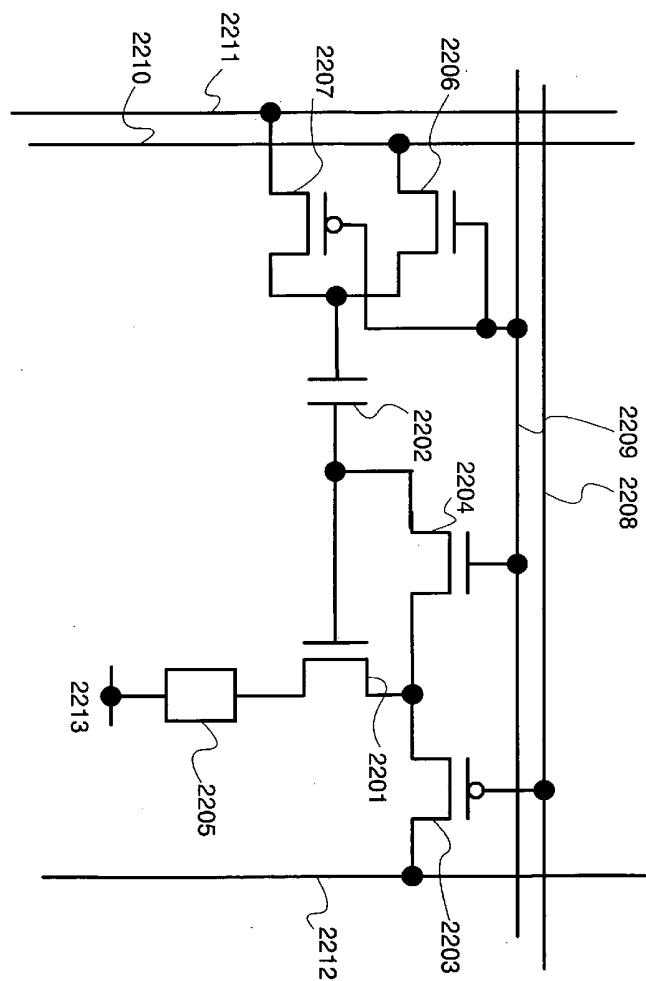

[0253] 화소는 구동 트랜지스터(2201)와, 용량소자(2202)와, 제1 스위칭용 트랜지스터(2203)와, 제2 스위칭용 트랜지스터(2204)와, 표시소자(2205)와, 제3 스위칭용 트랜지스터(2206)와, 제4 스위칭용 트랜지스터(2207)와, 제1 주사선(G1 line)(2208)과, 제2 주사선(G2 line)(2209)과, 제1 신호선(Data1 line)(2210)과, 제2 신호선(Data2 line)(2211)과, 전원선(Supply line)(2212)과, 제3 주사선(2214)을 구비한다. 이때, 구동 트랜지스터(2201), 제2 스위칭용 트랜지스터(2204) 및 제3 스위칭용 트랜지스터(2206)에는 n형 트랜지스터를 사용하고, 제1 스위칭용 트랜지스터(2203) 및 제4 스위칭용 트랜지스터(2207)에는 p형 트랜지스터를 사용한다.

[0254] 구동 트랜지스터(2201)의 소스 단자는 표시소자(2205)의 양극과 접속되고, 게이트 단자는 용량소자(2202)의 한 쪽 전극과 접속되고, 용량소자(2202)의 다른 쪽 전극은, 제3 스위칭용 트랜지스터(2206)의 제1 단자(소스 단자 또는 드레인 단자) 및 제4 스위칭용 트랜지스터(2207)의 제1 단자(소스 단자 또는 드레인 단자)와 접속된다. 제3 스위칭용 트랜지스터(2206)의 제2 단자(소스 단자 또는 드레인 단자)는 제1 신호선(2210)과, 제4 스위칭용 트랜지스터(2207)의 제2 단자(소스 단자 또는 드레인 단자)는 제2 신호선(2211)과 각각 접속된다. 구동 트랜지스터(2201)의 드레인 단자는 제1 스위칭용 트랜지스터(2203)의 드레인 단자와 접속된다. 또한 구동 트랜지스터(2201)의 드레인 단자는 제2 스위칭용 트랜지스터(2204)의 제1 단자(소스 단자 또는 드레인 단자)와 접속되고, 구동 트랜지스터(2201)의 게이트 단자는 제2 스위칭용 트랜지스터(2204)의 제2 단자(소스 단자 또는 드레인 단자)와 접속된다. 따라서 제2 스위칭용 트랜지스터(2204)가 온 상태일 때에는 구동 트랜지스터(2201)의 게이트 단자와 드레인 단자는 도통된다. 그리고, 제2 스위칭용 트랜지스터(2204)가 오프 상태가 되면, 구동 트랜지스터(2201)의 게이트 단자와 드레인 단자는 비도통이 되고, 그 순간의 구동 트랜지스터(2201)의 게이트 단자(드레인 단자)와 제1 신호선(2210)에 의해 공급되는 아날로그 신호 전위 사이의 전위차(전압)를 용량소자(2202)는 유지할 수 있다. 또한 제1 스위칭용 트랜지스터(2203)의 소스 단자는 전원선(2212)과 접속된다. 또한 표시소자(2205)의 음극은 Vss의 전위가 공급된 배선(2213)과 접속된다. 이때, Vss는 Vss<Vdd를 만족시키는 전위다. 예를 들면, Vss=GND(접지 전위)로 해도 된다. 또한, 전원선에 공급하는 전위는 Vdd에 한정되지 않고, 예를 들면, 색 요소 RGB로 이루어진 풀 컬러 표시의 경우에는, RGB의 각각의 색 요소의 화소마다 전원선의 전위의 값을 변환해도 된다.

[0255] 이때, 제1 스위칭용 트랜지스터(2203)의 온/오프는 게이트 단자에 접속된 제1 주사선(2208)에 입력되는 신호로

제어하고, 제2 스위칭용 트랜지스터(2204)의 온/오프는 게이트 단자에 접속된 제2 주사선(2209)에 입력되는 신호로 제어하고, 제3 스위칭용 트랜지스터(2206) 및 제4 스위칭용 트랜지스터(2207)의 온/오프는 각각의 게이트 단자가 모두 접속된 제3 주사선(2214)에 입력되는 신호로 제어한다. 즉, 제3 주사선이 H레벨일 때에는 제3 스위칭용 트랜지스터(2206)가 온 상태가 되고, L레벨일 때에는 제4 스위칭용 트랜지스터(2207)가 온 상태가 된다. 따라서, 기록 기간과 발광 기간 사이에 화소에 접속하는 배선을 변환할 수 있다.

[0256] 물론 제3 스위칭용 트랜지스터(2206)와 제4 스위칭용 트랜지스터(2207)의 온/오프를 제어하는 주사선을 각각 다르게 해도 되지만, 도 22와 같이 공통의 주사선으로 제어함으로써 화소의 개구율을 향상시킬 수 있다.

[0257] 계속해서, 본 화소 구성의 타이밍 차트를 도 24에 나타낸다. 또한, 도 5의 타이밍 차트와는, 도 24에 나타내는 G1 line(제1 주사선)의 구형파의 H레벨과 L레벨이 반전된다는 점이 다르다. 즉, 도 22의 화소 구성에 있어서, 제1 주사선(2208)이 L레벨일 때는, 제1 스위칭용 트랜지스터(2203)는 온 상태가 된다. 그리고, 제1 주사선(2208)이 L레벨에서 H레벨로 상승하면 제1 스위칭용 트랜지스터(2203)는 오프 상태가 된다. 다른 동작에 대해서는, 실시예 2의 도 4의 화소 구성의 설명과 같으므로 생략한다.

[0258] 여기에서, 제1 스위칭용 트랜지스터(2203)에서 소스 단자는 전원전위 Vdd에 접속되어 있기 때문에, 소스 단자의 전위는 고정되어 있다. 따라서, 제1 스위칭용 트랜지스터(2203)의 온/오프를 제어하는 제1 주사선(2208)에 공급하는 신호는, 제1 스위칭용 트랜지스터(2203)의 드레인 단자에 접속되어 있는 부하에 의존하지 않고 결정할 수 있다. 즉, 제1 스위칭용 트랜지스터의 온/오프를 제어하기 위한 신호는 고정 전위인 전원전위 Vdd와 게이트 단자의 전위 사이의 전위차가 역치전압 이상이면 되기 때문에, 신호의 진폭은 최소한 억제할 수 있어, 소비 전력을 절감할 수 있다.

[0259] 또한 제1 스위칭용 트랜지스터(2203)의 드레인 단자는 제2 스위칭용 트랜지스터(2204)를 통해 용량소자(2202)와 접속되어 있으므로, 제1 스위칭용 트랜지스터(2203)는 오프 전류가 작지 않아도 그다지 문제는 없다.

[0260] 따라서, 제1 스위칭용 트랜지스터(2203)에는 p형 트랜지스터가 바람직하다.

[0261] 또한, 제2 스위칭용 트랜지스터(2204)는 n형 트랜지스터이기 때문에, LDD영역을 설치하는 것이 용이해서, 오프 전류를 저감할 수 있다. 따라서, 용량소자(2202)의 전압을 유지할 수 있다.

[0262] 또한 도 22의 구성의 배선을 더욱 절감한 구성에 대해서, 도 23을 참조하여 설명한다. 도 23의 구성에서는, 제3 스위칭용 트랜지스터(2206)와 제4 스위칭용 트랜지스터(2207)의 게이트 단자가 접속되어 있는 배선이 제2 주사선(2209)과 접속된다. 즉, 도 22의 구성에서는, 용량소자(2202)의 다른 쪽 전극에 입력하는 신호를, 기록 기간과 발광 기간을 전환하기 위한 신호로서 제3 주사선(2214)에 입력하지만, 도 23의 구성에서는 이 기록 기간과 발광 기간을 전환하기 위한 신호로서, 제2 주사선(2209)에 입력되는 신호를 사용한다.

[0263] 도 23의 구성에서는 도 22의 구성에서보다 배선의 수를 더욱 줄일 수 있으므로 화소의 개구율을 향상시킬 수 있다.

[0264] 또한 도 1의 구성의 제1 스위치(103) 및 제2 스위치(104)로서 p형 트랜지스터를 사용해서 배선의 수를 줄인 구성 및 동작에 대해서 도 25 및 도 26을 참조하여 설명한다.

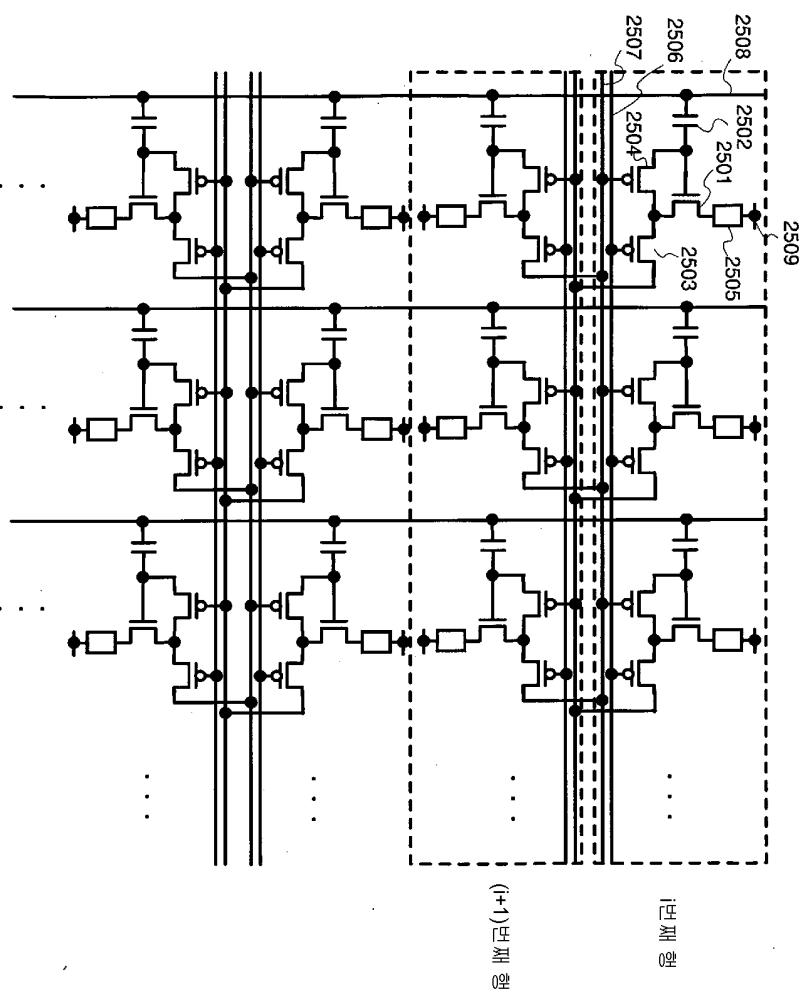

[0265] 도 25의 화소는 구동 트랜지스터(2501)와, 용량소자(2502)와, p형 트랜지스터인 제1 스위칭용 트랜지스터(2503)와, p형 트랜지스터인 제2 스위칭용 트랜지스터(2504)와, 표시소자(2505)와, 제1 주사선(G1 line)(2506)과, 제2 주사선(G2 line)(2507)과, 신호선(Data line)(2508)을 구비한다. 이때, 구동 트랜지스터(2501)에는 n형 트랜지스터를 사용한다.

[0266] 구동 트랜지스터(2501)의 소스 단자는 표시소자(2505)의 양극과 접속되고, 게이트 단자는 용량소자(2502)를 통해 신호선(2508)과 접속되고, 드레인 단자는 제1 스위칭용 트랜지스터(2503)의 드레인 단자 및 제2 스위칭용 트랜지스터(2504)의 제1 단자(소스 단자 또는 드레인 단자)와 접속된다. 또한 제1 스위칭용 트랜지스터(2503)의 소스 단자는 다른 행의 화소의 제2 주사선(2507)과 접속되고, 게이트 단자는 제1 주사선(2506)과 접속된다.

[0267] 따라서, 도 26에 나타낸 바와 같이, i번째 행의 제1 주사선(2506)에 L레벨의 신호를 공급하면 제1 스위칭용 트랜지스터(2503)는 온 상태가 된다. 또한 제2 스위칭용 트랜지스터(2504)의 제2 단자(소스 단자 또는 드레인 단자)는 구동 트랜지스터(2501)의 게이트 단자와 접속된다. 따라서, 제2 주사선(2507)에 L레벨의 신호를 공급하면 제2 스위칭용 트랜지스터(2504)는 온 상태가 되고, 구동 트랜지스터(2501)의 드레인 단자와 게이트 단자를 도통할 수 있다. 그리고, 제2 스위칭용 트랜지스터(2504)가 오프 상태가 되면, 구동 트랜지스터(2501)의 게이트 단자와 드레인 단자는 비도통이 되고, 그 순간의 구동 트랜지스터(2501)의 게이트 단자(드레인 단자)와 신호선

(2508) 사이의 전위차(전압)를 용량소자(2502)는 유지할 수 있다. 또한 표시소자(2505)의 음극은 Vss의 전위가 공급된 배선(2509)과 접속된다. 이때, 기록 기간 이외에는 다른 행의 화소의 전원선의 기능을 하는 제2 주사선(2507)에는, H레벨의 전위로서 Vdd가 공급된다. 이때, Vss는 Vss<Vdd를 만족시키는 전위다. 예를 들면, Vss=GND(접지 전위)로 해도 된다.

[0268] 계속해서, 본 화소 구성의 타이밍 차트를 도 26에 나타낸다. 도 3의 타이밍 차트와는, 도 26에 나타내는 G1 line(제1 주사선(2506)) 및 G2 line(제2 주사선(2507))의 구형파의 H레벨과 L레벨이 반전된다는 점이 다르다. 즉, 도 25의 화소 구성에 있어서, 제1 주사선(2506)이 H레벨에서 L레벨로 하강하면, 제1 스위칭용 트랜지스터(2503)는 온 상태가 된다. 마찬가지로, 제2 주사선(2507)이 H레벨에서 L레벨로 하강하면 제2 스위칭용 트랜지스터(2504)는 온 상태가 된다.

[0269] i번째 행의 제1 주사선(2506)에 L레벨의 신호가 공급되어, 제1 스위칭용 트랜지스터(2503)가 온 상태가 되면, i+1번째 행의 제2 주사선(2507)에는 H레벨이 공급되어 있기 때문에, 제1 스위칭용 트랜지스터(2503)의 소스 단자에 H레벨(Vdd)의 전위를 공급할 수 있다.

[0270] 이렇게 해서, 표시소자(2505)에 전류를 공급하기 위한 전원선을 별도로 설치하지 않고, 다른 행의 주사선을 사용할 수 있다. 이때, 도 25에서는 제1 스위칭용 트랜지스터(2503)의 소스 단자를 이웃하는 행의 제2 주사선(2507)에 접속하는 구성으로 했지만, 이것에 한정되지 않는다. 그러나, 화소의 배치를 고려하면, 전원선으로서 다른 행의 제2 주사선(2507)을 사용할 경우에는, 이웃하는 행의 화소의 제2 주사선(2507)을 사용하는 것이 바람직하다.

[0271] 또한, 제1 스위칭용 트랜지스터(2503)의 소스 단자를 접속하는 주사선의 전류 공급 능력을 높일 필요가 있으므로, 제2 주사선(2507)에는 베퍼를 설치하는 것이 바람직하다.

[0272] 이때, 본 실시예에 있어서, 표시소자를 구동하는 구동 트랜지스터의 소스 단자 및 드레인 단자, 및 표시소자의 양극 및 음극은, 표시소자에 순방향의 전압이 인가될 때의 단자 및 전극을 말한다.

[0273] (실시예 5)

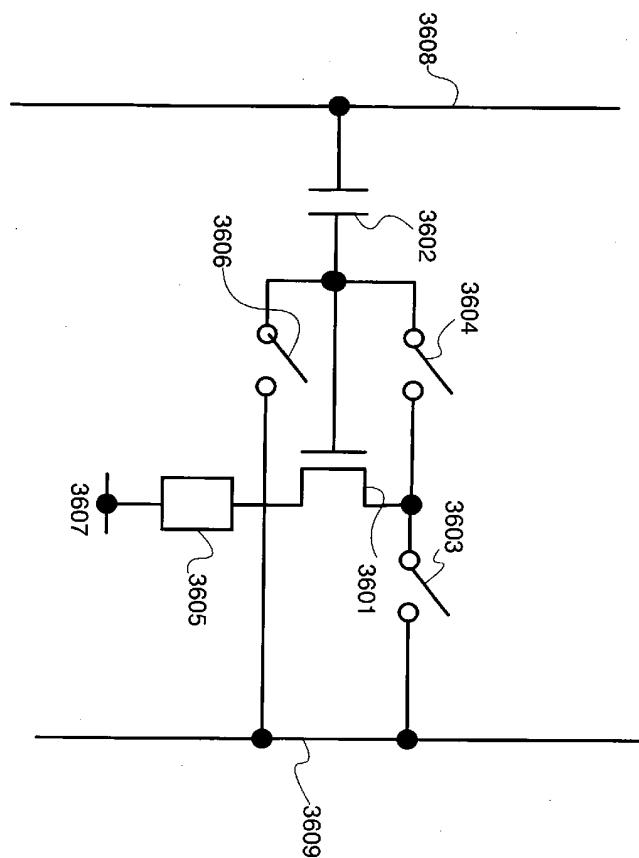

[0274] 본 실시예에서는 신호 기록 기간에 있어서, 표시소자에 흐르는 전류를 저감한 화소 구성 및 구동방법에 관하여 설명한다.

[0275] 우선, 실시예 1에 나타낸 화소 구성은 참고하여, 화소의 동작과 그때의 접속에 관하여 설명한다. 화소의 신호 기록 기간에 있어서, 구동 트랜지스터(101)를 온 상태로 하기 위해서 게이트 단자의 전위를 용량소자(102)에 축적할 때에는, 도 33과 같이, 전원선(109)과 신호선(108)을 용량소자(102)를 통해 접속한다. 이때, 구동 트랜지스터(101)의 드레인 단자는, 게이트 단자(혹은 전원선(109))와 접속되어 있어도 된다. 즉, 도 33의 접선으로 나타낸 부분은 접속되어 있어도 되고, 접속되지 않아도 된다.

[0276] 구동 트랜지스터(101)의 온/오프를 제어하는 데에 필요한 게이트 전위를 얻을 때에는, 도 34에 나타낸 바와 같이, 구동 트랜지스터(101)의 드레인 단자와 게이트 단자를 접속한다. 이렇게 해서, 구동 트랜지스터(101)가 온 상태로부터 오프가 될 때의 게이트 단자의 전위와, 그때 신호선(108)에 공급되어 있는 아날로그 신호 전위 사이의 전위 차분의 전하가 용량소자(102)에 축적된다.

[0277] 발광 기간에는, 도 35에 나타낸 바와 같이, 구동 트랜지스터(101)의 드레인 단자와 전원선(109)을 접속한다. 이렇게 해서, 구동 트랜지스터(101)의 드레인 단자에 전원선(109)의 전위를 공급할 수 있다. 따라서, 구동 트랜지스터(101)가 온 상태가 되면 전원선(109)로부터 표시소자(105)에 전류를 공급할 수 있다.

[0278] 여기에서, 본 실시예에서는, 도 33에 접선으로 나타낸 구동 트랜지스터(101)의 드레인 단자와 게이트 단자 및 전원선(109)을 접속하지 않음으로써, 구동 트랜지스터(101)를 충분히 온 상태로 하기 위해, 게이트 단자의 전위를 용량소자(102)에 축적할 때, 표시소자(105)에 전류가 흐르는 것을 방지할 수 있다. 따라서, 소비 전력을 저감할 수 있다. 그러한 화소 구성의 예를 도 36, 도 37 및 도 73에 나타낸다.

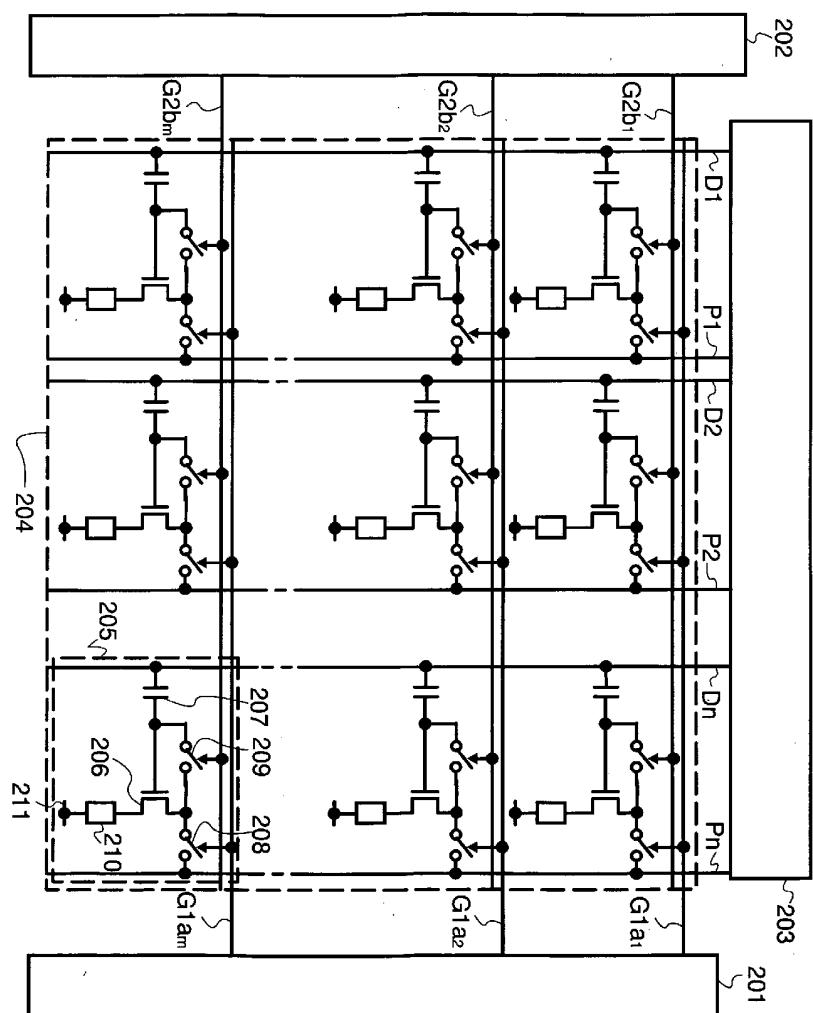

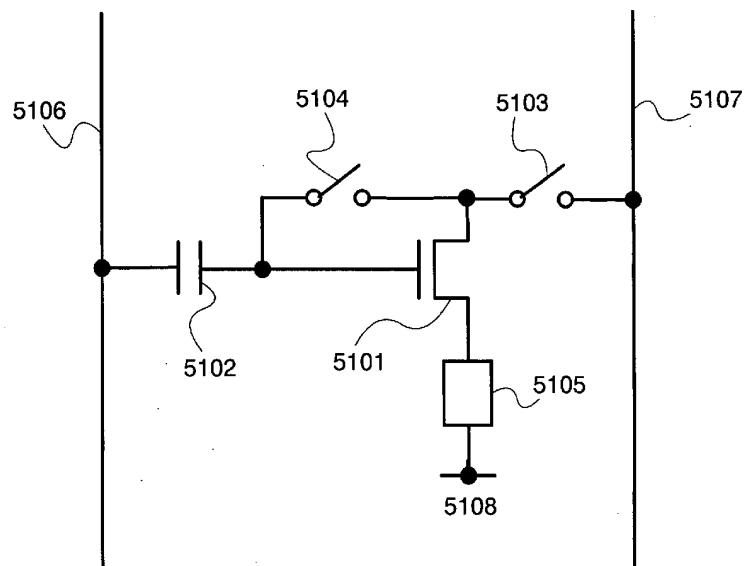

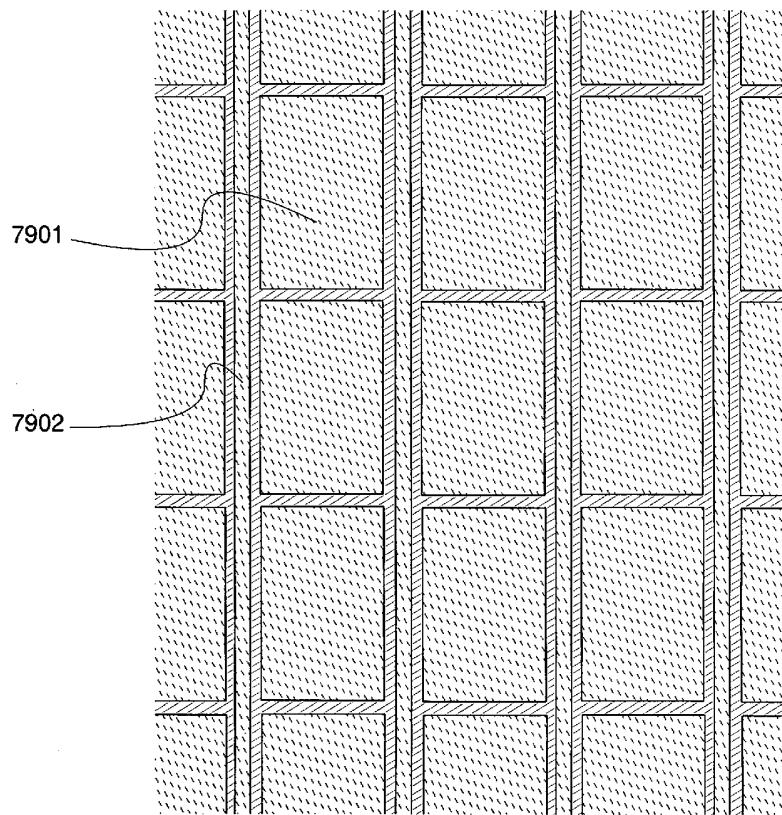

[0279] 도 36의 화소 구성에 대해서 상세히 설명한다. 화소는 구동 트랜지스터(3601)와, 용량소자(3602)와, 제1 스위치(3603)와, 제2 스위치(3604)와, 제3 스위치(3606)와, 표시소자(3605)와, 신호선(3608)과, 전원선(3609)을 구비한다. 이때, 구동 트랜지스터(3601)에는 n형 트랜지스터를 사용한다.

[0280] 구동 트랜지스터(3601)의 소스 단자는 표시소자(3605)의 양극과 접속되고, 게이트 단자는 용량소자(3602)를 통해 신호선(3608)과 접속되고, 드레인 단자는 제1 스위치(3603)를 통해 전원선(3609)과 접속된다. 이때, 전원선

(3609)에는 전원전위 Vdd가 공급된다. 또한 구동 트랜지스터(3601)의 게이트 단자는, 제3 스위치(3606)를 통해 전원선(3609)과, 제2 스위치(3604)를 통해 드레인 단자와 접속된다. 따라서 제2 스위치(3604)가 온 상태일 때에는 구동 트랜지스터(3601)의 게이트 단자와 드레인 단자는 도통한다. 그리고, 제2 스위치(3604)가 오프 상태가 되면, 구동 트랜지스터(3601)의 게이트 단자와 드레인 단자는 비도통이 되고, 그 순간의 구동 트랜지스터(3601)의 게이트 단자(드레인 단자)와 신호선(3608) 사이의 전위차(전압)를 용량소자(3602)는 유지할 수 있다. 또한 표시소자(3605)의 음극은 Vss의 전위가 공급된 배선(3607)과 접속된다. 이때, Vss는 Vss<Vdd를 만족시키는 전위다. 예를 들면, Vss=GND(접지 전위)로 해도 된다. 또한, 전원선(3609)에 공급하는 전위는 Vdd에 한정되지 않고, 예를 들면, 색 요소 RGB로 이루어진 풀 컬러 표시의 경우에는, RGB의 각각의 색 요소의 화소마다 전원선의 전위의 값을 변환해도 된다.

[0281] 다음으로, 도 36의 화소 구성의 동작 원리에 관하여 설명한다.

[0282] 화소에의 신호 기록 기간에, 우선, 제1 스위치(3603) 및 제2 스위치(3604)를 끈 상태에서 제3 스위치(3606)를 온 상태로 한다. 그러면, 용량소자(3602)에 전류가 흘러, 전하의 축적 또는 방전이 행해진다. 이때, 화소의 기록 기간에 신호선(3608)에는 아날로그 신호 전위가 공급된다. 이 아날로그 신호 전위는 비디오신호에 해당한다.

[0283] 이렇게 해서, 구동 트랜지스터(3601)를 충분히 온 상태로 하는 게이트 단자의 전위만큼의 전하가 용량소자(3602)에 축적된다. 본 구성에서는 이때, 표시소자(3605)에 전류가 흐르지 않는다.

[0284] 계속해서, 제1 스위치(3603)를 끈 상태에서 제3 스위치(3606)를 오프 상태로 하고, 제2 스위치(3604)를 온 상태로 한다. 그러면 용량소자(3602), 구동 트랜지스터(3601) 및 표시소자(3605)에 전류가 흐르기 시작한다.

[0285] 잠시 후, 구동 트랜지스터(3601) 및 용량소자(3602)에 전류가 흐르지 않게 된다. 이렇게 해서 구동 트랜지스터(3601)는 오프 상태가 된다. 이때, 구동 트랜지스터(3601)의 게이트-소스간 전압 Vgs는 역치전압 Vth와 대략 동등하다.

[0286] 이 상태가 되면, 제2 스위치(3604)는 오프 상태가 된다. 그러면, 용량소자(3602)에는 구동 트랜지스터(3601)를 오프 상태로 하는 게이트 단자의 전위와, 제2 스위치(3604)를 끈 순간에 신호선(3608)에 공급되어 있는 아날로그 신호 전위 사이의 전위차(Vp)가 유지된다. 이렇게 해서, 화소에 아날로그 신호가 기록된다.

[0287] 화소에 아날로그 신호가 기록되면, 그때에 신호선(3608)에 공급된 아날로그 신호 전위를 기준으로 해서, 신호선(3608)의 전위의 변동에 따라 구동 트랜지스터(3601)의 온/오프가 제어되게 된다. 즉, 신호선(3608)의 전위가, 신호 기록 기간에 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위 이하일 때에는 구동 트랜지스터(3601)는 오프 상태가 되고, 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위보다 높아지면 구동 트랜지스터(3601)는 온 상태가 된다.

[0288] 화소에 아날로그 신호가 기록되면, 용량소자(3602)가 전위차(Vp)를 유지하므로, 신호선(3608)의 전위가, 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위 이하일 때에는, 구동 트랜지스터(3601)의 게이트 단자의 전위도, 화소에 아날로그 신호가 기록될 때의 게이트 단자의 전위 이하가 되고, 구동 트랜지스터(3601)는 오프 상태가 된다. 한편, 신호선(3608)의 전위가, 기록 기간에 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위보다 높아지면, 구동 트랜지스터(3601)의 게이트 단자의 전위도, 화소에 아날로그 신호가 기록될 때의 게이트 단자의 전위보다 높아지므로, 구동 트랜지스터(3601)는 온 상태가 된다.

[0289] 따라서, 화소의 발광 기간에는, 제1 스위치(3603)를 온 상태로 하고, 제2 스위치(3604) 및 제3 스위치(3606)는 오프 상태로 하고, 신호선(3608)에 공급하는 전위를 아날로그적으로 변화시킴으로써 구동 트랜지스터(3601)의 온/오프를 제어한다. 이때, 신호선(3608)에 공급하는 전위로는, 실시예 1에 나타낸 바와 같이, 과형(5901), 과형(5902), 과형(5903), 과형(5904), 과형(5905), 과형(5906) 혹은 과형(5907), 또는 이것들을 복수 연속으로 공급해도 된다.

[0290] 연속으로 공급함으로써, 발광 시간을 1프레임 내에서 분산시킬 수 있다. 그 결과, 프레임 주파수가 외형상 향상되고, 화면의 깜박거림을 방지할 수 있다.

[0291] 이렇게 해서, 화소에 아날로그 신호를 기록할 때에 신호선(3608)에 공급되는 아날로그 신호 전위에 의해 화소의 아날로그 시간계조표시가 가능해진다.

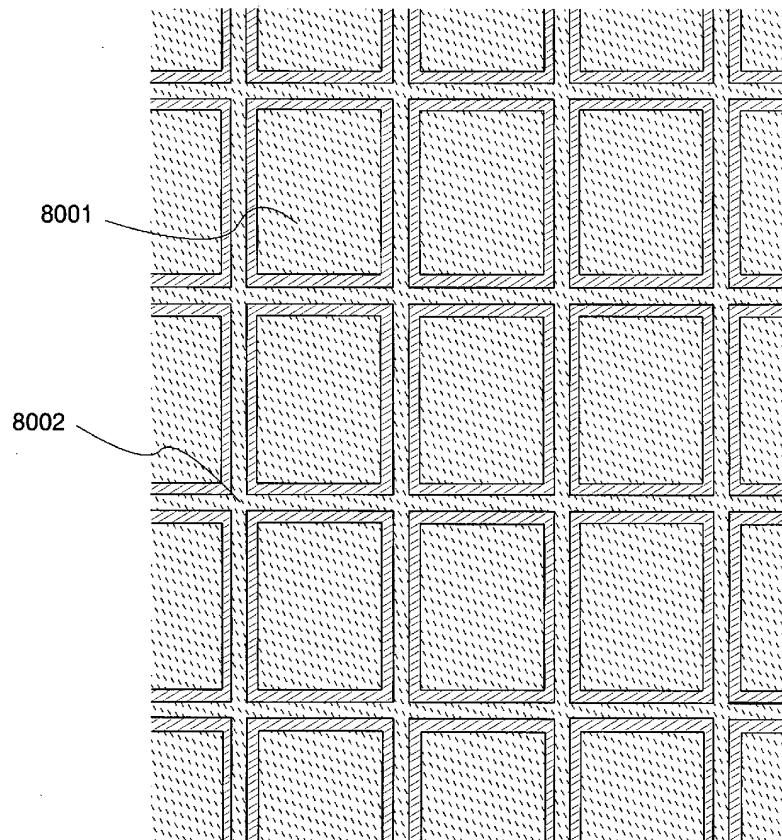

[0292] 다음으로, 도 37의 화소 구성에 대해서 상세히 설명한다.

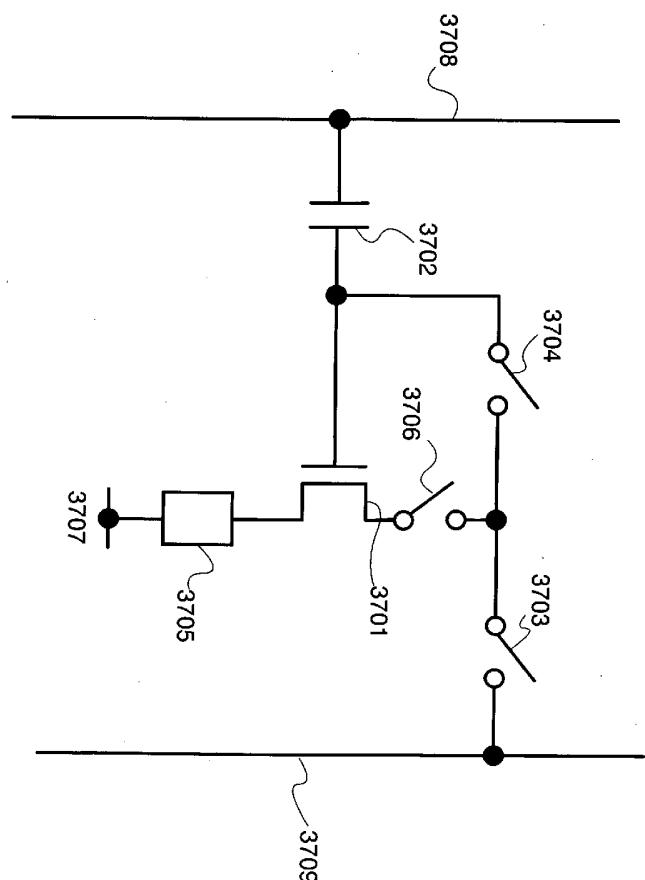

[0293] 화소는 구동 트랜지스터(3701)와, 용량소자(3702)와, 제1 스위치(3703)와, 제2 스위치(3704)와, 제3 스위치

(3706)와, 표시소자(3705)와, 신호선(3708)과, 전원선(3709)을 구비한다. 이때, 구동 트랜지스터(3701)에는 n형 트랜지스터를 사용한다.

[0294] 구동 트랜지스터(3701)의 소스 단자는 표시소자(3705)의 양극과 접속되고, 게이트 단자는 용량소자(3702)를 통해 신호선(3708)과 접속되고, 드레인 단자는 제3 스위치(3706) 및 제1 스위치(3703)를 통해 전원선(3709)과 접속된다. 이때, 전원선(3709)에는 전원전위 Vdd가 공급된다. 또한 구동 트랜지스터(3601)의 게이트 단자는, 제2 스위치(3704) 및 제3 스위치(3706)를 통해 드레인 단자와 접속된다. 따라서 제2 스위치(3704) 및 제3 스위치(3706)가 온 상태일 때에는 구동 트랜지스터(3701)의 게이트 단자와 드레인 단자는 도통한다. 그리고, 제2 스위치(3704)가 오프 상태가 되면, 구동 트랜지스터(3701)의 게이트 단자와 드레인 단자는 비도통이 되고, 그 순간의 구동 트랜지스터(3701)의 게이트 단자(드레인 단자)와 신호선(3708) 사이의 전위차(전압)를 용량소자(3702)는 유지할 수 있다. 또한 표시소자(3705)의 음극은 Vss의 전위가 공급된 배선(3707)과 접속된다. 이때, Vss는 Vss<Vdd를 만족시키는 전위다. 예를 들면, Vss=GND(접지 전위)로 해도 된다. 또한, 전원선에 공급하는 전위는 Vdd에 한정되지 않고, 예를 들면, 색 요소 RGB로 이루어진 풀 컬러 표시의 경우에는, RGB의 각각의 색 요소의 화소마다 전원선의 전위의 값을 변환해도 된다.

[0295] 다음으로, 도 37의 화소 구성의 동작 원리에 관하여 설명한다.

[0296] 화소의 신호 기록 기간에, 제3 스위치(3706)를 오프 상태로 하고, 제1 스위치(3703) 및 제2 스위치(3704)를 온 상태로 한다. 그러면, 용량소자(3702)에 전류가 흘러, 용량소자(3702)에서는 전하의 축적 또는 방전이 행해진다. 또한, 화소에의 신호 기록 기간에는, 신호선(3708)에는 아날로그 신호 전위가 공급된다. 이 아날로그 신호 전위는 비디오신호에 해당한다.

[0297] 잠시 후, 용량소자(3702)에 전류가 흐르지 않게 되고, 구동 트랜지스터(3701)를 온 상태로 하는 데 충분한 게이트 단자의 전위가 용량소자(3702)에 축적된다. 본 구성에서는 이때, 표시소자(3705)에는 전류가 흐르지 않는다.

[0298] 계속해서 제2 스위치(3704)를 켜 상태에서 제1 스위치(3703)를 오프 상태로 하고, 제3 스위치(3706)를 온 상태로 한다. 구동 트랜지스터(3701), 표시소자(3705) 및 용량소자(3702)에 전류가 흐르고, 잠시 후, 거기에 전류가 흐르지 않게 된다. 이렇게 해서, 구동 트랜지스터(3701)는 오프 상태가 된다.

[0299] 이 상태가 되면 제2 스위치(3704)는 오프 상태가 된다. 그러면, 용량소자(3702)에는 트랜지스터를 오프 상태로 하는 구동 트랜지스터(3701)의 게이트 단자의 전위와, 제2 스위치(3704)를 끈 순간에 신호선(3708)에 공급되어 있는 아날로그 신호 전위 사이의 전위차(Vp)가 유지된다. 이렇게 해서 화소에 아날로그 신호가 기록된다.

[0300] 화소에 아날로그 신호가 기록되면, 그때 신호선(3708)에 공급된 아날로그 신호 전위를 기준으로 해서, 신호선(3708)의 전위의 변동에 따라 구동 트랜지스터(3701)의 온/오프가 제어되게 된다. 즉, 신호선(3708)의 전위가, 기록 기간에 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위 이하일 때에는 구동 트랜지스터(3701)는 오프 상태가 되고, 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위보다 높아지면 구동 트랜지스터(3701)는 온 상태가 된다.

[0301] 화소에 아날로그 신호가 기록되면, 용량소자(3702)가 전위차(Vp)를 유지하므로, 신호선(3708)의 전위가, 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위 이하일 때에는, 구동 트랜지스터(3701)의 게이트 단자의 전위도, 화소에 아날로그 신호가 기록될 때의 게이트 단자의 전위 이하가 되고, 구동 트랜지스터(3701)는 오프 상태가 된다. 한편, 신호선(3708)의 전위가, 기록 기간에 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위보다 높아지면, 구동 트랜지스터(3701)의 게이트 단자의 전위도, 화소에 아날로그 신호가 기록될 때의 게이트 단자의 전위보다 높아지므로, 구동 트랜지스터(3701)는 온 상태가 된다.

[0302] 따라서, 화소의 발광 기간에는, 제1 스위치(3703) 및 제3 스위치(3706)는 온 상태로 하고, 제2 스위치(3704)는 오프 상태로 하고, 신호선(3608)에 공급하는 전위를 아날로그적으로 변화시킴으로써, 구동 트랜지스터(3701)의 온/오프를 제어한다. 이때, 신호선(3708)에 공급하는 전위로는, 실시예 1에 나타낸 바와 같이, 파형(5901), 파형(5902), 파형(5903), 파형(5904), 파형(5905), 파형(5906) 혹은 파형(5907), 또는 이것들을 복수 연속으로 공급해도 된다.

[0303] 연속으로 공급함으로써, 발광 시간을 1프레임 내에서 분산시킬 수 있다. 그 결과, 프레임 주파수가 외형상 향상되고, 화면의 깜박거림을 방지할 수 있다.

[0304] 이렇게 해서, 화소에 아날로그 신호를 기록할 때에 신호선(3708)에 공급되는 아날로그 신호 전위에 의해 화소의 아날로그 시간계조표시가 가능해진다.

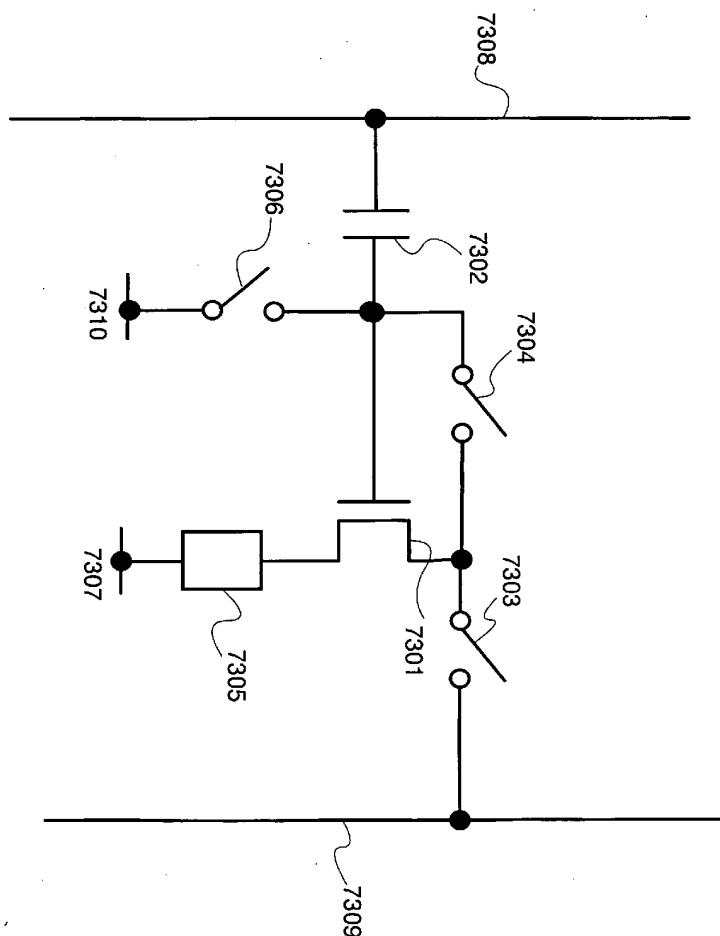

- [0305] 다음으로, 도 73의 화소 구성에 대해서 상세히 설명한다.

- [0306] 화소는 구동 트랜지스터(7301)와, 용량소자(7302)와, 제1 스위치(7303)와, 제2 스위치(7304)와, 제3 스위치(7306)와, 표시소자(7305)와, 신호선(7308)과, 전원선(7309)을 구비한다. 이때, 구동 트랜지스터(7301)에는 n형 트랜지스터를 사용한다.

- [0307] 구동 트랜지스터(7301)의 소스 단자는 표시소자(7305)의 양극과 접속되고, 게이트 단자는 용량소자(7302)를 통해 신호선(7308)과 접속되고, 드레인 단자는 제1 스위치(7303)를 통해 전원선(7309)과 접속된다. 이때, 전원선(7309)에는 전원전위 Vdd가 공급된다. 또한 구동 트랜지스터(7301)의 게이트 단자와 드레인 단자는 제2 스위치(7304)를 통해 접속된다. 따라서 제2 스위치(7304)가 온 상태일 때에는 구동 트랜지스터(7301)의 게이트 단자와 드레인 단자는 도통한다. 그리고, 제2 스위치(7304)가 오프 상태가 되면, 구동 트랜지스터(7301)의 게이트 단자와 드레인 단자는 비도통이 되고, 그 순간의 구동 트랜지스터(7301)의 게이트 단자(드레인 단자)와 신호선(7308)에 의해 공급되는 아날로그 신호 전위 사이의 전위차(전압)를 용량소자(7302)는 유지할 수 있다. 또한 표시소자(7305)의 음극은 Vss의 전위가 공급된 배선(7307)과 접속된다. 또한, 전원선(7309)에 공급하는 전위는 Vdd에 한정되지 않고, 예를 들면, 색 요소 RGB로 이루어진 풀 컬러 표시의 경우에는, RGB의 각각의 색 요소의 화소마다 전원선의 전위의 값을 변환해도 된다.

- [0308] 또한 구동 트랜지스터(7301)의 게이트 단자는 제3 스위치(7306)를 통해 제2 배선(7310)과 접속된다. 이때, 제2 배선(7310)은, 기록 기간에 구동 트랜지스터(7301)의 드레인 단자에 전원전위 Vdd가 공급되었을 때에 구동 트랜지스터(7301)가 충분히 온 상태가 되는 게이트 전위로 설정되는 것이 좋다. 따라서, 제2 배선(7310)은 그 화소의 또는 다른 행의 화소의 제1 스위치(7303), 제2 스위치(7304) 또는 제3 스위치(7306)를 제어하는 주사선으로 해도 된다.

- [0309] 다음으로, 도 73의 화소 구성의 동작 원리에 관하여 설명한다.

- [0310] 화소에의 신호 기록 기간에, 우선, 제1 스위치(7303) 및 제2 스위치(7304)를 끈 상태에서, 제3 스위치(7306)를 온 상태로 한다. 그러면, 용량소자(7302)에 전류가 흘러, 전하의 축적 또는 방전이 행해진다. 이때, 화소의 기록 기간에 신호선(7308)에는 아날로그 신호 전위가 공급된다. 이 아날로그 신호 전위는 비디오신호에 해당한다.

- [0311] 이렇게 해서, 구동 트랜지스터(7301)를 충분히 온 상태로 하는 게이트 단자의 전위만큼의 전하가 용량소자(7302)에 축적된다. 본 구성에 있어서는 이때, 표시소자(7305)에는 전류가 흐르지 않는다.

- [0312] 계속해서, 제1 스위치(7303)를 끈 상태로 제3 스위치(7306)를 오프 상태로 하고, 제2 스위치(7304)를 온 상태로 한다. 그러면 용량소자(7302), 구동 트랜지스터(7301) 및 표시소자(7305)에 전류가 흐르기 시작한다.

- [0313] 잠시 후, 구동 트랜지스터(7301) 및 용량소자(7302)에 전류가 흐르지 않게 되어, 구동 트랜지스터(7301)는 오프 상태가 된다. 이때, 구동 트랜지스터(7301)의 게이트-소스간 전압 Vgs는 역치전압 Vth와 대략 동등하다.

- [0314] 이 상태가 되면 제2 스위치(7304)는 오프 상태가 된다. 그러면, 용량소자(7302)에는 트랜지스터를 오프 상태로 하는 구동 트랜지스터(7301)의 게이트 단자의 전위와, 제2 스위치(7304)가 오프 상태가 될 때 신호선(7308)에 공급되어 있는 아날로그 신호 전위 사이의 전위차(Vp)가 유지된다. 이렇게 해서 화소에 아날로그 신호가 기록된다.

- [0315] 화소에 아날로그 신호가 기록되면, 그때 신호선(7308)에 공급된 아날로그 신호 전위를 기준으로 해서, 신호선(7308)의 전위의 변동에 따라 구동 트랜지스터(7301)의 온/오프가 제어되게 된다. 즉, 신호선(7308)의 전위가, 신호 기록 기간에 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위 이하일 때에는 구동 트랜지스터(7301)는 오프 상태가 되고, 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위보다 높아지면 구동 트랜지스터(7301)는 온 상태가 된다.

- [0316] 화소에 아날로그 신호가 기록되면, 용량소자(7302)가 전위차(Vp)를 유지하므로, 신호선(7308)의 전위가, 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위 이하일 때에는, 구동 트랜지스터(7301)의 게이트 단자의 전위도, 화소에 아날로그 신호가 기록될 때의 게이트 단자의 전위 이하가 되고, 구동 트랜지스터(7301)는 오프 상태가 된다. 한편, 신호선(7308)의 전위가, 기록 기간에 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위보다 높아지면, 구동 트랜지스터(7301)의 게이트 단자의 전위도, 화소에 아날로그 신호가 기록될 때의 게이트 단자의 전위보다 높아지므로, 구동 트랜지스터(7301)는 온 상태가 된다.

- [0317] 따라서, 화소의 발광 기간에는, 제1 스위치(7303)는 온 상태로 하고, 제2 스위치(7304) 및 제3 스위치(7306)는 오프 상태로 하고, 신호선(7308)에 공급하는 전위를 아날로그적으로 변화시킴으로써, 구동 트랜지스터(7301)의

온/오프를 제어한다. 이때, 신호선(7308)에 공급하는 전위로는, 실시예 1에 나타낸 바와 같이, 파형(5901), 파형(5902), 파형(5903), 파형(5904), 파형(5905), 파형(5906) 혹은 파형(5907), 또는 이것들을 복수 연속으로 공급해도 된다.

- [0318] 연속으로 공급함으로써, 발광 시간을 1프레임 내에서 분산시킬 수 있다. 그 결과, 프레임 주파수가 외형상 향상되고, 화면의 깜박거림을 방지할 수 있다.

- [0319] 이렇게 해서, 화소에 아날로그 신호를 기록할 때에 신호선(7308)에 공급되는 아날로그 신호 전위에 의해 화소의 아날로그 시간계조표시가 가능해진다.

- [0320] 실시예 1에 나타낸 도 4의 구성에도 마찬가지로, 화소의 신호 기록 기간에, 구동 트랜지스터(401)를 온 상태로 하기 위해서 게이트 단자의 전위를 용량소자(402)에 축적할 때에는, 도 38과 같이, 전원선(412)과 제1 신호선(410)을 용량소자(402)를 통해 접속한다. 이때, 구동 트랜지스터(401)의 드레인 단자는 게이트 단자(혹은 전원선(412))와 접속되어도 된다. 즉, 도 38의 점선으로 나타낸 부분은 접속되어 있어도 되고, 접속되지 않아도 된다.

- [0321] 구동 트랜지스터(401)의 온/오프를 제어하는 데에 필요한 게이트 전위를 얻을 때에는, 도 39에 나타낸 바와 같이, 구동 트랜지스터(401)의 드레인 단자와 게이트 단자를 접속한다. 이렇게 해서, 구동 트랜지스터(401)가 온 상태로부터 오프 상태가 될 때의 게이트 단자의 전위와, 그때 제1 신호선(410)에 공급되어 있는 아날로그 신호 전위 사이의 전위 차분의 전하가 용량소자(402)에 축적된다.

- [0322] 발광 기간에는, 도 40에 나타낸 바와 같이, 구동 트랜지스터(401)의 게이트 단자를 용량소자(402)를 통해 제2 신호선(411)과 접속하고, 구동 트랜지스터(401)의 드레인 단자와 전원선(412)을 접속한다. 이렇게 해서, 구동 트랜지스터(401)의 드레인 단자에 전원선(412)의 전위를 공급할 수 있다. 따라서, 구동 트랜지스터(401)가 온 상태가 되면 전원선(412)으로부터 표시소자(405)에 전류를 공급할 수 있다.

- [0323] 여기에서, 본 실시예에서는, 도 38에 있어서 점선으로 나타낸 구동 트랜지스터(401)의 드레인 단자와 게이트 단자 및 전원선(412)을 접속하지 않음으로써, 구동 트랜지스터(401)를 충분히 온 상태로 하기 위해서 게이트 단자의 전위를 용량소자(402)에 축적할 때, 표시소자(405)에는 전류를 흘려보내지 않게 할 수 있다. 따라서, 소비 전력을 저감할 수 있다. 그러한 화소 구성의 예를 도 41, 도 42 및 도 43에 나타낸다.

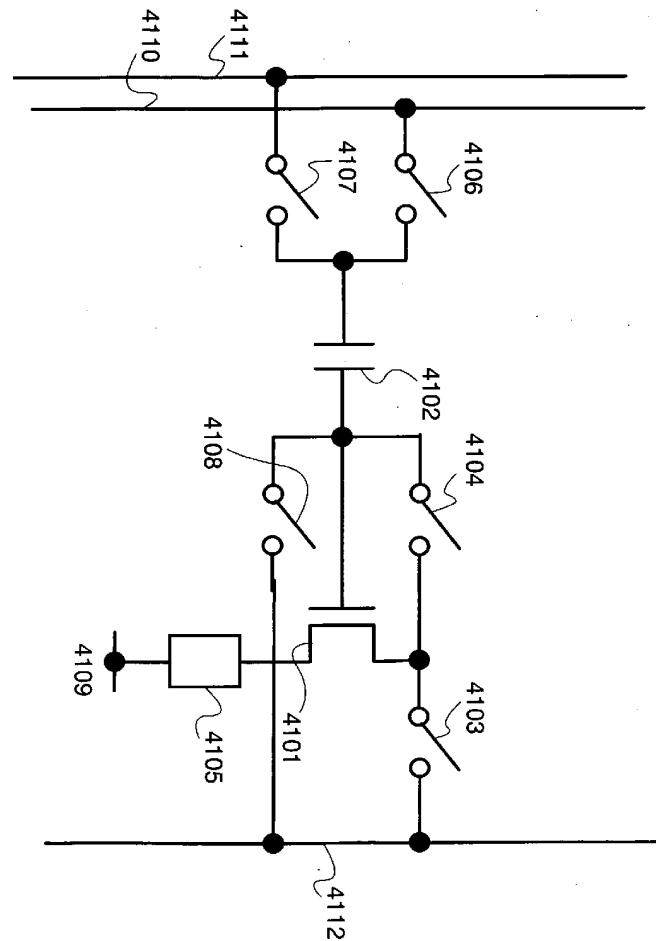

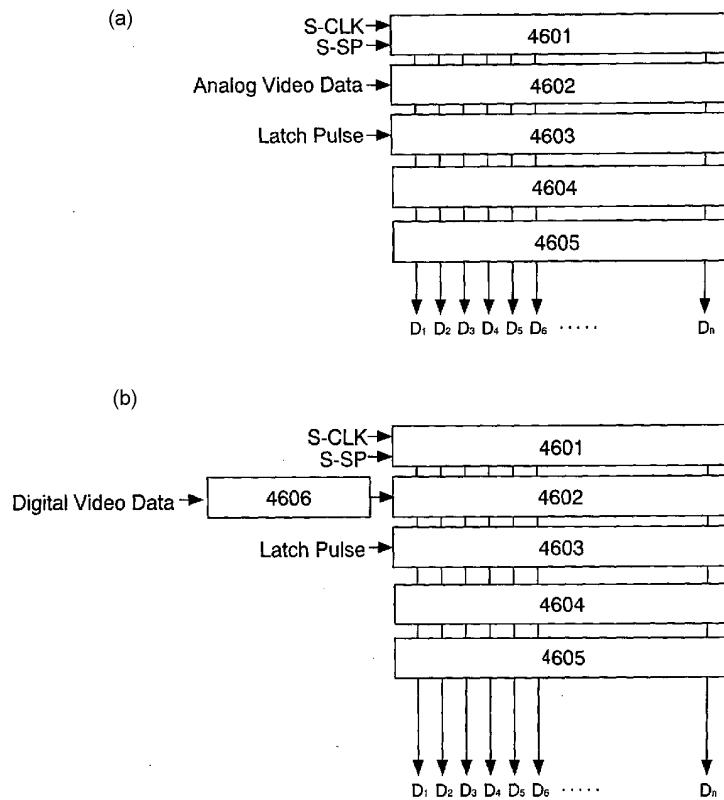

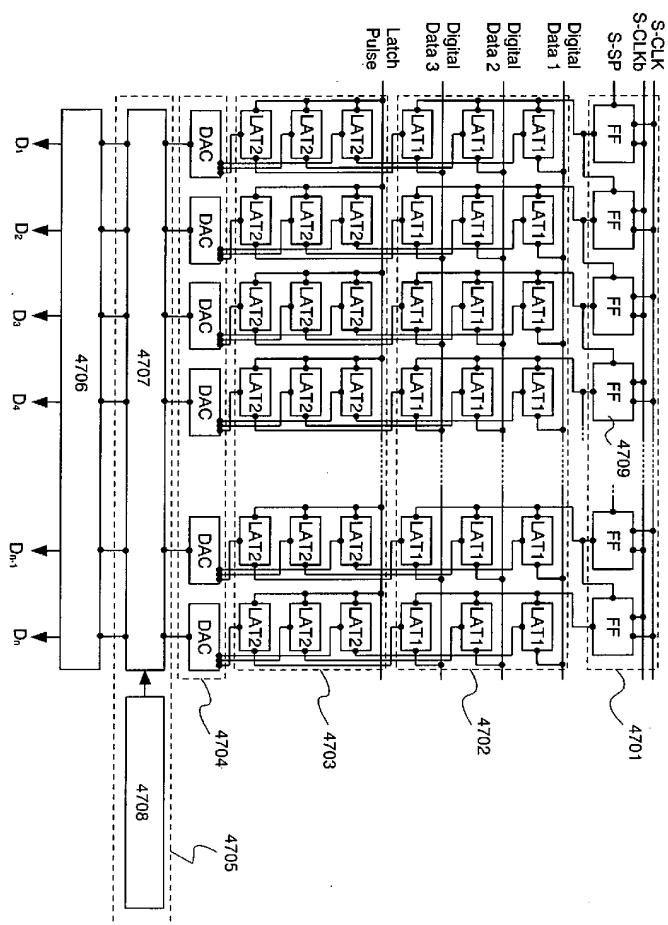

- [0324] 우선, 도 41의 화소 구성에 대해서 자세히 설명한다. 화소는 구동 트랜지스터(4101)와, 용량소자(4102)와, 제1 스위치(4103)와, 제2 스위치(4104)와, 표시소자(4105)와, 제3 스위치(4106)와, 제4 스위치(4107)와, 제5 스위치(4108)와, 제1 신호선(Data1 line)(4110)과, 제2 신호선(Data2 line)(4111)과, 전원선(Supply line)(4112)을 구비한다. 이때, 구동 트랜지스터(4101)에는 n형 트랜지스터를 사용한다.

- [0325] 구동 트랜지스터(4101)의 소스 단자는 표시소자(4105)의 양극과 접속되고, 게이트 단자는 용량소자(4102)의 한 쪽 전극과 접속되고, 용량소자(4102)의 다른 쪽 전극은, 제3 스위치(4106)를 통해 제1 신호선(4110)과, 제4 스위치(4107)를 통해 제2 신호선(4111)과 접속된다. 구동 트랜지스터(4101)의 드레인 단자는 제1 스위치(4103)를 통해 전원선(4112)과 접속된다. 이때, 전원선(4112)에는 전원전위 Vdd가 공급된다. 또한 구동 트랜지스터(4101)의 게이트 단자와 드레인 단자는 제2 스위치(4104)를 통해 접속된다. 따라서 제2 스위치(4104)가 온 상태일 때에는 구동 트랜지스터(4101)의 게이트 단자와 드레인 단자는 도통한다. 그리고, 제2 스위치(4104)가 오프 상태가 되면, 구동 트랜지스터(4101)의 게이트 단자와 드레인 단자는 비도통이 되고, 그 순간의 구동 트랜지스터(4101)의 게이트 단자(드레인 단자)와 제1 신호선(4110)에 의해 공급되는 아날로그 신호 전위 차(전압)를 용량소자(4102)는 유지할 수 있다. 또한 구동 트랜지스터(4101)의 게이트 단자는 제5 스위치(4108)를 통해 전원선(4112)과 접속된다. 또한 표시소자(4105)의 음극은 Vss의 전위가 공급된 배선(4109)과 접속된다. 이때, Vss는 Vss<Vdd를 만족시키는 전위다. 예를 들면, Vss=GND(접지 전위)로 해도 된다. 또한, 전원선에 공급하는 전위는 Vdd에 한정되지 않고, 예를 들면, 색 요소 RGB로 이루어진 폴 컬러 표시의 경우에는, RGB의 각각의 색 요소의 화소마다 전원선의 전위의 값을 변환해도 된다.

- [0326] 다음으로, 도 41의 화소 구성의 동작 원리에 대해서 간단히 설명한다.

- [0327] 화소에의 신호 기록 기간에는, 제4 스위치(4107), 제1 스위치(4103) 및 제2 스위치(4104)를 오프 상태로 하는 한편, 제3 스위치(4106)를 온 상태로 하고, 제5 스위치(4108)를 온 상태로 한다. 그러면, 용량소자(4102)에 전류가 흘러, 전하의 축적 또는 방전이 행해진다. 또한, 화소의 기록 기간에 제1 신호선(4110)에는 아날로그 신호 전위가 공급된다. 이 아날로그 신호 전위가 비디오신호에 해당한다.

- [0328] 이렇게 해서, 구동 트랜지스터(4101)를 충분히 온 상태로 하는 게이트 단자의 전위가 용량소자(4102)에 축적된다. 본 구성에 있어서는, 이때, 표시소자(4105)에는 전류가 흐르지 않는다.

- [0329] 계속해서, 제1 스위치(4103), 제4 스위치(4107)를 끄고, 제3 스위치(4106)를 켜 상태에서, 제5 스위치(4108)를 오프 상태로 하고, 제2 스위치(4104)를 온 상태로 한다. 그러면 용량소자(4102), 구동 트랜지스터(4101) 및 표시소자(4105)에 전류가 흐르기 시작한다.

- [0330] 잠시 후, 구동 트랜지스터(4101) 및 용량소자(4102)에 전류가 흐르지 않게 된다. 이때 구동 트랜지스터(4101)는 오프 상태가 된다.

- [0331] 이 상태가 되면, 제2 스위치(4104)는 오프 상태가 된다. 그러면, 용량소자(4102)에는 트랜지스터를 오프 상태로 하는 구동 트랜지스터(4101)의 게이트 단자의 전위와, 제2 스위치(4104)를 끈 순간 제1 신호선(4110)에 공급되어 있는 아날로그 신호 전위 사이의 전위차( $V_p$ )가 유지된다. 이렇게 해서, 화소에 아날로그 신호가 기록된다.

- [0332] 화소에 아날로그 신호가 기록되면, 그때 제1 신호선(4110)에 공급된 아날로그 신호 전위를 기준으로 해서, 용량소자(4102)의 다른 쪽 전극에 공급되는 전위의 변동에 따라 구동 트랜지스터(4101)의 온/오프가 제어되게 된다. 즉, 용량소자(4102)의 다른 쪽 전극의 전위가, 기록 기간에 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위 이하일 때에는 구동 트랜지스터(4101)는 오프 상태가 되고, 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위보다 높아지면 구동 트랜지스터(4101)는 온 상태가 된다.

- [0333] 화소에 아날로그 신호가 기록되면, 용량소자(4102)가 전위차( $V_p$ )를 유지하므로, 용량소자(4102)의 다른 쪽 전극의 전위가, 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위 이하일 때에는, 구동 트랜지스터(4101)의 게이트 단자의 전위도, 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위보다 높아지면, 구동 트랜지스터(4101)의 게이트 단자의 전위도, 화소에 아날로그 신호가 기록될 때의 게이트 단자의 전위보다 높아지므로, 구동 트랜지스터(4101)는 온 상태가 된다.

- [0334] 따라서, 화소의 발광 기간에는, 제2 스위치(4104), 제5 스위치(4108)가 오프인 상태에서, 제3 스위치(4106)를 오프 상태로 하고, 제1 스위치(4103) 및 제4 스위치(4107)를 온 상태로 한다. 그리고, 제2 신호선(4111)에 공급하는 전위를 아날로그적으로 변화시킴으로써 구동 트랜지스터(4101)의 온/오프를 제어한다. 이때, 제2 신호선(4111)에 공급하는 전위로는, 실시예 1에 나타낸 바와 같이, 과형(5901), 과형(5902), 과형(5903), 과형(5904), 과형(5905), 과형(5906) 혹은 과형(5907), 또는 이것들을 복수 연속으로 공급해도 된다.

- [0335] 연속으로 공급함으로써, 발광 시간을 1프레임 내에서 분산시킬 수 있다. 그 결과, 프레임 주파수가 외형상 향상되고, 화면의 깜박거림을 방지할 수 있다.

- [0336] 이렇게 해서, 화소에 아날로그 신호를 기록할 때에 제1 신호선(4110)에 공급되는 아날로그 신호 전위에 의해 화소의 아날로그 시간계조표시가 가능해진다.

- [0337] 다음으로, 도 42의 화소 구성에 대해서 상세히 설명한다.

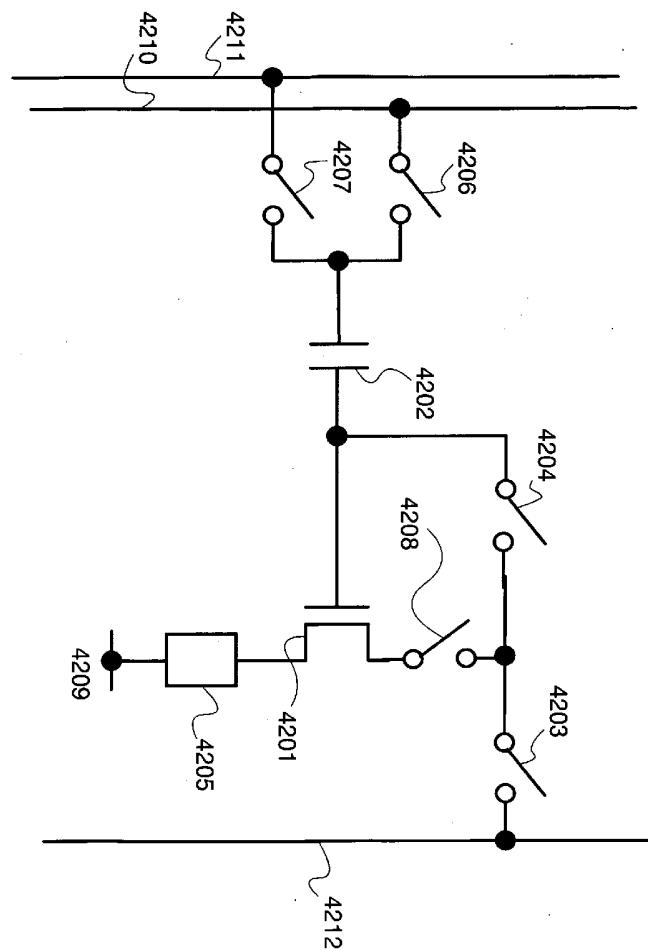

- [0338] 화소는 구동 트랜지스터(4201)와, 용량소자(4202)와, 제1 스위치(4203)와, 제2 스위치(4204)와, 표시소자(4205)와, 제3 스위치(4206)와, 제4 스위치(4207)와, 제5 스위치(4208)와, 제1 신호선(Data1 line)(4210)과, 제2 신호선(Data2 line)(4211)과, 전원선(Supply line)(4212)을 구비한다. 이때, 구동 트랜지스터(4201)에는 n형 트랜지스터를 사용한다.

- [0339] 구동 트랜지스터(4201)의 소스 단자는 표시소자(4205)의 양극과 접속되고, 게이트 단자는 용량소자(4202)의 한쪽 전극과 접속되고, 용량소자(4202)의 다른 쪽 전극은, 제3 스위치(4206)를 통해 제1 신호선(4210)과, 제4 스위치(4207)를 통해 제2 신호선(4211)과 접속된다. 구동 트랜지스터(4201)의 드레인 단자는 제5 스위치(4208) 및 제1 스위치(4203)를 통해 전원선(4212)과 접속된다. 또한 구동 트랜지스터(4201)의 게이트 단자와 드레인 단자는 제2 스위치(4204) 및 제5 스위치(4208)를 통해 접속된다. 따라서 제2 스위치(4204) 및 제5 스위치(4208)가 온 상태일 때에는 구동 트랜지스터(4201)의 게이트 단자와 드레인 단자는 도통한다. 그리고, 제2 스위치(4204) 및 제5 스위치(4208)가 오프 상태가 되면, 그 순간의 구동 트랜지스터(4201)의 게이트 단자(드레인 단자)와 제1 신호선(4210)에 의해 공급되는 아날로그 신호 전위 사이의 전위차(전압)를 용량소자(4202)는 유지할 수 있다. 또한 표시소자(4205)의 음극은  $V_{ss}$ 의 전위가 공급된 배선(4209)과 접속된다. 이때, 전원선에 공급하는 전위는  $V_{dd}$ 에桓정되지 않고, 예를 들면, 색 요소 RGB로 이루어진 풀 컬러 표시의 경우에는, RGB의 각각의 색 요소의 화소마다 전원선의 전위의 값을 변환해도 된다.

- [0340] 다음으로, 도 42의 화소 구성의 동작 원리에 대해서 간단히 설명한다.

- [0341] 화소에의 신호 기록 기간에는, 제3 스위치(4206), 제1 스위치(4203) 및 제2 스위치(4204)를 온 상태로 하고, 제4 스위치(4207), 제5 스위치(4208)를 오프 상태로 한다. 그러면, 용량소자(4202)에 전류가 흘러, 전하의 축적 또는 방전이 행해진다. 이때, 화소의 기록 기간에는, 제1 신호선(4210)에는 아날로그 신호 전위가 공급된다. 이 아날로그 신호 전위는 비디오신호에 해당한다.

- [0342] 이렇게 해서, 구동 트랜지스터(4201)를 충분히 온 상태로 하는 게이트 단자의 전위가 용량소자(4202)에 축적된다. 본 구성에 있어서는 이때, 표시소자(4205)에는 전류가 흐르지 않는다.

- [0343] 계속해서, 제3 스위치(4206), 제2 스위치(4204)를 켜고, 제4 스위치(4207)를 끈 상태에서, 제1 스위치(4203)를 오프 상태로 하고, 제5 스위치(4208)를 온 상태로 한다. 그러면 용량소자(4202), 구동 트랜지스터(4201) 및 표시소자(4205)에 전류가 흐르기 시작한다.

- [0344] 잠시 후, 구동 트랜지스터(4201) 및 용량소자(4202)에 전류가 흐르지 않게 된다. 이렇게 해서, 구동 트랜지스터(4201)는 오프 상태가 된다.

- [0345] 그리고, 이 상태가 되면 제2 스위치(4204)를 오프 상태로 한다. 그러면, 용량소자(4202)에는, 트랜지스터를 오프 상태로 하는 구동 트랜지스터(4201)의 게이트 단자의 전위와, 제2 스위치(4204)를 끈 순간 제1 신호선(4210)에 공급되어 있는 아날로그 신호 전위 사이의 전위차( $V_p$ )가 유지된다. 이렇게 해서 화소에 아날로그 신호가 기록된다.

- [0346] 화소에 아날로그 신호가 기록되면, 그때 제1 신호선(4210)에 공급된 아날로그 신호 전위를 기준으로 해서, 용량소자(4202)의 다른 쪽 전극에 공급되는 전위의 변동에 따라 구동 트랜지스터(4201)의 온/오프가 제어되게 된다. 즉, 용량소자(4202)의 다른 쪽 전극의 전위가, 기록 기간에 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위 이하일 때에는 구동 트랜지스터(4201)는 오프 상태가 되고, 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위보다 높아지면 구동 트랜지스터(4201)는 온 상태가 된다.

- [0347] 화소에 아날로그 신호가 기록되면, 용량소자(4202)가 전위차( $V_p$ )를 유지하므로, 용량소자(4202)의 다른 쪽 전극의 전위가, 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위 이하일 때에는, 구동 트랜지스터(4201)의 게이트 단자의 전위도, 화소에 아날로그 신호가 기록될 때의 게이트 단자의 전위 이하가 되고, 구동 트랜지스터(4201)는 오프 상태가 된다. 한편, 용량소자(4202)의 다른 쪽 전극의 전위가, 기록 기간에 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위보다 높아지면, 구동 트랜지스터(4201)의 게이트 단자의 전위도, 화소에 아날로그 신호가 기록될 때의 게이트 단자의 전위보다 높아지므로, 구동 트랜지스터(4201)는 온 상태가 된다.

- [0348] 따라서, 화소의 발광 기간에는, 제1 스위치(4203), 제4 스위치(4207) 및 제5 스위치(4208)를 온 상태로 하고, 제2 스위치(4204) 및 제3 스위치(4206)를 오프 상태로 한다. 그리고, 제2 신호선(4211)에 공급하는 전위를 아날로그적으로 변화시킴으로써 구동 트랜지스터(4201)의 온/오프를 제어한다. 이때, 제2 신호선(4211)에 공급하는 전위로는, 실시예 1에 나타낸 바와 같이, 과형(5901), 과형(5902), 과형(5903), 과형(5904), 과형(5905), 과형(5906) 혹은 과형(5907), 또는 이것들을 복수 연속으로 공급해도 된다.

- [0349] 연속으로 공급함으로써, 발광 시간을 1프레임 내에서 분산시킬 수 있다. 그 결과, 프레임 주파수가 외형상 향상되고, 화면의 깜빡거림을 방지할 수 있다.

- [0350] 이렇게 해서, 화소에 아날로그 신호를 기록할 때에 제1 신호선(4210)에 공급되는 아날로그 신호 전위에 의해 화소의 아날로그 시간계조표시가 가능해진다.

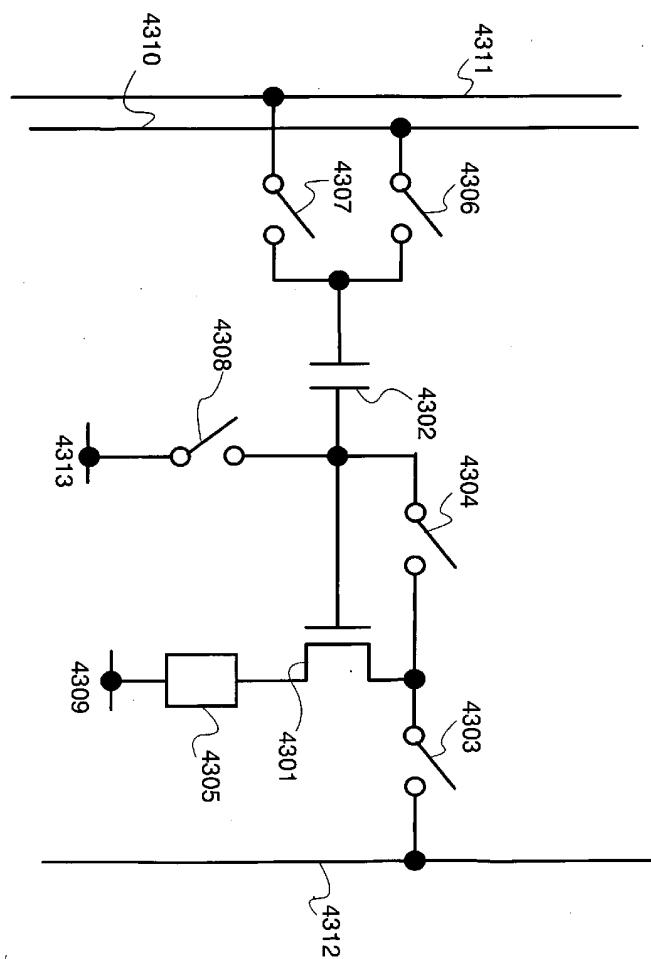

- [0351] 다음으로, 도 43의 화소 구성에 대해서 상세히 설명한다.

- [0352] 화소는 구동 트랜지스터(4301)와, 용량소자(4302)와, 제1 스위치(4303)와, 제2 스위치(4304)와, 표시소자(4305)와, 제3 스위치(4306)와, 제4 스위치(4307)와, 제5 스위치(4308)와, 제1 신호선(Data1 line)(4310)과, 제2 신호선(Data2 line)(4311)과, 전원선(Supply line)(4312)을 구비한다. 이때, 구동 트랜지스터(4301)에는 n형 트랜지스터를 사용한다.

- [0353] 구동 트랜지스터(4301)의 소스 단자는 표시소자(4305)의 양극과 접속되고, 게이트 단자는 용량소자(4302)의 한쪽 전극과 접속되고, 용량소자(4302)의 다른 쪽 전극은, 제3 스위치(4306)를 통해 제1 신호선(4310)과, 제4 스위치(4307)를 통해 제2 신호선(4311)과 접속된다. 구동 트랜지스터(4301)의 드레인 단자는 제1 스위치(4303)를 통해 전원선(4312)과 접속된다. 이때, 전원선(4312)에는 전원전위 Vdd가 공급된다. 또한 구동 트랜지스터(4301)

1)의 게이트 단자와 드레인 단자는 제2 스위치(4304)를 통해 접속된다. 따라서 제2 스위치(4304)가 온 상태일 때에는 구동 트랜지스터(4301)의 게이트 단자와 드레인 단자는 도통한다. 그리고, 제2 스위치(4304)가 오프 상태가 되면, 구동 트랜지스터(4301)의 게이트 단자와 드레인 단자는 비도통이 되고, 그 순간의 구동 트랜지스터(4301)의 게이트 단자(드레인 단자)와 제1 신호선(4310)에 의해 공급되는 아날로그 신호 전위 사이의 전위차(전압)를 용량소자(4302)는 유지할 수 있다. 또한 표시소자(4305)의 음극은 V<sub>ss</sub>의 전위가 공급된 배선(4309)과 접속된다. 이때, 전원선(4312)에 공급하는 전위는 V<sub>dd</sub>에 한정되지 않고, 예를 들면, 색 요소 RGB로 이루어진 풀컬러 표시의 경우에는, RGB의 각각의 색 요소의 화소마다 전원선의 전위의 값을 변환해도 된다.

[0354] 또한 구동 트랜지스터(4301)의 게이트 단자는 제5 스위치(4308)를 통해 제2 배선(4313)과 접속된다. 이때, 제2 배선(4313)은, 기록 기간에 구동 트랜지스터(4301)의 드레인 단자에 전원전위 V<sub>dd</sub>가 공급되었을 때에 구동 트랜지스터(4301)를 충분히 온 상태로 하는 게이트 전위가 설정되어 있으면 된다. 따라서, 제2 배선(4313)은 그 화소의 또는 다른 행의 화소의 제1 스위치(4303), 제2 스위치(4304), 제3 스위치(4306), 제4 스위치(4307) 또는 제5 스위치(4308)를 제어하는 주사선으로 해도 된다.

[0355] 다음으로, 도 43의 화소 구성의 동작 원리에 대해서 간단히 설명한다.

[0356] 화소에의 신호 기록 기간에는, 제1 스위치(4303), 제2 스위치(4304), 제4 스위치(4307)를 오프 상태로 하고, 제3 스위치(4306)를 온 상태로 하고, 제5 스위치(4308)를 온 상태로 한다. 그러면, 용량소자(4302)에 전류가 흘러, 전하의 축적 또는 방전이 행해진다. 이때, 화소의 기록 기간에 제1 신호선(4310)에는 아날로그 신호 전위가 공급된다. 이 아날로그 신호 전위가 비디오신호에 해당한다.

[0357] 이렇게 해서, 구동 트랜지스터(4301)를 충분히 온 상태로 하는 게이트 단자의 전위가 용량소자(4302)에 축적된다. 본 구성에 있어서는 이때, 표시소자(4305)에는 전류가 흐르지 않는다.

[0358] 계속해서, 제3 스위치(4306)를 켜고, 제4 스위치(4307) 및 제1 스위치(4303)를 끈 상태에서, 제5 스위치(4308)를 오프 상태로 하고, 제2 스위치(4304)를 온 상태로 한다. 그러면 용량소자(4302), 구동 트랜지스터(4301) 및 표시소자(4305)에 전류가 흐르기 시작한다.

[0359] 잠시 후, 구동 트랜지스터(4301) 및 용량소자(4302)에 전류가 흐르지 않게 된다. 이렇게 해서, 구동 트랜지스터(4301)는 오프 상태가 된다.

[0360] 이 상태가 되면 제2 스위치(4304)를 오프 상태로 한다. 그러면, 용량소자(4302)에는, 트랜지스터를 오프 상태로 하는 구동 트랜지스터(4301)의 게이트 단자의 전위와, 제2 스위치(4304)를 끈 순간의 제1 신호선(4310)에 공급되어 있는 아날로그 신호 전위 사이의 전위차(V<sub>p</sub>)가 유지된다. 이렇게 해서 화소에 아날로그 신호가 기록된다.

[0361] 화소에 아날로그 신호가 기록되면, 그때 제1 신호선(4310)에 공급된 아날로그 신호 전위를 기준으로 해서, 용량소자(4302)의 다른 쪽 전극에 공급되는 전위의 변동에 따라 구동 트랜지스터(4301)의 온/오프가 제어되게 된다. 즉, 용량소자(4302)의 다른 쪽 전극의 전위가, 기록 기간에 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위 이하일 때에는 구동 트랜지스터(4301)는 오프 상태가 되고, 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위보다 높아지면 구동 트랜지스터(4301)는 온 상태가 된다.

[0362] 화소에 아날로그 신호가 기록되면, 용량소자(4302)가 전위차(V<sub>p</sub>)를 유지하므로, 용량소자(4302)의 다른 쪽 전극의 전위가, 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위 이하일 때에는, 구동 트랜지스터(4301)의 게이트 단자의 전위도, 화소에 아날로그 신호가 기록될 때의 게이트 단자의 전위 이하가 되고, 구동 트랜지스터(4301)는 오프 상태가 된다. 한편, 용량소자(4302)의 다른 쪽 전극의 전위가, 기록 기간에 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위보다 높아지면, 구동 트랜지스터(4301)의 게이트 단자의 전위도, 화소에 아날로그 신호가 기록될 때의 게이트 단자의 전위보다 높아지므로, 구동 트랜지스터(4301)는 온 상태가 된다.

[0363] 따라서, 화소의 발광 기간에는, 제2 스위치(4304), 제3 스위치(4306), 제5 스위치(4308)를 오프 상태로 하고, 제1 스위치(4303), 제4 스위치(4307)를 온 상태로 한 상태에서, 제2 신호선(4311)에 공급하는 전위를 아날로그적으로 변화시킴으로써 구동 트랜지스터(4301)의 온/오프를 제어하고, 표시소자(4305)에 전류가 흐르고 있는 시간을 아날로그적으로 제어하여, 계조를 표현할 수 있게 된다.

[0364] 이때, 제2 신호선(4311)에 공급하는 전위로는, 실시예 1에 나타낸 바와 같이, 파형(5901), 파형(5902), 파형(5903), 파형(5904), 파형(5905), 파형(5906) 혹은 파형(5907), 또는 이것들을 복수 연속으로 공급해도 된다.

[0365] 연속으로 공급함으로써, 발광 시간을 1프레임 내에서 분산시킬 수 있다. 그 결과, 프레임 주파수가 외형상 향상

되고, 화면의 깜박거림을 방지할 수 있다

[0366] 이렇게 해서, 화소에 아날로그 신호를 기록할 때에 제1 신호선(4310)에 공급되는 아날로그 신호 전위에 의해 화소의 아날로그 시간계조표시가 가능해진다.

[0367] 이때, 실시예 1, 실시예 2, 실시예 3 및 실시예 4에 나타내는 구성을 적절히 조합할 수 있다. 그렇게 해서, 화소에의 신호 기록 기간에 있어서의 소비 전류를 감하고, 소비 전력을 줄일 수 있다.

[0368] 이때, 본 실시예에 있어서, 표시소자를 구동하는 구동 트랜지스터의 소스 단자 및 드레인 단자, 및 표시소자의 양극 및 음극은, 표시소자에 순방향의 전압이 인가될 때의 단자 및 전극을 말한다.

[0369] (실시예 6)

[0370] 본 실시예에서는, 실시예 1에 나타낸 화소 구성에 있어서, 표시소자의 신뢰성을 더욱 향상시키는 구동방법과, 실시예 1에 나타낸 화소 구성보다 더욱 표시소자의 신뢰성이 향상되는 화소 구성 및 그 구동방법에 관하여 설명한다.

[0371] 우선, 실시예 1의 도 1에 나타낸 화소 구성은 참고로, 본 실시예에 의한 구동방법에 대해 설명한다.

[0372] 본 실시예에 있어서는, 1프레임 기간에 순방향 바이어스 기간(기록 기간 및 발광 기간)과 역방향 바이어스 기간을 가진다. 순방향 바이어스 기간에 있어서 기록 기간 및 발광 기간은 실시예 1에 나타낸 동작과 같으므로 그 설명은 생략한다.

[0373] 역방향 바이어스 기간에는, 전원선(109)에 공급하는 전위 Vdd와 배선(110)에 공급하는 전위 Vss를 반대로 한다. 즉, 역방향 바이어스 기간에는 전원선(109)에 Vss를 공급하고, 배선(110)에는 Vdd의 전위를 공급한다. 그리고, 제2 스위치(104)를 오프 상태로 하고, 제1 스위치(103)를 온 상태로 한다. 그러면, 구동 트랜지스터(101)의 소스 단자와 드레인 단자는 순방향 바이어스 기간과는 역이 된다. 또한 표시소자(105)의 양극 또는 음극도 역이 된다. 이때, 신호선(108)에는 구동 트랜지스터(101)를 충분히 온 상태로 하도록 전위를 공급한다.

[0374] 이때, 역방향 바이어스 기간의 초기에 구동 트랜지스터(101)의 게이트 단자의 전위를 설정해도 된다. 즉, 도 68에 나타낸 바와 같이, 역방향 바이어스 기간의 초기에, 게이트 전위설정 기간 Tr를 설정한다. 이때, 제1 주사선(106) 및 제2 주사선(107)에 H레벨의 신호를 공급하고, 제1 스위치(103) 및 제2 스위치(104)를 온 상태로 한다. 그리고, 전원선(109)의 전위는 Vdd로 설정하고, 신호선(108)에는 L레벨의 전위를 공급해 둔다. 그러면, 구동 트랜지스터(101)의 게이트 단자의 전위 Vdd와 신호선(108)의 L레벨의 전위 사이의 전위차가 용량소자(102)에 유지된다.

[0375] 역방향 바이어스 기간에, 게이트 전위설정 기간 Tr이 종료되면, 제1 주사선(106)의 전위가 H레벨인 상태에서, 제2 주사선(107)의 전위는 L레벨이 되어, 제1 스위치(103)는 온, 제2 스위치(104)는 오프 상태가 된다. 그리고, 신호선(108)의 전위가 L레벨로부터 H레벨이 된다. 그러면, 용량소자(102)가 전위차를 유지한 상태에서, 신호선(108)의 전위가 높아지므로, 구동 트랜지스터(101)의 게이트 단자의 전위는 Vdd 이상이 되고, 구동 트랜지스터(101)는 충분히 온 상태로 할 수 있다.

[0376] 따라서, 구동 트랜지스터(101)는 온 상태가 되고, 표시소자(105)에는, 순방향 바이어스 기간과는 반대의 전압을 표시소자(105)에 인가할 수 있다.

[0377] 이렇게, 역방향 바이어스 기간에, 순방향 바이어스 기간과는 역방향의 전압을 표시소자(105)에 인가해도, 정상적인 표시소자(105)에는 전류가 흐르지 않는다(혹은 흐르더라도 극소량의 전류가 흐른다). 한편, 표시소자(105)에 단락 부분이 있는 경우에는, 그 단락 부분에 전류가 흐른다. 따라서, 역방향 바이어스 기간에는, 이 단락 부분을 절연하는 데에 충분한 전류가 흐르도록 역방향의 전압을 인가한다.

[0378] 따라서, 상기한 바와 같이, 역방향 바이어스 기간에, 전원선(109)에 공급하는 전위는 Vss에 한정되지 않는다. 또한 배선(110)에 공급하는 전위도 Vdd에 한정되지 않는다. 즉, 역방향 바이어스 기간에 표시소자(105)의 단락 부분을 절연하는 데에 충분한 전류를 흐르게 할 수 있으면 된다.

[0379] 이렇게, 표시소자(105)의 단락 부분을 절연함으로써, 화소의 표시 불량을 개선할 수 있다. 또한 표시소자(105)의 수명을 연장할 수 있다.

[0380] 다음으로, 실시예 1과는 다른 화소 구성에 의해, 표시소자의 신뢰성을 높이는 화소에 대해서도 66을 참조하여 설명한다.

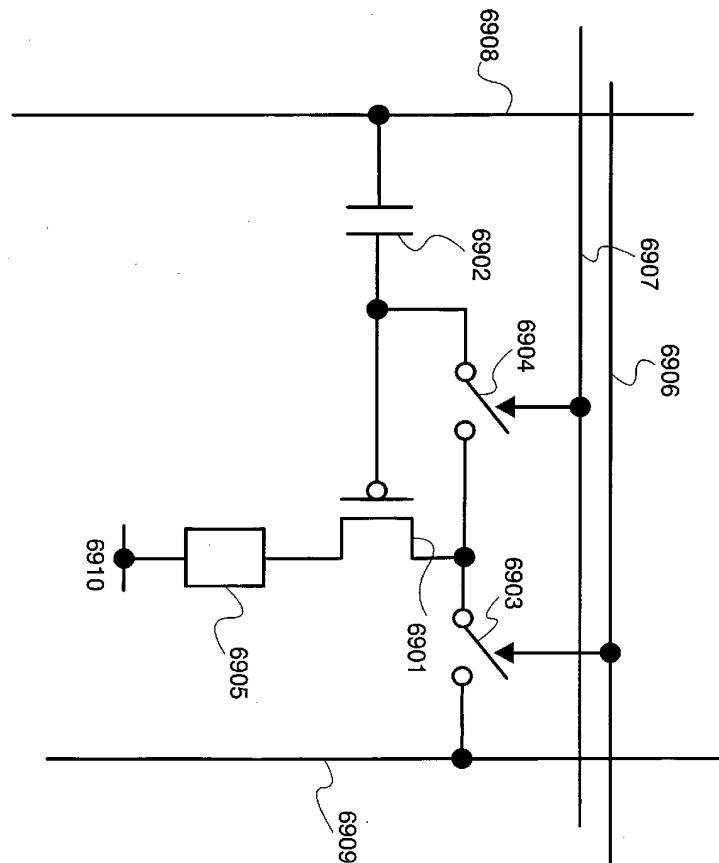

- [0381] 화소는 구동 트랜지스터(6601)와, 용량소자(6602)와, 제1 스위치(6603)와, 제2 스위치(6604)와, 표시소자(6605)와, 제1 주사선(G1 line)(6606)과, 제2 주사선(G2 line)(6607)과, 신호선(Data line)(6608)과, 전원선(Supply line)(6609)과, 역바이어스용 스위치(6621)를 구비한다. 이때, 구동 트랜지스터(6601)에는 n형 트랜지스터를 사용한다.

- [0382] 구동 트랜지스터(6601)의 소스 단자는 표시소자(6605)의 양극과 접속되고, 게이트 단자는 용량소자(6602)를 통해 신호선(6608)과 접속되고, 드레인 단자는 제1 스위치(6603)를 통해 전원선(6609)과 접속된다. 이때, 전원선(6609)에는 전원전위 Vdd가 공급된다. 또한, 전원선(6609)에 공급하는 전위는 Vdd에 한정되지 않고, 예를 들면, 색 요소 RGB로 이루어진 풀 컬러 표시의 경우에는, RGB의 각각의 색 요소의 화소마다 전원전위의 값을 변환해도 된다.

- [0383] 또한 구동 트랜지스터(6601)의 게이트 단자와 드레인 단자는 제2 스위치(6604)를 통해 접속된다. 따라서 제2 스위치(6604)가 온 상태일 때에는 구동 트랜지스터(6601)의 게이트 단자와 드레인 단자는 도통한다. 그리고, 제2 스위치(6604)가 오프 상태가 되면, 구동 트랜지스터(6601)의 게이트 단자와 드레인 단자는 비도통이 되고, 그 순간의 구동 트랜지스터(6601)의 게이트 단자(드레인 단자)와 신호선(6608) 사이의 전위차(전압)를 용량소자(6602)는 유지할 수 있다. 또한 표시소자(6605)의 음극은 Vss의 전위가 공급된 제1 배선(6610)과 접속된다. 이때, Vss는 Vss<Vdd를 만족시키는 전위다. 예를 들면, Vss=GND(접지 전위)로 해도 된다. 또한 구동 트랜지스터(6601)의 소스 단자와 표시소자(6605)의 양극은, 역바이어스용 스위치(6621)를 통해 Vss2의 전위가 공급된 제2 배선(6622)과 접속된다. 이때, Vss2는 Vss2<Vss를 만족시키는 전위다.

- [0384] 다음으로, 도 66의 화소 구성의 동작 원리에 관하여 설명한다.

- [0385] 이때, 본 실시예에 나타내는 화소 구성에서는, 1프레임 기간에 순방향 바이어스 기간(기록 기간 및 발광 기간)과 역방향 바이어스 기간을 가진다.

- [0386] 화소의 신호 기록 기간에는, 역바이어스용 스위치(6621)를 끈 상태에서, 제1 주사선(6606) 및 제2 주사선(6607)에 신호를 입력하고, 제1 스위치(6603) 및 제2 스위치(6604)를 온 상태로 한다. 그러면, 구동 트랜지스터(6601)의 드레인 단자와 게이트 단자에 전원선(6609)의 전원전위(Vdd)가 공급된다. 그리고, 용량소자(6602), 구동 트랜지스터(6601) 및 표시소자(6605)에 전류가 흘러, 용량소자(6602)에서는 전하의 축적 또는 방전이 행해진다. 이때, 화소에의 신호 기록 기간에 신호선(6608)에는 아날로그 신호 전위가 공급된다. 이 아날로그 신호 전위는 비디오신호에 해당한다.

- [0387] 잠시 후, 용량소자(6602)에는 전류가 흐르지 않게 된다. 그리고, 구동 트랜지스터(6601) 및 표시소자(6605)에 전류가 흐른다. 왜냐하면, 이때 구동 트랜지스터(6601)의 게이트 단자는, 제2 스위치(6604)에 의해 드레인 단자와 도통하고 있어, 게이트 단자의 전위는 전원전위(Vdd)가 되고 구동 트랜지스터(6601)는 온 상태이기 때문이다.

- [0388] 이 상태에서, 제1 스위치(6603)를 끄면, 구동 트랜지스터(6601)와 용량소자(6602)에 전류가 흐르고, 잠시 후, 거기에 전류가 흐르지 않게 된다. 이렇게 해서, 구동 트랜지스터(6601)는 오프 상태가 된다. 이때, 구동 트랜지스터(6601)의 게이트-소스간 전압 Vgs는 역치전압 Vth와 대략 동등하다.

- [0389] 이 상태가 되면 제2 스위치(6604)는 오프 상태가 되고, 용량소자(6602)에는, 트랜지스터를 오프 상태로 하는 구동 트랜지스터(6601)의 게이트 단자의 전위와, 제2 스위치(6604)를 끈 순간 신호선(6608)에 공급되어 있는 아날로그 신호 전위 사이의 전위차(Vp)가 유지된다. 이렇게 해서 화소에 아날로그 신호가 기록된다.

- [0390] 이때, 전술한 제1 스위치(6603), 및 제2 스위치(6604)의 온/오프는 제1 주사선(6606), 및 제2 주사선(6607)에 각각 펄스 신호를 입력해서 제어할 수 있다.

- [0391] 화소에 아날로그 신호가 기록되면, 그때 신호선(6608)에 공급된 아날로그 신호 전위를 기준으로 해서, 신호선(6608)의 전위의 변동에 따라 구동 트랜지스터(6601)의 온/오프가 제어되게 된다. 즉, 신호선(6608)의 전위가, 신호 기록 기간에 화소에 기록될 때의 아날로그 신호 전위 이하일 때에는 구동 트랜지스터(6601)는 오프 상태가 되고, 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위보다 높아지면 구동 트랜지스터(6601)는 온 상태가 된다.

- [0392] 화소에 아날로그 신호가 기록되면, 용량소자(6602)가 전위차(Vp)를 유지하므로, 신호선(6608)의 전위가, 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위 이하일 때에는, 구동 트랜지스터(6601)의 게이트 단자의 전위도, 화소에 아날로그 신호가 기록될 때의 게이트 단자의 전위 이하가 되고, 구동 트랜지스터(6601)는 오프 상태

가 된다. 한편, 신호선(6608)의 전위가, 기록 기간에 화소에 아날로그 신호가 기록될 때의 아날로그 신호 전위보다 높아지면, 구동 트랜지스터(6601)의 게이트 단자의 전위도, 화소에 아날로그 신호가 기록될 때의 게이트 단자의 전위보다 높아지므로 구동 트랜지스터(6601)는 온 상태가 된다.

[0393] 따라서, 화소의 발광 기간에는, 역바이어스용 스위치(6621)를 끈 상태에서, 제2 스위치(6604)를 오프 상태로 하고, 제1 스위치(6603)를 켠 상태에서, 신호선(6608)에 공급하는 전위를 아날로그적으로 변화시킴으로써 구동 트랜지스터(6601)의 온/오프를 제어하고, 표시소자(6605)에 전류가 흐르고 있는 시간을 아날로그적으로 제어하여, 제조를 표현할 수 있게 된다.

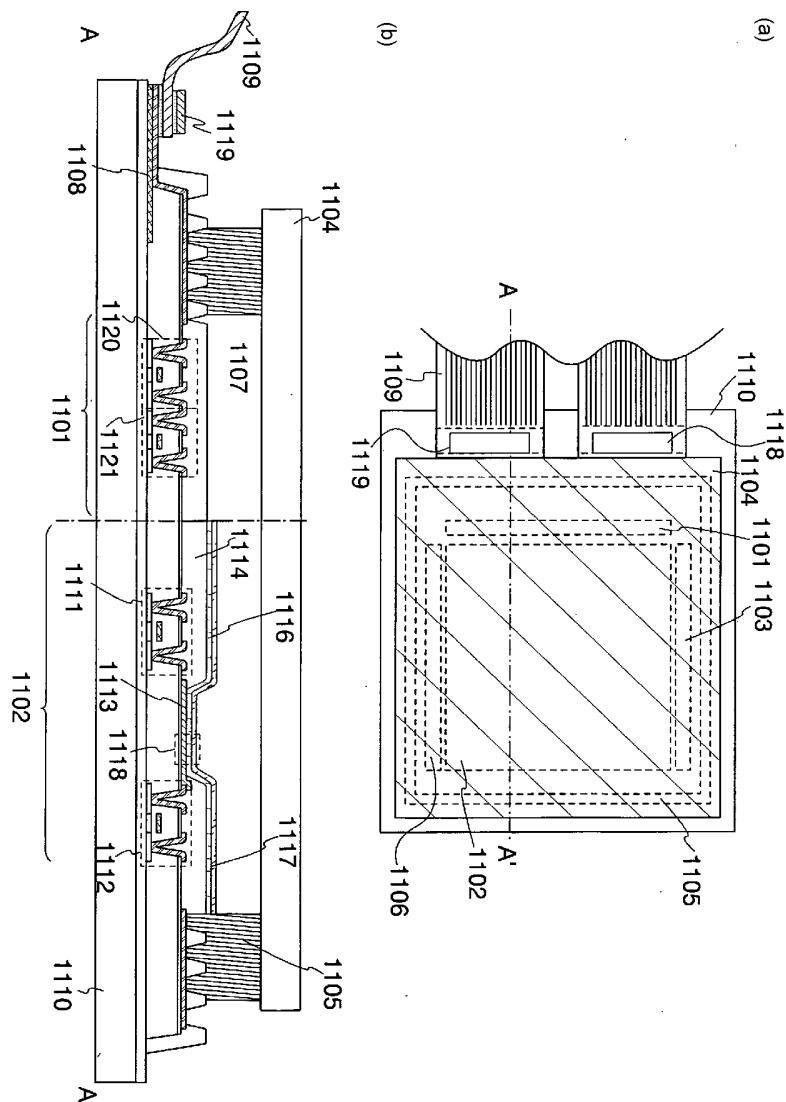

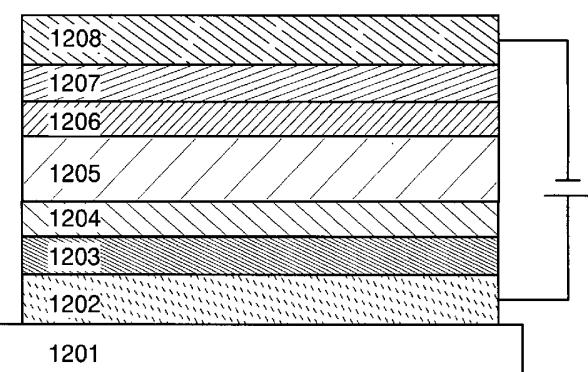

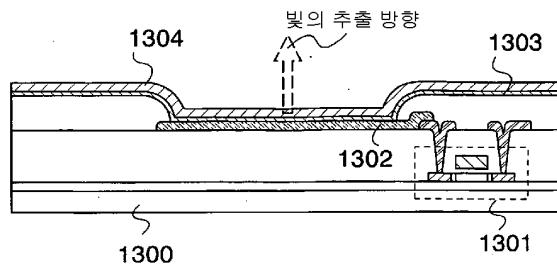

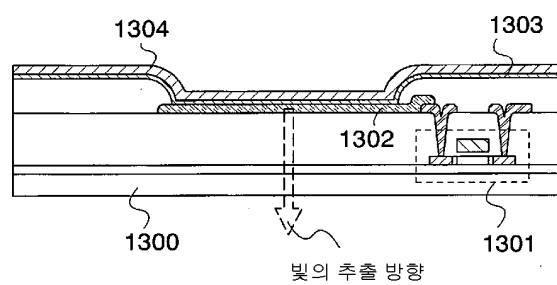

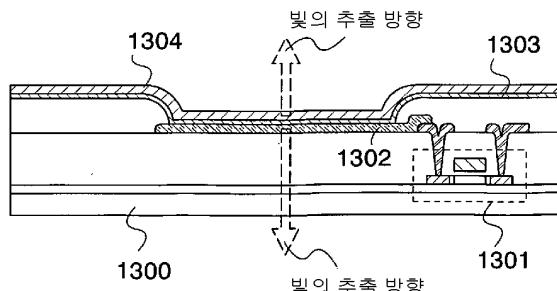

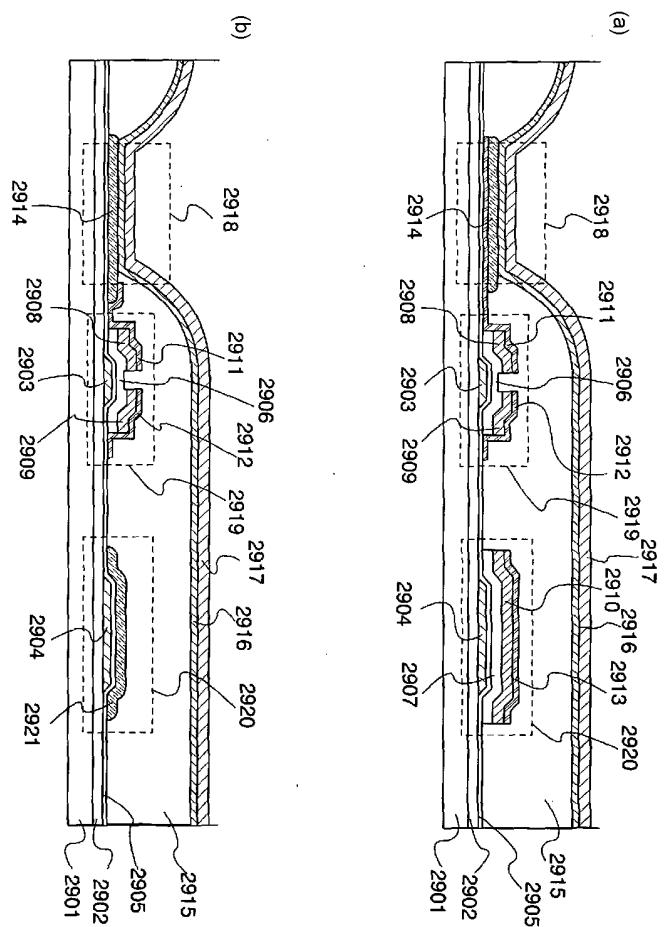

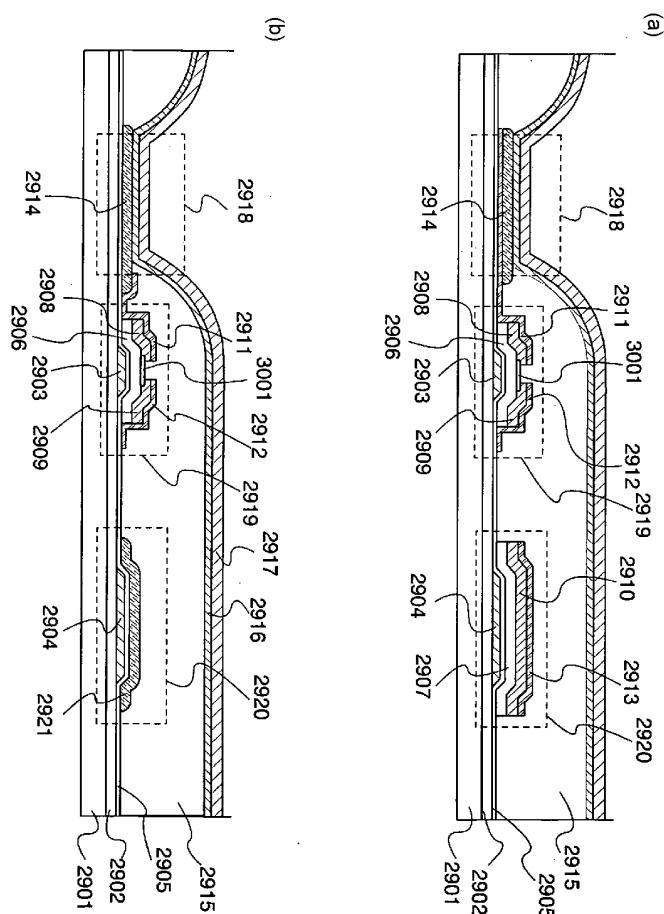

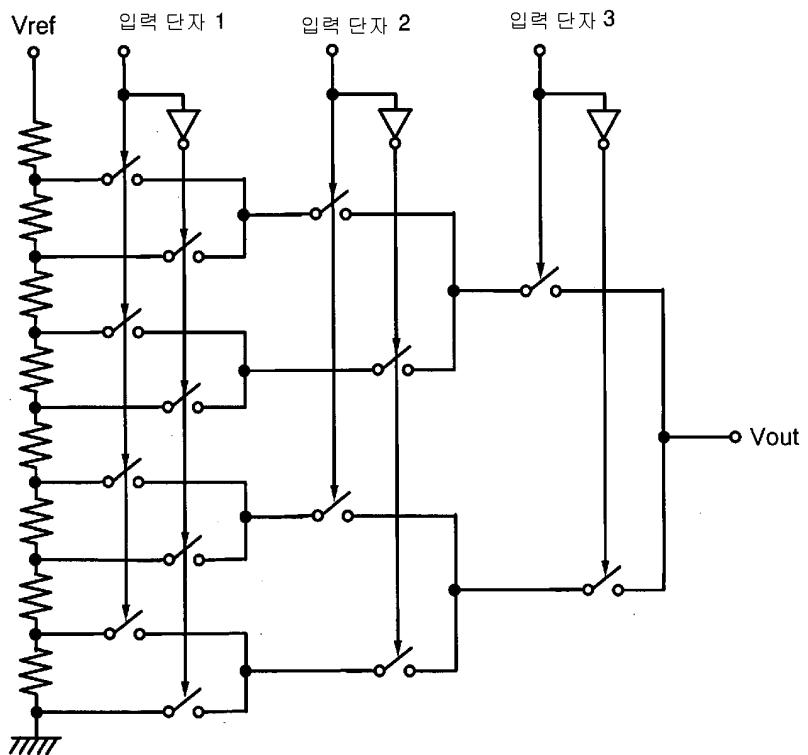

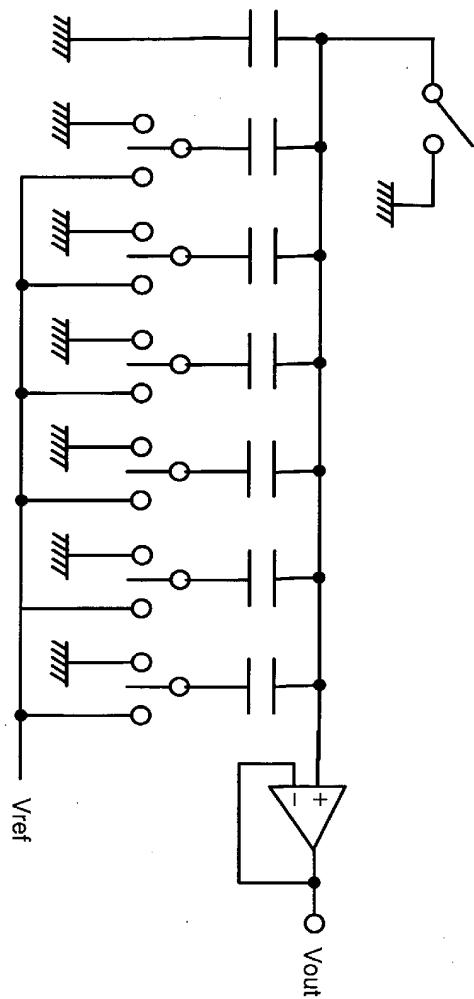

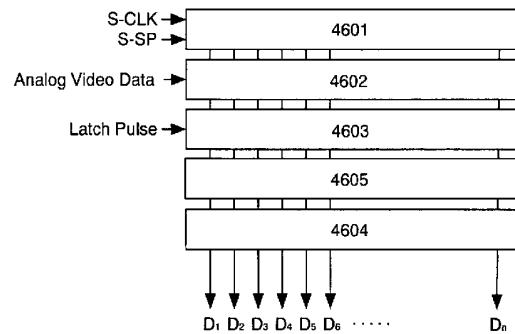

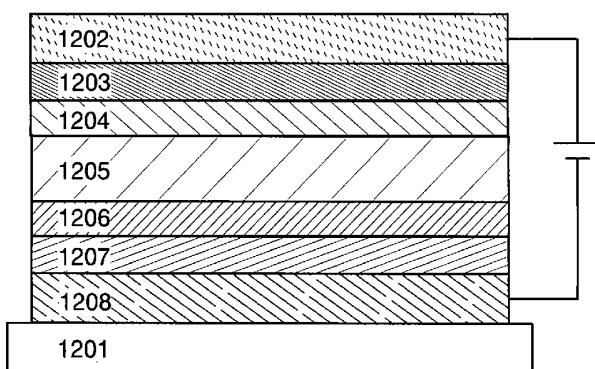

[0394] 이때, 신호선(6608)에 공급하는 전위로는, 실시예 1에 나타낸 바와 같이, 파형(5901), 파형(5902), 파형(5903), 파형(5904), 파형(5905), 파형(5906) 혹은 파형(5907), 또는 이것들을 복수 연속으로 공급해도 된다.