#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2016/012893 A1

(43) International Publication Date 28 January 2016 (28.01.2016)

(21) International Application Number:

PCT/IB2015/055183

(22) International Filing Date:

9 July 2015 (09.07.2015)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data: 2014-151623

25 July 2014 (25.07.2014)

JP

- (71) Applicant: SEMICONDUCTOR ENERGY LABORAT-ORY CO., LTD. [JP/JP]; 398, Hase, Atsugi-shi, Kanagawa 2430036 (JP).

- (72) Inventors: OKAMOTO, Yuki; c/o SEMICONDUCTOR ENERGY LABORATORY CO., LTD., 398, Hase, Atsugishi, Kanagawa 2430036 (JP). KUROKAWA, Yoshiyuki.

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM,

AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### Published:

with international search report (Art. 21(3))

(54) Title: OSCILLATOR CIRCUIT AND SEMICONDUCTOR DEVICE INCLUDING THE SAME

(57) Abstract: Controllability of an oscillator circuit is improved. The oscillator circuit has inverters in odd-numbered stages. A circuit is electrically connected to a power supply node of the inverters to which a high power supply potential is input. The circuit includes a first transistor, a second transistor, and a capacitor. The first transistor includes an oxide semiconductor in its channel. A holding circuit including the first transistor and the capacitor has a function of holding an analog potential that is input from the outside. The potential held by the holding circuit is input to a gate of the second transistor. A power supply potential is supplied to the inverters through the second transistor, so that the delay time of the inverter can be controlled by the potential of the gate of the second transistor.

#### **DESCRIPTION**

#### OSCILLATOR CIRCUIT AND SEMICONDUCTOR DEVICE INCLUDING THE SAME

### 5 TECHNICAL FIELD

[0001]

One embodiment of the present invention disclosed in this specification, the drawings, and the claims (hereinafter referred to as "this specification and the like") relates to a semiconductor device such as an oscillator circuit, a signal generating circuit, or a processing device, a driving method thereof, a manufacturing method thereof, and the like.

[0002]

15

20

Note that one embodiment of the present invention is not limited to the above technical field. The technical field of one embodiment of the present invention relates to an object, a method, or a manufacturing method. One embodiment of the present invention relates to a process, a machine, manufacture, or a composition of matter. Specific examples of the technical field of one embodiment of the present invention include a semiconductor device, an oscillator circuit, a signal generating circuit, a processing device, a memory device, a display device, a liquid crystal display device, a light-emitting device, a lighting device, a power storage device, an input device, an imaging device, a method for driving any of them, and a method for manufacturing any of them.

### **BACKGROUND ART**

[0003]

A voltage controlled oscillator (VCO) is one of oscillator circuits and has a function of controlling the oscillation frequency of an output signal by voltage. For example, a ring-oscillator-based VCO is known (e.g., Patent Document 1). The VCO is used in a phase-locked loop (PLL), for example (e.g., Non-Patent Document 1).

[Patent Document]

[0004]

Patent Document 1: Japanese Published Patent Application No. 06-310994

[Non-Patent Document]

[0005]

X. Gao, et al., "Jitter Analysis and a Benchmarking Figure-of-Merit for Phase-Locked Loops", IEEE Trans. On Circuits and Systems-II, vol. 56, no. 2, pp. 117-121, Feb. 2009

## DISCLOSURE OF INVENTION

[0006]

An object of one embodiment of the present invention is to provide a novel semiconductor device or a method for driving the same. Another object of one embodiment of the present invention is to provide a semiconductor device with excellent controllability and a method for driving the same, a semiconductor device having a short starting time and a method for driving the same, or a programmable semiconductor device and a method for driving the same.

10 [0007]

15

25

30

35

Note that the description of a plurality of objects does not preclude the existence of each object. One embodiment of the present invention does not necessarily achieve all the objects. Objects other than those listed above are apparent from the description of the specification, drawings, and claims, and also such objects could be an object of one embodiment of the present invention.

## MEANS FOR SOLVING THE PROBLEMS [0008]

One embodiment of the present invention is an oscillator circuit including first- to n-th-stage first circuits (n is an odd number) and a second circuit. Each of the first-to n-th-stage first circuits includes a first input node, a first output node, an inverter, and a third The first output node of the first circuit in an i-th stage (i is an integer greater than or equal to 1 and less than or equal to (n-1) is electrically connected to the first input node of the first circuit in a next stage. The output node of the first circuit in the *n*-th stage is electrically connected to the input node of the first circuit in the first stage. An input node of the inverter is electrically connected to the first input node. An output node of the inverter is electrically connected to the first output node. The inverter includes a first power supply node and a second power supply node. The third circuit includes a second input node, a second output node, a third node, a first transistor, a second transistor, and a first capacitor. The second output node is electrically connected to the first power supply node. A first potential is input to the second input node. A first terminal of the first transistor is electrically connected to the second input node. A second terminal of the first transistor is electrically connected to the third node. The first transistor includes an oxide semiconductor in its channel. The first capacitor has a function of holding a potential of the third node. A gate of the second transistor is electrically connected to the third node. A second potential is input to a first terminal of the second

transistor. A second terminal of the second transistor is electrically connected to the second output node. The second circuit has a function of changing an amplitude of an output signal of the first output node of the first circuit in the *n*-th stage.

[0009]

In the above embodiment, when a power supply potential input to the second power supply node is lower than a potential input to the first power supply node, the second transistor is preferably an n-channel transistor. Alternatively, when a power supply potential input to the second power supply node is higher than the potential input to the first power supply node, the second transistor is preferably a p-channel transistor.

10 [0010]

5

In the above embodiment, the first- to *n*-th-stage first circuits each include a first switch. A conduction state between the output node of the inverter and the first output node may be controlled by the first switch.

[0011]

In the above embodiment, the first- to *n*-th-stage first circuits each include a second switch. A conduction state between the first power supply node and the second output node may be controlled by the second switch.

[0012]

In the above embodiment, different signals are input to gates of first transistors of the 20 first- to *n*-th-stage first circuits.

[0013]

In this specification and the like, ordinal numbers such as first, second, and third are used to avoid confusion among components, and the terms do not limit the components numerically or do not limit the order.

25 [0014]

30

35

In this specification and the like, a semiconductor device refers to a device that utilizes semiconductor characteristics, and means a circuit including a semiconductor element (e.g., a transistor or a diode), a device including the circuit, and the like. The semiconductor device also means any device that can function by utilizing semiconductor characteristics. For example, an integrated circuit, and a chip including an integrated circuit are all semiconductor devices. Moreover, a memory device, a display device, a light-emitting device, a lighting device, an electronic device, and the like themselves might be semiconductor devices, or might each include a semiconductor device.

[0015]

Note that a transistor includes three terminals: a gate, a source, and a drain. The gate

serves as a control terminal for controlling the on/off of the transistor. Depending on the channel type of the transistor or levels of potentials applied to the terminals, one of terminals functions as a source and the other functions as a drain. In general, in an n-channel transistor, a terminal to which a lower potential is applied is called a source, and a terminal to which a higher potential is applied is called a drain. In contrast, in a p-channel transistor, a terminal to which a lower potential is applied is called a drain, and a terminal to which a higher potential is applied is called a source. In this specification, in some cases, two terminals that are not the gate of the transistor are referred to as a first terminal and a second terminal in some cases.

[0016]

5

10

15

20

25

35

In this specification, to clarify a circuit configuration and circuit operation, one of input and output terminals of a transistor is fixed as a source and the other is fixed as a drain in some cases. It is needless to say that, depending on a driving method, the magnitude relationship between potentials applied to three terminals of the transistor might be changed, and the source and the drain might be interchanged. Thus, in one embodiment of the present invention, the distinction between the source and drain of the transistor is not limited to that described in this specification and the drawings.

[0017]

A node can be referred to as a terminal, a wiring, an electrode, a conductor, an impurity region, or the like depending on a circuit configuration, a device structure, and the like. Furthermore, a terminal and the like can be referred to as a node.

[0018]

For example, in this specification and the like, an explicit description "X and Y are connected" means that X and Y are electrically connected, X and Y are functionally connected, and X and Y are directly connected. Accordingly, without limitation to a predetermined connection relation, for example, a connection relation shown in drawings or text, another connection relation is included in the drawings or the text.

[0019]

Here, X and Y each denote an object (e.g., a device, a circuit, an element, a wiring, an electrode, a terminal, a node, a film, a layer, and a region).

30 [0020]

Examples of the case where X and Y are directly connected include the case where an element that allows an electrical connection between X and Y (e.g., a switch, a transistor, a capacitor, an inductor, a resistor, a diode, a display element, a light-emitting element, and a load) is not connected between X and Y, and the case where X and Y are connected without the element that allows the electrical connection between X and Y provided therebetween.

[0021]

For example, in the case where X and Y are electrically connected, one or more elements which enable electrical connection between X and Y (e.g., a switch, a transistor, a capacitor, an inductor, a resistor, a diode, a display element, a light-emitting element, and a load) can be connected between X and Y. A switch is controlled to be on or off. That is, a switch is conducting or not conducting (is turned on or off) to determine whether current flows therethrough or not. Alternatively, the switch has a function of selecting and changing a current path. Note that the case where X and Y are electrically connected includes the case where X and Y are directly connected.

10 [0022]

15

5

For example, in the case where X and Y are functionally connected, one or more circuits that enable functional connection between X and Y (e.g., a logic circuit such as an inverter (NOT) circuit, a NAND circuit, or a NOR circuit; a signal converter circuit such as a D/A converter circuit, an A/D converter circuit, or a gamma correction circuit; a potential level converter circuit such as a power supply circuit (e.g., a step-up circuit or a step-down circuit) or a level shifter circuit for changing the potential level of a signal; a voltage source; a current source; a switching circuit; an amplifier circuit such as a circuit that can increase signal amplitude, the amount of current, or the like, an operational amplifier, a differential amplifier circuit, a source follower circuit, or a buffer circuit; a signal generation circuit; a memory circuit; or a control circuit) can be connected between X and Y. Note that for example, in the case where a signal output from X is transmitted to Y even when another circuit is interposed between X and Y, X and Y are functionally connected. Note that the case where X and Y are functionally connected includes the case where X and Y are directly connected and the case where X and Y are electrically connected.

25 [0023]

30

35

Note that in this specification and the like, an explicit description "X and Y are electrically connected" means that X and Y are electrically connected (i.e., the case where X and Y are connected with another element or another circuit provided therebetween), X and Y are functionally connected (i.e., the case where X and Y are functionally connected with another element or another circuit provided therebetween), and X and Y are directly connected (i.e., the case where X and Y are connected without another element or another circuit provided therebetween). That is, in this specification and the like, the explicit description "X and Y are electrically connected" is the same as the description "X and Y are connected".

[0024]

Note that, for example, the case where a first terminal of a transistor is electrically

connected to X through (or not through) Z1 and a second terminal of the transistor is electrically connected to Y through (or not through) Z2, or the case where a first terminal of a transistor is directly connected to one part of Z1 and another part of Z1 is directly connected to X while a second terminal of the transistor is directly connected to one part of Z2 and another part of Z2 is directly connected to Y, can be expressed by using any of the following expressions.

5

15

20

25

30

35

Examples of the expressions include, "X, Y, a first terminal of a transistor, and a second terminal of the transistor are electrically connected to each other, and X, the first terminal of the transistor, the second terminal of the transistor, and Y are electrically connected to each other in this order", "a first terminal of a transistor is electrically connected to X, a second terminal of the transistor is electrically connected to Y, and Y, the first terminal of the transistor, the second terminal of the transistor, and Y are electrically connected to each other in this order", and "X is electrically connected to Y through a first terminal and a second terminal of a transistor, and X, the first terminal of the transistor, the second terminal of the transistor, and Y are provided to be connected in this order. When the connection order in a circuit configuration is defined by an expression similar to the above examples, a first terminal and a second terminal of a transistor can be distinguished from each other to specify the technical scope [0026]

Another example of the expression is "a first terminal of a transistor is electrically connected to X through at least a first connection path, the first connection path does not include a second connection path, the second connection path is a path between the first terminal of the transistor and a second terminal of the transistor, Z1 is on the first connection path, the second terminal of the transistor is electrically connected to Y through at least a third connection path, the third connection path does not include the second connection path, and Z2 is on the third connection path." It is possible to use the expression "a first terminal of a transistor is electrically connected to X through Z1 on at least a first connection path, the first connection path does not include a second connection path, the second connection path includes a connection path through the transistor, a second terminal of the transistor is electrically connected to Y through Z2 on at least a third connection path, and the third connection path does not include the second connection path." It is also possible to use the expression "a first terminal of a transistor is electrically connected to X through Z1 on at least a first electrical path, the first electrical path does not include a second electrical path, the second electrical path is an electrical path from the first terminal of the transistor to a second terminal of the transistor, the second terminal of the transistor is electrically connected to Y through Z2 on at least a third electrical path, the third electrical path does not include a fourth electrical path, and the fourth electrical path is an

electrical path from the second terminal of the transistor to the first terminal of the transistor." When the connection path in a circuit configuration is defined by an expression similar to the above examples, a first terminal and a second terminal of a transistor can be distinguished from each other to specify the technical scope.

5 [0027]

Note that these expressions are examples and there is no limitation on the expressions. Here, X, Y, Z1, and Z2 each denote an object (e.g., a device, an element, a circuit, a wiring, an electrode, a terminal, a node, a conductive film, and a layer).

[0028]

10

Even when independent components are electrically connected to each other in a circuit diagram, one component has functions of a plurality of components in some cases. For example, when part of a wiring also functions as an electrode, one conductive film functions as the wiring and the electrode. Thus, "electrical connection" in this specification includes in its category such a case where one conductive film has functions of a plurality of components.

15 [0029]

Note that in this specification and the like, it might be possible for those skilled in the art to constitute one embodiment of the invention even when portions to which all the terminals of an active element (e.g., a transistor or a diode), a passive element (e.g., a capacitor or a resistor), or the like are connected are not specified. In other words, one embodiment of the invention can be clear even when connection portions are not specified. Further, in the case where a connection portion is disclosed in this specification and the like, it can be determined that one embodiment of the invention in which a connection portion is not specified is disclosed in this specification and the like, in some cases. In particular, in the case where the number of portions to which the terminal is connected might be plural, it is not necessary to specify the portions to which the terminal is connected. Therefore, it might be possible to constitute one embodiment of the invention by specifying only portions to which some of terminals of an active element (e.g., a transistor or a diode), a passive element (e.g., a capacitor or a resistor), or the like are connected.

[0030]

25

30

35

Note that in this specification and the like, it might be possible for those skilled in the art to specify the invention when at least a connection portion of a circuit is specified. Alternatively, it might be possible for those skilled in the art to specify the invention when at least a function of a circuit is specified. In other words, when a function is specified, an embodiment of the invention can be obvious. Further, it can be determined that one embodiment of the present invention whose function is specified is disclosed in this specification

and the like. Therefore, when a connection portion of a circuit is specified, the circuit is disclosed as one embodiment of the invention even when a function of the circuit is not specified, and one embodiment of the invention can be constituted. Alternatively, when a function of a circuit is specified, the circuit is disclosed as one embodiment of the invention even when a connection portion is not specified, and one embodiment of the invention can be constituted.

[0031]

Note that in this specification, the terms "film" and "layer" can be interchanged depending on the case or circumstances. For example, the term "conductive layer" can be changed into the term "conductive film", and the term "insulating film" can be changed into the term "insulating layer" in some cases.

[0032]

5

15

20

30

One embodiment of the present invention can provide a novel semiconductor device or a method for driving the same. Alternatively, one embodiment of the present invention can provide a semiconductor device with excellent controllability and a method for driving the same, a semiconductor device with a short starting time and a method for driving the same, or a programmable semiconductor device and a method for driving the same.

[0033]

Note that the description of the plurality of effects does not disturb the existence of other effects. In one embodiment of the present invention, there is no need to achieve all the effects described above. In one embodiment of the present invention, an object other than the above objects, an effect other than the above effects, and a novel feature will be apparent from the description of the specification and the drawings.

### BRIEF DESCRIPTION OF DRAWINGS

25 [0034]

In the accompanying drawings:

FIG. 1 is a block diagram showing a configuration example of a circuit;

FIG. 2 is a circuit diagram showing a configuration example of a circuit;

FIG. 3 is a block diagram showing a configuration example of a circuit;

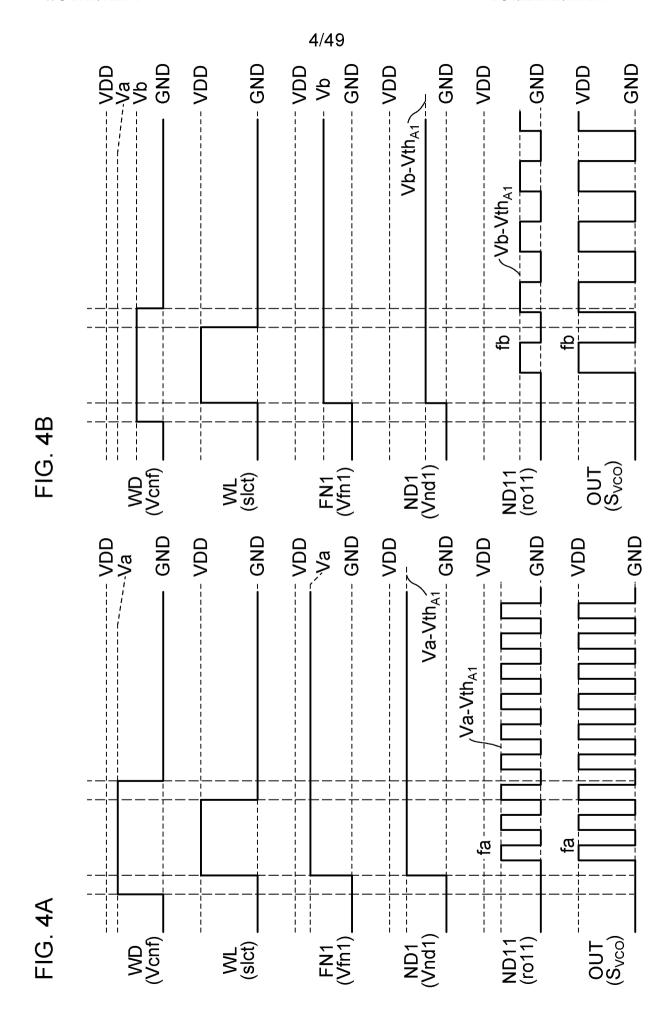

FIGS. 4A and 4B are timing charts showing operation examples of a circuit;

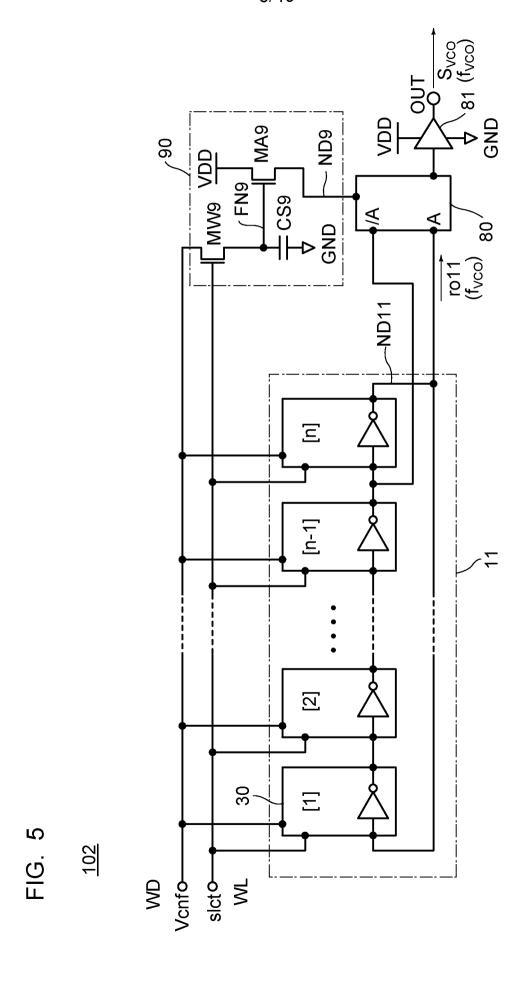

FIG. 5 is a block diagram showing a configuration example of a circuit;

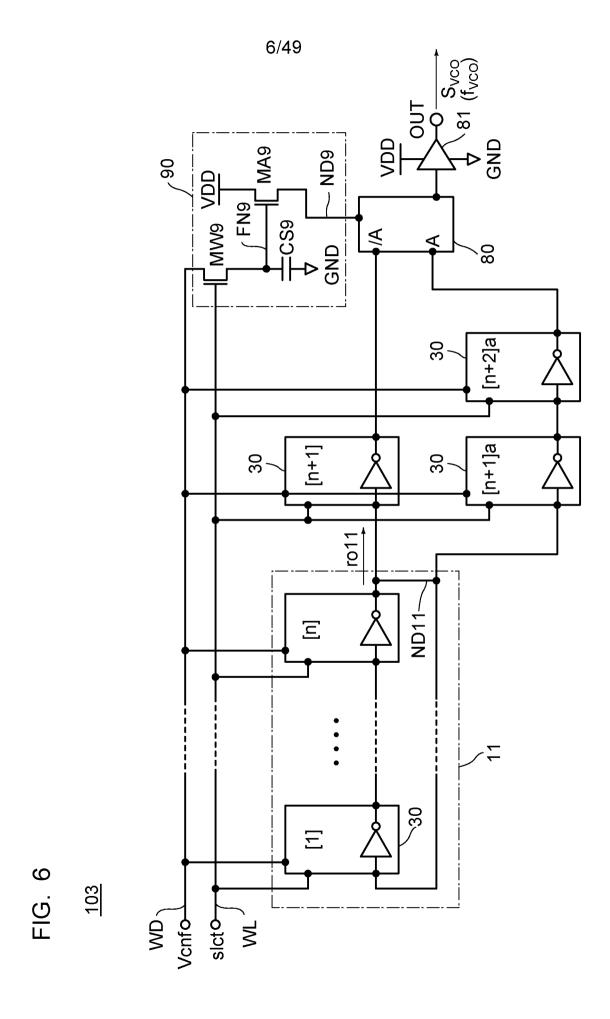

FIG. 6 is a block diagram showing a configuration example of a circuit;

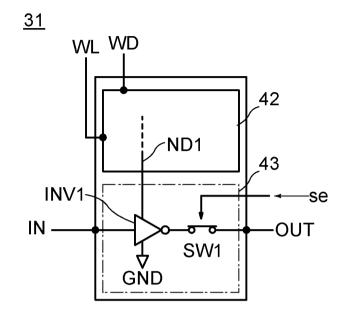

FIGS. 7A and 7B are a block diagram and a circuit diagram each showing a configuration example of a circuit;

FIGS. 8A and 8B are a block diagram and a circuit diagram each showing a

configuration example of a circuit;

- FIG. 9 is a timing chart showing an operation example of a circuit;

- FIG. 10 is a circuit diagram showing a configuration example of a circuit;

- FIG. 11 is a block diagram showing a configuration example of a circuit;

- FIG. 12 is a circuit diagram showing a configuration example of a circuit;

- FIG. 13 is a timing chart showing an operation example of a circuit;

- FIG. 14 is a circuit diagram showing a configuration example of a circuit;

- FIG. 15 is a block diagram showing a configuration example of a circuit;

- FIG. 16 is a block diagram showing a configuration example of a circuit;

- FIG. 17 is a block diagram showing a configuration example of a circuit;

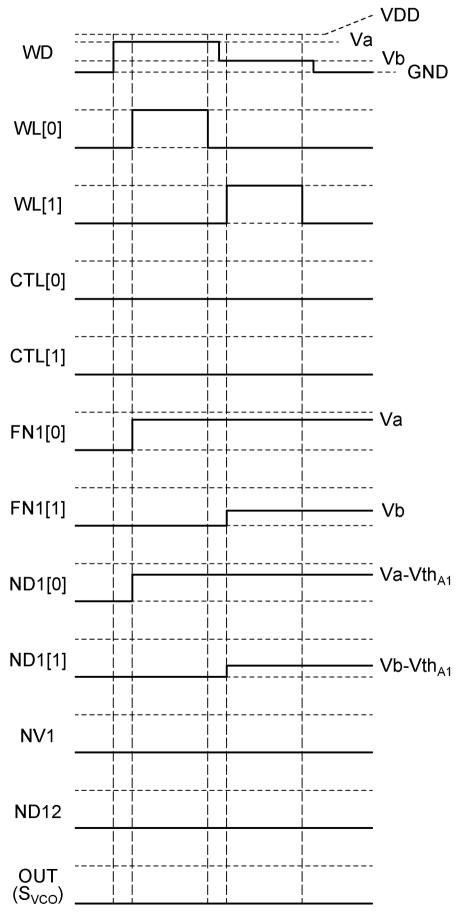

- FIG. 18 is a timing chart showing an operation example of a circuit;

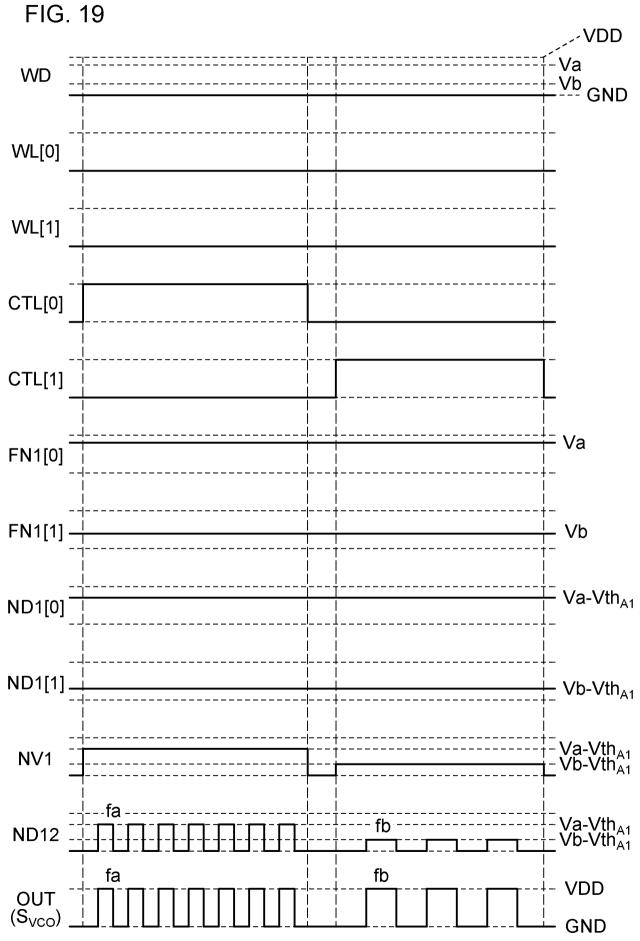

- FIG. 19 is a timing chart showing an operation example of a circuit;

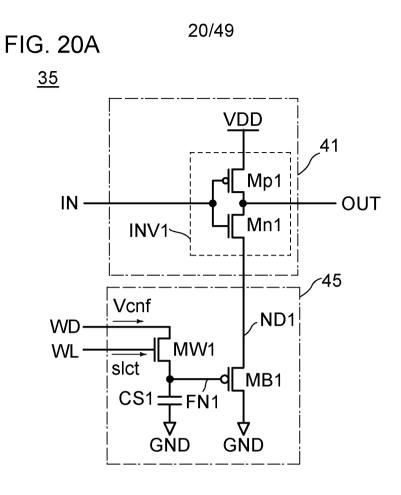

- FIGS. 20A to 20C are circuit diagrams each showing a configuration example of a circuit;

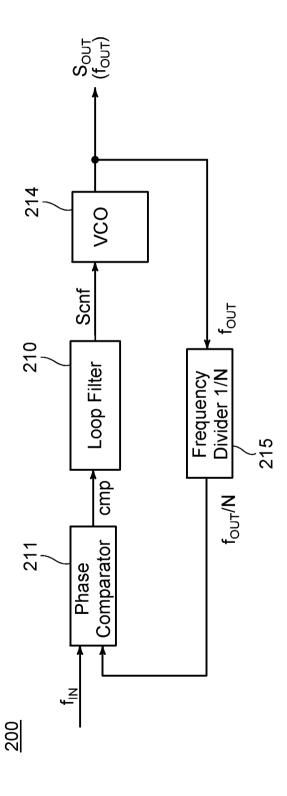

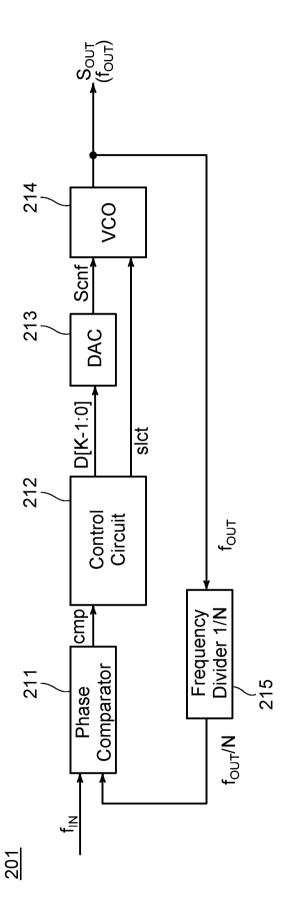

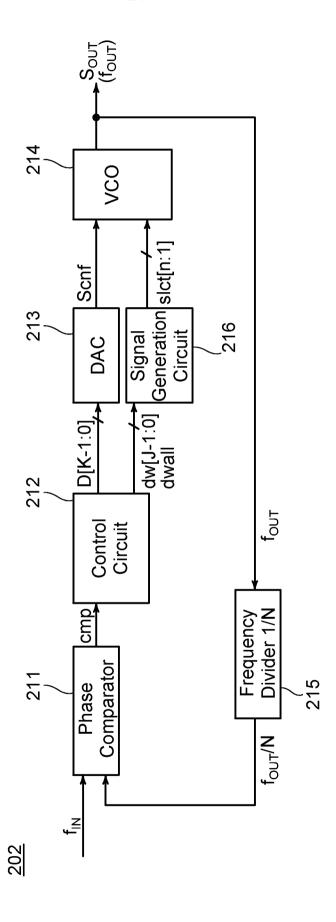

- FIG. 21 is a block diagram showing a configuration example of a PLL;

- FIG. 22 is a block diagram showing a configuration example of a PLL;

- FIG. 23 is a block diagram showing a configuration example of a PLL;

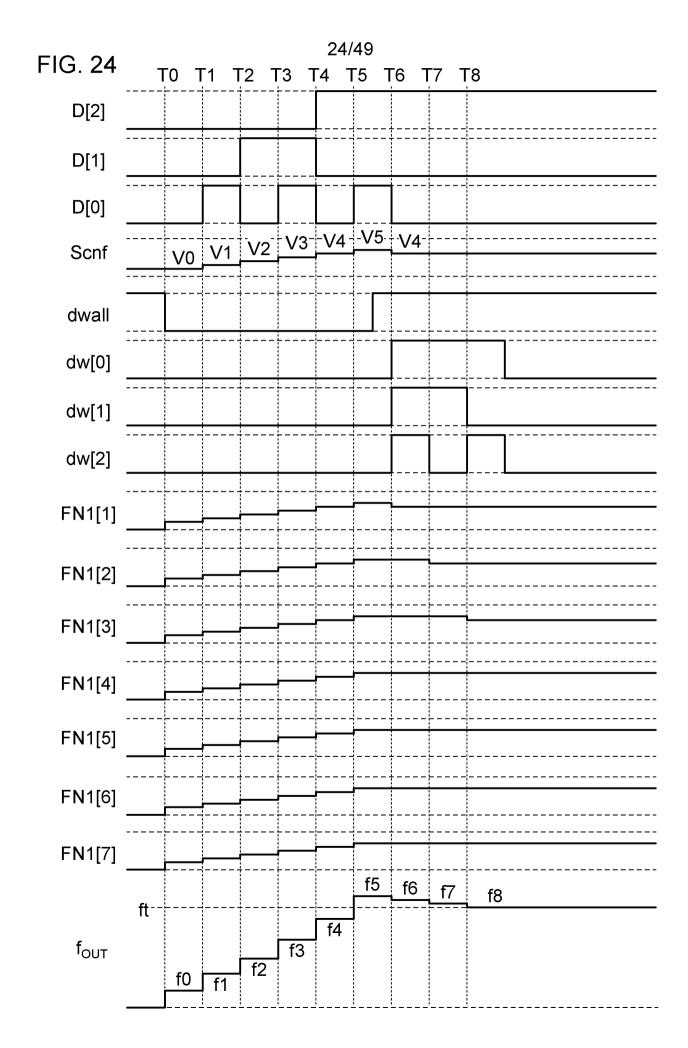

- FIG. 24 is a timing chart showing an operation example of a PLL;

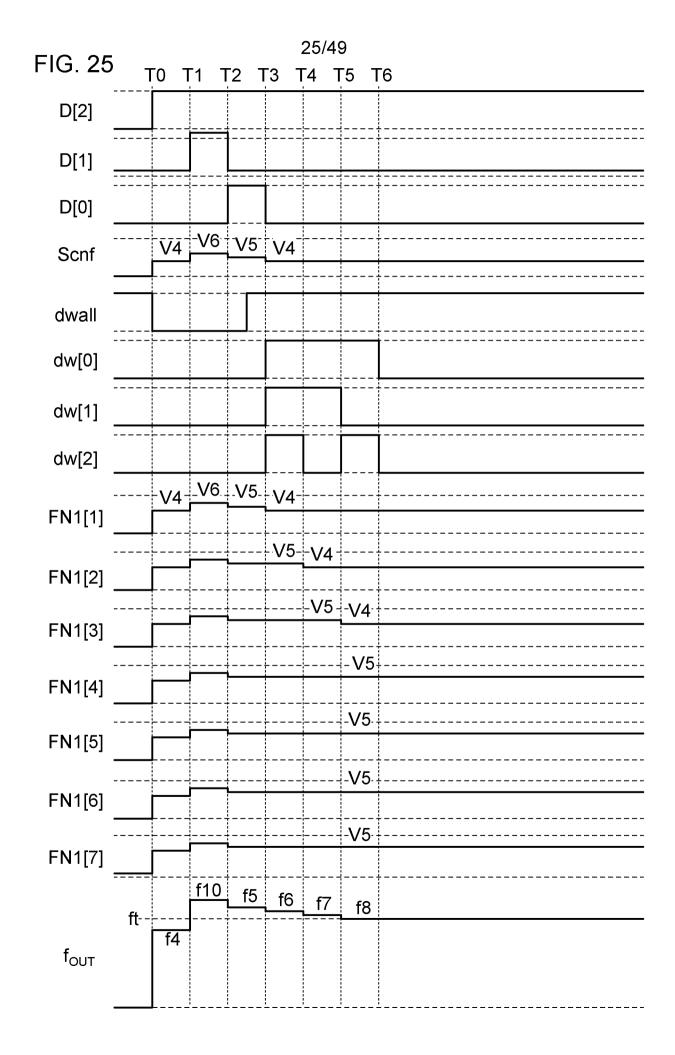

- FIG. 25 is a timing chart showing an operation example of a PLL;

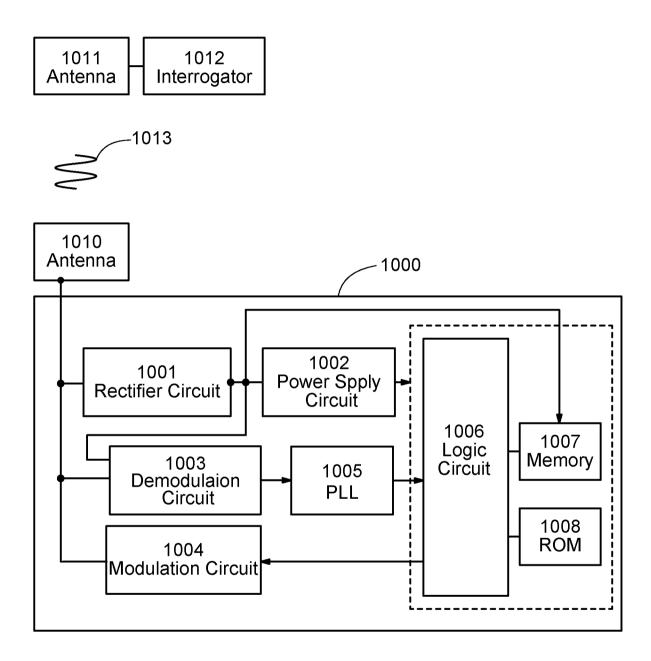

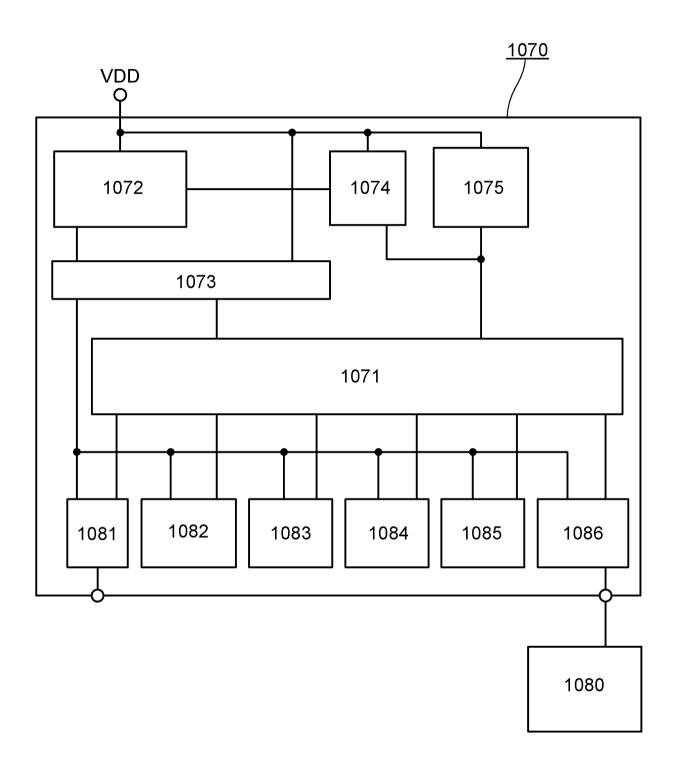

- FIG. 26 is a block diagram showing a configuration example of a processing unit (wireless IC);

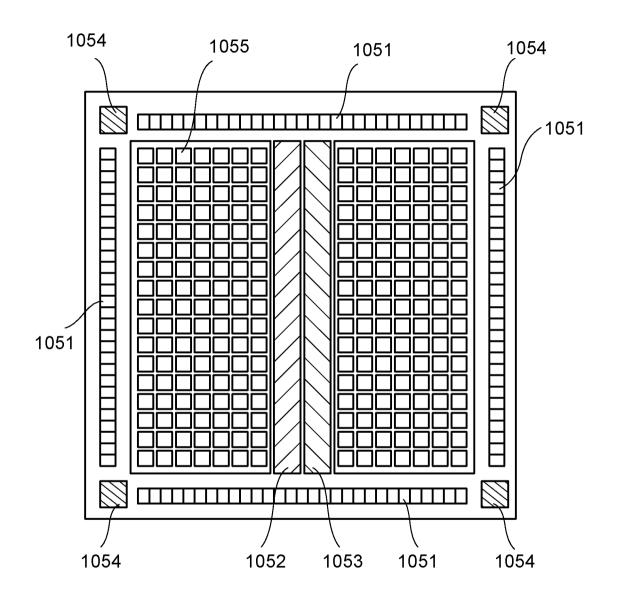

- FIGS. 27A to 27F illustrate usage examples of RFID tags;

- FIG. 28 is a schematic diagram showing a configuration example of a processing unit (PLD);

- FIG. 29 is a block diagram showing a configuration example of a processing unit (MCU);

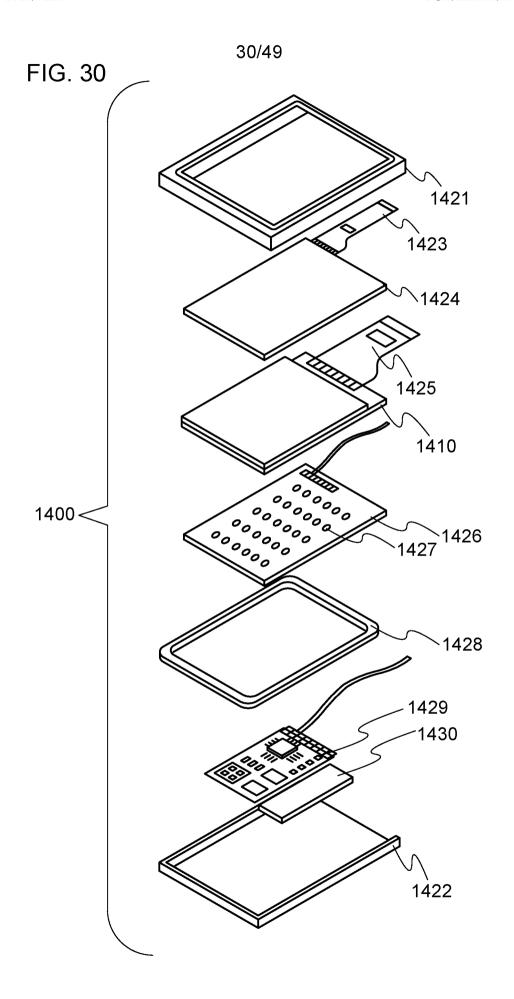

- FIG. 30 is a perspective exploded view showing an example of a display device;

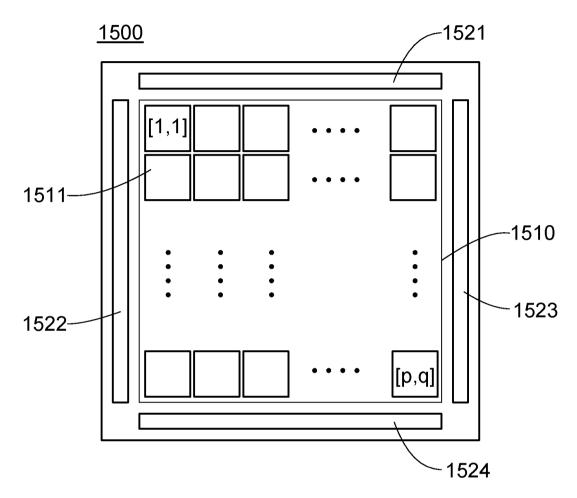

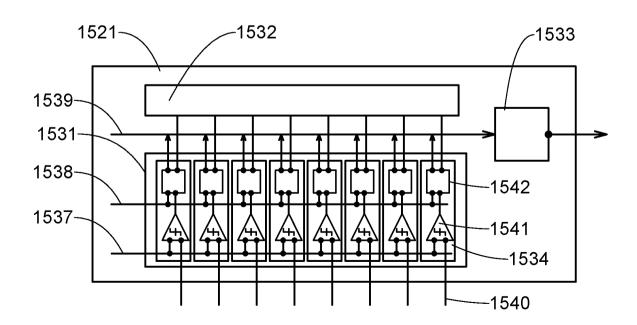

- FIGS. 31A and 31B are a block diagram showing a configuration example of an imaging device and a block diagram showing a configuration example of a driving circuit;

- FIGS. 32A to 32H show structure examples of electronic devices;

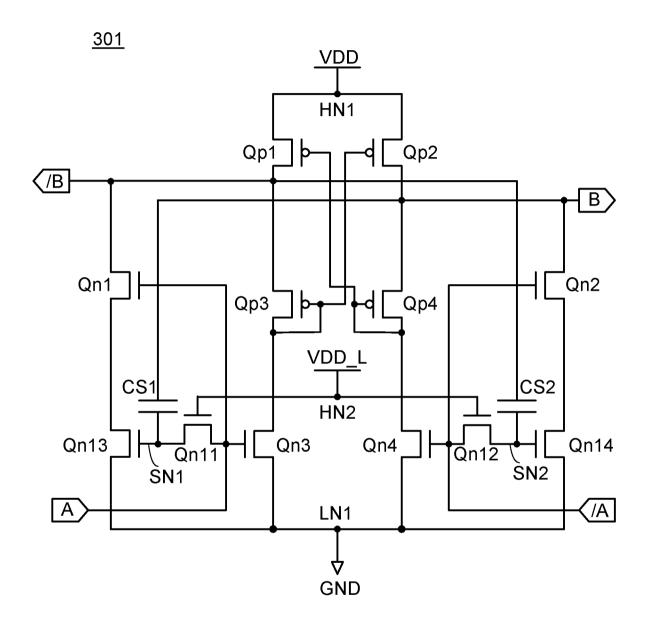

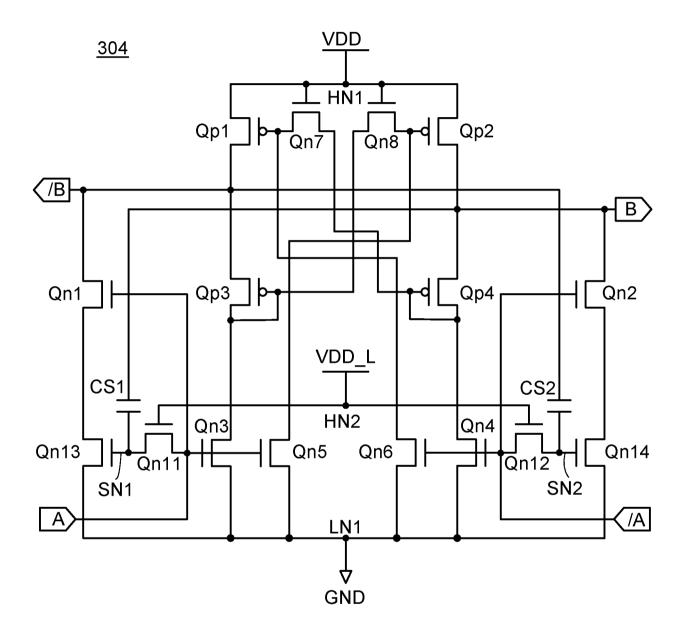

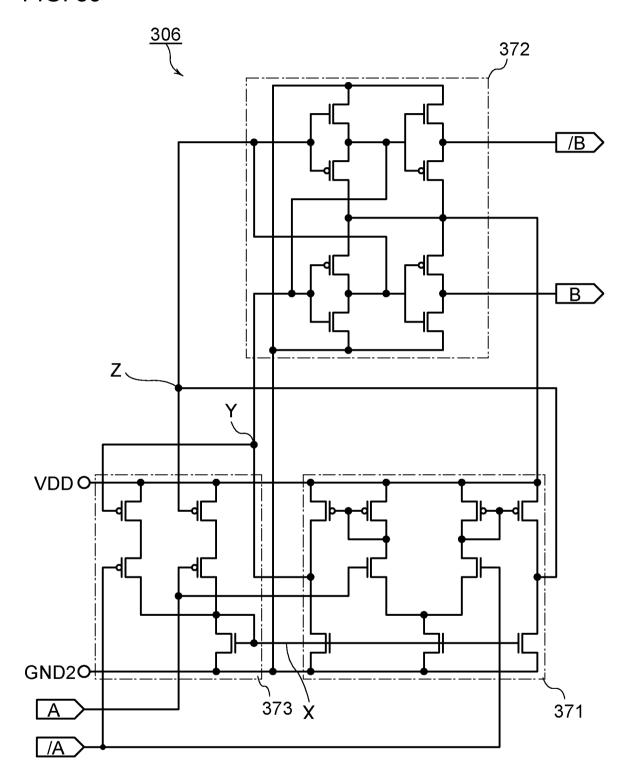

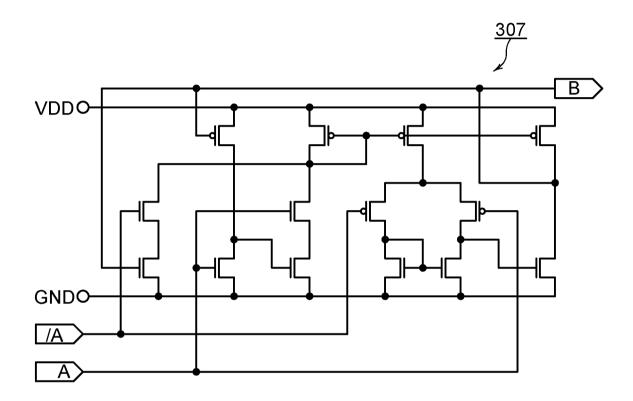

- FIG. 33 is a circuit diagram showing a configuration example of a level shift circuit;

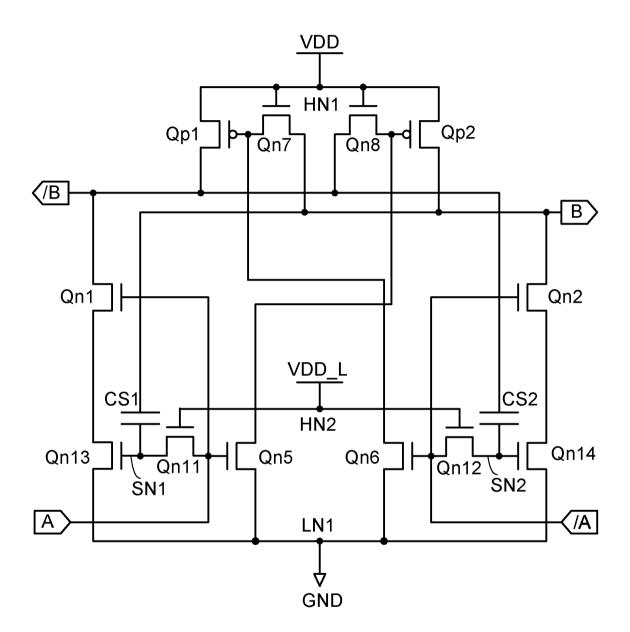

- FIG. 34 is a circuit diagram showing a configuration example of a level shift circuit;

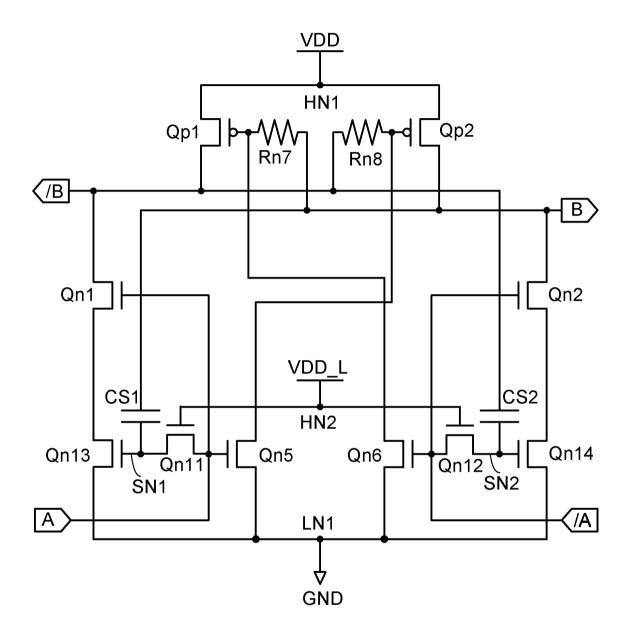

- FIG. 35 is a circuit diagram showing a configuration example of a level shift circuit;

- FIG. 36 is a circuit diagram showing a configuration example of a level shift circuit;

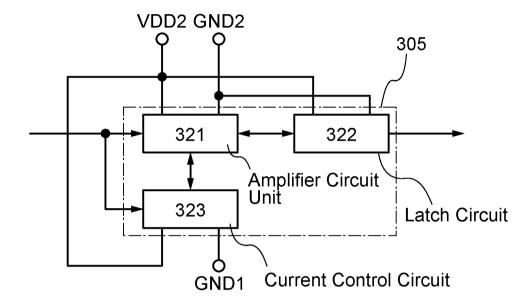

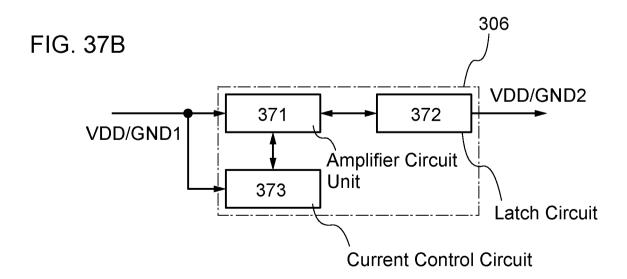

- FIGS. 37A and 37B are block diagrams each showing a configuration example of a level

shift circuit;

5

15

20

25

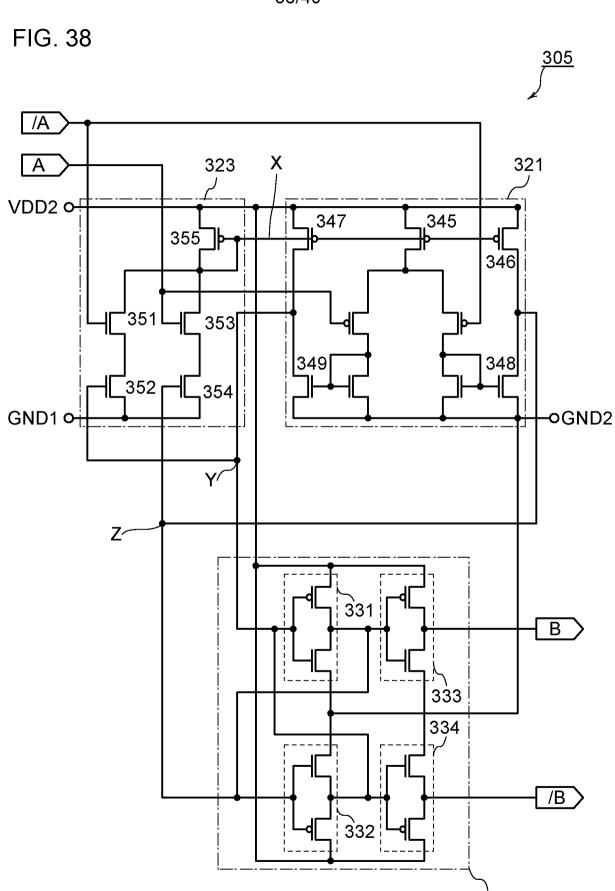

FIG. 38 is a circuit diagram showing a configuration example of a level shift circuit;

FIG. 39 is a circuit diagram showing a configuration example of a level shift circuit;

FIG. 40 is a circuit diagram showing a configuration example of a level shift circuit;

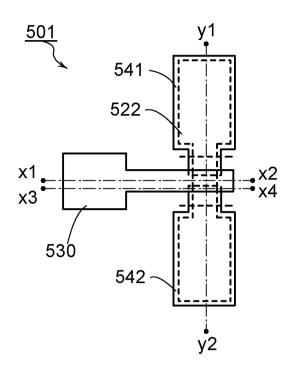

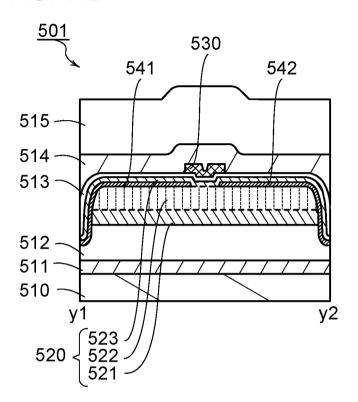

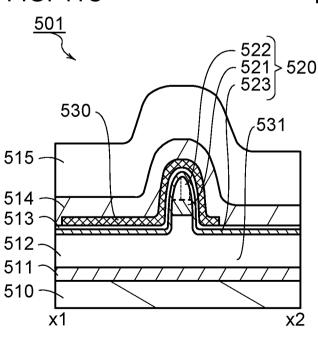

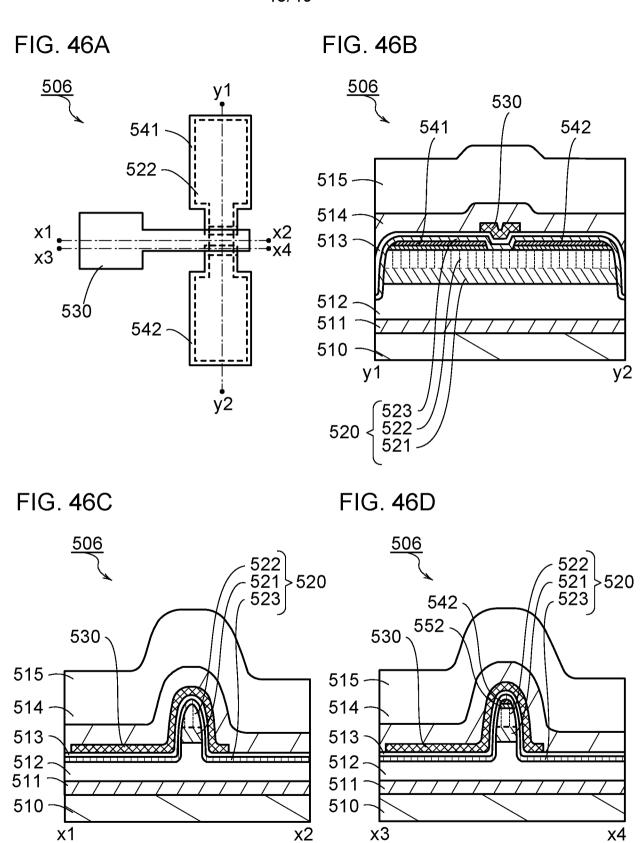

FIGS. 41A to 41D illustrate a structure example of an OS transistor: FIG. 41A is a top view; FIG. 41B is a cross-sectional view taken along line y1–y2; FIG. 41C is a cross-sectional view taken along line x1–x2; and FIG. 41D is a cross-sectional view taken along line x3–x4;

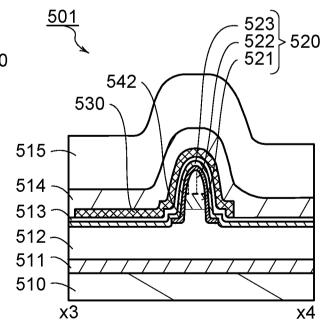

FIGS. 42A to 42D illustrate a structure example of an OS transistor: FIG. 42A is a top view; FIG. 42B is a cross-sectional view taken along line y1–y2; FIG. 42C is a cross-sectional view taken along line x1–x2; and FIG. 42D is a cross-sectional view taken along line x3–x4;

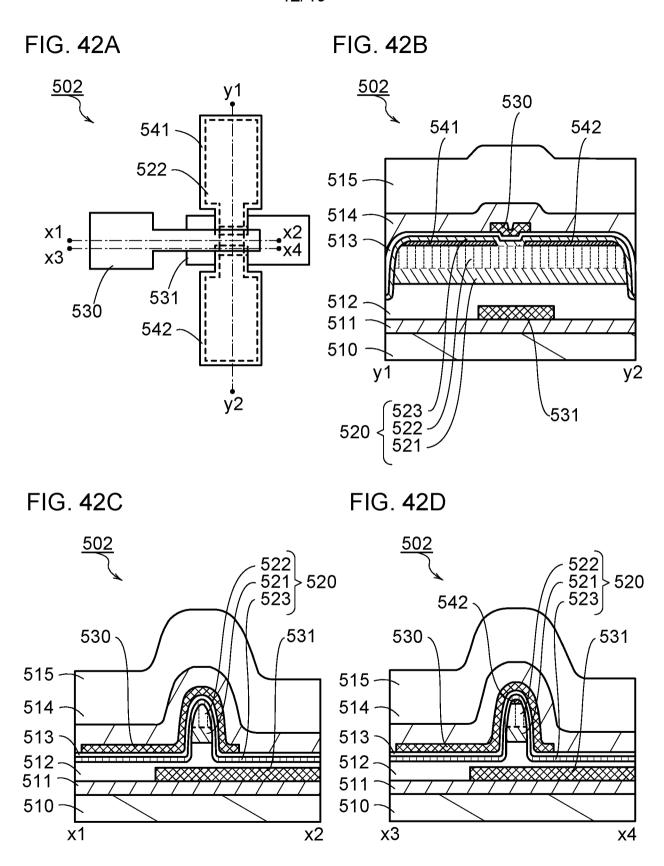

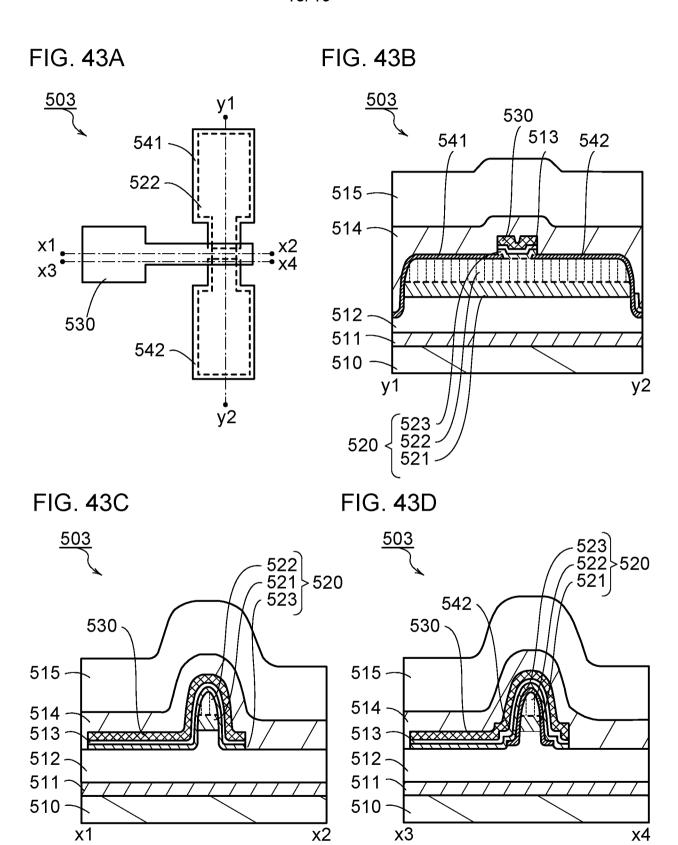

FIGS. 43A to 43D illustrate a structure example of an OS transistor: FIG. 43A is a top view; FIG. 43B is a cross-sectional view taken along line y1–y2; FIG. 43C is a cross-sectional view taken along line x1–x2; and FIG. 43D is a cross-sectional view taken along line x3–x4;

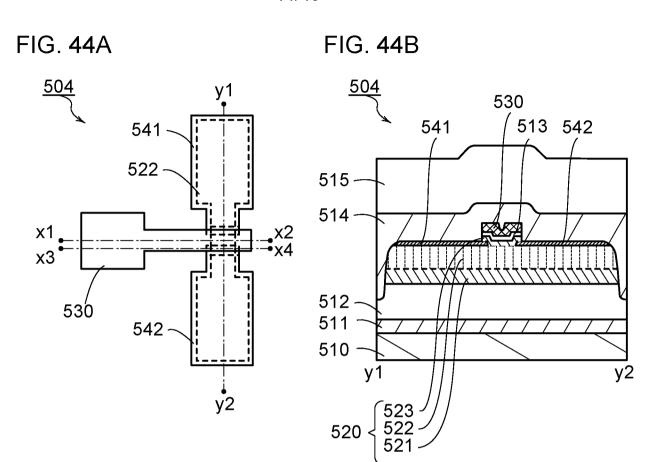

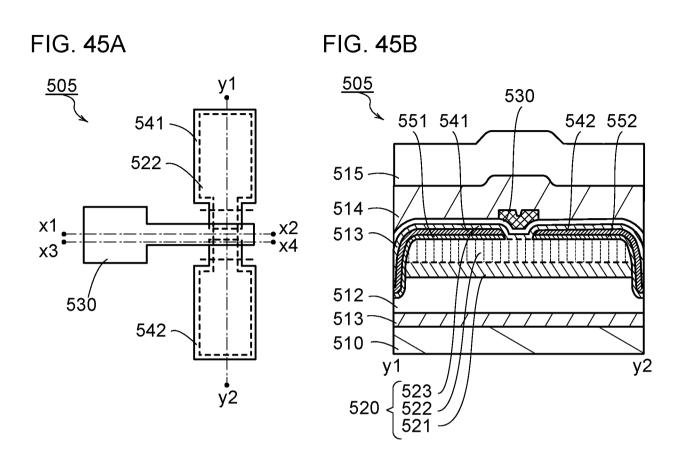

FIGS. 44A to 44D illustrate a structure example of an OS transistor: FIG. 44A is a top view; FIG. 44B is a cross-sectional view taken along line y1–y2; FIG. 44C is a cross-sectional view taken along line x1–x2; and FIG. 44D is a cross-sectional view taken along line x3–x4;

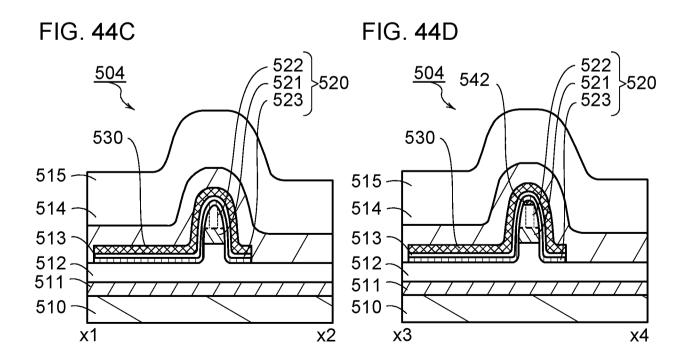

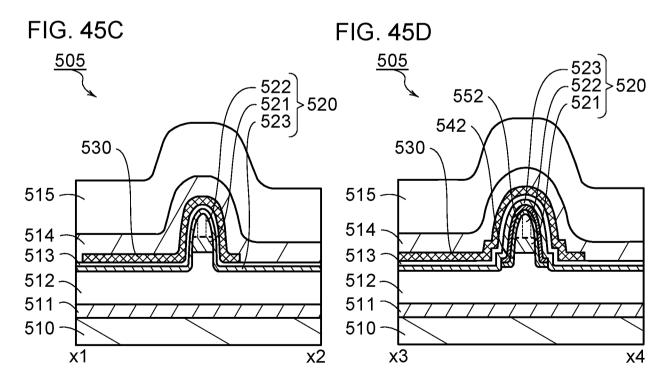

FIGS. 45A to 45D illustrate a structure example of an OS transistor: FIG. 45A is a top view; FIG. 45B is a cross-sectional view taken along line y1–y2; FIG. 45C is a cross-sectional view taken along line x1–x2; and FIG. 45D is a cross-sectional view taken along line x3–x4;

FIGS. 46A to 46D illustrate a structure example of an OS transistor: FIG. 46A is a top view; FIG. 46B is a cross-sectional view taken along line y1–y2; FIG. 46C is a cross-sectional view taken along line x1–x2; and FIG. 46D is a cross-sectional view taken along line x3–x4;

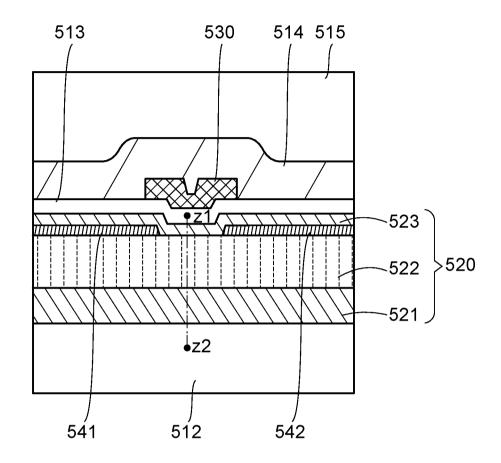

FIG. 47A is an enlarged view of a portion in FIG. 41B and FIG. 47B is an energy band diagram of an OS transistor;

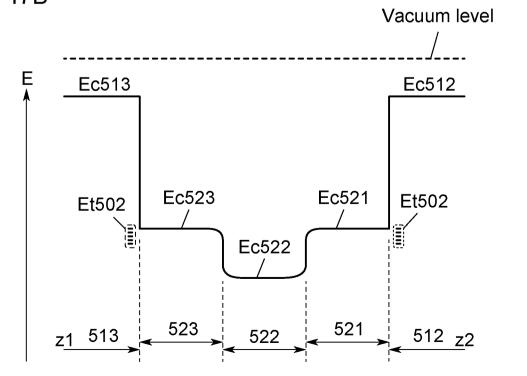

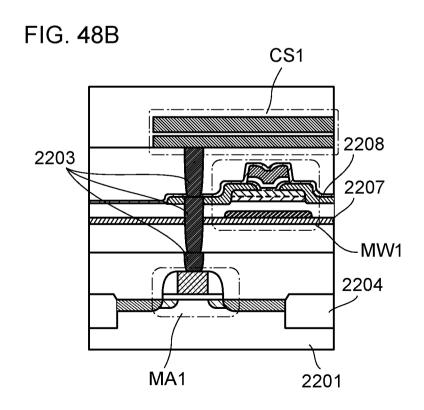

FIGS. 48A and 48B are cross-sectional views each showing a structure example of a semiconductor device; and

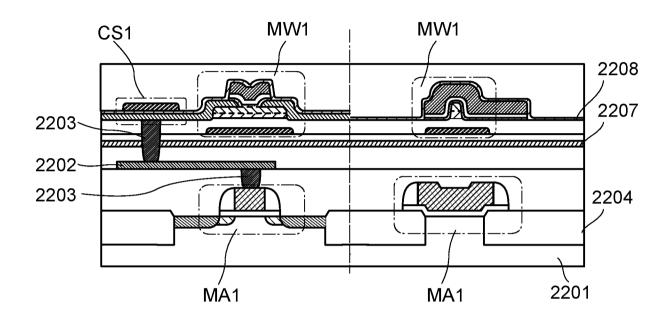

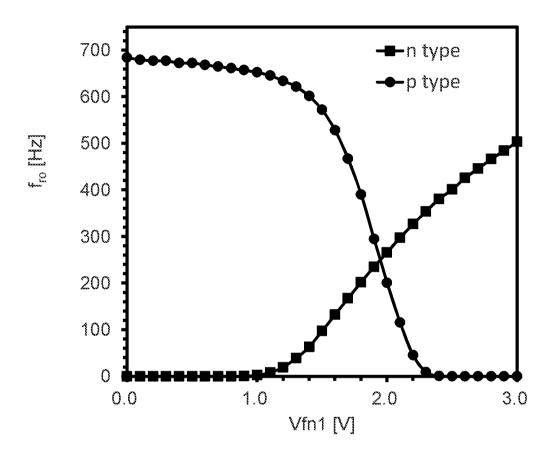

FIG. 49 is a graph showing a change in oscillation frequency calculated by simulation with respect to a holding potential of a ring oscillator circuit.

# 30 BEST MODE FOR CARRYING OUT THE INVENTION [0035]

Hereinafter, an embodiment and examples of the present invention will be described. Note that the present invention is not limited to the following description. It will be readily appreciated by those skilled in the art that modes and details of the present invention can be

modified in various ways without departing from the spirit and scope of the present invention. The present invention therefore should not be construed as being limited to the following description of the embodiments and example.

[0036]

5

10

In the drawings, the same components, components having similar functions, components formed of the same material, or components formed at the same time are denoted by the same reference numerals in some cases, and description thereof is not repeated in some cases. [0037]

When the same reference numerals are used for a plurality of elements and those elements need to be distinguished from each other, "\_1", "\_2", "[n]", "[m, n]", or the like may be added to the reference numerals. For example, in the case where a plurality of wirings WLW in a memory cell array are individually distinguished from one another, the wiring WLW in the second row is described using an address number (row number) of the memory cell array, as a wiring WLW[2] in some cases.

15 [0038]

In this specification, for example, a high power supply potential VDD is abbreviated to a "potential VDD", a "VDD", or the like in some cases. The same applies to other components (e.g., a signal, a voltage, a potential, a circuit, an element, an electrode, and a wiring).

[0039]

Embodiments and an example are described below. Any of the embodiments and the example can be combined as appropriate. In addition, in the case where some structure examples are given in one embodiment or example, any of the structure examples can be combined as appropriate.

[0040]

## 25 (Embodiment 1)

An oscillator circuit is described as an example of a semiconductor device. The oscillator circuit is a device which has a function of generating an AC signal in which current or voltage changes.

[0041]

35

30 ((Configuration Example 1 of Oscillator Circuit))

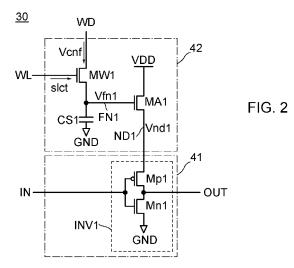

FIG. 1 is a block diagram showing a configuration example of an oscillator circuit. A circuit 101 in FIG. 1 includes (n+1) circuits 30 (n) is an odd number), a circuit 80, a buffer circuit 81, and a circuit 90. The (n+1) circuits 30 and the circuit 90 are each electrically connected to a wiring WD and a wiring WL. A potential Vcnf is input to the wiring WD, and a signal slct is input to the wiring WL. The potential Vcnf is an analog potential, and the oscillation frequency

$f_{VCO}$  of an output signal  $S_{VCO}$  of the circuit 101 can be changed by the potential Vcnf. [0042]

A VDD is a high power supply potential of the circuit 30 and a GND is a low power supply potential of the circuit 30. Note that in general, a potential (a voltage) is relative and is determined depending on the amount relative to a certain potential. Thus, "ground" and "GND" are each a potential lower than the VDD; for example, they may be a ground potential or 0 V, and are not necessarily 0 V. For example, the "ground potential" or "GND" may be defined using the lowest potential in a circuit as a reference. Alternatively, the "ground potential" or "GND" may be defined using an intermediate potential in a circuit as a reference. In those cases, a positive potential and a negative potential are set using the potential as a reference. 101 is electrically connected to a power supply line that supplies the VDD and a power supply line that supplies the GND.

[0043]

15

20

25

30

5

An output terminal of the circuit 30 is connected to an input terminal of the circuit 30 in a next stage. An output terminal of the circuit 30 in an *n*-th stage is electrically connected to an input terminal of the circuit 30 in a first stage and an input terminal of the circuit 30 in an The circuit 30 includes a circuit 41. The circuit 41 has functions of transmitting an input signal from an input terminal of the circuit 30 to an output terminal of the circuit 30 and inverting the potential level of the input signal. In a signal transmission path of the circuit 41, an inverter (NOT gate circuit) is provided.

[0044]

Hereinafter, the circuit 30 in the first stage is referred to as a circuit 30[1] in some cases, and the same applies to the circuits 30 in other stages and other components. [0045]

A circuit 11 includes n circuits 30 that are electrically connected in a ring shape, and can operate as a ring oscillator circuit. A node ND 11 is an output node of the circuit 11. [0046]

The circuit 80 has a function of changing the potential level of an input signal of an input terminal A. The circuit 80 can be a level shift circuit, for example. A signal whose potential level is reverse to that of the input signal of the terminal A is input to a terminal/A. In the circuit 101, the circuit 80 can perform level shift operation in which respective amplitudes of the input signals of the input terminal A and the terminal/A are increased. Furthermore, in an example in FIG. 1, a signal that is obtained by level-shifting the input signal of the input terminal A is output from an output terminal of the circuit 80. The circuit 30[n+1] is provided so as to

35 generate an inversion signal rob11 of a signal ro11.

[0047]

The circuit 90 has a function of generating a power supply potential of the circuit 80. [0048]

The buffer circuit 81 has a function of amplifying an output current of the circuit 80.

The buffer circuit 81 is provided as appropriate.

[0049]

[Circuit 30]

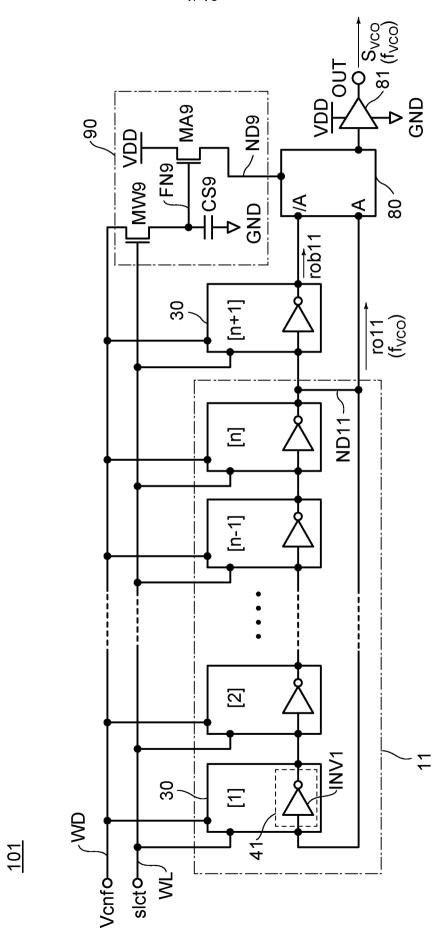

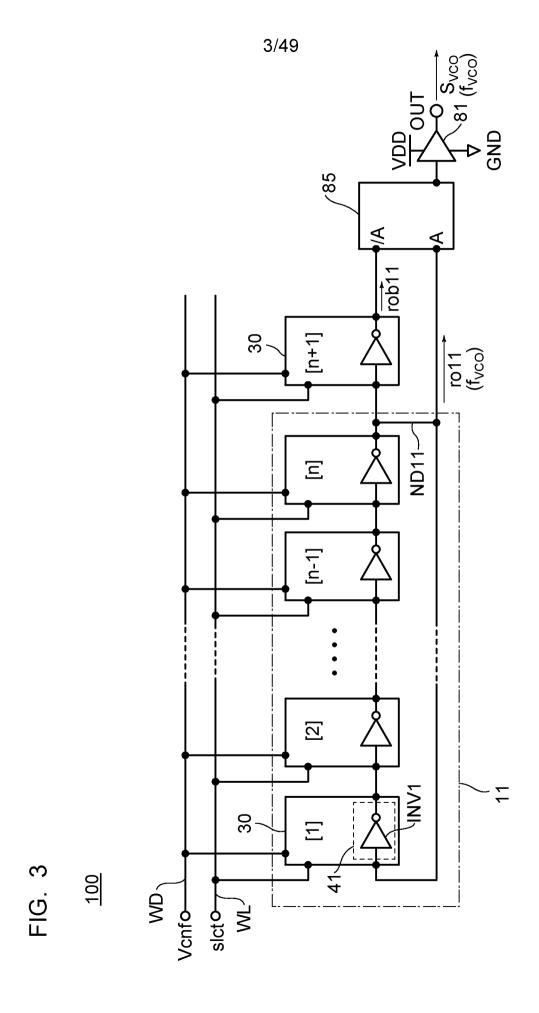

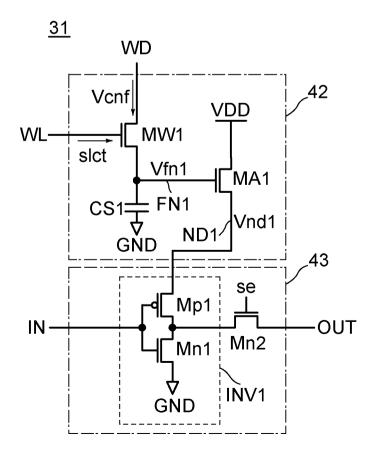

FIG. 2 is a circuit diagram illustrating a configuration example of the circuit 30. The circuit 30 includes the circuit 41 and a circuit 42.

10 [0050]

The circuit 41 includes an inverter INV1. Here, the INV1 is a CMOS inverter including a transistor Mp1 and a transistor Mn1. The INV1 can be formed only including n-channel transistors or p-channel transistors. A source of the transistor Mn1 can function as a node to which a low power supply potential is supplied. Here, the source of the transistor Mn1 is electrically connected to a power supply line to which a GND is supplied. A source of the transistor Mp1 can function as a node to which a high power supply potential is supplied. Here, the source of the transistor Mn1 is electrically connected to a node ND1 of the circuit 42. An output node of the INV1 is electrically connected to an input node of the INV1 of the circuit 30 in the next stage.

20 [0051]

15

The circuit 42 has a function of controlling the high power supply potential of the INV1. The circuit 42 includes a transistor MW1, a transistor MA1, and a capacitor CS1. A VDD is input to a drain of the transistor MA1. The drain of the transistor MA1 is electrically connected to the source of the transistor Mp1. The source of the transistor MA1 is referred to as the node ND1. The node ND1 can function as an output node of the circuit 42. A potential Vnd1 of the node ND1 is supplied to the INV1 as a high power supply potential. A gate of the transistor MA1 is electrically connected to a node FN1. A gate voltage of the transistor MA1 can be changed by a potential Vfn1 of the node FN1, so that the potential Vnd1 can be changed by the potential Vfn1. As described below, the output potential Vnd1 of the circuit 42 can be changed by the potential Vcnf.

[0052]

35

In the circuit 42, a circuit block including the transistor MW1, the capacitor CS1, and the node FN1 has a function of holding an analog potential corresponding to the potential Vcnf. The node FN1 is a data holding portion in which the analog potential can be held. The capacitor CS1 can function as a storage capacitor that holds the potential Vfn1 of the node FN1.

The transistor MW1 can function as a writing transistor. A gate of the transistor MW1 is electrically connected to the wiring WL, and the conduction state thereod is controlled by the signal *slct*.

[0053]

5

20

25

30

35

When the transistor MW1 is turned on, a potential corresponding to the potential Vcnf is written to the node FN1. That is, the potential Vfn1 is also an analog potential. Then, when the transistor MW1 is turned off, the node FN1 is electrically floating and the circuit 42 is in a state of holding the potential Vfn1. In order to suppress a change in the potential Vfn1, it is preferable that the transistor MW1 have an extremely low off-state current. In other words, it is preferable that the off-state resistance of the transistor MW1 be high.

[0054]

Extremely low off-state current means that off-state current per micrometer of the channel width is lower than or equal to 100 zA (z represents zepto and denotes a factor of  $10^{-21}$ ). Since the off-state current is preferably as low as possible, the normalized off-state current is preferably lower than or equal to  $10 \text{ zA/}\mu\text{m}$  or lower than or equal to  $1 \text{ zA/}\mu\text{m}$ ), more preferably lower than or equal to  $10 \text{ yA/}\mu\text{m}$  (y represents yocto and denotes a factor of  $10^{-24}$ ). [0055]

In order to make the off-state current of the transistor extremely low, a channel of the transistor is formed in a semiconductor whose bandgap is wide, for example, a semiconductor whose band gap is greater than or equal to 3.0 eV. As an example of such a semiconductor, an oxide semiconductor containing a metal oxide can be given. A transistor including an oxide semiconductor in its channel (hereinafter also referred to as an OS transistor) has low leakage current due to thermal excitation and extremely low off-state current.

An oxide semiconductor of an OS transistor preferably contains at least one of indium (In) and zinc (Zn). Typical examples of the oxide semiconductor of the OS transistor include In-Ga-Zn oxide and In-Sn-Zn oxide. By reducing impurities serving as electron donors, such as moisture or hydrogen, and also reducing oxygen vacancies, an i-type (intrinsic) or a substantially i-type oxide semiconductor can be obtained. Here, such an oxide semiconductor is referred to as a highly purified oxide semiconductor. By forming the channel using a highly purified oxide semiconductor, the off-state current of the OS transistor that is normalized by channel width can be as low as several yoctoamperes per micrometer to several zeptoamperes per micrometer. Note that the oxide semiconductor and the OS transistor are described in detail in Embodiment 4. [0057]

Unless otherwise specified, the off-state current in this specification refers to a drain

current of a transistor in the off state (also referred to as non-conduction state and cutoff state). Unless otherwise specified, the off state of an n-channel transistor means that a potential difference (Vgs) between its gate and source is lower than the threshold voltage (Vth), and the off state of a p-channel transistor means that Vgs is higher than Vth. For example, the off-state current of an n-channel transistor sometimes refers to a drain current that flows when the gate-source voltage Vgs is lower than the threshold voltage Vth.

[0058]

5

10

15

20

25

30

The off-state current of a transistor depends on Vgs in some cases. Thus, "the off-state current of a transistor is smaller than or equal to I" means "there is Vgs with which the off-state current of a transistor becomes smaller than or equal to I' in some cases. Furthermore, "the off-state current of a transistor" means "the off-state current in an off state at predetermined Vgs", "the off-state current in an off state at Vgs in a predetermined range", "the off-state current in an off state at Vgs with which sufficiently reduced off-state current is obtained", or the like. [0059]

As an example, the assumption is made of an n-channel transistor where the threshold voltage Vth is 0.5 V and the drain current is  $1 \times 10^{-9}$  A at Vgs of 0.5 V,  $1 \times 10^{-13}$  A at Vgs of 0.1 V,  $1 \times 10^{-19}$  A at Vgs of -0.5 V, and  $1 \times 10^{-22}$  A at Vgs of -0.8 V. The drain current of the transistor is  $1 \times 10^{-19}$  A or lower at Vgs of -0.5 V or at Vgs in the range of -0.8 V to -0.5 V; therefore, it can be said that the off-state current of the transistor is  $1 \times 10^{-19}$  A or lower. Since there is Vgs at which the drain current of the transistor is  $1 \times 10^{-22}$  A or lower, it may be said that the off-state current of the transistor is  $1 \times 10^{-22}$  A or lower. [0060]

In this specification, the off-state current of a transistor with a channel width W is sometimes represented by a current value for the channel width W or by a current value per given channel width (e.g., 1 µm). In the latter case, the unit of off-state current may be represented by current per length (e.g., A/µm).

[0061]

The off-state current of a transistor depends on temperature in some cases. Unless otherwise specified, the off-state current in this specification may be an off-state current at room temperature, 60 °C, 85 °C, 95 °C, or 125 °C. Alternatively, the off-state current may be an off-state current at a temperature at which the reliability required of a semiconductor device or the like including the transistor is ensured or a temperature at which the semiconductor device or the like including the transistor is used (e.g., temperature in the range of 5 °C to 35 °C). The description "an off-state current of a transistor is lower than or equal to I" may mean that there is

Vgs at which the off-state current of a transistor is lower than or equal to I at room temperature, 60 °C, 85 °C, 95 °C, 125 °C, a temperature at which the reliability required of a semiconductor device or the like including the transistor is ensured, or a temperature at which the semiconductor device or the like including the transistor is used (e.g., temperature in the range of 5 °C to 35 °C).

[0062]

5

15

The off-state current of a transistor depends on a voltage *V* ds between its drain and source in some cases. Unless otherwise specified, the off-state current in this specification may be an off-state current at *V* ds of 0.1 V, 0.8 V, 1 V, 1.2 V, 1.8 V, 2.5 V, 3 V, 3.3 V, 10 V, 12 V, 16 V, or 20 V. Alternatively, the off-state current might be an off-state current at *V* ds at which the reliability of a semiconductor device or the like including the transistor is ensured or at *V* ds at which the semiconductor device or the like including the transistor is used. The description "an off-state current of a transistor is lower than or equal to *I*" may mean that there is *V* gs at which the off-state current of a transistor is lower than or equal to *I* at *V* ds of 0.1 V, 0.8 V, 1 V, 1.2 V, 1.8 V, 2.5 V, 3 V, 3.3 V, 10 V, 12 V, 16 V, or 20 V, at *V* ds at which the reliability of a semiconductor device or the like including the transistor is ensured, or at *V* ds at which in the semiconductor device or the like including the transistor is used.

In the above description of an off-state current, a drain may be replaced with a source.

That is, the off-state current sometimes refers to a current that flows through a source of a transistor in the off state.

[0064]

In this specification, the term "leakage current" sometimes expresses the same meaning as an off-state current.

25 [0065]

In this specification, the off-state current sometimes refers to a current that flows between a source and a drain when a transistor is off, for example.

[0066]

The threshold voltage of the transistor MA1 is denoted by Vth<sub>A1</sub>. The VDD is input to the drain of the transistor MA1, and the source of the transistor MA1 corresponds to the output node ND1. Thus, the transistor MA1 can perform source follower operation in which the output potential Vnd1 (source potential) follows the input potential (Vfn1). When VDD> (Vfn1-Vth<sub>A1</sub>), the maximum value of the potential Vnd1 is (Vfn1-Vth<sub>A1</sub>). That is, the output potential Vnd1 in the circuit 42 can be controlled by the potential Vcnf. Thus, the delay time of the INV1 can be controlled by the potential Vnd1 of the node ND1. Furthermore, the amplitude

of an output signal of the INV1 is changed by the potential Vnd1. As the Vnd1 is increased, the delay time of the INV1 is shortened; thus, the oscillation frequency  $f_{VCO}$  of the output signal ro11 of the circuit 11 is increased, and the amplitude of the output signal ro11 is increased. The Vnd1 is controlled by the potential Vcnf that is input to the wiring WD. Therefore, the delay time and the amplitude of the output signal ro11 of the circuit 11 can be changed by the potential Vcnf.

[0067]

When the potential of the input terminal of the INV1 is the GND, the transistor Mp1 is turned on and the potential Vnd1 of the node ND1 is decreased. Because the node FN1 and the node ND1 are capacitively coupled by the gate capacitance of the transistor MA1, the Vfn1 is decreased when the Vnd1 is decreased. To suppress the change in the Vfn1 due to the decrease in the Vnd1, the capacitance of the capacitor CS1 is desirably larger than the gate capacitance of the transistor MA1. When the Vnd1 is decreased, the potential between the gate and the source of the transistor MA1 is increased, and the transistor MA1 is turned on. Thus, the node ND1 is immediately charged by the VDD, leading to an increase in the Vnd1.

[0068]

15

20

25

As described above, it is possible to change the oscillation frequency  $f_{VCO}$  of the output signal ro11 of the circuit 11 in response to the change in the Vfn1; however, the amplitude of the output signal ro11 is also changed. Thus, in order to make the amplitude of the signal  $S_{VCO}$  constant regardless of the Vfn1, it is effective to provide the circuit 80 at an output stage of the circuit 101.

[0069]

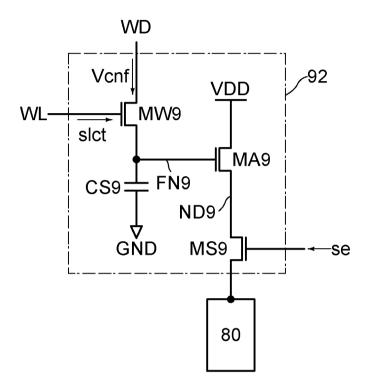

The circuit 90 is provided so as to supply a potential that is at the same level as the potential Vnd1 of the node ND1 of the circuit 30[n] to the circuit 80. The circuit 90 includes a transistor MW9, a transistor MA9, a capacitor CS9, and a node FN9. The configuration and the operation of the circuit 90 are similar to those of the circuit 42; thus, the description of the circuit 42 is referred to.

[0070]

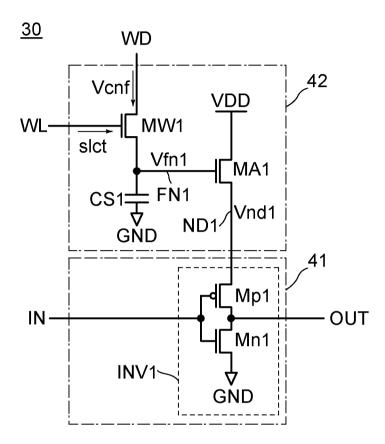

The circuit 90 is not necessarily provided depending on the circuit configuration of the circuit 80. FIG. 3 shows a configuration example of such an oscillator circuit. A circuit 100 in FIG. 3 is a modification example of the circuit 101, and a circuit 85 is provided instead of the circuit 80 and the circuit 90. The circuit 85 has a function similar to that of the circuit 80. The circuit 85 can perform level shift operation in which the amplitudes of input signals of a terminal A and a terminal/A are increased. In the example in FIG. 3, a signal obtained by level-shifting the input signal of the input terminal A is output from an output terminal of the circuit 85. The

circuit 85 is a circuit that can perform level shift operation even when a potential that is at the same level as the potential of the node ND1 of the circuit 30[n] is not supplied. Configuration examples of the circuit 80 and the circuit 85 are described in Embodiment 3. [0071]

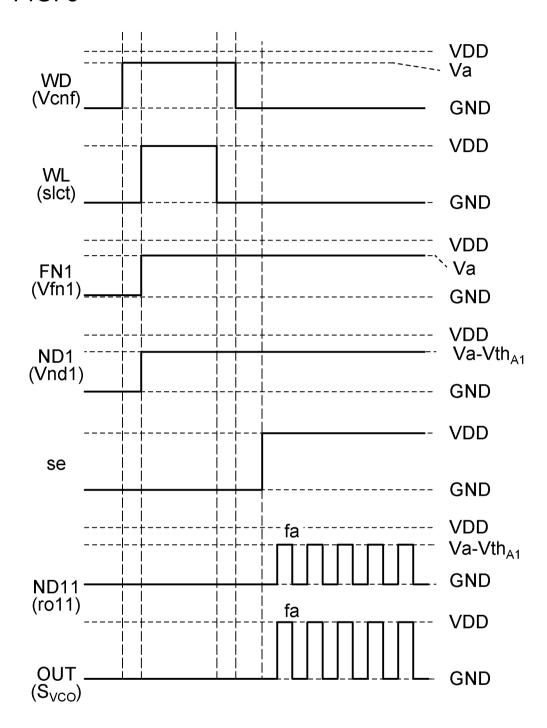

5 ((Operation Example 1 of Oscillator Circuit))

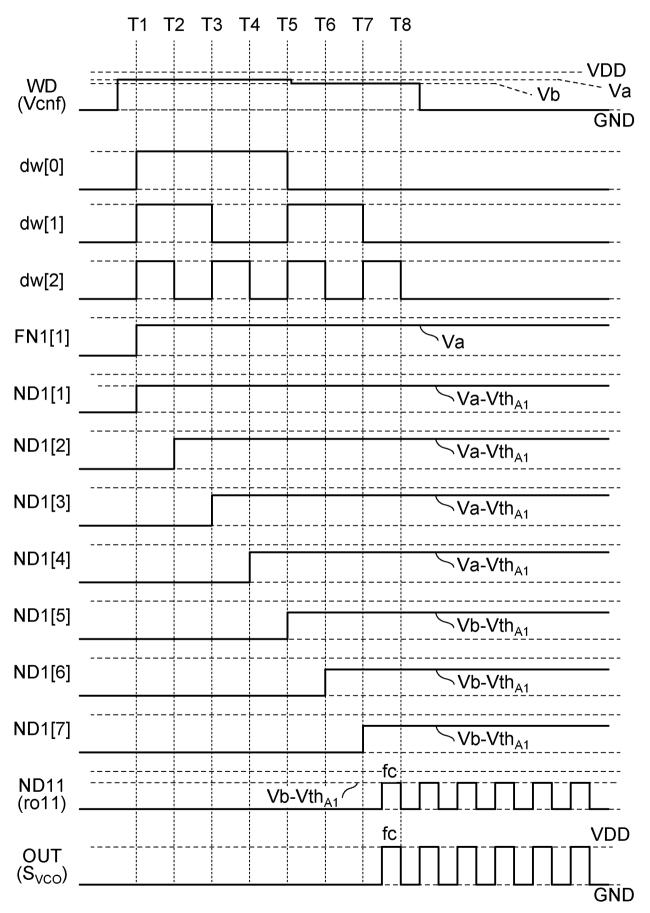

Operation examples of the circuit 101 shown in FIG. 1 are described. FIGS. 4A and 4B are timing charts showing the operation examples of the circuit 101. The potential Vcnf of the wiring WD is Va in FIG. 4A and Vb in FIG. 4B. Note that a relation of VDD>Va>Bb> GND is satisfied.

10 [0072] (V cnf = V a)

15

As shown in FIG. 4A, in a period where the Vcnf is a GND, the signal  $S_{VCO}$  does not oscillate. In order to make the signal  $S_{VCO}$  oscillate, supply of Va to the wiring WD is started. In a period where the wiring WD is at the Va, the VDD is supplied to the wiring WL. In all the circuits 30, the transistor MW1 is turned on, the analog potential Va is written to the node FN1, and the potential Vnd1 of the node ND1 becomes (Va-Vth<sub>A1</sub>). The potential of the wiring WL is set to the GND after setting it to the VDD in a certain period. In all the circuits 30, the analog potential Va is held by turning off the transistor MW1.

When the potential of the node FN1 is set to the Va, the circuit 101 starts to output the signal S<sub>VCO</sub> at an oscillation frequency of fa. Since the potential of the node ND1 is (Va–Vth<sub>A1</sub>), the amplitude of the output signal ro11 of the circuit 11 becomes (Va–Vth<sub>A1</sub>–GND). The circuit 80 performs level shift operation in which the high level potential of the signal ro11 is converted into the VDD. The circuit 101 oscillates at a frequency fa that is the same frequency as that of the signal ro11, and outputs the signal S<sub>VCO</sub> at an amplitude of (VDD–GND).

[0074]

30

$(V \operatorname{cnf} = V \operatorname{b})$

As shown in FIG. 4B, the operation of the circuit 101 is similar to that in FIG. 4A. Because Vcnf is Vb, the potential of the node ND1 is  $(Vb-Vth_{A1})$ . The signal ro11 oscillates at a frequency fb that is lower than the fa. The circuit 101 oscillates at the frequency of fb and outputs the signal  $S_{VCO}$  at an amplitude of (VDD-GND).

As shown in FIGS. 4A and 4B in the circuit 101, the oscillation frequency  $f_{VCO}$  of the signal  $S_{VCO}$  can be controlled by the potential Vcnf, and the amplitude of the signal  $S_{VCO}$  can be

constant without being affected by the potential Vcnf. That is, the circuit 101 can oscillate at a stable amplitude and a desired frequency.

[0076]

The circuit 42 has a function of storing analog data for setting the high power supply potential that is supplied to the inverter INV1. In other words, the circuit 42 has a function of storing analog data for setting the delay time of the INV1. Specifically, the analog data stored in the circuit 42 is the analog potential Vcnf input from the wiring WD. When a transistor with low off-state current is used as the transistor MW1, the circuit 42 can hold the potential Vfn1 of the node FN1 for a long period. The holding of the potential Vfn1 corresponding to the analog potential Vcnf in the circuit 42 means setting of the oscillation frequency  $S_{VCO}$  of the circuit 101, which is tuning operation of the circuit 101. Accordingly, the circuit 42 can function as a nonvolatile memory in which data (analog data) of the Vfn1 is stored, so that writing operation of the analog potential Vcnf is not required every time the circuit 101 is started up and oscillation at a predetermined frequency is possible without delay.

15 [0077]

10

20

For example, in the case of a PLL in which the circuit 101 is incorporated, after the circuit 101 is tuned so that the PLL oscillates at a desired frequency, the circuit 101 can output a signal at a predetermined frequency even when power of peripheral circuits other than the circuit 101 is turned off. Furthermore, when the PLL is restarted after the power of the whole PLL is shut off, the PLL can instantly output a signal which oscillates at a frequency similar to the frequency used before the power shutdown even without performing the tuning of the circuit 101. With the use of the circuit 101 in this manner, a PLL capable of quick restarting can be provided. [0078]

⟨⟨Configuration Examples 2 and 3 of Oscillator Circuit⟩⟩

FIG. 5 and FIG. 6 show modification examples of the circuit 101.

[0079]

In the circuit 101 in FIG. 1, an output signal of the circuit 30[n+1] is input to the input terminal/A of the circuit 80. In contrast, the circuit 30[n+1] is not provided for a circuit 102 in FIG. 5. In the circuit 102, an output signal of a circuit 30[n-1] is input to the input terminal /A of the circuit 80.

[0800]

30

35

The output signal of the circuit 30[n-1] is used for driving the circuit 30[n] and the circuit 80. An output signal of the circuit 30[n] is used for driving the circuit 30[1] and the circuit 80. Loads on output nodes of the circuit 30[n-1] and the circuit 30[n] can be equal to each other. A delay between the input signals of the terminal A and the terminal/A of the circuit

80 hardly occurs, so that performance of the circuit 80 is not lowered. This applies to the circuit 103 in FIG. 6.

[0081]

In the circuit 103 in FIG. 6, a circuit 30 in the (n+1)a-th stage and a circuit 30 in the (n+2)a-th stage are added in an output path of the circuit 11. Accordingly, loads on output nodes of the circuit 30[n+1] and the circuit 30[n+2)]a can be equal to each other. Thus, it hardly allows a delay to be caused between the input signals of the terminal A and the terminal/A of the circuit 80.

[0082]

There is no particular limitation on the circuit 80 as long as the level shift operation of the signal *ro*11 that is oscillated in the circuit 11 is possible. For example, the output signal of the circuit 11 (the circuit 30[n]) or a signal obtained by delaying the output signal of the circuit 11 with the k-stage-circuits 30 (k is one or two) can be input to the input terminal A of the circuit 80. An output terminal of any one of the circuits 30 is electrically connected to the input terminal/A of the circuit 80 so that an inverted signal of the input signal of the input terminal A is input to the input terminal/A.

[0083]

⟨⟨Configuration Example 4 of Oscillator Circuit⟩⟩

FIGS. 7A and 7B show a modification example of the circuit 30 in FIG. 2.

20 [0084]

In a circuit 31 in FIG. 7A, a circuit 43 is provided instead of the circuit 41. In the circuit 43, a switch SW1 is connected to an output terminal of the INV1. The switch SW1 has a function of controlling the conduction state between output terminals of the INV1 and the circuit 43. A signal *se* is a signal for controlling operation of the switch SW1.

25 [0085]

FIG. 7B illustrates an example of a specific circuit configuration of the circuit 43. FIG. 7B illustrates an example in which a transistor Mn2 is used as the switch SW1. The signal *se* is input to a gate of the transistor Mn2. Instead of the transistor Mn2, a p-channel transistor may be used as the switch SW1.

30 [0086]

(Operation Example)

FIG. 9 illustrates an operation example of the circuit 101 in which the circuit 31 is used. [0087]

Also in FIG. 9, similarly to FIG. 4A, an example in which the potential Vcnf is set to Va is shown. The signal se is set to a low level in a period where writing operation of an analog

potential into the circuit 31 is performed, so that the node ND11 does not oscillate. When the signal *se* is set to a high level, the circuit 11 functions as a ring oscillator circuit and starts oscillation. The signal S<sub>VCO</sub> at an oscillation frequency *f*a and an amplitude of (*V*DD–GND) is output from an output terminal OUT of the circuit 101. That is, in the circuit 101 including the circuit 31, the start of the oscillation can be controlled by the signal *se*. The circuits 100, 102, and 103 in each of which the circuit 31 is used can operate in a manner similar to that of the circuit 101.

[0088]

⟨⟨Configuration Example 5 of Oscillator Circuit⟩⟩

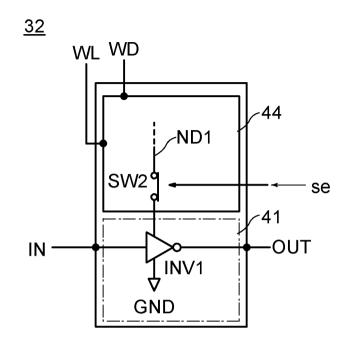

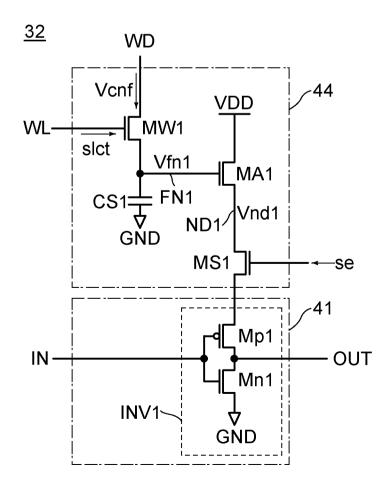

FIGS. 8A and 8B illustrate a configuration example of the circuit 30 (FIG. 2). [0089]

A circuit 32 in FIG. 8A is provided with a circuit 44 instead of the circuit 42. The circuit 44 is the one in which a switch SW2 is added to the circuit 42. The switch SW2 has a function of controlling the conduction state between the node ND1 and the input node of the high power supply potential of the INV1. The signal *se* is a signal for controlling the operation of the switch SW2.

[0090]

20

FIG. 8B illustrates an example of a specific circuit configuration of the circuit 32. In FIG. 8B, a transistor MS1 is used as the switch SW2. Instead of the transistor MS1, a p-channel transistor may be used as the switch SW2. The circuit 44 in FIG. 8B has a circuit configuration similar to that of a three-transistor gain cell. In contrast, the circuit 42 that is used in the circuit 30 and the circuit 31 has a circuit configuration similar to that of a two-transistor gain cell.

[0091]

## 25 < Operation Example>

The circuit 101 in which the circuit 32 is used can operate in accordance with the timing chart in FIG. 9. The circuits 100, 102, and 103 in each of which the circuit 32 is used can also operate in a manner to that of the circuit 101. That is, in each of the circuits 100, 102, and 103 in which the circuit 32 is used, the oscillation operation can be stopped by the signal se regardless of the value of V fn1 of the circuit 32.

[0092]

30

35

<Another Configuration Example of Circuit 90>

In the oscillator circuit including the circuit 31 or the circuit 32 as described in the configuration example 4 or 5, a circuit 92 shown in FIG. 10 may be provided instead of the circuit 90. The circuit 92 is a circuit in which a transistor MS9 is added to the circuit 90. The

transistor MS9 has a function of controlling the conduction state between the node ND9 and the input node of the circuit 80. The signal *se* is input to a gate of the transistor MS9. The supply of a potential from the circuit 92 to the circuit 80 can be stopped when the oscillation operation of the oscillator circuit is stopped by the signal *se*.

5 [0093]

<<Configuration Example 6 of Oscillator Circuit>>

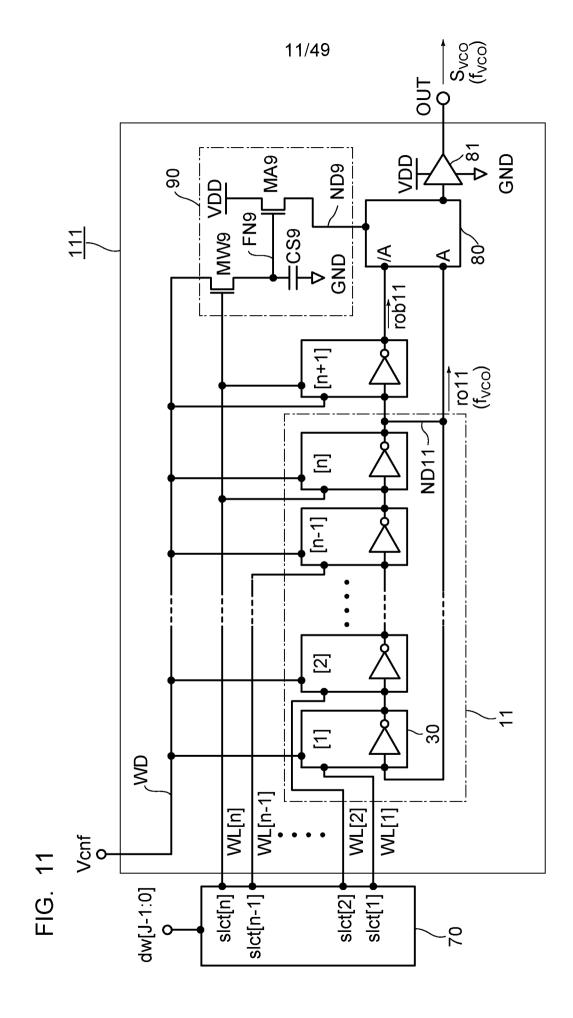

FIG. 11 is a modification example of the circuit 101 (FIG. 1). In the circuit 101, a common signal *slct* is input to all the circuits 30; thus, timing of writing operation of the potential Vcnf is the same in all the circuits 30. In contrast, in a circuit 111 in FIG. 11, signals *slct* which are different from one another can be input to the n circuits 30 included in the circuit 11. In the circuit 111, n wirings WL are provided corresponding to the first- to n-th-stage circuits 30. The (n+1)-th stage circuit 30 and the circuit 90 are electrically connected to the wiring WL[n].

[0094]

15 (Circuit 70)

The n wirings WL are electrically connected to a circuit 70. The circuit 70 has a function of generating n signals slct. The circuit 70 has a function of setting one of the signals slct[1] to slct[n] to a high level and the other signals to a low level. Such signals slct[1] to slct[n] are supplied to the circuit 111, so that one of the n circuits 30 can be in a writing state of the potential Vcnf and the others can be in a holding state of the potential Vfn1.

[0095]

20

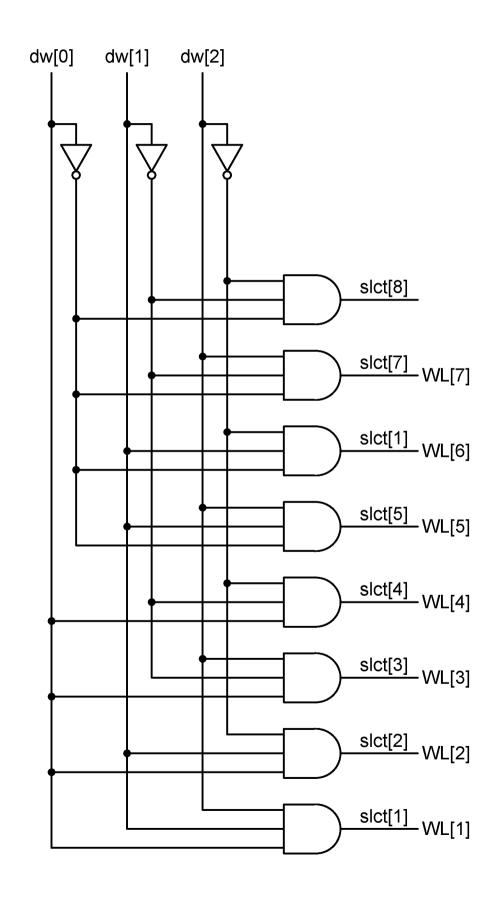

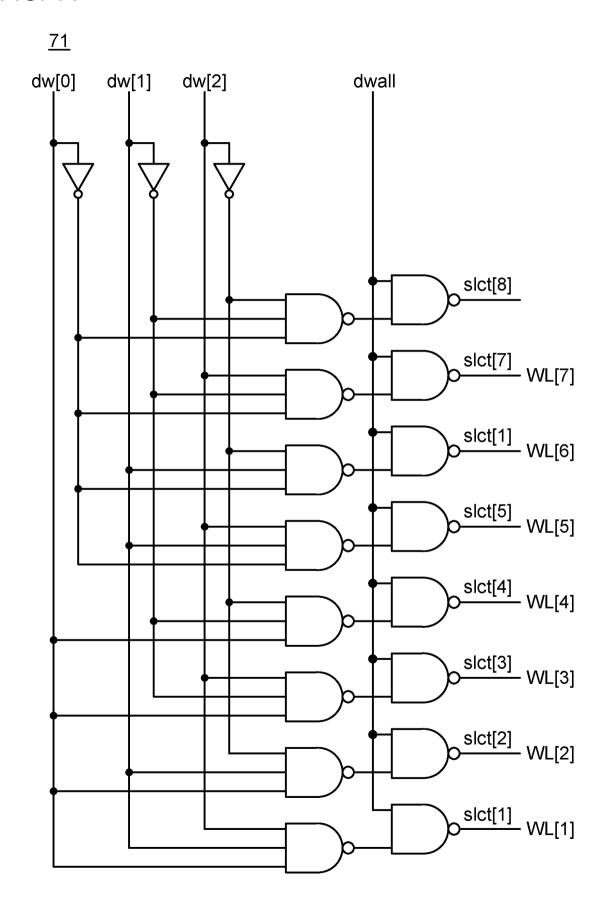

The circuit 70 can be a decoder circuit for decoding a *J*-bit digital signal dw[J-1:0], for example. Note that *J* is an integer greater than or equal 2, which satisfies  $n < 2^j$ . FIG. 12 illustrates a configuration example of a signal generation circuit that can be applied to the circuit 70. FIG. 12 illustrates a configuration example of the circuit 70 in the case where n = 7 and J = 3. The circuit 70 in FIG. 12 includes three inverters and eight AND circuits (AND gate circuits). To the circuit 70, 3-bit digital signal dw[2:0] is input. The circuit 70 decodes the signal dw[2:0] to generate eight signals slct[1] to slct[8]. The signals slct[1] to slct[7] are output to the wirings WL[1] to WL[7]. The signal slct[8] is a signal which is not used.

30 [0096]

<Operation Example>

An operation example of the circuit 111 in which the circuit 70 shown in FIG. 12 is used is described. FIG. 13 is a timing chart illustrating the operation example of the circuit 111 when n = 7 and J = 3.

35 [0097]

The waveform maximum potential and the waveform minimum potential in FIG. 13 are a VDD and a GND, respectively. Here, the  $f_{VCO}$  is  $f_0$  at the time when the potentials Vfn1 of all the nodes FN1 in the circuit 11 are Va, and the  $f_{VCO}$  is  $f_0$  at the time when the potentials Vfn1 of all the nodes FN1 are Vb. Note that relations of VDD > Va > Vb > GND and  $f_0 > f_0$  are satisfied. FIG. 13 illustrates an example in which, by tuning operation, an analog potential Va is written to each of the nodes FN1 of the circuits 30[1] to 30[4] and an analog potential Va is written to each of the nodes FN1 of the circuits 30[5] to 30[7] so that the circuit 111 oscillates at a frequency fc. Note that a relation of fa > fc > fb is satisfied. [0098]

As illustrated in FIG. 13, in a period during which the analog potential Va is supplied to the wiring WD, the wiring WL[1], the wiring WL[2], the wiring WL[3], and the wiring WL[4] are sequentially set at a high level. At time T1, a transistor MW1[1] is turned on. The potential Va is written to a node FN1[1] and the potential of a node ND1[1] becomes ( $Va - Vth_{A1}$ ). Similarly, at time T2, T3, and T4, the analog potential Va is written to each of nodes FN1[2], FN1[3], and FN1[4]. Each of the potentials of nodes ND1[2] to ND1[4] also becomes ( $Va - Vth_{A1}$ ).

In a period during which the analog potential Vb is supplied to the wiring WD, the wirings WL[5], WL[6], and WL[7] are sequentially set to a high level. At time T5, the potential levels of signals dw[0], dw[1], and dw[2] are changed. After that, the analog potential Vb is supplied to the wiring WD. The analog potential Vb is written to a node FN1[5], and the potential of a node ND1[5] becomes (Vb–Vth<sub>A1</sub>). Similarly, at time T6 and T7, Vb is written to each of a node FN1[6] and a node FN1[7]. Also at time T7, Vb is written to each of a node FN1[8] and the node FN9. The potentials of nodes ND1[6] to ND1[8] each also becomes (Vb–Vth<sub>A1</sub>).

[0100]

30

[0099]

10

15

After time T8, the nodes FN1[1] to FN1[8] and the node FN9 are electrically floating, and writing of the analog potential to all the circuits 30 and the circuit 90 is completed. At time T8, the circuit 111 starts to oscillate at the oscillation frequency fc. Since the potential of the node ND1 of the circuit 30[7] is  $(Vb-Vth_{A1})$ , the amplitude of the signal ro11 becomes  $(Vb-Vth_{A1}-GND)$ . The signal ro11 is boosted by the circuit 80 and the signal  $S_{VCO}$  at an amplitude of (VDD-GND) and the oscillation frequency fc is output from the circuit 111.

In the example of FIG. 11, in the circuit 11, potentials of the nodes FN1 of the *n*-stage circuits 30 can be individually set, so that the oscillation frequency  $f_{VCO}$  of the circuit 111 can be

minutely set. Thus, the circuit 111 has higher controllability than the circuit 101. [0102]

In the circuit 111, in the case where the circuit 31 (FIGS. 7A and 7B) is provided instead of the circuit 30, the transistor Mn2 is brought out of conduction by the signal *se* until writing of the analog potential to all the circuits 31 is completed, and then after the completion of the writing, the transistor Mn2 is turned on by the signal *se*. For example, in the operation example in FIG. 13, the transistor Mn2 is turned on by the signal *se* after time T8, so that the signal S<sub>VCO</sub> at an amplitude of (*V*DD–GND) and the oscillation frequency *fc* is output from the circuit 111. The same applies to the case where the circuit 32 (FIG. 8) is provided instead of the circuit 30.

10 [0103]

15

20

FIG. 11 illustrates the configuration example in which the circuit 111 does not include the circuit 70; however, the scope of this configuration example also includes an oscillator circuit including a circuit that can generate the signal *slct*.

[0104]

Note that FIG. 13 illustrates an operation example in which the circuit 70 can generate the signals *slct* whose number is greater than the number of the wirings WL; however, the number of the signals *slct* generated in the circuit 70 may be less than the number of the wirings WD. That is, n can be greater than  $2^J$ . For example, in the case where J = 3 and n = 11, the signal *slct*[1] is input to the wirings WL[1] to WL[3], the signal *slct*[2] is input to the wirings WL[4] and WL[5], and the signals *slct*[3] to *slct*[8] are input to the wirings WL[6] to WL[11]. Also in such a case, the oscillation frequency  $f_{VCO}$  can be minutely adjusted compared to the case of using the circuit 101.

Although the wirings WL as many as the circuits 30 included in the circuit 11 are provided in the example in FIG. 11, the configuration example is not limited thereto. The number of the wirings WL can be greater than two and less than n. When n = 11 and the number of the wirings WL is four, the circuits 30[1] to 30[3], the circuits 30[3] to 30[6], the circuit 30[7], and the circuit 30[8] can be electrically connected to the wiring WL[1], the wiring WL[2], the wiring WL[3], and the wiring WL[4], respectively.

30 [0106]

[0105]

(Circuit 71)

A circuit 71 in FIG. 14 is a modification example of the circuit 70. The circuit 71 can also generate eight signals *slct* like the circuit 70. The circuit 71 includes three inverters, eight three-input NAND gate circuits, and eight two-input NAND gate circuits.

35 [0107]

A three-bit digital signal dw[2:0] and a signal dwall are input to the circuit 71. The circuit 71 has a function of decoding the signal dw[2:0] to set any one of the signals slct[1] to slct[8] to a high level. The signal dwall has a function of setting the potential levels of the signals slct[1] to slct[8] to a high level regardless of the signal dw[2:0]. Specifically, when the signal dwall is a low level, the signals slct[1] to slct[8] become a high level regardless of the signal dw[2:0]. When the signal dwall is at a high level, any one of the signals slct[1] to slct[8]becomes a high level in accordance with the signal dw[2:0] and the others become a low level. With the use of the circuit 71, writing operation of the potential Vcnf to all the circuits 30 in the circuit 111 becomes possible at the same timing.

10 [0108]

<< Configuration Example 7 of Oscillator Circuit>>

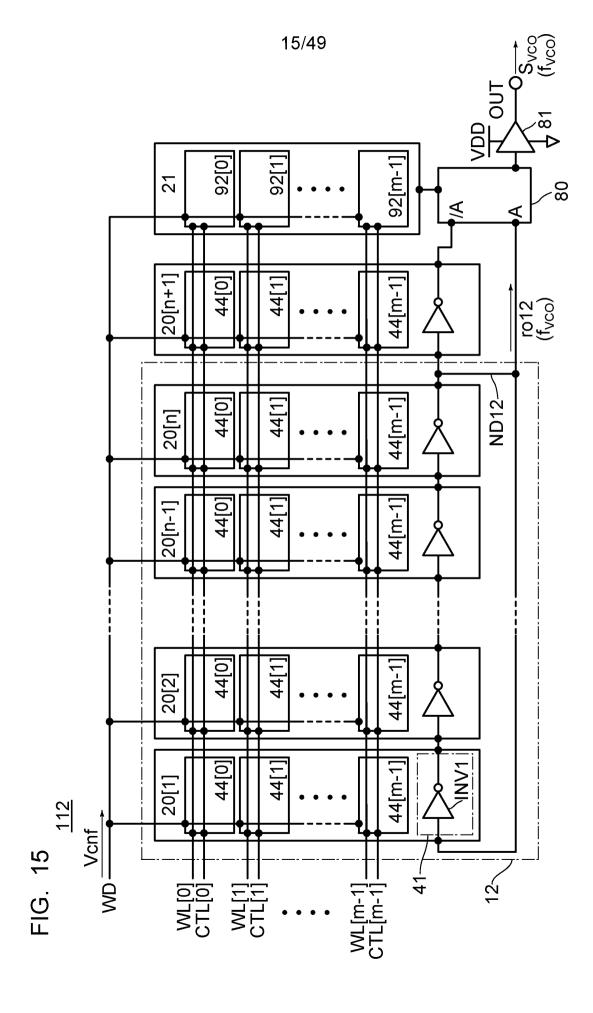

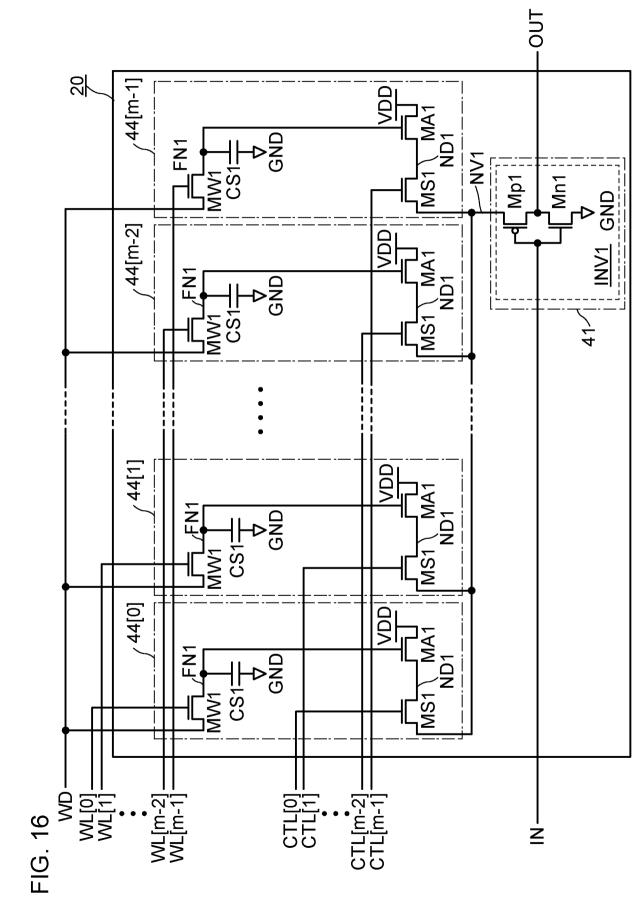

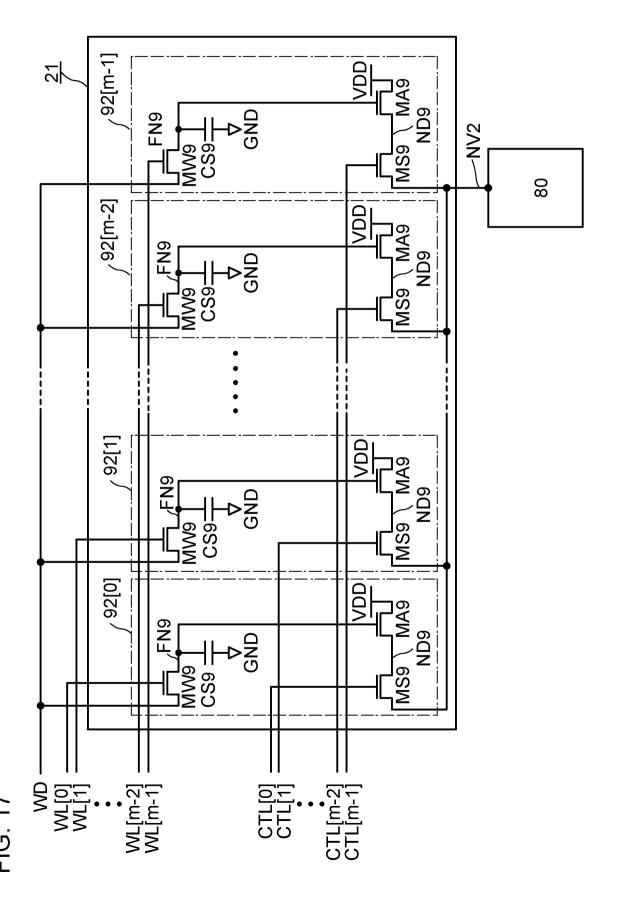

FIG. 15 illustrates a configuration example of an oscillator circuit. A circuit 112 in FIG. 15 is a modification example of the oscillator circuit in which the circuit 32 (FIGS. 8A and 8B) described in Configuration Example 5 is used. The circuit 112 includes (n+1)-stage circuits 20, a circuit 21, the circuit 80, and the buffer circuit 81. The (n+1)-stage circuits 20 and the circuit 21 are each electrically connected to the wiring WD, m wirings WL, and m wirings CTL (m is an integer greater than or equal to 2). The circuit 20 and the circuit 21 correspond to the circuit 32 and the circuit 90, respectively. FIG. 16 shows a configuration example of the circuit 20. FIG. 17 shows a configuration example of the circuit 21.

[0109] 20

15

25

35

<Circuit 20>

The circuit 20 includes the circuit 41 and m circuits 44. The circuit 41 includes the inverter INV1. Each of output nodes of first- to *n*-th-stage circuits 20 is electrically connected to an input node of the circuit 20 in the next stage. An output node ND12 of the circuit 20 in the *n*-th stage is electrically connected to an input node of the circuit 20 in the first stage. A circuit 12 includes the first- to *n*-th-stage circuits 20. That is, the circuit 12 includes *n* inverters INV1, and can function as a ring oscillator like the circuit 11 (in FIG. 1). [0110]

A plurality of circuits 44 is provided in each circuit 20, so that a plurality of configuration data for setting a high power supply potential that is to be supplied to the INV1 can 30 The configuration data is an analog potential Vcnf input from the wiring WD. In each circuit 20, any one of the plurality of configuration data is selected, so that the high power supply potential that is to be supplied to the INV1 can be changed and thus the delay time of the INV1 can be changed. The oscillation frequency  $f_{VCO}$  of the output signal  $S_{VCO}$  of the circuit 112 can be controlled. Thus, the circuit 112 can be referred to as a multi-context programmable

oscillator circuit.

[0111]

For the m circuits 44, m wirings WL and m wirings CTL are provided. As shown in FIG. 16, in a circuit 44[h] (h is an integer greater than or equal to 0 and less than or equal to (m-1)), a gate of a transistor MW1 is electrically connected to a wiring WL[h], and a gate of a wiring MS1 is electrically connected to a wiring CTL[h]. Each drain of the transistors MW1 in the m circuits 44 is electrically connected to the wiring WD. In the circuit 20, any one of the m transistors MS1 is turned on, so that the potential Vnd1 of the node ND1 of the corresponding circuit 44 can be supplied to the node NV1. The node NV1 is an input node of the high power supply potential of the node INV1.

[0112]

15

20

<Circuit 21>

The circuit 21 includes *m* circuits 92. Similarly to the circuit 90, the circuit 21 has a function of generating power supply potential that is to be supplied to the circuit 80. The circuit 21 is provided in accordance with the circuit configuration of the circuit 80. The circuit 21 has a circuit configuration in which the circuit 41 is omitted from the circuit 20. [0113]

In the circuit 92[h] in FIG. 17, a gate of the transistor MW9 is electrically connected to the wiring WL[h] and a gate of the transistor MS9 is electrically connected to the wiring CTL[h]. Each drain of the transistors MW9 in the m circuits 92 is electrically connected to the wiring WD. Any one of the transistors MS9 in the m circuits 92 is turned on, so that the potential of the node ND9 of a corresponding circuit 92 can be supplied to the node NV2. The node NV2 is an input node of the high power supply potential of the circuit 80.

25 < Operation Example>

The circuit 112 can be referred to as a multi-context programmable oscillator circuit. A set of configuration data is referred to as a context. The input signals of wirings CTL[0] to CTL[m-1] can function as signals which can select the context. The context can be quickly switched in accordance with the input signals of the wirings CTL[0] to CTL[m-1].

30 [0115]

35

In the circuit 112, a set of m configuration data can be stored. Thus, after the set of m configuration data is stored in the circuit 112, the oscillation frequency  $f_{VCO}$  can be changed by switching the context even in oscillation operation. An example of the operation of the circuit 112 is described with reference to FIG. 18. FIG. 18 and FIG. 19 are each a timing chart of the circuit 112 in the case where the number of contexts is two (m = 2). FIG. 18 shows an example

of writing operation of the configuration data, that is configuration operation. FIG. 19 is a timing chart continued from FIG. 18, which shows an example of the oscillation operation.

[0116]

As in FIGS. 4A and 4B, VDD>VA>Vb. The threshold voltages of the transistors MA1 and MA9 are denoted by  $Vth_{A1}$  and  $Vth_{A9}$ , respectively. In FIG. 18 and FIG. 19, the waveform maximum potential and the waveform minimum potential are a VDD and a GND, respectively. [0117]

(Configuration Operation)

In the configuration operation, only the wiring WL[h] corresponding to a context[h] is set to a high level and the other wirings WL are set to a low level, whereby the analog potential of the wiring WD is written to the circuit 44[h] and the circuit 92[h] which correspond to the context[h]. In the configuration operation, the potentials of all the wirings CTL are maintained at a low level. In the circuit 20, the circuit 44 and the circuit 41 are in a non-conduction state, and the circuit 21 and the circuit 80 are also in a non-conduction state; thus, the potentials of the node NV1 and the node NV2 are at a low level.

[0118]

10

15

20

25 [0119]

30

Next, writing of configuration data with a context[1] is performed. An analog potential Vb is supplied to the wiring WD. The wiring WL[1] is set at a high level, so that Vb is written to the circuits 44[1] of the first- to the (n+1)-th-stage circuits 20. The wiring WL[1] is set to a low level, so that writing of configuration data is completed. In each circuit 44[1], the potential of the node FN1[1] becomes Vb and the potential of the node ND1[1] becomes  $(Vb-Vth_{A1})$ . Furthermore, in the circuit 21, the potential of the node FN9[1] of the circuit 92[1] becomes  $(Vb-Vth_{A9})$ .

[0120]

Here, the oscillator frequency of the circuit 12 is set to *f*a or *f*b depending on the configuration data with the context[0] and the context[1].

[0121]

(Oscillation Operation)

When the circuit 112 oscillates, only a wiring CTL[h] corresponding to a context[h] to be selected is set to a high level, and the other wirings are set to a low level. In the first- to (n+1)-th-stage circuits 20, a node FN1[h] of the circuit 44 [h] and the node NV1 of the INV1 are brought into conduction. The delay time of INV1 in each circuit 20 is the length of time based on the configuration data of the context[h], and the circuit 112 can oscillate at a predetermined frequency. In the circuit 21, the node FN9[h] is in conduction with the node NV2.

In the example in FIG. 19, the wiring CTL[0] is selected, and the potential of the wiring CTL[0] is set to a high level. The potential of the node NV1 of each circuit 20 is substantially equal to the potential  $(Va-Vth_{A1})$  of the node ND1[0]; thus, a signal ro12 at an oscillation frequency of fa and an amplitude of  $(Va-Vth_{A1}-GND)$  is output from the output node ND12 of the circuit 12. The signal ro12 is amplified by the circuit 80. The signal  $S_{VCO}$  at an oscillation frequency of fa and an amplitude of (VDD-GND) is output from an output terminal of the circuit 112.

[0123]

10

15

25

30

35

When the wiring CTL[0] is set to a low level, the supply of the power supply potential to the INV1 of each circuit 21 is interrupted, and the circuit 112 does not oscillate.

20 [0124]

A wiring CTL[1] is set to a high level to select the context [1]. The potential of the node NV1 of each circuit 20 is substantially equal to the potential ( $Vb-Vth_{A1}$ ) of the node ND1[1]; thus, a signal ro12 at an oscillation frequency of fb and an amplitude of ( $Vb-Vth_{A1}$ -GND) is output from the output node ND12 of the circuit 12. The signal ro12 is amplified by the circuit 80. The signal  $S_{VCO}$  at an oscillation frequency fb and an amplitude of (VDD-GND) is output from the circuit 112.

It is possible to perform oscillation operation with only a wiring CTL corresponding to a certain context number setting to a high level and, at the same time, to rewrite configuration data of wirings CTL corresponding to other context numbers.

[0126]

As described above, in the circuit 112, the oscillation frequency can be changed at a high speed even in the oscillation operation by changing contexts. Furthermore, extremely low off-state current of the transistor MW1 allows the circuit 44 to hold the configuration data for a long period even after the power supply is stopped. Thus, there is no need to perform the

configuration operation every time the circuit 112 is restarted, and the circuit 112 can oscillates at a desired frequency immediately after it is restarted.

[0127]

<< Configuration Example 8 of Oscillator Circuit >>

FIGS. 20A to 20C are modification examples of the circuits 30 to 32.

[0128]

5

10

The circuit 30 (FIG. 2), the circuit 31 (FIGS. 7A and 7B), and the circuit 32 (FIGS. 8A and 8B) are each a basic circuit of a ring oscillator circuit. The circuits 30 to 32 each has a function of controlling the high power supply potential that is to be supplied to the INV1 by the potential held at the node FN1. The delay time of the INV1 can be changed by changing the high power supply potential, and the delay time of the INV1 can also be changed by changing the low power supply potential. The circuits 35 to 37 in FIGS. 20A to 20C each has a function of changing the low power supply potential by the potential held at the node FN1.

The circuit 35 in FIG. 20A is a modification example of the circuit 30. The circuit 35 includes a circuit 41 and a circuit 45. An output node ND1 of the circuit 45 is electrically connected to an input node of the low power supply potential of the INV1. The circuit 45 has a structure similar to that of the circuit 42 (FIG. 2). Here, a p-channel transistor MB1 is provided instead of the n-channel transistor MA1. Note that an n-channel transistor can be used as the transistor MB1. The operation of the circuit 45 is similar to that of the circuit 42; thus, description of the circuit 42 is referred to.

[0130]

The circuit 36 shown in FIG. 20B is a modification example of the circuit 31. In the circuit 36, a circuit 45 is provided instead of the circuit 42. The circuit 37 shown in FIG. 20C is a modification example of the circuit 32. In the circuit 37, a circuit 46 is provided instead of the circuit 42.

[0131]

25

30

The circuits 35 to 37 can be used in the circuit 100 (FIG. 3). When a ring oscillator circuit is formed using the circuits 35 to 37, as shown in FIG. 3, it is preferable that an output signal of the ring oscillator be boosted by the circuit 85 in which the circuit 90 is not necessary. [0132]

<< Configuration Example 9 of Oscillator Circuit >>

The basic circuit of the ring oscillator can have a circuit configuration in which both the high power supply potential and the low power supply potential of the inverter can be controlled.

35 [0133]