(19)中華民國智慧財產局

(12)發明說明書公告本 (11)證書號數：TW I618252 B

(45)公告日：中華民國 107 (2018) 年 03 月 11 日

(21)申請案號：103103936

(22)申請日：中華民國 103 (2014) 年 02 月 06 日

(51)Int. Cl. : **H01L29/78 (2006.01)****H01L21/336 (2006.01)**

(30)優先權：2013/02/12 日本

2013-025025

(71)申請人：半導體能源研究所股份有限公司 (日本) SEMICONDUCTOR ENERGY

LABORATORY CO., LTD. (JP)

日本

(72)發明人：田中哲弘 TANAKA, TETSUHIRO (JP)；山根靖正 YAMANE, YASUMASA (JP)；

須澤英臣 SUZAWA, HIDEO MI (JP)；松林大介 MATSUBAYASHI, DAISUKE

(JP)；山崎舜平 YAMAZAKI, SHUNPEI (JP)

(74)代理人：林志剛

(56)參考文獻：

US 2013/0009220A1

US 2013/0063675A1

審查人員：邱迺軒

申請專利範圍項數：6 項 圖式數：50 共 207 頁

(54)名稱

半導體裝置

SEMICONDUCTOR DEVICE

(57)摘要

本發明的一個方式的目的之一是提供一種具有良好的電特性的電晶體等。本發明的一個方式是一種半導體裝置，包括：閘極電極；與閘極電極接觸的閘極絕緣膜；以及與閘極絕緣膜接觸並從離閘極絕緣膜最遠的一側依次包括第一氧化物半導體層、第二氧化物半導體層以及第三氧化物半導體層的多層膜，第一氧化物半導體層、第二氧化物半導體層以及第三氧化物半導體層包含銦、元素 M(鋁、鎵、鈦或錫)及鋅，第一氧化物半導體層的元素 M 對銦的原子數比大於第二氧化物半導體層的元素 M 對銦的原子數比，且第一氧化物半導體層的厚度為 20nm 以上且 200nm 以下，第三氧化物半導體層的元素對銦的原子數比大於第二氧化物半導體層的元素 M 對銦的原子數比，且第三氧化物半導體層的厚度為 0.3nm 以上且小於 10nm。

A transistor or the like having excellent electrical characteristics is provided. A semiconductor device includes a gate electrode; a gate insulating film in contact with the gate electrode; and a multilayer film which is in contact with the gate insulating film and includes a first oxide semiconductor layer, a second oxide semiconductor layer, and a third oxide semiconductor layer in the order from a side farthest from the gate insulating film. The first oxide semiconductor layer, the second oxide semiconductor layer, and the third oxide semiconductor layer each contain indium, an element M (aluminum, gallium, yttrium, or tin), and zinc. The first oxide semiconductor layer has a thickness greater than or equal to 20 nm and less than or equal to 200 nm. The third oxide semiconductor layer has a thickness greater than or equal to 0.3 nm and less than 10 nm.

指定代表圖：

圖 1A

# 發明專利說明書

(本說明書格式、順序，請勿任意更動)

## 【發明名稱】(中文/英文)

半導體裝置

Semiconductor device

## 【技術領域】

[0001] 本發明係關於一種物體、方法或製造方法。或者，本發明關於一種程式 (process) 、機器 (machine) 、產品 (manufacture) 或者組成物 (composition of matter)。尤其是，本發明關於例如半導體層、半導體裝置、顯示裝置、液晶顯示裝置、發光裝置。或者，本發明關於半導體層、半導體裝置、顯示裝置、液晶顯示裝置、發光裝置的製造方法。或者，本發明關於半導體裝置、顯示裝置、液晶顯示裝置、發光裝置的驅動方法。尤其是，本發明關於例如具有電晶體的半導體裝置、顯示裝置、發光裝置或上述裝置的驅動方法。或者，本發明關於例如包括該半導體裝置、該顯示裝置或該發光裝置的電子裝置。

[0002] 注意，在本說明書中半導體裝置是指能夠藉由利用半導體特性而工作的所有裝置，因此電光裝置、半導體電路以及電子裝置等都是半導體裝置。

## 【先前技術】

[0003] 使用形成在具有絕緣表面的基板上的半導體膜構成電晶體的技術受到關注。該電晶體被廣泛地應用於如積體電路或顯示裝置等的半導體裝置。作為可用於電晶體的半導體膜，已知矽膜。

[0004] 關於用於電晶體的半導體膜的矽膜，根據用途分別使用非晶矽膜或多晶矽膜。例如，當用於構成大型顯示裝置的電晶體時，較佳為使用已有大面積基板上進行成膜的技術的非晶矽膜。另一方面，當用於構成一起形成有驅動電路的高功能的顯示裝置的電晶體時，較佳為使用製造具有高場效移動率的電晶體的多晶矽膜。作為形成多晶矽膜的方法，已知藉由對非晶矽膜進行高溫下的加熱處理或進行雷射處理形成的方法。

[0005] 近年來氧化物半導體膜受到關注。例如，公開了使用包含銦、鎵及鋅的非晶氧化物半導體膜的電晶體（參照專利文獻 1）。

[0006] 因為氧化物半導體膜可以利用濺射法等形成，所以可以將它用於構成大型顯示裝置的電晶體的通道形成區。另外，使用氧化物半導體膜的電晶體具有高場效移動率，從而可以實現一起形成有驅動電路的高功能的顯示裝置。另外，因為當製造使用氧化物半導體膜的電晶體時可以改良使用非晶矽層的電晶體的生產裝置的一部分而利用，所以在可以抑制生產投資的方面上優勢。

[0007] 此外，已知由  $\text{InMO}_3 (\text{ZnO})_m$  (M 是 Fe、Ga、Al；m 是自然數) 表示的同源化合物 (homologous

compound) (參照非專利文獻 1)。在由  $\text{InMO}_3 (\text{ZnO})_m$  表示的同源化合物中，尤其是，M 是 Ga 的結晶根據在世界上首次合成其結晶的君塚升博士有時被稱為“君塚結晶”。

[0008] [專利文獻 1]日本專利申請公開第 2006-165528 號公報

[0009] [非專利文獻 1] N.Kimizuka, M.Isobe, and M.Nakamura, "Syntheses and Single-Crystal Data of Homologous Compounds,  $\text{In}_2\text{O}_3 (\text{ZnO})_m$  ( $m=3, 4$ , and  $5$ ),  $\text{InGaO}_3 (\text{ZnO})_3$ , and  $\text{Ga}_2\text{O}_3 (\text{ZnO})_m$  ( $m=7, 8, 9$ , and  $16$ ) in the  $\text{In}_2\text{O}_3\text{-ZnGa}_2\text{O}_4\text{-ZnO}$  System" (同系物的合成和單晶資料,  $\text{In}_2\text{O}_3\text{-ZnGa}_2\text{O}_4\text{-ZnO}$  類的  $\text{In}_2\text{O}_3 (\text{ZnO})_m$  ( $m=3, 4$ 、以及  $5$ )、 $\text{InGaO}_3 (\text{ZnO})_3$  以及  $\text{Ga}_2\text{O}_3 (\text{ZnO})_m$  ( $m=7, 8, 9$  以及  $16$ ) ), *J. Solid State Chem.*, 1995, Vol.116, pp.170-178

### 【發明內容】

[0010] 本發明的一個方式的目的之一是提供一種具有良好的電特性的電晶體等。或者，本發明的一個方式的目的之一是提供一種通態電流大的電晶體等。或者，本發明的一個方式的目的之一是提供一種具有穩定的電特性的電晶體等。

[0011] 或者，本發明的目的之一是提供一種關態電流 (off-state current) 小的電晶體等。本發明的目的之一

是提供一種具有高場效移動率的電晶體等。本發明的目的之一是提供一種良率高的電晶體等。本發明的目的之一是提供一種具有該電晶體等的半導體裝置等。本發明的目的之一是提供一種新穎的半導體裝置等。

[0012] 注意，這些目的的記載不妨礙其他目的的存在。此外，本發明的一個方式並不需要實現所有上述目的。另外，從說明書、圖式、申請專利範圍等的記載得知並可以抽出上述以外的目的。

[0013] 本發明的一個方式是一種半導體裝置，包括：閘極電極；與閘極電極接觸的閘極絕緣膜；以及與閘極絕緣膜接觸並從離閘極絕緣膜最遠的一側依次包括第一氧化物半導體層、第二氧化物半導體層以及第三氧化物半導體層的多層膜，第一氧化物半導體層、第二氧化物半導體層以及第三氧化物半導體層包含銻、元素 M（鋁、鎵、鈓或錫）及鋅，第一氧化物半導體層的元素 M 對銻的原子數比大於第二氧化物半導體層的元素 M 對銻的原子數比，且第一氧化物半導體層的厚度為 20nm 以上且 200nm 以下，第三氧化物半導體層的元素 M 對銻的原子數比大於第二氧化物半導體層的元素 M 對銻的原子數比，且第三氧化物半導體層的厚度為 0.3nm 以上且小於 10nm。

[0014] 或者，本發明的一個方式是一種半導體裝置，包括：閘極電極；與閘極電極接觸的閘極絕緣膜；以及與閘極絕緣膜接觸並從離閘極絕緣膜最遠的一側依次包括第一氧化物半導體層、第二氧化物半導體層以及第三氧

化物半導體層的多層膜，第一氧化物半導體層、第二氧化物半導體層以及第三氧化物半導體層包含銦、元素 M 及鋅，第一氧化物半導體層的元素 M 對銦的原子數比為第二氧化物半導體層的元素 M 對銦的原子數比的 1.5 倍以上，且第一氧化物半導體層的厚度為 20nm 以上且 200nm 以下，第三氧化物半導體層的元素 M 對銦的原子數比為第二氧化物半導體層的元素 M 對銦的原子數比的 1.5 倍以上，且第三氧化物半導體層的厚度為 0.3nm 以上且小於 10nm。

[0015] 或者，本發明的一個方式是一種半導體裝置，包括：閘極電極；與閘極電極接觸的閘極絕緣膜；以及與閘極絕緣膜接觸並從離閘極絕緣膜最遠的一側依次包括第一氧化物半導體層、第二氧化物半導體層以及第三氧化物半導體層的多層膜，第一氧化物半導體層、第二氧化物半導體層以及第三氧化物半導體層包含銦、元素 M 及鋅，第一氧化物半導體層的導電帶底的能量比第二氧化物半導體層高，且第一氧化物半導體層的厚度為 20nm 以上且 200nm 以下，第三氧化物半導體層的導電帶底的能量比第二氧化物半導體層高，且第三氧化物半導體層的厚度為 0.3nm 以上且小於 10nm。

[0016] 或者，本發明的一個方式是一種半導體裝置，包括：閘極電極；與閘極電極接觸的閘極絕緣膜；以及與閘極絕緣膜接觸並從離閘極絕緣膜最遠的一側依次包括第一氧化物半導體層、第二氧化物半導體層以及第三氧

化物半導體層的多層膜，第一氧化物半導體層、第二氧化物半導體層以及第三氧化物半導體層包含銦、元素 M 及鋅，第一氧化物半導體層的傳導帶底的能量比第二氧化物半導體層高  $0.2\text{eV}$  以上且  $2\text{eV}$  以下，且第一氧化物半導體層的厚度為  $20\text{nm}$  以上且  $200\text{nm}$  以下，第三氧化物半導體層的傳導帶底的能量比第二氧化物半導體層高  $0.2\text{eV}$  以上且  $2\text{eV}$  以下，且第三氧化物半導體層的厚度為  $0.3\text{nm}$  以上且小於  $10\text{nm}$ 。

[0017] 或者，在上述本發明的一個方式的半導體裝置的任一個中，在第二氧化物半導體層與第三氧化物半導體層之間包括源極電極及汲極電極。

[0018] 本發明的一個方式可以提供一種具有良好的電特性的電晶體等。或者，本發明的一個方式可以提供一種通態電流大的電晶體等。或者，本發明的一個方式可以提供一種具有穩定的電特性的電晶體等。

[0019] 或者，本發明的一個方式可以提供一種關態電流小的電晶體等。本發明的一個方式可以提供一種具有高場效移動率的電晶體等。本發明的一個方式可以提供一種良率高的電晶體等。本發明的一個方式可以提供一種具有該電晶體等的半導體裝置等。本發明的一個方式可以提供一種新穎的半導體裝置等。

### 【圖式簡單說明】

[0020] 在圖式中：

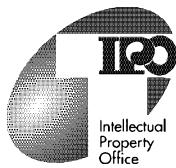

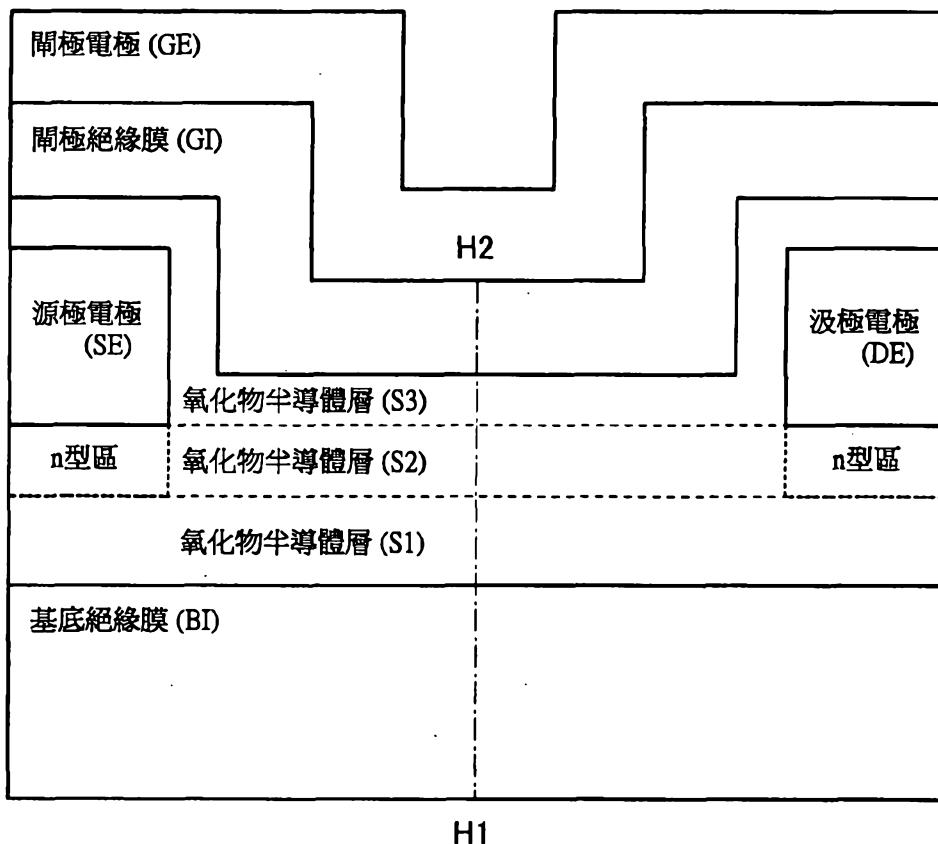

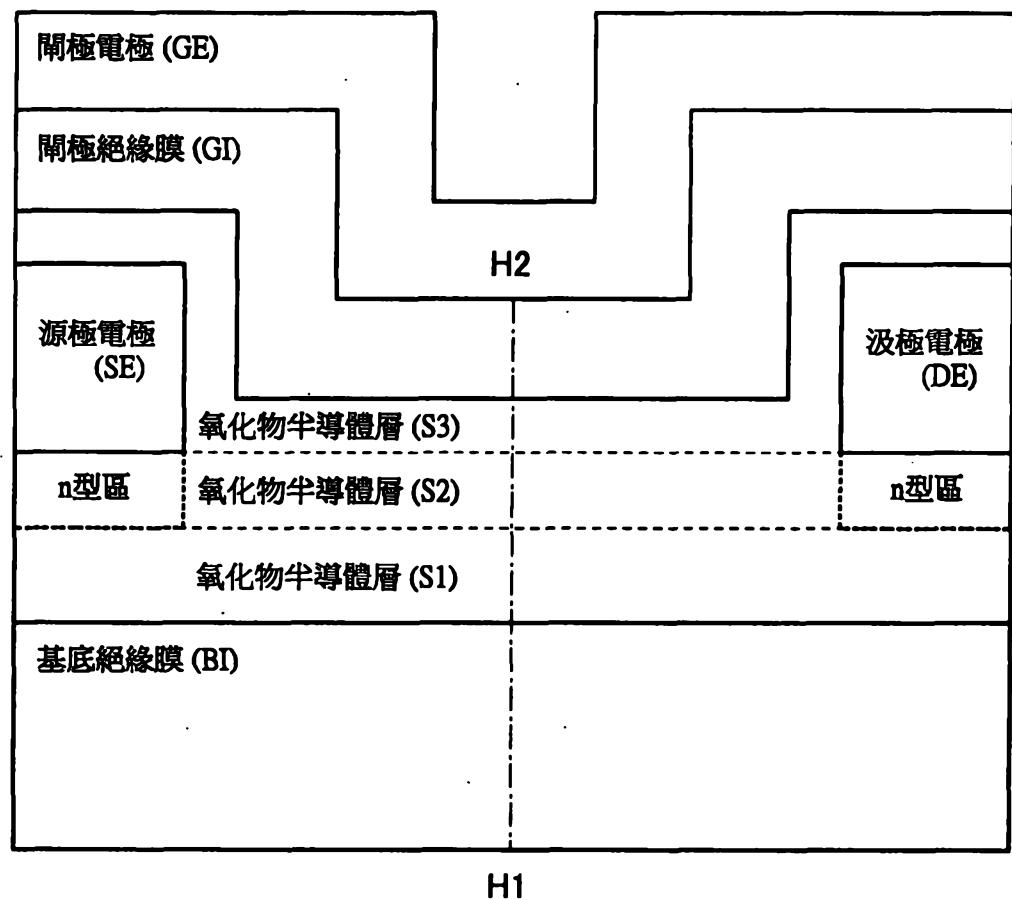

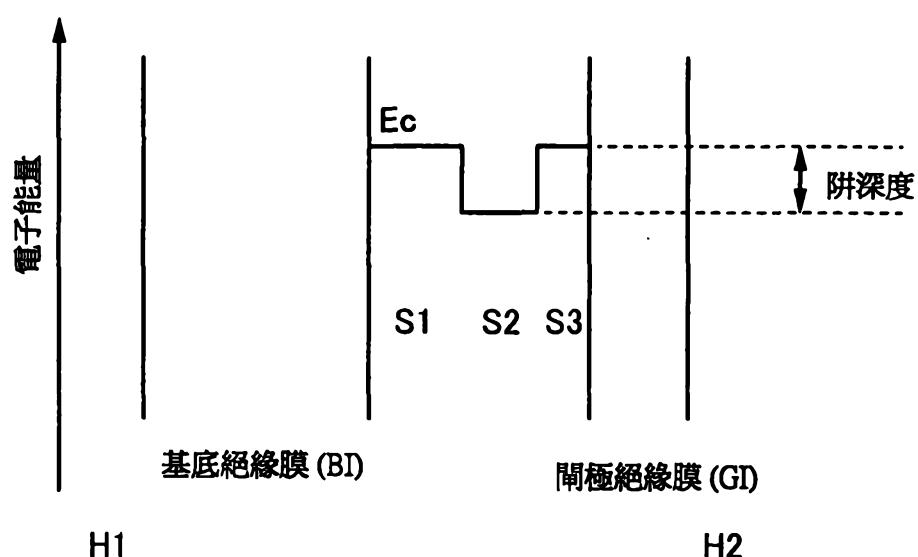

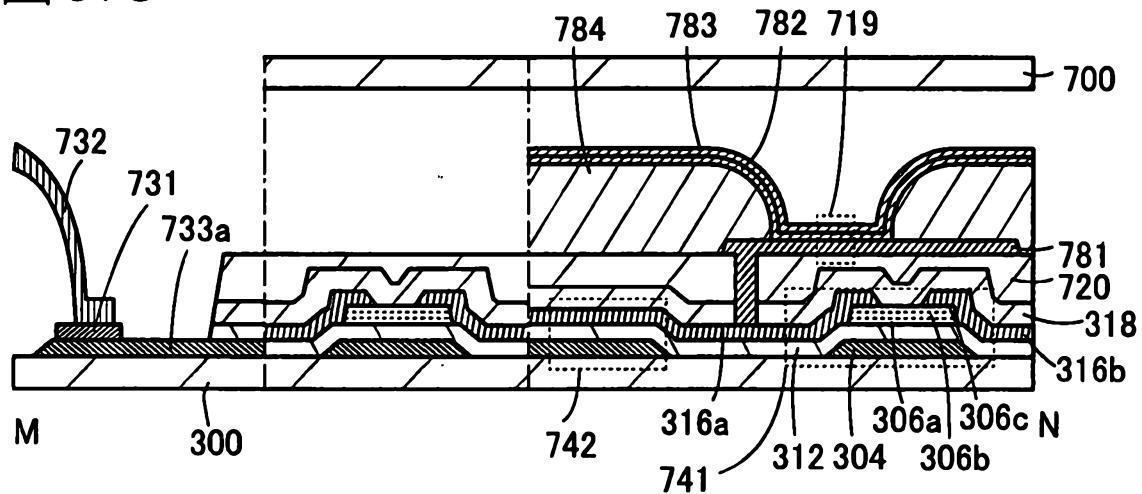

圖 1A 和圖 1B 是電晶體的剖面圖以及說明帶結構的圖；

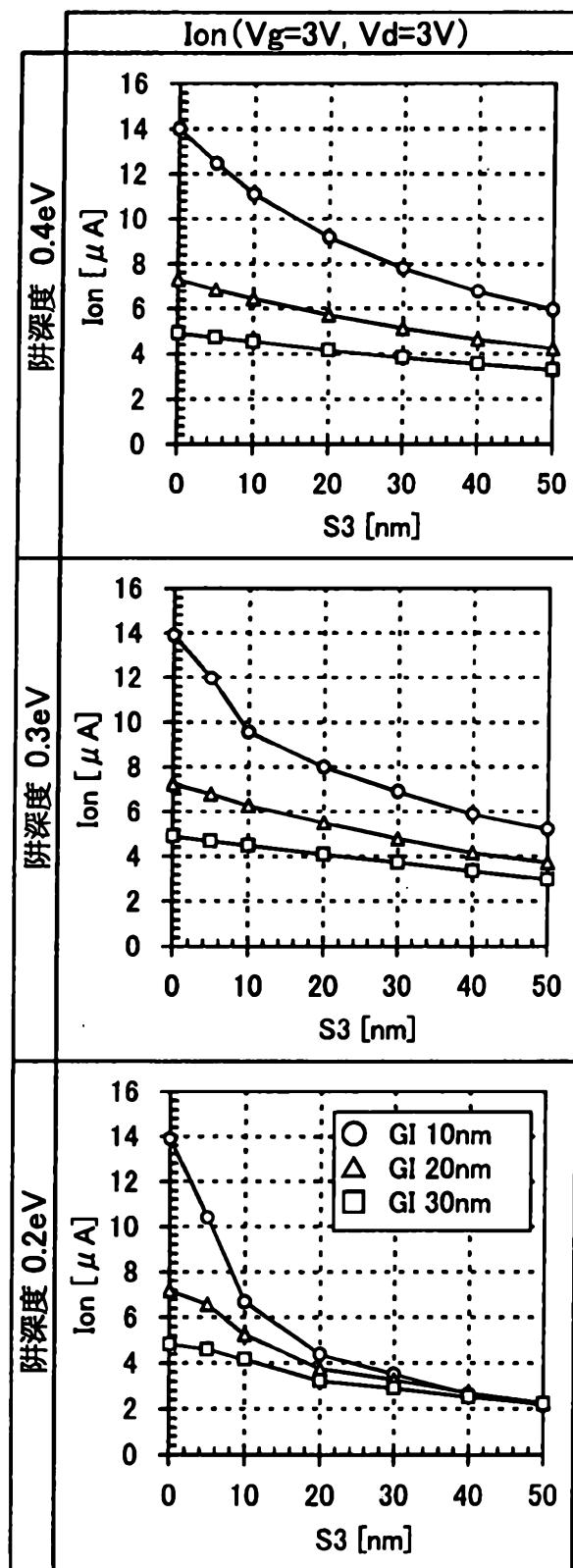

圖 2 是說明多層膜的結構與通態電流的關係的圖；

圖 3 是說明多層膜的結構與通態電流的關係的圖；

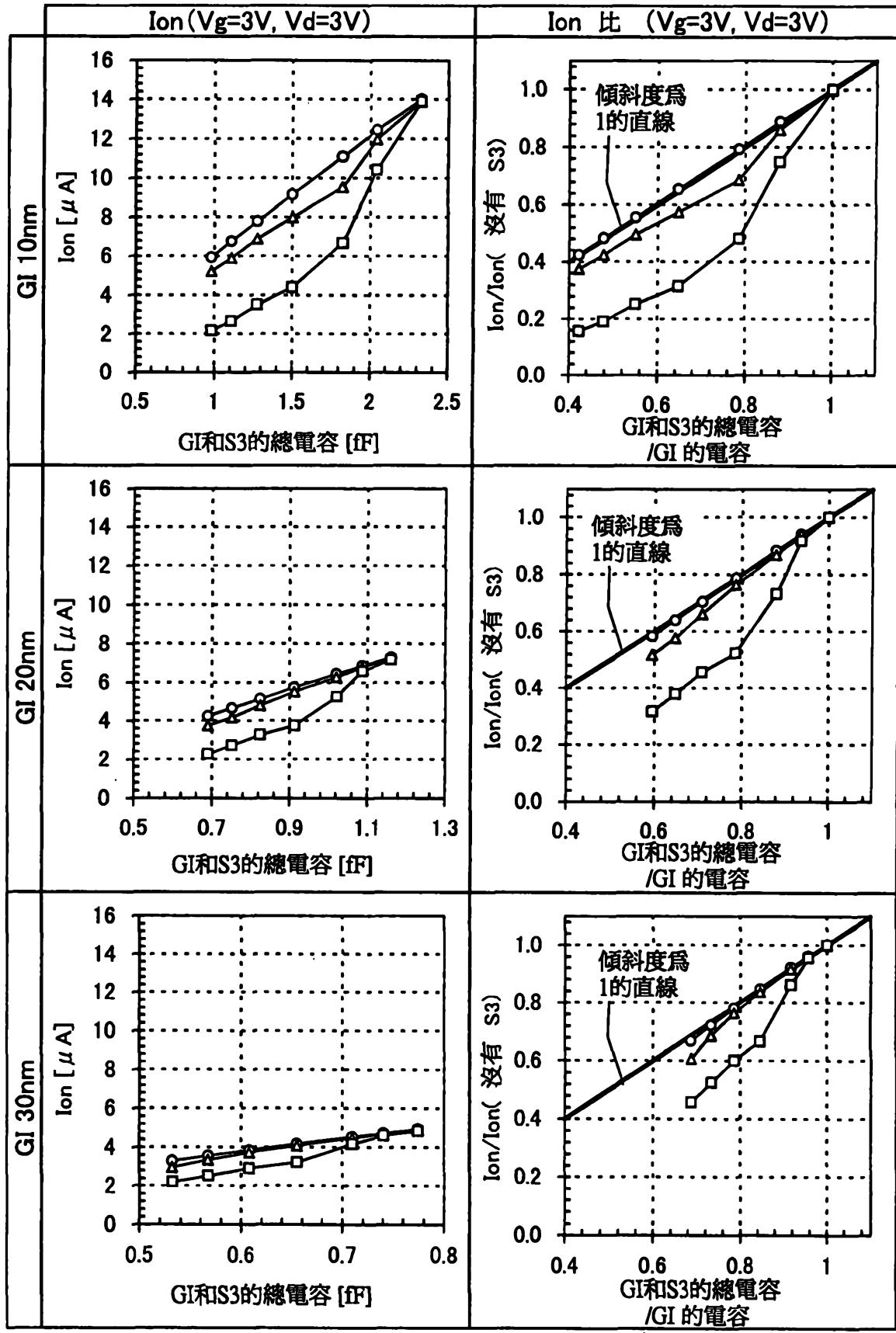

圖 4 是說明多層膜的結構與電流密度的關係以及多層膜的結構與電子密度的關係的圖；

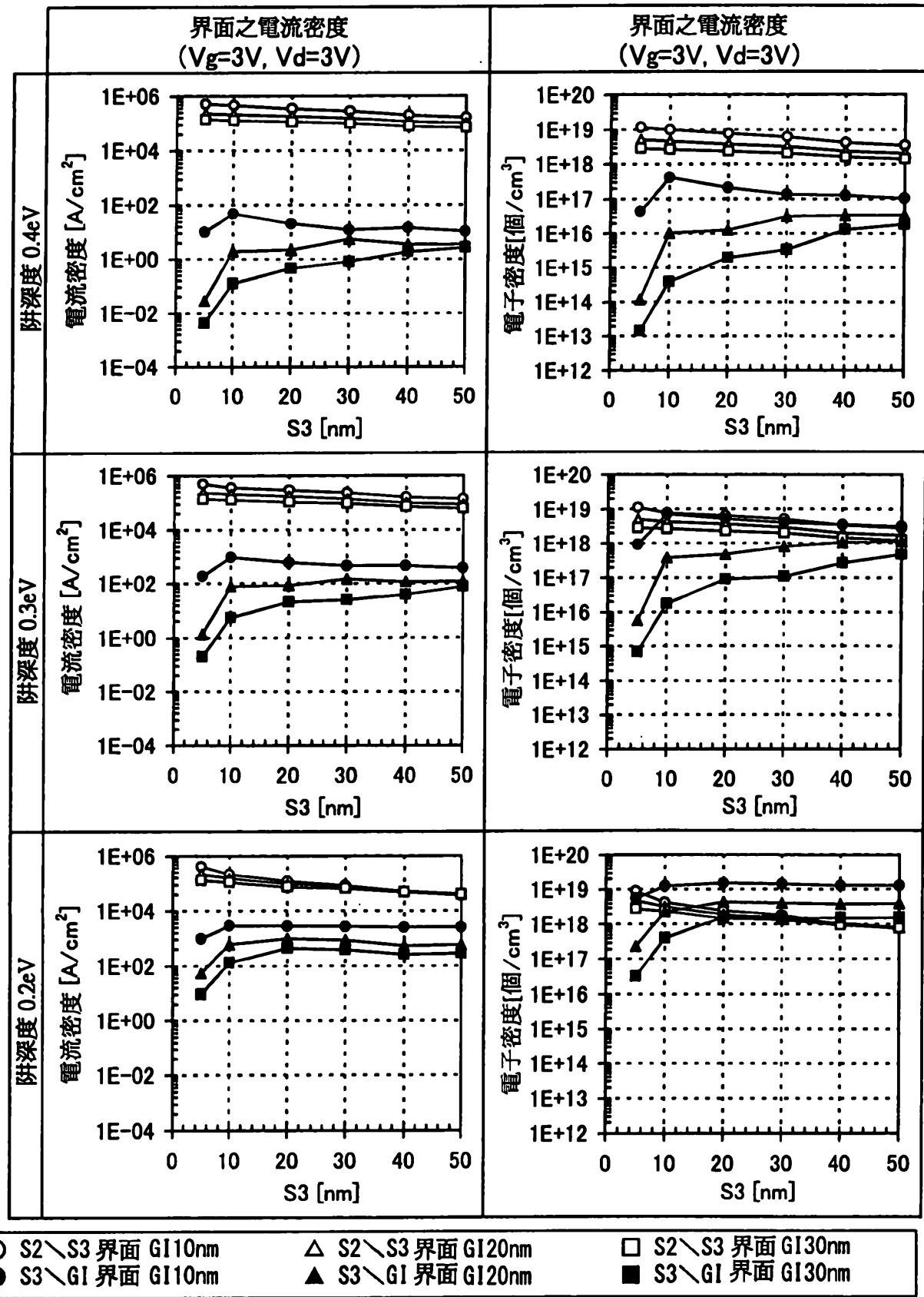

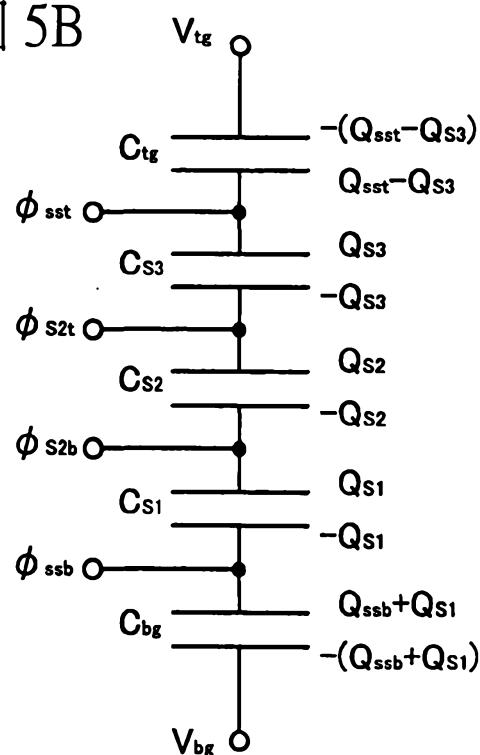

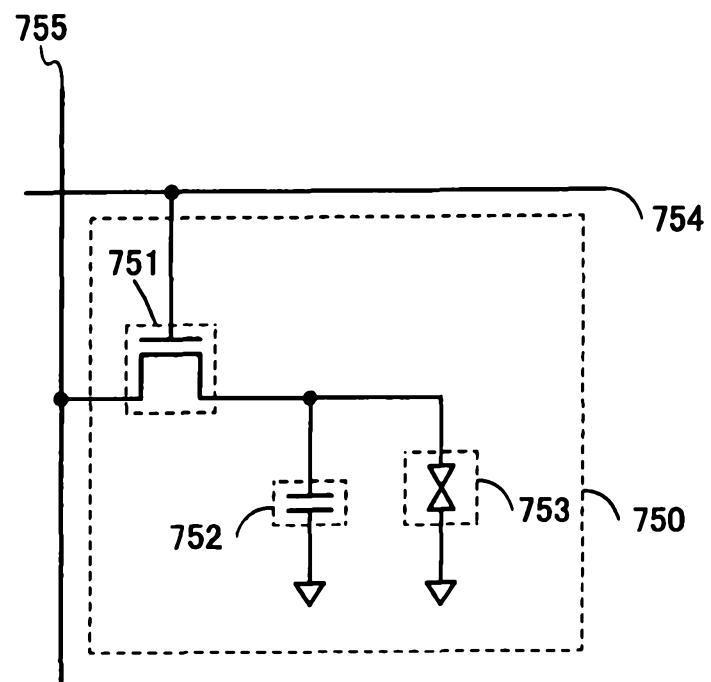

圖 5A 和圖 5B 是電晶體的剖面圖以及說明等效電路的圖；

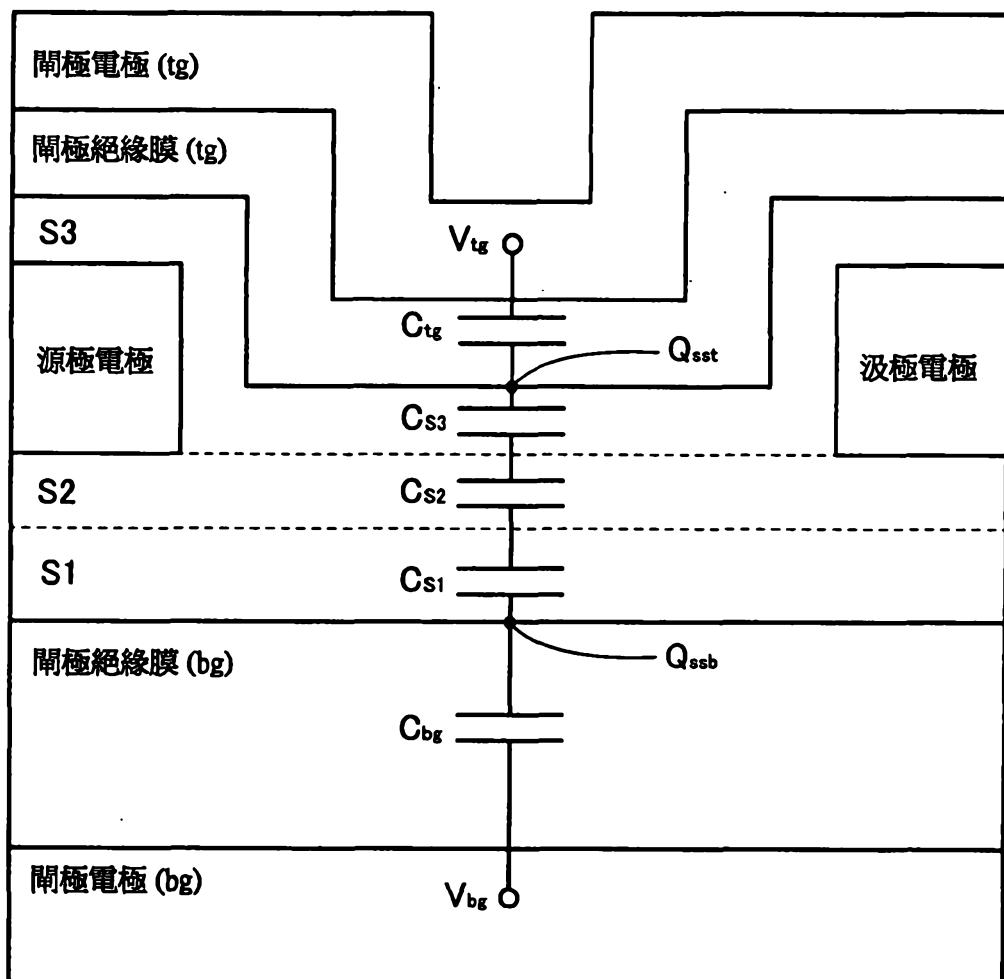

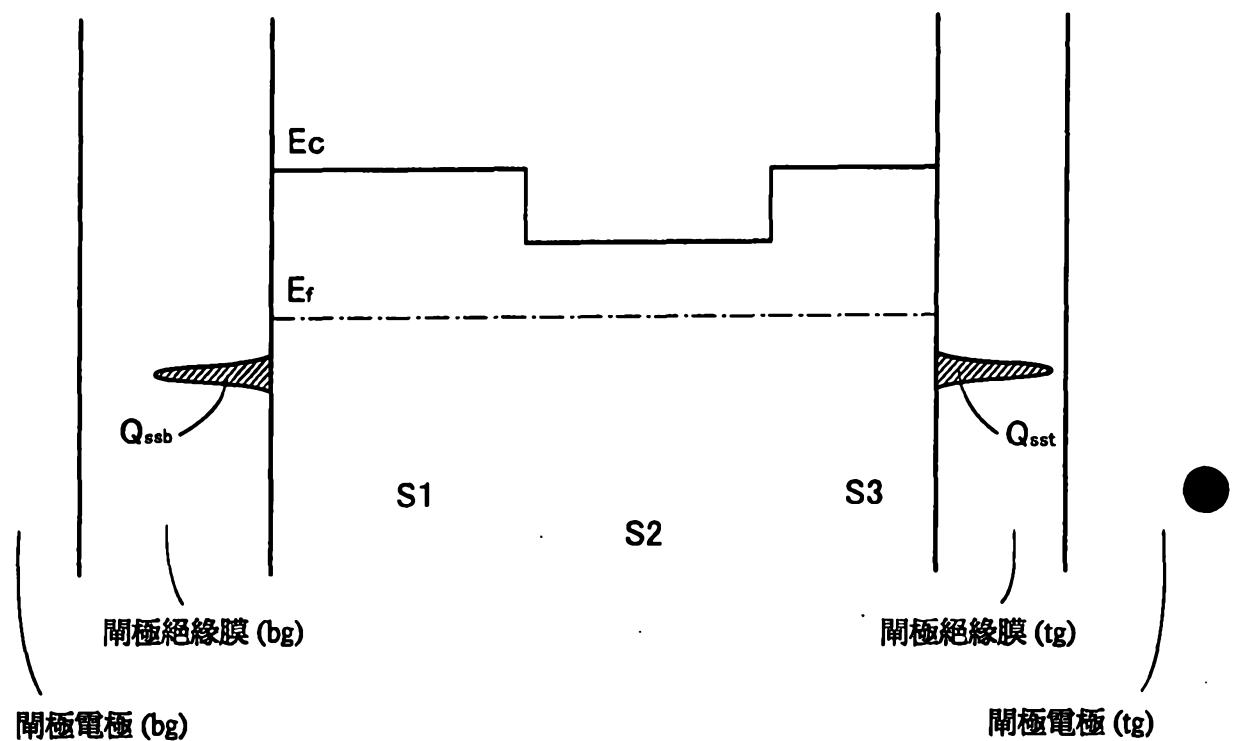

圖 6A 和圖 6B 是說明帶結構的圖；

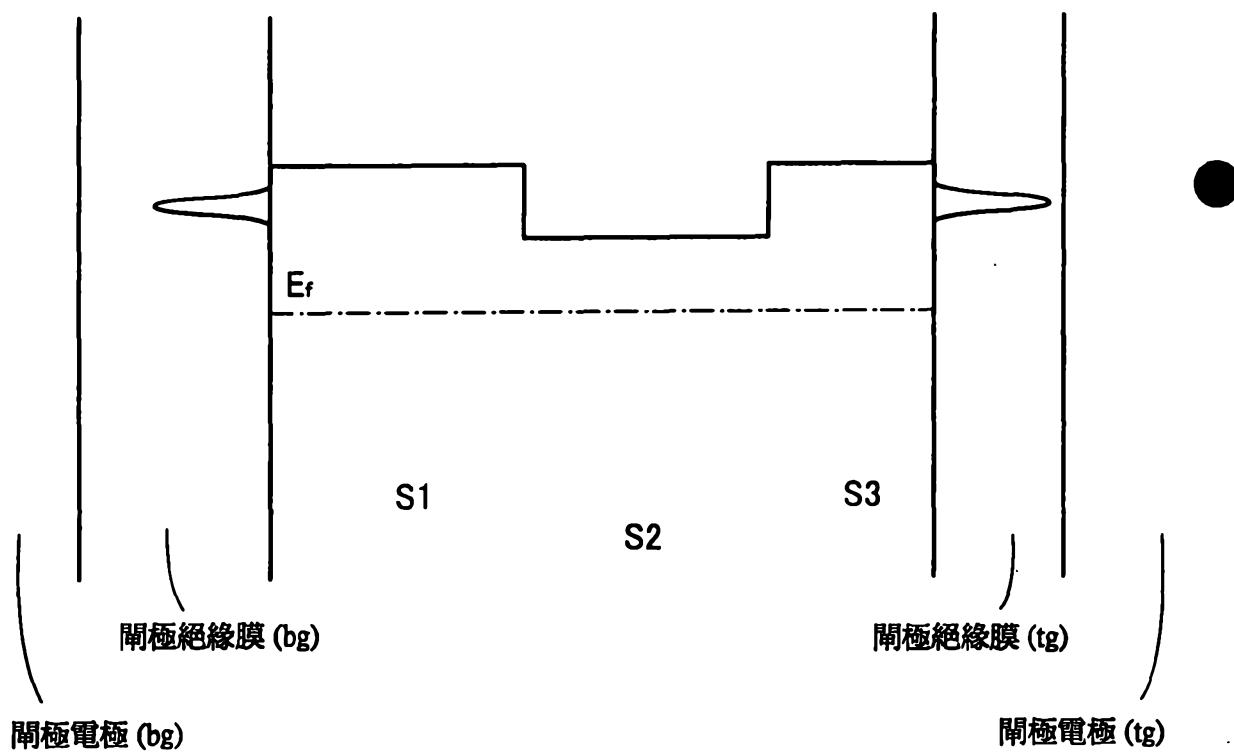

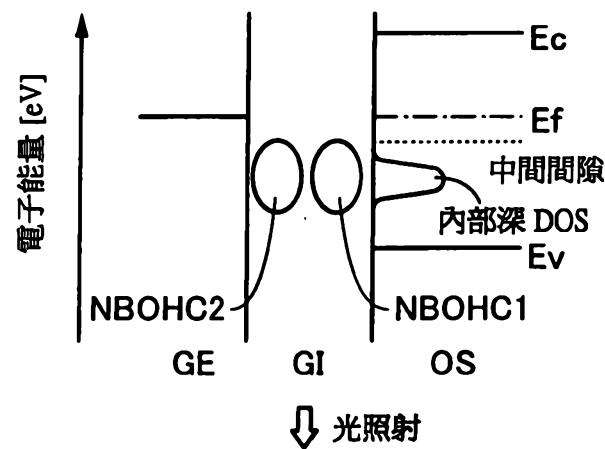

圖 7 是示出氧化物半導體層內部及其介面附近的 DOS 的帶結構；

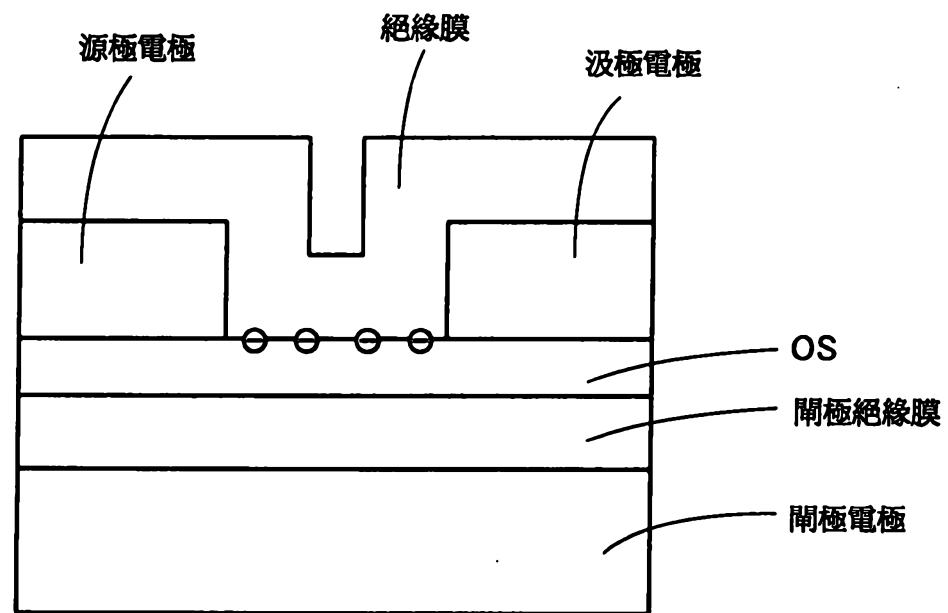

圖 8 是具有氧化物半導體層的電晶體的剖面示意圖；

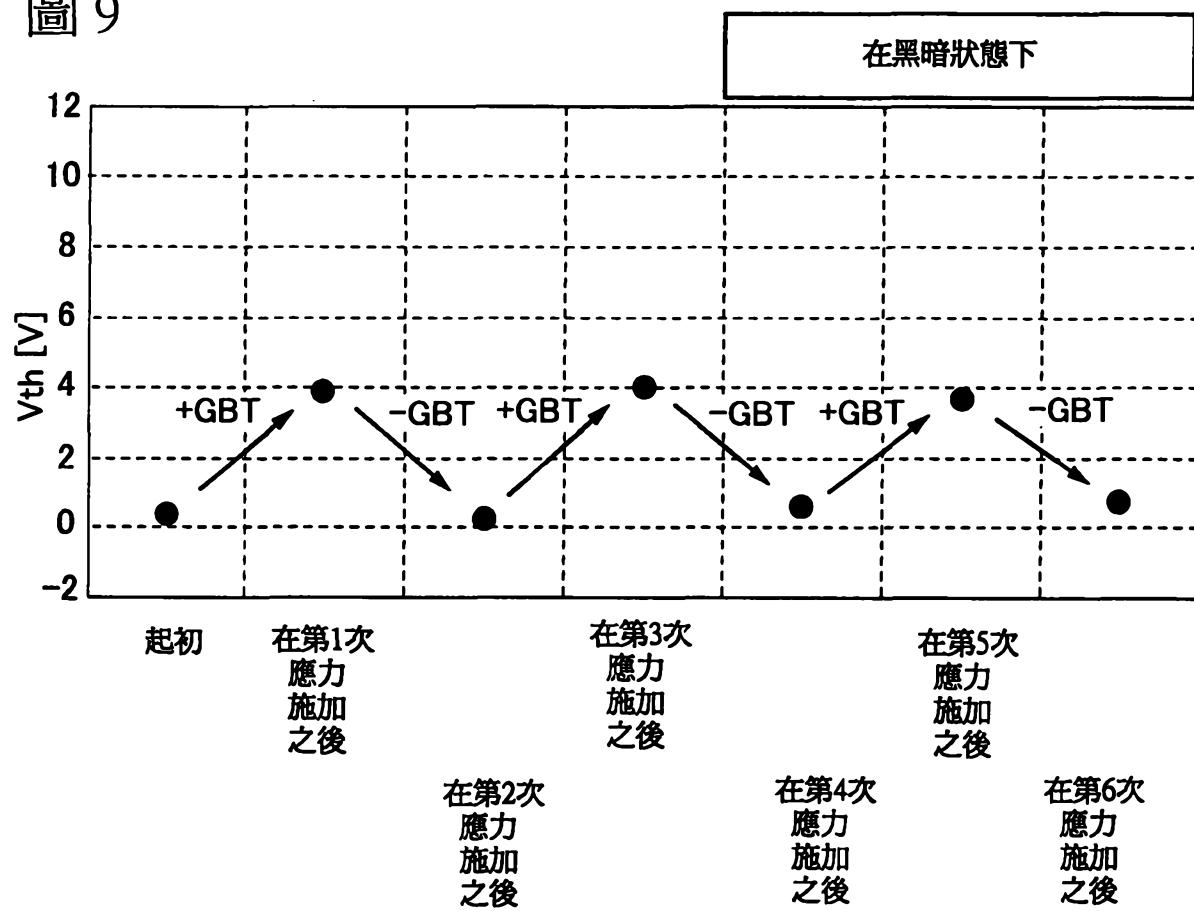

圖 9 是說明具有氧化物半導體層的電晶體的黑暗狀態下的劣化的圖；

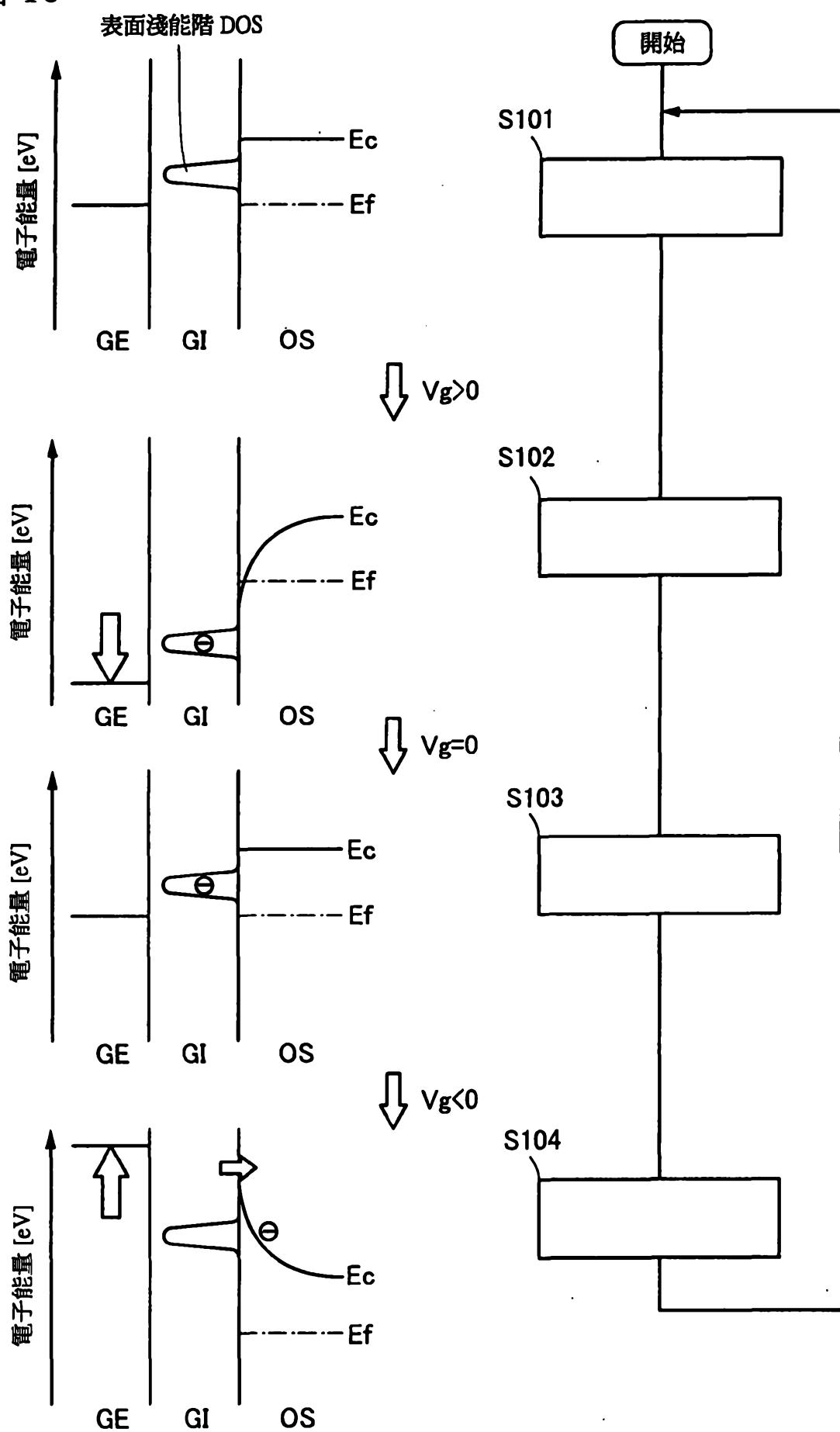

圖 10 是說明具有氧化物半導體層的電晶體的黑暗狀態下的劣化的圖；

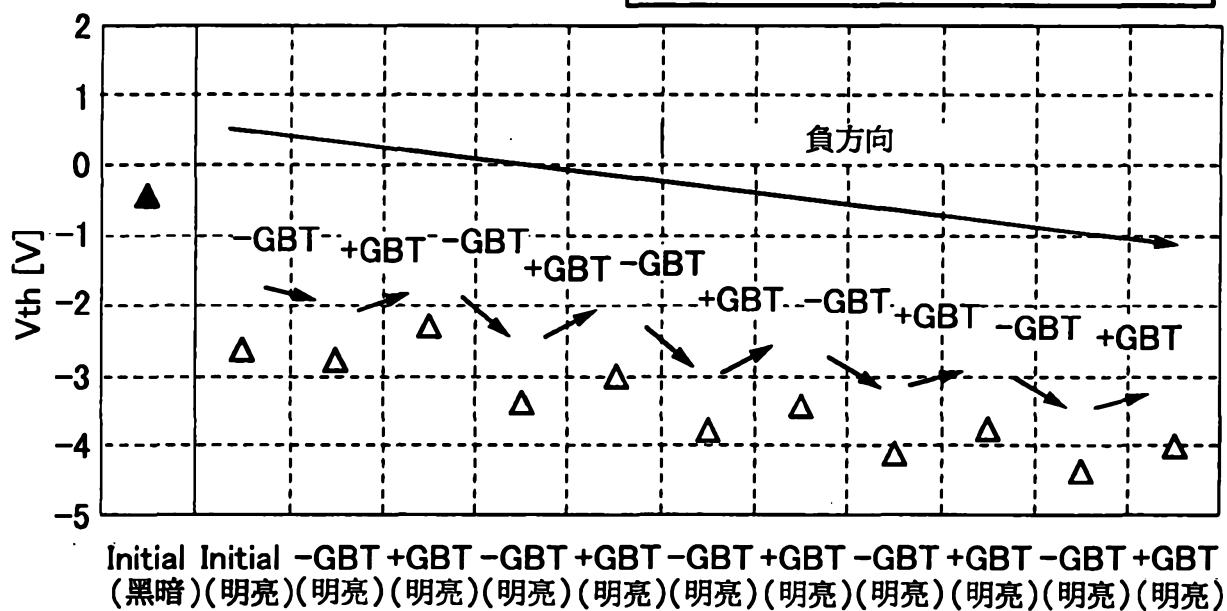

圖 11 是說明具有氧化物半導體層的電晶體的光照射狀態下的劣化的圖；

圖 12 是說明具有氧化物半導體層的電晶體的光照射狀態下的劣化的圖；

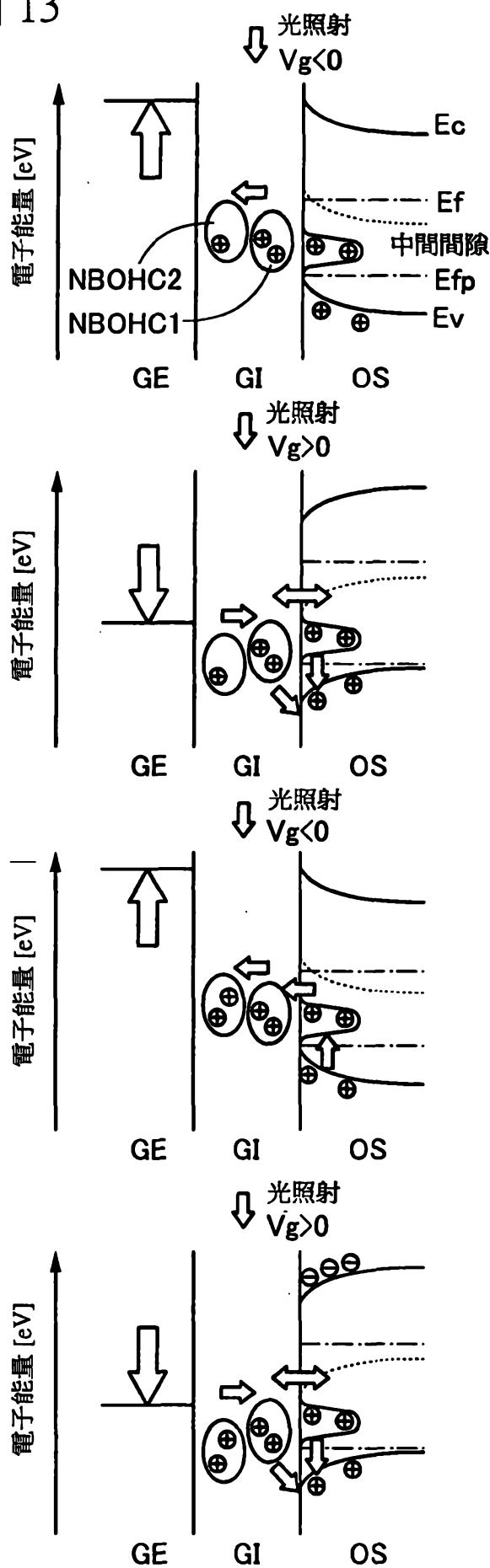

圖 13 是說明具有氧化物半導體層的電晶體的光照射狀態下的劣化的圖；

圖 14A 至圖 14F 是說明氧化物半導體層的高純度本質化的模型圖；

圖 15A 至圖 15C 是示出根據本發明的一個方式的電晶體的一個例子的俯視圖及剖面圖；

圖 16A 至圖 16C 是示出根據本發明的一個方式的電晶體的一個例子的俯視圖及剖面圖；

圖 17A 至圖 17C 是示出根據本發明的一個方式的電晶體的源極電極及汲極電極附近的剖面圖的一個例子的圖；

圖 18A 至圖 18D 是示出根據本發明的一個方式的電晶體的製造方法的一個例子的剖面圖；

圖 19A 至圖 19D 是示出根據本發明的一個方式的電晶體的製造方法的一個例子的剖面圖；

圖 20A 至圖 20C 是示出根據本發明的一個方式的電晶體的一個例子的俯視圖及剖面圖；

圖 21A 至圖 21C 是示出根據本發明的一個方式的電晶體的一個例子的俯視圖及剖面圖；

圖 22A 至圖 22D 是示出根據本發明的一個方式的電晶體的製造方法的一個例子的剖面圖；

圖 23A 至圖 23D 是示出根據本發明的一個方式的電晶體的製造方法的一個例子的剖面圖；

圖 24A 至圖 24D 是示出根據本發明的一個方式的電晶體的一個例子的俯視圖及剖面圖；

圖 25A 至圖 25D 是示出根據本發明的一個方式的電晶體的製造方法的一個例子的剖面圖；

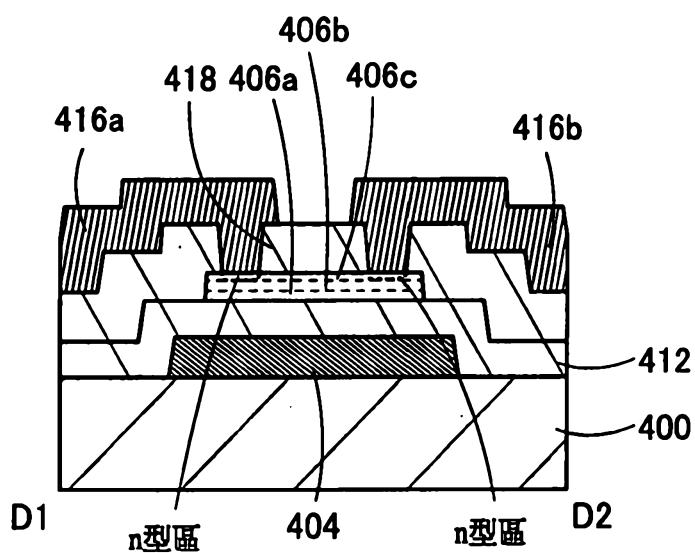

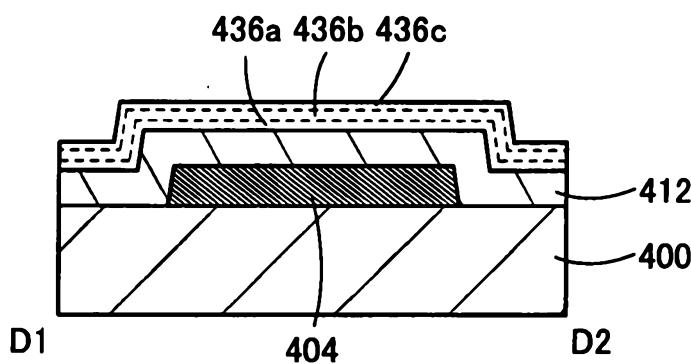

圖 26A 至圖 26C 是示出根據本發明的一個方式的電

晶體的一個例子的俯視圖及剖面圖；

圖 27A 至圖 27D 是示出根據本發明的一個方式的電晶體的製造方法的一個例子的剖面圖；

圖 28 是說明根據本發明的一個方式的多層膜的帶結構的圖；

圖 29A 至圖 29C2 是示出氧化物半導體的奈米電子束繞射圖案的圖；

圖 30 是示出利用 CPM 得到的吸收係數的圖；

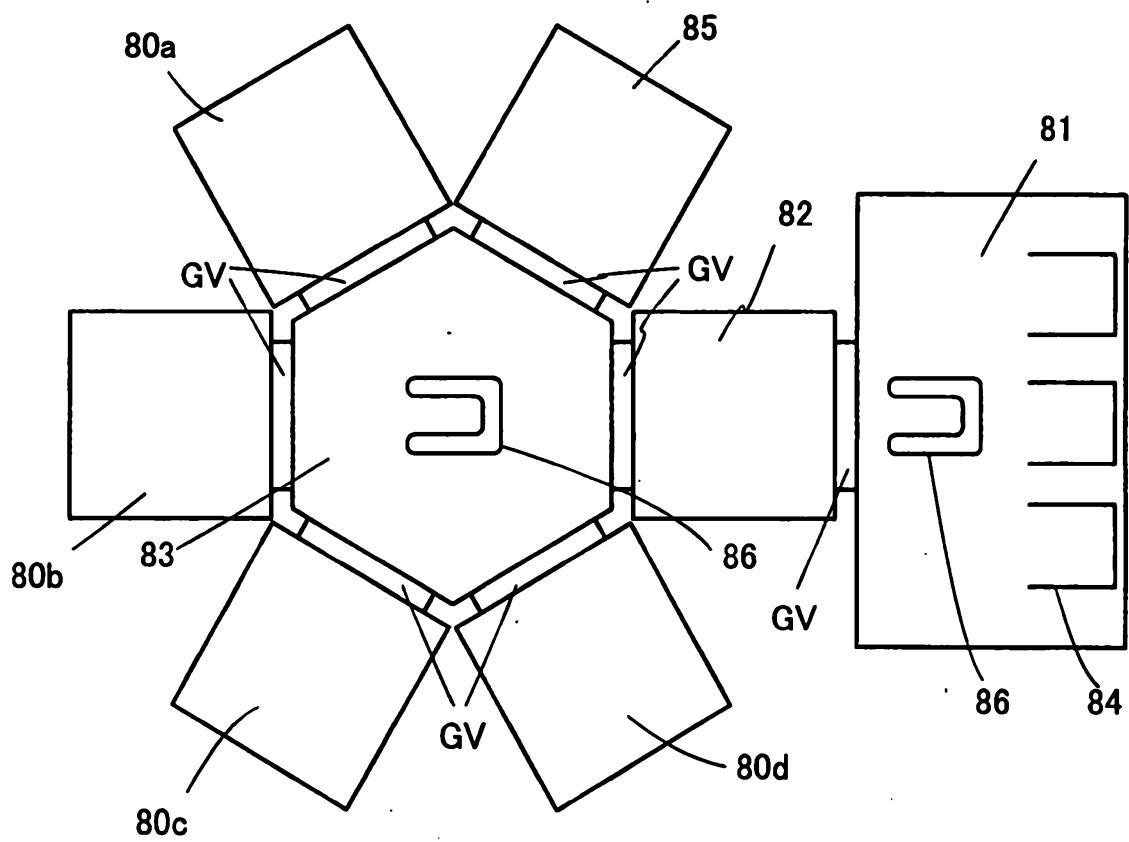

圖 31A 和圖 31B 是示出成膜裝置的一個例子的俯視圖；

圖 32A 和圖 32B 是示出成膜室的一個例子的剖面圖；

圖 33 是示出加熱處理室的一個例子的圖；

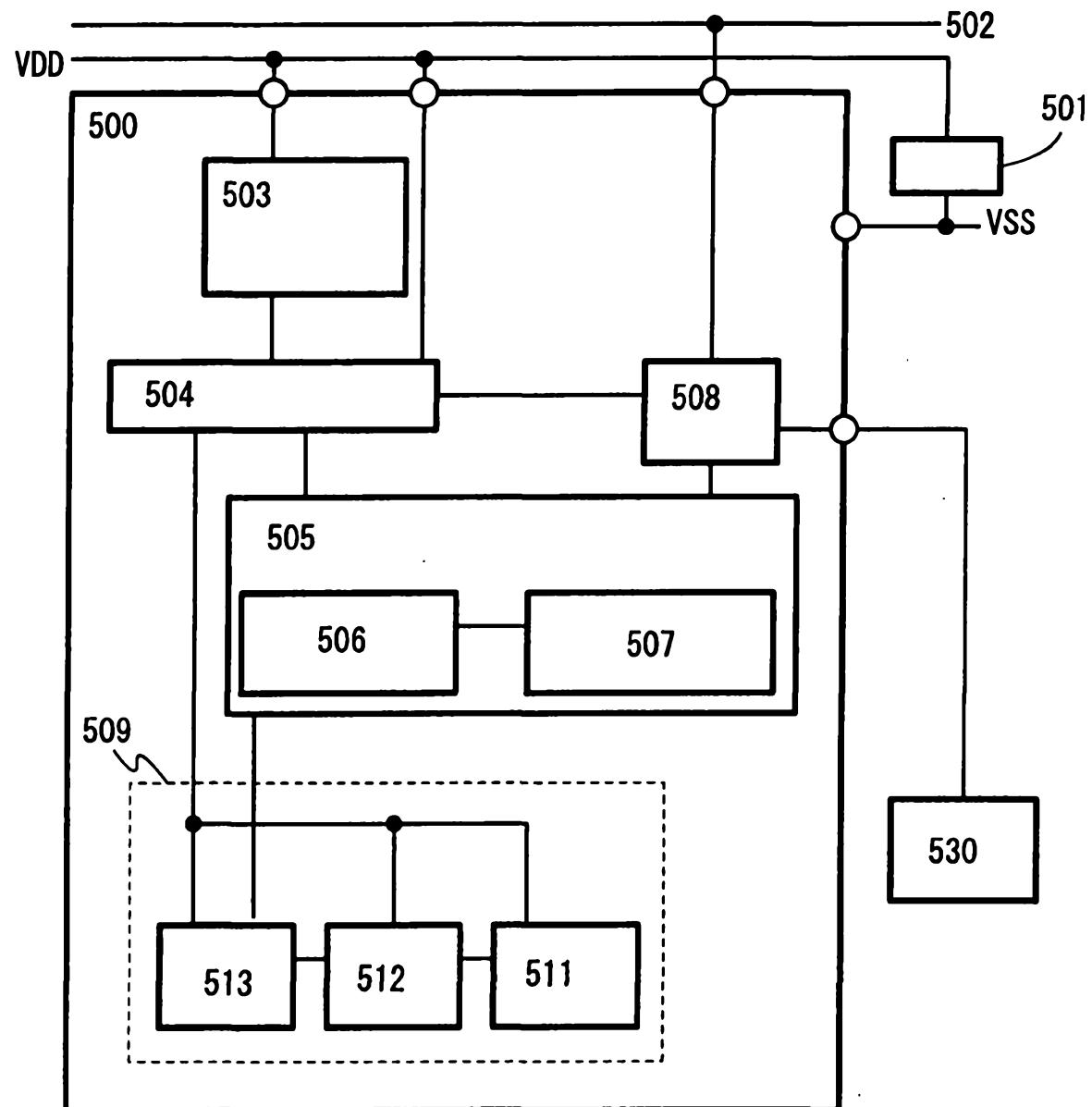

圖 34 是示出根據本發明的一個方式的半導體裝置的一個例子的方塊圖；

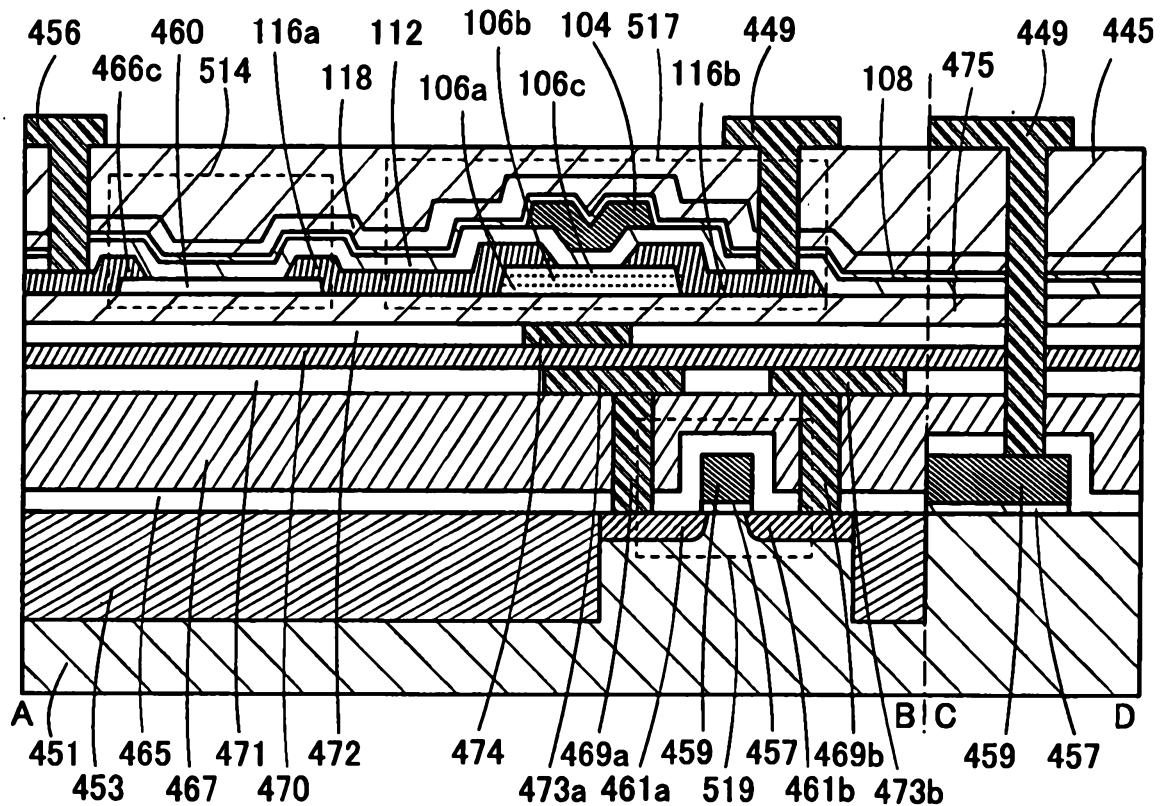

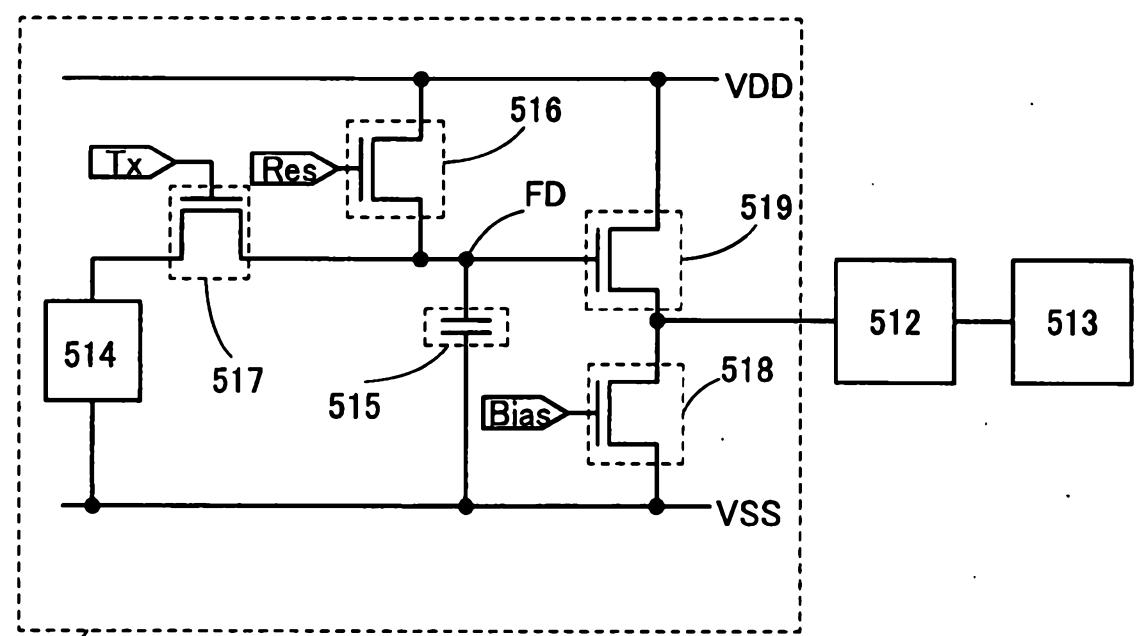

圖 35A 和圖 35B 是示出根據本發明的一個方式的半導體裝置的一個例子的剖面圖及電路圖；

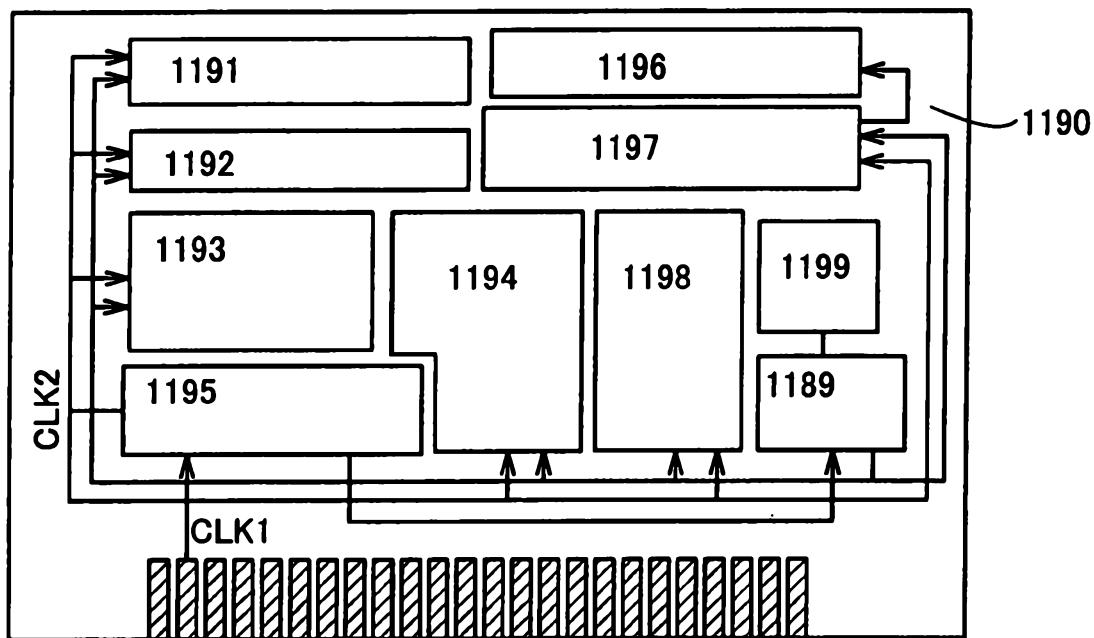

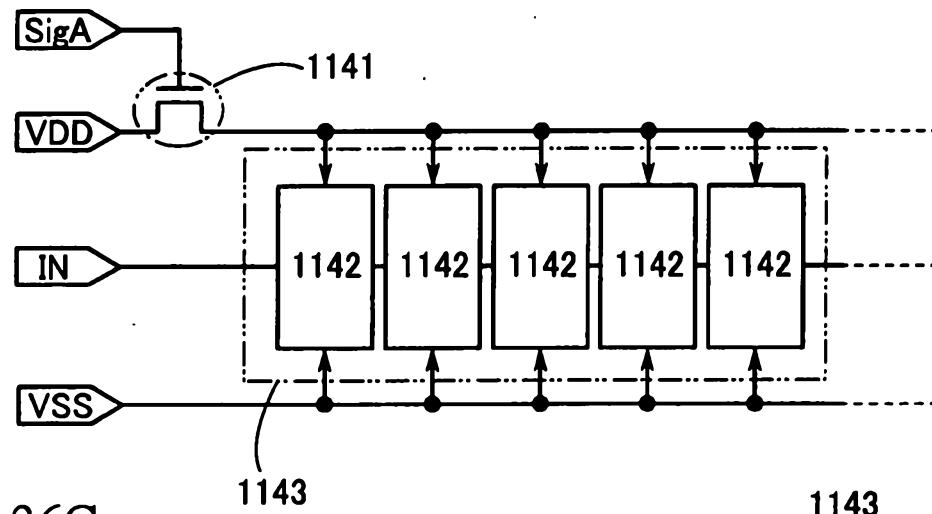

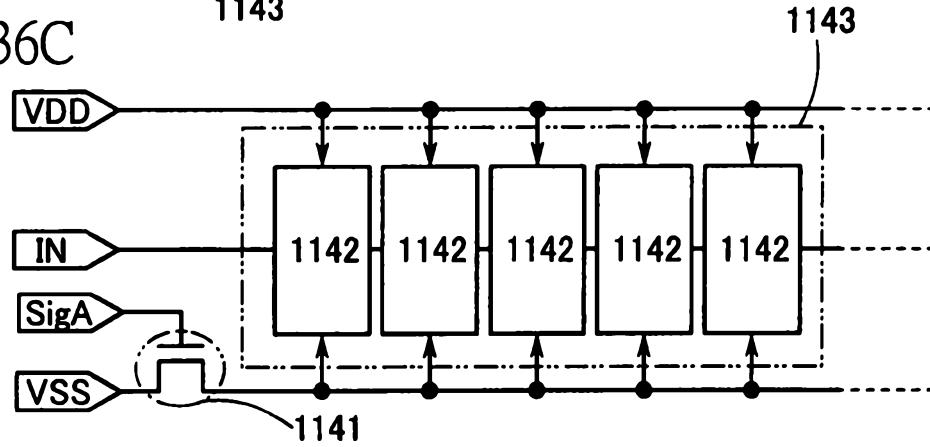

圖 36A 至圖 36C 是示出根據本發明的一個方式的 CPU 的一個例子的方塊圖；

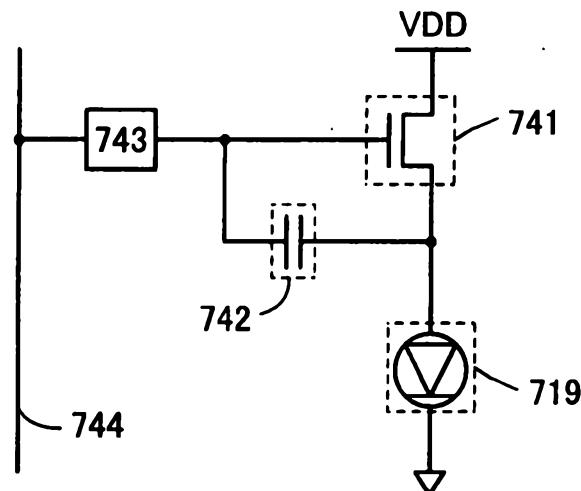

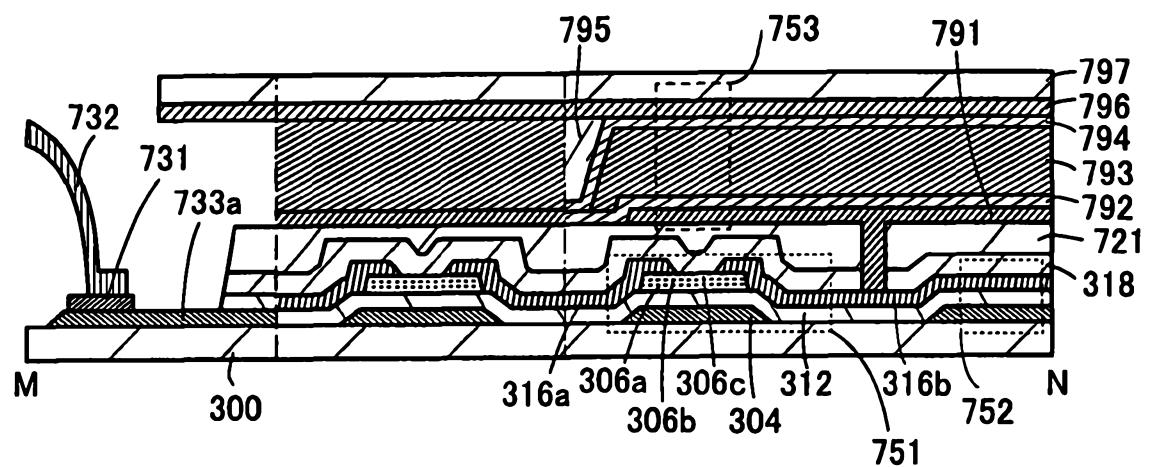

圖 37A 至圖 37C 是示出根據本發明的一個方式的 EL 顯示裝置的電路圖、俯視圖及剖面圖；

圖 38A 和圖 38B 是示出根據本發明的一個方式的液晶顯示裝置的一個例子的電路圖及剖面圖；

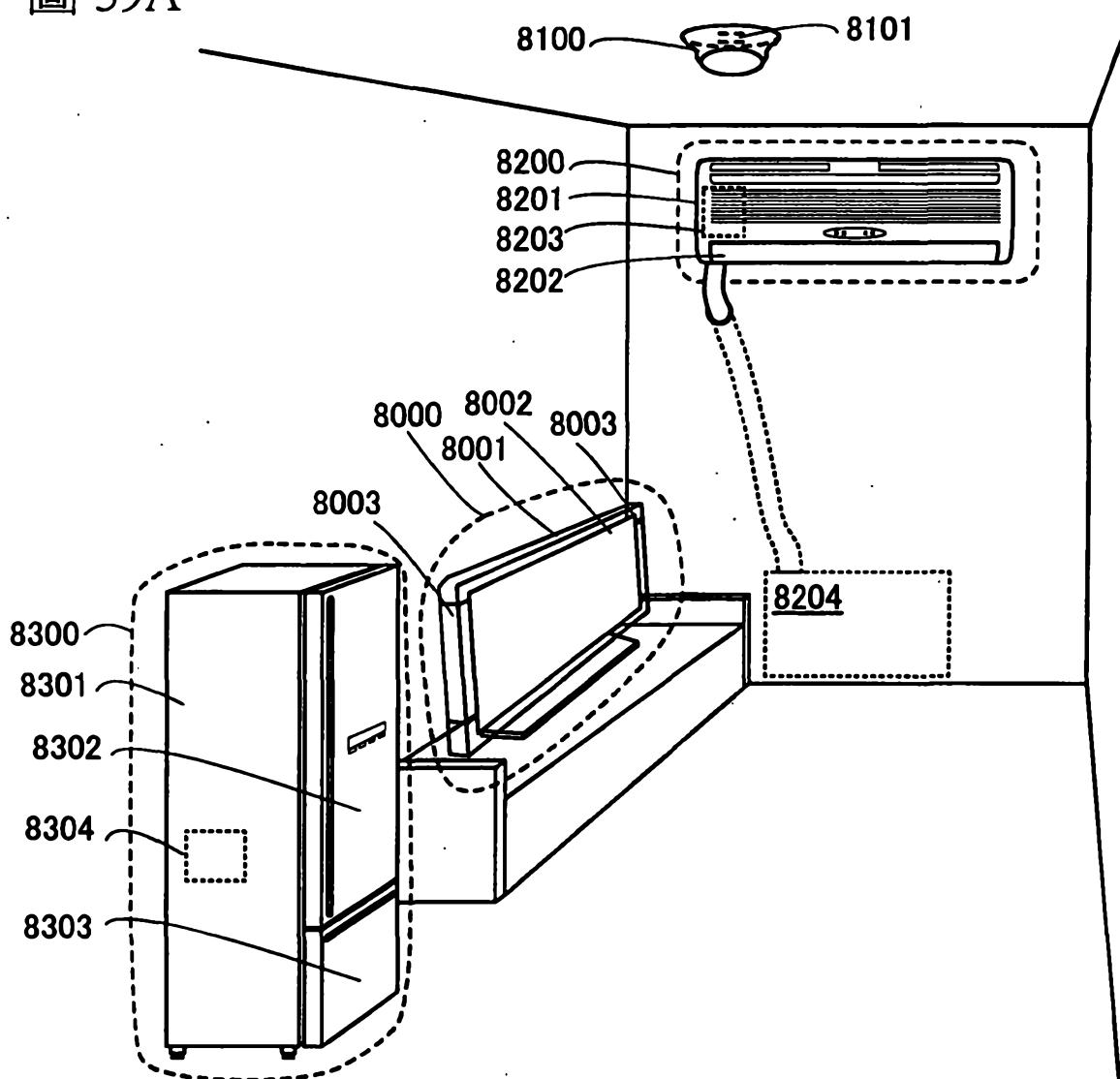

圖 39A 至圖 39C 是示出根據本發明的一個方式的電

子裝置的一個例子的圖；

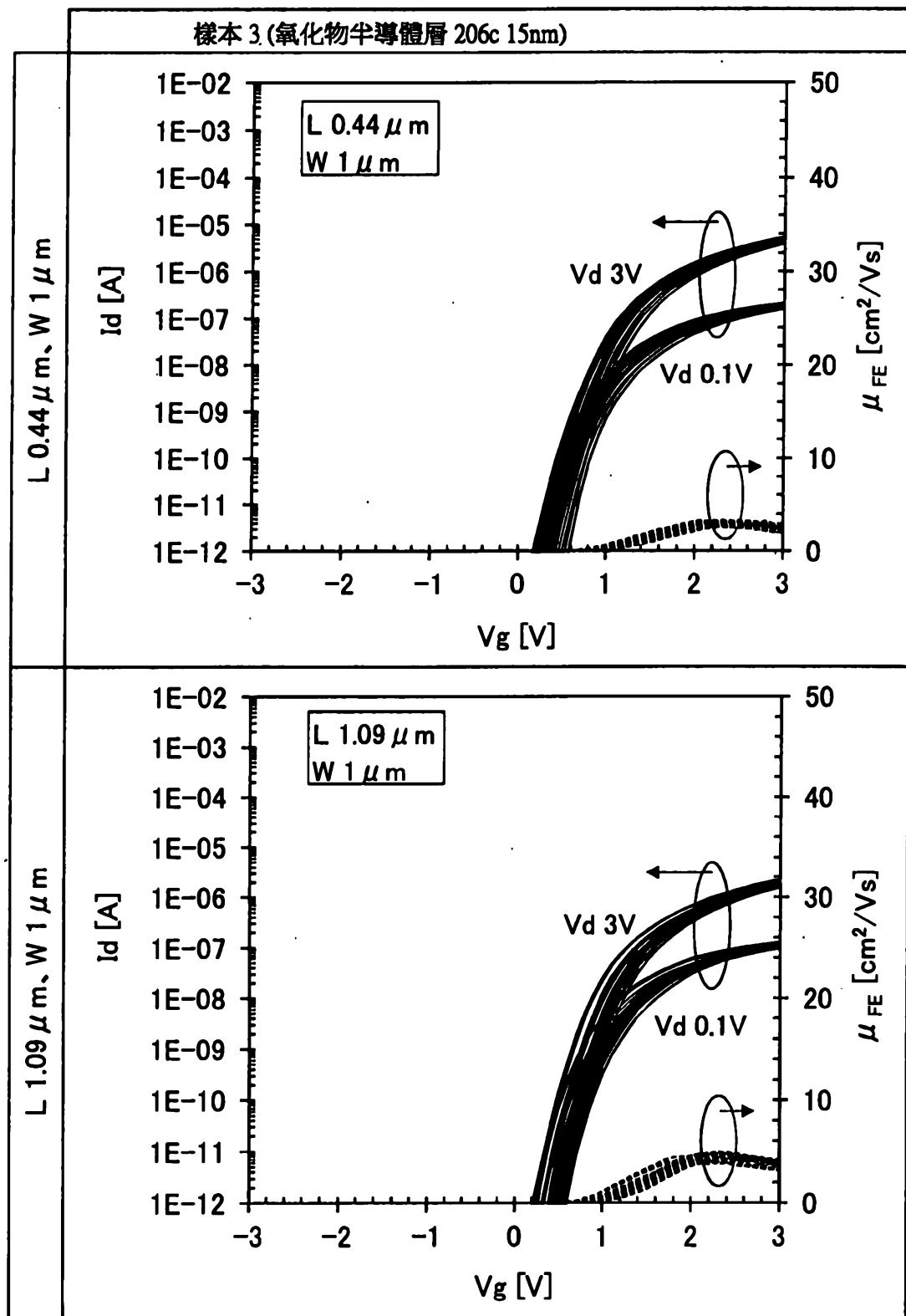

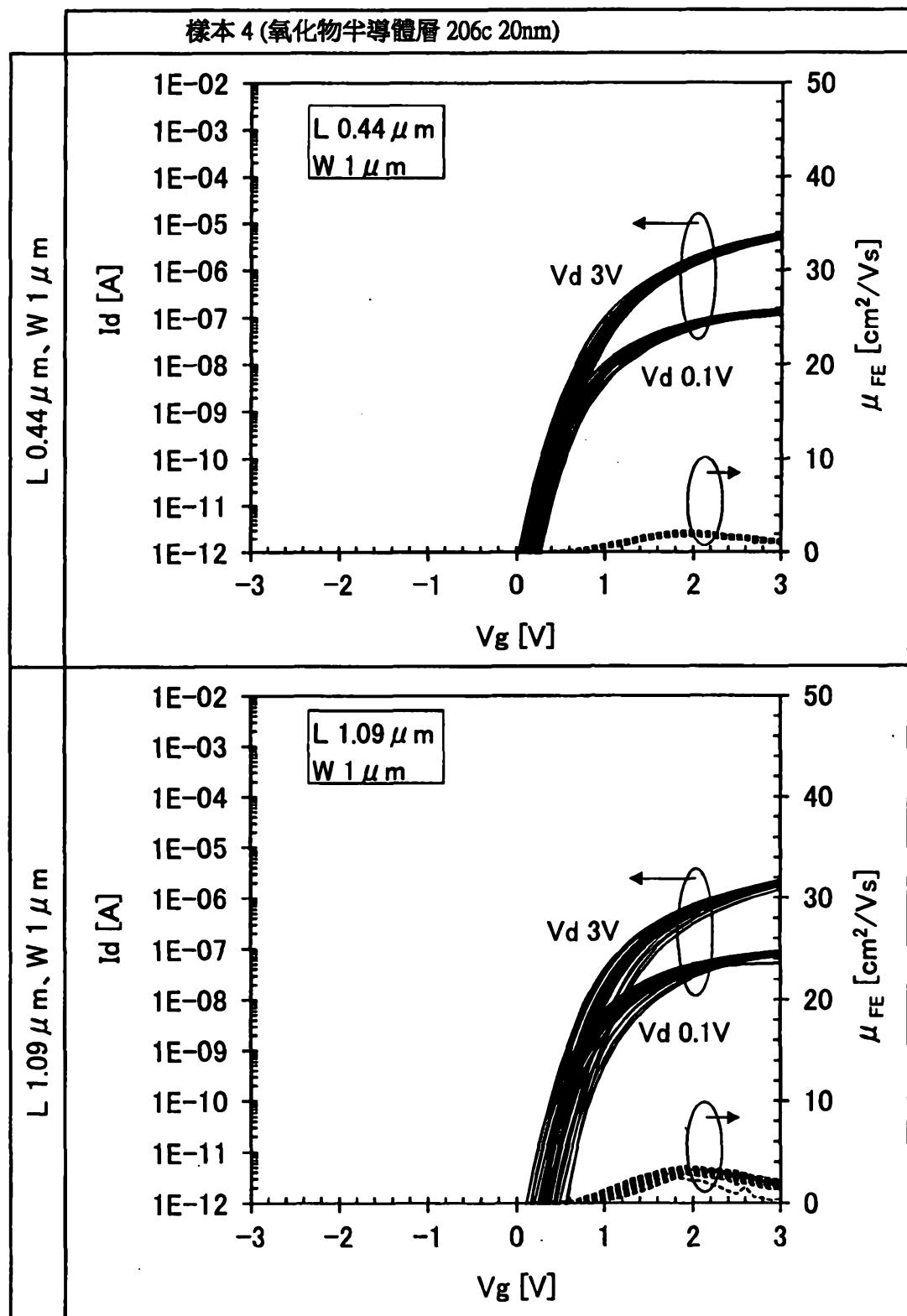

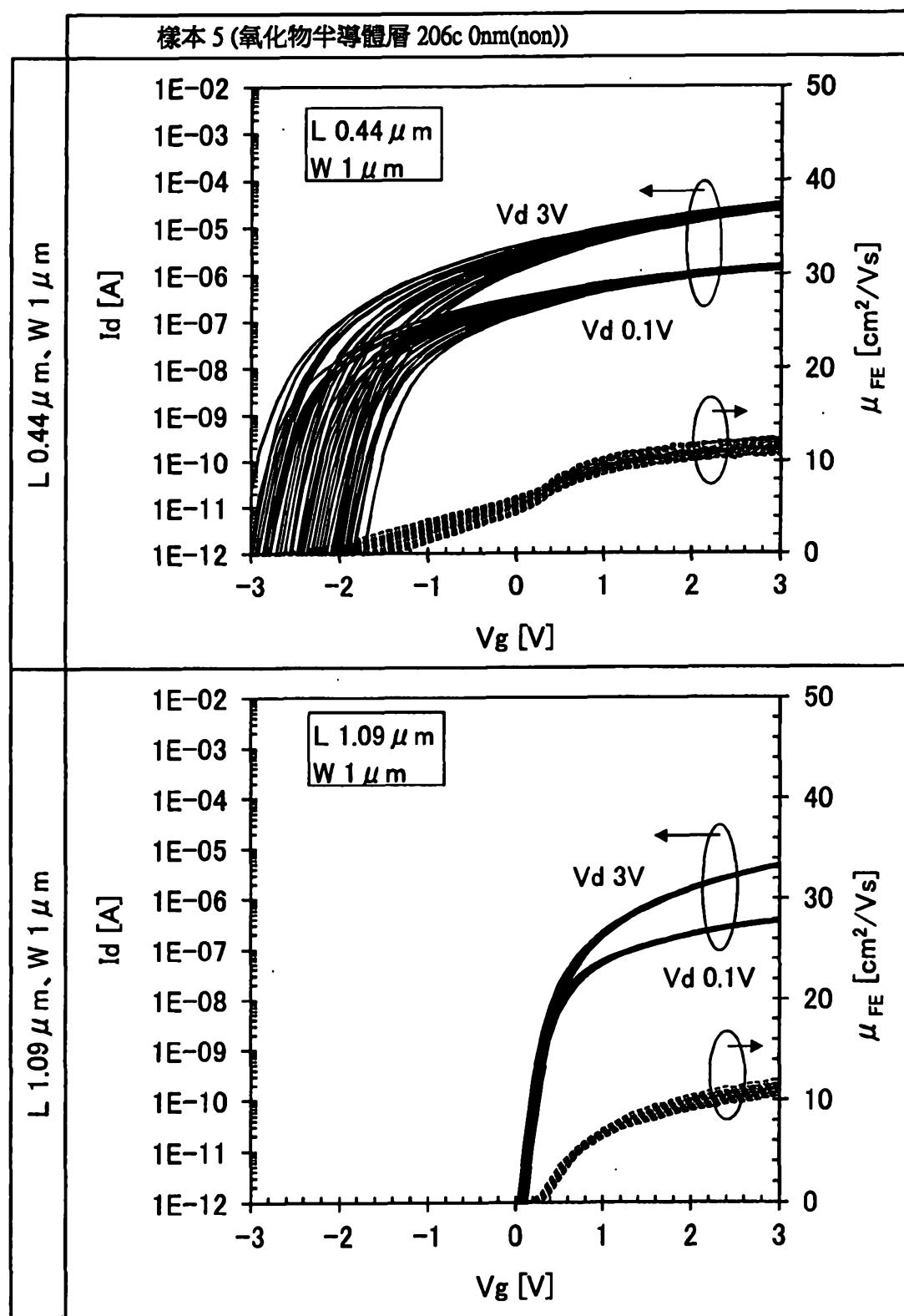

圖 40 是示出電晶體的電特性的圖；

圖 41 是示出電晶體的電特性的圖；

圖 42 是示出電晶體的電特性的圖；

圖 43 是示出電晶體的電特性的圖；

圖 44 是示出電晶體的電特性的圖；

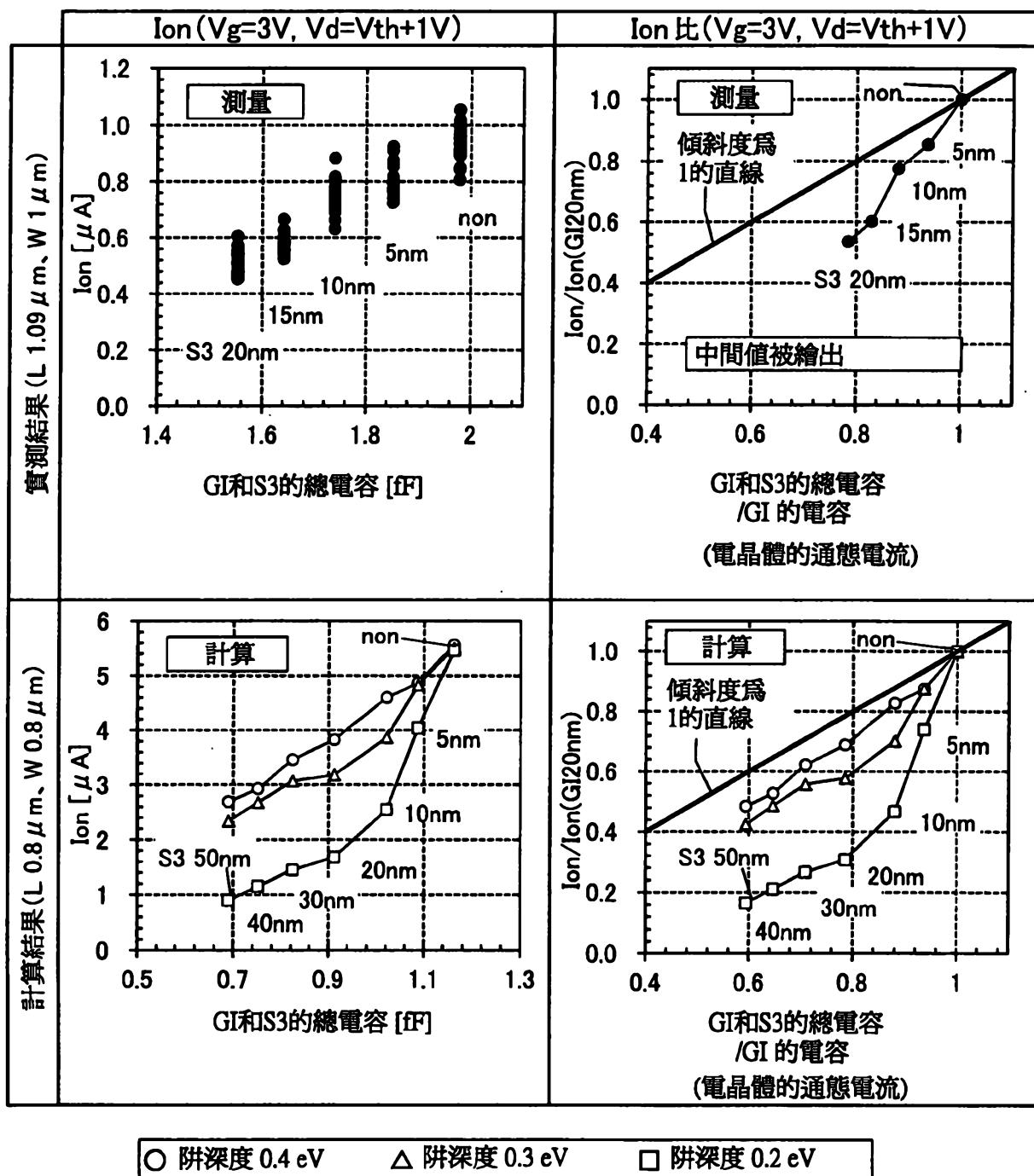

圖 45 是示出電晶體的電特性的實測結果與計算結果的比較的圖；

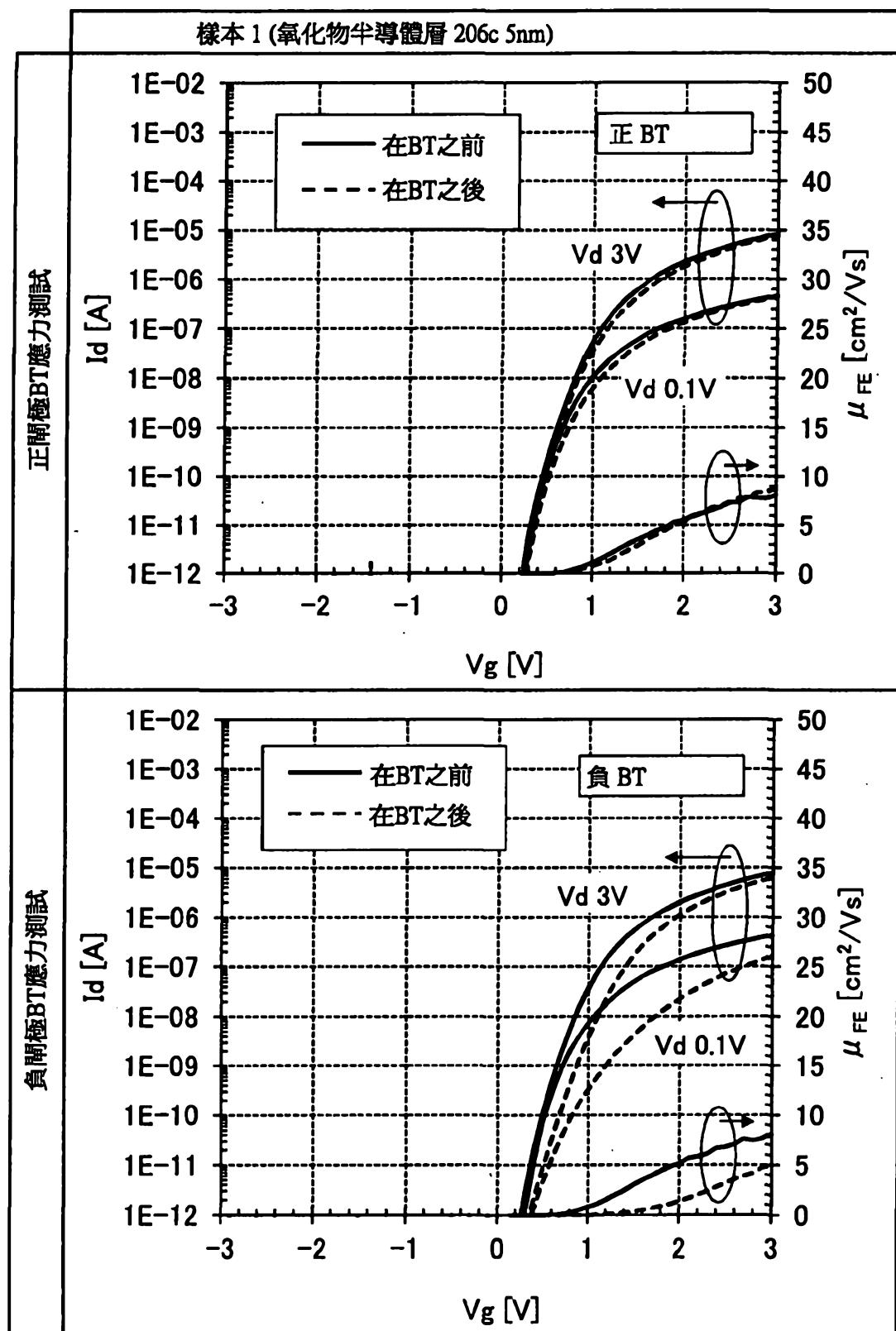

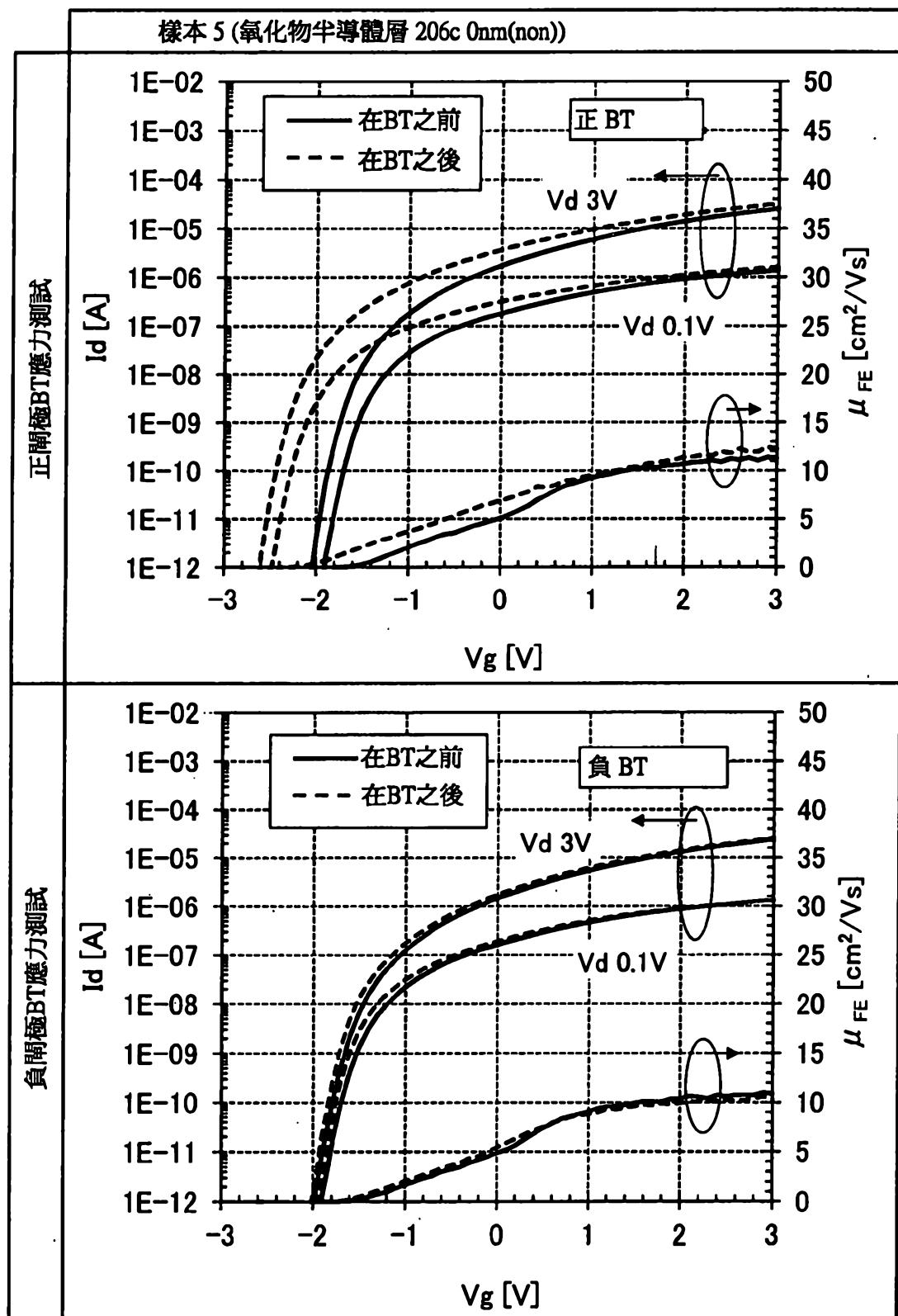

圖 46 是示出電晶體的閘極 BT 應力測試前後的電特性的圖；

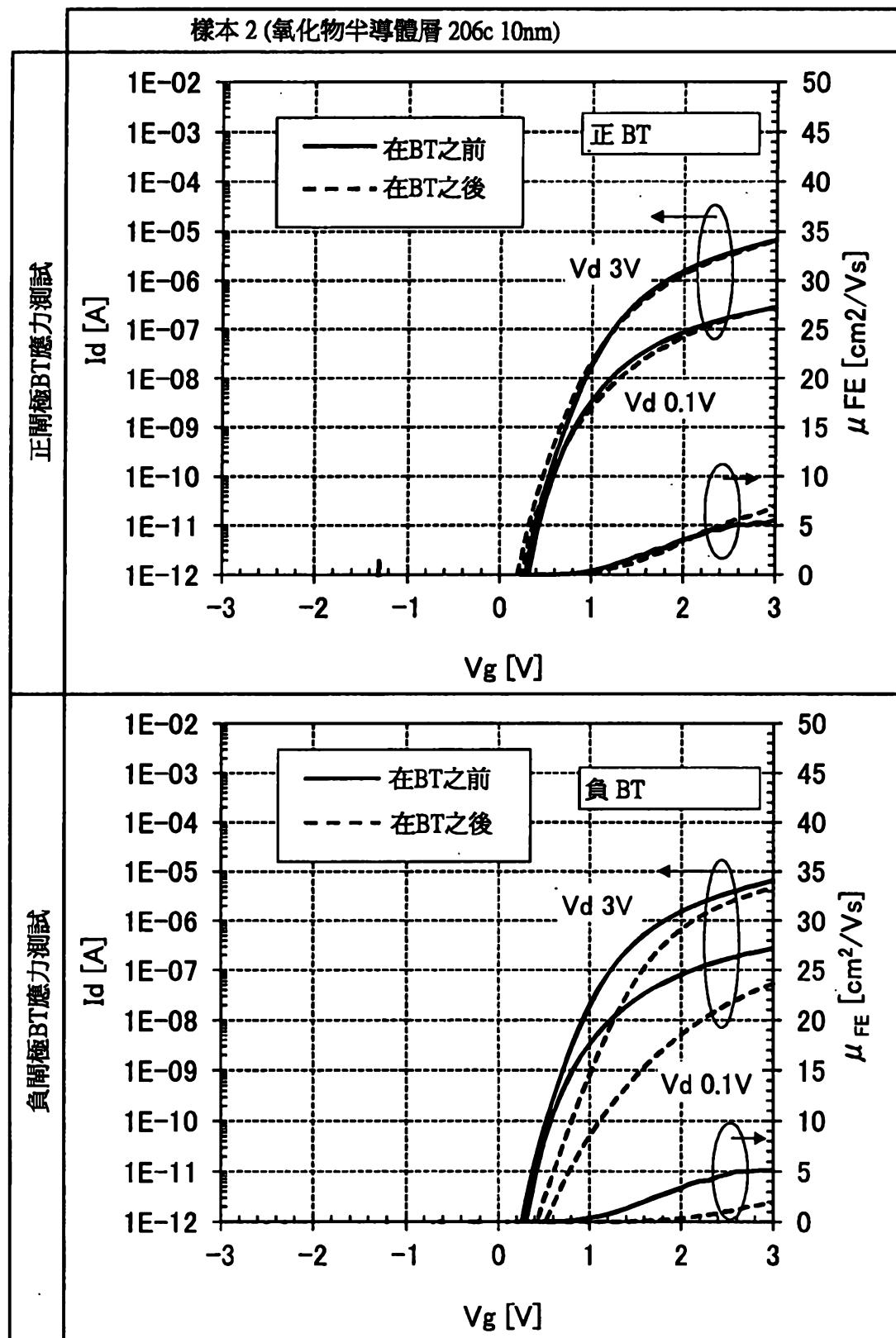

圖 47 是示出電晶體的閘極 BT 應力測試前後的電特性的圖；

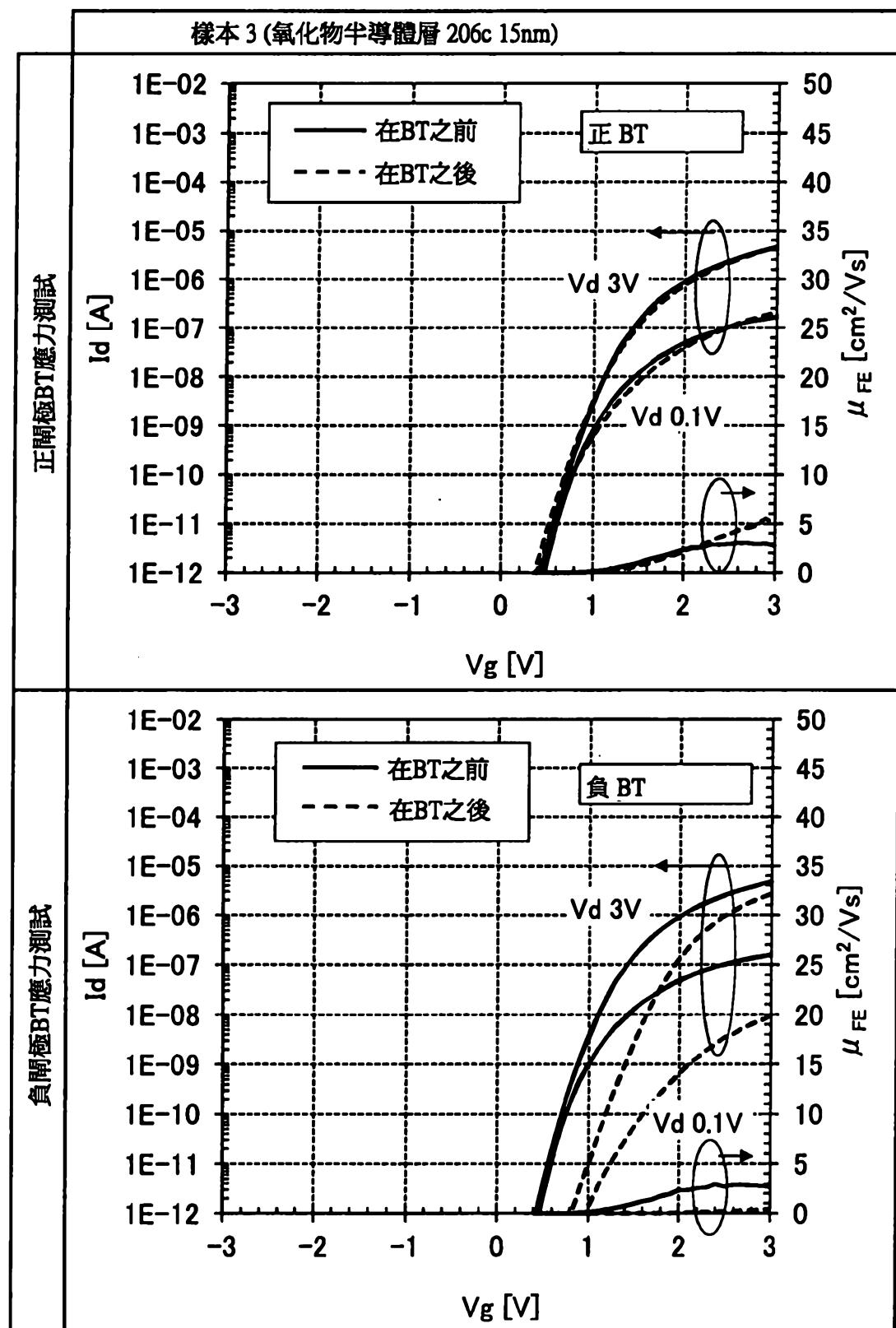

圖 48 是示出電晶體的閘極 BT 應力測試前後的電特性的圖；

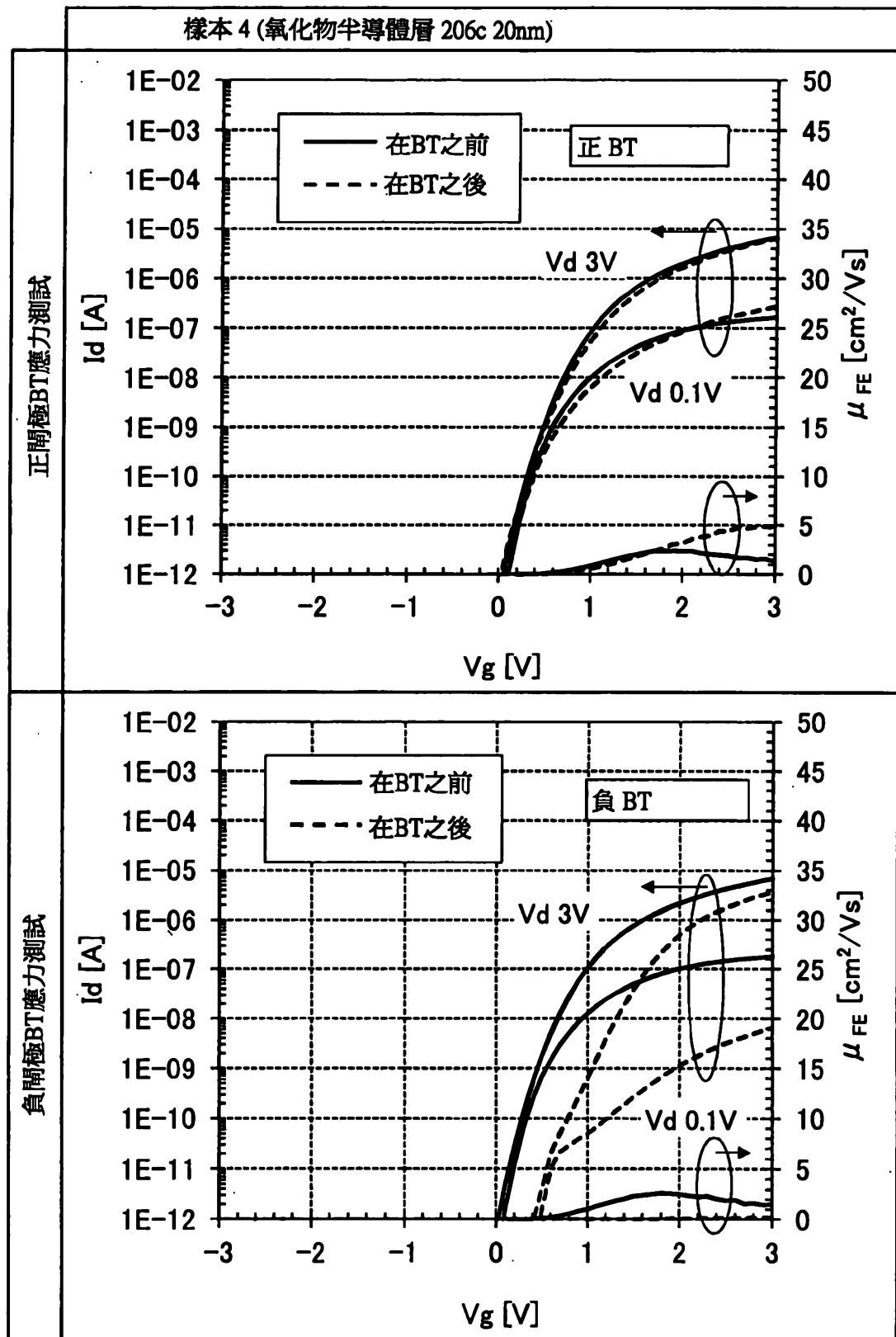

圖 49 是示出電晶體的閘極 BT 應力測試前後的電特性的圖；

圖 50 是示出電晶體的閘極 BT 應力測試前後的電特性的圖。

## 【實施方式】

[0021] 參照圖式對本發明的實施方式進行詳細說明。但是，本發明不侷限於以下說明，所屬技術領域的普通技術人員可以很容易地理解一個事實，就是本發明的方式和詳細內容可以被變換為各種各樣的形式。此外，本發

明不應該被解釋為僅限定在以下所示的實施方式所記載的內容中。注意，當利用圖式說明發明結構時，表示相同目標的元件符號在不同的圖式中共同使用。另外，有時使用相同的陰影圖案表示相同的部分，而不特別附加標記。

[0022] 此外，在某一個實施方式中說明的內容（也可以是其一部分的內容）對於在該實施方式中說明的其他內容（也可以是其一部分的內容）可以進行應用、組合或置換等。

[0023] 注意，在圖式中，大小、厚度或區域有時為了明確起見而被誇大。因此，本發明的一個方式並不限於圖式中的尺寸。

[0024] 注意，圖式是示意性地示出理想例子的，因此，本發明的一個方式不侷限於圖式所示的形狀或值等。例如，可以包括製造技術所引起的形狀偏差、誤差所引起的形狀偏差、雜訊所引起的信號、電壓或電流的偏差、時序差所引起的信號、電壓或電流的偏差等。

[0025] 注意，“電壓”大多是指某個電位與標準電位（例如，接地電位（GND）或源電位）之間的電位差。由此，可以將電壓換稱為電位。

[0026] 在本說明書中，即使記載為“電連接”時，有時在現實的電路中沒有物理連接的部分而只是佈線延伸。

[0027] 注意，為方便起見，附加了第一、第二等序數詞，而其並不表示製程順序或疊層順序。此外，本說明

書中的序數不表示用來特定發明的事項的固有名稱。

[0028] 在本說明書中，例如，當使用“直徑”、“粒徑”、“大小”、“尺寸”、“寬度”等規定物體的形狀時，也可以將其換稱為容納物體的最小立方體的一邊的長度或者物體的一個剖面的圓等效直徑。物體的一個剖面的圓等效直徑是指等於物體的一個剖面的面積的正圓形的直徑。

[0029] 注意，即使記載為“半導體”時，例如，當導電性充分低時，也有時具有作為“絕緣體”的特性。此外，有時“半導體”與“絕緣體”之間的界限模糊，不能嚴格地區別“半導體”與“絕緣體”。因此，有時可以將在本說明書中記載的“半導體”換稱為“絕緣體”。同樣地，有時可以將在本說明書中記載的“絕緣體”換稱為“半導體”。

[0030] 注意，即使記載為“半導體”時，例如，當導電性充分高時，也有時具有作為“導電體”的特性。此外，有時“半導體”與“導電體”之間的界限模糊，不能嚴格地區別“半導體”與“導電體”。因此，有時可以將在本說明書中記載的“半導體”換稱為“導電體”。同樣地，有時可以將在本說明書中記載的“導電體”換稱為“半導體”。

[0031] 此外，半導體層的雜質例如是指構成半導體層的主要成分以外的元素。例如，濃度小於0.1 atomic%的元素是雜質。由於半導體層包含雜質，而有時導致半導體

層中的 DOS (Density of State: 態密度) 的形成、載子移動率的降低或結晶性的降低等。當半導體層是氧化物半導體層時，作為改變半導體層的特性的雜質，例如有第 1 族元素、第 2 族元素、第 14 族元素、第 15 族元素、主要成分以外的過渡金屬等。尤其是，例如有氫（也包含水）、鋰、鈉、矽、硼、磷、碳、氮等。當採用氧化物半導體時，由於雜質混入，而有可能形成氧缺陷。當半導體層是矽層時，作為改變半導體層的特性的雜質，例如有氧、除了氫以外的第 1 族元素、第 2 族元素、第 13 族元素、第 15 族元素等。

[0032] 在本說明書中，過剩氧例如是指超過化學計量組成的氧。或者，過剩氧例如是指因加熱而釋放的氧。過剩氧例如可以移動在膜或層的內部。過剩氧在膜或層中的原子之間，或者，過剩氧和構成膜或層的氧取代並如撞球那樣移動。此外，包含過剩氧的絕緣膜例如是具有藉由加熱處理釋放氧的功能的絕緣膜。

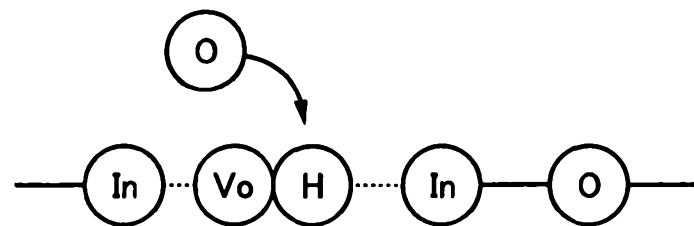

[0033]

〈關於具有多層膜的電晶體的通態電流〉

以下，進行用來確認具有包括氧化物半導體層的多層膜的電晶體的通態電流 (Ion) 與各層的物性或厚度之間的關係的計算。

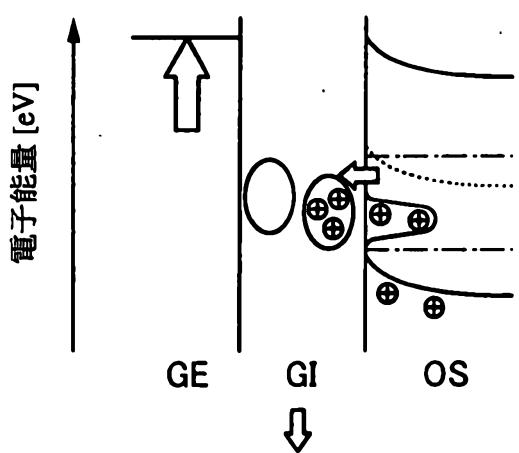

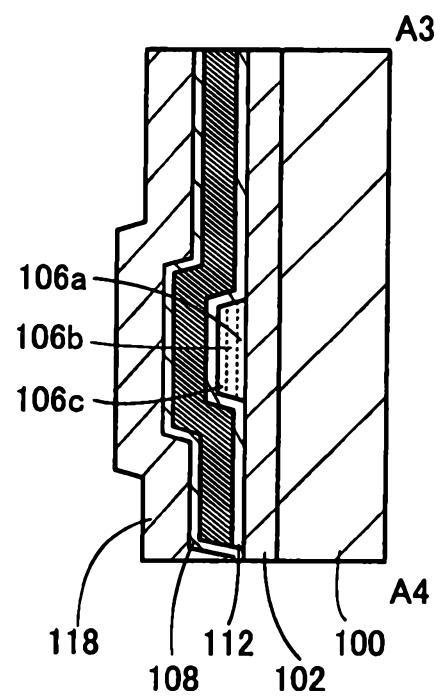

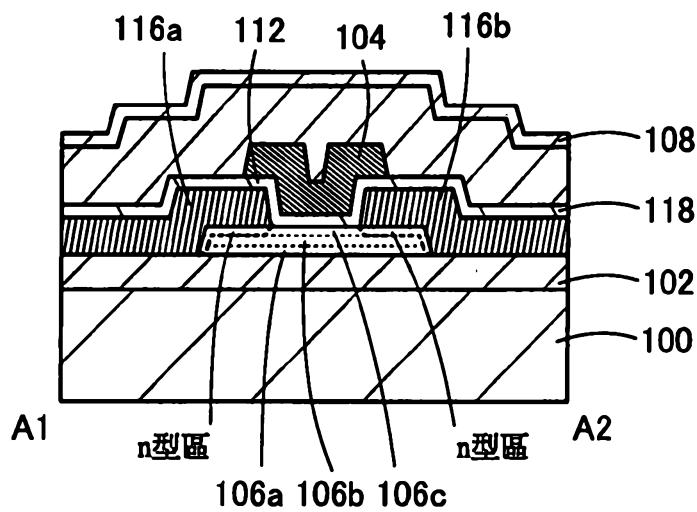

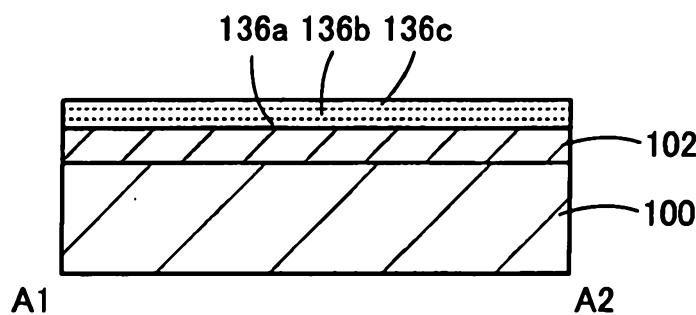

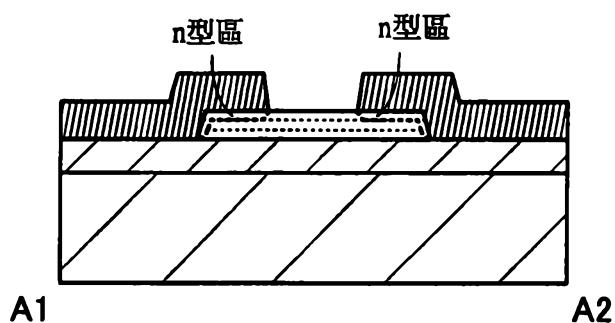

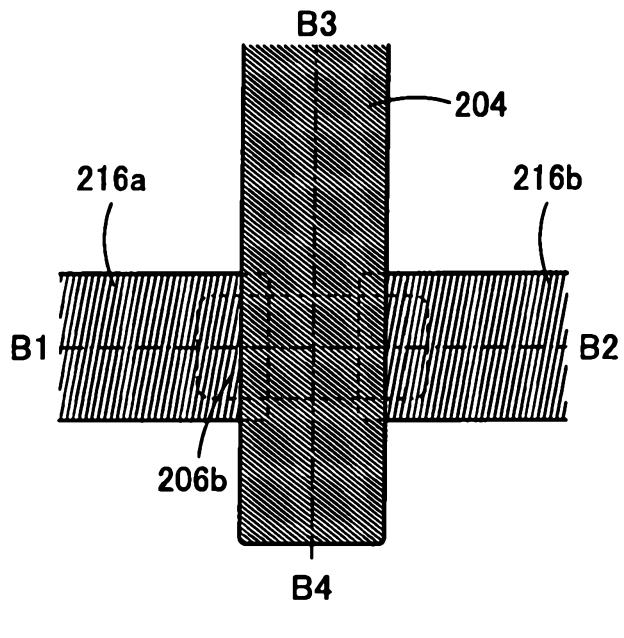

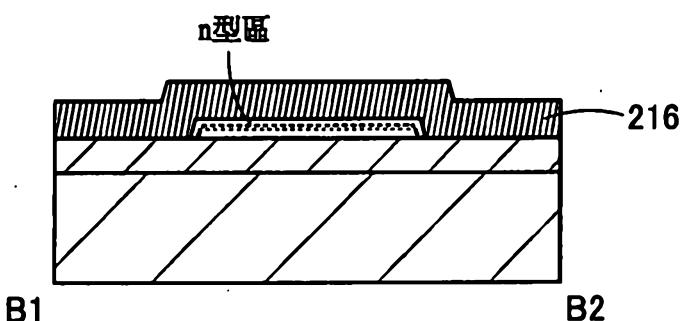

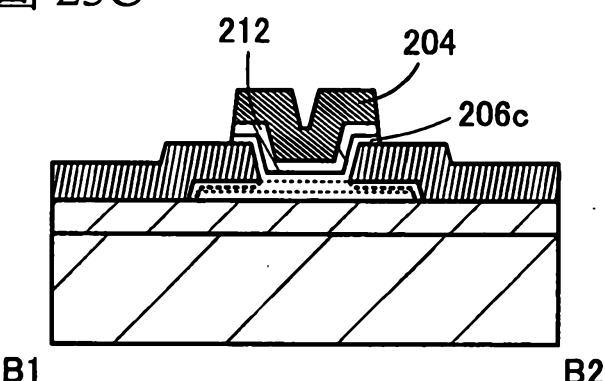

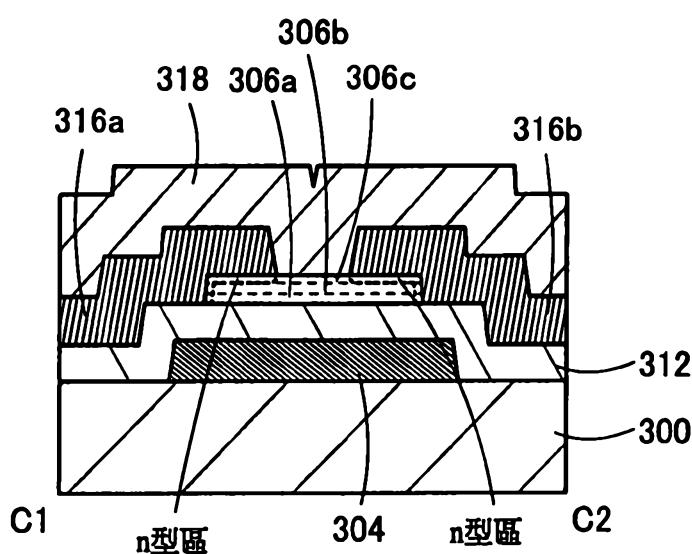

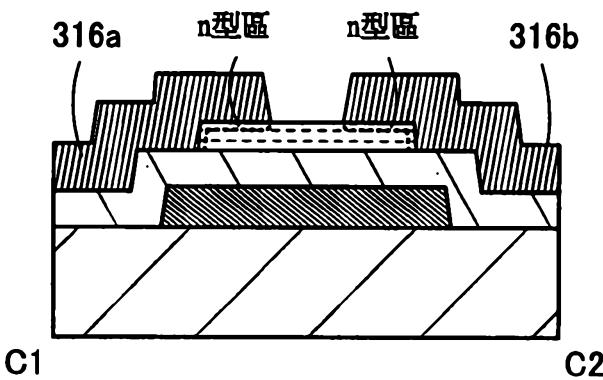

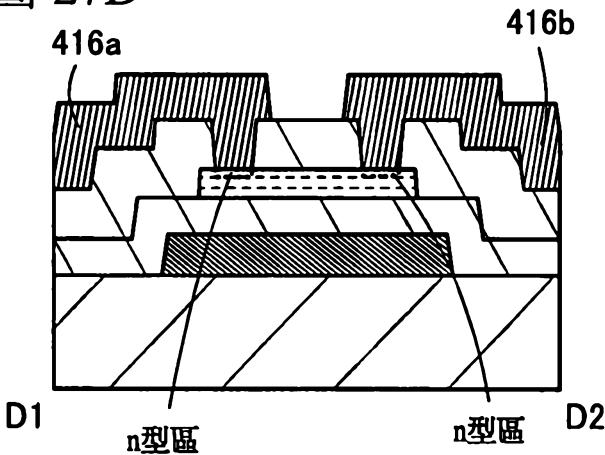

[0034] 圖 1A 示出在計算中使用的電晶體的剖面示意圖。電晶體包括：基底絕緣膜 (BI)；基底絕緣膜 (BI) 上的氧化物半導體層 (S1)；氧化物半導體層 (S1) 上的

氧化物半導體層 (S2)；氧化物半導體層 (S2) 上的源極電極 (SE) 及汲極電極 (DE)；氧化物半導體層 (S2)、源極電極 (SE) 及汲極電極 (DE) 上的氧化物半導體層 (S3)；氧化物半導體層 (S3) 上的閘極絕緣膜 (GI)；以及閘極絕緣膜 (GI) 上的閘極電極 (GE)。氧化物半導體層 (S2) 在與源極電極 (SE) 及汲極電極 (DE) 接觸的區域中包括 n 型區。

[0035] 此時，將氧化物半導體層 (S1)、氧化物半導體層 (S2) 和氧化物半導體層 (S3) 總稱為多層膜。

[0036] 在計算中，採用以下所示的數值。作為基底絕緣膜 (BI) 假設氮化矽膜，將其厚度設定為 300nm，將介電常數設定為 4.1。

[0037] 作為氧化物半導體層 (S1) 假設其 Ga 的原子數比高的 In-Ga-Zn 氧化物，將其厚度設定為 20nm，將介電常數設定為 15，將電子親和力設定為三個條件 (4.2eV、4.3eV、4.4eV)，將能隙設定為 3.6eV，將施體密度設定為  $1 \times 10^{-9}$  個/cm<sup>3</sup>，將電子移動率設定為 0.1cm<sup>2</sup>/Vs，將電洞移動率設定為 0.01cm<sup>2</sup>/Vs。電子親和力是指真空中能階的能量與導帶底的能量 (Ec) 之間的差異。

[0038] 作為氧化物半導體層 (S2) 假設其 In 和 Ga 的原子數比大致相同的 In-Ga-Zn 氧化物，將其厚度設定為 15nm，將介電常數設定為 15，將電子親和力設定為 4.6eV，將能隙設定為 3.2eV，將施體密度設定為  $1 \times 10^{-9}$

個/ $\text{cm}^3$ ，將電子移動率設定為  $10\text{cm}^2/\text{Vs}$ ，將電洞移動率設定為  $0.01\text{cm}^2/\text{Vs}$ 。將 n 型區的施體密度設定為  $5 \times 10^{18}$  個/ $\text{cm}^3$ 。

[0039] 作為氧化物半導體層 (S3) 假設其 Ga 的原子數比高的 In-Ga-Zn 氧化物，將其厚度設定為七個條件 (0nm、5nm、10nm、20nm、30nm、40nm、50nm)，將介電常數設定為 15，將電子親和力設定為三個條件 (4.2eV、4.3eV、4.4eV)，將能隙設定為 3.6eV，將施體密度設定為  $1 \times 10^{-9}$  個/ $\text{cm}^3$ ，將電子移動率設定為  $0.1\text{cm}^2/\text{Vs}$ ，將電洞移動率設定為  $0.01\text{cm}^2/\text{Vs}$ 。此外，使氧化物半導體層 (S1) 與氧化物半導體層 (S3) 的電子親和力相同。

[0040] 作為閘極絕緣膜 (GI) 假設氮化矽膜，將其厚度設定為三個條件 (10nm、20nm、30nm)，將介電常數設定為 4.1。

[0041] 作為閘極電極 (GE) 假設鎢膜，將功函數設定為 5.0eV。

[0042] 此外，將電晶體的通道長度設定為  $0.8\mu\text{m}$ ，將電晶體的通道寬度設定為  $0.8\mu\text{m}$ 。當俯視時，氧化物半導體層 (S2) 中的被形成通道的區域為與閘極電極 (GE) 重疊並位於源極電極 (SE) 與汲極電極 (DE) 之間的區域。因此，當俯視時，該電晶體的通道長度相當於源極電極 (SE) 與汲極電極 (DE) 之間的距離。此外，當俯視時，該電晶體的通道寬度相當於通道形成區的垂直於通道

長度方向的方向的長度。

[0043] 在圖 1A 中示出剖面的電晶體根據氧化物半導體層 (S1)、氧化物半導體層 (S2) 和氧化物半導體層 (S3) 的電子親和力的關係，在點劃線 H1-H2 具有圖 1B 所示的帶結構。此時，在氧化物半導體層 (S2) 中形成阱 (well)。將氧化物半導體層 (S2) 與氧化物半導體層 (S1) 及氧化物半導體層 (S3) 之間的電子親和力的差異 (傳導帶底的能量差異) 稱為阱深度 (well depth)。

[0044] 在此，氧化物半導體層 (S2) 的電子親和力是  $4.6\text{eV}$ 。因此，當氧化物半導體層 (S1) 及氧化物半導體層 (S3) 的電子親和力是  $4.2\text{eV}$ 、 $4.3\text{eV}$ 、 $4.4\text{eV}$  時，阱深度分別是  $0.4\text{eV}$ 、 $0.3\text{eV}$ 、 $0.2\text{eV}$ 。

[0045] 一般而言，在半導體層與基底絕緣膜之間的介面、半導體層與閘極絕緣膜之間的介面等形成 DOS。DOS 有時導致通態電流的減少或可靠性的降低。另一方面，在圖 1A 所示的電晶體中，可以在多層膜中的氧化物半導體層 (S2) 的阱中形成通道。在此情況下，有時基底絕緣膜 (BI) 與氧化物半導體層 (S1) 之間的介面、氧化物半導體層 (S3) 與閘極絕緣膜 (GI) 之間的介面的影響相對變小，可以抑制通態電流的減少或可靠性的降低。

[0046] 基於以上所示的條件，使用矽谷科技有限公司 (Silvaco Inc.) 製造的元件模擬軟體 “Atlas” 進行了計算。注意，假設理想狀態而進行了計算。例如，對在基底絕緣膜 (BI) 與氧化物半導體層 (S1) 之間的介面、氧

化物半導體層（S3）與閘極絕緣膜（GI）之間的介面等不設置 DOS 的情況進行了計算。就是說，本計算不是為了示出多層膜所形成的阱的效果進行的，而是為了示出通態電流與各層的物性或厚度的關係進行的。

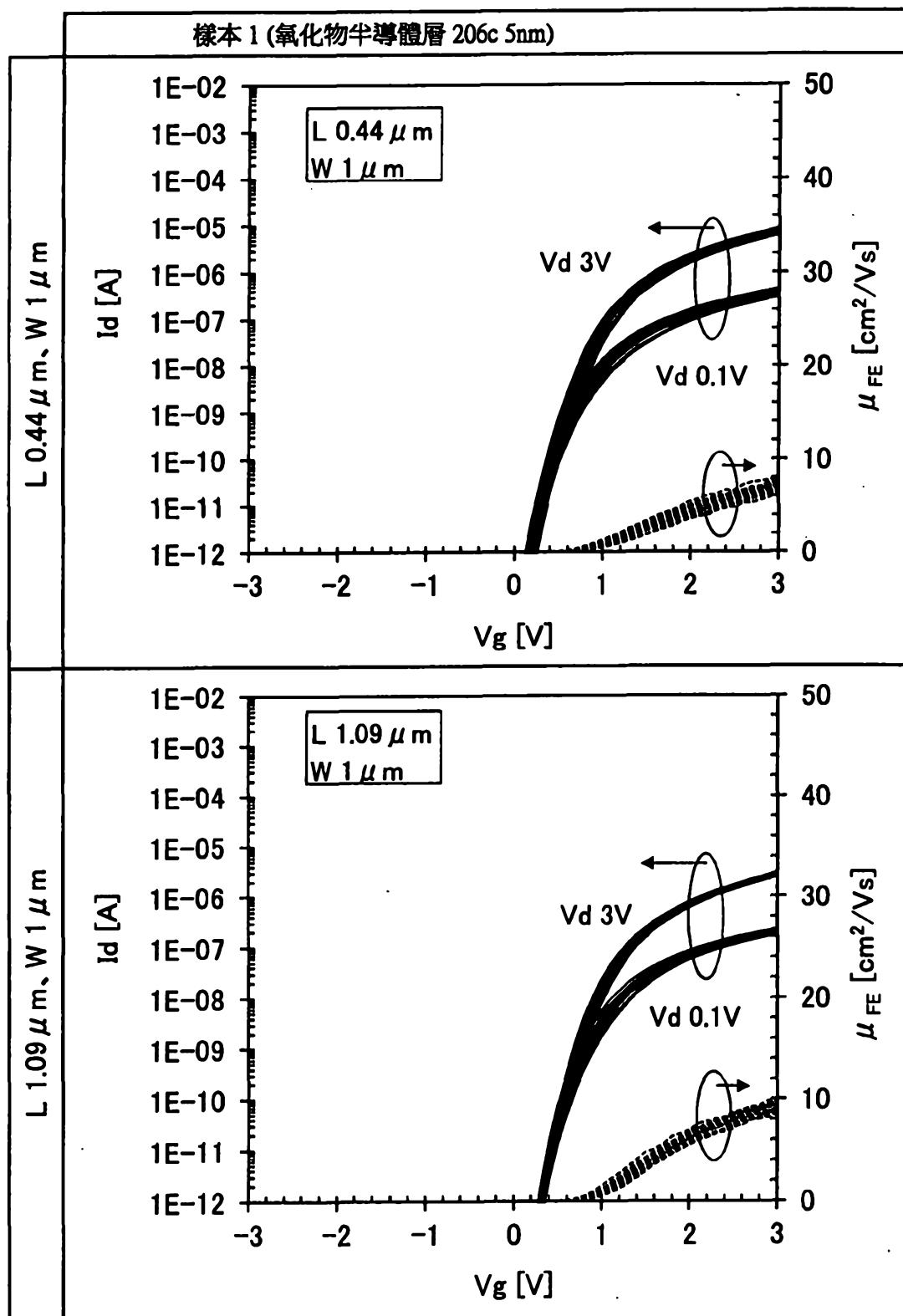

[0047] 圖 2 是標繪出通態電流（Ion）對氧化物半導體層（S3）的厚度的圖。通態電流是閘極電壓  $V_g$  為 3V 且汲極電壓  $V_d$  為 3V 時的汲極電流  $I_d$ 。在圖 2 中，上段示出阱深度為 0.4eV 時的通態電流的曲線，中段示出阱深度為 0.3eV 時的通態電流的曲線，並且下段示出阱深度為 0.2eV 時的通態電流的曲線。此外，在圖式中，符號白圈表示閘極絕緣膜（GI）的厚度為 10nm 時的通態電流，符號白三角表示閘極絕緣膜（GI）的厚度為 20nm 時的通態電流，並且符號白四角表示閘極絕緣膜（GI）的厚度為 30nm 時的通態電流。

[0048] 從圖 2 可知，氧化物半導體層（S3）的厚度越大，通態電流越小。此外可知，阱深度越小，相對於氧化物半導體層（S3）的厚度通態電流越明顯減少。可知閘極絕緣膜（GI）的厚度越大，通態電流越小。

[0049] 當只在包括介面的氧化物半導體層（S2）中形成通道時，氧化物半導體層（S3）用作閘極絕緣膜的一部分。此外，已知電晶體的通態電流與閘極絕緣膜的電容成比例。

[0050] 圖 3 的左列是以氧化物半導體層（S3）和閘極絕緣膜（GI）的總電容為橫軸，以電晶體的通態電流為

縱軸而標繪出資料的圖。圖 3 的右列是以氧化物半導體層 (S3) 和閘極絕緣膜 (GI) 的總電容除以閘極絕緣膜 (GI) 的電容而得到的值 (歸一化電容) 為橫軸，以電晶體的通態電流除以沒有氧化物半導體層 (S3) (0nm) 時的通態電流而得到的值 (歸一化通態電流或  $I_{on}$  比) 為縱軸而標繪出資料的圖。

[0051] 此外，在圖 3 的右列中，示出傾斜度為 1 的直線。當氧化物半導體層 (S3) 用作閘極絕緣膜的一部分時，理想上歸一化電容和歸一化通態電流標繪在傾斜度為 1 的直線上。但是，在阱深度為  $0.3\text{eV}$  時的一部分條件、阱深度為  $0.2\text{eV}$  時的一部分條件下，有時標繪在傾斜度為 1 的直線的下方。這可認為是因為氧化物半導體層 (S3) 不用作閘極絕緣膜。

[0052] 就是說，根據條件，有可能因為由於閘極電極 (GE) 的電場而電子被誘導在氧化物半導體層 (S3)，閘極電極 (GE) 的電場被電子密度得到提高的氧化物半導體層 (S3) 遮蔽，所以施加到氧化物半導體層 (S2) 的電場變弱，而電晶體的通態電流減少。

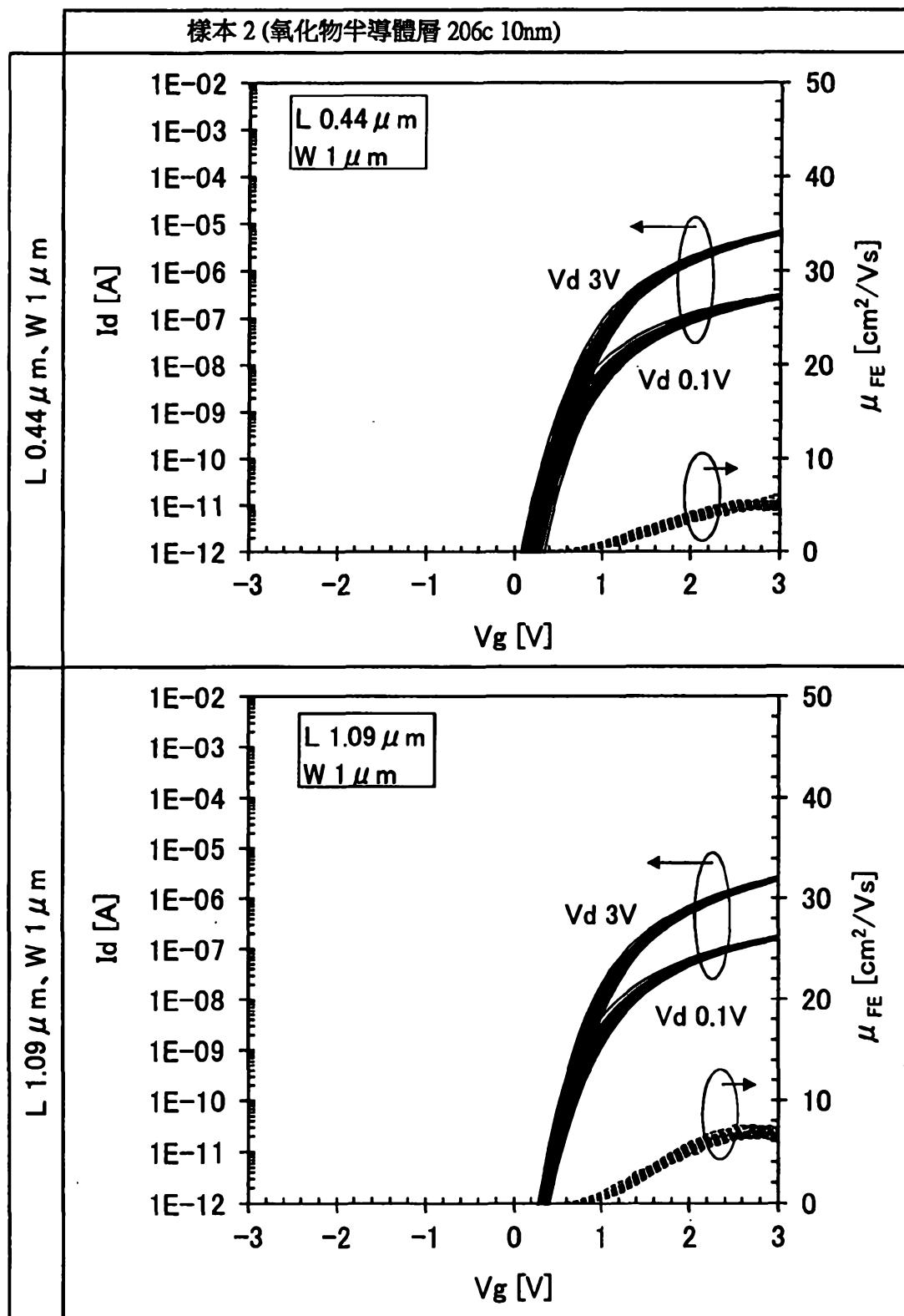

[0053] 於是，接著，說明計算氧化物半導體層 (S2) 與氧化物半導體層 (S3) 之間的界面 (S2\S3 介面) 或者氧化物半導體層 (S3) 與閘極絕緣膜 (GI) 之間的界面 (S3\GI 介面) 的電流密度及電子密度的結果。

[0054] 圖 4 的左列是標繪出界面的電流密度對氧化物半導體層的厚度 (S3) 的曲線的圖。電流密度是閘極電

壓  $V_g$  為 3V 且汲極電壓  $V_d$  為 3V 時的電流密度。白圈、白三角、白四角的符號表示  $S2\backslash S3$  介面的電流密度，黑圈、黑三角、黑四角的符號表示  $S3\backslash GI$  介面的電流密度。在圖 4 的左列中，上段示出阱深度為 0.4eV 時的電流密度的曲線，中段示出阱深度為 0.3eV 時的電流密度的曲線，並且下段示出阱深度為 0.2eV 時的電流密度的曲線。此外，在圖式中，符號圓圈表示閘極絕緣膜 (GI) 的厚度為 10nm 時的電流密度，符號三角形表示閘極絕緣膜 (GI) 的厚度為 20nm 時的電流密度，並且符號四角形表示閘極絕緣膜 (GI) 的厚度為 30nm 時的電流密度。

[0055] 從圖 4 的左列可知，在任何條件下， $S2\backslash S3$  介面的電流密度都高於  $S3\backslash GI$  介面的電流密度。因此，可知該電晶體的通道形成在  $S2\backslash S3$  介面處。

[0056] 注意，在本計算中，將氧化物半導體層 ( $S3$ ) 的電子移動率估計為低於氧化物半導體層 ( $S2$ ) 的電子移動率。因此，有可能由於氧化物半導體層 ( $S3$ ) 的電子移動率與氧化物半導體層 ( $S2$ ) 的電子移動率之間的差異，而在  $S2\backslash S3$  介面形成通道。

[0057] 圖 4 的右列是標繪出介面的電子密度對氧化物半導體層的厚度 ( $S3$ ) 曲線的圖。電子密度是閘極電壓  $V_g$  為 3V 且汲極電壓  $V_d$  為 3V 時的電子密度。白色符號表示  $S2\backslash S3$  介面的電子密度，黑色符號表示  $S3\backslash GI$  介面的電子密度。在圖 4 的右列中，上段示出阱深度為 0.4eV 時的電子密度的曲線，中段示出阱深度為 0.3eV 時的電子密

度的曲線，並且下段示出阱深度為  $0.2\text{eV}$  時的電子密度的曲線。此外，在圖式中，符號圓圈表示閘極絕緣膜 (GI) 的厚度為  $10\text{nm}$  時的電子密度，符號三角形表示閘極絕緣膜 (GI) 的厚度為  $20\text{nm}$  時的電子密度，並且符號四角形表示閘極絕緣膜的厚度為  $30\text{nm}$  時的電子密度。

[0058] 從圖 4 的右列可知，在一部分條件下， $S2\backslash S3$  介面的電子密度相同於或高於  $S3\backslash GI$  介面的電子密度。就是說，可知有時由於閘極電極 (GE) 的電場而多個電子被誘導在氧化物半導體層 ( $S3$ )。當多個電子被誘導在氧化物半導體層 ( $S3$ ) 時，閘極電極 (GE) 的電場被電子密度得到提高的氧化物半導體層 ( $S3$ ) 遮蔽。其結果是，可以考慮到施加到氧化物半導體層 ( $S2$ ) 的電場變弱，而電晶體的通態電流減少。

[0059] 明確而言，當阱深度為  $0.2\text{eV}$  且閘極絕緣膜 (GI) 的厚度為  $10\text{nm}$  時，不管氧化物半導體層 ( $S3$ ) 的厚度如何（在  $5\text{nm}$  以上且  $50\text{nm}$  以下的範圍內）， $S3\backslash GI$  介面的電子密度都是  $1\times 10^{18}$  個/ $\text{cm}^3$  以上。當阱深度為  $0.2\text{eV}$  且閘極絕緣膜 (GI) 的厚度為  $20\text{nm}$  時，在氧化物半導體層 ( $S3$ ) 的厚度為  $10\text{nm}$  以上且  $50\text{nm}$  以下的情況下， $S3\backslash GI$  介面的電子密度是  $1\times 10^{18}$  個/ $\text{cm}^3$  以上。當阱深度為  $0.2\text{eV}$  且閘極絕緣膜 (GI) 的厚度為  $30\text{nm}$  時，在氧化物半導體層 ( $S3$ ) 的厚度為  $20\text{nm}$  以上且  $50\text{nm}$  以下的情況下， $S3\backslash GI$  介面的電子密度是  $1\times 10^{18}$  個/ $\text{cm}^3$  以上。

[0060] 當阱深度為  $0.3\text{eV}$  且閘極絕緣膜 (GI) 的厚

度為  $10\text{nm}$  時，在氧化物半導體層（S3）的厚度為  $10\text{nm}$  以上且  $50\text{nm}$  以下的情況下，S3\GI 介面的電子密度都是  $1 \times 10^{18}$  個/ $\text{cm}^3$  以上。當阱深度為  $0.3\text{eV}$  且閘極絕緣膜（GI）的厚度為  $20\text{nm}$  時，在氧化物半導體層（S3）的厚度為  $40\text{nm}$  以上且  $50\text{nm}$  以下的情況下，S3\GI 介面的電子密度是  $1 \times 10^{18}$  個/ $\text{cm}^3$  以上。當阱深度為  $0.3\text{eV}$  且閘極絕緣膜（GI）的厚度為  $30\text{nm}$  時，不管氧化物半導體層（S3）的厚度如何（在  $5\text{nm}$  以上且  $50\text{nm}$  以下的範圍內），S3\GI 介面的電子密度都不到  $1 \times 10^{18}$  個/ $\text{cm}^3$  以上。

[0061] 當阱深度為  $0.4\text{eV}$  時，在任何條件下，S2\S3 介面的電子密度都不到  $1 \times 10^{18}$  個/ $\text{cm}^3$  以上。

[0062] 從上述可知，根據條件，氧化物半導體層（S3）導致電晶體的通態電流的減少。

[0063] 由此可知，較佳為以不使電晶體的通態電流減少的條件選擇各層。

[0064] 明確而言，當阱深度為  $0.2\text{eV}$  且閘極絕緣膜（GI）的厚度為  $20\text{nm}$  時，將氧化物半導體層（S3）的厚度設定為小於  $10\text{nm}$ （或者， $5\text{nm}$  以下），即可。當阱深度為  $0.2\text{eV}$  且閘極絕緣膜（GI）的厚度為  $30\text{nm}$  時，將氧化物半導體層（S3）的厚度設定為小於  $20\text{nm}$ （或者， $10\text{nm}$  以下），即可。

[0065] 當阱深度為  $0.3\text{eV}$  且閘極絕緣膜（GI）的厚度為  $10\text{nm}$  時，將氧化物半導體層（S3）的厚度設定為小於  $10\text{nm}$ （或者， $5\text{nm}$  以下），即可。當阱深度為  $0.3\text{eV}$

且閘極絕緣膜 (GI) 的厚度為 20nm 時，將氧化物半導體層 (S3) 的厚度設定為小於 40nm (或者，30nm 以下)，即可。

[0066] 或者，將阱深度設定為 0.4eV 以上，即可。

[0067]

〈DOS 所導致的劣化小的降低電晶體的結構〉

如上所述，在具有氧化物半導體層的電晶體中，有時在氧化物半導體層與絕緣膜之間的介面形成 DOS。另外，當電荷被形成了的 DOS 俘獲時，有可能導致電晶體的臨界電壓的變化。

[0068] 例如，藉由採用具有多層膜的電晶體結構，可以使通道遠離 DOS，但是不能完全去掉 DOS 本身。因此，下面，考察 DOS 改變電晶體的臨界電壓的劣化模型。此外，考察降低臨界電壓的變化的結構。

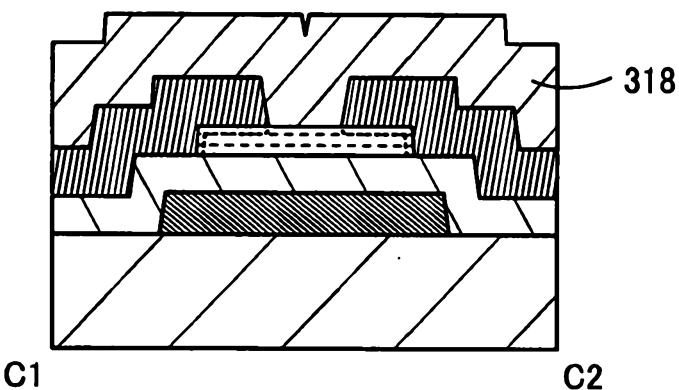

[0069] 圖 5A 為具有氧化物半導體層的電晶體的剖面圖的一個例子。圖 5A 所示的電晶體包括：閘極電極 (bg)；閘極電極 (bg) 上的閘極絕緣膜 (bg)；閘極絕緣膜 (bg) 上的氧化物半導體層 (S1)；氧化物半導體層 (S1) 上的氧化物半導體層 (S2)；氧化物半導體層 (S2) 上的源極電極及汲極電極；氧化物半導體層 (S2)、源極電極及汲極電極上的氧化物半導體層 (S3)；氧化物半導體層 (S3) 上的閘極絕緣膜 (tg)；以及閘極絕緣膜 (tg) 上的閘極電極 (tg)。另外，為了容易理解，圖 5A 所示的電晶體包括閘極電極 (bg)，但

是也可以將以下劣化模型應用於不包括閘極電極（bg）的電晶體。另外，在不包括閘極電極（bg）的情況下，閘極絕緣膜（bg）用作基底絕緣膜。

[0070] 在此，氧化物半導體層（S1）及氧化物半導體層（S3）例如包含一種以上，較佳為兩種以上，更佳為包含三種以上的構成氧化物半導體層（S2）的金屬元素。另外，閘極絕緣膜（bg）例如不包含構成氧化物半導體層（S1）的金屬元素。另外，閘極絕緣膜（tg）例如不包含構成氧化物半導體層（S3）的金屬元素。

[0071] 閘極絕緣膜（bg）與氧化物半導體層（S1）之間的介面為異種物質之間的結合介面，因此 DOS 得到增加。另外，閘極絕緣膜（tg）與氧化物半導體層（S3）之間的介面為異種物質之間的結合介面，因此 DOS 得到增加。另一方面，氧化物半導體層（S1）與氧化物半導體層（S2）之間的介面為同種物質之間的結合介面，因此 DOS 得到減少。另外，氧化物半導體層（S3）與氧化物半導體層（S2）之間的介面為同種物質之間的結合介面，因此 DOS 得到減少。

[0072] 在此，假設閘極絕緣膜（bg）與氧化物半導體層（S1）之間的介面的 DOS 為電荷陷阱。另外，假設閘極絕緣膜（tg）與氧化物半導體層（S3）之間的介面的 DOS 為電荷陷阱。另外，當假設被該 DOS 俘獲的電荷具有極長的弛豫時間時，該電荷有可能改變電晶體的臨界電壓。由於電晶體的工作應力 DOS 有可能俘獲電荷。

[0073] 在此，由  $Q_{ssb}$  表示被閘極絕緣膜（bg）與氧化物半導體層（S1）之間的介面的 DOS 俘獲的電荷。另外，由  $Q_{sst}$  表示被閘極絕緣膜（tg）與氧化物半導體層（S3）之間的介面的 DOS 俘獲的電荷。在此，驗證  $Q_{ssb}$ 、 $Q_{sst}$  改變電晶體的臨界電壓。

[0074] 注意，例如固定閘極電極（bg）的勢能。因此，電晶體的開關例如由閘極電極（tg）控制。另外，在圖 5A 中，描述設置有閘極電極（bg）及閘極絕緣膜（bg）的情況，但是不侷限於此。作為閘極電極（bg）也可以設置導電層、半導體層、添加有雜質的半導體層（例如，p 型半導體或 n 型半導體）。另外，閘極電極（bg）並不需要具有閘極電極的功能。另外，閘極絕緣膜（bg）並不需要具有作為閘極絕緣膜的功能。

[0075] 圖 5B 為對應於圖 5A 的電晶體的閘極電極（bg）到閘極電極（tg）的疊層結構的等效電路。其中， $C_{bg}$  表示閘極絕緣膜（bg）的電容， $C_{s1}$  表示氧化物半導體層（S1）的電容， $C_{s2}$  表示氧化物半導體層（S2）的電容， $C_{s3}$  表示氧化物半導體層（S3）的電容， $C_{tg}$  表示閘極絕緣膜（tg）的電容。如圖 5B 所示，圖 5A 所示的電晶體的閘極電極（bg）到閘極電極（tg）的疊層結構可以由如下等效電路表示：在閘極電極（bg）與閘極電極（tg）之間具有串聯連接的對應於閘極絕緣膜（bg）、氧化物半導體層（S1）、氧化物半導體層（S2）、氧化物半導體層（S3）以及閘極絕緣膜（tg）的電容器的等效電路。

[0076] 另外， $V_{bg}$  表示閘極電極（bg）的勢能， $V_{tg}$  表示閘極電極（tg）的勢能。另外， $\phi_{ssb}$  表示閘極絕緣膜（bg）與氧化物半導體層（S1）之間的界面的勢能， $\phi_{s2b}$  表示氧化物半導體層（S1）與氧化物半導體層（S2）之間的界面的勢能， $\phi_{s2t}$  表示氧化物半導體層（S2）與氧化物半導體層（S3）之間的界面的勢能， $\phi_{sst}$  表示氧化物半導體層（S3）與閘極絕緣膜（tg）之間的界面的勢能。

[0077] 閘極絕緣膜（bg）在閘極電極（bg）一側具有電荷- $(Q_{ssb}+Q_{S1})$  並在氧化物半導體層（S1）一側具有電荷  $Q_{ssb}+Q_{S1}$ 。氧化物半導體層（S1）在閘極絕緣膜（bg）一側具有電荷- $Q_{S1}$  並在氧化物半導體層（S2）一側具有電荷  $Q_{S1}$ 。氧化物半導體層（S2）在氧化物半導體層（S1）一側具有電荷  $Q_{S2}$  並在氧化物半導體層（S3）一側具有電荷  $Q_{S2}$ 。氧化物半導體層（S3）在氧化物半導體層（S2）一側具有電荷- $Q_{S3}$  並在閘極絕緣膜（tg）一側具有電荷  $Q_{S3}$ 。閘極絕緣膜（tg）在氧化物半導體層（S3）一側具有電荷  $Q_{sst}-Q_{S3}$  並在閘極電極（tg）一側具有電荷- $(Q_{sst}-Q_{S3})$ 。

[0078] 下面示出各電容與電荷之間的關係。注意，假設氧化物半導體層（S1）及氧化物半導體層（S3）為絕緣體。

[0079] 在閘極絕緣膜（tg）中，電容與電荷之間的關係可以由算式（1）表示。

[0080]

[算式 1]

$$C_{tg}[(V_{tg} - V_{fbt}) - \phi_{sst}] = -(\mathcal{Q}_{sst} - \mathcal{Q}_{s3})$$

[0081] 在氧化物半導體層 (S3) 中，電容與電荷之間的關係可以由算式 (2) 表示。

[0082]

[算式 2]

$$C_{s3}(\phi_{sst} - \phi_{s2t}) = \mathcal{Q}_{s3}$$

[0083] 在氧化物半導體層 (S2) 中，電容與電荷之間的關係可以由算式 (3) 表示。

[0084]

[算式 3]

$$C_{s2}(\phi_{s2t} - \phi_{s2b}) = \mathcal{Q}_{s2}$$

[0085] 在氧化物半導體層 (S1) 中，電容與電荷之間的關係可以由算式 (4) 表示。

[0086]

[算式 4]

$$C_{s1}(\phi_{s2b} - \phi_{ssb}) = \mathcal{Q}_{s1}$$

[0087] 在閘極絕緣膜 (bg) 中，電容與電荷之間的關係可以由算式 (5) 表示。

[0088]

[算式 5]

$$C_{bg}[\phi_{ssb} - (V_{bg} - V_{fbt})] = \mathcal{Q}_{ssb} + \mathcal{Q}_{s1}$$

[0089] 接著，利用算式 (1) 及算式 (2) 消去  $\phi_{sst}$ ，得到算式 (6)。注意， $V_{fbt}$  表示平帶電壓。

[0090]

[算式 6]

$$(V_{tg} - V_{fb}) - \phi_{S2l} + \frac{Q_{ssl}}{C_{tg}} = \left( \frac{1}{C_{tg}} + \frac{1}{C_{s3}} \right) Q_{s3}$$

[0091] 另外，利用算式 (4) 及算式 (5) 消去  $\phi_{ssb}$ ，得到算式 (7)。注意， $V_{fb}$  表示平帶電壓。

[0092]

[算式 7]

$$\phi_{S2b} - (V_{bg} - V_{fb}) - \frac{Q_{ssb}}{C_{bg}} = \left( \frac{1}{C_{bg}} + \frac{1}{C_{s1}} \right) Q_{s1}$$

[0093] 假設氧化物半導體層 (S2) 整體被空乏化。換言之，在  $0 < x < t_{S2}$  的情況下，滿足  $\phi(x) < 0$ 。 $t_{S2}$  表示氧化物半導體層 (S2) 的厚度。在此，氧化物半導體層 (S2) 中的泊松方程由算式 (8) 表示。

[0094]

[算式 8]

$$\frac{d^2\phi}{dx^2} = -\frac{e(N_D - n)}{\epsilon_{s2}}$$

[0095] 注意， $e$  表示基本電荷。另外， $N_D$  表示氧化物半導體層 (S2) 的施體密度。另外， $n$  表示氧化物半導體層 (S2) 的電子密度。另外， $\epsilon_{s2}$  表示氧化物半導體層 (S2) 的介電常數。

[0096] 當氧化物半導體層 (S2) 整體被空乏化時，由於  $N_D \gg n$ ，因此算式 (8) 可以被近似為算式 (9)。

[0097]

[算式 9]

$$\frac{d^2\phi}{dx^2} = -\frac{eN_D}{\epsilon_{s2}}$$

[0098] 接著，將算式(9)變形為算式(10)及算式(11)。 $E(x)$ 表示膜厚度方向的電場， $k_1$ 及 $k_2$ 表示待定係數。

[0099]

[算式 10]

$$\phi(x) = -\frac{eN_D}{2\epsilon_{s2}}x^2 + k_1x + k_2$$

[0100]

[算式 11]

$$E(x) = -\frac{d\phi}{dx} = \frac{eN_D}{\epsilon_{s2}}x - k_1$$

[0101] 根據邊界條件 $\phi(0) = \phi_{s21}$ 、 $\phi(t_{s2}) = \phi_{s2b}$ ，利用算式(10)及算式(11)， $k_1$ 及 $k_2$ 可以分別由算式(12)及算式(13)表示。

[0102]

[算式 12]

$$k_1 = \frac{\phi_{s2b} - \phi_{s21}}{t_{s2}} + \frac{eN_D t_{s2}}{2\epsilon_{s2}}$$

[0103]

[算式 13]

$$k_2 = \phi_{s21}$$

[0104] 另外，根據高斯定律，表面電荷密度可以由算式(14)及算式(15)表示。

[0105]

[算式 14]

$$Q_{s3} = \epsilon_{s2}E(0)$$

[0106]

[算式 15]

$$Q_{S1} = \varepsilon_{S2} E(t_{S2})$$

[0107] 因此， $Q_{S3}$  以及  $Q_{S1}$  可以由以下算式 (16) 及算式 (17) 表示。

[0108]

[算式 16]

$$Q_{S3} = C_{S2} (\phi_{S2t} - \phi_{S2b}) - \frac{eN_D t_{S2}}{2}$$

[0109]

[算式 17]

$$Q_{S1} = C_{S2} (\phi_{S2t} - \phi_{S2b}) + \frac{eN_D t_{S2}}{2}$$

[0110] 將算式 (16) 及算式 (17) 代入算式 (6) 及算式 (7)，可以獲得算式 (18) 及算式 (19)。

[0111]

[算式 18]

$$(V_{tg} - V_{fb}) + \frac{Q_{sst}}{C_{tg}} = \left[ \left( \frac{1}{C_{tg}} + \frac{1}{C_{S3}} \right) C_{S2} + 1 \right] \phi_{S2t} - \left( \frac{1}{C_{tg}} + \frac{1}{C_{S3}} \right) \left( C_{S2} \phi_{S2b} + \frac{eN_D t_{S2}}{2} \right)$$

[0112]

[算式 19]

$$(V_{bg} - V_{fb}) + \frac{Q_{ssb}}{C_{bg}} = - \left( \frac{1}{C_{bg}} + \frac{1}{C_{S1}} \right) \left( C_{S2} \phi_{S2t} + \frac{eN_D t_{S2}}{2} \right) + \left[ \left( \frac{1}{C_{bg}} + \frac{1}{C_{S1}} \right) C_{S2} + 1 \right] \phi_{S2b}$$

[0113] 在此，假設電晶體的通道從氧化物半導體層 (S1) 與氧化物半導體層 (S2) 之間的界面一側形成，臨界電壓  $V_{th}$  為  $\phi_{S2b} = 0$  時的  $V_{tg}$ 。因此，藉由計算算式 (18) 和算式 (19) 的聯立方程消去  $\phi_{S2t}$ ，臨界電壓  $V_{th}$  可以由

算式 (20) 表示。

[0114]

[算式 20]

$$V_{th} = V_{fbt} - \frac{Q_{sst}}{C_{tg}} - \left( \frac{1}{C_{tg}} + \frac{1}{C_{s1}} + \frac{1}{C_{s2}} \right) \frac{C_{s1}}{C_{bg} + C_{s1}} [Q_{ssb} + C_{bg} (V_{bg} - V_{fb})] - \left( \frac{1}{C_{tg}} + \frac{1}{C_{s3}} + \frac{1}{2C_{s2}} \right) eN_D t_{s2}$$

[0115] 因此，由電荷  $Q_{sst}$  及電荷  $Q_{ssb}$  引起的臨界電壓  $V_{th}$  的變化量  $\Delta V_{th}$  可以由算式 (21) 表示。

[0116]

[算式 21]

$$\Delta V_{th} = - \frac{Q_{sst}}{C_{tg}} - \left( \frac{1}{C_{tg}} + \frac{1}{C_{s3}} + \frac{1}{C_{s2}} \right) \frac{C_{s1}}{C_{bg} + C_{s1}} Q_{ssb}$$

[0117] 由此可知，當增大  $C_{s3}$  (例如，減薄氧化物半導體層 (S3))， $Q_{ssb}$  對  $\Delta V_{th}$  的影響減少。此外，當增大  $C_{s2}$  (例如，減薄氧化物半導體層 (S2)) 時， $Q_{ssb}$  對  $\Delta V_{th}$  的影響減少。另外，當減少  $C_{s1}$  (例如，加厚氧化物半導體層 (S1)) 時， $Q_{ssb}$  對  $\Delta V_{th}$  的影響減少。

[0118] 另外，當增大  $C_{tg}$  (減薄閘極絕緣膜 (tg)) 時， $Q_{ssb}$  的影響減少。另外，當增大  $C_{bg}$  (減薄閘極絕緣膜 (bg)) 時， $Q_{ssb}$  的影響減少。

[0119] 另一方面， $C_{s3}$ 、 $C_{s2}$ 、 $C_{s1}$  不與  $Q_{sst}$  的影響有關。另外，當增大  $C_{tg}$  (減薄閘極絕緣膜 (tg)) 時， $Q_{sst}$  對  $\Delta V_{th}$  的影響減少。

[0120] 因此，在圖 5A 所示的電晶體中，為了減少由 DOS 引起的臨界電壓的變化，減薄氧化物半導體層 (S3)

即可。或者，減薄氧化物半導體層 (S2) 即可。或者，加厚氧化物半導體層 (S1) 即可。或者，減薄閘極絕緣膜 (tg) 即可。或者，減薄閘極絕緣膜 (bg) 即可。

[0121] 另外，電晶體的通道形成在氧化物半導體層 (S2) 中。換而言之，氧化物半導體層 (S1) 及氧化物半導體層 (S3) 的傳導帶底的能量 (Ec) 比氧化物半導體層 (S2) 高。圖 6A 和圖 6B 示出此時的電晶體的能帶結構的示意圖。

[0122] 在上述劣化模型中，閘極絕緣膜 (bg) 與氧化物半導體層 (S1) 之間的介面的 DOS 的勢能以及閘極絕緣膜 (tg) 與氧化物半導體層 (S3) 之間的介面的 DOS 的勢能低於費米能階的情況。此時，即使閘極電極 (bg) 及閘極電極 (tg) 的電壓為 0V，各介面的 DOS 也俘獲電子，儲存電荷  $Q_{ssb}$  及電荷  $Q_{sst}$  (參照圖 6A)。

[0123] 另一方面，在設置有氧化物半導體層 (S1) 及氧化物半導體層 (S3) 的情況下，與沒有設置氧化物半導體層 (S1) 及氧化物半導體層 (S3) 的情況相比，各介面的 DOS 的勢能有時高於費米能階 (接近於傳導帶底的能量)。如此，在各介面的 DOS 的勢能高於費米能階的情況下，各介面的 DOS 不俘獲電子，因此不儲存電荷  $Q_{ssb}$  及電荷  $Q_{sst}$  (參照圖 6B)。另外，當電壓被施加到閘極電極 (tg) 等時，電荷有可能被各介面的 DOS 俘獲。由於各介面的 DOS 的勢能近於傳導帶底的能量，因此被俘獲的電荷在很短的弛豫時間內消失。因此，各介面的

DOS 不容易導致電晶體的臨界電壓的變化。

[0124] 如圖 6B 所示，根據各介面的 DOS 的勢能與費米能階之間的大小關係，在設置氧化物半導體層 (S3) 時，有時不儲存電荷  $Q_{sst}$ 。在不儲存電荷  $Q_{sst}$  的情況下，劣化的主要原因不存在，因此電晶體的可靠性得到提高。

[0125] 參照以上所示的劣化模型，說明了在具有多層膜的電晶體的臨界電壓的變化量小的結構。為了減少由 DOS 引起的臨界電壓的變化，減薄離控制電晶體的開關的閘極電極近的氧化物半導體層即可。另外，加厚離控制電晶體的開關的閘極電極遠的氧化物半導體層即可。

[0126]

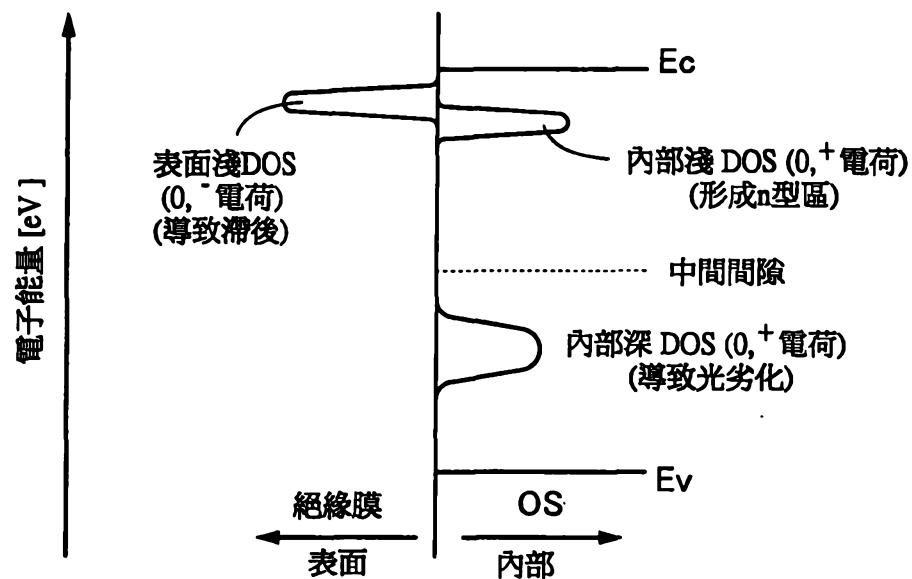

〈說明氧化物半導體層中的 DOS 以及原因元素的關係的模型〉

如上所述，當在氧化物半導體層內部以及氧化物半導體層與外部之間的介面附近存在有 DOS 時，DOS 導致具有氧化物半導體層的電晶體的劣化。因此，藉由認識氧化物半導體層中的 DOS 的來源，可以認識電晶體劣化的主要原因。

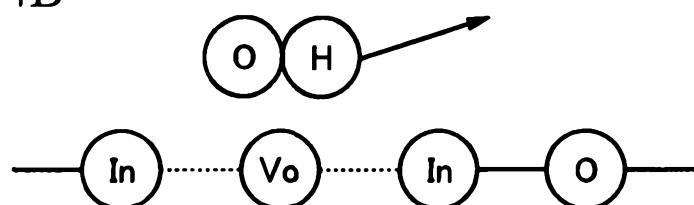

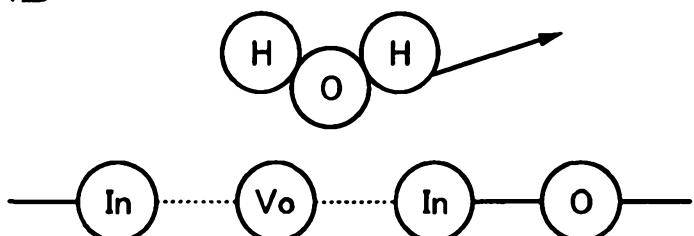

[0127] 可以根據氧 (O)、氧缺陷 (Vo) 和氫 (H) 的位置或鍵合關係說明氧化物半導體層內部以及其介面附近的 DOS。以下，說明本發明人的模型概要。

[0128] 總結來說，為了降低半導體層內部以及其介面附近的 DOS，需要降低氧缺陷及氫。以下，使用模型說明為了降低氧化物半導體層內部及其介面附近的 DOS 需

要降低氧缺陷及氫的理由。

[0129] 圖 7 示出氧化物半導體層內部以及其介面附近的 DOS 的帶結構。以下，說明氧化物半導體層是包含銦、鎵及鋅的氧化物半導體層的情況。

[0130] 首先，一般而言，DOS 包括位於淺能階的 DOS (shallow level DOS) 和位於深能階的 DOS (deep level DOS)。此外，在本說明書中，位於淺能階的 DOS (shallow level DOS) 是指傳導帶底的能量 ( $E_c$ ) 與能帶間隙中心 (mid gap) 之間的 DOS。因此，例如位於淺能階的 DOS (shallow level DOS) 位於傳導帶底的能量附近。此外，在本說明書中，位於深能階的 DOS (deep level DOS) 是指價電子帶頂端的能量 ( $E_v$ ) 與能帶間隙中心之間的 DOS。因此，例如位於深能階的 DOS (deep level DOS) 位於離價電子帶頂端比離能帶間隙中心近的位置。

[0131] 於是，當考慮氧化物半導體層中的 DOS 時，位於淺能階的 DOS (shallow level DOS) 包括兩種 DOS。第一個位於淺能階的 DOS (shallow level DOS) 是氧化物半導體層的表面附近（與絕緣膜之間的介面或其附近）的 DOS (surface shallow DOS)。第二個位於淺能階的 DOS (shallow level DOS) 是氧化物半導體層內部的 DOS (bulk shallow DOS)。另一方面，作為位於深能階的 DOS (deep level DOS)，有氧化物半導體層內部的 DOS (bulk deep DOS)。

[0132] 這些 DOS 有可能起到如下作用。首先，因為氧化物半導體層的表面附近的 surface shallow DOS 位於離導帶底淺的位置上，所以容易俘獲電荷或導致電荷的消失。接著，因為與氧化物半導體層的表面附近的 surface shallow DOS 相比，氧化物半導體層內部的 bulk shallow DOS 位於離導帶底深的位置上，所以不容易導致電荷的消失。

[0133] 以下，說明在氧化物半導體層中形成 DOS 的原因元素。

[0134] 例如，在氧化物半導體層上形成氧化矽膜時，有時氧化物半導體層所包含的銻進入氧化矽膜中，該銻取代矽，由此形成位於淺能階的 DOS (shallow level DOS)。

[0135] 例如，在氧化物半導體層與氧化矽膜之間的界面，氧化物半導體層所包含的銻與氧的鍵合斷開，而該氧與矽鍵合。這起因於矽和氧的鍵合能量比銻和矽的鍵合能量高，並且矽（4 價）的化合價比銻（3 價）大。而且，由於氧化物半導體層所包含的氧被矽奪取，而與銻鍵合了的氧的位點（site）成為氧缺陷。除了在表面上以外，在矽進入氧化物半導體層內部時也同樣地發生該現象。這些氧缺陷形成位於深能階的 DOS (deep level DOS)。

[0136] 除了由於矽以外，有時由於其他原因而銻和氧的鍵合斷開。例如，在包含銻、鎵及鋅的氧化物半導體

層中，銻和氧的鍵合比鎵或鋅和氧的鍵合弱，所以容易斷開。因此，例如，由於電漿所造成的損傷或濺射粒子所造成的損傷等而銻和氧的鍵合斷開，而會產生氧缺陷。該氧缺陷形成位於深能階的 DOS (deep level DOS)。該位於深能階的 DOS (deep level DOS) 可以俘獲電洞，由此成為電洞陷阱（電洞俘獲中心）。就是說，該氧缺陷形成氧化物半導體層內部的 bulk deep DOS。

[0137] 在後面說明那樣，這些氧缺陷所形成的位於深能階的 DOS (deep level DOS) 由於氫而成爲形成氧化物半導體層的表面附近的 surface shallow DOS、氧化物半導體層內部的 bulk shallow DOS 的主要原因之一。

[0138] 因爲這些氧缺陷形成 DOS，所以成爲氧化物半導體層不穩定的主要原因。此外，氧化物半導體層中的氧缺陷藉由俘獲氫處於準穩定狀態。就是說，當位於深能階的 DOS (deep level DOS) 且可以俘獲電洞的電洞陷阱的氧缺陷俘獲氫時，形成位於淺能階的 DOS (shallow level DOS)。其結果是，位於淺能階的 DOS (shallow level DOS) 可以成爲能夠俘獲電子的電子陷阱，也可以成爲電子的發生源。如此，氧缺陷俘獲氫。但是，如在後面說明那樣，根據氧化物半導體層中的氫的位置，氧缺陷有可能帶正（中性或正），也帶負（中性或負）。因此，氫有可能給具有氧化物半導體層的電晶體帶來負面影響。

[0139] 作爲一個例子，在圖 8 中示出底閘極頂接觸結構的電晶體的剖面示意圖。氧化物半導體層 (OS) 在

與絕緣膜之間的介面附近具有 surface shallow DOS。surface shallow DOS 俘獲有電子，而帶負。因此，surface shallow DOS 導致電晶體的臨界電壓的改變。

[0140] 於是，爲了防止氧缺陷給電晶體帶來負面影響，降低氧缺陷的密度是重要的。藉由對氧化物半導體層供應過剩氧，即由過剩氧填補氧缺陷，可以降低氧化物半導體層的氧缺陷的密度。就是說，由於過剩氧的進入，而氧缺陷可以處於穩定狀態。例如，使氧化物半導體層的內部或者設置在氧化物半導體層的介面附近的絕緣膜中包含過剩氧。於是，由於該過剩氧填補氧化物半導體層的氧缺陷，而可以有效地消滅或降低氧化物半導體層的氧缺陷。

[0141] 如此，氧缺陷由於氫或氧而處於準穩定狀態或穩定狀態。當氧化物半導體層中的氫濃度高時，俘獲氫的氧缺陷增多。此外，在氧缺陷中存在有氫時，即使供應過剩氧，過剩氧也首先被用來去除氫。由此，在去除氫之後，過剩氧才被用來填補氧缺陷。因此，當氧化物半導體層中的氫濃度高時，由過剩氧可以降低的氧缺陷很少。與此相反，當氧化物半導體層中的氫濃度低時，被氧缺陷俘獲的氫很少。因此，藉由供應過剩氧，可以大幅度地降低氧缺陷的密度。

[0142] 如已說明那樣，氧缺陷俘獲氫，但是根據俘獲氫的方法而有可能帶正（中性或正），也帶負（中性或負）。在此，考慮氧化物半導體層內部的 bulk shallow DOS 及表面附近的 surface shallow DOS。只考慮氫（氫鍵

合)、氧缺陷以及氧的相對位置可以理解一個事實，就是這些 shallow level DOS 帶中性或負與中性或正中的任一個。例如，當在氧化物半導體層內部氫被氧缺陷俘獲而形成  $\text{V}_{\text{O}}\text{H}$  時，氫帶中性或正。就是說， $\text{H}^+ + \text{e}^-$  形成氧化物半導體層內部的 bulk shallow DOS，而成為在氧化物半導體層中形成 n 型區的主要原因。

[0143] 另一方面，氫不但有時帶中性或正，而且有時帶中性或負。鑒於此，而可以想到形成氧化物半導體層內部的 bulk shallow DOS 及氧化物半導體層的表面附近的 surface shallow DOS 的如下模型。注意，模型中的“...”不是表示鍵合的。模型中的“...”是用來與模型中的表示原子間的離子性鍵合的“—”區別的。

[0144] 首先，在表 1 中列舉出如下模型，其中包含在氧化物半導體層中的銻和氧的鍵合斷開，該氧與矽鍵合，而且存在有氫。

[0145]

[表 1]

| 模型   | 缺陷的種類                                                    |                                                            |

|------|----------------------------------------------------------|------------------------------------------------------------|

| 模型 A | $\text{In} \cdots \text{V}_{\text{O}}$                   | $\text{H}^{\delta-} \cdots \text{O}^{\delta+} - \text{Si}$ |

| 模型 B | $\text{In} \cdots \text{V}_{\text{O}}\text{H}^{\delta-}$ | $\text{O}^{\delta-} - \text{Si}$                           |

| 模型 C | $\text{In} \cdots \text{V}_{\text{O}}$                   | $\text{H}^{\delta+} - \text{O}^{\delta-} - \text{In}$      |

| 模型 D | $\text{In} \cdots \text{V}_{\text{O}}\text{H}^{\delta-}$ | $\text{O}^{\delta-} - \text{In}$                           |

[0146] 例如，有氫和氧鍵合的模型 A。

[0147] 此外，例如有氫被氧缺陷俘獲的模型 B。

[0148] 此外，在將矽取代為銻時也是同樣的。例如，有氫和氧鍵合的模型 C。

[0149] 此外，例如有氫被氧缺陷俘獲的模型 D。

[0150] 如此，可以想到模型 A 至模型 D 的四個模型。根據該模型，可以說明 DOS 帶中性或正與中性或負中的任一個。注意，因為銻的與氧的鍵合比矽的與氧的鍵合強，所以可以認為與模型 D 相比，模型 B 的可能性低。

[0151] 因此，根據氫、氧缺陷及氧的相對位置關係，氫有可能帶正和負的兩者。就是說，氧缺陷和氫有可能形成帶正的 DOS 和帶負的 DOS 的兩者。按照周圍的環境（配置在周圍的元素的電負性），它們有可能帶正和負中的任一個。

[0152]

〈具有氧化物半導體層的電晶體的黑暗狀態下的滯後劣化模型〉

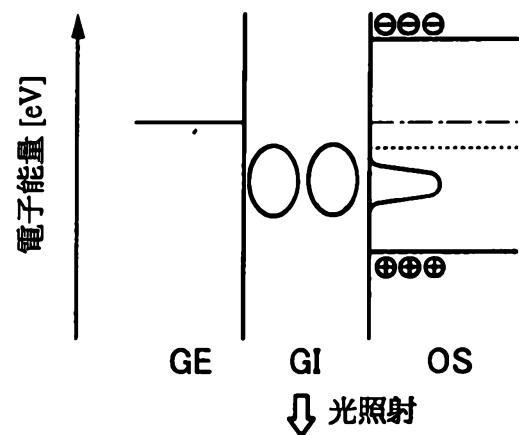

接著，說明具有氧化物半導體層的電晶體的滯後劣化機制。在被照射光的情況和不被照射光的情況下，具有氧化物半導體層的電晶體不同地劣化。在被照射光時，劣化有可能起因於氧化物半導體層內部的位於深能階的 DOS (bulk deep DOS)。在不被照射光時，劣化有可能起因於氧化物半導體層的表面附近（與絕緣膜的介面或其附近）的位於淺能階的 DOS (surface shallow DOS)。

[0153] 於是，首先說明具有氧化物半導體層的電晶

體不被照射光的情況（黑暗狀態）。在此情況下，根據由氧化物半導體層的表面附近（與絕緣膜的界面或其附近）的位於淺能階的 DOS (surface shallow DOS) 的電荷俘獲與釋放的關係，可以說明電晶體的劣化機制。

[0154] 在圖 9 中，示出在黑暗狀態下對具有氧化物半導體層的電晶體反復進行閘極 BT (bias temperature: 偏壓-溫度) 應力測試時的臨界電壓 ( $V_{th}$ ) 變化。如從圖 9 可知那樣，在進行正閘極 BT 應力測試 (+GBT) 時，臨界電壓向正方向漂移。接著，在進行負閘極 BT 應力測試 (-GBT) 時，臨界電壓向負方向漂移，而成為與初期值 (Initial) 相同程度的臨界電壓。如此，當交替反復進行正閘極 BT 應力測試和負閘極 BT 應力測試時，臨界電壓升降（產生滯後）。就是說，可知：當在不照射光的狀態下反復進行負閘極 BT 應力測試和正閘極 BT 應力測試時，臨界電壓向正方向和負方向反復漂移，但是在總體上，該漂移保持在一定的範圍內。

[0155] 根據氧化物半導體層的表面附近的 surface shallow DOS，可以說明這種黑暗狀態下的閘極 BT 應力測試中的電晶體的臨界電壓變化。圖 10 示出包括氧化物半導體層的帶結構以及對應於帶結構的流程圖。注意，在此考慮不被照射光的情況下的劣化機制，因此假設在進行閘極 BT 應力測試之前、閘極 BT 應力測試中以及閘極 BT 應力測試之後都不被照射光的情況。

[0156] 在施加閘極 BT 應力之前（閘極電壓 ( $V_g$ )

爲 0 ) ，氧化物半導體層的表面附近的 surface shallow DOS 具有高於費米能階 (Ef) 的能量並沒有俘獲電子，因此是電中性的 (步驟 S101) 。此時，將所測量的臨界電壓設定爲施加閘極 BT 應力之前的初期值。

[0157] 接著，進行正閘極 BT 應力測試 (黑暗狀態)，施加正閘極電壓。於是，由於施加正閘極電壓，而傳導帶彎曲，氧化物半導體層的表面附近的 surface shallow DOS 變爲低於費米能階的能量。由此，氧化物半導體層的表面附近的 surface shallow DOS 俘獲電子，氧化物半導體層的表面附近的 surface shallow DOS 帶負 (步驟 S102) 。

[0158] 接著，停止應力，使閘極電壓爲 0。藉由使閘極電壓爲 0，氧化物半導體層的表面附近的 surface shallow DOS 變爲高於費米能階的能量。但是氧化物半導體層的表面附近的 surface shallow DOS 所俘獲的電子釋放需要長時間。因此，氧化物半導體層的表面附近的 surface shallow DOS 維持帶負狀態 (步驟 S103) 。此時，電晶體的通道形成區除了被施加閘極電壓以外還被施加負電壓。因此，爲了使電晶體導通，需要施加高於初期值的閘極電壓，而臨界電壓向正方向漂移。就是說，電晶體有可能容易成爲常關閉 (normally off) 。

[0159] 接著，進行負閘極 BT 應力測試 (黑暗狀態)，施加負閘極電壓。由於施加負閘極電壓，而傳導帶彎曲，氧化物半導體層的表面附近的 surface shallow DOS

變為更高的能階。由此，氧化物半導體層的表面附近的 surface shallow DOS 所俘獲的電子被釋放，氧化物半導體層的表面附近的 surface shallow DOS 成為電中性（步驟 S104）。起因於該電子的釋放，臨界電壓有可能恢復到與進行閘極 BT 應力測試之前的初期值大致相同的值。

[0160] 接著，停止應力，使閘極電壓為 0。此時，氧化物半導體層的表面附近的 surface shallow DOS 已釋放所俘獲的電子，因此是電中性的（步驟 S101）。由此，臨界電壓向正方向漂移，其結果是恢復到進行閘極 BT 應力測試之前的初期值。就是說，當在不照射光的狀態下反復進行負閘極 BT 應力測試和正閘極 BT 應力測試時，臨界電壓向正方向和負方向反復漂移。但是，氧化物半導體層的表面附近的 surface shallow DOS 在進行正閘極 BT 應力測試時俘獲電子並在進行負閘極 BT 應力測試時釋放該電子，由此可知，在總體上，只在一定的範圍內發生漂移。

[0161] 如上所述，藉由理解氧化物半導體層的表面附近的 surface shallow DOS，可以說明黑暗狀態下的閘極 BT 應力測試所引起的電晶體的臨界電壓漂移。

[0162]

〈具有氧化物半導體層的電晶體的光照射狀態下的劣化模型〉

如已說明那樣，在被照射光的情況和不被照射光的情況下，具有氧化物半導體層的電晶體不同地劣化。已說明

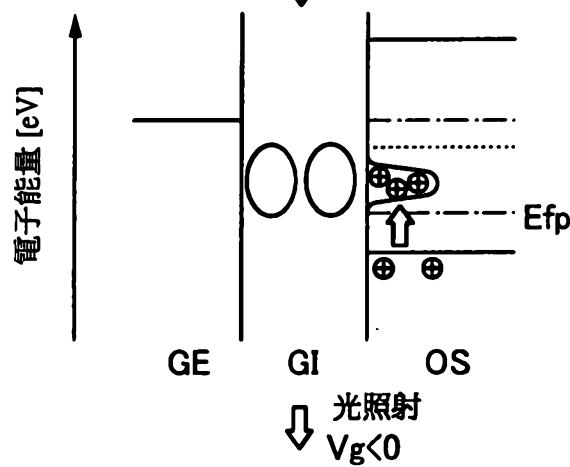

不被照射光的情況。因此，在此，說明被照射光的情況下的劣化機制。在被照射光時，氧化物半導體層內部的位於深能階的 DOS (bulk deep DOS) 造成影響。在此，根據氧化物半導體層內部的位於深能階的 DOS (bulk deep DOS) 的電荷俘獲與釋放的關係，說明被照射光時（明亮狀態）的電晶體的劣化機制。

[0163] 在圖 11 中，示出在光照射的狀態下對具有氧化物半導體層的電晶體反復進行閘極 BT 應力測試時的臨界電壓 ( $V_{th}$ ) 漂移。如從圖 11 可知那樣，臨界電壓 ( $V_{th}$ ) 從初期值 (Initial) 漂移。

[0164] 在圖 11 中，首先，作為臨界電壓的初期值，示出在不施加閘極 BT 應力且遮光的狀態（黑暗狀態）下測量的結果。接著，在不施加閘極 BT 應力且照射光的狀態（明亮狀態）下測量臨界電壓。其結果是，可知與遮光狀態（黑暗狀態）下的臨界電壓相比，照射光的狀態（明亮狀態）下的臨界電壓向負方向大幅度地漂移。這有可能是因為：藉由照射光，生成電子及電洞 (hole)，所生成的電子被激發到導帶。換言之，可以說，即使在不施加閘極 BT 應力的情況下，也由於光照射，而具有氧化物半導體層的電晶體的臨界電壓向負方向漂移，容易常導通化。此時，氧化物半導體層的能隙越大或者能帶間隙中的 DOS 越少，被激發的電子個數越少。因此，在此情況下，只由光照射而導致的臨界電壓漂移較小。

[0165] 接著，當在繼續照射光的狀態下進行負閘極

BT 應力測試 (-GBT) 時，臨界電壓進一步向負方向漂移。這有可能是因為：被氧化物半導體層內部的 bulk deep DOS 俘獲的電洞由電場注入到閘極絕緣膜 (GI) 中的非橋氧電洞中心 (NBOHC: Non Bridging Oxygen Hole Center)，而帶正。

[0166] 然後，當在繼續照射光的狀態下進行正閘極 BT 應力測試 (+GBT) 時，臨界電壓向正方向漂移。這有可能是因為：閘極絕緣膜中的非橋氧電洞中心 (NBOHC) 中的電洞由電場而降低。但是，臨界電壓不恢復到初期值，由此可以判斷為並非所有的引入在閘極絕緣膜中的電洞被釋放。

[0167] 而且，當在繼續照射光的狀態下反復進行負閘極 BT 應力測試和正閘極 BT 應力測試時，臨界電壓反復向正方向和負方向漂移，由此可知，在總體上，逐漸向負方向漂移。這有可能起因於閘極絕緣膜中的非橋氧電洞中心 (NBOHC) 的電洞。就是說，由於正閘極 BT 應力測試，而閘極絕緣膜中的非橋氧電洞中心 (NBOHC) 的電洞減少。注意，並非所有的該電洞被釋放，而電洞的一部分殘留在閘極絕緣膜中的非橋氧電洞中心 (NBOHC)。而且，當在稍微殘留有電洞的狀態下進行負閘極 BT 應力測試時，以沉積在殘留的電洞上的方式電洞追加到閘極絕緣膜中的非橋氧電洞中心 (NBOHC) 而蓄積。然後，藉由再次進行正閘極 BT 應力測試，閘極絕緣膜中的非橋氧電洞中心 (NBOHC) 中的電洞稍微減少，但是在其次進

行負閘極 BT 應力測試時，電洞再次追加。就是說，可以考慮到：在進行正閘極 BT 應力測試時，閘極絕緣膜中的非橋氧電洞中心（NBOHC）中的電洞減少但是稍微殘留，在進行負閘極 BT 應力測試時，電洞進一步追加到閘極絕緣膜中的非橋氧電洞中心（NBOHC）中，由此臨界電壓向正方向和負方向反復漂移，在總體上，逐漸向負方向漂移。

[0168] 使用圖 12 及圖 13 所示的帶結構，說明在以上的光照射下的閘極 BT 應力測試（正閘極 BT 與負閘極 BT 的反復測試）中的電晶體的臨界電壓漂移的機制。在圖 12 和圖 13 中，使用氧化物半導體層內部的 bulk deep DOS 以及閘極絕緣膜中的非橋氧電洞中心（NBOHC1 及 NBOHC2）進行說明。注意，非橋氧電洞中心（NBOHC1）是與非橋氧電洞中心（NBOHC2）相比位於接近與氧化物半導體層的界面的位置（表面一側）的非橋氧電洞中心（NBOHC）。

[0169] 在施加閘極 BT 應力和照射光之前（閘極電壓（ $V_g$ ）是 0），氧化物半導體層內部的 bulk deep DOS 的能量低於費米能階（ $E_f$ ），並沒有俘獲電洞因此是電中性的（步驟 S111）。此時，將在黑暗狀態下測量的臨界電壓設定為黑暗狀態下的初期值。

[0170] 接著，當不施加閘極 BT 應力並對氧化物半導體層照射光時，電子和電洞生成（步驟 S112）。所生成的電子激發到導帶，使臨界電壓向負方向漂移（在以後

的製程中，不示出電子）。此外，由於電洞的生成，而電洞的准費米能階（ $E_{fp}$ ）下降。由於電洞的准費米能階（ $E_{fp}$ ）下降，而電洞被氧化物半導體層內部的 bulk deep DOS 俘獲（步驟 S113）。因此，有可能當不施加閘極 BT 應力並照射光時，與黑暗狀態下相比，臨界電壓向負方向漂移，而電晶體容易常導通化。

[0171] 接著，當繼續照射光的狀態下進行負閘極 BT 應力測試時，產生電場梯度，被氧化物半導體層內部的 bulk deep DOS 俘獲的電洞注入到閘極絕緣膜中的非橋氧電洞中心（NBOHC1）（步驟 S114）。此外，如圖 13 所示那樣，由於電場而電洞的一部分移動到閘極絕緣膜的更深的部分中的非橋氧電洞中心（NBOHC2）（步驟 S115）。在閘極絕緣膜中，施加電場的時間越長，從非橋氧電洞中心（NBOHC1）到非橋氧電洞中心（NBOHC2）的電洞移動越進展。閘極絕緣膜中的非橋氧電洞中心（NBOHC1 及 NBOHC2）的電洞像正固定電荷那樣動作，因此使臨界電壓向負方向變化，而電晶體容易常導通化。

[0172] 注意，在此，為了容易理解，以不同的步驟分別示出光照射和負閘極 BT 應力測試，但是不侷限於此。例如，也可以認為步驟 S112 至步驟 S115 都是同時進行的步驟。

[0173] 接著，當繼續照射光的狀態下進行正閘極 BT 應力測試時，由於正閘極電壓的施加，而被氧化物半導體層內部的 bulk deep DOS 俘獲的電洞以及閘極絕緣膜中的

非橋氧電洞中心 (NBOHC1) 中的電洞被釋放 (步驟 S116)。其結果是，臨界電壓向正方向漂移。注意，閘極絕緣膜中的非橋氧電洞中心 (NBOHC2) 位於閘極絕緣膜內部的深位置，因此即使在繼續照射光的狀態下進行正閘極 BT 應力測試，也其中的電洞幾乎不直接被釋放。為了釋放閘極絕緣膜中的非橋氧電洞中心 (NBOHC2) 中的電洞，一旦將該電洞移動到表面一側的閘極絕緣膜中的非橋氧電洞中心 (NBOHC1) 中。從閘極絕緣膜中的非橋氧電洞中心 (NBOHC2) 到非橋氧電洞中心 (NBOHC1) 的電洞移動按照施加電場的時間逐漸發生。因此，臨界電壓的向正方向的漂移量也小，而不能恢復到初期值。

[0174] 此外，在閘極絕緣膜中的非橋氧電洞中心 (NBOHC1) 與氧化物半導體層內部的 bulk deep DOS 之間也發生電洞的移動。但是，氧化物半導體層內部的 bulk deep DOS 已俘獲有很多電洞，由此氧化物半導體層及閘極絕緣膜整體的帶電量幾乎不減少。

[0175] 接著，當繼續照射光的狀態下再次進行負閘極 BT 應力測試時，產生電場梯度，被氧化物半導體層內部的 bulk deep DOS 俘獲的電洞注入到閘極絕緣膜中的非橋氧電洞中心 (NBOHC1) 中。此外，由於電場，而電洞的一部分也被注入閘極絕緣膜的更深的部分中的非橋氧電洞中心 (NBOHC2) (步驟 S117)。注意，在閘極絕緣膜中的非橋氧電洞中心 (NBOHC2) 中不被釋放而殘留有在步驟 S115 中進入的電洞。因此，由於閘極絕緣膜中的非

橋氧電洞中心（NBOHC2）還被注入電洞，像固定電荷那樣動作的電洞個數進一步增多。於是，使臨界電壓向負方向進一步漂移，電晶體更容易常導通化。

[0176] 接著，當繼續照射光的狀態下進行正閘極 BT 應力測試時，由於正閘極電壓的施加，而被氧化物半導體層內部的 bulk deep DOS 俘獲的電洞以及閘極絕緣膜中的非橋氧電洞中心（NBOHC1）中的電洞被釋放（步驟 S118）。其結果是，臨界電壓向正方向漂移。注意，閘極絕緣膜中的非橋氧電洞中心（NBOHC2）中的電洞幾乎不被釋放。因此，臨界電壓的向正方向的漂移量也小，而不能恢復到初期值。

[0177] 如上所述，可以認為藉由在照射光的狀態下，反復進行負閘極 BT 應力測試和正閘極 BT 應力測試，臨界電壓反復向正方向和負方向漂移，在總體上，逐漸向負方向漂移。

[0178] 如上所述，藉由理解氧化物半導體層內部的 bulk deep DOS 以及閘極絕緣膜中的非橋氧電洞中心（NBOHC1 以及 NBOHC2），可以說明光照射狀態下的閘極 BT 應力測試所引起的電晶體的臨界電壓漂移。

[0179]

〈氧化物半導體層的脫水化、脫氫化以及加氧化的過程模型〉

為了使電晶體具有穩定的電特性，重要的是降低氧化物半導體層中以及其界面附近的 DOS（高純度本質化）。

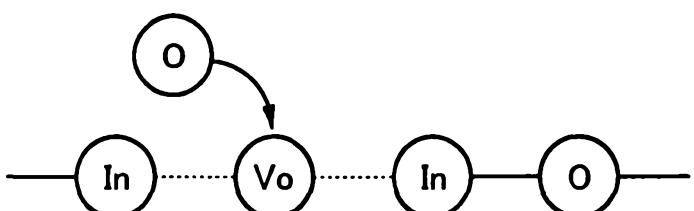

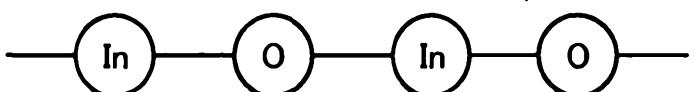

下面，對氧化物半導體層的高純度本質化的過程模型進行說明。首先，對氧化物半導體層的脫水化及脫氫化進行說明，然後對用氧填補氧缺陷（ $\text{V}_\text{O}$ ）的加氧化進行說明。

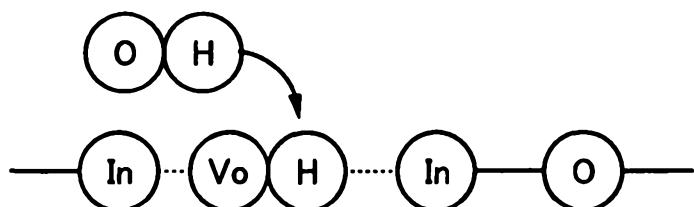

[0180] 下面，對銦與氧的鍵合斷開而形成氧缺陷的模型進行說明。

[0181] 當銦與氧的鍵合斷開時，氧被脫離，與銦鍵合的氧的位點成為氧缺陷。氧缺陷形成氧化物半導體層的位於深能階的 DOS (deep level DOS)。由於氧化物半導體層的氧缺陷不穩定，因此有藉由俘獲氧或氫而處於穩定的趨向。因此，當在氧缺陷的附近存在氫時，氧缺陷藉由俘獲氫而成為  $\text{V}_\text{O}\text{H}$ 。 $\text{V}_\text{O}\text{H}$  形成氧化物半導體層的位於淺能階的 DOS (shallow level DOS)。

[0182] 接著，當氧靠近氧化物半導體層中的  $\text{V}_\text{O}\text{H}$  時，氧從  $\text{V}_\text{O}\text{H}$  奪取氫，使氫脫離而形成羥基 (OH) (參照圖 14A 和圖 14B)。氧在經過加熱處理等時在氧化物半導體層中移動而靠近  $\text{V}_\text{O}\text{H}$ 。

[0183] 另外，當脫離了的羥基靠近氧化物半導體層中的其他的  $\text{V}_\text{O}\text{H}$  時，從  $\text{V}_\text{O}\text{H}$  奪取氫，再次使氫脫離而形成水分子 ( $\text{H}_2\text{O}$ ) (參照圖 14C 和圖 14D)。如上所述，一個氧會使氧化物半導體層中的兩個氫脫離。將這稱為氧化物半導體層的脫水化和脫氫化。藉由脫水化和脫氫化，氧化物半導體層的位於淺能階的 DOS (shallow level DOS) 得到降低，而形成位於深能階的 DOS (deep level DOS)。

[0184] 另外，當氧靠近氧化物半導體層中的氧缺陷時，氧被氧缺陷俘獲，氧缺陷消失（參照圖 14E 和圖 14F）。將這稱為氧化物半導體層的加氧化。藉由加氧化，可以降低氧化物半導體層的位於深能階的 DOS (deep level DOS)。

[0185] 如上所述，藉由上述步驟，進行氧化物半導體層的脫水化、脫氫化以及加氧化，可以降低氧化物半導體層的位於淺能階的 DOS (shallow level DOS) 及位於深能階的 DOS (deep level DOS)。將這稱為氧化物半導體的高純度本質化。

[0186]

〈關於具有多層膜的電晶體的結構以及其製造方法的說明〉

下面，對具有多層膜的電晶體的結構以及其製造方法進行說明。

[0187]

〈電晶體結構（1）〉

首先，對頂閘極頂接觸電晶體的一個例子進行說明。

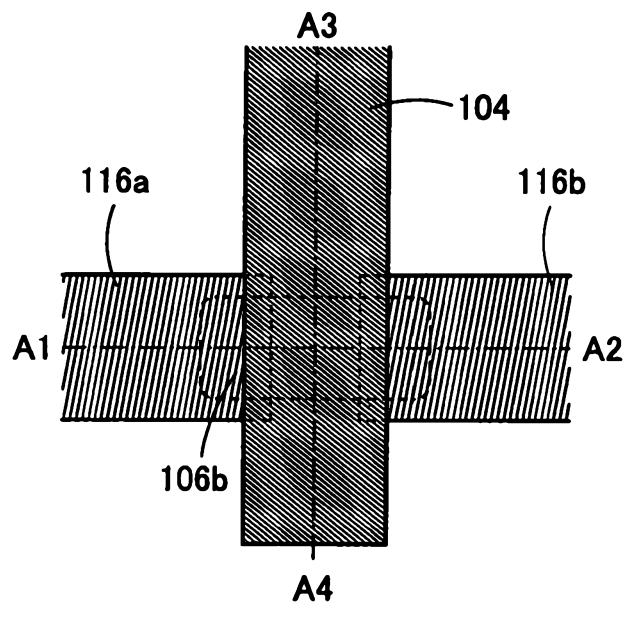

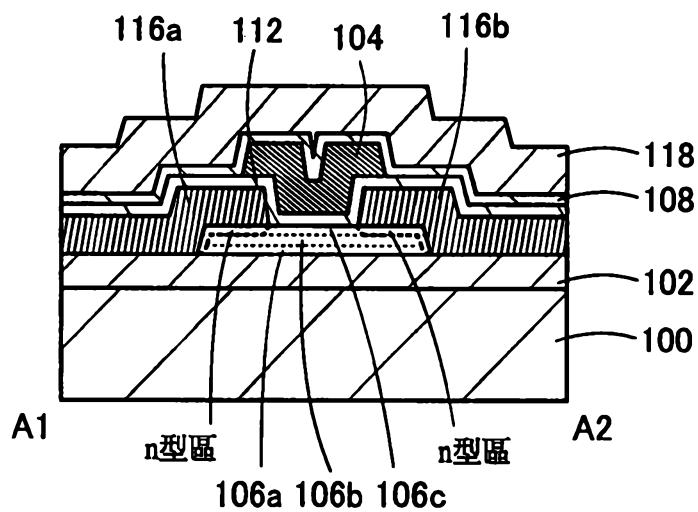

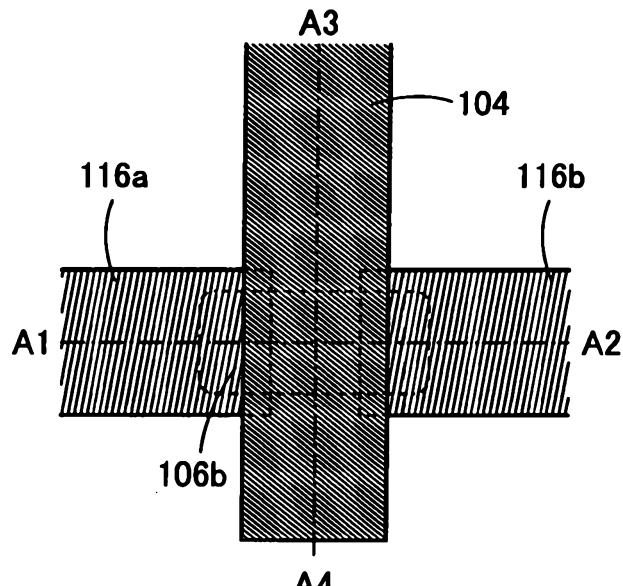

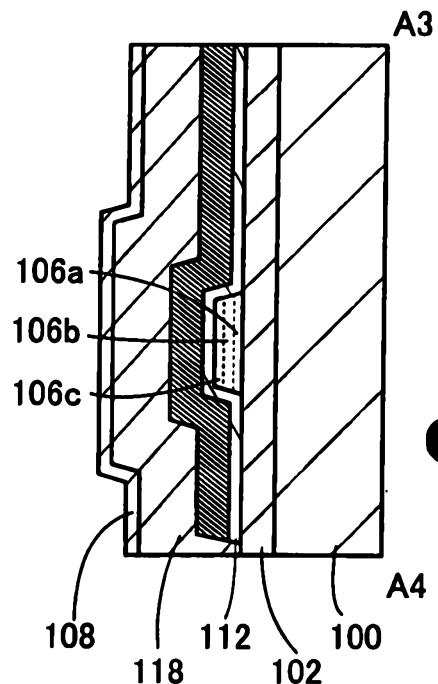

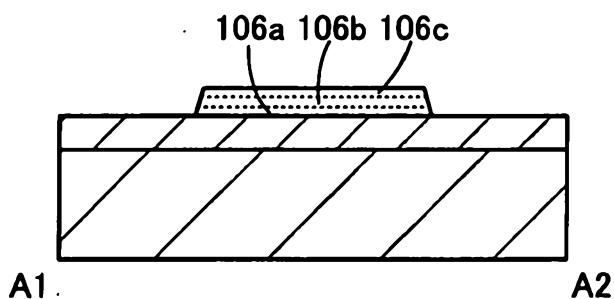

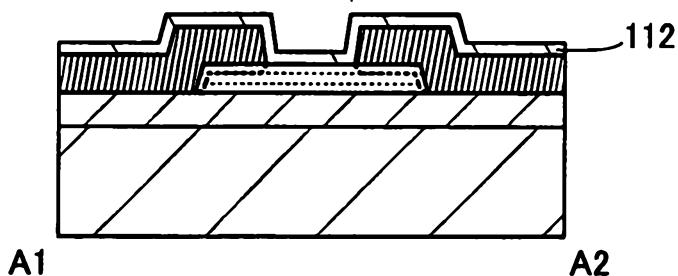

[0188] 圖 15A 至圖 15C 為電晶體的俯視圖及剖面圖。圖 15A 示出電晶體的俯視圖。圖 15B 示出對應於圖 15A 中的點劃線 A1-A2 的剖面圖。另外，圖 15C 示出對應於圖 15A 中的點劃線 A3-A4 的剖面圖。

[0189] 圖 15B 所示的電晶體包括：基板 100 上的基底絕緣膜 102；基底絕緣膜 102 上的氧化物半導體層

106a；氧化物半導體層 106a 上的氧化物半導體層 106b；氧化物半導體層 106b 上的氧化物半導體層 106c；接觸於氧化物半導體層 106c 的源極電極 116a 及汲極電極 116b；氧化物半導體層 106c、源極電極 116a 以及汲極電極 116b 上的閘極絕緣膜 112；閘極絕緣膜 112 上的閘極電極 104。另外，較佳為在閘極絕緣膜 112 及閘極電極 104 上設置保護絕緣膜 108 及保護絕緣膜 108 上的保護絕緣膜 118。另外，電晶體也可以不具有基底絕緣膜 102。

[0190] 此外，在圖 15B 所示的電晶體中，也可以調換保護絕緣膜 108 和保護絕緣膜 118 的疊層順序（參照圖 16A 至圖 16C）。有時與在圖 15A 至圖 15C 所示的電晶體中相比，在圖 16A 至圖 16C 所示的電晶體中不容易發生從基底絕緣膜 102 釋放的過剩氧的外方擴散。因此，與在圖 15A 至圖 15C 所示的電晶體中相比，在圖 16A 至圖 16C 所示的電晶體中，有可以降低氧化物半導體層 106a、氧化物半導體層 106b 以及氧化物半導體層 106c 中的氧缺陷（可以降低 DOS）的可能性。

[0191] 圖 15A 至圖 15C 所示的電晶體中的氧化物半導體層 106a 例如對應於圖 1A 所示的氧化物半導體層（S1）。圖 15A 至圖 15C 所示的電晶體中的氧化物半導體層 106b 例如對應於圖 1A 所示的氧化物半導體層（S2）。圖 15A 至圖 15C 所示的電晶體中的氧化物半導體層 106c 例如對應於圖 1A 所示的氧化物半導體層（S3）。

[0192] 另外，圖 15A 至圖 15C 所示的電晶體的基底絕緣膜 102 例如相當於圖 5A 所示的電晶體的閘極絕緣膜 (bg)。另外，圖 15A 至圖 15C 所示的電晶體例如可以具有圖 5A 所示的電晶體的閘極電極 (bg)。圖 15A 至圖 15C 所示的電晶體例如也可以具有與閘極電極 104 對置且接觸於基底絕緣膜 102 的底面的背閘極電極。另外，在圖 15A 至圖 15C 所示的電晶體中，在基板 100 具有導電性的情況下，例如，基板 100 可以相當於圖 5A 所示的電晶體的閘極絕緣膜 (bg)。另外，在圖 15A 至圖 15C 所示的電晶體中，在基底絕緣膜 102 下設置有佈線等的導電膜的情況下，該導電膜也可以相當於圖 5A 所示的電晶體的閘極絕緣膜 (bg)。

[0193] 另外，用於源極電極 116a 及汲極電極 116b 的導電膜的有些材料有可能抽出氧化物半導體層 106b 和氧化物半導體層 106c 的一部分中的氧，或者形成混合層而在氧化物半導體層 106b 和氧化物半導體層 106c 中形成 n 型區（低電阻區）。

[0194] 在圖 15A 中，將重疊於閘極電極 104 的區域中的源極電極 116a 與汲極電極 116b 之間的間隔稱為通道長度。注意，在電晶體包括 n 型區的情況下，也可以將重疊於閘極電極 104 的區域中的源極區與汲極區之間的間隔稱為通道長度。

[0195] 另外，通道形成區是指氧化物半導體層 106a、氧化物半導體層 106b 以及氧化物半導體層 106c 中

的重疊於閘極電極 104 且夾在源極電極 116a 與汲極電極 116b 之間的區域（參照圖 15B）。另外，通道是指通道形成區中的電流主要流過的區域。

[0196] 另外，如圖 15A 的俯視圖所示，氧化物半導體層 106b 的一部分設置在閘極電極 104 的外側。注意，氧化物半導體層 106b 的整體也可以設置在閘極電極 104 的內側。由此，當光從閘極電極 104 一側入射時，可以抑制因光而在氧化物半導體層 106b 中產生載子。換言之，閘極電極 104 具有遮光膜的功能。

[0197] 下面，對氧化物半導體層 106a、氧化物半導體層 106b 以及氧化物半導體層 106c 進行說明。

[0198] 氧化物半導體層 106b 為包含銦的氧化物。氧化物例如在包含銦的情況下具有高載子移動率（電子移動率）。另外，氧化物半導體層 106b 較佳為包含元素 M。元素 M 例如為鋁、鎵、釔或錫等。例如，元素 M 與氧之間的鍵能高。元素 M 例如增大氧化物的能隙。此外，氧化物半導體層 106b 較佳為包含鋅。例如，氧化物在包含鋅時容易被晶化。氧化物的價帶頂的能量例如可以由鋅的原子數比控制。

[0199] 注意，氧化物半導體層 106b 不侷限於包含銦的氧化物。氧化物半導體層 106b 例如也可以為 Zn-Sn 氧化物、Ga-Sn 氧化物。

[0200] 氧化物半導體層 106a 包含一種或多種構成氧化物半導體層 106b 的除了氧以外的元素。由於氧化物半

導體層 106a 包含一種或多種構成氧化物半導體層 106b 的除了氧以外的元素，因此在氧化物半導體層 106b 與氧化物半導體層 106a 之間的介面不容易形成 DOS。

[0201] 氧化物半導體層 106c 包含一種或多種構成氧化物半導體層 106b 的除了氧以外的元素。由於氧化物半導體層 106c 包含一種或多種構成氧化物半導體層 106b 的除了氧以外的元素，因此在氧化物半導體層 106b 與氧化物半導體層 106c 之間的介面不容易形成 DOS。

[0202] 另外，在氧化物半導體層 106a 為 In-M-Zn 氧化物且在 In 和 M 的總和為 100atomic%的情況下，較佳的是，In 的比率低於 50atomic%，M 的比率為 50atomic%以上，更佳的是，In 的比率低於 25atomic%，M 的比率為 75atomic%以上。另外，在氧化物半導體層 106b 為 In-M-Zn 氧化物且在 In 和 M 的總和為 100atomic%的情況下，較佳的是，In 的比率為 25atomic%以上，M 的比率低於 75atomic%，更佳的是，In 的比率為 34atomic%以上，M 的比率低於 66atomic%。另外，在氧化物半導體層 106c 為 In-M-Zn 氧化物且在 In 和 M 的總和為 100atomic%的情況下，較佳的是，In 的比率低於 50atomic%，M 的比率為 50atomic%以上，更佳的是，In 的比率低於 25atomic%，M 的比率為 75atomic%以上。注意，氧化物半導體層 106c 也可以使用與氧化物半導體層 106a 相同的氧化物。

[0203] 在此，在氧化物半導體層 106a 與氧化物半導體層 106b 之間有時形成有氧化物半導體層 106a 和氧化物

半導體層 106b 的混合區。另外，在氧化物半導體層 106b 與氧化物半導體層 106c 之間有時形成有氧化物半導體層 106b 和氧化物半導體層 106c 的混合區。混合區的 DOS 較少。因此，在氧化物半導體層 106a、氧化物半導體層 106b 以及氧化物半導體層 106c 的疊層體的能帶結構中，各層之間的介面附近的能量連續地變化（也稱為連接結合）（參照圖 28）。注意，EcA 表示氧化物半導體層 106a 的傳導帶底的能量，EcB 表示氧化物半導體層 106b 的傳導帶底的能量，EcC 表示氧化物半導體層 106c 的傳導帶底的能量。

[0204] 另外，氧化物半導體層 106b 使用能隙寬的氧化物。氧化物半導體層 106b 的能隙例如為 2.5eV 以上且 4.2eV 以下，較佳為 2.8eV 以上且 3.8eV 以下，更佳為 3eV 以上且 3.5eV 以下。另外，氧化物半導體層 106c 的能隙例如為 2.7eV 以上且 4.9eV 以下，較佳為 3eV 以上且 4.7eV 以下，更佳為 3.2eV 以上且 4.4eV 以下。

[0205] 另外，氧化物半導體層 106a 使用能隙寬的氧化物。例如，氧化物半導體層 106a 的能隙為 2.7eV 以上且 4.9eV 以下，較佳為 3eV 以上且 4.7eV 以下，更佳為 3.2eV 以上且 4.4eV 以下。

[0206] 另外，氧化物半導體層 106c 使用能隙寬的氧化物。例如，氧化物半導體層 106c 的能隙為 2.7eV 以上且 4.9eV 以下，較佳為 3eV 以上且 4.7eV 以下，更佳為 3.2eV 以上且 4.4eV 以下。注意，氧化物半導體層 106a 及

氧化物半導體層 106c 的能隙比氧化物半導體層 106b 寬。

[0207] 氧化物半導體層 106b 使用其電子親和力大於氧化物半導體層 106a 的氧化物。例如，氧化物半導體層 106b 使用如下氧化物，該氧化物的電子親和力比氧化物半導體層 106a 大 0.07eV 以上且 1.3eV 以下，較佳大 0.1eV 以上且 0.7eV 以下，更佳大 0.15eV 以上且 0.4eV 以下。這裡，電子親和力是指真空能階與導帶底之間的能量差。

[0208] 另外，氧化物半導體層 106b 使用其電子親和力大於氧化物半導體層 106c 的氧化物。例如，氧化物半導體層 106b 使用如下氧化物，該氧化物的電子親和力比氧化物半導體層 106c 大 0.07eV 以上且 1.3eV 以下，較佳大 0.1eV 以上且 0.7eV 以下，更佳大 0.15eV 以上且 0.4eV 以下。

[0209] 在此，當對閘極電極 104 施加電場時，在氧化物半導體層 106a、氧化物半導體層 106b 和氧化物半導體層 106c 中的電子親和力大的氧化物即氧化物半導體層 106b 中形成通道。

[0210] 此外，如使用圖 1A 至圖 4 進行說明那樣，為了提高電晶體的通態電流，氧化物半導體層 106c 的厚度越小越好。例如，將氧化物半導體層 106c 的厚度設定為小於 10nm，較佳為 5nm 以下，更佳為 3nm 以下。另一方面，氧化物半導體層 106c 具有防止構成閘極絕緣膜 112 的氧以外的元素（矽等）進入被形成通道的氧化物半導體

層 106b 的功能。因此，氧化物半導體層 106c 較佳為具有一定的厚度。例如，將氧化物半導體層 106c 的厚度設定為 0.3nm 以上，較佳為 1nm 以上，更佳為 2nm 以上。

[0211] 另外，如上述電晶體的劣化模型所示，較佳的是氧化物半導體層 106a 厚，氧化物半導體層 106b 薄，氧化物半導體層 106c 薄。明確而言，氧化物半導體層 106a 的厚度為 20nm 以上，較佳為 30nm 以上，更佳為 40nm 以上，進一步較佳為 60nm 以上。藉由將氧化物半導體層 106a 的厚度設定為 20nm 以上，較佳為 30nm 以上，更佳為 40nm 以上，進一步較佳為 60nm 以上，可以將基底絕緣膜 102 和氧化物半導體層 106a 的界面與通道形成在其中的氧化物半導體層 106b 之間的距離設定為 20nm 以上，較佳為 30nm 以上，更佳為 40nm 以上，進一步較佳為 60nm 以上。注意，這有可能使半導體裝置的生產率下降，因此將氧化物半導體層 106a 的厚度設定為 200nm 以下，較佳為 120nm 以下，更佳為 80nm 以下。另外，將氧化物半導體層 106b 的厚度設定為 3nm 以上且 100nm 以下，較佳為 3nm 以上且 80nm 以下，更佳為 3nm 以上且 50nm 以下。

[0212] 例如，使氧化物半導體層 106a 的厚度大於氧化物半導體層 106b，並且，使氧化物半導體層 106b 的厚度大於氧化物半導體層 106c，即可。

[0213] 雖然在此對包括氧化物半導體層 106a、氧化物半導體層 106b 及氧化物半導體層 106c 的三層的多層膜

進行說明，但是不侷限於此。例如，也可以採用氧化物半導體層 106b 的單層。此外，例如，也可以採用氧化物半導體層 106a 與氧化物半導體層 106b 的兩層的多層膜，或者氧化物半導體層 106b 與氧化物半導體層 106c 的兩層的多層膜。此外，例如，也可以採用在氧化物半導體層 106a 與氧化物半導體層 106b 之間設有氧化物半導體層的四層以上的多層膜。在此情況下，氧化物半導體層 106a 與氧化物半導體層 106b 之間的氧化物半導體層例如使用具有氧化物半導體層 106a 以上且氧化物半導體層 106b 以下的電子親和力的氧化物。此外，例如，也可以採用在氧化物半導體層 106c 與氧化物半導體層 106b 之間設有氧化物半導體層的四層以上的多層膜。在此情況下，氧化物半導體層 106c 與氧化物半導體層 106b 之間的氧化物半導體層例如使用具有氧化物半導體層 106c 以上且氧化物半導體層 106b 以下的電子親和力的氧化物。

[0214] 另外，當利用濺射法形成氧化物半導體層 106a、氧化物半導體層 106b 以及氧化物半導體層 106c 時，為了抑制微粒數的增大，較佳為使用包含銦的靶材。另外，當使用元素 M 的原子數比高的氧化物靶材時，靶材的導電性有可能下降。元素 M 例如為鋁、鎵、釔或錫等。當使用包含銦的靶材時，可以提高靶材的導電率，容易進行 DC 放電、AC 放電，因此容易在大面積基板上進行成膜。因此，可以提高半導體裝置的生產率。

[0215] 當利用濺射法形成氧化物半導體層 106a 時，

可以將靶材的原子數比設定為  $In:M:Zn=1:1:0.5$ 、 $1:1:1$ 、 $1:1:2$ 、 $1:3:1$ 、 $1:3:2$ 、 $1:3:4$ 、 $1:3:6$ 、 $1:6:2$ 、 $1:6:4$ 、 $1:6:6$ 、 $1:6:8$ 、 $1:6:10$ 、 $1:9:2$ 、 $1:9:4$ 、 $1:9:6$ 、 $1:9:8$ 、 $1:9:10$  等。

[0216] 當利用濺射法形成氧化物半導體層 106b 時，可以將靶材的原子數比設定為  $In:M:Zn=3:1:1$ 、 $3:1:2$ 、 $3:1:4$ 、 $1:1:0.5$ 、 $1:1:1$ 、 $1:1:2$  等。

[0217] 當利用濺射法形成氧化物半導體層 106c 時，可以將靶材的原子數比設定為  $In:M:Zn=1:1:0.5$ 、 $1:1:1$ 、 $1:1:2$ 、 $1:3:1$ 、 $1:3:2$ 、 $1:3:4$ 、 $1:3:6$ 、 $1:6:2$ 、 $1:6:4$ 、 $1:6:6$ 、 $1:6:8$ 、 $1:6:10$ 、 $1:9:2$ 、 $1:9:4$ 、 $1:9:6$ 、 $1:9:8$ 、 $1:9:10$  等。

[0218] 當利用濺射法形成氧化物半導體層 106a、氧化物半導體層 106b 以及氧化物半導體層 106c 時，形成之後的膜的原子數比有時與靶材的原子數比不一致。尤其是，形成之後的膜中的鋅的原子數比有時小於靶材中的鋅的原子數比。明確而言，該膜中的鋅的原子數比有時為靶材中的鋅的原子數比的 40atomic% 以上且 90atomic% 以下左右。

[0219] 下面，說明氧化物中的矽的影響。另外，為了使電晶體的電特性穩定，降低氧化物半導體層 106b 中的雜質濃度而實現高純度本質是有效的。另外，氧化物半導體層 106b 的載子密度小於  $1 \times 10^{17}/\text{cm}^3$ 、小於  $1 \times 10^{15}/\text{cm}^3$  或小於  $1 \times 10^{13}/\text{cm}^3$ 。另外，在氧化物中，主要

成分以外（小於 1 atomic%）的輕元素、半金屬元素以及金屬元素等為雜質。例如，在氧化物中，氫、鋰、碳、氮、氟、鈉、矽、氯、鉀、鈣、鈦、鐵、鎳、銅、鋒、銑、鋯以及鉿都有可能成為雜質。因此，較佳為還降低附近的膜中的雜質濃度。

[0220] 例如，如上所述，當氧化物包含矽時，有可能形成 DOS。另外，當在氧化物半導體層 106b 的表層存在矽時，有可能形成 DOS。因此，將氧化物半導體層 106b 與氧化物半導體層 106a 之間的矽濃度設定為小於  $1 \times 10^{19} \text{ atoms/cm}^3$ 、較佳小於  $5 \times 10^{18} \text{ atoms/cm}^3$ 、更佳小於  $2 \times 10^{18} \text{ atoms/cm}^3$ 。另外，將氧化物半導體層 106b 與氧化物半導體層 106c 之間的矽濃度設定為小於  $1 \times 10^{19} \text{ atoms/cm}^3$ 、較佳小於  $5 \times 10^{18} \text{ atoms/cm}^3$ 、更佳小於  $2 \times 10^{18} \text{ atoms/cm}^3$ 。

[0221] 另外，如上所述，氫在氧化物中有可能形成 DOS 而使載子密度增大。將利用二次離子質譜（SIMS：Secondary Ion Mass Spectrometry）分析測定出的氧化物半導體層 106b 中的氫濃度設定為  $2 \times 10^{20} \text{ atoms/cm}^3$  以下，較佳為  $5 \times 10^{19} \text{ atoms/cm}^3$  以下，更佳為  $1 \times 10^{19} \text{ atoms/cm}^3$  以下，進一步較佳為  $5 \times 10^{18} \text{ atoms/cm}^3$  以下。另外，氮在氧化物中有可能形成 DOS 而使載子密度增大。將利用 SIMS 測定出的氧化物半導體層 106b 中的氮濃度設定為小於  $5 \times 10^{19} \text{ atoms/cm}^3$ ，較佳為  $5 \times 10^{18} \text{ atoms/cm}^3$  以下，更佳為  $1 \times 10^{18} \text{ atoms/cm}^3$  以下，進一步較佳為  $5 \times 10^{17} \text{ atoms/cm}^3$  以

下。

[0222] 另外，爲了降低氧化物半導體層 106b 中的氫濃度，較佳爲降低氧化物半導體層 106a 中的氫濃度。將利用 SIMS 測定出的氧化物半導體層 106a 中的氫濃度設定爲  $2 \times 10^{20} \text{ atoms/cm}^3$  以下，較佳爲  $5 \times 10^{19} \text{ atoms/cm}^3$  以下，更佳爲  $1 \times 10^{19} \text{ atoms/cm}^3$  以下，進一步較佳爲  $5 \times 10^{18} \text{ atoms/cm}^3$  以下。另外，爲了降低氧化物半導體層 106b 中的氮濃度，較佳爲降低氧化物半導體層 106a 中的氮濃度。將利用 SIMS 測定出的氧化物半導體層 106a 中的氮濃度設定爲小於  $5 \times 10^{19} \text{ atoms/cm}^3$ ，較佳爲  $5 \times 10^{18} \text{ atoms/cm}^3$  以下，更佳爲  $1 \times 10^{18} \text{ atoms/cm}^3$  以下，進一步較佳爲  $5 \times 10^{17} \text{ atoms/cm}^3$  以下。

[0223] 另外，爲了降低氧化物半導體層 106b 中的氫濃度，較佳爲降低氧化物半導體層 106c 中的氫濃度。將利用 SIMS 測定出的氧化物半導體層 106c 中的氫濃度設定爲  $2 \times 10^{20} \text{ atoms/cm}^3$  以下，較佳爲  $5 \times 10^{19} \text{ atoms/cm}^3$  以下，更佳爲  $1 \times 10^{19} \text{ atoms/cm}^3$  以下，進一步較佳爲  $5 \times 10^{18} \text{ atoms/cm}^3$  以下。另外，爲了降低氧化物半導體層 106b 中的氮濃度，較佳爲降低氧化物半導體層 106c 中的氮濃度。將利用 SIMS 測定出的氧化物半導體層 106c 中的氮濃度設定爲小於  $5 \times 10^{19} \text{ atoms/cm}^3$ ，較佳爲  $5 \times 10^{18} \text{ atoms/cm}^3$  以下，更佳爲  $1 \times 10^{18} \text{ atoms/cm}^3$  以下，進一步較佳爲  $5 \times 10^{17} \text{ atoms/cm}^3$  以下。

[0224] 下面，對可用於氧化物半導體層 106b 等的氧

化物半導體的結構進行說明。氧化物半導體例如可以包括非單晶。非單晶例如由 CAAC ( C Axis Aligned Crystal : c 軸配向結晶 ) 、多晶、微晶或非晶部中的至少一個構成。

[0225] 氧化物半導體也例如可以具有 CAAC。注意，將包括 CAAC 的氧化物半導體稱為 CAAC-OS ( C Axis Aligned Crystalline Oxide Semiconductor : c 軸配向結晶氧化物半導體 ) 。

[0226] 例如，有時可以在使用穿透式電子顯微鏡 ( TEM : Transmission Electron Microscope ) 得到的影像中 ( 以下，稱為 TEM 影像 ) ，確認到 CAAC-OS 中的結晶部。另外，在大多情況下，例如在 TEM 影像中，包含在 CAAC-OS 中的結晶部的尺寸為能夠容納在一個邊長為 100nm 的立方體內的尺寸。此外，在 TEM 影像中，有時無法明確地確認到 CAAC-OS 中的非晶部與結晶部之間的邊界、結晶部與結晶部之間的邊界。此外，在 TEM 影像中，有時無法明確地確認到 CAAC-OS 中的晶界 ( grain boundary ) 。CAAC-OS 例如不具有明確的晶界，所以不容易產生雜質的偏析。另外，CAAC-OS 例如不具有明確的晶界，所以缺陷密度很少變高 ( DOS 變多 ) 。另外，CAAC-OS 例如不具有明確的晶界，所以電子移動率的低下較小。

[0227] CAAC-OS 例如具有多個結晶部，有時在該多個結晶部中 c 軸在平行於形成有 CAAC-OS 的表面的法線向量或 CAAC-OS 的表面的法線向量的方向上一致。此

外，例如使用 X 射線繞射（XRD：X-Ray Diffraction）裝置，並且利用 out-of-plane 法來分析 CAAC-OS，有時在表示配向的  $2\theta$  為  $31^\circ$  附近觀察到峰值。另外，有時在 CAAC-OS 的電子繞射圖案中，例如觀察到斑點（亮點）。注意，尤其將使用電子束徑為  $10\text{nm}\phi$  以下或  $5\text{nm}\phi$  以下的電子線而得到的電子繞射圖案稱為奈米電子束繞射圖案。另外，CAAC-OS 例如在不同的結晶部間，有時 a 軸及 b 軸的方向不同。在 CAAC-OS 中，例如有時 c 軸配向且 a 軸或/及 b 軸在宏觀上不一致。

[0228] 圖 29A 是包括 CAAC-OS 的樣本的奈米電子束繞射圖案的一個例子。在此，將樣本沿著垂直於形成有 CAAC-OS 的表面的方向截斷，將其薄片化以使其厚度為  $40\text{nm}$  左右。此外，在此使電子束徑為  $1\text{nm}\phi$  的電子線從垂直於樣本的截斷面的方向入射。藉由圖 29A 可知，在 CAAC-OS 的奈米電子束繞射圖案中可以觀察到斑點。藉由使用氬離子的離子銑削（ion milling）法進行樣本的薄片化。

[0229] 在包括在 CAAC-OS 中的結晶部中，例如 c 軸在平行於形成有 CAAC-OS 的表面的法線向量或 CAAC-OS 的表面的法線向量的方向上一致。並且，當從垂直於 ab 面的方向看時金屬原子排列為三角形或六角形，且當從垂直於 c 軸的方向看時，金屬原子排列為層狀或者金屬原子和氧原子排列為層狀。另外，在不同結晶部之間 a 軸和 b 軸的方向可以不同。在本說明書中，“垂直”的用語包括

80°到 100°的範圍，較佳為包括 85°到 95°的範圍。並且，“平行”的用語包括 -10°到 10°的範圍，較佳為包括 -5°到 5°的範圍。

[0230] 因為包括在 CAAC-OS 中的結晶部的 c 軸在平行於形成有 CAAC-OS 的表面的法線向量或 CAAC-OS 的表面的法線向量的方向上一致，所以有時根據 CAAC-OS 的形狀（形成有 CAAC-OS 的表面的剖面形狀或 CAAC-OS 的表面的剖面形狀）c 軸的方向可以彼此不同。另外，結晶部在成膜時或在成膜後藉由諸如加熱處理等晶化處理而形成。因此，結晶部的 c 軸在平行於形成有 CAAC-OS 的表面的法線向量或 CAAC-OS 的表面的法線向量的方向上一致。

[0231] CAAC-OS 例如有時可以藉由降低雜質濃度來形成。在此，雜質是指氫、碳、矽以及過渡金屬元素等氧化物半導體的主要成分以外的元素。特別是，矽等元素與氧的鍵合力比構成氧化物半導體的金屬元素與氧的鍵合力強。因此，當該元素從氧化物半導體奪取氧時，有時打亂氧化物半導體的原子排列，使結晶性下降。另外，由於鐵或鎳等的重金屬、氬、二氧化碳等的原子半徑（或分子半徑）大，所以有時會打亂氧化物半導體的原子排列，導致氧化物半導體的結晶性下降。因此，CAAC-OS 是雜質濃度低的氧化物半導體。此外，包含在氧化物半導體中的雜質有時成為載子發生源。

[0232] 另外，在 CAAC-OS 中，結晶部的分佈也可以

不均勻。例如，在 CAAC-OS 的形成過程中，在從氧化物半導體的表面一側進行結晶生長的情況下，有時氧化物半導體的表面附近的結晶部所占的比例高於形成有氧化物半導體的表面附近的結晶部所占的比例。此外，當雜質混入到 CAAC-OS 時，有時在該混入有雜質的區域中結晶部會非晶化或微晶化。

[0233] 另外，CAAC-OS 例如可以藉由降低 DOS 形成。例如，如上所述，在氧化物半導體中，氧缺陷形成 DOS。氧缺陷有時成為電洞陷阱或因俘獲氫而成為載子發生源。為了形成 CAAC-OS，例如重要的是不使在氧化物半導體中產生氧缺陷。因此，CAAC-OS 是 DOS 少的氧化物半導體。或者，CAAC-OS 是氧缺陷少的氧化物半導體。

[0234] 將雜質濃度低且 DOS 少（氧缺陷的個數少）的狀態稱為“高純度本質”或“實質上高純度本質”。高純度本質或實質上高純度本質的氧化物半導體具有較少的載子發生源，因此有時可以降低其載子密度。因此，有時將該氧化物半導體用於通道形成區的電晶體很少具有負臨界電壓（也稱為常開啓特性）。此外，高純度本質或實質上高純度本質的氧化物半導體包括較少的 DOS，因此有時電荷陷阱也變少。因此，有時將該氧化物半導體用於通道形成區的電晶體的電特性變動小，而成為可靠性高的電晶體。此外，被氧化物半導體的電洞陷阱俘獲的電洞直到被釋放為止需要較長的時間，有時像固定電荷那樣動作。因

此，有時將電洞陷阱多的氧化物半導體用於通道形成區的電晶體的電特性不穩定。

[0235] 另外，在使用高純度本質或實質上高純度本質的 CAAC-OS 的電晶體中，起因於可見光或紫外光的照射的電特性變動小。

[0236] CAAC-OS 例如可以藉由使用 DC 電源的濺射法來形成。

[0237] 氧化物半導體例如可以包括多晶。注意，將包括多晶的氧化物半導體稱為多晶氧化物半導體。多晶氧化物半導體包括多個晶粒。多晶氧化物半導體有時例如包括非晶部。

[0238] 在 TEM 影像中，例如有時可以觀察到多晶氧化物半導體中的晶粒。多晶氧化物半導體所包括的晶粒例如在使用 TEM 的觀察影像中，在大多數情況下，粒徑為 2nm 以上且 300nm 以下、3nm 以上且 100nm 以下或 5nm 以上且 50nm 以下。此外，在 TEM 影像中，例如有時可以確認到多晶氧化物半導體中的非晶部與晶粒之間的邊界、晶粒與晶粒之間的邊界。此外，例如在 TEM 影像中，有時可以確認到多晶氧化物半導體中的晶界。

[0239] 多晶氧化物半導體例如具有多個晶粒，該多個晶粒有時配向不同。此外，多晶氧化物半導體例如使用 XRD 裝置並採用 out-of-plane 法進行分析，有時出現單一或多個峰值。例如，在多晶 IGZO 膜中，有時出現表示配向的  $2\theta$  為  $31^\circ$  附近的峰值或表示多種配向的多個峰值。此

外，多晶氧化物半導體例如在利用電子繞射而得到的圖案中，有時觀察到斑點。

[0240] 因為多晶氧化物半導體例如具有較高的結晶性，所以有時具有較高的電子移動率。因此，將多晶氧化物半導體用於通道形成區的電晶體具有較高的場效移動率。注意，多晶氧化物半導體有時在晶界產生雜質的偏析。此外，多晶氧化物半導體的晶界成為缺陷。由於多晶氧化物半導體的晶界有時成為載子發生源、電荷陷阱，因此有時與將 CAAC-OS 用於通道形成區的電晶體相比，將多晶氧化物半導體用於通道形成區的電晶體的電特性變動較大，且可靠性較低。

[0241] 多晶氧化物半導體可以使用高溫加熱處理或雷射處理來形成。

[0242] 氧化物半導體膜例如可以包括微晶。注意，將包括微晶的氧化物半導體稱為微晶氧化物半導體。

[0243] 在 TEM 影像中，例如有時無法明確地確認到微晶氧化物半導體中的結晶部。微晶氧化物半導體中含有的結晶部的尺寸在大多數情況下為 1nm 以上且 100nm 以下，或 1nm 以上且 10nm 以下。尤其是，例如將 1nm 以上且 10nm 以下的微晶稱為奈米晶 (nc:nanocrystal)。將具有奈米晶的氧化物半導體稱為 nc-OS (nanocrystalline Oxide Semiconductor)。此外，在 TEM 影像中，例如有時無法明確地確認到 nc-OS 中的非晶部與結晶部之間的邊界、結晶部與結晶部之間的邊界。此外，在使用 TEM 觀

察的 nc-OS 的影像中，例如由於不具有明確的晶界，所以很少產生雜質的偏析。另外，nc-OS 例如不具有明確的晶界，所以 DOS 很少變多。另外，nc-OS 例如不具有明確的晶界，所以電子移動率的低下較小。

[0244] nc-OS 例如在微小區域（例如 1nm 以上且 10nm 以下的區域）中有時其原子排列具有週期性。此外，nc-OS 例如在結晶部與結晶部之間沒有規律性，所以有時在宏觀上觀察不到原子排列的週期性，或者有時觀察不到長程有序。因此，例如根據分析方法，有時無法辨別 nc-OS 與非晶氧化物半導體。例如使用 XRD 裝置，並且利用電子束徑比結晶部大的 X 線的 out-of-plane 法來分析 nc-OS，有時檢測不到表示配向的峰值。此外，nc-OS 例如在使用電子束徑比結晶部大（例如  $20\text{nm}\phi$  以上或  $50\text{nm}\phi$  以上）的電子線而得到的電子繞射圖案中，有時可以觀察到光暈圖案。此外，nc-OS 例如在使用其電子束徑與結晶部大小相同或比結晶部小（例如  $10\text{nm}\phi$  以下或  $5\text{nm}\phi$  以下）的電子線而得到的奈米電子束繞射圖案中，有時可以觀察到斑點。此外，在 nc-OS 的奈米電子束繞射圖案中，例如有時觀察到如圓圈那樣的亮度高的區域。此外，在 nc-OS 的奈米電子束繞射圖案中，例如有時在該區域內觀察到多個斑點。

[0245] 圖 29B 是包括 nc-OS 的樣本的奈米電子束繞射圖案的一個例子。在此，將樣本沿著垂直於形成有 nc-OS 的表面的方向截斷，將其薄片化以使其厚度為 40nm 左

右。此外，在此使電子束徑爲  $1\text{nm}\phi$  的電子線從垂直於樣本的截斷面的方向入射。藉由圖 29B 可知，在 nc-OS 的奈米電子束繞射圖案中可以觀察到如圓圈那樣的亮度高的區域，並且在該區域中觀察到多個斑點。藉由使用氬離子的離子銑削 (ion milling) 法進行樣本的薄片化。

[0246] 圖 29C1 和圖 29C2 是包括 nc-OS 的樣本的奈米電子束繞射圖案的一個例子。在此，將樣本沿著垂直於形成有 nc-OS 的表面的方向截斷，將其薄片化以使其厚度爲  $5\text{nm}$  至  $10\text{nm}$  左右。此外，藉由在此使電子束徑爲  $1\text{nm}\phi$  的電子線從垂直於樣本的截斷面的方向入射，根據觀察的位置，在測量部分 1 中觀察到斑點（參照圖 29C1），在測量部分 2 中觀察到如圓圈那樣的亮度高的區域（參照圖 29C2）。這有可能是因爲如下緣故：在如圓圈那樣的亮度高的區域中，由於電子線透過顆粒狀結晶，而觀察到在縱深方向上存在的其他顆粒狀結晶的斑點。藉由以低角度（ $3^\circ$ 左右）使氬離子入射的離子銑削 (ion milling) 法進行樣本的薄片化。

[0247] 由於有時 nc-OS 在微小區域中原子排列具有週期性，因此其 DOS 比非晶氧化物半導體少。注意，由於 nc-OS 的結晶部與結晶部之間沒有規律性，因此與 CAAC-OS 相比，有時 nc-OS 的 DOS 變多。

[0248] 因此，與 CAAC-OS 相比，有時 nc-OS 的載子密度較高。有時載子密度較高的氧化物半導體的電子移動率較高。因此，將 nc-OS 用於通道形成區的電晶體有時具

有較高的場效移動率。另外，因為與 CAAC-OS 相比，nc-OS 的 DOS 較多以有時電荷陷阱也變多。因此，有時與將 CAAC-OS 用於通道形成區的電晶體相比，將 nc-OS 用於通道形成區的電晶體的電特性變動較大，且可靠性較低。注意，因為 nc-OS 即使包含較多量的雜質也可以形成，所以 nc-OS 比 CAAC-OS 更容易形成，有時可以根據用途適當地使用。例如，也可以藉由使用 AC 電源的濺射法等成膜方法來形成 nc-OS。由於使用 AC 電源的濺射法可以在大尺寸基板上均勻地成膜，因此，具有將 nc-OS 用於通道形成區的電晶體的半導體裝置的生產性較高。

[0249] 氧化物半導體例如可以包括非晶部。注意，將包括非晶部的氧化物半導體稱為非晶氧化物半導體。非晶氧化物半導體例如具有無秩序的原子排列且不具有結晶部。或者，非晶氧化物半導體例如具有像石英那樣的無定形狀態，其原子排列沒有規律性。

[0250] 例如，在 TEM 影像中，有時無法觀察到非晶氧化物半導體中的結晶部。

[0251] 非晶氧化物半導體例如在使用 XRD 裝置並採用 out-of-plane 法進行分析時，有時檢測不到表示配向的峰值。此外，非晶氧化物半導體例如在利用電子繞射而得到的圖案中，有時觀察到光暈圖案。此外，非晶氧化物半導體例如在利用奈米電子束繞射而得到的圖案中，有時觀察不到斑點，而觀察到光暈圖案。

[0252] 有時非晶氧化物半導體可以藉由包含高濃度

的氫等雜質來形成。因此，非晶氧化物半導體例如是包含高濃度的雜質的氧化物半導體。

[0253] 當高濃度的雜質包含在氧化物半導體中時，有時在氧化物半導體中形成氧缺陷等 DOS。因此，雜質濃度高的非晶氧化物半導體的 DOS 較多。此外，因為非晶氧化物半導體的結晶性較低，所以與 CAAC-OS 或 nc-OS 相比，非晶氧化物半導體的 DOS 較多。

[0254] 因此，有時非晶氧化物半導體與 nc-OS 相比，載子密度更高。因此，將非晶氧化物半導體用於通道形成區的電晶體有時成為常開啓電特性。因此，有時可以適當地將其用於需要常開啓電特性的電晶體。因為非晶氧化物半導體的 DOS 多，所以有時 DOS 也變多。因此，有時與將 CAAC-OS 或 nc-OS 用於通道形成區的電晶體相比，將非晶氧化物半導體用於通道形成區的電晶體的電特性變動較大，且可靠性較低。注意，因為即使利用包含多量的雜質的成膜方法也可以形成非晶氧化物半導體，所以非晶氧化物半導體可以較容易形成，有時可以根據用途適當地使用。例如，可以利用旋塗法、溶膠-凝膠法、浸漬法、噴射法、絲網印刷法、接觸印刷法、噴墨法、輥塗法、霧化 CVD 法 (mist CVD method) 等成膜方法來形成非晶氧化物半導體。因此，具有將非晶氧化物半導體用於通道形成區的電晶體的半導體裝置的生產性較高。

[0255] 另外，氧化物半導體也可以是包括 CAAC-OS、多晶氧化物半導體、微晶氧化物半導體和非晶氧化

物半導體中的兩種以上的混合膜。混合膜例如有時包括非晶氧化物半導體的區域、微晶氧化物半導體的區域、多晶氧化物半導體的區域和 CAAC-OS 的區域中的兩種以上的區域。此外，混合膜例如有時具有非晶氧化物半導體的區域、微晶氧化物半導體的區域、多晶氧化物半導體的區域和 CAAC-OS 的區域中的兩種以上的區域的疊層結構。

[0256] 氧化物半導體例如可以包括單晶。注意，將包括單晶的氧化物半導體稱為單晶氧化物半導體。

[0257] 例如，因為單晶氧化物半導體的雜質濃度低且 DOS 少（氧缺陷少），所以可以降低載子密度。因此，將單晶氧化物半導體用於通道形成區的電晶體很少成為常開啓電特性。此外，因為單晶氧化物半導體的 DOS 少，所以電荷陷阱有時也變少。因此，有時將該單晶氧化物半導體用於通道形成區的電晶體的電特性變動小，而成為可靠性高的電晶體。

[0258] 例如氧化物半導體缺陷越少其密度越高。此外，例如氧化物半導體結晶性越高其密度越高。此外，氧化物半導體例如氫等雜質的濃度越低其密度越高。此外，單晶氧化物半導體的密度有時比 CAAC-OS 的密度高。此外，例如 CAAC-OS 的密度有時比微晶氧化物半導體的密度高。此外，例如多晶氧化物半導體的密度有時比微晶氧化物半導體的密度高。此外，例如微晶氧化物半導體的密度有時比非晶氧化物半導體的密度高。

[0259] 下面，對氧化物半導體層 106b 中的 DOS 進

行說明。藉由降低氧化物半導體層 106b 中的 DOS，可以使使用氧化物半導體層 106b 的電晶體具有穩定的電特性。可以利用恆定光電流法 (CPM : Constant Photocurrent Method) 對氧化物半導體層 106b 中的 DOS 進行評價。

[0260] 為了使電晶體具有穩定的電特性，使利用 CPM 測定出的氧化物半導體層 106b 中的起因於 DOS 的吸收係數小於  $1 \times 10^{-3} \text{ cm}^{-1}$ ，較佳小於  $3 \times 10^{-4} \text{ cm}^{-1}$ ，即可。藉由使利用 CPM 測定出的氧化物半導體層 106b 中的起因於 DOS 的吸收係數小於  $1 \times 10^{-3} \text{ cm}^{-1}$ ，較佳小於  $3 \times 10^{-4} \text{ cm}^{-1}$ ，可以提高電晶體的場效移動率。另外，為了使利用 CP 測定出的氧化物半導體層 106b 中的起因於 DOS 的吸收係數小於  $1 \times 10^{-3} \text{ cm}^{-1}$ ，較佳小於  $3 \times 10^{-4} \text{ cm}^{-1}$ ，使在氧化物中形成 DOS 的元素的氫、鋰、碳、氮、氟、鈉、矽、氯、鉀、鈣、鈦、鐵、鎳、銅、鎗、銠、鎔以及鎗等的濃度小於  $2 \times 10^{19} \text{ atoms/cm}^3$ ，較佳小於  $2 \times 10^{18} \text{ atoms/cm}^3$ ，更佳小於  $2 \times 10^{17} \text{ atoms/cm}^3$ ，即可。

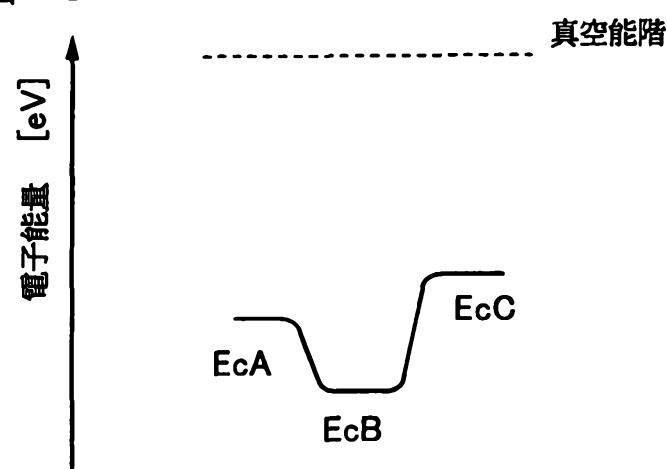

[0261] 在此，利用 CPM 對在基板上設置有氧化物半導體層 106a、氧化物半導體層 106b 及氧化物半導體層 106c 的疊層的樣本的 DOS 進行評價。

[0262] 氧化物半導體層 106a 使用 In-Ga-Zn 氧化物 (In:Ga:Zn=1:3:2[原子數比]) 的靶材利用濺射法形成。另外，作為成膜氣體使用 30sccm 的氰氣體和 15sccm 的氧氣體，將壓力設定為 0.4Pa，將基板溫度設定為 200°C，施加

0.5kW 的 DC 功率。

[0263] 氧化物半導體層 106b 使用 In-Ga-Zn 氧化物 (In:Ga:Zn=1:1:1[原子數比]) 的靶材利用濺射法形成。另外，作為成膜氣體使用 30sccm 的氬氣體和 15sccm 的氧氣體，將壓力設定為 0.4Pa，將基板溫度設定為 200°C，施加 0.5kW 的 DC 功率。

[0264] 氧化物半導體層 106c 是使用 In-Ga-Zn 氧化物 (In:Ga:Zn=1:3:2[原子數比]) 的靶材利用濺射法形成。另外，作為成膜氣體使用 30sccm 的氬氣體和 15sccm 的氧氣體，將壓力設定為 0.4Pa，將基板溫度設定為 200°C，施加 0.5kW 的 DC 功率。

[0265] 在此，為了提高 CPM 測定的精度，將氧化物半導體層 106a 的厚度設定為 30nm，將氧化物半導體層 106b 的厚度設定為 100nm，將氧化物半導體層 106c 的厚度設定為 30nm。

[0266] 在 CPM 測定中，在電壓施加到與氧化物半導體層 106b 接觸地設置的第一電極與第二電極之間的狀態下以使光電流值固定的方式調整照射到樣本表面的光量且根據照射光量得到吸收係數。在此，獲得各波長的吸收係數。在 CPM 測定中，樣本具有 DOS 時對應於 DOS 的能量（根據波長換算）的吸收係數增加。藉由用常數乘以該吸收係數的增加值，可以得到樣本的 DOS。

[0267] 圖 30 示出在氧化物半導體層 106b 的能隙以上的能量範圍中，將利用分光光度計測定出的吸收係數

(虛線) 與利用 CPM 測定出的吸收係數(實線)擬合的結果。另外，根據利用 CPM 測定出的吸收係數得到的耳巴赫能量為  $78.7\text{ meV}$ 。在圖 30 中，藉由從利用 CPM 測定出的吸收係數減背景值(短劃線)而算出吸收係數的積分值，由此可知本樣本的起因於 DOS 的吸收係數為  $2.02 \times 10^{-4}\text{ cm}^{-1}$ 。

[0268] 作為如圖 15A 至圖 15C 所示的基底絕緣膜 102，例如可以使用包含氧化鋁、氧化鎂、氧化矽、氮氧化矽、氮氧化矽、氮化矽、氧化鎵、氧化鋨、氧化鈷、氧化鋯、氧化鑭、氧化鋟、氧化鈦和氧化鉭中的一種以上的絕緣膜的單層或疊層。

[0269] 作為基底絕緣膜 102，例如可以採用第一層為氮化矽層，第二層為氧化矽層的多層膜。在此情況下，氧化矽層也可以為氮氧化矽層。另外，氮化矽層也可以為氮氧化矽層。氧化矽層較佳為使用缺陷密度低的氧化矽層。明確而言，使用如下氧化矽層：在利用電子自旋共振(ESR:Electron Spin Resonance)測定出的來源於  $g$  值為 2.001 的信號的自旋的密度為  $3 \times 10^{17}\text{ spins/cm}^3$  以下，較佳為  $5 \times 10^{16}\text{ spins/cm}^3$  以下。氮化矽層使用氫氣體及氮氣體的釋放量少的氮化矽層。氫氣體及氮氣體的釋放量藉由熱脫附譜(TDS: Thermal Desorption Spectroscopy)分析測定即可。另外，氮化矽層使用不使氫、水以及氧透過或幾乎不使其透過的氮化矽層。

[0270] 或者，作為基底絕緣膜 102，例如可以採用第

一層爲氮化矽層，第二層爲第一氧化矽層以及第三層爲第二氧化矽層的多層膜。在此情況下，第一氧化矽層和／或第二氧化矽層也可以爲氫氮化矽層。另外，氮化矽層也可以爲氮氧化矽層。第一氧化矽層較佳爲使用缺陷密度低的氧化矽層。明確而言，使用如下氧化矽層：在利用 ESR 測定出的來源於  $g$  值爲 2.001 的信號的自旋的密度爲  $3 \times 10^{17} \text{ spins/cm}^3$  以下，較佳爲  $5 \times 10^{16} \text{ spins/cm}^3$  以下。第二氧化矽層使用包含過剩氧的氧化矽層。氮化矽層使用氫氣體及氮氣體的釋放量少的氮化矽層。另外，氮化矽層使用不使氫、水以及氧透過或幾乎不使其透過的氮化矽層。

[0271] 包含過剩氧的氧化矽層是指在經過加熱處理等時可以釋放氧的氧化矽層。另外，包含過剩氧的絕緣膜是具有在經過加熱處理時釋放氧的功能的絕緣膜。

[0272] 包含過剩氧的絕緣膜能夠降低氧化物半導體層 106b 中的氧缺陷。在氧化物半導體層 106b 中氧缺陷形成 DOS 而成爲電洞陷阱等。當氫進入氧缺陷的位點時，有時生成作爲載子的電子。因此，藉由降低氧化物半導體層 106b 中的氧缺陷，可以使電晶體具有穩定的電特性。

[0273] 在此，在經過加熱處理時釋放氧的膜有時在 TDS 分析中在膜的表面溫度爲 100°C 以上且 700°C 以下或者 100°C 以上且 500°C 以下的範圍內釋放  $1 \times 10^{18} \text{ atoms/cm}^3$  以上、 $1 \times 10^{19} \text{ atoms/cm}^3$  以上或  $1 \times 10^{20} \text{ atoms/cm}^3$  以上的氧（換算爲氧原子）。

[0274] 在此，以下說明利用 TDS 分析測量氧的釋放

量的方法。

[0275] 對測量樣本進行 TDS 分析時的氣體的總釋放量與釋放氣體的離子強度的積分值成比例。並且，藉由對該測量樣本與標準樣本進行比較，可以計算出氣體的總釋放量。

[0276] 例如，根據作為標準樣本的含有指定密度的氫的矽晶片的 TDS 分析結果以及測量樣本的 TDS 分析結果，可以藉由算式 22 求出測量樣本中的氧分子的釋放量 ( $N_{O_2}$ )。這裡，假定藉由 TDS 分析而得到的被檢出為質量數 32 的氣體都來源於氧分子。雖然  $CH_3OH$  的質量數為 32，但是  $CH_3OH$  存在的可能性較低，所以這裡不加考慮。此外，包含作為氧原子的同位素的質量數 17 的氧原子及質量數 18 的氧原子的氧分子也在自然界的存在比率極低，所以不加考慮。

[0277]

[算式 22]

$$N_{O_2} = \frac{N_{H_2}}{S_{H_2}} \times S_{O_2} \times \alpha$$

[0278]  $N_{H_2}$  是以密度換算從標準樣本脫離的氫分子的值。 $S_{H_2}$  是對標準樣本進行 TDS 分析而得到的離子強度的積分值。在此，將標準樣本的基準值設定為  $N_{H_2}/S_{H_2}$ 。 $S_{O_2}$  是對測量樣本進行 TDS 分析而得到的離子強度的積分值。 $\alpha$ 是在 TDS 分析中影響到離子強度的係數。關於算式 22 的詳細說明，可以參照日本專利申請公開平第 6-

275697 公報。注意，上述氧的釋放量是使用由電子科學公司製造的熱脫附裝置 EMD-WA1000S/W，並以包含  $1 \times 10^{16} \text{ atoms/cm}^2$  的氫原子的矽晶片為標準樣本而測量的。

[0279] 此外，在 TDS 分析中，氧的一部分作為氧原子被檢測出。氧分子與氧原子的比率可以從氧分子的電離率算出。另外，因為上述的  $\alpha$  包括氧分子的電離率，所以藉由評估氧分子的釋放量，可以估算出氧原子的釋放量。

[0280] 注意， $N_{O_2}$  是氧分子的釋放量。換算為氧原子時的釋放量是氧分子的釋放量的 2 倍。

[0281] 或者，在經過加熱處理時釋放氧的膜有時包含過氧化自由基。明確而言，是指起因於過氧化自由基的自旋密度為  $5 \times 10^{17} \text{ spins/cm}^3$  以上。另外，包含過氧化自由基的膜有時在 ESR 中具有  $g$  值為 2.01 附近的非對稱性的信號。

[0282] 另外，包含過剩氧的絕緣膜也可以是氧過剩的氧化矽 ( $SiO_x (X>2)$ )。在氧過剩的氧化矽 ( $SiO_x (X>2)$ ) 中，每單位體積中含有的氧原子數多於矽原子數的 2 倍。每單位體積的矽原子數及氧原子數為藉由拉塞福背散射光譜學法 (RBS:Rutherford Backscattering Spectrometry) 測定的值。

[0283] 源極電極 116a 及汲極電極 116b 例如可以使用包含鋁、鈦、鉻、鈷、鎳、銅、釔、鋯、鉬、釤、銀、鉭和鎢中的一種以上的導電膜的單層或疊層。較佳的是，

作為源極電極 116a 及汲極電極 116b 使用具有包含銅的層的多層膜。在使用與源極電極 116a 及汲極電極 116b 相同的層形成佈線的情況下，藉由作為源極電極 116a 及汲極電極 116b 使用具有包含銅的層的多層膜，可以降低佈線電阻。另外，源極電極 116a 和汲極電極 116b 的組成可以相同，也可以不同。

[0284] 注意，當作為源極電極 116a 及汲極電極 116b 使用具有包含銅的層的多層膜時，有時銅混入氧化物半導體層 106b 而使其載子密度增加。或者，有時銅在氧化物半導體層 106b 中形成 DOS，該 DOS 具有電荷陷阱的功能。在此，如果氧化物半導體層 106c 對銅具有阻擋功能，可以抑制銅混入氧化物半導體層 106b 而導致電晶體的關態電流的增加和臨界電壓的變化。

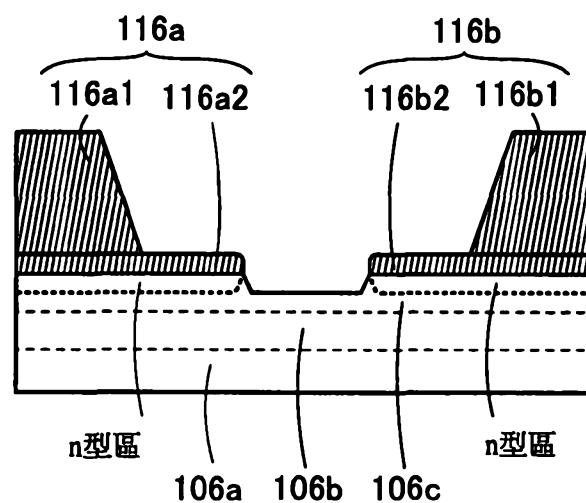

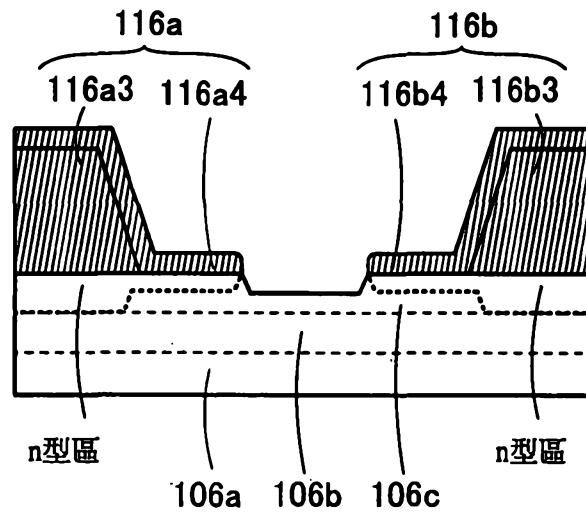

[0285] 圖 17A 至圖 17C 示出電晶體的源極電極 116a 及汲極電極 116b 附近的剖面圖。源極電極 116a 及汲極電極 116b 可以採用圖 17A 至圖 17C 中示出的任一結構。注意，圖 17A 至圖 17C 示出在形成源極電極 116a 及汲極電極 116b 時氧化物半導體層 106c 的頂面的一部分被削掉的情況。

[0286] 圖 17A 示出源極電極 116a 及汲極電極 116b 具有步階形狀的結構。氧化物半導體層 106c 中的以虛線表示的區域中，形成有 n 型區。n 型區由於在氧化物半導體層 106c 中產生氧缺陷而形成，該氧缺陷起因於在氧化物半導體層 106c 上形成源極電極 116a 及汲極電極 116b

時的損傷或用作源極電極 116a 及汲極電極 116b 的導電膜的作用。例如，當氫進入氧缺陷的位點時，有時生成作為載子的電子。注意，雖然 n 型區形成於氧化物半導體層 106c 與氧化物半導體層 106b 之間的邊界附近，但是不侷限於此。例如，n 型區既可以形成於氧化物半導體層 106c 和氧化物半導體層 106b 中，又可以僅形成於氧化物半導體層 106c 中。

[0287] 圖 17B 示出如下結構：源極電極 116a 包括不容易被氧化的導電層 116a2 以及設置於導電層 116a2 上的導電層 116a1；汲極電極 116b 包括不容易被氧化的導電層 116b2 以及設置於導電層 116b2 上的導電層 116b1。另外，不容易被氧化的導電層是使氧化物半導體層 106c 還原的作用小的導電層。藉由使源極電極 116a 及汲極電極 116b 具有圖 17B 所示的結構，n 型區僅形成於氧化物半導體層 106c 中。另外，氧缺陷很少在通道長度方向上擴散，因此通道形成區不容易被 n 型化。另外，由於設置有導電層 116a1 及導電層 116b1，所以導電層 116a2 及導電層 116b2 的導電性較低也無妨。因此，導電層 116a2 及導電層 116b2 的厚度可以較小，而有利於微型加工。即，圖 17B 所示的結構適用於通道長度較小的微型電晶體。

[0288] 另外，導電層 116a1 和導電層 116a2 可以是相同的導電層。另外，導電層 116b1 和導電層 116b2 可以是相同的導電層。

[0289] 圖 17C 示出如下結構：源極電極 116a 包括導

電層 116a3 以及設置於導電層 116a3 上的不容易被氧化的導電層 116a4；汲極電極 116b 包括導電層 116b3 以及設置於導電層 116b3 上的不容易被氧化的導電層 116b4。藉由使源極電極 116a 及汲極電極 116b 具有圖 17C 所示的結構，形成於氧化物半導體層 106c 的 n 型區的一部分形成至氧化物半導體層 106c 與氧化物半導體層 106b 之間的邊界附近，其他的一部分僅形成於氧化物半導體層 106c 中。因此，氧缺陷很少在通道長度方向上擴散，所以通道形成區不容易被 n 型化。另外，在導電層 116a3 以及導電層 116b3 的下方，n 型區形成至氧化物半導體層 106b，因此源極電極 116a 與汲極電極 116b 之間的電阻降低，可以提高電晶體的場效移動率。另外，由於設置有導電層 116a3 及導電層 116b3，所以導電層 116a4 及導電層 116b4 的導電性較低也無妨。因此，導電層 116a4 及導電層 116b4 的厚度可以較小，而有利於微型加工。即，圖 17C 所示的結構適用於通道長度較小的微型電晶體。

[0290] 另外，導電層 116a3 和導電層 116a4 可以是相同的導電層。另外，導電層 116b3 和導電層 116b4 可以是相同的導電層。

[0291] 作為圖 15A 至圖 15C 所示的閘極絕緣膜 112，例如可以使用包含氧化鋁、氧化鎂、氧化矽、氮氧化矽、氮氧化矽、氮化矽、氧化鎵、氧化鋒、氧化鈷、氧化鋁、氧化鑭、氧化釤、氧化鉻和氧化鉬中的一種以上的絕緣膜的單層或疊層。

[0292] 作為閘極絕緣膜 112，例如可以採用第一層為氮化矽層，第二層為氧化矽層的多層膜。在此情況下，氧化矽層也可以為氧氮化矽層。另外，氮化矽層也可以為氮氧化矽層。氧化矽層較佳為使用缺陷密度低的氧化矽層。明確而言，使用如下氧化矽層：在 ESR 測定出的來源於 g 值為 2.001 的信號的自旋的密度為  $3 \times 10^{17} \text{ spins/cm}^3$  以下，較佳為  $5 \times 10^{16} \text{ spins/cm}^3$  以下。氧化矽層較佳為包含過剩氧。氮化矽層使用氫氣體及氮氣體的釋放量少的氮化矽層。氫氣體及氮氣體的釋放量藉由 TDS 分析測定即可。

[0293] 當閘極絕緣膜 112 和基底絕緣膜 102 中的至少一個包括包含過剩氧的絕緣膜時，可以降低氧化物半導體層 106b 中的氧缺陷而使電晶體具有穩定的電特性。

[0294] 閘極電極 104 例如可以使用包含鋁、鈦、鉻、鈷、鎳、銅、釔、鋯、鉬、釤、銀、鉭和鎢中的一種以上的導電膜的單層或疊層。

[0295] 作為保護絕緣膜 108，例如可以使用包含氧化鋁、氧化鎂、氧化矽、氧氮化矽、氮氧化矽、氮化矽、氧化鎗、氧化鎗、氧化釔、氧化鋯、氧化釤、氧化釤、氧化釤、氧化鎔和氧化鉬中的一種以上的絕緣膜的單層或疊層。

[0296] 保護絕緣膜 108 例如包括氮化矽層。在此情況下，氮化矽層也可以為氮氧化矽層。氮化矽層的氫氣體和氮氣體的釋放量較佳少。氫氣體及氮氣體的釋放量藉由 TDS 分析測定即可。另外，氮化矽層較佳為不使氫、水以及氧透過或幾乎不使其透過。

[0297] 保護絕緣膜 108 例如包括氧化鋁層。氧化鋁層的氫氣體的釋放量較佳少。氫氣體的釋放量藉由 TDS 分析測定即可。另外，氧化鋁層較佳為不使氫、水以及氧透過或幾乎不使其透過。

[0298] 保護絕緣膜 118，例如可以使用包含氧化矽、氧化氮化矽、氧化鋒、氧化鈦、氧化鋯、氧化鑭、氧化鈦、氧化鋁和氧化鉭中的一種以上的絕緣膜的單層或疊層。當設置保護絕緣膜 118 時，有時可以不設置保護絕緣膜 108。

[0299] 對基板 100 沒有很大的限制。例如，作為基板 100，可以使用玻璃基板、陶瓷基板、石英基板、藍寶石基板等。此外，作為基板 100，也可以採用以矽或碳化矽等為材料的單晶半導體基板或多晶半導體基板、以矽鋒等為材料的化合物半導體基板、SOI (Silicon On Insulator：絕緣體上矽晶片) 基板等，並且也可以使用在這些基板上設置有半導體元件的基板。

[0300] 另外，在作為基板 100，在使用第五代 (1000mm×1200mm 或 1300mm×1500mm)、第六代 (1500mm×1800mm)、第七代 (1870mm×2200mm)、第八代 (2200mm×2500mm)、第九代 (2400mm×2800mm)、第十代 (2880mm×3130mm) 等大型玻璃基板的情況下，由於半導體裝置的製程中的加熱處理等導致基板 100 的收縮，有時難以進行微細加工。因此，在作為基板 100 使用上述大型玻璃基板的情況下，較佳為使用起因

於加熱處理的收縮少的基板。例如，作為基板 100 可以使用在 400°C，較佳為 450°C，更佳為 500°C 的溫度下進行 1 小時的加熱處理之後的收縮量為 10ppm 以下，較佳為 5ppm 以下，更佳為 3ppm 以下的大型玻璃基板。

[0301] 此外，基板 100 也可以使用撓性基板。另外，作為在撓性基板上設置電晶體的方法，可以舉出如下方法：在不具有撓性的基板上形成電晶體之後，將該電晶體剝離並轉置到具有撓性的基板 100 上。在此情況下，較佳為在不具有撓性的基板和電晶體之間設置剝離層。

[0302]

〈電晶體結構（1）的製造方法〉

下面，對電晶體結構（1）的製造方法的一個例子進行說明。

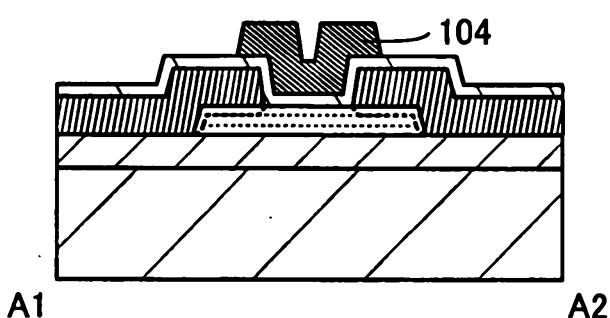

[0303] 圖 18A 至圖 19D 為對應於圖 15B 的剖面圖。

[0304] 首先，準備基板 100。

[0305] 接著，形成基底絕緣膜 102。基底絕緣膜 102 可以藉由濺射法、化學氣相沉積（CVD：Chemical Vapor Deposition）法、分子束磊晶（MBE：Molecular Beam Epitaxy）法、原子層沉積（ALD：Atomic Layer Deposition）法或脈衝雷射沉積（PLD：Pulsed Laser Deposition）法形成。

[0306] 在作為基板 100 使用矽晶片的情況下，基底絕緣膜 102 可以利用熱氧化法形成。

[0307] 接著，為了使基底絕緣膜 102 的表面平坦，

可以進行化學機械拋光 (CMP:Chemical Mechanical Polishing) 處理。藉由進行 CMP 處理，使基底絕緣膜 102 的平均表面粗糙度 ( $R_a$ ) 設定為  $1\text{nm}$  以下，較佳為  $0.3\text{nm}$  以下，更佳為  $0.1\text{nm}$  以下。當  $R_a$  的值為上述數值以下時，氧化物半導體層 106b 的結晶性有時得到提高。另外， $R_a$  是將 JIS B 0601:2001 (ISO4287:1997) 中定義的算術平均粗糙度擴大為三維以使其能夠應用於曲面，可以以“將從基準面到指定面的偏差的絕對值平均而得的值”表示，以算式 23 定義。

[0308]

[算式 23]

$$R_a = \frac{1}{S_0} \int_{y_1}^{y_2} \int_{x_1}^{x_2} |f(x, y) - Z_0| dx dy$$

[0309] 這裡，指定面是指成為測量粗糙度對象的面，並且是以座標 ( $x_1, y_1, f(x_1, y_1)$ ) ( $x_1, y_2, f(x_1, y_2)$ ) ( $x_2, y_1, f(x_2, y_1)$ ) ( $x_2, y_2, f(x_2, y_2)$ ) 的四點表示的四角形的區域，指定面投影在 xy 平面的長方形的面積為  $S_0$ ，基準面的高度 (指定面的平均高度) 為  $Z_0$ 。可以利用原子力顯微鏡 (AFM: Atomic Force Microscope) 測量  $R_a$ 。

[0310] 接著，也可以對基底絕緣膜 102 添加氧離子，來形成包含過剩氧的絕緣膜。當添加氧離子時，例如，利用離子植入法，將加速電壓設定為  $2\text{kV}$  以上且  $100\text{kV}$  以下，將劑量設定為  $5 \times 10^{14}\text{ions/cm}^2$  以上且  $5 \times 10^{16}\text{ions/cm}^2$  以下，即可。

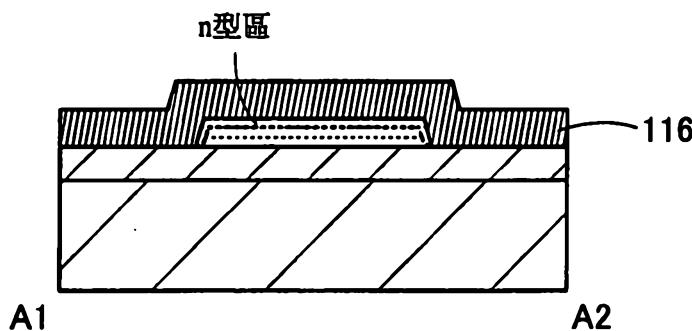

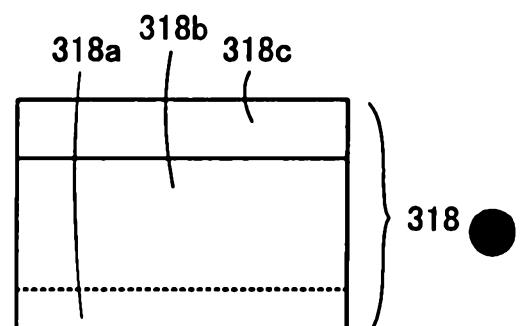

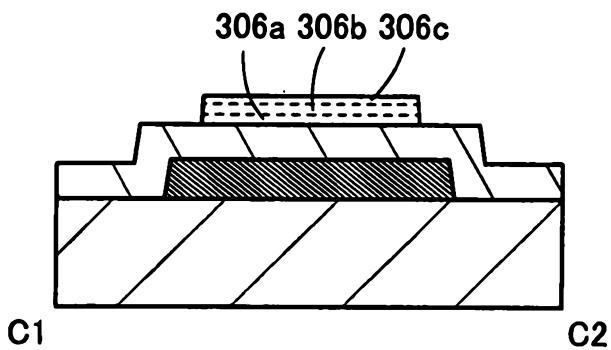

[0311] 接著，依次形成氧化物半導體層 136a、氧化物半導體層 136b 以及氧化物半導體層 136c（參照圖 18A）。氧化物半導體層 136a、氧化物半導體層 136b 以及氧化物半導體層 136c 可以分別使用選自用於氧化物半導體層 106a、氧化物半導體層 106b 以及氧化物半導體層 106c 的氧化物形成。氧化物半導體層 136b 及氧化物半導體層 136c 可以利用濺射法、CVD 法、MBE 法、ALD 法或者 PLD 法形成。

[0312] 在形成氧化物半導體層 136c 之後，較佳為進行第一加熱處理。第一加熱處理以 250°C 以上且 650°C 以下的溫度，較佳為以 300°C 以上且 500°C 以下的溫度進行即可。第一加熱處理在惰性氣體氛圍或者包含 10ppm 以上、1% 以上或 10% 以上的氧化氣體的氛圍下進行。第一加熱處理也可以在減壓狀態下進行。或者，作為第一加熱處理，也可以進行惰性氣體氛圍下的加熱處理之後，為了填補脫離了的氧而進行包含 10ppm 以上、1% 以上或 10% 以上的氧化氣體的氛圍下的加熱處理。藉由進行第一加熱處理，可以提高氧化物半導體層 136b 的結晶性，還可以從氧化物半導體層 136b 去除氫和水等雜質。另外，藉由進行第一加熱處理，可以降低氧化物半導體層 106b 中的 DOS 並使氧化物半導體層 106b 高純度本質化。另外，降低 DOS 的模型參照高純度本質化的記載。

[0313] 接著，對氧化物半導體層 136a、氧化物半導體層 136b 以及氧化物半導體層 136c 的一部分進行蝕刻，

來形成島狀的氧化物半導體層 106a、氧化物半導體層 106b 以及氧化物半導體層 106c（參照圖 18B）。

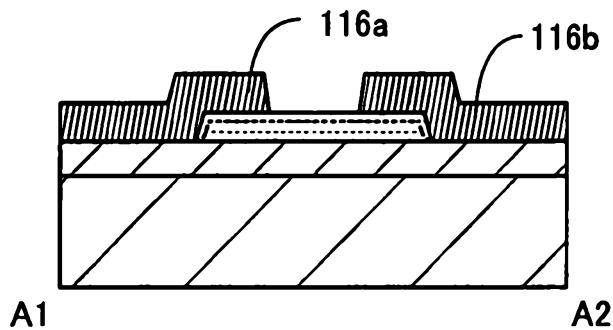

[0314] 接著，形成導電膜 116。導電膜 116 使用選自用作源極電極 116a 及汲極電極 116b 的導電膜形成。導電膜 116 可以利用濺射法、CVD 法、MBE 法、ALD 法或者 PLD 法形成。此時，有時氧化物半導體層 106a、氧化物半導體層 106b 以及氧化物半導體層 106c 中的以虛線所示的區域中形成 n 型區（參照圖 18C）。n 型區由於在氧化物半導體層 106c 中產生氧缺陷而形成，該氧缺陷起因於在氧化物半導體層 106c 上形成導電膜 116 時的損傷或導電膜 116 的作用。例如，當氫進入氧缺陷的位點時，有時生成作為載子的電子。注意，雖然 n 型區形成至氧化物半導體層 106c 與氧化物半導體層 106b 之間的邊界附近，但是不侷限於此。例如，n 型區既可以形成於氧化物半導體層 106c 和氧化物半導體層 106b 中，又可以僅形成於氧化物半導體層 106c 中。

[0315] 接著，對導電膜 116 的一部分進行蝕刻，來形成源極電極 116a 及汲極電極 116b（參照圖 18D）。

[0316] 接著，較佳為進行第二加熱處理。第二加熱處理可以以選自第一加熱處理的條件進行。藉由進行第二加熱處理，有時可以使氧化物半導體層 106c 的露出的 n 型區成為 i 型區（參照圖 19A）。因此，可以僅在氧化物半導體層 106c 中的位於源極電極 116a 及汲極電極 116b 之下的區域形成 n 型區。藉由設置 n 型區，可以降低氧化

物半導體層 106c 與源極電極 116a 和汲極電極 116b 之間的接觸電阻，因此可以提高電晶體的通態電流。另外，當進行第二加熱處理時，有時可以不進行第一加熱處理。

[0317] 接著，形成閘極絕緣膜 112（參照圖 19B）。閘極絕緣膜 112 可以利用濺射法、CVD 法、MBE 法、ALD 法或者 PLD 法形成。

[0318] 接著，形成成為閘極電極 104 的導電膜。成為閘極電極 104 的導電膜可以使用選自用作閘極電極 104 的導電膜形成。成為閘極電極 104 的導電膜可以利用濺射法、CVD 法、MBE 法、ALD 法或者 PLD 法形成。

[0319] 接著，對成為閘極電極 104 的導電膜的一部分進行蝕刻，來形成閘極電極 104（參照圖 19C）。

[0320] 接著，形成保護絕緣膜 108。保護絕緣膜 108 可以利用濺射法、CVD 法、MBE 法、ALD 法或者 PLD 法形成。

[0321] 接著，形成保護絕緣膜 118（參照圖 19D）。保護絕緣膜 118 可以利用濺射法、CVD 法、MBE 法、ALD 法或者 PLD 法形成。

[0322] 接著，較佳為進行第三加熱處理。第三加熱處理以選自第一加熱處理的條件進行或者以比第一加熱處理和第二加熱處理低的溫度進行，即可。

[0323] 藉由以上步驟，可以製造圖 15A 至圖 15C 所示的電晶體。

[0324]

〈關於製造裝置〉

當氧化物半導體層 106b 中的雜質濃度低，缺陷密度低時（即，當氧化物半導體層 106b 為高純度本質時），電晶體的電特性穩定。另外，在氧化物半導體層 106b 具有高結晶性的情況下，與氧化物半導體層 106b 為非晶的情況相比，電晶體的電特性穩定。下面，說明用來形成低雜質濃度且高結晶性的氧化物半導體層 106b 的成膜裝置。注意，以下說明的成膜裝置在形成電晶體的其他構成要素時也可以使用。藉由使用以下說明的成膜裝置，也可以降低其他構成要素中的雜質濃度。

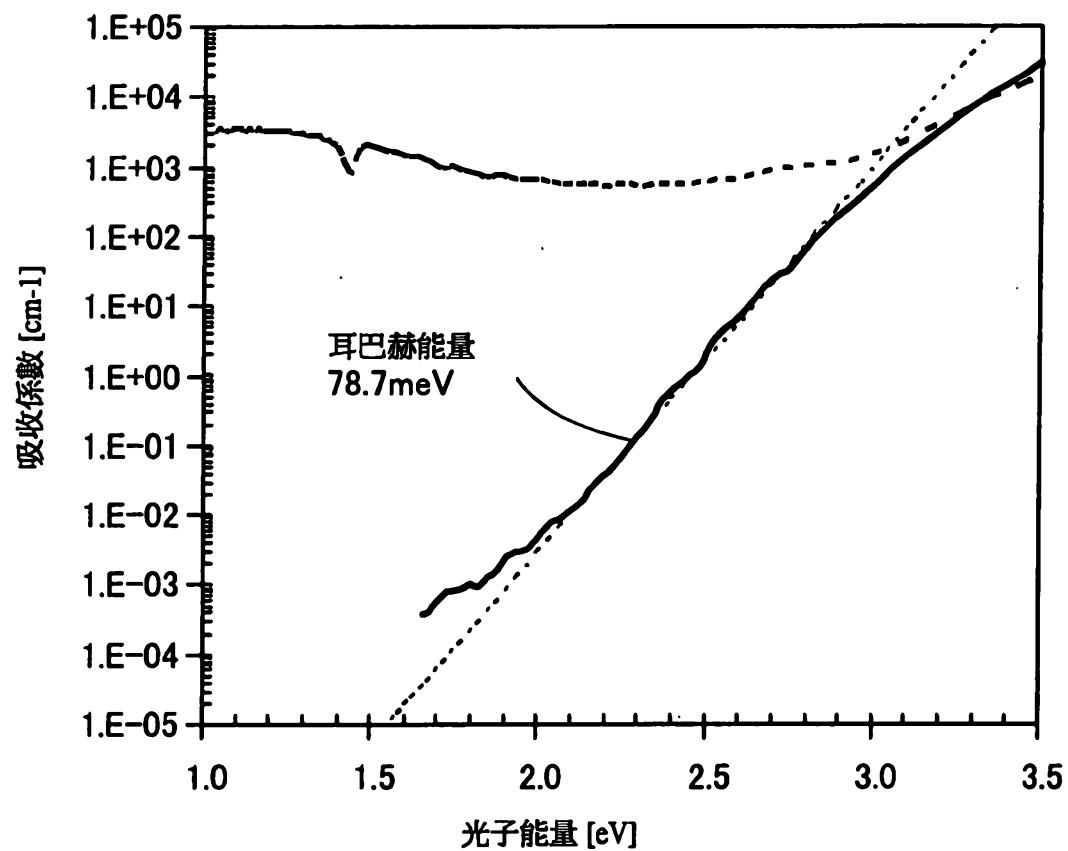

[0325] 首先，使用圖 31A 和圖 31B 對進行成膜時雜質進入少的成膜裝置的結構進行說明。

[0326] 圖 31A 示出多室成膜裝置的俯視圖。該成膜裝置包括：具有三個用於收納基板的盒式介面（cassette port）74 的大氣側基板供應室 71、裝載閉鎖室 72a、卸載閉鎖室 72b、傳送室 73、傳送室 73a、傳送室 73b、基板加熱室 75、成膜室 70a 以及成膜室 70b。大氣側基板供應室 71 與裝載閉鎖室 72a 以及卸載閉鎖室 72b 連接。裝載閉鎖室 72a 及卸載閉鎖室 72b 藉由傳送室 73a 及傳送室 73b 與傳送室 73 連接。基板加熱室 75、成膜室 70a 及成膜室 70b 只與傳送室 73 連接。另外，各室的連接部設置有閘閥（GV），由此可以使大氣側基板供應室 71 以外的各室獨立地保持為真空狀態。另外，大氣側基板供應室 71 及傳送室 73 具有一個以上的基板傳送機器人 76，使用

它可以傳送基板。這裡，較佳為基板加熱室 75 兼作電漿處理室。由於多室成膜裝置能夠在處理與處理之間以不暴露於大氣的方式傳送基板，由此可以抑制雜質附著到基板上。另外，可以自由地決定成膜、加熱處理等的順序。另外，傳送室、成膜室、裝載閉鎖室、卸載閉鎖室以及基板加熱室的數目不侷限於上述數目，可以根據設置空間或製程適當地決定。

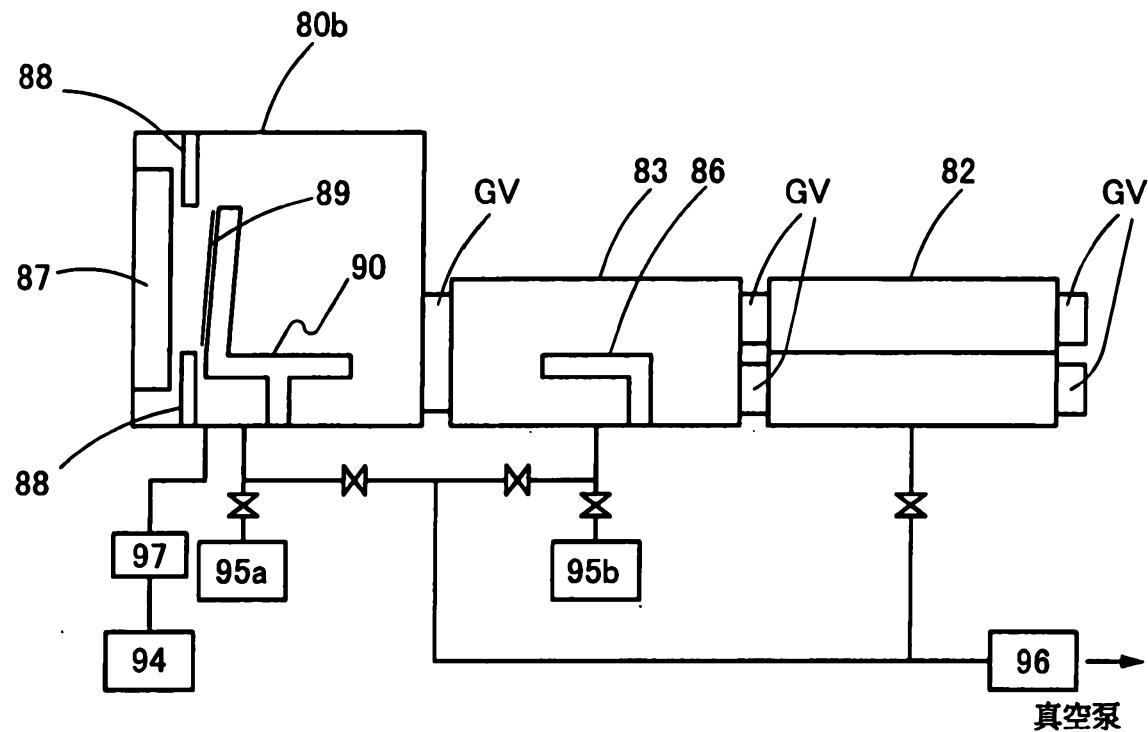

[0327] 圖 31B 示出與圖 31A 的結構不同的多室成膜裝置的俯視圖。該成膜裝置包括：具有盒式介面 84 的大氣側基板供應室 81、裝載/卸載閉鎖室 82、傳送室 83、基板加熱室 85、基板傳送機器人 86、成膜室 80a、成膜室 80b、成膜室 80c 以及成膜室 80d。大氣側基板供應室 81、基板加熱室 85、成膜室 80a、成膜室 80b、成膜室 80c 以及成膜室 80d 藉由傳送室 83 彼此連接。

[0328] 在此，使用圖 32A 對圖 31B 所示的成膜室（濺射室）的一個例子進行說明。例如，成膜室 80b 具有靶材 87、防著板 88 以及基板載物台 90。另外，這裡在基板載物台 90 上設置有玻璃基板 89。雖然未圖示，但是基板載物台 90 也可以具備保持玻璃基板 89 的基板保持結構或從背面對玻璃基板 89 進行加熱的背面加熱器等。另外，藉由使用防著板 88，可以抑制從靶材 87 被濺射的粒子沉積在不需要進行濺射的區域。

[0329] 另外，圖 32A 所示的成膜室 80b 藉由質量流量控制器 97 與精製器 94 連接。注意，雖然可以根據氣體

種類的數目設置精製器 94 及質量流量控制器 97，但是為了方便起見只示出一個。作為導入到成膜室 80b 等的氣體，使用露點為  $-80^{\circ}\text{C}$  以下，較佳為  $-100^{\circ}\text{C}$  以下，更佳為  $-120^{\circ}\text{C}$  以下的氣體。藉由使用露點低的氧氣體及稀有氣體（氬氣體等）等，可以降低成膜時混入的水分。

[0330] 另外，真空泵 96 例如可以使用乾燥泵與機械增壓泵串聯連接的泵。藉由採用該結構，當對成膜室 80b 及傳送室 83 進行排氣時，可以使用真空泵 96 進行大氣壓至低真空（ $0.1\text{ Pa}$  至  $10\text{ Pa}$  程度）的排氣，並在進行閥切換後使用低溫泵 95a 或低溫泵 95b 進行低真空至高真空（ $1 \times 10^{-7}\text{ Pa}$  至  $1 \times 10^{-4}\text{ Pa}$ ）的排氣。

[0331] 另外，使用圖 32B 對圖 31B 所示的成膜室的其他例子進行說明。

[0332] 圖 32B 所示的成膜室 80b 藉由閘閥與傳送室 83 連接，傳送室 83 藉由閘閥與裝載/卸載閉鎖室 82 連接。

[0333] 圖 32B 所示的成膜室 80b 藉由氣體加熱機構 98 與質量流量控制器 97 連接，氣體加熱機構 98 藉由質量流量控制器 97 與精製器 94 連接。藉由氣體加熱機構 98 可以將導入成膜室 80b 的氣體加熱為  $40^{\circ}\text{C}$  以上且  $400^{\circ}\text{C}$  以下、或者  $50^{\circ}\text{C}$  以上且  $200^{\circ}\text{C}$  以下。注意，雖然可以根據氣體種類的數目設置氣體加熱機構 98、精製器 94 及質量流量控制器 97，但是為了方便起見只示出一個。

[0334] 圖 32B 所示的成膜室 80b 藉由閥與渦輪分子

泵 95c 以及真空泵 96b 連接。另外，渦輪分子泵 95c 藉由閥與作為輔助泵的真空泵 96a 連接。真空泵 96a 以及真空泵 96b 可以與真空泵 96 採用同樣的結構。另外，圖 32B 所示的成膜室 80b 設置有低溫冷阱 99。

[0335] 已知渦輪分子泵 95c 能夠穩定地排出大分子（原子）且維修頻率低，因此在生產率上佔有優勢，但是排氫、排水的能力較低。因此，將低溫冷阱 99 連接於成膜室 80b，低溫冷阱 99 對水等的相對來說熔點較高的分子（原子）的排氣能力高。低溫冷阱 99 的製冷機的溫度為 100K 以下，較佳為 80K 以下。另外，當低溫冷阱 99 具有多個製冷機時，較佳為各個製冷機的溫度不同，這樣可以高效率地進行排氣。例如，可以將第一階段的製冷機的溫度設定為 100K 以下，將第二階段的製冷機的溫度設定為 20K 以下。

[0336] 另外，圖 32B 所示的傳送室 83 藉由閥與真空泵 96b、低溫泵 95d 以及低溫泵 95e 連接。當只有 1 台低溫泵時，在低溫泵進行再生時無法進行排氣，但是當並聯連接 2 台以上的低溫泵時，即使 1 台進行再生，也可以利用其它的低溫泵進行排氣。另外，低溫泵的再生是指將積存於低溫泵內的分子（原子）排出的處理。當低溫泵積存過多分子（原子）時其排氣能力下降，因此需要定期進行再生。

[0337] 圖 32B 所示的裝載/卸載閉鎖室 82 藉由閥連接與低溫泵 95f 以及真空泵 96c。另外，真空泵 96c 可以

與真空泵 96 採用同樣的結構。

[0338] 在成膜室 80b 中可以使用對向靶材式濺射裝置。另外，也可以在成膜室 80b 中使用平行平板型濺射裝置、離子束濺射裝置。

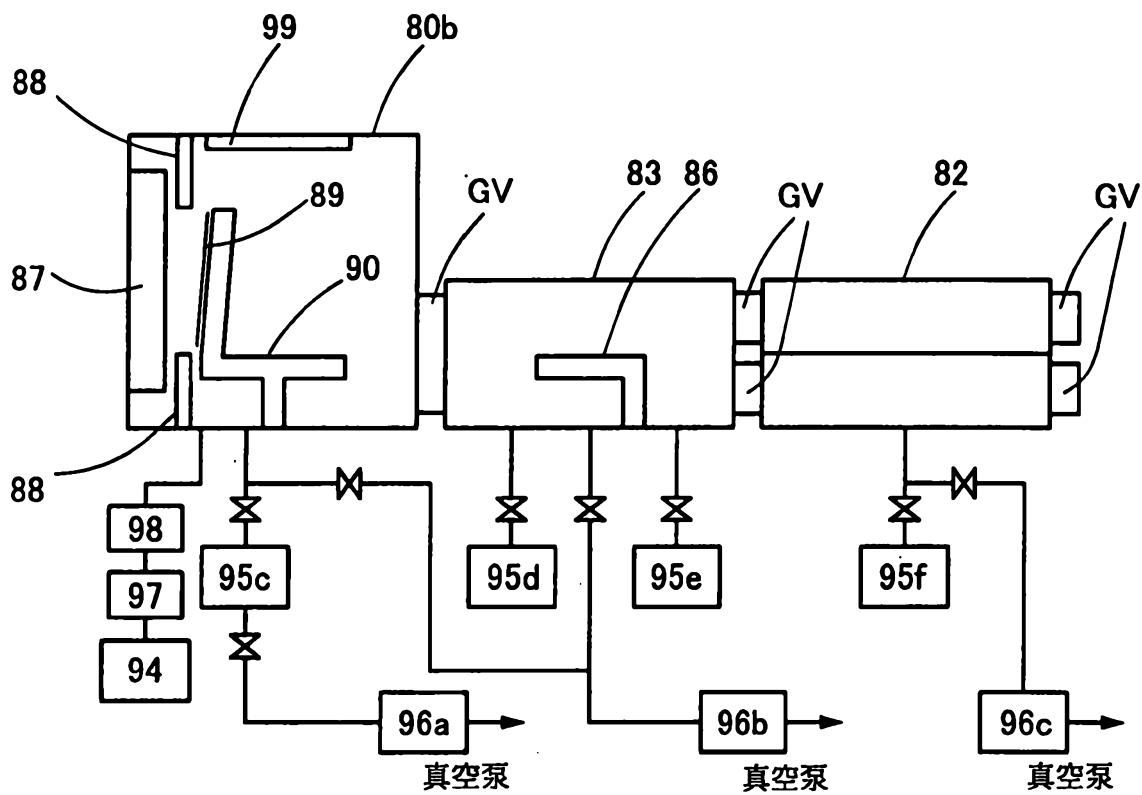

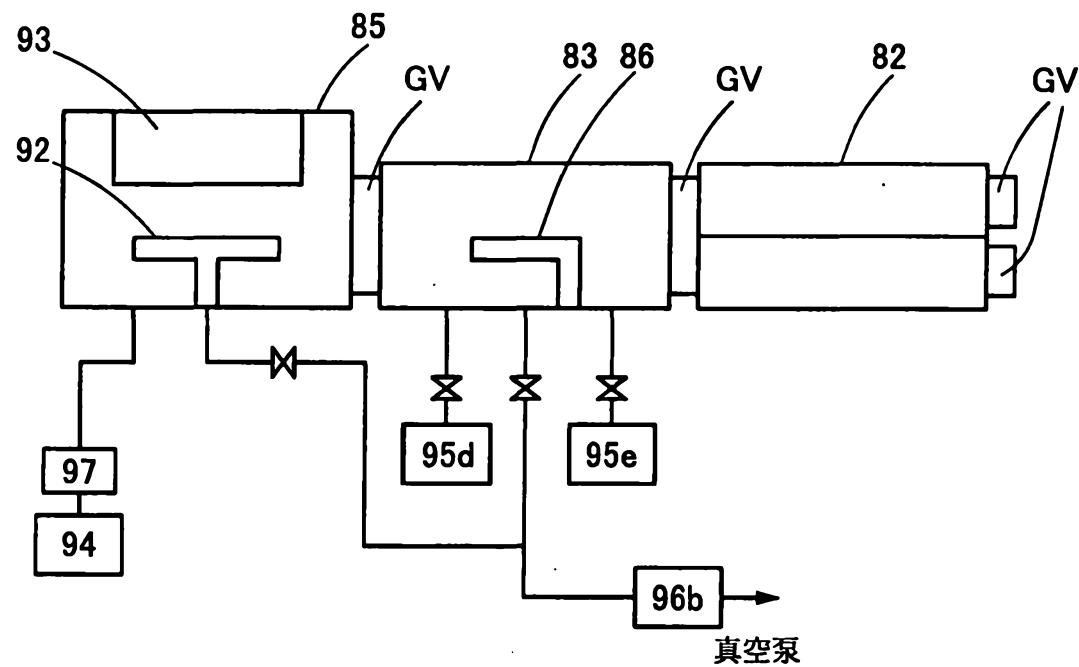

[0339] 接著，使用圖 33 對圖 31B 所示的基板加熱室的一個例子的排氣進行說明。

[0340] 圖 33 所示的基板加熱室 85 藉由閘閥與傳送室 83 連接。另外，傳送室 83 還藉由閘閥與裝載/卸載閂鎖室 82 連接。

[0341] 圖 33 所示的基板加熱室 85 藉由質量流量控制器 97 與精製器 94 連接。另外，雖然可以根據氣體種類的數目設置精製器 94 及質量流量控制器 97，但是為了方便起見僅示出一個。另外，基板加熱室 85 藉由閥與真空泵 96b 連接。

[0342] 另外，基板加熱室 85 具有基板載物台 92。在基板載物台 92 上至少可以設置一個基板，也可以設置多個基板。另外，基板加熱室 85 具有加熱機構 93。加熱機構 93 例如也可以為使用電阻發熱體等進行加熱的加熱機構。或者，還可以為使用利用被加熱的氣體等的介質的熱傳導或熱輻射來進行加熱的加熱機構。例如，可以使用 GRTA (Gas Rapid Thermal Anneal：氣體快速熱退火) 裝置、LRTA (Lamp Rapid Thermal Anneal：燈快速熱退火) 裝置等的 RTA (Rapid Thermal Anneal：快速熱退火) 裝置。LRTA 裝置是藉由鹵素燈、金屬鹵化物燈、氙

弧燈、碳弧燈、高壓鈉燈或者高壓汞燈等的燈發射的光（電磁波）的輻射來加熱被處理物的裝置。GRTA 裝置是利用高溫氣體進行加熱處理的裝置。氣體使用惰性氣體。藉由採用 RTA，可以以短時間進行加熱處理，因此可以抑制由加熱處理所引起的基板的彎曲。尤其是，在採用大型玻璃基板的情況下，即使很小的彎曲也會導致半導體裝置的良率的下降。因此，在以會發生基板的彎曲的高溫進行加熱處理的情況下，較佳為採用 RTA。

[0343] 另外，成膜室 80b 及基板加熱室 85 的背壓為  $1 \times 10^{-4}$ Pa 以下，較佳為  $3 \times 10^{-5}$ Pa 以下，更佳為  $1 \times 10^{-5}$ Pa 以下。另外，在成膜室 80b 及基板加熱室 85 中，質量電荷比 (m/z) 是 18 的氣體分子 (原子) 的分壓為  $3 \times 10^{-5}$ Pa 以下，較佳為  $1 \times 10^{-5}$ Pa 以下，更佳為  $3 \times 10^{-6}$ Pa 以下。另外，在成膜室 80b 及基板加熱室 85 中，m/z 是 28 的氣體分子 (原子) 的分壓為  $3 \times 10^{-5}$ Pa 以下，較佳為  $1 \times 10^{-5}$ Pa 以下，更佳為  $3 \times 10^{-6}$ Pa 以下。另外，在成膜室 80b 及基板加熱室 85 中，m/z 是 44 的氣體分子 (原子) 的分壓為  $3 \times 10^{-5}$ Pa 以下，較佳為  $1 \times 10^{-5}$ Pa 以下，更佳為  $3 \times 10^{-6}$ Pa 以下。

[0344] 另外，在成膜室 80b 及基板加熱室 85 中，洩漏率為  $3 \times 10^{-6}$ Pa·m<sup>3</sup>/s 以下，較佳為  $1 \times 10^{-6}$ Pa·m<sup>3</sup>/s 以下。另外，在成膜室 80b 及基板加熱室 85 中，m/z 是 18 的氣體分子 (原子) 的洩漏率為  $1 \times 10^{-7}$ Pa·m<sup>3</sup>/s 以下，較佳為  $3 \times 10^{-8}$ Pa·m<sup>3</sup>/s 以下。另外，在成膜室 80b 及基板加熱室

85 中， $m/z$  是 28 的氣體分子（原子）的洩漏率爲  $1 \times 10^{-5}$  Pa·m<sup>3</sup>/s 以下，較佳爲  $1 \times 10^{-6}$  Pa·m<sup>3</sup>/s 以下。另外，在成膜室 80b 及基板加熱室 85 中， $m/z$  是 44 的氣體分子（原子）的洩漏率爲  $3 \times 10^{-6}$  Pa·m<sup>3</sup>/s 以下，較佳爲  $1 \times 10^{-6}$  Pa·m<sup>3</sup>/s 以下。

[0345] 另外，成膜室、基板加熱室以及傳送室等的真空室中的全壓及分壓可以使用質量分析器進行測量。例如，ULVAC, Inc. 製造的四極質量分析器（也稱爲 Q-mass）Qulee CGM-051 即可。另外，洩漏率可以根據利用上述質量分析器測量出的全壓及分壓算出。洩漏率由外部洩漏及內部洩漏決定。外部洩漏是指：由於微小的孔或密封不良等，氣體從真空系統的外部流入的現象。此外，內部洩漏是指來自真空系統中的閥等隔板的洩漏或內部構件的氣體釋放。爲了將洩漏率設定爲上述數值以下，需要從外部洩漏及內部洩漏的兩個方面採取措施。

[0346] 雖然存在於成膜室內的附著物附著於內壁等而不影響成膜室的壓力，但是其是對成膜室進行排氣時產生的氣體釋放的主要原因。所以，使用排氣能力高的泵儘量地使存在於成膜室內的附著物脫離是十分重要的。另外，爲了促進附著物的脫離，也可以對成膜室進行烘烤。

[0347] 或者，較佳爲藉由導入被加熱的稀有氣體等的惰性氣體或氧等提高成膜室內的壓力，並在經過一定時間之後再次對成膜室進行排氣處理。藉由導入被加熱的氣體可以使成膜室內的附著物脫離，由此可以減少存在於成

膜室內的雜質。

[0348] 另外，藉由進行偽成膜也可以進一步提高附著物的脫離速度。偽成膜是指藉由濺射法等對偽基板進行成膜以在偽基板上及成膜室內壁沉積膜，由此將成膜室內的雜質及成膜室內壁的附著物密封於膜中。偽基板較佳為使用釋放氣體少的基板，例如也可以使用與在後面說明的基板 100 相同的基板。藉由進行偽成膜可以降低在後面形成的膜中的雜質濃度。另外，可以與烘烤同時進行偽成膜。

[0349] 藉由利用上述成膜裝置形成氧化物半導體層 106b，可以抑制雜質進入氧化物半導體層 106b。並且，藉由利用上述成膜裝置形成接觸於氧化物半導體層 106b 的膜，可以抑制雜質從接觸於氧化物半導體層 106b 的膜進入氧化物半導體層 106b。

[0350] 接著，說明利用上述成膜裝置連續地形成氧化物半導體層 106a、氧化物半導體層 106b 及氧化物半導體層 106c 的方法。

[0351] 首先，形成氧化物半導體層 106a。成膜時的基板加熱溫度越高，氧化物半導體層 106a 的雜質濃度越低。例如，將成膜時的基板溫度設定為 150°C 以上且 500 °C 以下，較佳為 170°C 以上且 450°C 以下。在將基板傳送到成膜室之後，導入成膜氣體，為了穩定壓力保持基板 10 秒以上且 1000 秒以下，較佳為 15 秒以上且 720 秒以下，然後形成氧化物半導體層 106a。為了穩定壓力，藉

由在上述時間保持基板，可以減少形成氧化物半導體層 106a 時的雜質的混入量。

[0352] 接著，將基板傳送到其他的成膜室，形成氧化物半導體層 106b。成膜時的基板加熱溫度越高，氧化物半導體層 106b 的雜質濃度越低。例如，將成膜時的基板溫度設定為 150°C 以上且 500°C 以下，較佳為 170°C 以上且 450°C 以下。在將基板傳送到成膜室之後，導入成膜氣體，為了穩定壓力保持基板 10 秒以上且 1000 秒以下，較佳為 15 秒以上且 720 秒以下，然後形成氧化物半導體層 106b。為了穩定壓力，藉由在上述時間保持基板，可以減少形成氧化物半導體層 106b 時的雜質的混入量。

[0353] 然後，將基板傳送到其他的成膜室，形成氧化物半導體層 106c。成膜時的基板加熱溫度越高，氧化物半導體層 106c 的雜質濃度越低。例如，將成膜時的基板溫度設定為 150°C 以上且 500°C 以下，較佳為 170°C 以上且 450°C 以下。在將基板傳送到成膜室之後，導入成膜氣體，為了穩定壓力保持基板 10 秒以上且 1000 秒以下，較佳為 15 秒以上且 720 秒以下，然後形成氧化物半導體層 106c。為了穩定壓力，藉由在上述時間保持基板，可以減少形成氧化物半導體層 106c 時的雜質的混入量。

[0354] 當對多個基板形成氧化物半導體層 106a、氧化物半導體層 106b 以及氧化物半導體層 106c 時，較佳為在不進行成膜的期間也繼續導入微量的稀有氣體或氧氣體等。由此，可以將成膜室的壓力保持為高，因此可以抑制

雜質從真空泵等倒流。另外，可以抑制雜質從管道或其他構件等放出來。因此，可以減少混入氧化物半導體層 106a、氧化物半導體層 106b 以及氧化物半導體層 106c 的雜質。例如，導入 1sccm 以上且 500sccm 以下，較佳為 2sccm 以上且 200sccm 以下，更佳為 5sccm 以上且 100sccm 以下的氬，即可。

[0355] 接著，進行加熱處理。加熱處理在惰性氛圍或氧化性氛圍下進行。加熱處理也可以在減壓狀態下進行。利用加熱處理可以降低氧化物半導體層 106a、氧化物半導體層 106b 以及氧化物半導體層 106c 中的雜質濃度。

[0356] 作為加熱處理，較佳為在惰性氛圍下進行加熱處理之後，在保持溫度的狀態下將氛圍切換為氧化氛圍再進行加熱處理。這是因為當在惰性氛圍下進行加熱處理時，雖然可以降低氧化物半導體層 106a、氧化物半導體層 106b 以及氧化物半導體層 106c 中的雜質濃度，但是有時在同時產生氧缺陷。藉由在氧化氛圍下進行加熱處理，可以減少此時產生的氧缺陷。

[0357] 藉由上述步驟獲得的氧化物半導體層 106a、氧化物半導體層 106b 以及氧化物半導體層 106c 的利用 SIMS 測定出的氬濃度為  $2 \times 10^{20} \text{ atoms/cm}^3$  以下，較佳為  $5 \times 10^{19} \text{ atoms/cm}^3$  以下，更佳為  $1 \times 10^{19} \text{ atoms/cm}^3$  以下，進一步較佳為  $5 \times 10^{18} \text{ atoms/cm}^3$  以下。

[0358] 另外，氧化物半導體層 106a、氧化物半導體

層 106b 以及氧化物半導體層 106c 的利用 SIMS 測定出的各碳濃度小於  $5 \times 10^{19} \text{ atoms/cm}^3$ ，較佳為  $5 \times 10^{18} \text{ atoms/cm}^3$  以下，更佳為  $2 \times 10^{18} \text{ atoms/cm}^3$  以下，進一步較佳為  $5 \times 10^{17} \text{ atoms/cm}^3$  以下。

[0359] 藉由上述步驟形成氧化物半導體層 106a、氧化物半導體層 106b 以及氧化物半導體層 106c，可以提高氧化物半導體層 106b 的結晶性並降低氧化物半導體層 106a、氧化物半導體層 106b、氧化物半導體層 106c、氧化物半導體層 106a 與氧化物半導體層 106b 之間界面以及氧化物半導體層 106b 與氧化物半導體層 106c 之間的界面的雜質濃度。

[0360]

〈電晶體結構（2）〉

接著，對與電晶體結構（1）不同的頂閘極頂接觸電晶體的一個例子進行說明。

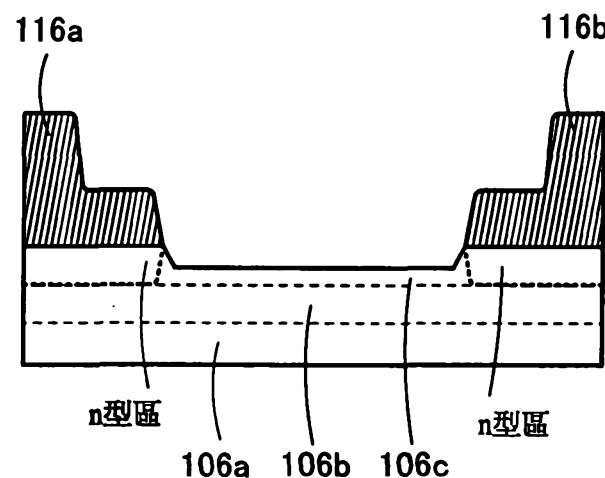

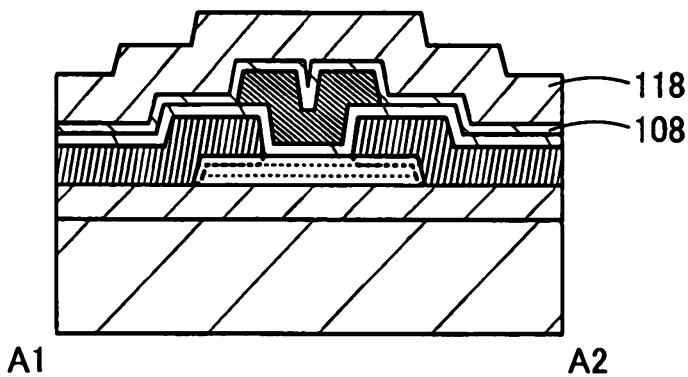

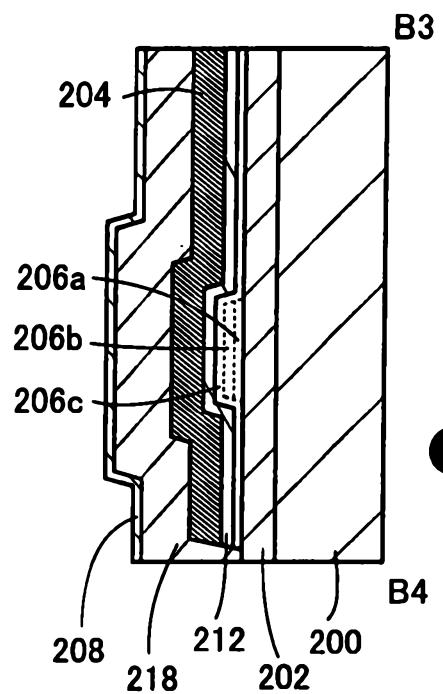

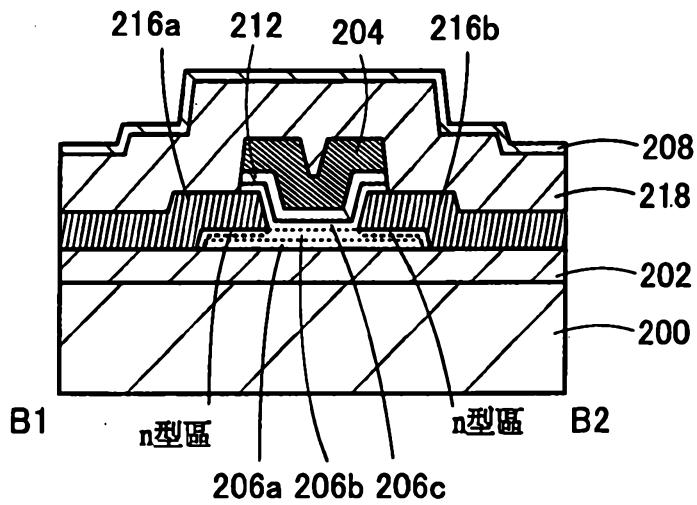

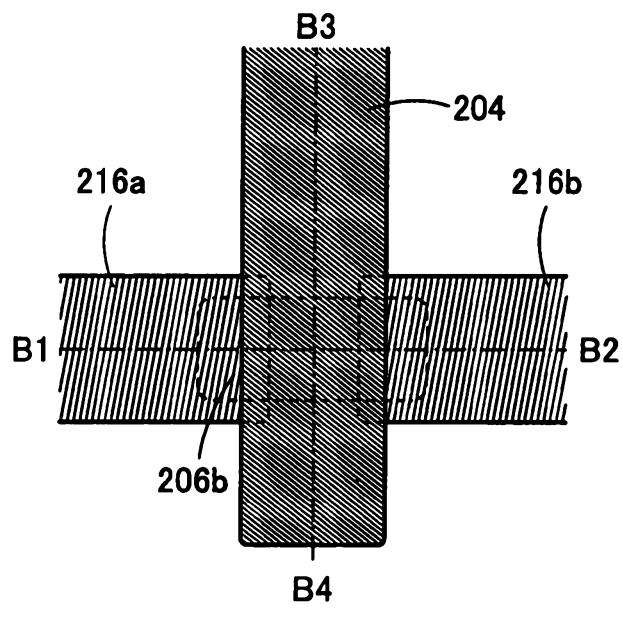

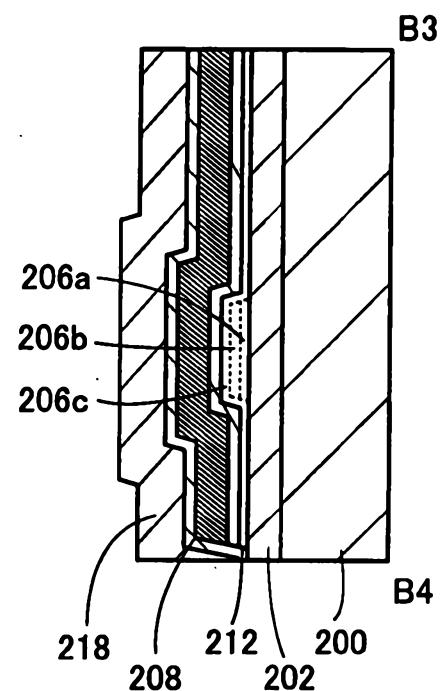

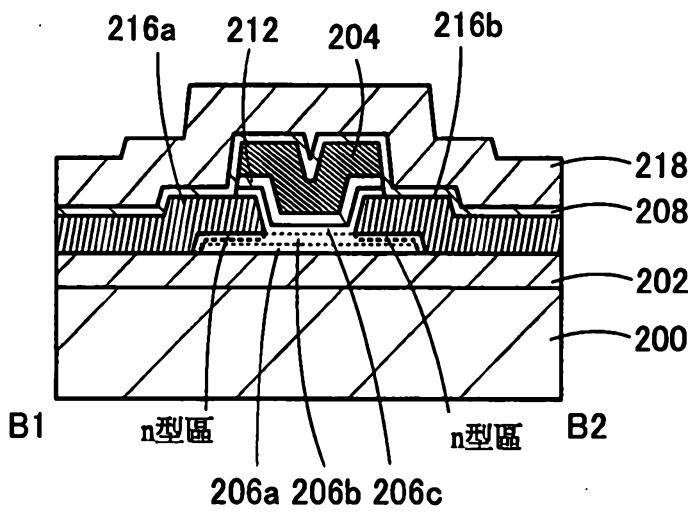

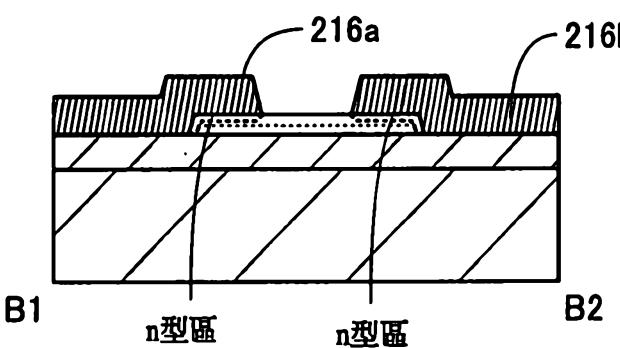

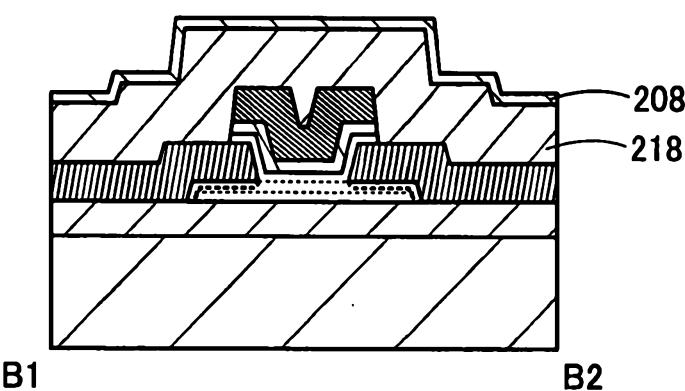

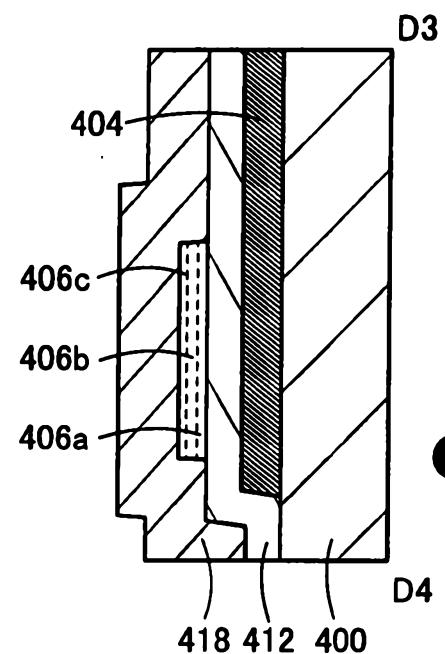

[0361] 圖 20A 至圖 20C 為電晶體的俯視圖及剖面圖。圖 20A 示出電晶體的俯視圖。圖 20B 示出對應於圖 20A 中的點劃線 B1-B2 的剖面圖。另外，圖 20C 示出對應於圖 20A 中的點劃線 B3-B4 的剖面圖。

[0362] 圖 20B 所示的電晶體包括：基板 200 上的基底絕緣膜 202；基底絕緣膜 202 上的氧化物半導體層 206a；氧化物半導體層 206a 上的氧化物半導體層 206b；接觸於氧化物半導體層 206b 的源極電極 216a 及汲極電極 216b；氧化物半導體層 206b、源極電極 216a 以及汲極電

極 216b 上的氧化物半導體層 206c；氧化物半導體層 206c 上的閘極絕緣膜 212；閘極絕緣膜 212 上的閘極電極 204。另外，較佳為在閘極絕緣膜 212 及閘極電極 204 上設置保護絕緣膜 218 及保護絕緣膜 218 上的保護絕緣膜 208。另外，電晶體也可以不具有基底絕緣膜 202。

[0363] 此外，在圖 20B 所示的電晶體中，也可以調換保護絕緣膜 208 和保護絕緣膜 218 的疊層順序（參照圖 21A 至圖 21C）。有時與在圖 20A 至圖 20C 所示的電晶體中相比，在圖 21A 至圖 21C 所示的電晶體中不容易發生從基底絕緣膜 202 釋放的過剩氧的外方擴散。因此，與在圖 20A 至圖 20C 所示的電晶體中相比，有可以降低氧化物半導體層 206a、氧化物半導體層 206b 以及氧化物半導體層 206c 中的氧缺陷（可以降低 DOS）的可能性。

[0364] 圖 20A 至圖 20C 所示的電晶體中的氧化物半導體層 206a 例如對應於圖 1A 和圖 1B 所示的氧化物半導體層 (S1)。圖 20A 至圖 20C 所示的電晶體中的氧化物半導體層 206b 例如對應於圖 1A 和圖 1B 所示的氧化物半導體層 (S2)。圖 20A 至圖 20C 所示的電晶體中的氧化物半導體層 206c 例如對應於圖 1A 和圖 1B 所示的氧化物半導體層 (S3)。

[0365] 另外，圖 20A 至圖 20C 所示的電晶體的基底絕緣膜 202 例如相當於圖 5A 所示的電晶體的閘極絕緣膜 (bg)。另外，圖 20A 至圖 20C 所示的電晶體例如可以具有圖 5A 所示的電晶體的閘極電極 (bg)。圖 20A 至圖

20C 所示的電晶體例如也可以具有與閘極電極 204 對置且接觸於基底絕緣膜 202 的底面的背閘極電極。另外，在圖 20A 至圖 20C 所示的電晶體中，在基板 200 具有導電性的情況下，例如，基板 200 可以相當於圖 5A 所示的電晶體的閘極絕緣膜 (bg)。另外，在圖 20A 至圖 20C 所示的電晶體中，在基底絕緣膜 202 下設置有佈線等的導電膜的情況下，該導電膜也可以相當於圖 5A 所示的電晶體的閘極絕緣膜 (bg)。

[0366] 注意，在圖 20A 至圖 20C 中，示出閘極電極 204、閘極絕緣膜 212 和氧化物半導體層 206c 具有大致相同的俯視形狀（俯視圖中的形狀）的例子，但是不侷限於此。例如，氧化物半導體層 206c 或/及閘極絕緣膜 212 的也可以設置在閘極電極 204 的外側。

[0367] 另外，用於源極電極 216a 及汲極電極 216b 的導電膜的有些材料有可能抽出氧化物半導體層 206b 的一部分中的氧，或者形成混合層而在氧化物半導體層 206b 中形成 n 型區。

[0368] 另外，如圖 20A 的俯視圖所示，氧化物半導體層 206b 的一部分設置在閘極電極 204 的外側。注意，氧化物半導體層 206b 的整體也可以設置在閘極電極 204 的內側。由此，當光從閘極電極 204 一側入射時，可以抑制因光而在氧化物半導體層 206b 中產生載子。換言之，閘極電極 204 具有遮光膜的功能。

[0369] 另外，也可以調換保護絕緣膜 218 和保護絕

緣膜 208 的上下位置。例如，也可以在保護絕緣膜 208 上設置有保護絕緣膜 218。

[0370] 關於氧化物半導體層 206a、氧化物半導體層 206b 和氧化物半導體層 206c 分別參照氧化物半導體層 106a、氧化物半導體層 106b 和氧化物半導體層 106c 的記載。關於基底絕緣膜 202，參照基底絕緣膜 102 的記載。關於源極電極 216a 及汲極電極 216b，參照源極電極 116a 及汲極電極 116b 的記載。關於閘極絕緣膜 212，參照閘極絕緣膜 112 的記載。關於閘極電極 204，參照閘極電極 104 的記載。關於保護絕緣膜 218，參照保護絕緣膜 118 的記載。關於保護絕緣膜 208，參照保護絕緣膜 108 的記載。關於基板 200，參照基板 100 的記載。

[0371]

〈電晶體結構（2）的製造方法〉

下面，對電晶體結構（2）的製造方法的一個例子進行說明。

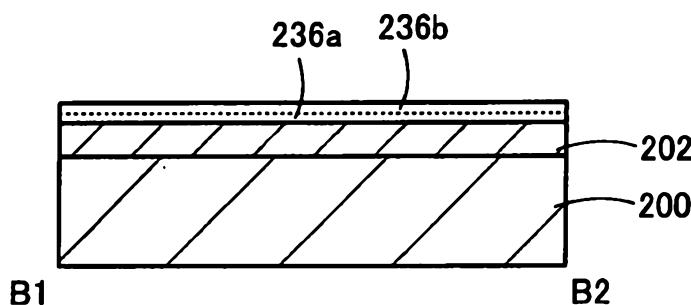

[0372] 圖 22A 至圖 23D 為對應於圖 20B 的剖面圖。

[0373] 首先，準備基板 200。

[0374] 接著，形成基底絕緣膜 202。關於基底絕緣膜 202 的形成方法，參照基底絕緣膜 102 的形成方法的記載。

[0375] 接著，依次形成氧化物半導體層 236a 及氧化物半導體層 236b（參照圖 22A）。關於氧化物半導體層 236a 及氧化物半導體層 236b 的形成方法，分別參照氧化

物半導體層 136a 及氧化物半導體層 136b 的形成方法。

[0376] 接著，較佳為進行第一加熱處理。關於第一加熱處理，參照電晶體結構 (1) 的製造方法的記載。

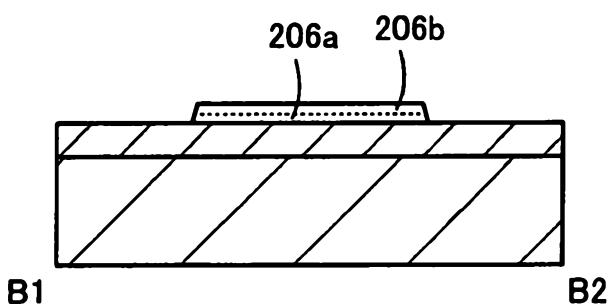

[0377] 接著，對氧化物半導體層 236a 及氧化物半導體層 236b 的一部分進行蝕刻，來形成島狀的氧化物半導體層 206a 及氧化物半導體層 206b (參照圖 22B)。

[0378] 接著，形成導電膜 216 (參照圖 22C)。關於導電膜 216 的形成方法，參照導電膜 116 的形成方法的記載。

[0379] 接著，對導電膜 216 的一部分進行蝕刻，來形成源極電極 216a 及汲極電極 216b。

[0380] 接著，較佳為進行第二加熱處理。關於第二加熱處理，參照電晶體結構 (1) 的製造方法的記載。藉由進行第二加熱處理，有時可以使氧化物半導體層 206b 的露出的 n 型區成為 i 型區 (參照圖 22D)。

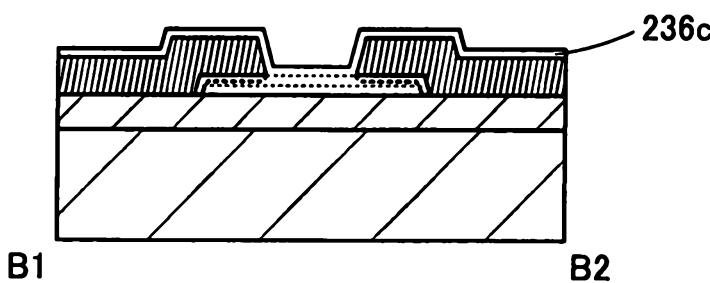

[0381] 接著，形成氧化物半導體層 236c (參照圖 23A)。關於氧化物半導體層 236c 的形成方法，參照氧化物半導體層 136c 的形成方法的記載。

[0382] 接著，形成絕緣膜 242。關於絕緣膜 242 的形成方法，參照閘極絕緣膜 112 的形成方法。

[0383] 絶緣膜 242 例如可以藉由利用電漿的 CVD 法形成。當進行 CVD 法時，基板溫度越高，可以得到具有較低的缺陷密度的較緻密的絕緣膜。因為絕緣膜 242 在被加工之後用作閘極絕緣膜 212，所以越緻密且缺陷密度越

低，而電晶體的電特性越穩定。另一方面，在基底絕緣膜 202 包含過剩氧時，電晶體的電特性穩定。但是，由於在基底絕緣膜 202 露出的狀態下增高基板溫度，而有可能從基底絕緣膜 202 氧釋放而過剩氧減少。在此，在形成絕緣膜 242 時，基底絕緣膜 202 由氧化物半導體層 236c 覆蓋，由此可以抑制氧從基底絕緣膜 202 釋放。因此，可以形成緻密且缺陷密度低的絕緣膜 242 而不減少包含在基底絕緣膜 202 中的過剩氧。由此，可以提高電晶體的可靠性。

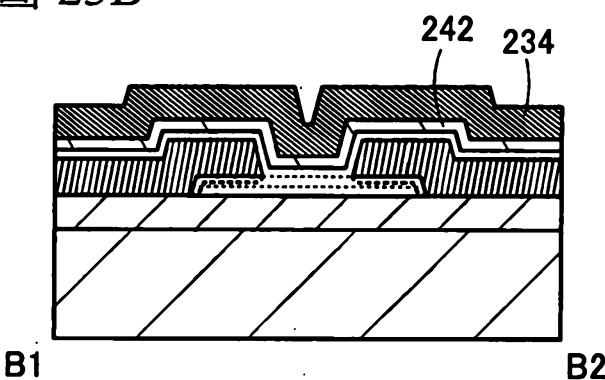

[0384] 接著，形成導電膜 234（參照圖 23B）。關於導電膜 234 的形成方法，參照成為閘極電極 104 的導電膜的形成方法的記載。

[0385] 接著，對氧化物半導體層 236c、絕緣膜 242 及導電膜 234 的一部分進行蝕刻，來形成氧化物半導體層 206c、閘極絕緣膜 212 及閘極電極 204（參照圖 23C）。

[0386] 接著，形成保護絕緣膜 218。關於保護絕緣膜 218 的形成方法，參照保護絕緣膜 118 的形成方法的記載。

[0387] 接著，形成保護絕緣膜 208（參照圖 23D）。關於保護絕緣膜 208 的形成方法，參照保護絕緣膜 108 的形成方法的記載。

[0388] 接著，較佳為進行第三加熱處理。關於第三加熱處理，參照電晶體結構（1）的製造方法的記載。

[0389] 藉由以上步驟，可以製造圖 20A 至圖 20C 所

示的電晶體。

[0390]

〈電晶體結構（3）〉

接著，對底閘極頂接觸電晶體的一個例子進行說明。

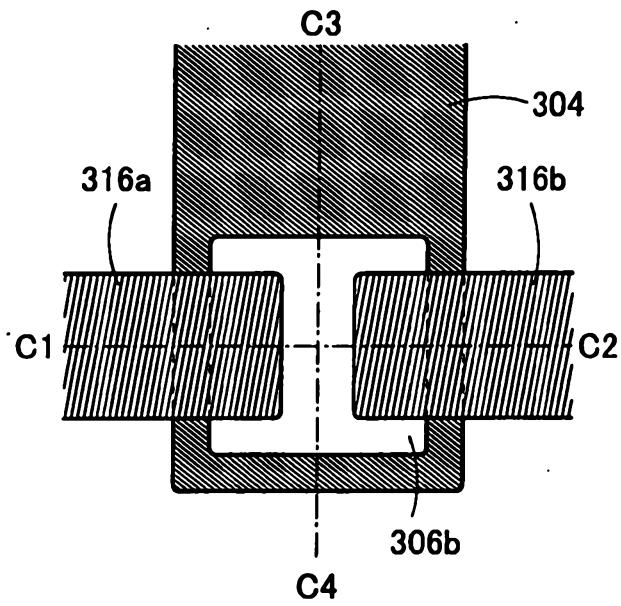

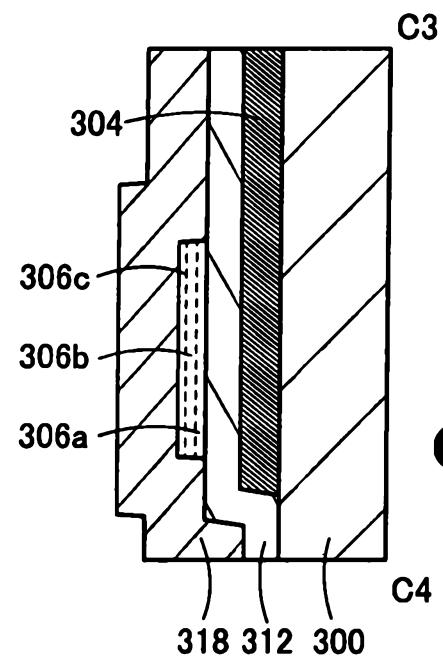

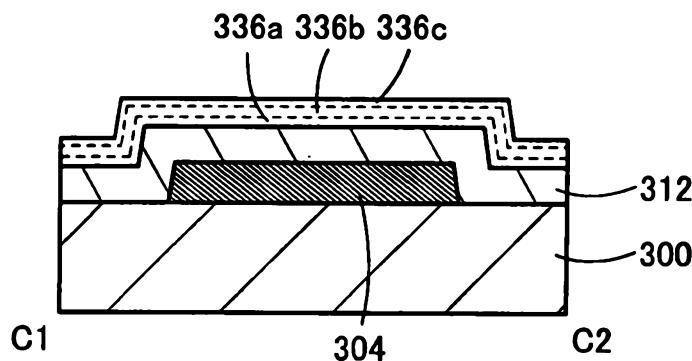

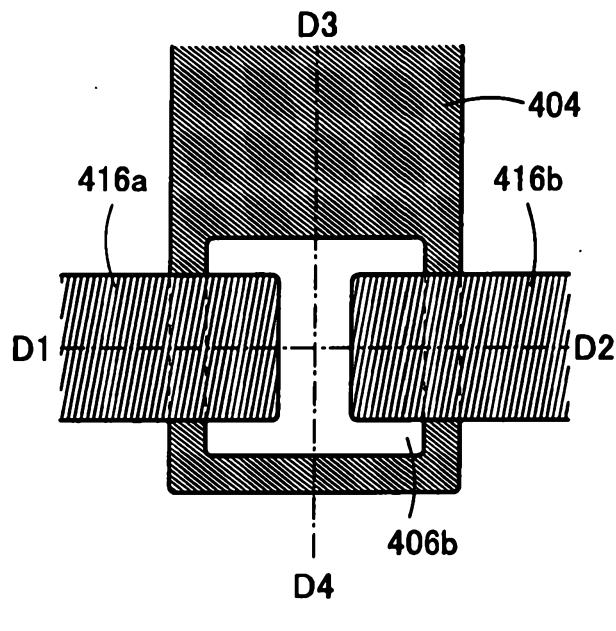

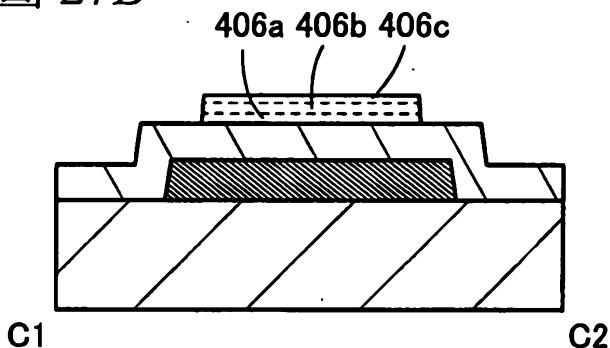

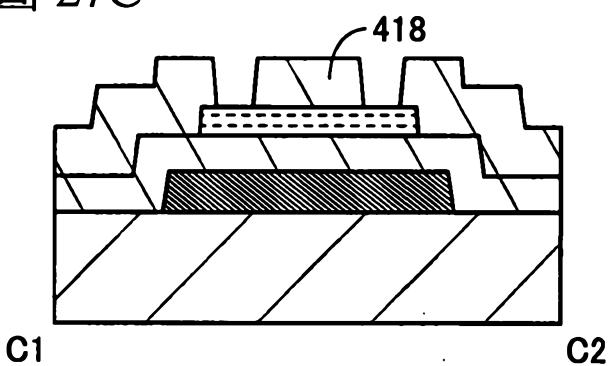

[0391] 圖 24A 至圖 24C 為電晶體的俯視圖及剖面圖。圖 24A 示出電晶體的俯視圖。圖 24B 示出對應於圖 24A 中的點劃線 C1-C2 的剖面圖。另外，圖 24C 示出對應於圖 24A 中的點劃線 C3-C4 的剖面圖。

[0392] 圖 24B 所示的電晶體包括：基板 300 上的閘極電極 304；閘極電極 304 上的閘極絕緣膜 312；閘極絕緣膜 312 上的氧化物半導體層 306a；氧化物半導體層 306a 上的氧化物半導體層 306b；氧化物半導體層 306b 上的氧化物半導體層 306c；以及接觸於氧化物半導體層 306c 的源極電極 316a 及汲極電極 316b。另外，較佳為設置氧化物半導體層 306c、源極電極 316a 及汲極電極 316b 上的保護絕緣膜 318。

[0393] 另外，圖 24A 至圖 24D 所示的電晶體的保護絕緣膜 318 例如相當於圖 5A 所示的電晶體的閘極絕緣膜（bg）。另外，圖 24A 至圖 24D 所示的電晶體例如可以具有圖 5A 所示的電晶體的閘極電極（bg）。圖 24A 至圖 24D 所示的電晶體例如也可以具有與閘極電極 304 對置且接觸於保護絕緣膜 318 的頂面的背閘極電極。另外，在圖 24A 至圖 24D 所示的電晶體中，在保護絕緣膜 318 上設置有佈線等的導電膜的情況下，該導電膜也可以相當於圖

5A 所示的電晶體的閘極絕緣膜 (bg) 。

[0394] 另外，用於源極電極 316a 及汲極電極 316b 的導電膜的有些材料有可能抽出氧化物半導體層 306b、氧化物半導體層 306c 的一部分中的氧，或者形成混合層而在氧化物半導體層 306b、氧化物半導體層 306c 中形成 n 型區（低電阻區）。

[0395] 另外，如圖 24A 所示，在俯視圖中以氧化物半導體層 306b 的邊緣部位於閘極電極 304 的邊緣部的內側的方式設置閘極電極 304。由此，當光從閘極電極 304 一側入射時，可以抑制因光而在氧化物半導體層 306b 中產生載子。換言之，閘極電極 304 具有遮光膜的功能。注意，氧化物半導體層 306b 的邊緣部也可以位於閘極電極 304 的邊緣部的外側。

[0396] 關於氧化物半導體層 306a、氧化物半導體層 306b 和氧化物半導體層 306c 分別參照氧化物半導體層 106c、氧化物半導體層 106b 和氧化物半導體層 106a 的記載。就是說，底閘極頂接觸電晶體具有如將頂閘極頂接觸電晶體的上下翻轉那樣的疊層結構。

[0397] 作為保護絕緣膜 318，可以使用包含氧化鋁、氧化鎂、氧化矽、氮氧化矽、氮氧化矽、氮化矽、氧化鎵、氧化鋒、氧化釔、氧化鋯、氧化鑭、氧化釤、氧化鉻和氧化鉬中的一種以上的絕緣膜的單層或疊層。

[0398] 作為保護絕緣膜 318，例如可以採用第一層為氧化矽層，第二層為氮化矽層的多層膜。在此情況下，氧

化矽層也可以為氧化矽層。另外，氮化矽層也可以為氮氧化矽層。氧化矽層較佳為使用缺陷密度低的氧化矽層。明確而言，使用如下氧化矽層：在利用 ESR 測定出的來源於  $g$  值為 2.001 的信號的自旋的密度為  $3 \times 10^{17} \text{ spins/cm}^3$  以下，較佳為  $5 \times 10^{16} \text{ spins/cm}^3$  以下。氮化矽層使用氫氣體及氮氣體的釋放量少的氮化矽層。氫氣體及氮氣體的釋放量藉由 TDS 分析測定即可。另外，氮化矽層使用不使氫、水以及氧透過或幾乎不使其透過的氮化矽層。