RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(A n'utiliser que pour les

commandes de reproduction).

**2 496 342**

A1

**DEMANDE

DE BREVET D'INVENTION**

(21)

**N° 81 20526**

(54) Dispositif semi-conducteur du type métal-oxyde-semi-conducteur et son procédé de fabrication.

(51) Classification internationale (Int. Cl. 3). H 01 L 29/78, 21/18.

(22) Date de dépôt ..... 2 novembre 1981.

(33) (32) (31) Priorité revendiquée : Japon, 12 décembre 1980, n° 175304/80.

(41) Date de la mise à la disposition du

public de la demande ..... B.O.P.I. — « Listes » n° 24 du 18-6-1982.

(71) Déposant : Société dite : TOKYO SHIBAURA DENKI KK, résidant au Japon.

(72) Invention de : Yukimasa Uchida.

(73) Titulaire : *Idem* (71)

(74) Mandataire : Cabinet Beau de Loménie,

55, rue d'Amsterdam, 75008 Paris.

La présente invention concerne un dispositif semi-conducteur du type métal-oxyde-semiconducteur et son procédé de fabrication.

Pour préparer un dispositif métal-oxyde-semiconducteur

5 (soit MOS) intégré à grande échelle de haute rapidité ou pour améliorer la densité d'intégration, il est avantageux de former un transistor MOS sur un substrat isolant constitué par exemple de saphir ou de spinelle (rubis). Comme semblable type de dispositif semiconducteur MOS, il est généralement utilisé un dispositif MOS

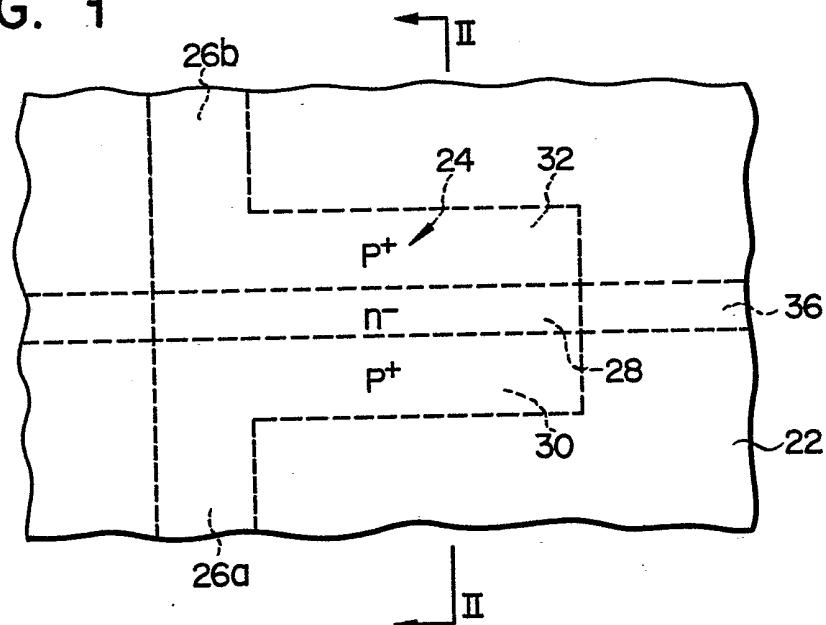

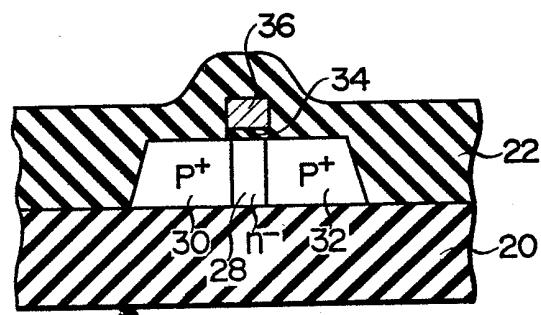

10 intégré à grande échelle ayant une structure silicium sur saphir (connue sous le nom de structure SOS), selon laquelle on forme un transistor MOS sur une couche de silicium, laquelle est elle-même formée sur un substrat de saphir. La figure 1 est une vue en plan d'un transistor à canal p d'un dispositif MOS intégré à grande

15 échelle de structure SOS, et la figure 2 est une vue en coupe suivant la ligne II-II de la figure 1. Sur un substrat de saphir 20, on forme une couche de silicium, que l'on revêt complètement, pour l'isoler, d'une pellicule 22 constituant un isolant par rapport au champ. Cette couche de silicium comprend une région d'élément 24

20 et des couches de câblage de diffusion de type p<sup>+</sup> 26a et 26b qui se prolongent, à l'extrémité de la région d'élément 24, suivant la direction de la longueur du canal. Dans la région d'élément 24, on forme une région source 30 de type p<sup>+</sup> et une région drain 32 de type p<sup>+</sup> entre lesquelles est interposée une région substrat 28 de

25 type n<sup>-</sup>, où le canal doit être formé. La région source 30 est connectée à la couche de câblage 26a de diffusion de type p<sup>+</sup>, et la région source 32 est connectée à la couche de câblage 26b de diffusion de type p<sup>+</sup>. On forme une électrode de grille 36 sur la région substrat 28 en interposant entre elles une pellicule 34 d'oxyde

30 pour grille en oxyde de silicium.

Dans un dispositif semiconducteur de type MOS à structure SOS selon cette forme, puisque chaque région d'élément 24 est séparée des autres par le substrat isolant 20 de saphir, la capacité de diffusion de la région d'élément 24 est extrêmement faible. De plus, les capacités des couches de câblage de diffusion 26a et 26b et les capacités de câblage générales sont également

extrêmement faibles. Ceci autorise un fonctionnement très rapide des éléments semiconducteurs. Puisque les éléments semiconducteurs sont isolés et séparés les uns des autres, il n'est pas besoin de former une couche de diffusion de puits dans le cas d'un dispositif 5 semiconducteur MOS complémentaire. Ceci empêche le phénomène de verrouillage même lorsque la distance entre les éléments semiconducteurs est courte. Puisque les couches de câblage de diffusion 26a et 26b sont séparées des couches de câblage de diffusion des autres éléments semiconducteurs par des isolants, le phénomène de perçage 10 ne se produit pas lorsque les couches de câblage de diffusion sont proches l'une de l'autre. On peut donc former les éléments semi-conducteurs avec une densité d'intégration élevée.

Le dispositif MOS à structure SOS possède les avantages décrits ci-dessus ainsi que les inconvénients qui vont être décrits 15 ci-après. Comme on peut le voir sur les figures 1 et 2, dans un dispositif MOS à structure SOS, on ne forme généralement pas d'électrode de substrat, puisque celle-ci est dure à former. Pour cette raison, dans le cas d'un transistor à canal p tel que celui présenté 20 par exemple sur les figures 1 et 2, le potentiel de la région de type n<sup>-</sup> (ci-après désignée comme étant la région substrat) se trouvant au-dessous de l'électrode de grille 36 où le canal doit être formé est instable, ce qui entraîne l'effet dit de substrat flottant selon lequel le potentiel de la région substrat flotte. Ceci produit des problèmes de caractéristiques qui vont être décrits 25 ci-après. Lorsqu'un courant de fuite circule entre la région drain 32 et la région substrat 28, une charge s'accumule dans la région substrat 28, si bien que la région substrat 28 est polarisée en sens passant par rapport à la région source 30. En résultat, la tension de seuil s'abaisse et le transistor peut ne pas passer dans l'état 30 non conducteur. De plus, les caractéristiques tension-courant du transistor présentent un phénomène d'entortillement, et la circulation anormale du courant peut rendre instable le fonctionnement du transistor.

Dans le cas d'un transistor à canal n, le phénomène dit 35 de pompage de charge survient, dans lequel les électrons du canal restent dans la région substrat lorsque le transistor passe dans

l'état non conducteur. Une polarisation inverse est donc induite entre la région substrat et la région source. La tension de seuil du transistor est augmentée par l'effet de rétropolarisation de grille que provoque la polarisation inverse. Puisque la transconductance  $g_m$  5 s'abaisse, le retard de fonctionnement tend à dépendre de la fréquence.

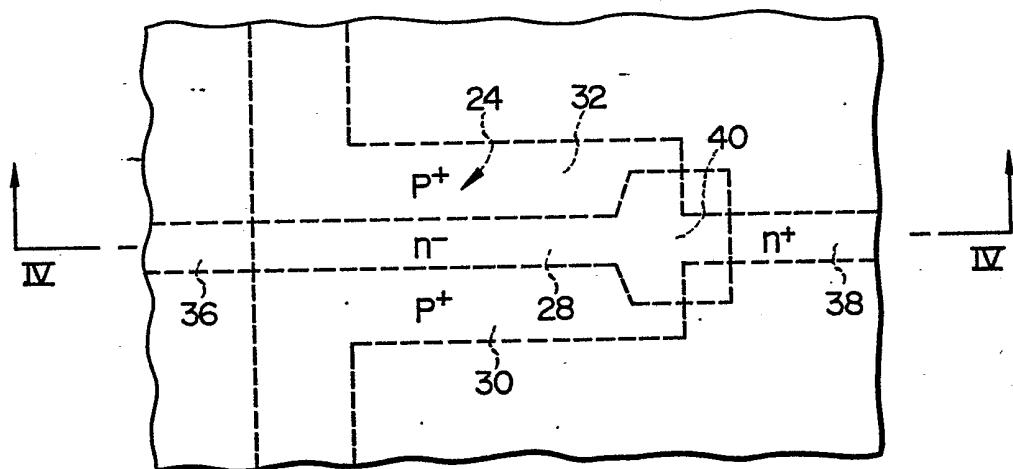

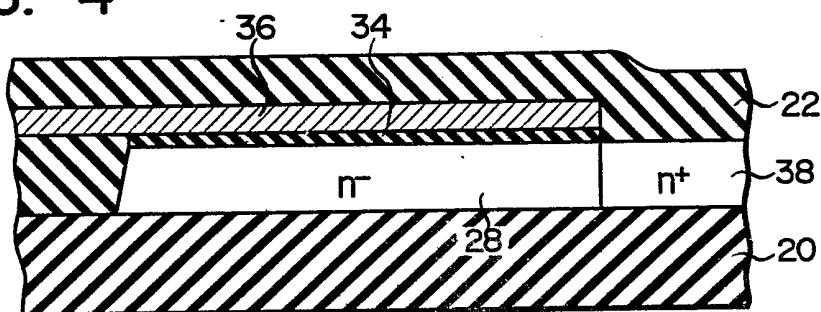

Pour éliminer les inconvénients qui peuvent ainsi être provoqués dans un dispositif MOS à structure SOS en raison de l'effet de substrat flottant, il a été proposé un dispositif MOS à structure SOS, comme le montrent les figures 3 et 4, dans lequel il est formé 10 une couche de câblage 38 de substrat qui part de la région substrat 28 dans la direction de la largeur de canal. Un potentiel constant est appliqué à la région substrat 28 par l'intermédiaire de l'électrode de substrat formée dans la couche de câblage 38 de substrat. La figure 3 est une vue en plan d'un transistor à canal p d'un dispositif MOS à 15 structure SOS classique ayant une électrode de substrat, et la figure 4 est une vue en coupe prise suivant la ligne IV-IV de la figure 3. La couche de câblage 38 de substrat consiste en du silicium de type  $n^+$ .

Dans un dispositif MOS à structure SOS classique où 20 l'électrode de substrat est formée de la manière présentée sur la figure 3, l'électrode de grille 36 se termine en une partie qui est légèrement à l'extérieur de la partie terminale de la région d'élément 24, et la partie terminale 40 de l'électrode de grille 36 est 25 élargie, si bien que la couche de câblage de substrat peut s'aligner d'elle-même en utilisant l'électrode de grille 36 comme masque. La largeur de la partie terminale 40 de l'électrode de grille 36 augmente pour les raisons qui vont être indiquées ci-après.

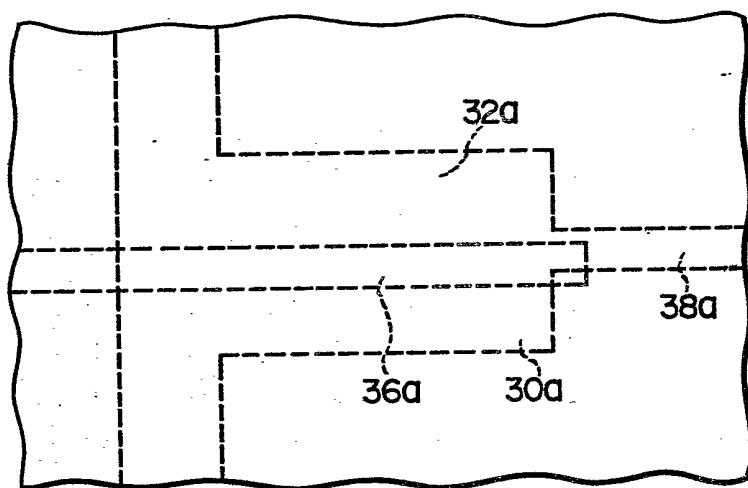

On configure l'électrode de grille 36 par un moyen photolithographique. Lorsqu'une erreur s'introduit dans l'alignement 30 de masquage, l'électrode de grille 36 est mal alignée. Ainsi, si la partie terminale de l'électrode de grille n'est pas élargie, il se forme une électrode de grille 36a, comme le montre la figure 5. Ensuite, on introduit une impureté de type p, par exemple du bore, en utilisant l'électrode de grille 36a comme masque pour former une 35 région source 30a de type  $p^+$  et une région drain 32a de type  $p^+$ . De plus, on introduit une impureté de type n, par exemple du phos-

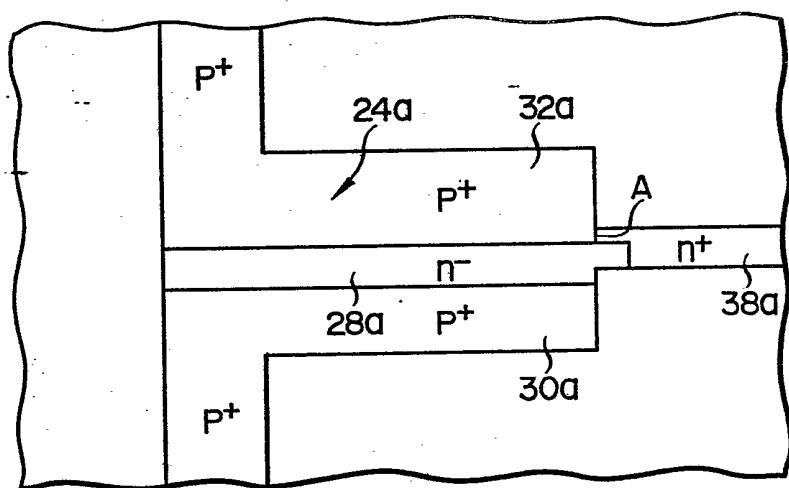

phore, pour former une couche de câblage de substrat 38a de type  $n^+$ . La figure 6 montre une région d'élément 24a et la couche de câblage de substrat 38a alors que l'électrode de grille 36a et la couche isolante ont été enlevées. La région source 30a et la région drain 32a 5 formées par introduction d'une impureté de dopage utilisant l'électrode de grille 36a comme masque sont de type  $p^+$ . D'autre part, puisque l'impureté de dopage de type  $n$  est introduite dans la région d'élément 24a avant la formation de la région source 30a et de la région drain 32a afin de rendre la région d'élément de type  $n^-$ , une 10 région substrat 28a se trouvant au-dessous de l'électrode de grille 36a où le canal doit être formé est de type  $n^-$ . La couche de câblage de substrat 38a est de type  $n^+$ , ainsi que cela a déjà été indiqué. Lorsque l'électrode de grille 36a est mal alignée, la région drain 32a de type  $p^+$  et la couche de câblage de substrat 38a de 15 type  $n^+$  forment une jonction directe au niveau de la partie A. Par conséquent, puisque la capacité de jonction est notablement augmentée par la jonction  $p^+ - n^+$  à concentration élevée, la rapidité de fonctionnement de l'élément semiconducteur subit une diminution.

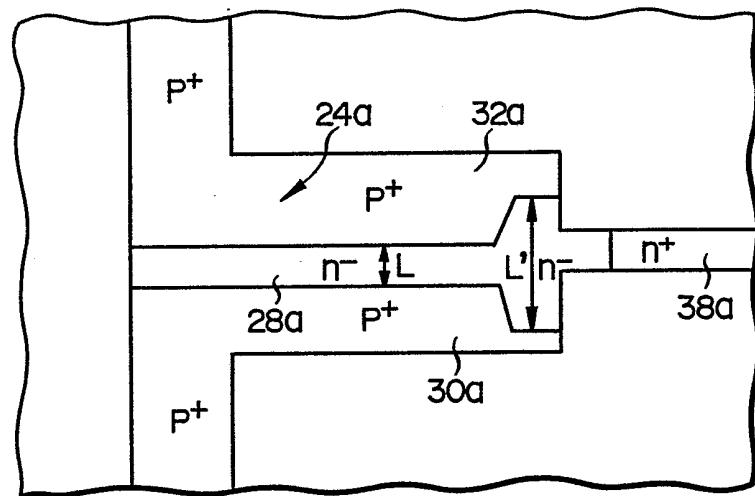

D'autre part, lorsqu'une partie terminale 40 de 20 l'électrode de grille 36 est élargie de la manière présentée sur la figure 3, la région d'élément 24a et la couche de câble de substrat 38a, que l'on peut voir sur la figure 7, se forment même lorsque l'électrode de grille 36 a été réalisée d'une manière mal alignée. Dans ce cas, puisque la partie terminale 40 de l'électrode 25 de grille 36 est élargie et est utilisée comme masque pendant la formation de la région source 30a de type  $p^+$  et de la région drain 32a de type  $p^+$  par introduction d'une impureté de dopage, le défaut d'alignement de l'électrode de grille 36 n'enraîne pas la formation d'une jonction directe entre la région drain 32a de type  $p^+$  et la 30 couche de câblage de substrat 38a de type  $n^+$ . Puisque la jonction  $p^+ - n^+$  à concentration élevée ne se forme pas, il est possible d'empêcher l'importante augmentation signalée ci-dessus de la capacité de jonction. Bien que les aires de jonction reliant la région source 30a et la région substrat 28a et reliant la région 35 drain 32a et la région substrat 28a soient élargies, ces jonctions sont des jonctions  $p^+ - n^-$ . La capacité est dans ce cas beaucoup plus

petite que la capacité de jonction de la jonction  $p^{+}-n^{+}$  à concentration élevée qui a été décrite ci-dessus.

Pour les raisons données ci-dessus, la partie terminale 40 de l'électrode de grille 36 est élargie dans le dispositif MOS à structure SOS classique où l'on forme une électrode de substrat. Toutefois, l'élargissement de la partie terminale 40 de l'électrode de grille 36 est la cause de certains problèmes indiqués ci-dessous.

(1) Puisque la longueur de canal  $L'$  de la région d'élément 24a dans laquelle est agrandie la largeur de l'électrode de grille est plus longue que la longueur de canal  $L$  de la région d'élément dans laquelle la largeur de l'électrode de grille n'est pas agrandie, la longueur de canal n'est pas constante sur toute la région d'élément. Ainsi, on ne peut obtenir les caractéristiques voulues pour les éléments semiconducteurs.

(2) Puisque l'on rend plus grande l'aire de la partie terminale 40 de l'électrode de grille, on augmente la capacité d'électrode de grille. La largeur (longueur de canal) de la partie non élargie de l'électrode de grille d'un dispositif MOS à structure SOS de ce type est généralement d'environ 2  $\mu\text{m}$ . Toutefois, la largeur de la partie terminale 40 de l'électrode de grille est dans ce cas de 8 à 10  $\mu\text{m}$ . Ainsi, l'augmentation de la capacité d'électrode de grille qui est due à la partie terminale 40 peut augmenter à un degré considérable.

(3) L'élargissement de la partie terminale 40 de l'électrode de grille augmente l'aire de l'élément.

Un but de l'invention est de proposer un dispositif semiconducteur de type MOS perfectionné que l'on forme sur une couche isolante et qui possède une électrode de substrat.

Pour réaliser le but visé, il est proposé selon l'invention un dispositif semiconducteur de type MOS qui se distingue en ce que, à une région substrat d'une première couche semiconductrice formée sur une couche isolante et destinée à former un élément de type MOS où un canal doit être formé, est connectée une deuxième couche semiconductrice qui est plus mince que la première couche semiconductrice et qui possède le même type de conductivité que la région substrat au niveau de laquelle le canal doit être formé.

Avec la structure décrite ci-dessus, on peut former l'électrode de substrat sans élargir la partie terminale de l'électrode de grille. On peut également empêcher l'augmentation de la capacité de jonction due à la jonction à concentration élevée 5 formée par le défaut d'alignement de configuration de l'électrode de grille.

De plus, puisque l'on peut rendre constante la longueur de canal sur toute la région d'élément, on peut obtenir des caractéristiques stables et voulues pour l'élément.

10 Puisqu'il n'est pas nécessaire d'augmenter l'aire de l'électrode de grille, on peut empêcher l'augmentation de la capacité d'électrode de grille et de l'aire de l'élément.

15 Puisque l'on n'est pas obligé de configurer la couche de câblage d'électrode constituant l'électrode de grille de manière qu'elle se termine en un certain point, on peut obtenir une densité d'intégration plus élevée.

20 La description suivante, conçue à titre d'illustration de l'invention, vise à donner une meilleure compréhension de ses caractéristiques et avantages; elle s'appuie sur les dessins annexés, parmi lesquels :

- la figure 1 est une vue en plan montrant une partie transistor à canal p d'un dispositif MOS à structure SOS classique;

- la figure 2 est une vue en coupe du dispositif de la figure 1 suivant la ligne II-II;

25 - la figure 3 est une vue en plan d'une partie transistor à canal p d'un autre dispositif MOS à structure SOS classique;

- la figure 4 est une vue en coupe du dispositif de la figure 3 suivant la ligne IV-IV;

- la figure 5 est une vue en plan d'une partie transistor 30 à canal p dans laquelle une électrode de grille, dont la partie terminale n'est pas élargie, est mal alignée;

- la figure 6 est une vue en plan du substrat semi-conducteur de la figure 5 (l'électrode de grille et la couche isolante ayant été enlevées), dans laquelle une impureté de dopage a été 35 introduite afin de former les régions source et drain;

- la figure 7 est une vue en plan du substrat semi-conducteur dans lequel une électrode de grille, dont la partie terminale est élargie, est mal alignée;

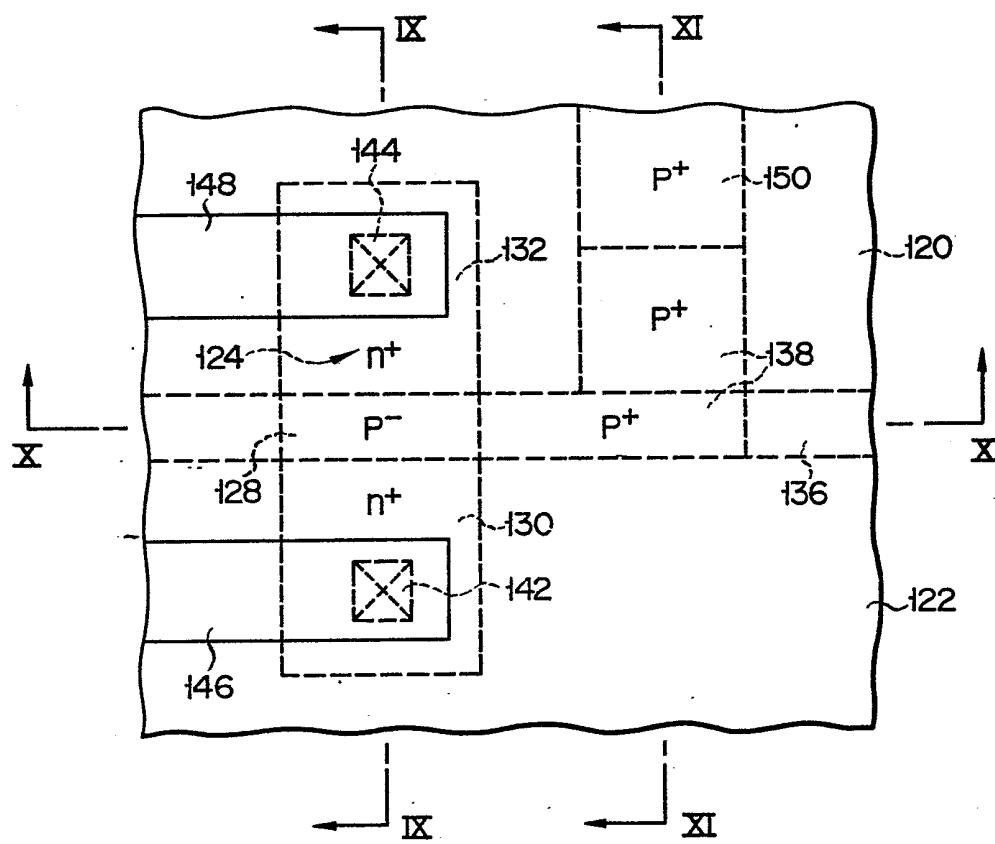

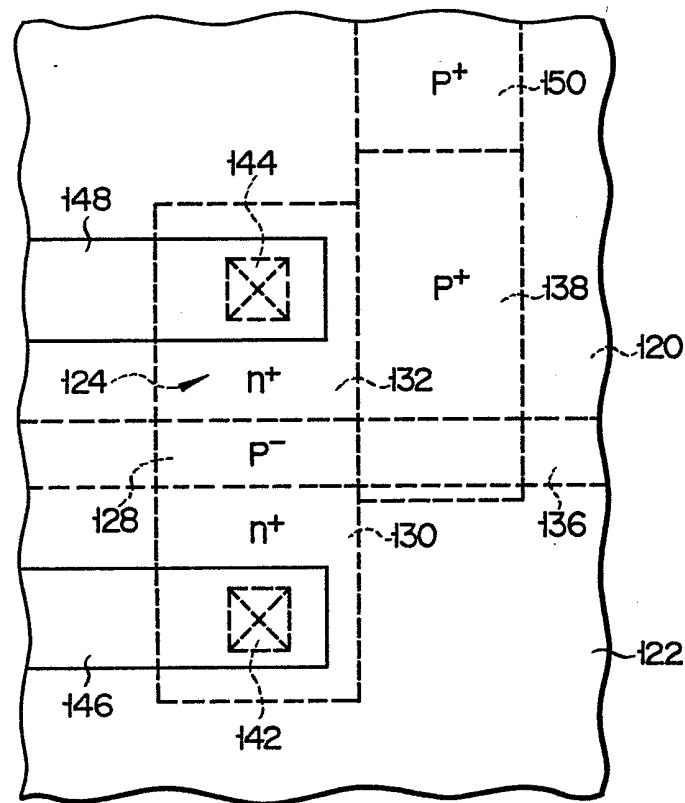

5 - la figure 8 est une vue en plan montrant un transistor à canal n d'un dispositif MOS à structure SOS selon l'invention;

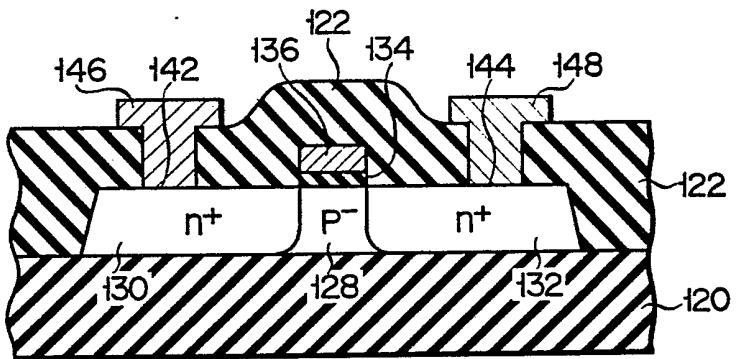

- la figure 9 est une vue en coupe du dispositif de la figure 8 suivant la ligne IX-IX;

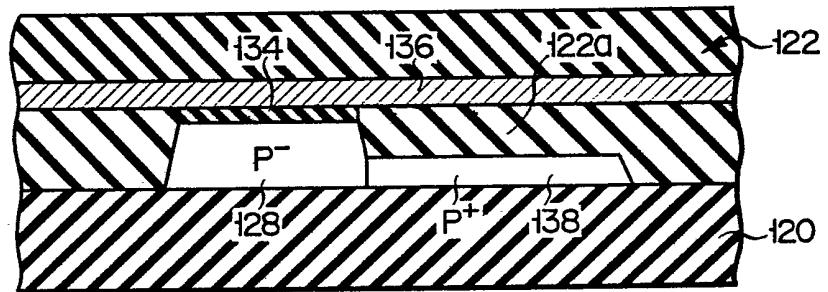

- la figure 10 est une vue en coupe du dispositif de la figure 8 suivant la ligne X-X;

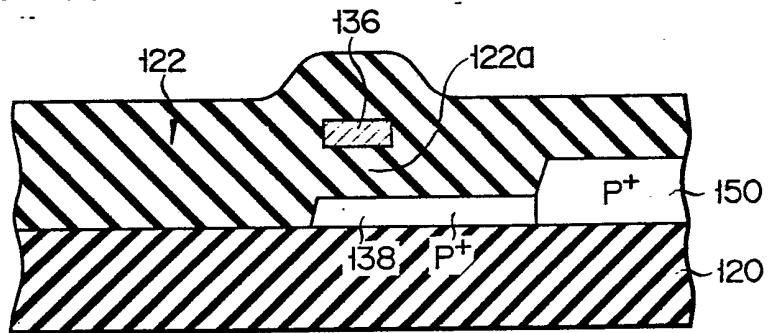

10 - la figure 11 est une vue en coupe du dispositif de la figure 8 suivant la ligne XI-XI;

- les figures 12A à 12G sont des vues en coupe du substrat semiconducteur du dispositif MOS à structure SOS de la figure 8 permettant de présenter le procédé de fabrication;

15 - la figure 13 est une vue en plan d'une partie transistor à canal n d'un autre dispositif MOS à structure SOS selon l'invention; et

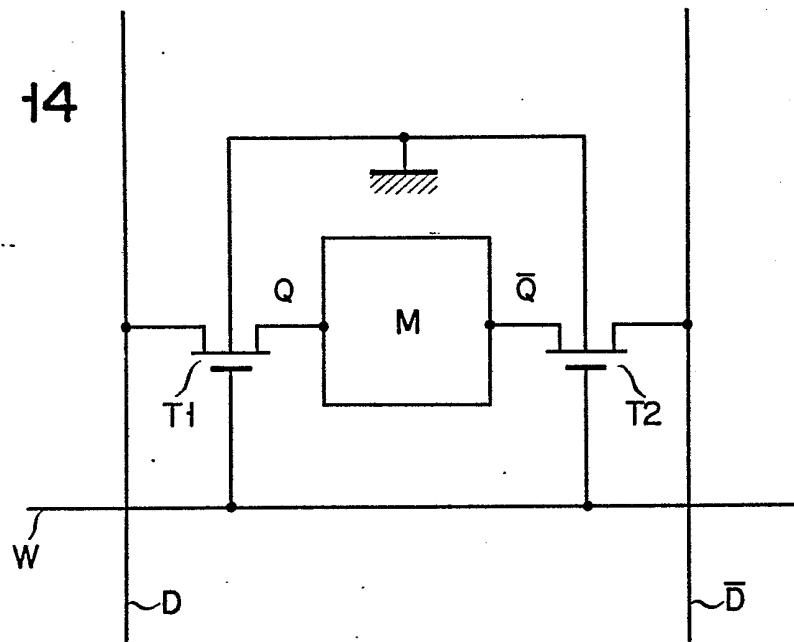

- la figure 14 est un schéma de circuit d'un dispositif MOS à structure SOS intégré à grande échelle qui est une application du dispositif MOS à structure SOS de l'invention.

20 Les modes de réalisation préférés du dispositif MOS à structure SOS de l'invention vont maintenant être décrits en relation avec les figures 8 à 11. La figure 8 est une vue en plan d'un transistor à canal n d'un dispositif MOS à structure SOS intégré à grande échelle selon l'invention. Sur un substrat de saphir 120, est

25 formée une région d'élément 124 de 0,6  $\mu$ m d'épaisseur qui comprend une couche de silicium formant un flot. Un transistor à canal n est formé dans la région d'élément 124. La région d'élément 124 et ce qui l'entoure vont être décrits en relation avec la figure 9, qui est une vue en coupe de la figure 8 suivant la ligne IX-IX. La région

30 d'élément 124 est revêtue d'une couche d'isolation 122 constituée de  $\text{SiO}_2$ . La région d'élément 124 comprend une région substrat 128 de type p- destinée à former un canal dans laquelle du bore a été introduit jusqu'à une concentration de dopage de  $10^{16} \text{ cm}^{-3}$ , ainsi qu'une région source 130 de type n<sup>+</sup> et une région drain 132 de type

35 n<sup>+</sup> dans lesquelles de l'arsenic est introduit jusqu'à une concentration de dopage de  $10^{19}$  à  $10^{20} \text{ cm}^{-3}$ . Un câblage 136 d'électrode de grille

en silicium polycristallin est formé sur la région substrat 128 de manière qu'une pellicule d'oxyde pour grille 134 en oxyde de silicium d'une épaisseur de 500 Å soit interposée entre eux. Le câblage d'électrode de grille 136 constitue l'électrode de grille du 5 transistor MOS. Le câblage d'électrode de grille 136 est revêtu par la couche d'isolation 122. Sur la couche d'isolation 122, sont formés des câblages 146 et 148 en aluminium qui établissent des contacts ohmiques avec la région source 130 et la région drain 132 via des trous de contact 142 et 144 ménagés respectivement dans la 10 couche d'isolation 122.

Comme le montre la figure 8, sur le substrat de saphir 120, est formée une couche de câblage 138 de substrat en silicium, en plus de la région d'élément 124. Cette couche de câblage de substrat 138 va être décrite en relation avec la figure 10, qui est une vue 15 en coupe du dispositif MOS à structure SOS de la figure 8 suivant la ligne X-X. La couche de câblage de substrat 138 comprend une couche de silicium formant un filot de 0,3  $\mu\text{m}$  d'épaisseur. Ainsi, l'épaisseur de la couche de câblage de substrat 138 vaut la moitié de l'épaisseur de la région d'élément 124, laquelle est de 0,6  $\mu\text{m}$ . 20 Du bore est introduit dans la couche de câblage de substrat 138 jusqu'à une concentration de dopage de  $10^{17} \text{ cm}^{-3}$ , cette valeur étant inférieure à la concentration en impuretés de  $10^{19}$  à  $10^{20} \text{ cm}^{-3}$  de la région source 130 et de la région drain 132, mais étant supérieure 25 à la concentration en impuretés de  $10^{16} \text{ cm}^{-3}$  de la région substrat 128. La couche de câblage de substrat 138 possède le même type de conductivité que la région substrat, mais a une concentration en impuretés plus élevée. Toutefois, la couche de câblage de substrat 30 138 a une conductivité opposée à celle de la région source 130 et de la région drain 132 et présente une concentration en impuretés inférieure à celles de la région source 130 et de la région drain 132. La couche de câblage de substrat est formée solidairement avec la région d'élément 124 de manière à prolonger la face terminale de la région substrat 128 de type p<sup>+</sup> dans la direction de la largeur de canal. La couche de câblage de substrat 35 138 est revêtue d'une couche d'isolation 122a en oxyde de silicium  $\text{SiO}_2$ . Le câblage d'électrode de grille 136 est formé sur la couche

de câblage de substrat 138 de manière que cette couche d'isolation 122a soit interposée entre eux. Dans ce cas, puisque l'épaisseur de la région d'élément 124 est de 0,6  $\mu\text{m}$ , l'épaisseur de la pellicule d'oxyde pour grille 134 est de 500  $\text{\AA}$  et l'épaisseur de la couche de câblage de substrat 138 est de 0,3  $\mu\text{m}$ , la couche d'isolation 122a possédant une épaisseur de 0,35  $\mu\text{m}$ , ce qui est suffisant, est interposée entre la couche de câblage de substrat 138 et le câblage d'électrode de grille 136.

La couche de câblage de substrat 138 prolonge sur une certaine longueur la face terminale de la région substrat 128 suivant la direction de la largeur de canal, puis s'étend suivant la direction de la longueur de canal afin de prendre une forme globale en L. L'autre extrémité de la couche de câblage de substrat 138 est connectée à une région 150, constituant une borne pour le substrat, qui est formée sur le substrat de saphir 120. Cette structure sera décrite en relation avec la figure 11. La région de borne de substrat 150 comprend une couche de silicium en filot qui est formée sur le substrat de saphir 120 de manière à être solidaire de la région d'élément 124 et de la couche de câblage de substrat 138. Elle a une épaisseur de 0,6  $\mu\text{m}$ , c'est-à-dire la même épaisseur que la région d'élément 124. Cette région de borne de substrat 150 est une région de type  $p^+$  contenant du bore à une concentration de  $10^{19}$  à  $10^{20} \text{ cm}^{-3}$ . La région de borne de substrat 150 est revêtue de la couche d'isolation 122 décrite ci-dessus. Sur la région de borne de substrat 150, sont également formés des câblages en aluminium (non représentés) qui établissent des contacts ohmiques par l'intermédiaire de trous de contact.

Dans le transistor à canal n du dispositif MOS à structure SOS décrit ci-dessus, puisqu'un potentiel constant est appliqué à la région de substrat 128 par l'intermédiaire de la couche de câblage de substrat 138, les problèmes relatifs à l'effet de substrat flottant du transistor MOS à structure SOS ne peuvent pas se produire.

On donne à l'épaisseur de la couche de câblage de substrat 138 une valeur suffisamment inférieure à celle de la région d'élément 124. Ainsi, même si un défaut d'alignement de masquage se

produit pendant la formation du câblage d'électrode de grille 136, reliant ainsi la région source 130 ou la région drain 132 à la couche de câblage du substrat 138, l'augmentation de la capacité de jonction est faible en raison de la petite aire de la jonction.

- 5 De plus, puisque la concentration en impuretés de la couche de câblage de substrat 138 est plus petite que celle de la région source 130 ou de la région drain 132, la capacité de la jonction formée est petite. Par conséquent, puisqu'il n'est pas nécessaire 10 d'élargir la partie terminale 40 de l'électrode de grille 36, au contraire du cas du dispositif MOS à structure SOS classique représenté sur la figure 3, la longueur de canal L peut être constante sur toute la région d'élément 124. En résultat, on peut obtenir 15 les caractéristiques voulues pour l'élément semiconducteur. Puisque l'électrode de grille peut être configurée suivant une forme générale, on peut éviter l'augmentation de la capacité de l'électrode de grille. De plus, on peut également éliminer l'augmentation de l'aire de l'élément qui provient de l'élargissement de l'électrode de grille 36.

Du fait que l'on rend mince la couche de câblage de substrat 138, on peut former la couche d'isolation 122a suffisamment épaisse sur la couche de câblage de substrat 138. Dans ce cas, même si l'on forme le câblage d'électrode de grille 136 de manière qu'il parte de l'électrode de grille du transistor MOS, la capacité d'électrode de grille existant entre la couche de câblage de substrat 138 et le câblage d'électrode de grille 136 est sensiblement négligeable. Par exemple, lorsque l'épaisseur de la couche de câblage de substrat 138 est rendue égale à celle de la région d'élément 124 et que le câblage d'électrode de grille 136 est formé parallèlement à la couche de câblage de substrat 138, l'épaisseur de la couche 25 d'isolation 122a devient égale à 500 Å, ce qui est la même valeur que pour la pellicule d'oxyde pour grille 134. Puisque l'épaisseur de la couche d'isolation 122a est, dans ce mode de réalisation, de 0,35  $\mu$ m (soit 3.500 Å), la capacité de l'électrode de grille 30 vaut 500/3.500 (soit 1/7) fois celle du cas décrit ci-dessus. Ainsi, il devient possible de prolonger le câblage d'électrode de grille 136 sans le faire se terminer à la partie terminale de la région 35

d'élément 124 comme c'était le cas pour le dispositif MOS à structure SOS classique représenté sur la figure 3. Il suffit que l'épaisseur de la couche d'isolation 122a soit telle que la couche de câblage de substrat globale ne puisse être appauvrie et qu'une couche 5 d'inversion ne puisse se former dans la couche de câblage de substrat à l'application d'une tension au câblage d'électrode de grille 136. Ainsi, on peut choisir l'épaisseur de la couche de câblage de substrat 138 et celle de la couche d'isolation 122a en fonction des conditions de fonctionnement de l'élément semiconducteur, en 10 tenant compte des points soulignés ci-dessus.

Dans le mode de réalisation décrit ci-dessus, on rend l'épaisseur de la région de borne de substrat 150 égale à celle de la région d'élément 124 dans le but de former les câblages en aluminium (non représentés) en contact ohmique avec la région de borne 15 de substrat 150 au cours du même processus pour former les câblages en aluminium 146 et 148 respectivement connectés à la région source 130 et à la région drain 132.

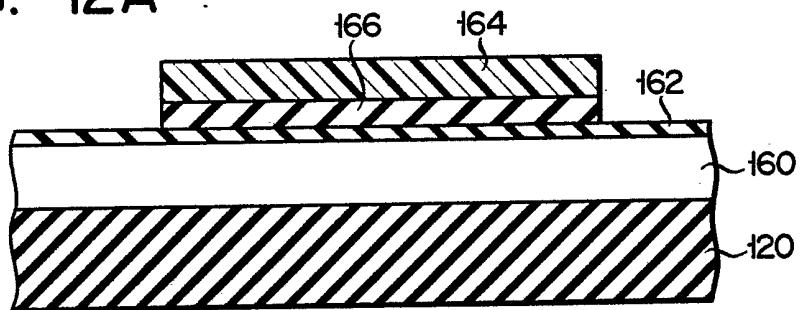

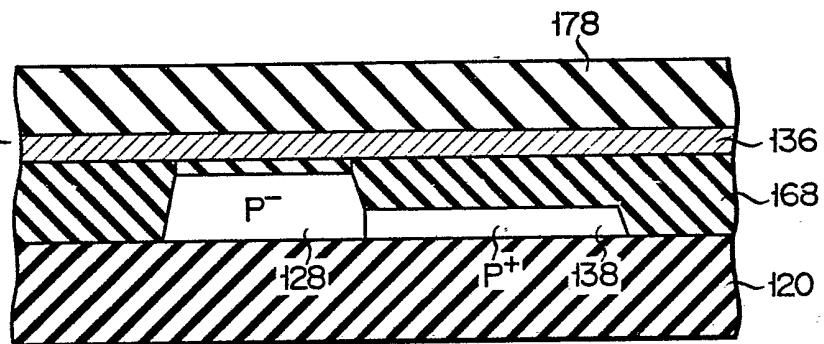

On va maintenant décrire, en relation avec les figures 12A à 12G, le procédé de fabrication du dispositif MOS à structure SOS représenté sur les figures 8 à 11. Comme le montre la figure 12A, on fait croître de manière épitaxiale une couche de silicium 160 sur le substrat de saphir jusqu'à une épaisseur de 0,6  $\mu$ m. On oxyde thermiquement la surface de la couche de silicium 160 pour former une pellicule de  $\text{SiO}_2$  162 d'une épaisseur de 200 Å. Après la 25 formation d'une pellicule de nitrure de silicium sur toute la surface du substrat semiconducteur, on forme sur celle-ci un tracé 164 en vernis photorésistant. On attaque sélectivement la pellicule de nitrure de silicium en utilisant le tracé de vernis photorésistant 164 comme masque afin de former un tracé 166 en nitrure de silicium 30 dans une région où doivent être formées la région d'élément, la couche de câblage de substrat, et la région de borne de substrat.

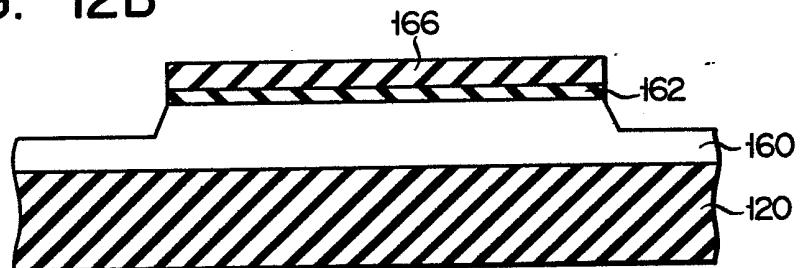

Ensuite, comme le montre la figure 12B, on attaque sélectivement la pellicule 162 de  $\text{SiO}_2$  et la couche 160 de silicium en utilisant comme masque le tracé de vernis photorésistant 164, 35 de manière à rendre l'épaisseur de la partie non masquée de la couche de silicium 160 égale à 0,25  $\mu$ m. Ensuite, on enlève le tracé de vernis photorésistant 164.

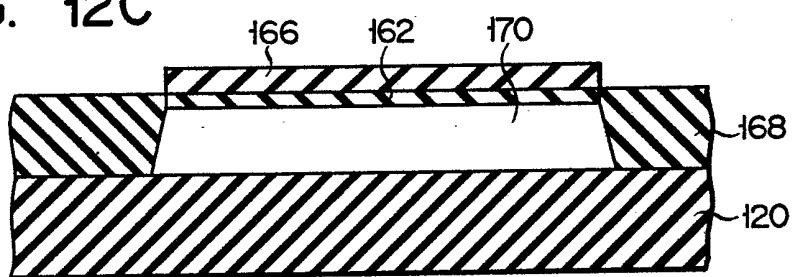

5 Comme le montre la figure 12C, on oxyde ensuite sélectivement le substrat de silicium dans une atmosphère de vapeur d'eau à 900°C en utilisant le tracé de nitrure de silicium 166 comme masque anti-oxydant. Pendant cette opération, on oxyde la partie non masquée de la couche de silicium 160 jusqu'à sa frontière avec le substrat de saphir 120 afin de former une pellicule d'isolation de champ 168 ayant une épaisseur d'environ 0,6  $\mu\text{m}$ . La couche de silicium 160 entourée par cette pellicule d'isolation de champ 168 devient un filot de silicium 170.

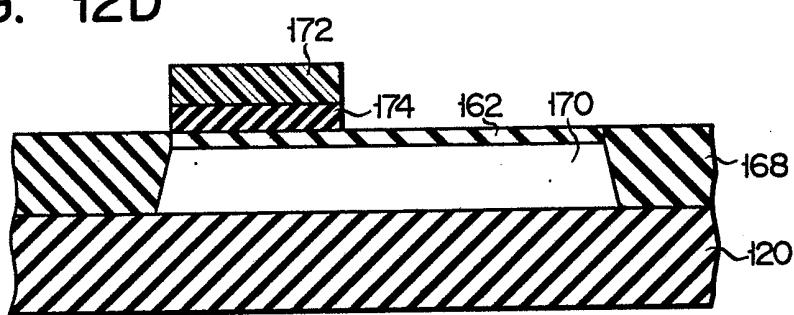

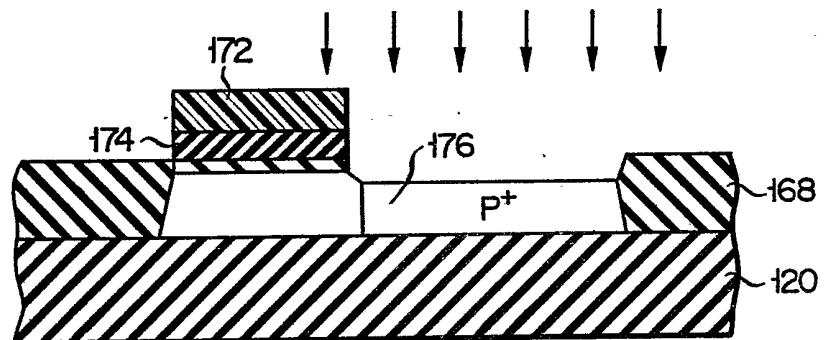

10 15 Comme le montre la figure 12D, on forme ensuite un tracé 172 en vernis photorésistant sur le tracé de nitrure de silicium 166, et on attaque sélectivement le tracé de nitrure de silicium 166 en utilisant le tracé de vernis photorésistant 172 comme masque, afin de former un tracé 174 en nitrure de silicium qui ne subsiste que sur la région d'élément et la région de borne de substrat.

20 25 Ensuite, comme le montre la figure 12E, on attaque sélectivement la pellicule 162 de  $\text{SiO}_2$  et l'filot 170 de silicium en utilisant le tracé de vernis photorésistant 172 comme masque afin de rendre égale à environ 0,45  $\mu\text{m}$  l'épaisseur de la partie non masquée de l'filot de silicium 170 où la couche de câblage de substrat doit être formée. Ensuite, on introduit par implantation ionique des atomes de bore à raison de  $5 \times 10^{12} \text{ cm}^{-2}$  en utilisant le tracé de vernis photorésistant 172 comme masque. A l'aide d'une opération de recuit ultérieure, on active la partie implantée 176 de l'filot de silicium 170 pour lui donner une conductivité de type p<sup>+</sup>.

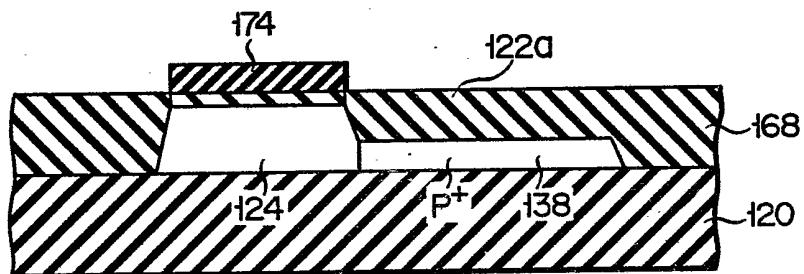

30 35 Comme cela est représenté sur la figure 12F, après avoir retiré le tracé de vernis photorésistant 172, on oxyde sélectivement la partie implantée 176, c'est-à-dire la région 176 de type p<sup>+</sup> de l'filot de silicium 170, dans une atmosphère de vapeur d'eau à 900°C en utilisant le tracé de nitrure de silicium 174 comme masque anti-oxydant. En résultat, on forme la couche de câblage de substrat 138 de 0,3  $\mu\text{m}$  d'épaisseur, et on forme sur la couche de câblage de substrat 138 une pellicule d'isolation de champ 122a en  $\text{SiO}_2$  de 0,35  $\mu\text{m}$  d'épaisseur. La partie de l'filot de silicium qui diffère de la couche de câblage de substrat 138 fournit la région d'élément 124

de  $0,6\text{ }\mu\text{m}$  d'épaisseur et la région de borne de substrat (non représentée) de  $0,6\text{ }\mu\text{m}$  qui est connectée à la couche de câblage de substrat 138.

Enfin, comme le montre la figure 12G, après élimination 5 du tracé de nitrure de silicium 174, on introduit par implantation ionique du bore dans la région d'élément 124 afin de transformer cette région en une région de type  $p^-$  contenant des impuretés à une concentration basse. On introduit également du bore, par implantation ionique, à une concentration élevée dans la région de borne de substrat (non représentée) afin de faire de cette région une région 10 de type  $p^+$ . Ensuite, selon le procédé général, on forme le câblage d'électrode de grille 136 sur la couche de câblage de substrat 138 et sur la partie de la région d'élément 124 où la région de substrat doit être formée. On introduit ensuite de l'arsenic en utilisant 15 le câblage d'électrode de grille 136 comme masque pour former la région source de type  $n^+$  et la région drain de type  $n^+$ . L'aire de la région d'élément 124 qui est masquée par le câblage d'électrode de grille 136 devient la région de substrat 128. Ensuite, on fait déposer une couche 178 d'oxyde de silicium  $\text{SiO}_2$  par une technique 20 de dépôt de vapeur chimique (CVD- $\text{SiO}_2$ ). On forme des trous de contact et on dépose par évaporation sous vide une couche d'aluminium. On configure la couche d'aluminium de manière à former des câblages d'aluminium pour compléter le dispositif MOS à structure SOS.

Lorsque le dispositif MOS à structure SOS se présente 25 de la façon décrite ci-dessus, on peut former la région d'élément 124, la couche de câblage de substrat 138, et la région de borne de substrat par auto-alignement à partir d'un unique filot de silicium. De plus, puisque la pellicule d'isolation de champ 122a est épaisse, il n'est pas nécessaire de former un masque sur la couche d'isolation 30 de champ 122a pour former la région source et la région drain dans la région d'élément 124.

On va maintenant présenter en relation avec la figure 13 un autre mode de réalisation du dispositif MOS à structure SOS de l'invention. Sur le substrat de saphir 120, est formée la région 35 d'élément 124 constituant la région source 130 de type  $n^+$ , la région drain 132 de type  $n^+$  et la région substrat 128 de type  $p^-$  où le

canal doit être formé. La région source 130 est connectée au câblage d'aluminium 146 via le trou de contact 142. La région drain 132 est connectée au câblage d'aluminium 148 via le trou de contact 144. La région substrat 128 est connectée à l'autre couche de câblage de substrat 138 de type  $p^+$  qui est plus mince que la région d'élément 124. La couche de câblage de substrat 138 s'étend dans la direction de la longueur du canal et est contiguë à une surface latérale de la région drain 132 de type  $n^+$ . La couche de câblage de substrat 138 est également contiguë à la région source 130 sur une petite aire. La couche de câblage de substrat 138 est connectée à la région de borne de substrat 150 de type  $p^+$  présentant la même épaisseur que la région d'élément 124. La région de borne de substrat 150 se présente comme séparée de la région drain 132 contenant des impuretés à une concentration élevée, de manière à ne pas être contiguë avec cette région drain 132. Le câblage d'électrode de grille 136 est formé sur la région substrat 128 et la couche de câblage de substrat 138, la couche isolante étant interposée entre elles.

Bien que des jonctions  $p^+ - n^+$  à concentration élevée soient formées aux frontières entre la couche de câblage de substrat 138 et, respectivement, la région source 130 et la région drain 132, les aires de jonction sont petites, puisque l'épaisseur de la couche de câblage de substrat 138 est suffisamment petite. Ainsi, la capacité de jonction est petite et ne pose aucun problème. On peut encore réduire la capacité de jonction en donnant à la concentration en impuretés de la couche de câblage de substrat 138 une valeur plus élevée que celle de la région substrat 128 mais inférieure à celle de la région drain 132 ou de la région source 130.

Alors que le mode de réalisation précédent a été décrit en relation avec un transistor MOS à canal n, l'invention s'appliquerait de façon analogue à un transistor à canal p ou à un condensateur de commutation à dispositif MOS à canal n ou canal p.

De manière analogue, on peut utiliser un substrat isolant qui n'est pas un substrat de saphir. L'invention s'applique également au cas où on forme un élément semiconducteur MOS sur une couche isolante de  $SiO_2$  ou de  $Si_3N_4$ , formée par exemple sur le substrat semiconducteur.

On va maintenant décrire une application réelle du dispositif semiconducteur MOS selon l'invention, en relation avec la figure 14. Un noeud de mémoire Q d'une cellule de mémorisation M comprenant un circuit basculeur est connecté à une ligne D de données numériques par l'intermédiaire d'un transistor T1 de transfert de données. Un noeud de mémoire  $\bar{Q}$  de la cellule de mémorisation M est connecté à une ligne  $\bar{D}$  de données numériques par l'intermédiaire d'un transistor T2 de transfert de données. Les grilles des transistors T1 et T2 de transfert de données sont connectées à une ligne de mots W, et les régions substrat des transistors T1 et T2 de transfert de données sont toutes deux connectées à la terre.

Puisque le potentiel de substrat des transistors T1 et T2 de transfert de données est constant pour cette configuration, il est possible d'empêcher l'effet de substrat flottant des transistors T1 et T2 de transfert de données.

Ceci empêche l'apparition de fluctuations du niveau de sortie des transistors T1 et T2 par hystérésis des transistors T1 et T2. De plus, selon l'invention, on peut réduire au minimum l'augmentation de l'aire de l'élément lors de la formation des électrodes de substrat des transistors T1 et T2. Il est également possible de réduire au minimum l'augmentation du nombre de réseaux de cellules de mémorisation et celle de la capacité de câblage de la ligne de mots W. En mettant au potentiel de la terre le substrat des transistors T1 et T2, on peut empêcher une notable augmentation de la capacité électrostatique de la ligne de données numériques due à l'effet de substrat flottant des transistors T1 et T2 de transfert de données.

Bien entendu, l'homme de l'art sera en mesure d'imaginer, à partir des dispositifs et du procédé dont la description vient d'être donnée à titre simplement illustratif et nullement limitatif, diverses autres variantes et modifications ne sortant pas du cadre de l'invention.

## RE V E N D I C A T I O N S

1. Dispositif semiconducteur du type MOS comprenant une couche isolante (120); et un élément de type MOS consistant en une première couche semiconductrice (124) qui est formée sur ladite 5 couche isolante (120) et qui possède une région substrat (128) d'un premier type de conductivité où un canal doit être formé et une région d'impuretés du type opposé de conductivité, et comportant en outre une électrode (36) formée sur ladite première couche semiconductrice de manière qu'une première pellicule d'isolation (134) soit interposée entre elles, le dispositif étant caractérisé en ce que :

une deuxième couche semiconductrice (138) suffisamment plus mince que ladite première couche semiconductrice (24) est formée sur ladite couche isolante (120);

15 ladite deuxième couche semiconductrice (138) a le même type de conductivité que ladite région substrat (128) et est connectée à au moins ladite région substrat (128) de ladite première couche semiconductrice (124) où ledit canal doit être formé; et un potentiel constant est appliqué à ladite région 20 substrat (128) par l'intermédiaire de ladite deuxième couche semiconductrice (138).

2. Dispositif selon la revendication 1, caractérisé en ce que ladite deuxième couche semiconductrice (138) possède une concentration en impuretés plus élevée que la concentration en impuretés 25 de ladite région substrat (128) de ladite première couche semiconductrice (124) où ledit canal doit être formé, mais inférieure à la concentration en impuretés de ladite région d'impuretés (130, 132) de ladite première couche semiconductrice.

3. Dispositif selon la revendication 1 ou 2, caractérisé 30 en ce qu'une électrode (136) dudit élément de type MOS s'étend au-dessus de ladite deuxième couche semiconductrice (138) de manière qu'une deuxième couche d'isolation (122a) soit interposée entre elles; et

ladite deuxième pellicule d'isolation (122a) présente une épaisseur telle que l'ensemble de la deuxième couche semi-conductrice (138) puisse rester non appauvri ou qu'une couche d'inversion ne puisse pas s'y former suivant la direction d'épaisseur 5 de ladite deuxième couche semiconductrice (138) lorsqu'une tension de fonctionnement est appliquée à ladite électrode (136) dudit élément de type MOS.

4. Dispositif selon la revendication 1, 2 ou 3, caractérisé en ce que la première couche semiconductrice (124) et la deuxième 10 couche semiconductrice (138) sont entourées par un isolant (122) de manière à former un îlot.

5. Dispositif selon l'une quelconque des revendications 1 à 4, caractérisé en ce que la largeur de la partie de la deuxième couche semiconductrice (138) connectée à la première couche semiconductrice 15 (124) est plus grande que la longueur de canal de la région substrat (128) de la première couche semiconductrice (124) où le canal doit être formé.

6. Procédé de fabrication d'un dispositif semiconducteur de type MOS, caractérisé en ce qu'il comprend les opérations 20 suivantes :

former une couche semiconductrice (160) sur une couche isolante (120);

former un premier masque anti-oxydant (166) sur la couche semiconductrice (160);

25 oxyder sélectivement la couche semiconductrice (160) en utilisant ledit premier masque anti-oxydant pour former un îlot de silicium (170);

introduire une impureté de dopage d'un premier type de conductivité dans une partie dudit îlot de silicium (170) qui 30 diffère d'une région de formation d'élément semiconducteur de l'îlot;

former un deuxième masque anti-oxydant (174) sur ladite région formant un élément semiconducteur (124) dudit îlot de silicium (170);

35 oxyder sélectivement ladite partie de l'îlot de silicium (170) en utilisant ledit deuxième masque anti-oxydant (174) afin de rendre ladite partie non masquée suffisamment plus mince que ladite

région de formation d'élément semiconducteur et afin de former simultanément une pellicule d'oxyde épaisse (122a) sur la partie non masquée;

5 introduire une impureté de dopage d'un premier type de conductivité dans ladite région de formation d'élément semi-conducteur (124);

formер un câblage d'électrode de grille (136) sur l'îlot de silicium de manière qu'une pellicule d'oxyde pour grille soit interposée entre eux; et

10 introduire une impureté de dopage de type opposé de conductivité dans ladite région de formation d'élément semiconducteur (124) en utilisant ledit câblage d'électrode de grille comme masque pour former une région source (130), une région drain (132) et une région substrat (128) où un canal doit être formé.

15 7. Procédé selon la revendication 6, caractérisé en ce que la concentration en impuretés du premier type de conductivité introduite dans ladite partie d'îlot de silicium autre que ladite région de formation d'élément semiconducteur est supérieure à la concentration en lesdites impuretés du premier type de conductivité 20 de la région substrat (128) et est inférieure à la concentration en lesdites impuretés de type opposé de conductivité de ladite région source (130) et de ladite région drain (132).

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 12A

FIG. 12B

FIG. 12C

FIG. 12D

FIG. 12E

FIG. 12F

FIG. 12G

F I G. 13

FIG. 14