(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6496401号

(P6496401)

(45) 発行日 平成31年4月3日(2019.4.3)

(24) 登録日 平成31年3月15日(2019.3.15)

(51) Int.Cl.

G06F 21/56 (2013.01)

G06F 9/455 (2006.01)

F 1

G06F 21/56

G06F 9/455 150

請求項の数 21 (全 24 頁)

(21) 出願番号 特願2017-509643 (P2017-509643)

(86) (22) 出願日 平成27年8月11日 (2015.8.11)

(65) 公表番号 特表2017-526071 (P2017-526071A)

(43) 公表日 平成29年9月7日 (2017.9.7)

(86) 國際出願番号 PCT/R02015/050009

(87) 國際公開番号 WO2016/118033

(87) 國際公開日 平成28年7月28日 (2016.7.28)

審査請求日 平成30年2月26日 (2018.2.26)

(31) 優先権主張番号 62/038,476

(32) 優先日 平成26年8月18日 (2014.8.18)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 14/489,820

(32) 優先日 平成26年9月18日 (2014.9.18)

(33) 優先権主張国 米国(US)

(73) 特許権者 312016539

ピットディフェンダー アイピーアール

マネジメント リミテッド

キプロス共和国、ニコシア、クレオントス

、12 シーワイー1076

(74) 代理人 100140109

弁理士 小野 新次郎

(74) 代理人 100118902

弁理士 山本 修

(74) 代理人 100106208

弁理士 富前 勲

(74) 代理人 100120112

弁理士 中西 基晴

(74) 代理人 100196508

弁理士 松尾 淳一

最終頁に続く

(54) 【発明の名称】仮想マシンを終了する際に現在のプロセッサ命令の結果を公開するためのシステムおよび方法

## (57) 【特許請求の範囲】

## 【請求項 1】

仮想マシンとコンピュータセキュリティプログラムとを実行するように構成された少なくとも1つのハードウェアプロセッサを備えたホストシステムであって、前記少なくとも1つのハードウェアプロセッサは、

実行のためのゲスト命令を受け取るのに応答して、前記ゲスト命令の前記仮想マシン内の実行によりメモリアクセス許可の違反が生じるかどうかを判定することであって、前記ゲスト命令は、前記少なくとも1つのハードウェアプロセッサに、オペレータのオペランドへの適用の結果を求めるように命令し、前記ゲスト命令の前記違反のない実行は、前記結果の第1の場所への書き込みを生じさせる、判定することと、

前記ゲスト命令の実行により前記違反が生じるかどうかの判定に応答して、前記ゲスト命令の実行により前記違反が生じる場合に、前記結果を前記第1の場所とは異なる第2の場所に書き込むことであって、前記第2の場所は前記コンピュータセキュリティプログラムからアクセス可能である、書き込むことと、

前記結果の前記第2の場所への書き込みに応答して、前記ゲスト命令の実行から前記コンピュータセキュリティプログラムの実行に切り換えることであって、前記コンピュータセキュリティプログラムは、前記違反がコンピュータセキュリティの脅威を示すかどうかを判定するように構成された、切り換えることと

を行うようにさらに構成された、ホストシステム。

## 【請求項 2】

10

20

請求項 1 に記載のホストシステムであって、前記第 1 の場所は前記少なくとも 1 つのハードウェアプロセッサの汎用レジスタである、ホストシステム。

【請求項 3】

請求項 1 に記載のホストシステムであって、前記第 1 の場所は前記少なくとも 1 つのハードウェアプロセッサの制御レジスタである、ホストシステム。

【請求項 4】

請求項 1 に記載のホストシステムであって、前記第 1 の場所は前記ホストシステムのメモリのセクションを含む、ホストシステム。

【請求項 5】

請求項 1 に記載のホストシステムであって、前記結果はメモリアドレスを含む、ホストシステム。 10

【請求項 6】

請求項 1 に記載のホストシステムであって、前記結果は前記オペランドを含む、ホストシステム。

【請求項 7】

請求項 1 に記載のホストシステムであって、前記コンピュータセキュリティプログラムは前記仮想マシン内で実行される、ホストシステム。

【請求項 8】

請求項 1 に記載のホストシステムであって、前記コンピュータセキュリティプログラムは前記仮想マシン外で実行される、ホストシステム。 20

【請求項 9】

請求項 1 に記載のホストシステムであって、前記第 2 の場所は、前記少なくとも 1 つのハードウェアプロセッサの所定のレジスタを含む、ホストシステム。

【請求項 10】

請求項 1 に記載のホストシステムであって、前記第 2 の場所は、前記ホストシステムのメモリの所定のセクションを含む、ホストシステム。

【請求項 11】

請求項 1 に記載のホストシステムであって、前記第 2 の場所は、前記仮想マシンの現在状態を示すデータ構造を含む、ホストシステム。

【請求項 12】

請求項 1 に記載のホストシステムであって、前記少なくとも 1 つのハードウェアプロセッサは、前記コンピュータセキュリティプログラムの実行に切り換えるのに応答して、前記結果を前記第 2 の場所から読み出すようにさらに構成された、ホストシステム。 30

【請求項 13】

請求項 12 に記載のホストシステムであって、前記少なくとも 1 つのハードウェアプロセッサは、前記結果を読み出すのに応答して、前記結果を、前記ゲスト命令に従って定まる宛先に書き込むようにさらに構成された、ホストシステム。

【請求項 14】

請求項 1 に記載のホストシステムであって、前記コンピュータセキュリティプログラムは、前記少なくとも 1 つのハードウェアプロセッサにより実行されると、前記少なくとも 1 つのハードウェアプロセッサに、前記結果を前記第 2 の場所から読み出し、前記結果を、前記ゲスト命令に従って定まる宛先に書き込むことをさせる命令を含む、ホストシステム。 40

【請求項 15】

請求項 1 に記載のホストシステムであって、前記少なくとも 1 つのハードウェアプロセッサは、前記コンピュータセキュリティプログラムの実行に切り換えるのに応答して、

前記ゲスト命令がアトミック命令であるかどうかを判定し、

それに応答して、前記ゲスト命令がアトミック命令である場合に、前記ゲスト命令を前記仮想マシン内で実行する

ようにさらに構成された、ホストシステム。 50

**【請求項 16】**

ホストシステムをコンピュータセキュリティの脅威から保護する方法であって、

実行のためのゲスト命令を受け取るのに応答して、前記ホストシステムの少なくとも1つのハードウェアプロセッサが、前記ゲスト命令の実行によりメモリアクセス許可の違反が生じるかどうかを判定するステップであって、前記ゲスト命令は、前記ホストシステムによって公開されるゲスト仮想マシン内で実行され、前記ゲスト命令は、前記少なくとも1つのハードウェアプロセッサに、オペレータのオペランドへの適用の結果を求めるように命令し、前記ゲスト命令の前記違反のない実行は、前記結果の第1の場所への書き込みを生じさせる、ステップと、

前記ゲスト命令の実行により前記違反が生じるかどうかの判定に応答して、前記ゲスト命令の実行により前記違反が生じる場合に、前記少なくとも1つのハードウェアプロセッサが、前記結果を前記第1の場所とは異なる第2の場所に書き込むステップであって、前記第2の場所はコンピュータセキュリティプログラムからアクセス可能である、ステップと、

前記結果の前記第2の場所への書き込みに応答して、前記少なくとも1つのハードウェアプロセッサが、前記ゲスト命令の実行から前記コンピュータセキュリティプログラムの実行に切り換えるステップであって、前記コンピュータセキュリティプログラムは、前記違反がコンピュータセキュリティの脅威を示すかどうかを判定するように構成された、ステップと

を含む方法。

10

**【請求項 17】**

請求項16に記載の方法であって、前記コンピュータセキュリティプログラムの実行に切り換えるのに応答して、前記少なくとも1つのハードウェアプロセッサが、前記結果を前記第2の場所から読み出すステップをさらに含む方法。

**【請求項 18】**

請求項17に記載の方法であって、前記結果を読み出すのに応答して、前記少なくとも1つのハードウェアプロセッサが、前記結果を、前記ゲスト命令に従い定まる宛先に書き込むステップをさらに含む方法。

**【請求項 19】**

ホストシステムの少なくとも1つのハードウェアプロセッサであって、

30

実行のためのゲスト命令を受け取るのに応答して、前記ゲスト命令の実行によりメモリアクセス許可の違反が生じるかどうかを判定することであって、前記ゲスト命令は、前記ホストシステムによって公開されるゲスト仮想マシン内で実行され、前記ゲスト命令は、前記ホストシステムによって公開されるゲスト仮想マシン内で実行され、前記ゲスト命令は、前記少なくとも1つのハードウェアプロセッサに、オペレータのオペランドへの適用の結果を求めるように命令し、前記ゲスト命令の前記違反のない実行は、前記結果の第1の場所への書き込みを生じさせる、判定することと

前記ゲスト命令の実行により前記違反が生じるかどうかの判定に応答して、前記ゲスト命令の実行により前記違反が生じる場合に、前記結果を前記第1の場所とは異なる第2の場所に書き込むことであって、前記第2の場所はコンピュータセキュリティプログラムからアクセス可能である、書き込むことと、

40

前記結果の前記第2の場所への書き込みに応答して、前記ゲスト命令の実行からコンピュータセキュリティプログラムの実行に切り換えることであって、前記コンピュータセキュリティプログラムは、前記違反がコンピュータセキュリティの脅威を示すかどうかを判定するように構成された、切り換えることと

を行うように構成された少なくとも1つのハードウェアプロセッサ。

**【請求項 20】**

ホストシステムをコンピュータセキュリティの脅威から保護するためのプログラムであって、前記プログラムは、前記ホストシステムの少なくとも1つのハードウェアプロセッサに、

50

実行のためのゲスト命令を受け取るのに応答して、前記ゲスト命令の実行によりメモリアクセス許可の違反が生じるかどうかを判定することであって、前記ゲスト命令は、前記ホストシステムによって公開されるゲスト仮想マシン内で実行され、前記ゲスト命令は、前記少なくとも1つのハードウェアプロセッサに、オペレータのオペランドへの適用の結果を求めるように命令し、前記ゲスト命令の前記違反のない実行は、前記結果の第1の場所への書き込みを生じさせる、判定することと、

前記ゲスト命令の実行により前記違反が生じるかどうかの判定に応答して、前記ゲスト命令の実行により前記違反が生じる場合に、前記結果を前記第1の場所とは異なる第2の場所に書き込むことであって、前記第2の場所はコンピュータセキュリティプログラムからアクセス可能である、書き込むことと、

前記結果の前記第2の場所への書き込みに応答して、前記ゲスト命令の実行から前記コンピュータセキュリティプログラムの実行に切り換えることであって、前記コンピュータセキュリティプログラムは、前記違反がコンピュータセキュリティの脅威を示すかどうかを判定するように構成された、切り替えることとを行わせる、プログラム。

【請求項21】

請求項20に記載のプログラムを格納したコンピュータ可読記憶媒体。

【発明の詳細な説明】

【技術分野】

【0001】

関連出願

[0001]本出願は、2014年8月18日に出願された、「Systems And Methods for Exposing A Current Processor Instruction Upon Exiting A Virtual Machine (仮想マシンを終了する際に現在のプロセッサ命令を公開するためのシステムおよび方法)」という名称の米国仮特許出願第62/038,476号の出願日の利益を主張するものであり、そのすべての内容は、参照により本明細書に組み込まれている。

【0002】

[0002]本発明はコンピュータセキュリティに関し、詳細にはハードウェア仮想化構成でのコンピュータセキュリティ動作の実施に関する。

【背景技術】

【0003】

[0003]マルウェアとしても知られている悪意のあるソフトウェアは、世界中で非常に多くのコンピュータシステムに影響を及ぼしている。マルウェアは、コンピュータウイルス、ワーム、ルートキットおよびスパイウェアなどの多くの形態で何百万ものコンピュータユーザを重大な危険にさらし、したがってコンピュータユーザは、とりわけ、データおよび機密情報の損失、個人情報の盗難、および生産性の損失の攻撃にさらされている。

【0004】

[0004]現代の計算アプリケーションは、しばしばハードウェア仮想化技術を使用して、仮想マシン(VM)として知られている、物理コンピュータシステムと同じように様々な方式で振る舞う模擬的なコンピュータ環境を生成している。サーバ統合およびサービスとしてのインフラストラクチャ(Infrastructure-as-a-service)などの用途では、いくつかの仮想マシンが同じコンピュータシステム上で同時に走り、それらの間でハードウェア資源を共有することができ、したがって投下資本および運転コストを低減することができる。個々の仮想マシンは、その独自のオペレーティングシステムおよび/またはソフトウェアを他の仮想マシンとは別に走らせることができる。マルウェアおよびスパイウェアなどのコンピュータセキュリティの脅威の止まることのない拡散のため、個々のこののような仮想マシンは保護を必要とする可能性がある。

【0005】

[0005]いくつかのセキュリティ解決法は、保護されたVM内で実行されているゲストブ

10

20

30

40

50

ロセスがメモリにアクセスする方式を監視して、潜在的な悪意のあるアクティビティを識別することによって仮想マシンを保護している。一例では、コンピュータセキュリティプログラムは、メモリの特定の領域、例えばゲストプロセスによって使用されるメモリの領域への書き込みが試行され、またはその領域からのコードの実行が試行される際に、内部イベント（例えば例外イベントまたはVM終了イベント）を生成するためのプロセッサを構成することができる。このようなプロセッサイベントは、典型的には、現在のスレッドの実行を中断し、また、プロセッサを、コンピュータセキュリティプログラムの一部を形成することができるイベントハンドラルーチンの実行に切り換える。コンピュータセキュリティプログラムは、そのようにして、マルウェアであることが疑われる方式によるメモリアクセスの試行を検出することができる。イベントを分析した後、コンピュータセキュリティプログラムは、イベントが生じた時点で実行されていたプロセッサ命令をエミュレートすることができ、また、実行を元のスレッドに戻すことができる。このような方法は、当分野ではトラップアンドエミュレートとして総称的に知られている。10

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0006】

[0006]従来のトラップアンドエミュレート方法は、相当な計算負荷をホストコンピュータシステムに課すことがあり、潜在的にユーザ体験および生産性に影響を及ぼす可能性がある。したがって仮想化環境に適した有効なコンピュータセキュリティシステムおよび方法を開発することは大いなる関心事である。20

#### 【課題を解決するための手段】

#### 【0007】

[0007]一態様によれば、ホストシステムは、仮想マシンおよびコンピュータセキュリティプログラムを実行するように構成された少なくとも1つのハードウェアプロセッサを備える。少なくとも1つのハードウェアプロセッサは、実行のためのゲスト命令を受け取るのに応答して、ゲスト命令の仮想マシン内の実行によりメモリアクセス許可の違反が生じるかどうかを判定するようにさらに構成される。少なくとも1つのハードウェアプロセッサは、ゲスト命令の実行により違反が生じるかどうかの判定に応答して、ゲスト命令の実行により違反が生じる場合に、ゲスト命令のオペレータをゲスト命令のオペランドへの適用の結果を求め、その結果を、コンピュータセキュリティプログラムからアクセス可能な所定の場所に書き込み、ゲスト命令の実行を中断するようにさらに構成される。少なくとも1つのハードウェアプロセッサは、ゲスト命令の実行の中止に応答して、コンピュータセキュリティプログラムの実行に切り換えるようにさらに構成され、コンピュータセキュリティプログラムは、違反がコンピュータセキュリティの脅威を示すかどうかを判定するように構成される。30

#### 【0008】

[0008]別の態様によれば、ホストシステムをコンピュータセキュリティの脅威から保護する方法であって、実行のためのゲスト命令を受け取るのに応答して、ゲスト命令を実行することによりメモリアクセス許可の違反が生じるかどうかを、ホストシステムの少なくとも1つのハードウェアプロセッサを使用して判定するステップを含み、ゲスト命令は、ホストシステムによって公開される仮想マシン内で実行される。方法は、ゲスト命令が違反を生じさせるかどうかの決定に応答して、ゲスト命令を実行することにより違反が生じる場合に、少なくとも1つのハードウェアプロセッサを使用して、ゲスト命令のオペレータのゲスト命令のオペランドへの適用の結果を求めるステップと、少なくとも1つのハードウェアプロセッサを使用して、その結果を、コンピュータセキュリティプログラムからアクセス可能な所定の場所に書き込むステップと、ゲスト命令の実行を中断するステップとをさらに含む。方法は、ゲスト命令の実行の中止に応答して、コンピュータセキュリティプログラムの実行に切り換えるステップをさらに含み、コンピュータセキュリティプログラムは、違反がコンピュータセキュリティの脅威を示すかどうかを判定するように構成される。40

## 【0009】

[0009] 別の態様によれば、ホストシステムの少なくとも1つのハードウェアプロセッサは、実行のためのゲスト命令を受け取るのに応答して、ゲスト命令を実行することによりメモリアクセス許可の違反が生じるかどうかを決定するように構成することができ、ゲスト命令は、ホストシステムによって公開されるゲスト仮想マシン内で実行される。少なくとも1つのハードウェアプロセッサは、ゲスト命令が違反を生じさせるかどうかの判定に応答して、ゲスト命令を実行することにより違反が生じる場合に、ゲスト命令のオペレータのゲスト命令のオペランドへの適用の結果を求め、その結果を、コンピュータセキュリティプログラムからアクセス可能な所定の場所に書き込み、ゲスト命令の実行を中断するようにさらに構成することができる。少なくとも1つのハードウェアプロセッサは、ゲスト命令の実行の中断に応答して、コンピュータセキュリティプログラムの実行に切り換えるようにさらに構成することができ、コンピュータセキュリティプログラムは、違反がコンピュータセキュリティの脅威を示すかどうかを判定するように構成される。

10

## 【0010】

[0010] 別の態様によれば、非一時的コンピュータ可読媒体は、ホストシステムの少なくとも1つのハードウェアプロセッサによって実行されると、ホストシステムに、メモリアクセス許可の違反がコンピュータセキュリティの脅威を示すかどうかを判定するように構成されたコンピュータセキュリティプログラムを形成させる命令を記憶する。少なくとも1つのハードウェアプロセッサは、実行のためのゲスト命令を受け取るのに応答して、ゲスト命令を実行することにより違反が生じるかどうかを判定するように構成することができ、ゲスト命令は、ホストシステムによって公開される仮想マシン内で実行される。少なくとも1つのハードウェアプロセッサは、ゲスト命令が違反を生じさせるかどうかの判定に応答して、ゲスト命令を実行することにより違反が生じる場合に、ゲスト命令のオペレータのゲスト命令のオペランドへの適用の結果を求め、その結果を、コンピュータセキュリティプログラムからアクセス可能な所定の場所に書き込み、ゲスト命令の実行を中断するようにさらに構成することができる。少なくとも1つのハードウェアプロセッサは、ゲスト命令の実行の中断に応答して、コンピュータセキュリティプログラムの実行に切り換えるようにさらに構成することができる。

20

## 【0011】

[0011] 本発明の上記態様および利点は、以下の詳細な説明を読み、また、図面を参照することにより、より良好に理解されるであろう。

30

## 【図面の簡単な説明】

## 【0012】

【図1】 [0012] 本発明のいくつかの実施形態によるホストコンピュータシステムの例示的ハードウェア構成を示す図である。

【図2 - A】 [0013] 本発明のいくつかの実施形態による、ホストシステム上で実行するハイパーバイザによって公開される仮想マシンの例示的セット、および仮想マシンのセットを保護するコンピュータセキュリティモジュール（CSM）を示す図である。

【図2 - B】 [0014] CSMが仮想マシンの下で実行され、また、例外ハンドラが保護された仮想マシン内で実行される、本発明の代替実施形態を示す図である。

40

【図2 - C】 [0015] CSMおよび例外ハンドラの両方が保護された仮想マシン内で実行する、本発明のさらに別の実施形態を示す図である。

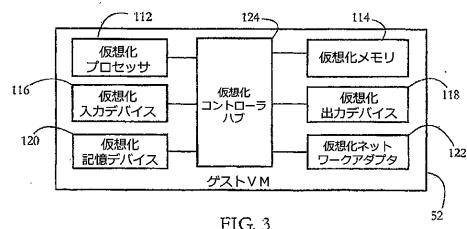

【図3】 [0016] 本発明のいくつかの実施形態による、ゲスト仮想マシンとして公開された仮想化ハードウェアの例示的構成を示す図である。

【図4】 [0017] 本発明のいくつかの実施形態による、図2 - Aに示されるハードウェア仮想化構成における一組の例示的メモリアドレス変換を示す図である。

【図5】 [0018] 本発明のいくつかの実施形態によるプロセッサの例示的構成要素を示す図である。

【図6】 [0019] 本発明のいくつかの実施形態によるプロセッサの例示的中断イベントレジスタを示す図である。

50

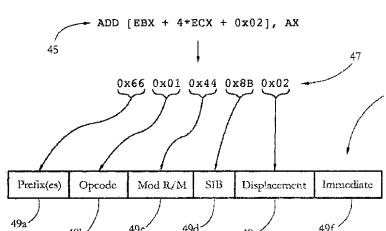

【図7】[0020] × 8 6 命令セットの例示的プロセッサ命令のアセンブリ言語表現、およびその対応するマシンコード表現を示す図である。

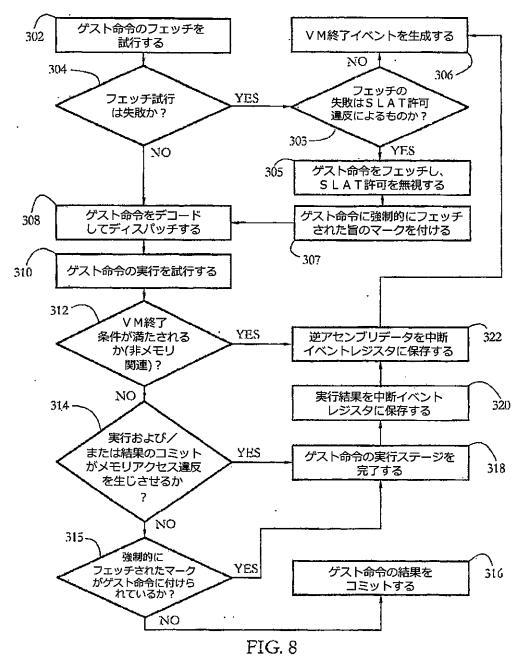

【図8】[0021]本発明のいくつかの実施形態による、プロセッサ命令を実行するためにプロセッサによって実施されるステップの例示的シーケンスを示す図である。

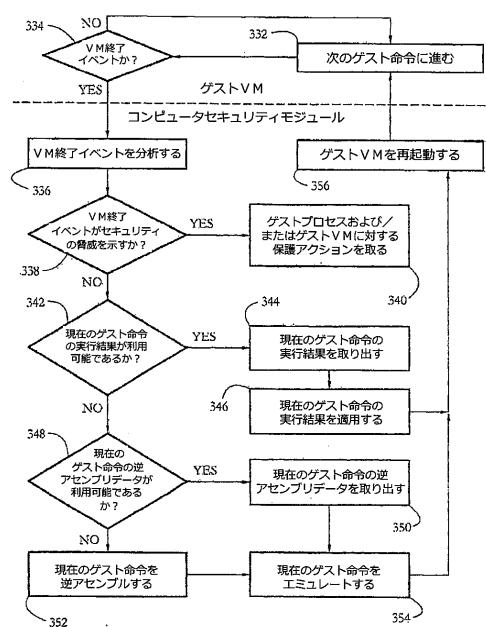

【図9】[0022]本発明のいくつかの実施形態による、ゲスト仮想マシンを保護するためにコンピュータセキュリティモジュールによって実施されるステップの例示的シーケンスを示す図である。

【発明を実施するための形態】

【0013】

[0023]以下の説明では、構造間の詳説されているすべての接続は、直接の動作接続であっても、あるいは中間構造を介した間接的な動作接続であってもよいことを理解されたい。一組の要素は、1つまたは複数の要素を含む。要素の詳説は、すべて、少なくとも1つの要素を意味することを理解されたい。複数の要素は、少なくとも2つの要素を含む。特に要求されない限り、説明されているすべての方法ステップは、必ずしも示されている特定の順序で実施される必要はない。第2の要素から導出される第1の要素（例えばデータ）は、第2の要素に等しい第1の要素、ならびに第2の要素を処理することによって生成される第1の要素、および任意選択で他のデータを包含する。パラメータに従って決定する（making a determine or a decision；判定する、求める）ことは、パラメータに従って、また、任意選択で他のデータに従って決定することを包含する。特に明記されていない限り、何らかの量/データのインジケータは、その量/データ自体であっても、あるいはその量/データ自体とは異なるインジケータであってもよい。コンピュータプログラムは、タスクを実行する一連のプロセッサ命令である。本発明のいくつかの実施形態で説明されるコンピュータプログラムは、他のコンピュータプログラムの独立型ソフトウェアエンティティまたはサブエンティティ（例えばサブルーチン、ライブラリ）であってもよい。特に明記されていない限り、コンピュータセキュリティプログラムは、意図されないまたは許可されていないアクセス、修正または破壊から機器およびデータを保護するコンピュータプログラムである。特に明記されていない限り、プロセスは、アプリケーションまたはオペレーティングシステムの一部などのコンピュータプログラムのインスタンスであり、また、少なくとも実行スレッドおよび実行スレッドに割り当てられた仮想メモリ空間を有することを特徴とし、それぞれの仮想メモリ空間の内容は実行可能コードを含む。特に明記されていない限り、ページは、ホストシステムの物理メモリに個々にマッピングされ得る仮想メモリの最小単位を表している。「論理」という用語は、固定された機能または再構成可能な機能（例えばフィールドプログラマブルゲートアレイ回路）を有するハードウェア回路機構を包含するが、このような機能を汎用コンピュータ上でエミュレートするソフトウェアは包含しない。特に明記されていない限り、レジスタは、プロセッサと一体化された、すなわちプロセッサの一部を形成している記憶構成要素を表しており、また、ランダムアクセスメモリ（RAM）とは全く異なる。コンピュータ可読媒体は、磁気記憶媒体、光記憶媒体および半導体記憶媒体などの非一時的媒体（例えばハードドライブ、光ディスク、フラッシュメモリ、DRAM）、ならびに導電ケーブルなどの通信リンクおよび光ファイバリンクを包含している。いくつかの実施形態によれば、本発明は、とりわけ、本明細書において説明される方法を実施するようにプログラムされたハードウェア（例えば1つまたは複数のプロセッサ）、ならびに本明細書において説明される方法を実施するための命令をエンコードするコンピュータ可読媒体を備えるコンピュータシステムを提供する。

【0014】

[0024]以下の説明は、一例として本発明の実施形態を示したものであり、必ずしも制限するためのものではない。

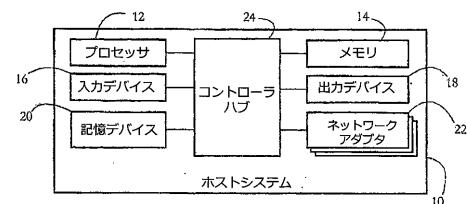

[0025]図1は、本発明のいくつかの実施形態によるホストシステム10の例示的ハードウェア構成を示したものである。ホストシステム10は、企業サーバなどの法人組織の計算デバイス、またはパーソナルコンピュータ、タブレットコンピュータもしくはスマート

10

20

30

40

50

フォンなどのエンドユーザデバイスを表すことができる。他の例示的ホストシステムは、T V、ゲームコンソール、着用可能計算デバイス、またはメモリおよびプロセッサを有する任意の他の電子デバイスを含む。ホストシステム10を使用して、とりわけ、ブラウザ、文書処理アプリケーションおよび電子通信（例えば電子メール、インスタントメッセージング）アプリケーションなどの一組のソフトウェアアプリケーションが実行され得る。いくつかの実施形態では、ホストシステム10は、ハードウェアの仮想化を支援し、また、以下で示されるように一組の仮想マシンを公開するように構成される。

#### 【0015】

[0026]図1は、コンピュータシステムを示したもので、スマートフォンおよびタブレットコンピュータなどの他のホストシステムのハードウェア構成は異なる場合がある。システム10は、プロセッサ12、メモリユニット14、一組の入力デバイス16、一組の出力デバイス18、一組の記憶デバイス20、および一組のネットワークアダプタ22を含む一組の物理デバイスを備えており、すべてがコントローラハブ24によって接続されている。いくつかの実施形態では、プロセッサ12は、一組の信号および/またはデータを使用して計算および/または論理演算を実行するように構成された物理デバイス（例えば半導体基板の上に形成されたマルチコア集積回路）を備えている。いくつかの実施形態では、このような論理演算は、一連のプロセッサ命令（例えばマシンコードまたは他のタイプのソフトウェア）の形態でプロセッサ12に引き渡される。本発明のいくつかの実施形態は、従来のプロセッサの構造および機能に変更を導入し、それぞれの変更により、ハードウェア仮想化構成におけるプロセッサ12のより有効な動作が可能になる。

#### 【0016】

[0027]メモリユニット14は、命令を実行する過程でプロセッサ12によってアクセスまたは生成されるデータ/信号を記憶する揮発性コンピュータ可読媒体（例えばRAM）を備えることができる。入力デバイス16は、とりわけ、コンピュータキーボード、マウスおよびマイクロホンを含むことができ、これらは、ホストシステム10へのデータおよび/または命令のユーザによる導入を可能にするそれぞれのハードウェアインターフェースおよび/またはアダプタを含む。出力デバイス18は、とりわけ、モニタなどの表示デバイスおよびスピーカを含むことができ、また、ホストシステム10によるユーザへのデータ通信を可能にする、グラフィックカードなどのハードウェアインターフェース/アダプタを含むことができる。いくつかの実施形態では、入力デバイス16および出力デバイス18は、タッチスクリーンデバイスの場合と同様、1つの共通のハードウェアを共有することができる。記憶デバイス20は、不揮発性記憶装置によるプロセッサ命令および/またはデータの読み出しおよび書き込みを可能にするコンピュータ可読媒体を含む。例示的記憶デバイス20は、磁気ディスク、光ディスクおよびフラッシュメモリデバイス、ならびにCDおよび/またはDVDディスクおよびドライブなどの取外し可能媒体を含む。一組のネットワークアダプタ22は、コンピュータネットワークおよび/または他のデバイス/コンピュータシステムへのホストシステム10の接続を可能にしている。コントローラハブ24は、複数のシステム、周辺装置および/もしくはチップセットバス、ならびに/またはプロセッサ12とデバイス14、16、18、20、および22との間の通信を可能にするあらゆる他の回路機構を総称的に表している。例えばコントローラハブ24は、とりわけ、メモリ管理ユニット（MMU）、入力/出力（I/O）コントローラ、および割込みコントローラを含むことができる。別の例では、コントローラハブ24は、プロセッサ12をメモリ14に接続するノースブリッジ、ならびに/またはプロセッサ12をデバイス16、18、20、および22に接続するサウスブリッジを備えることができる。いくつかの実施形態では、コントローラハブ（MMUなどの）の部分はプロセッサ12と統合されることができ、すなわち共通基板をプロセッサ12と共有することができる。

#### 【0017】

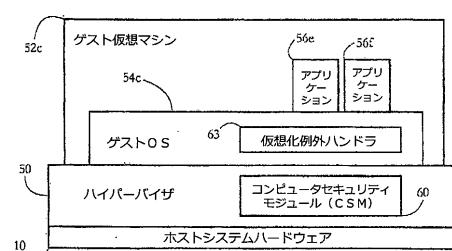

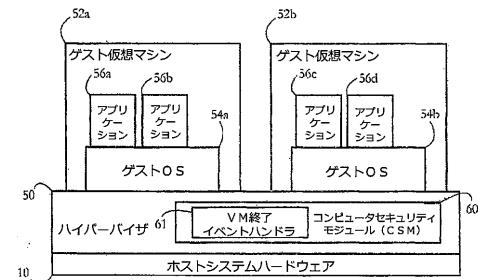

[0028]図2-Aは、本発明のいくつかの実施形態による例示的機能構成を示したもので、ホストシステム10は、ハードウェア仮想化技術を使用して、ハイパーバイザ50によって公開される一組のゲスト仮想マシン52a～bを動作させる。このような構成は、と

10

20

30

40

50

りわけ、クラウドコンピューティングおよびサーバ統合などの用途で一般的である。仮想マシン（VM）は、当分野では、実際の物理マシン／コンピュータシステムの抽象化、例えばソフトウェアエミュレーションとして知られており、VMは、オペレーティングシステムおよび他のソフトウェアを走らせることができる。いくつかの実施形態では、ハイパーバイザ50は、仮想プロセッサおよび仮想コントローラハブなどの複数の仮想化デバイスを生成または可能にするように構成され、また、ホストシステム10の現実の物理デバイスの代わりにこのような仮想化デバイスをソフトウェアに提供するように構成されたソフトウェアを含む。ハイパーバイザ50のこのような動作は、当分野では、仮想マシンの公開として広く知られている。いくつかの実施形態では、ハイパーバイザ50は、複数の仮想マシンによるホストシステム10のハードウェア資源の多重化（共有）を可能にする。ハイパーバイザ50は、さらに、個々のゲストVM52a～bが独立して動作し、また、ホストシステム10上で同時に実行している他のVM実行を認識しないように、このような多重化を管理することができる。一般的なハイパーバイザの例は、とりわけ、VMware社のVMware vSphere（商標）、およびオープンソースのXenハイパーバイザを含む。

10

#### 【0018】

[0029]個々のVM52a～bは、それぞれゲストオペレーティングシステム（OS）54a～bを実行することができる。一組の例示的アプリケーション56a～dは、とりわけ、文書処理、画像処理、メディアプレーヤ、データベース、カレンダ、個人連絡先管理、ブラウザ、ゲーミング、音声通信、データ通信、およびマルウェア防止アプリケーションなどの任意のソフトウェアアプリケーションを総称的に表している。オペレーティングシステム54a～bは、とりわけ、Microsoft Windows（登録商標）、Mac OS（登録商標）、Linux（登録商標）、iOS（登録商標）、またはAndroid（商標）などの広く利用可能な任意のオペレーティングシステムを含むことができる。個々のOS54a～bは、それぞれのVMおよびそれぞれのVMの仮想化ハードウェアデバイス内で実行するアプリケーション間のインターフェースを提供する。以下の説明では、仮想マシンの仮想プロセッサ上で実行するソフトウェアは、それぞれの仮想マシン内で実行する、と言われる。例えば図2-Aの例では、アプリケーション56a～bはゲストVM52a内で実行する、と言われ、一方、アプリケーション56c～dはゲストVM52b内で実行する、と言われる。それとは対照的に、ハイパーバイザ50はゲストVM52a～bの外部、すなわち下で実行する、と言われる。

20

30

#### 【0019】

[0030]図3は、ハイパーバイザ50によって公開される仮想マシン52の例示的構成を示したものである。VM52は、図2-Aの任意のVM52a～bを表すことができる。VM52は、仮想化プロセッサ112、仮想化メモリユニット114、仮想化入力デバイス116、仮想化出力デバイス118、仮想化記憶装置120、仮想化ネットワークアダプタ122、および仮想化コントローラハブ124を含む。仮想化プロセッサ112は、プロセッサ12の機能のうちの少なくともいくつかのエミュレーションを含み、また、オペレーティングシステムおよび他のアプリケーションなどのソフトウェアの一部を形成するプロセッサ命令を受け取って実行するように構成される。プロセッサ112を使用して実行するソフトウェアは、仮想マシン52内で実行すると見なされる。いくつかの実施形態では、仮想化メモリユニット114は、仮想化プロセッサ112によって使用されるデータを記憶し、かつ、取り出すためのアドレス指定可能空間を備えている。他の仮想化デバイス（例えば仮想化入力、出力、記憶装置、等々）は、ホストシステム10のそれぞれの物理デバイスの機能の少なくともいくつかをエミュレートする。仮想化プロセッサ112は、あたかも対応する物理デバイスと対話するかのように、このような仮想化デバイスと対話するように構成され得る。例えばVM52内で実行するソフトウェアは、仮想化ネットワークアダプタ122を介してネットワークトライフィックを送信および／または受信することができる。いくつかの実施形態では、ハイパーバイザ50は、仮想化デバイスのサブセットのみ（例えば仮想化プロセッサ112、仮想化メモリ114、およびハ

40

50

ブ 1 2 4 の部分のみ) を V M 5 2 に公開することができる。また、ハイパーバイザ 5 0 は、選択された V M に、ホストシステム 1 0 のいくつかのハードウェアデバイスの排他的な使用を与えることも可能である。1 つのそのような例では、V M 5 2 a ( 図 2 - A ) は、入力デバイス 1 6 および出力デバイス 1 8 の排他的な使用を有することができるが、仮想化ネットワークアダプタは持たない。一方、V M 5 2 b は、ネットワークアダプタ 2 2 の排他的な使用を有することができる。このような構成は、例えば I n t e l ( 登録商標 ) の V T - d ( 登録商標 ) 技術を使用して実現され得る。

#### 【 0 0 2 0 】

[0031] 現代のプロセッサは、当分野では保護リングとしても知られている、プロセッサ特権レベルの階層を実現している。個々のこのようなリングすなわちレベルは、それぞれのリング内で実行するソフトウェアがその実行を許可される一組のアクションおよび / またはプロセッサ命令を特徴とする。例示的な特権レベル / リングは、ユーザモード ( リング 3 ) およびカーネルモード ( リング 0 ) を含む。ハードウェアの仮想化を支援するように構成されるいくつかのホストシステムは、プロセッサ特権が最も高い追加リングを含むことができる ( 例えばリング - 1 、ルートモードまたは I n t e l ( 登録商標 ) プラットフォーム上の V M X r o o t ) 。いくつかの実施形態では、ハイパーバイザ 5 0 は、最も特権の高いレベル ( リング - 1 ) でプロセッサ 1 2 の制御を獲得し、したがってホストシステム 1 0 上で実行する他のソフトウェアに仮想マシンとして公開されるハードウェア仮想化プラットフォームを生成する。図 2 - A のゲスト O S 5 4 a などのオペレーティングシステムは、典型的にはプロセッサ特権がハイパーバイザ 5 0 より劣るそれぞれの V M の仮想環境内 ( 例えばリング 0 すなわちカーネルモード ) で実行する。5 6 a ~ b などの共通ユーザアプリケーションは、典型的には、O S 3 4 a より劣るプロセッサ特権で ( 例えばリング 3 すなわちユーザモードで ) 実行する。アプリケーション 5 6 a ~ b のいくつかの部分は、カーネル特権レベルで実行することができ、一方、O S 3 4 a のいくつかの部分は、ユーザモード ( リング 3 ) で実行することができる。ソフトウェアオブジェクトが、その割り当てられた保護リングによって許容される特権より高いプロセッサ特権を必要とするアクションまたは命令の実行を試行する場合、その試行は、典型的には、それぞれのアクションを実行するのに十分な特権を有するリング内で実行するエンティティ ( 例えばハンドラルーチン ) へプロセッサ 1 2 の制御を移行する、例外または障害などのプロセッサイベントを生成する。

#### 【 0 0 2 1 】

[0032] 詳細には、ゲスト V M の中から特定のアクションを実施する試行、または特定の命令を実行する試行は、本明細書において総称的に V M 中断イベントと呼ばれる特定のカテゴリのプロセッサイベントをトリガすることができる。いくつかの実施形態では、V M 中断イベントは、ゲスト V M 内の現在のスレッドの実行を中断し、かつ、プロセッサ 1 2 をハンドラルーチンの実行に切り換える。例示的 V M 中断イベントは、とりわけ、V M 終了イベント ( 例えば I n t e l ( 登録商標 ) プラットフォーム上の V M E x i t ) および仮想化例外 ( 例えば I n t e l ( 登録商標 ) プラットフォーム上の # V E ) を含む。V M 終了イベントは、プロセッサ 1 2 を、典型的にはハイパーバイザ 5 0 のレベルであるそれぞれのゲスト V M の外部のハンドラルーチンの実行に切り換える。仮想化例外は、それぞれの V M を終了する代わりに、プロセッサ 1 2 をそれぞれのゲスト V M 内のハンドラルーチンの実行に切り換えることができる。

#### 【 0 0 2 2 】

[0033] V M 中断イベントをトリガする例示的命令は、I n t e l ( 登録商標 ) プラットフォームの V M C A L L を含む。また、V M 中断イベントは、メモリアクセス違反などの他のイベントによってもトリガされ得る。1 つのそのような例では、V M 内で実行しているソフトウェアオブジェクトが、非書き込み可能とマークされたメモリのセクションへの書き込みを試行するか、または非実行可能とマークされたメモリのセクションからのコードの実行を試行すると、プロセッサ 1 2 は、V M 終了イベントを生成することができる。このような V M 切換え機構は、例えばコンピュータセキュリティプログラムによる、それぞれ

10

20

30

40

50

のVMの外部からの仮想マシンの保護を可能にする。コンピュータセキュリティプログラムは、VM内で走っているソフトウェアによって実施される、セキュリティの脅威を示し得る特定のアクションに応答して、生じているVM終了イベントを傍受することができる。コンピュータセキュリティプログラムは、次に、このようなアクションを阻止し、および／または、可能性としてはVM内ソフトウェアの知識を必要とすることなく、このようなアクションをさらに分析することができる。このような構成は、コンピュータセキュリティを実質的に強化することができる。

#### 【0023】

[0034]いくつかの実施形態（例えば図2-A）では、ハイパーバイザ50は、とりわけ、このようなコンピュータセキュリティ動作を実施するように構成されたコンピュータセキュリティモジュール（CSM）60を含む。モジュール60は、ハイパーバイザ50に組み込まれ得るか（例えばライブラリとして）、またはハイパーバイザ50とは異なりハイパーバイザ50から独立しているが、ハイパーバイザ50の特権レベルで実行するコンピュータプログラムとして引き渡され得る。単一のモジュール60が、ホストシステム10上で実行する複数のゲストVMを保護するように構成され得る。モジュール60によって実行されるセキュリティ動作は、ゲストVM内で実行するプロセスによって実施されるアクション（例えばOSの特定の機能の呼出し、OSのレジストリのアクセス、遠隔の場所からのファイルのダウンロード、ファイルへのデータの書き込み、等々）の検出を含むことができる。モジュール60の他のセキュリティ動作は、ゲストVM内で実行するソフトウェアオブジェクトの一部を含むメモリセクションのアドレスの決定、それぞれのメモリセクションへのアクセス、およびそれぞれのメモリセクションに記憶されている内容の分析を含むことができる。セキュリティ動作の他の例は、このようなメモリセクションへのアクセスの傍受および／または制限、例えば保護されたプロセスに属するコードまたはデータの重ね書きの防止、および特定のメモリページに記憶されているコードの実行の防止を含む。いくつかの実施形態では、CSM60は、ゲストVM52a～b内で生じるVM終了イベントを傍受するように構成されたVM終了イベントハンドラ61を含む。代替実施形態では、ハンドラ61は、VM終了イベントを傍受し、かつ、生じた個々のVM終了の理由および／またはタイプを決定した後に、制御をCSM60に選択的に移行する、CSM60とは別のハイパーバイザ50の全く異なるモジュール（例えばライブラリ）であってもよい。

10

20

30

#### 【0024】

[0035]図2-Bは、コンピュータセキュリティモジュール60がそれぞれのVMの外部からゲストVM52cを保護する代替実施形態を示したものである。このような実施形態では、プロセッサ12は、メモリアクセス違反が生じると仮想化例外を生成するように構成され得る（図2-Aに関連して上で説明したVM終了イベントの代わりに）。図2-Bの例示的実施形態では、仮想化例外ハンドラ63は、VM52c内で、例えばオペレーティングシステム54cの特権レベルで実行し、また、仮想化例外を傍受し、CSM60とインタフェースするように構成される。

#### 【0025】

[0036]ハンドラ63とCSM60の間の通信は、当分野で知られている任意のプロセス間通信方法に従って進行することができる。データを保護されたVM内からハイパーバイザ50のレベルへ传送するために、ハンドラ63のいくつかの実施形態は、専用の命令（例えばIntel（登録商標）プラットフォームのVMCALL）を使用して、プロセッサ12の制御をそれぞれのVMからハイパーバイザ50へ移行する。传送されるデータは、例外ハンドラ63によって、CSM60と共有されるメモリの所定のセクションに置かれ得る。データをハンドラ63に传送するために、CSM60のいくつかの実施形態は、ハンドラ63によって処理される割込みをVM52cにかけることができる。それぞれのデータは、上で説明した共有メモリセクションを介して再度传送され得る。

40

#### 【0026】

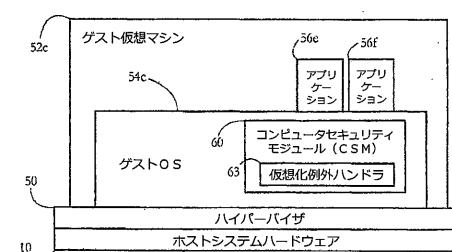

[0037]図2-Cに示されているさらに別の実施形態では、CSM60およびハンドラ6

50

3の両方が、保護されたVM内で、例えばカーネルモード（リング0）で実行する。このような実施形態は、仮想化例外を使用してメモリアクセス違反を検出することも可能である。構成2-A-B-C間の決定は、性能とセキュリティの間のトレードオフを評価することを含み得る。VM終了イベントは、計算の点で比較的コストがかかり、典型的には、個々の終了および再開始サイクルでのメモリへの/メモリからの大型データ構造のロードおよび/またはアンロードが必要である。したがって2-Aなどの構成は、2-B-Cなどの構成よりも、イベントを傍受するためにより多くの計算を必要とし得る。一方、CSM60およびハンドラ61～63などの重要なセキュリティ構成要素を保護されたVMの外部に維持することは（例2-A-Bの場合のように）、それぞれのVM内で実行するマルウェアがこのような構成要素の動作を妨害することはより困難であり得るため、セキュリティを強化し得る。

10

#### 【0027】

[0038]図2-A-Bに示されている構成で（すなわちそれぞれのVMの外部から）ゲストVMを保護することができるようにするために、CSM60のいくつかの実施形態は、プロセッサ12のアドレス変換データ構造および/またはアドレス変換機構を使用する。仮想マシンは、典型的には、当分野でゲスト物理メモリとして知られている仮想化物理メモリを使用して動作する（例えば図3のメモリ114を参照されたい）。仮想化物理メモリは、例えばアドレスの連続空間として実際の物理メモリ14の抽象表現を含み、これは一般にゲスト物理アドレス（GPA）と呼ばれる。個々のこのようなアドレス空間は、ゲストVMに固有に結び付けられ、前記アドレス空間の部分は、物理メモリ14および/または物理記憶デバイス20のセクションにマッピングされる。仮想化を支援するように構成されるシステムでは、このようなマッピングは、典型的には、プロセッサ12によって制御される、第2のレベルのアドレス変換（SLAT）として知られている、ハードウェアで高速化された専用データ構造および機構を使用して達成される。一般的なSLAT実施態様は、Intel（登録商標）プラットフォーム上の拡張ページテーブル（EPT）、およびAMD（登録商標）プラットフォーム上の高速仮想化指標付け（RVI）/入れ子ページテーブル（NPT）を含む。このようなシステムでは、仮想化物理メモリは、当分野でページとして知られている単位で分割されることが可能であり、ページは、EPT/NPTなどの機構を介して物理メモリに個々にマッピングされる仮想化物理メモリの最小単位を表し、すなわち物理メモリと仮想化物理メモリの間のマッピングは、ページ単位の粒度で実施される。すべてのページは、典型的には、所定のサイズ、例えば4キロバイト、2メガバイト、等々を有している。仮想化物理メモリのページへの分割は、通常、ハイパーバイザ50によって構成される。いくつかの実施形態では、ハイパーバイザ50もSLAT構造を構成し、したがって物理メモリと仮想化物理メモリの間のアドレス変換を構成する。このようなアドレス変換は、当分野ではゲスト物理-ホスト物理（GPA-to-HPA）変換として知られている。

20

#### 【0028】

[0039]いくつかの実施形態では、VM内で実行するオペレーティングシステムは、それぞれのVM内で実行するプロセス毎に仮想メモリ空間をセットアップし、前記仮想メモリ空間は、物理メモリの抽象化を表している。プロセス仮想メモリは、典型的には、当分野で一般にゲスト仮想アドレス（GVA）またはゲスト線形アドレス（GLA）として知られている、アドレスの連続空間を含む。いくつかの実施形態では、プロセス仮想メモリ空間も同じくページに分割され、このようなページは、OSによってそれぞれのVMの仮想化物理メモリに個々にマッピングされる仮想メモリの最小単位を表し、すなわち仮想化物理メモリへの仮想メモリのマッピングは、ページ単位の粒度で実施される。OSは、ゲスト仮想-ゲスト物理、すなわちGVA-GPAアドレス変換を実施するためにそれぞれのVMの仮想化プロセッサによって使用される、ページテーブルなどの専用データ構造を構成することができる。

30

#### 【0029】

[0040]図4は、図2-Aの実施形態における例示的メモリアドレス変換を示したもので

40

50

ある。ハイパーバイザ 50 による公開後、ゲスト VM 52a は、仮想化物理メモリ空間 114a をその独自の物理メモリ空間として見る。ゲスト VM 52a 内で実行するプロセスには、ゲスト OS 54a によって仮想メモリ空間 214a が割り当てられる。ゲスト仮想アドレス 62 へのメモリアクセスをプロセスが試行すると、GVA 62 は、ゲスト VM 52a の（仮想化）MMU によって仮想化物理メモリ空間 114a 内のゲスト物理アドレス 64 に変換される。GVA - GPA 変換 70a は、例えばゲスト OS 34a によって構成され、かつ、制御されるページテーブルに従って進行することができる。GPA 64 は、MMU によってホストシステム 10 の物理メモリ 14 内のホスト物理アドレス（HPA）66 にさらにマッピングされる。GPA - HPA 変換 70b は、例えばハイパーバイザ 50 によって構成される SLAT 構造に従って進行することができる。

10

### 【0030】

[0041] ゲスト VM 52a ~ b の下で実行する個々のプロセスには、典型的には、当分野でホスト仮想アドレス（HVA）として知られるものを介してアドレス指定できる仮想メモリ空間が割り当てられる。図 4 の例では、ハイパーバイザ 50 は、コンピュータセキュリティモジュール 60 のための仮想メモリ空間 214b をセットアップしている。すると、CSM 60 は、HVA 68 を介して HPA 66 を参照することができる。モジュール 60 が例えばライブラリとしてハイパーバイザ 50 内に統合される場合、メモリ空間 214b は、ハイパーバイザ 50 の仮想メモリ空間と一致し得る。このような空間を管理するために、ハイパーバイザ 50 は、変換 70c などの HVA - HPA 変換を実施するために MMU によって使用される専用データ構造および機構（例えばページテーブル）を構成することができる。

20

### 【0031】

[0042] いくつかの実施形態では、ハイパーバイザ 50 および / または CSM 60 は、物理メモリページのサブセットの各々に対してアクセス許可を設定することができる。このようなメモリページは、例えば、OS および / またはマルウェア防止ルーチンのプロセスなど、保護された VM 内で実行する特定の重要なゲストプロセスによって使用され得る。アクセス許可は、例えばそれぞれのページがそのページから読み出され、そのページに書き込まれ得るかどうか、また、ソフトウェアがそれぞれのページからのコードの実行を許可されるかどうかを示す。アクセス許可は、例えばそれぞれのメモリページを表す SLAT エントリの一部として示され得る。いくつかのホストシステムは、サブページ単位の粒度でアクセス許可の設定を許可することができる。

30

### 【0032】

[0043] ハイパーバイザ 50 および / または CSM 60 は、さらに、ゲスト VM 内で実行しているソフトウェアがアクセス許可を違反するようなメモリアクセス（例えば非書き込み可能とマークされているメモリページへの書き込み）を試行すると、VM 中断イベントを生成するようにプロセッサ 12 を構成することができる。このような試行は、本明細書においてはメモリアクセス違反と呼ばれる。それぞれの VM 中断イベントは、図 2 - A などの構成における VM 終了イベント、および図 2 - B - C などの構成における仮想化例外であつてもよい。

40

### 【0033】

[0044] 本発明のいくつかの実施形態は、ハードウェア仮想化構成においてプロセッサがより有効に機能することができるよう、従来のハードウェアプロセッサの構造および機能に変更を導入している。図 5 は、本発明のいくつかの実施形態によるプロセッサ 12 の例示的ハードウェア構成要素を示したものである。示されている構成要素は、説明されている機能を実施する一般化デバイスを意味しており、構造的詳細は、実施態様間で大きく変更することが可能である。例えば示されている個々の構成要素は、相互接続された複数のサブシステムを備えることができ、これらは、必ずしも互いに物理的に近接している必要はない。示されている構成要素は、すべてを網羅したものではなく、プロセッサ 12 は、多くの他の構成要素（例えばスケジューラ、割込みコントローラ、様々なキャッシュ、等々）を含むことができ、それらは、描写を簡潔にするために図 5 から省略されている。

50

## 【 0 0 3 4 】

[0045] プロセッサ 12 は、プロセッサパイプラインの様々なステージを実行するように構成された論理 / 回路機構を含むことができる。例えば命令デコーダ 30 は命令デコード操作を実施し、この操作は、一組の基本プロセッサ動作および / またはマイクロオペレーションへの個々のプロセッサ命令の変換を含むことができる。デコーダ 30 に接続された一組の実行ユニット 36 は、パイプラインの実行ステージを実施することができる。例示的実行ユニット 36 は、とりわけ、演算論理ユニット (A L U) および浮動小数点ユニット (F P U) を含む。

## 【 0 0 3 5 】

[0046] いくつかの実施形態では、命令のためのパイプラインの実行ステージは、それぞれの命令のオペレータをそれぞれの命令のオペランドに適用した結果を決定することを含む。このような結果は、とりわけ、メモリアドレス、メモリアドレス、またはプロセッサレジスタ (例えば A X などの汎用レジスタ、モデル特化レジスタ - M S R、E F L A G S などの制御レジスタ、または同じく記述子キャッシュとして知られている x 8 6 セグメントレジスタの隠れた部分などの隠れレジスタ) にコミットされる値、命令ポインタ (例えば R I P) の値、およびスタックポインタ (例えば R S P) の値を含むことができる。

10

## 【 0 0 3 6 】

[0047] 命令のオペランドは、命令文の中で明示的であっても、あるいは暗示的であってもよい。オペランドが暗示的である例示的 x 8 6 命令は、プロセッサの E F L A G S 制御レジスタのキャリーフラグを 1 に設定する S T C 命令である。いくつかの実施形態では、レジスタ E F L A G S および値 1 は、(暗示的な) オペランドとして解釈されるが、それらは S T C 命令文には明示的に出現しない。

20

## 【 0 0 3 7 】

[0048] コミットユニット 38 は、パイプラインのコミットステージを実施することができ、すなわち実行ユニット 36 の出力をメモリ 14 に記憶することができ、および / または特定のプロセッサレジスタの内容を更新して、実行ステージによって生成される変化 / 結果を反映することができる。コミットユニット 38 は、当分野では退却ユニットとして知られている論理モジュールを備えることができる。

## 【 0 0 3 8 】

[0049] デコーダ 30 および実行ユニット 36 に接続されたメモリアクセスマジュール 34 は、例えばメモリから命令をフェッチするため、メモリからデータをロードするため、およびプロセッサ命令の実行の結果をメモリに記憶するために、メモリ 14 とインタフェースするように構成された論理を含む。いくつかの実施形態では、メモリアクセスマジュールは、メモリアクセスに必要な仮想 - 物理アドレス変換を実施するように構成された M M U を備えている。

30

## 【 0 0 3 9 】

[0050] 現代のプロセッサは、典型的には、プロセッサ命令の o u t - o f - o r d e r 実行および / または投機的実行をサポートする。このようなシステムでは、同じ実行ユニット 36 によって複数の命令が同時にフェッチされ、デコードされ、実行される。このような実行の結果は、次に、それぞれのコンピュータプログラムの意図されたフローを保存するために出現順に (i n - o r d e r) コミットされる。このような構成は、例えばプロセッサ 12 の性能を改善するために分岐予測アルゴリズムと共に使用される。o u t - o f - o r d e r 実行のために構成されるいくつかの実施形態では、プロセッサ 12 は、デコーダ 30 および実行ユニット 36 に結合されたディスパッチャユニット 32、および実行ユニット 36 およびコミットユニット 38 に結合されたレジスタファイル 40 をさらに備えることができる。ディスパッチャユニット 36 は、実行のために個々のマイクロオペレーションをスケジュールすることができ、また、実行およびコミットの順序を制御するために、そのそれぞれの命令を使用して、個々のマイクロオペレーションに関連するマッピングを維持することができる。レジスタファイル 40 は、例えばリオーダバッファとして編成された内部プロセッサレジスタのアレイを備えている。レジスタファイル 40 は

40

50

、ディスパッチャユニット 36 による、スケジュールされた個々のマイクロオペレーションへのファイル 40 のレジスタの行の結合を可能にする論理をさらに備えることができ、これは当分野でレジスタリネーミングとして知られている動作である。このような構成では、レジスタの個々のこののような行は、例えばプロセッサ 12 の汎用レジスタおよび／または状態レジスタの値を保持することができ、前記値は、特定のプロセッサ命令の実行の中間ステージに対応する。

#### 【 0 0 4 0 】

[0051] プロセッサ 12 は、仮想マシンの状態データを管理するように構成された仮想マシン制御ユニット 38 をさらに含むことができる。いくつかの実施形態では、仮想マシン状態オブジェクト (VMSO) は、ホストシステム 10 上に公開された個々の仮想化プロセッサの現在の状態を示すためにプロセッサ 12 によって内部で使用されるデータ構造を備えている。例示的 VMSO は、Intel (登録商標) プラットフォームの仮想マシン制御構造 (VMCS)、および AMD (登録商標) プラットフォームの仮想マシン制御ブロック (VMCB) を含む。VMSO は、典型的には、ハイパーバイザ 50 によって、個々の仮想マシンを公開する部分としてセットアップされる。いくつかの実施形態では、プロセッサ 12 は、ソフトウェアがメモリアドレスまたはポインタ (例えば Intel (登録商標) プラットフォーム上の VMCS ポインタ) を使用して特定の VMSO を参照することができるよう、メモリ内のある領域を個々の VMSO と結合する。

#### 【 0 0 4 1 】

[0052] 個々の VMSO は、ゲスト状態領域およびホスト状態領域を備えることができ、ゲスト状態領域は、それぞれのゲスト VM の CPU 状態を保持し、ホスト状態領域は、ハイパーバイザ 50 の現在の状態を記憶する。いくつかの実施形態では、VMSO のゲスト状態領域は、とりわけ、制御レジスタ (例えば CR0、CR3、等々)、命令ポインタ (例えば RIP)、汎用レジスタ (例えば EAX、ECX、等々)、およびそれぞれのゲスト VM の仮想プロセッサの状態レジスタ (例えば EFLAGS) の内容を含む。VMSO のホスト状態領域は、それぞれのゲスト VM のための GPA - HPA アドレス変換のために構成された SLAT データ構造に対するポインタ (例えば Intel (登録商標) プラットフォーム上の EPT ポインタ) を含むことができる。

#### 【 0 0 4 2 】

[0053] いくつかの実施形態では、プロセッサ 12 は、VMSO の一部を専用内部レジスタ / キャッシュに記憶することができ、一方、それぞれの VMSO の他の部分は、メモリに存在させることができる。任意の所与の時に、最大でも 1 つの VMSO (本明細書においては現在の VMSO と呼ばれる) がプロセッサにロードされ得、プロセッサ 12 の制御を現在有する仮想マシンを識別する。現代のプロセッサは、通例、マルチスレッドのために構成されている。このような構成では、物理プロセッサ 12 は複数のコアを動作させることができ、個々のコアは複数の論理プロセッサをさらに備え、個々の論理プロセッサは、他の論理プロセッサとは独立して、かつ、他の論理プロセッサと同時に実行スレッドを処理することができる。複数の論理プロセッサは、いくつかのハードウェア資源、例えば共通 MMU を共有することができる。マルチスレッド実施形態では、全く異なる VMSO が個々の全く異なる論理プロセッサ上にロードされ得る。

#### 【 0 0 4 3 】

[0054] プロセッサ 12 がそれぞれの VM の実行からハイパーバイザ 50 の実行に切り換える場合 (例えば VM 終了に応じて)、プロセッサ 12 は、それぞれの VM の状態を現在の VMSO のゲスト状態領域に保存することができる。プロセッサ 12 が第 1 の VM の実行から第 2 の VM の実行に切り換えると、第 1 の VM に結合された VMSO がアンロードされ、また、第 2 の VM に結合された VMSO がプロセッサにロードされ、第 2 の VMSO が現在の VMSO になる。いくつかの実施形態では、このような VMSO データのプロセッサ 12 へのロード / プロセッサ 12 からのアンロードは、仮想マシン制御モジュール 38 によって実施される。モジュール 38 は、メモリ 14 からの VMSO データの取り出しあり／またはメモリ 14 への VMSO データの保存をさらに実行することができる。

10

20

30

40

50

## 【0044】

[0055]いくつかの実施形態では、プロセッサ12は、実行ユニット36および/またはコミットユニット38に接続され、かつ、ゲスト命令と結合した命令特化データを記憶するように構成された中断イベントレジスタ44をさらに備えており、前記ゲスト命令を実行するとVM中断イベントが生じる（例えばVM終了または仮想化例外）。いくつかの実施形態では、中断イベントレジスタ44は公開されたレジスタであり、ホストシステム10上で実行しているソフトウェアからアクセスすることができ、すなわちレジスタ44に記憶されているデータは、セキュリティモジュール60などのソフトウェアによって読み出され得る。1つのこののような例では、中断イベントレジスタ44は、プロセッサ12のモデル特化レジスタ（MSR）を含む。いくつかの実施形態は、レジスタ44へのアクセスを、プロセッサ特権（例えばリング1またはルートモードのみ）またはオブジェクトタイプ（例えばドライバのみ）などの基準に従って選択されたソフトウェアオブジェクトのサブセットに制限することができる。いくつかの実施形態は、レジスタ44へのソフトウェアアクセスを操作のサブセットのみに制限することができる（例えば読み出しのみ）。

## 【0045】

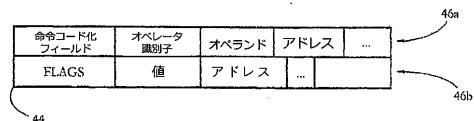

[0056]図6は、本発明のいくつかの実施形態による中断イベントレジスタ44のフィールドの例示的セットを示したものである。レジスタ44は、逆アセンブリフィールド46aおよび実行結果フィールド46bを含むことができる。逆アセンブリフィールド46aは、それぞれのゲスト命令を逆アセンブルすることによって得られるデータを記憶することができる。

## 【0046】

[0057]図7は、例示的なIntel（登録商標）×86プロセッサ命令のアセンブリ言語表現45を示したものである。示されている命令は、メモリの（仮想）アドレスEBX+4\*ECX+0x02に記憶されている内容を、レジスタAXに現在記憶されている値だけ増分するようにプロセッサに命令する。それぞれの命令は、マシンコード表現47としてメモリの中に表現されており、表現45と47の間の変換は、典型的にはコンパイラまたはアセンブラーによって実施される。×86命令のマシンコード表現は、一連のエンコードフィールド49を含む一般化形態48を有しており、このようなエンコードフィールドは、とりわけ、Prefix、Opcode、およびDisplacementフィールドを含む（他のISAの命令の表現は異なりうる）。図7は、所与の例示的×86命令についての個々のエンコードフィールドの例を示したものである。いくつかのISAでは、マシンコード表現は可変長を有することができ、例えばいくつかのエンコードフィールドは、特定の命令のマシンコード表現に出現し得るが、他の命令の表現には出現し得ない。

## 【0047】

[0058]いくつかの実施形態では、命令の逆アセンブルは、命令のマシンコード表現を構文解析して、一組の意味要素を識別および/または計算することを含む。このような意味要素は、とりわけ、命令のオペレータ（例えばMOV、ADD、等々）およびオペランド（例えばAX、[EBX+4\*ECX+0x02]）を含むことができる。いくつかの実施形態において、命令の意味要素は、個々の命令エンコードフィールド（例えば、×86ISAの場合、Prefix、Opcode、modR/M、SIB、Displacement、およびImmediate）を含む。そのような逆アセンブリは、少なくとも部分的に、命令デコーダ30によって、および/または実行ユニット36によって実行され得る。

## 【0048】

[0059]図7の例では、命令の逆アセンブルは、マシンコード表現47と一般化形態48との間の対応を示す矢印によって示されているように、個々のエンコードフィールドの内容を決定することを含みうる。いくつかの実施形態では、示されている命令の逆アセンブルは、ADDオペレータを識別すること、および/またはマシンコード47に従って、それぞれの命令が2つのオペランドを有し、オペランドのうちの1つがAXレジスタの内容

であり、第2のオペランドがメモリの内容であると決定すること、並びに、それぞれのメモリアドレスの式（例えば  $E B X + 4 * E C X + 0 \times 02$ ）を決定することを含むことができる。いくつかの実施形態では、命令の逆アセンブルは、それぞれの命令のオペランドによって示されるメモリアドレス（例えば、図7の例における式  $E B X + 4 * E C X + 0 \times 02$  の値）を計算することをさらに含む。逆アセンブルされる命令が相対ジャンプ命令（例えばマシンコードの中に  $0 \times E B 0 \times 08$  として表現された、 $\times 8$  6 プラットフォーム上の  $J M P \$ + 10$ ）である別の例では、命令の逆アセンブルは、命令のアドレス、ゲスト命令の長さ、および／または相対ジャンプのサイズに従って、行先の絶対メモリアドレスを計算することを含むことができる。

#### 【0049】

10

[0060]いくつかの実施形態では、レジスタ44の逆アセンブリフィールド46a（図6）は、それぞれの命令の命令エンコードフィールドの内容を含む（図7を参照）。フィールド46aの他の例示的内容は、それぞれの命令のオペレータを示すオペレータ識別子、およびそれぞれの命令のオペランドのインジケータを含む。オペランドインジケータは、プロセッサレジスタ（例えばAX）の識別子、および例えばそれぞれのオペランドがレジスタの内容であるか、またはメモリの内容であるかどうかを示すフラグをさらに含むことができる。逆アセンブリフィールド46aは、オペランドによって示されるメモリアドレス（例えばGVA、GPAおよび／またはHPA）をさらに含むことができる。逆アセンブルフィールド46aの構造は、プラットフォーム固有でありうる。例えば、インテル（登録商標）プラットフォームでは、逆アセンブリフィールド46aは、現在のゲスト命令のprefix、opcode、modR/M、SIB、displacement、およびimmediateのエンコードフィールドの内容を含むことができる。他のプラットフォームでは、フィールド46aは、それぞれのプラットフォームの命令セットアーキテクチャ（ISA）に従う他の値を記憶することができる。

#### 【0050】

20

[0061]いくつかの実施形態では、中断イベントレジスタ44の実行結果フィールド46bは、それぞれのプロセッサ命令を実行した結果を示すデータを記憶することができる。このような結果は、それぞれの命令を実行することによって得られる、状態レジスタ（例えばFLAGS）の値、命令ポインタ（例えばRIP）の値、および汎用レジスタ（例えばEAX）の値を含むことができる。フィールド46bは、それぞれの命令を実行した結果としてメモリにコミットされる値、それぞれの値のサイズ（例えばバイト、語、等々）、および／またはそれぞれの値がコミットされるメモリアドレスをさらに含むことができる。

#### 【0051】

30

[0062]いくつかの実施形態では、実行ユニット36および／またはコミットユニット38は、ゲスト命令の実行がVMプロセッサイベント（仮想化例外のVM終了などの）を生じさせるかどうかを決定し、生じさせる場合、それぞれのイベントを生成する前に、命令逆アセンブリデータを中断イベントレジスタ44に保存するように構成され得る。プロセッサ12は、それぞれのゲスト命令の実行ステージが完了するまでプロセッサイベントの生成を遅延し、かつ、それぞれの命令を実行した結果をメモリおよび／またはプロセッサ12の汎用レジスタにコミットする代わりに、そのような結果をイベントレジスタ44に保存するようにさらに構成され得る。そのような命令の結果をコミットするのを回避するために、プロセッサ12は、それぞれの命令のためのパイプラインのコミットステージの前に、VMプロセッサイベントを生成するように構成され得る。このような機能については、以下でさらに詳細に説明される。

40

#### 【0052】

[0063]図8は、本発明のいくつかの実施形態による、ゲスト命令を実行するためにプロセッサ12によって実施されるステップの詳細な例示的シーケンスを示したものである。図8は、プロセッサ12がメモリアクセス違反に応答してVM終了イベントを生成するように構成される一実施形態を示している。当業者は、この説明が、VM終了イベントの代

50

わりに他のVM中断イベント（仮想化例外など）を生成する実施形態を包含するべく容易に修正され得ることを認識するであろう。「ゲスト命令」は、本明細書においては、図2-AのVM52a～bなどのゲストVM内で実行するコンピュータプログラムの一部を形成しているプロセッサ命令を表すために使用される用語である。

#### 【0053】

[0064]ステップ302は、ゲスト命令のフェッチを試行する。フェッチの試行に失敗すると、ステップ303は、失敗がメモリアクセス違反によるものかどうかを決定することができる（例えばゲストVMのSLAT構造内の非実行可能とマークされたメモリページにゲスト命令が存在する場合）。メモリアクセス違反によるものではない場合、ステップ306でプロセッサ12は、VM終了イベントを生成し、かつ、実行を図2-Aのハンドラ61などのイベントハンドラに移行する。ゲスト命令のフェッチの失敗がメモリアクセス違反によるものである場合、そのような失敗は、セキュリティプログラム（例えばマルウェア防止モジュール）がそれぞれのメモリページの内容を保護しようとしていることを示し得る。このようにして典型的に実行から保護された例示的メモリセクションは、ゲストプロセスの実行スタックを記憶する。スタックを非実行可能としてマークすることにより、例えばスタックの活用からゲストプロセスを保護することができる。このような状況では、いくつかの実施形態は、ゲスト命令のフェッチを再試行し、それぞれのメモリアクセス許可を無視することができる（ステップ305）。ステップ307で、フェッチされたゲスト命令に、それぞれの命令が「強制的にフェッチされた」とこと、すなわちメモリアクセス許可を無効化している間にフェッチされたことを示すために専用フラグの印が付けられる。プロセッサ12は、次にステップ308へ進行することができる。10

#### 【0054】

[0065]フェッチステージに続いて、ステップ308は、ゲスト命令をデコードし、ディスパッチする。ステップ310でゲスト命令が実行される。ゲスト命令の実行がメモリアクセスには無関係のVM終了基準を満たすと、プロセッサ12は、以下で詳細に説明されるステップ322に進行する。このようなVM終了は、様々な状況でトリガされ得る。例えばゲスト命令は、ゲストVM内から呼び出されると、VM終了イベントを自動的にトリガするVMCALLなどの専用命令であってもよい。メモリアクセスには無関係である、VM終了の別の例示的理由は、ゲスト命令を実行している間のハードウェアイベント（例えば割込み）の発生である。20

#### 【0055】

[0066]ゲスト命令の実行がメモリアクセス違反を生じさせる場合（例えばゲスト命令が非書込み可能とマークされたメモリページに結果を書き込むようにプロセッサに命令する場合）、従来のプロセッサは、典型的にはゲスト命令の実行を中断し、プロセッサパイプラインをフラッシュして、VM中断イベント（例えばVMExit）を生成する。一方、本発明のいくつかの実施形態では、ゲスト命令の実行は中断されない。その代わりにステップ318で、ゲスト命令のためのパイプラインの実行ステージが終了するまでVM終了イベントが遅延される。しかしながら、いくつかの実施形態では、従来のシステムで発生した場合と同様、完了した実行ステージの結果はコミットされない。その代わりにステップ320で、プロセッサ12が、ゲスト命令の完了した実行ステージの結果を中断イベントレジスタ44に記憶するようにコミットユニット38に命令することができる。このような機能は、例えば、メモリアクセス違反が生じると、結果をメモリおよび/またはプロセッサ12の汎用レジスタにコミットすることから、結果をレジスタ44に記憶することへコミットユニット38を切り換えるための起動信号を使用して達成され得る。制御信号は、ゲスト命令の実行がメモリアクセス違反を生じさせたかどうかを示すことができる。コミットユニット38は、例えばMMUからメモリアクセスモジュール34を介してこのような信号を受け取ることができる。いくつかの実施形態では、ステップ320は、コミットユニット38が、ゲスト命令を実行した結果をレジスタファイル40から取り出すことを含む。40

#### 【0056】

[0067]一代替実施形態では、ゲスト命令の実行結果をレジスタ44に保存する代わりに、ステップ320は、それぞれのゲストVMのVMSOのゲスト状態領域などの専用メモリ領域にこのような結果を保存することができる。さらに別の実施形態では、プロセッサ12は、VM終了を実行すると(ステップ306)、このような結果をVM終了ハンドラ61に伝送することができる。

#### 【0057】

[0068]ステップ322で、プロセッサ12は、ゲスト命令の逆アセンブルの結果を中断イベントレジスタ44に(および/または上で説明したようにメモリに)記憶することができる。あるいは、命令逆アセンブリデータは、現在実行しているゲストVMのVMSOの専用エリアに記憶することができる。命令逆アセンブリデータは、ゲスト命令をデコードおよび/または実行するプロセスにおいて、命令デコーダ30および/または実行ユニット36によって生成されることが可能であり、ステップ322は、このようなデータをそれぞれのプロセッサモジュールから取り出すことを含むことができる。ゲスト命令に対する実行結果および/または逆アセンブリデータを記憶すると、プロセッサ12は、VM終了イベントを生成することができる(ステップ306)。

10

#### 【0058】

[0069]メモリアクセス違反を生じさせることなく(ステップ314)、また、VM終了に対する非メモリ関連の理由なく(ステップ312)、現在のゲスト命令の実行が進行すると、ステップ315は、現在のゲスト命令が強制的にフェッチされたものであるかどうかを決定することができる(上記ステップ305～307を参照されたい)。強制的にフェッチされたものではない場合、ステップ316は、実行の結果をメモリおよび/または汎用プロセッサレジスタにコミットする。現在のゲスト命令が強制的にフェッチされたものである場合、いくつかの実施形態は、それぞれの命令を、メモリアクセス違反を生じさせる命令として処理することができ、すなわちそれぞれの命令がパイプラインの実行ステージを完了するのを待機することにより、VM終了イベントを生成する前に結果および/または命令逆アセンブリデータをレジスタ44に記憶することができる(上記ステップ318～320～322～306を参照されたい)。

20

#### 【0059】

[0070]図9は、コンピュータセキュリティに関する本発明のいくつかの実施形態による、ゲストVMおよび/またはコンピュータセキュリティモジュール60(図2-A-B)によって実施されるステップの例示的シーケンスを示したものである。アプリケーション(例えば図2-Aの56a)などのゲストプロセス、またはオペレーティングシステム(例えば図2-AのゲストOS54a)のプロセスは、ゲストVM内で実行し、一連のゲスト命令を介してステップ方式で進行することができる(ステップ332)。ゲストプロセスの実行は、例えば図8に関連して上で説明したシナリオに従ってVM終了が生成されるまで継続する。当業者は、この説明が、プロセッサ12がVM終了イベントの代わりに仮想化例外を生成し、また、ゲストVM内で実行する例外ハンドラ(例えば図2-Bのハンドラ63)が、それぞれの例外を傍受するように構成されるシステムに如何に適合され得るかを認識することができる。

30

#### 【0060】

[0071]ステップ336で、ハンドラ61がVM終了イベントを傍受し、このVM終了イベントがセキュリティの脅威の証拠であることが分析される。イベントがセキュリティの脅威(例えば悪意のある意図で実行された操作)を示す場合、ステップ340でCSM60は、ゲストプロセスに対する保護アクション、および/またはゲストVMに対する保護アクションを取ることができる。このようなアクションは、とりわけ、ゲストプロセスの実行を阻止すること、エラーメッセージまたは一組の疑似結果をゲストプロセスに返すこと、およびホストシステムの管理者に警告することを含むことができる。

40

#### 【0061】

[0072]VM終了イベントがセキュリティの脅威を示さない場合、ステップ342は、ゲスト命令を実行した結果が利用可能である(プロセッサ12のイベントレジスタ44また

50

はメモリのいずれかにある)かどうかを決定する。利用可能でない場合、CSM60は、以下で詳細に説明されるステップ348に進行する。利用可能である場合、ステップ344は、それぞれの結果をレジスタ44および/またはメモリ(例えばそれぞれのゲストVMのVMSOのゲスト状態領域)から取り出す。ステップ346でCSM60は、現在のゲスト命令を実行した結果を適用することができる。いくつかの実施形態では、ステップ346は、コミットステージにおいて従来のシステムの中で実行される一組の操作を含む。例えばステップ346は、それぞれのゲストVMの仮想化プロセッサの汎用、制御、および状態プロセッサレジスタの値を更新することを含むことができる。いくつかの実施形態では、このようなレジスタは、それぞれのゲストVMのVMSOのゲスト状態領域内でアクセスすることができる。ステップ346は、現在のゲスト命令のオペランドによって示されるメモリアドレスにいくつかの結果を保存することをさらに含むことができる。ステップ346は、現在のゲスト命令の実行が完了したことを示すために、命令ポインタ(例えばx86プラットフォーム内のRIP)を増分することをさらに含むことができる。

10

#### 【0062】

[0073]本発明のいくつかの実施形態は、プロセッサ12の現在の命令セットアーキテクチャ(ISA)に専用命令を追加し、この新しい命令は、ゲスト命令を実行した結果を、それぞれのゲスト命令を実行しているゲストVMの下から直接適用するようにプロセッサ12に命令する。この新しい命令(例示的ニーモニックはVMAPPLYである)は、ステップ346(図9)の操作を実行することができ、例えば内容を中断イベントレジスタ44からそれぞれのゲストVMの仮想化プロセッサの仮想レジスタおよび/またはメモリにコピーすることができる。

20

#### 【0063】

[0074]いくつかの実施形態では、ステップ346は、さらに、現在のゲスト命令がアトミック命令(例えばLOCKプレフィックスで示される)であるかどうかを検証することができる。アトミック命令である場合、結果をゲストのレジスタおよび/またはメモリに直接適用する代わりに、ステップ346は、ゲストVMへ戻すと、現在のゲスト命令の再実行を強制することができる(以下のステップ356を参照されたい)。

20

#### 【0064】

[0075]現在のゲスト命令の実行結果を利用することができない場合(例えば現在のVM終了がVMCALLなどの特権命令によって生じたものである場合)、ステップ348でコンピュータセキュリティモジュール60は、逆アセンブリデータが現在のゲスト命令のために利用可能であるかどうかを決定する。利用可能である場合、ステップ350でCSM60は、そのデータを例えばレジスタ44の逆アセンブリフィールド46a(例えば図6を参照されたい)から取り出すことができる。CSM60は、次に、取り出された逆アセンブリデータに応じた現在のゲスト命令のエミュレートへ進行することができる(ステップ354)。

30

#### 【0065】

[0076]逆アセンブリデータを利用することができない場合、ステップ352は、エミュレーションを進める前に、現在のゲスト命令を逆アセンブルすることができる。ステップ356でCSM60は、それぞれのゲストVMを再起動することができる(例えばIntel(登録商標)プラットフォームのVMRESUME命令を発行することによって)。ステップ346が命令ポインタの修正を含むいくつかの実施形態では、ゲストプロセスの実行は、現在のゲスト命令の直後のプロセッサ命令で開始するか、または現在のゲスト命令によって示されるプロセッサ命令で開始することができる(例えばJMP、CALL、等々などの制御フロー変更命令の場合)。

40

#### 【0066】

[0077]上で説明した例示的システムおよび方法は、コンピュータまたはスマートフォンなどのホストシステムによる、ハードウェア仮想化構成で動作している場合のコンピュータセキュリティタスクの有効な実行を可能にする。セキュリティタスクは、とりわけ、コンピュータウイルスおよびスパイウェアなどのマルウェアに対するホストシステムの保護

50

を含むことができる。いくつかの実施形態では、ホストシステムは、オペレーティングシステムおよび一組のソフトウェアアプリケーションを仮想マシン内で実行するように構成される。セキュリティモジュールは、それぞれの仮想マシンの外部で、例えばハイパーバイザのレベルで実行することができ、また、それぞれの仮想マシンをマルウェアから保護することができる。

#### 【0067】

[0078]いくつかの実施形態では、セキュリティモジュールは、保護されたVMのセキュリティには極めて重要なコードおよび/またはデータを含むメモリのセクション（例えば一組のメモリページ）を識別し、かつ、メモリのそれぞれのセクションに対するアクセス許可を構成する。このようなアクセス許可は、例えばメモリのそれぞれのセクションが非書込み可能および/または非実行可能であることを示すことができる。セキュリティモジュールは、さらに、例えば保護されたVM内で実行しているソフトウェアが、非書込み可能とマークされたメモリのセクションへの書込みを試行し、または非実行可能とマークされたメモリのセクションからのコードの実行を試行すると、メモリアクセス違反に応答してVM中断イベント（VM終了または仮想化例外など）を生成するようにホストシステムのプロセッサを構成することができる。セキュリティモジュールは、次に、イベントハンドラを介してこのようなプロセッサイベントを傍受することができ、また、このようなイベントがコンピュータセキュリティの脅威を示すかどうかを決定することができる。セキュリティモジュールが保護されたVMの外部で実行する構成では、セキュリティモジュールのアクティビティは、マルウェアを含む、保護されたVM内で実行するソフトウェアには見ることができない可能性がある。

#### 【0068】

[0079]従来のシステムでは、VM中断イベントの傍受は、当分野で総称的に「トラップアンドエミュレート」として知られる方法に従って進行する。従来の技法の一例では、それぞれのイベント（例えばVM終了）を生じさせた命令を決定した後、実行を保護されたVMに戻す前に、また、それぞれの命令が既に実行されていることを示すために命令ポインタを修正する前に、マルウェア防止プログラムがそれぞれの命令をエミュレートする。エミュレーションステップがない場合、実行を保護されたVMに戻すと、典型的にはVM終了を再トリガすることになり、したがって無限ループを生成することになる。

#### 【0069】

[0080]したがって、従来のトラップアンドエミュレートシステムおよび方法には、場合によっては、命令逆アセンブリおよび/または命令エミュレータを含むためのマルウェア防止プログラムが必要である。このような構成要素は、場合によっては開発および維持が複雑であり、また、例えば1つのプロセッサから別のプロセッサに移植できないことがある。さらに、従来のシステムでは、逆アセンブリおよび/またはエミュレーションステップは、典型的にはすべてのVM中断イベントに対して実行され、相当な計算負荷をホストシステムに課す。一方、本発明のいくつかの実施形態は、逆アセンブリおよび/またはエミュレータの必要性をなくし、コンピュータセキュリティ動作を実質的に加速する。

#### 【0070】

[0081]本発明のいくつかの実施形態は、従来のプロセッサの構成および動作に変更を導入し、ハードウェア仮想化構成におけるこのようなプロセッサのより有効な動作を可能にする。いくつかの実施形態において、プロセッサは、VM中断イベントの生成を、現在の命令のためのパイプラインの実行フェーズが完了するまで、少なくともある状況（例えば、VM中断イベントがメモリアクセス違反によりトリガされるとき）では遅らせるように構成される。プロセッサは、現在の命令の実行ステージの結果を、特別なプロセッサレジスタ（プロセッサの汎用レジスタ若しくは制御レジスタとは異なる）または特別なメモリ領域（例えば、それぞれのゲストVMのゲスト状態領域）に保存するようにさらに構成することができる。

#### 【0071】

[0082]このような改善は、コンピュータセキュリティアプリケーションにはとりわけ有

10

20

30

40

50

利であり、外部、例えばそれぞれのVMを公開するハイパーバイザのレベルからの仮想マシンの有効な保護を可能にすることができる。従来のコンピュータセキュリティ解決法と比較すると、本発明のいくつかの実施形態は、VM中断イベントを傍受し、かつ、分析するように構成されるセキュリティソフトウェアの操作から逆アセンブリおよびエミュレーションのステージを除去することにより、計算の実質的な低減を可能にする。それぞれのイベントを生成した命令のエミュレートに代えて、いくつかの実施形態は、セキュリティソフトウェアが、それぞれの結果をプロセッサレジスタまたはメモリの場所から読み出し、そのような結果を直接適用することを可能にする。

## 【0072】

[0083]従来のシステムとは対照的に、本発明のいくつかの実施形態は、VM中断イベントを、現在のゲスト命令がパイプラインの実行ステージを完了した後にのみ生成する。ハードウェアコンポーネントの機能に対するそのような変更は、それぞれの命令の実行ステージを実行するのに必要な余分なクロックチックによる遅延を導入することがある。しかしながら、そのような性能のペナルティは、従来のコンピュータセキュリティソフトウェアには必要な（潜在的には、各VM中断イベントに対して数百の追加命令に達する）命令エミュレーションおよび/または逆アセンブリの操作を除去することによって実質的に相殺される。

## 【0073】

[0084]上記実施形態は、本発明の範囲を逸脱することなく、多くの方法で変更され得ることは当業者には明らかであろう。したがって本発明の範囲は、以下の特許請求の範囲およびそれらの合法等価物によって決定されるものとする。

【図1】

FIG. 1

【図2-B】

FIG. 2-B

【図2-A】

FIG. 2-A

【図2-C】

FIG. 2-C

【図3】

FIG. 3

【図6】

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

【図9】

FIG. 9

---

フロントページの続き

(72)発明者 ルカクス , サンドル

ルーマニア国ジュデツ・クルジュ , コム . フロレシチ , サト・フロレシチ , ビルド . チェタテア ·

フェテイ ブロック 8 , エタジユル 3

(72)発明者 ルツアス , アンドレイ - ヴラド

ルーマニア国ジュデツ・サトウ・マーレ , サトウ・マーレ , ビルド . クロシカ ヌマルル 111

審査官 上島 拓也

(56)参考文献 特表2007-528084 (JP, A)

特開2011-227939 (JP, A)

特開2009-9232 (JP, A)

特表2005-528690 (JP, A)

(58)調査した分野(Int.Cl. , DB名)

G 06 F 21 / 56

G 06 F 9 / 455