(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-88083

(P2004-88083A)

(43) 公開日 平成16年3月18日(2004.3.18)

(51) Int.Cl.<sup>7</sup>

H01L 33/00

F 1

H01L 33/00

C

テーマコード(参考)

5FO41

審査請求 未請求 請求項の数 33 O L (全 30 頁)

(21) 出願番号 特願2003-175716 (P2003-175716)

(22) 出願日 平成15年6月20日 (2003.6.20)

(31) 優先権主張番号 特願2002-183919 (P2002-183919)

(32) 優先日 平成14年6月25日 (2002.6.25)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000005821

松下電器産業株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100077931

弁理士 前田 弘

(74) 代理人 100094134

弁理士 小山 廣毅

(74) 代理人 100110939

弁理士 竹内 宏

(74) 代理人 100113262

弁理士 竹内 祐二

(74) 代理人 100115059

弁理士 今江 克実

(74) 代理人 100117710

弁理士 原田 智雄

最終頁に続く

(54) 【発明の名称】半導体発光素子、その製造方法及びその実装方法

## (57) 【要約】

【課題】化合物半導体、特にGaN系半導体からなる半導体発光素子に対して、その放熱性を良好とすると共に静電耐圧を増大し、さらに発光効率の向上と直列抵抗の低減とを図る。

【解決手段】発光ダイオード素子10は、互いに異なる導電型を持つ少なくとも2層の半導体層を含む素子構造体11を有し、該素子構造体11の上にはITOからなる透光性を有するp側電極15が形成され、該p側電極15の上の一部の領域にはボンディングパッド16が形成されている。素子構造体11におけるp側電極15の反対側の面上にはTi/Auからなるn側電極17が形成され、一方、n側電極17のAu層を下地層として、厚さが約50μmの金めっきによる金属膜18が形成されている。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

互いに異なる導電型を持つ少なくとも 2 つの半導体層を含む半導体積層膜と、前記半導体積層膜の一方の面上に形成された第 1 の電極と、前記半導体積層膜の前記一方の面と対向する対向面上に形成された第 2 の電極と、前記第 1 の電極又は前記第 2 の電極と接するように形成され、前記半導体積層膜の膜厚よりも大きいか等しい膜厚を有する金属膜とを備えていることを特徴とする半導体発光素子。

**【請求項 2】**

前記半導体積層膜は、V 族元素に窒素を含む III-V 族化合物半導体からなることを特徴とする請求項 1 に記載の半導体発光素子。 10

**【請求項 3】**

前記金属膜の膜厚は 10 μm 以上であることを特徴とする請求項 1 又は 2 に記載の半導体発光素子。

**【請求項 4】**

前記金属膜は、金、銅又は銀からなることを特徴とする請求項 1 又は 2 に記載の半導体発光素子。

**【請求項 5】**

前記金属膜はめっきにより形成されていることを特徴とする請求項 1 又は 2 に記載の半導体発光素子。 20

**【請求項 6】**

前記金属膜は、前記半導体積層膜の反対側部分に融点が 300 以下である金属層を含むことを特徴とする請求項 1 又は 2 に記載の半導体発光素子。

**【請求項 7】**

前記金属層は錫を含むことを特徴とする請求項 6 に記載の半導体発光素子。

**【請求項 8】**

前記第 1 の電極及び第 2 の電極のうち、前記金属膜と接するように形成された電極は、前記半導体積層膜から発光される光に対して 90 % 以上の反射率を有していることを特徴とする請求項 1 又は 2 に記載の半導体発光素子。

**【請求項 9】**

前記第 1 の電極及び第 2 の電極のうち、前記金属膜と接するように形成された電極は、金、白金、銅、銀及びロジウムのうちの少なくとも 1 つからなる単層膜、又はこれらのうちの 2 つ以上を含む積層膜からなることを特徴とする請求項 1、2 又は 8 のいずれか 1 項に記載の半導体発光素子。 30

**【請求項 10】**

前記半導体積層膜と前記金属膜との間に形成され、誘電体又は半導体からなるミラー構造体をさらに備え、

前記ミラー構造体は、前記半導体積層膜から発光される光に対して 90 % 以上の反射率を有していることを特徴とする請求項 1、2 又は 8 のいずれか 1 項に記載の半導体発光素子。 40

**【請求項 11】**

前記ミラー構造体は、酸化シリコン、酸化チタン、酸化ニオブ、酸化タンタル及び酸化ハフニウムのうちのいずれか、又は窒化アルミニウムガリウムインジウム ( $\text{Al}_x \text{Ga}_y \text{In}_{1-x-y} \text{N}$ ) (但し、 $0 < x, y < 1$  である。) を含み、前記半導体積層膜からの発光波長に対する屈折率が周期的に変化するように形成されていることを特徴とする請求項 10 に記載の半導体発光素子。

**【請求項 12】**

前記第 1 の電極及び第 2 の電極のうち、前記半導体積層膜に対して前記金属膜の反対側に設けられた電極は、透光性を有していることを特徴とする請求項 1 に記載の半導体発光素子。 50

**【請求項 1 3】**

前記第1の電極及び第2の電極のうち、前記半導体積層膜に対して前記金属膜の反対側に設けられた電極は、インジウム錫酸化物からなるか、又は膜厚が20nm以下のニッケルを含む金属からなることを特徴とする請求項1に記載の半導体発光素子。

**【請求項 1 4】**

前記半導体積層膜と前記金属膜との間で且つその側部に形成され、誘電体からなる電流狭窄膜をさらに備えていることを特徴とする請求項1に記載の半導体発光素子。

**【請求項 1 5】**

単結晶からなる基板上に、互いに異なる導電型を持つ少なくとも2つの半導体層を含む半導体積層膜を形成する工程(a)と、

10

前記基板を前記半導体積層膜から分離する工程(b)と、

前記半導体積層膜の一方の面上に第1の電極を形成し、前記半導体積層膜の前記一方の面と対向する対向面上に第2の電極を形成する工程(c)と、

前記第1の電極及び第2の電極のうちの一方の上に金属膜を形成する工程(d)とを備えていることを特徴とする半導体発光素子の製造方法。

**【請求項 1 6】**

前記半導体積層膜は、V族元素に窒素を含むIII-V族化合物半導体からなることを特徴とする請求項15に記載の半導体発光素子の製造方法。

**【請求項 1 7】**

前記工程(b)において、

20

前記基板における前記半導体積層膜の反対側の面から、前記基板を透過し且つ前記半導体積層膜の一部に吸収される波長を有する照射光を照射して、前記半導体積層膜の内部に前記半導体積層膜の一部が分解してなる分解層を形成することにより、前記基板を前記半導体積層膜から分離することを特徴とする請求項15又は16に記載の半導体発光素子の製造方法。

**【請求項 1 8】**

前記工程(b)において、

20

前記基板を研磨により除去することにより、前記基板を前記半導体積層膜から分離することを特徴とする請求項15又は16に記載の半導体発光素子の製造方法。

**【請求項 1 9】**

前記工程(a)は、

30

前記半導体積層膜の一部を形成した後、前記基板における前記半導体積層膜の反対側の面から、前記基板を透過し且つ前記半導体積層膜に吸収される波長を有する照射光を照射することにより、前記半導体積層膜の一部の内部に前記半導体積層膜が分解してなる分解層を形成する工程と、

前記分解層を形成した後、前記半導体積層膜の一部の上に、前記半導体積層膜の残部を形成する工程とを含むことを特徴とする請求項15又は16に記載の半導体発光素子の製造方法。

**【請求項 2 0】**

前記照射光は、パルス状に発振するレーザ光であることを特徴とする請求項17又は19に記載の半導体発光素子の製造方法。

40

**【請求項 2 1】**

前記照射光は、水銀ランプの輝線であることを特徴とする請求項17又は19に記載の半導体発光素子の製造方法。

**【請求項 2 2】**

前記照射光は、前記基板の面内をスキャンするように照射することを特徴とする請求項17又は19に記載の半導体発光素子の製造方法。

**【請求項 2 3】**

前記照射光は、前記基板を加熱しながら照射することを特徴とする請求項17又は19に記載の半導体発光素子の製造方法。

50

**【請求項 2 4】**

前記工程 ( a ) と前記工程 ( b )との間に、

前記半導体積層膜の上に誘電体又は半導体からなる積層膜を形成した後、形成した積層膜をパターニングする工程 ( e ) をさらに備え、

前記工程 ( c )において、前記第1の電極及び第2の電極のうちのいずれか一方を、パターニングされた前記積層膜の上に形成し、

前記工程 ( d )において、前記金属膜は、パターニングされた前記積層膜の上に形成した電極の上に形成することを特徴とする請求項 1 5 又は 1 6 に記載の半導体発光素子の製造方法。

**【請求項 2 5】**

前記工程 ( c )において、前記基板を前記半導体積層膜から分離した後に、前記第1の電極及び第2の電極のうちの他方を、前記半導体積層膜における前記積層膜の反対側の面上に形成することを特徴とする請求項 2 4 に記載の半導体発光素子の製造方法。

**【請求項 2 6】**

前記工程 ( a ) と前記工程 ( b )との間に、

前記半導体積層膜を構成する材料と異なる材料からなり、前記半導体積層膜を保持する膜状の第1の保持部材を前記半導体積層膜に貼り合わせる工程 ( f ) と、

前記工程 ( b )よりも後に、前記第1の保持部材を前記半導体積層膜から剥離する工程 ( g ) とをさらに備えていることを特徴とする請求項 1 5 又は 1 6 に記載の半導体発光素子の製造方法。

**【請求項 2 7】**

前記工程 ( g ) の前に、前記第1の保持部材とは特性が異なる膜状の第2の保持部材を、前記半導体積層膜における前記第1の保持部材の反対側の面上に貼り合わせる工程 ( h ) と、

前記工程 ( g )よりも後に、前記第2の保持部材を前記半導体積層膜から剥離する工程 ( i ) とをさらに備えていることを特徴とする請求項 2 6 に記載の半導体発光素子の製造方法。

**【請求項 2 8】**

前記第1の保持部材又は前記第2の保持部材は、高分子材料フィルム、半導体からなる単結晶基板又は金属板であることを特徴とする請求項 2 6 又は 2 7 に記載の半導体発光素子の製造方法。

**【請求項 2 9】**

前記高分子材料フィルムは、その貼り合わせ面に加熱により剥離可能な接着材層が設けられていることを特徴とする請求項 2 8 に記載の半導体発光素子の製造方法。

**【請求項 3 0】**

前記工程 ( c )よりも前に、前記半導体積層膜の上に誘電体からなる電流狭窄膜を選択的に形成する工程 ( j ) をさらに備えていることを特徴とする請求項 1 5 又は 1 6 に記載の半導体発光素子の製造方法。

**【請求項 3 1】**

単結晶からなる基板上に、互いに異なる導電型を持つ少なくとも 2 つの半導体層を含む半導体積層膜を形成する工程 ( a ) と、

前記半導体積層膜を構成する材料と異なる材料からなり、前記半導体積層膜を保持する膜状の保持部材を前記半導体積層膜に貼り合わせる工程 ( b ) と、

前記半導体積層膜を前記保持部材と共にダイシングを行なって、それぞれ個別化された前記保持部材に保持された状態の複数のチップを作製する工程 ( c ) と、

前記保持部材に保持された前記各チップに対してダイスボンディングを行なった後、前記保持部材を前記各チップから剥離する工程 ( d ) とを備えていることを特徴とする半導体発光素子の実装方法。

**【請求項 3 2】**

前記保持部材は、高分子材料フィルムであることを特徴とする請求項 3 1 に記載の半導体

10

20

30

40

50

発光素子の実装方法。

【請求項 3 3】

前記高分子材料フィルムは、その貼り合わせ面に加熱により剥離可能な接着材層が設けられていることを特徴とする請求項 3 2 に記載の半導体発光素子の実装方法。

【発明の詳細な説明】

【0 0 0 1】

【発明の属する技術分野】

本発明は、短波長発光ダイオード素子等の半導体発光素子、その製造方法及びその実装方法に関する。

【0 0 0 2】

【従来の技術】

一般式が  $B_z Al_x Ga_{1-x-y-z} In_y N_{1-v-w} As_v P_w$  (但し、 $x, y, z, v, w$  は、 $0 \leq x \leq 1, 0 \leq y \leq 1, 0 \leq z \leq 1, 0 \leq x+y+z \leq 1, 0 \leq v \leq 1, 0 \leq w \leq 1, 0 \leq v+w \leq 1$  である。) で表わされる III-V 族窒化物半導体 (一般に  $BAI_3GaInNAsP$  で表記され、以下、GaN 系半導体と呼ぶ。) は、例えば窒化ガリウム (GaN) の場合には、室温における禁制帯幅が 3.4 eV と比較的に広い禁制帯幅を有しているため、青色光若しくは緑色光を出力する可視域発光ダイオード素子又は短波長半導体レーザ素子等の発光デバイスや、高温下での動作が可能なトランジスタ又は高速動作が可能な大電力トランジスタ等の幅広い応用が期待されている。発光デバイスは、発光ダイオード素子及び半導体レーザ素子が商品化されている。なかでも、発光ダイオード素子は、青色光又は緑色光を出力する各種表示装置、大型ディスプレイ装置及び交通信号機で実用化されている。また、蛍光材料が励起されて発光する白色発光ダイオード素子は、現行の蛍光灯や白熱灯を置き換える、いわゆる半導体照明の実現に向け、その高輝度化及び発光効率の改善を図って研究開発が活発に進められている。

【0 0 0 3】

これまで、GaN 系半導体は他のワイドギャップ半導体と同様に、結晶成長法による成長が困難であったが、最近になって有機金属気相成長 (Metal Organic Chemical Vapor Deposition: MOCVD) 法を中心とする結晶成長技術が大きく進展したため、前述の発光ダイオード素子が実用化されるに至っている。

【0 0 0 4】

ところで、結晶成長層 (エピタキシャル層) の成長用基板として、窒化ガリウム (GaN) からなる基板を作製することは容易ではなく、従って、シリコン (Si) 又はヒ化ガリウム (GaAs) のように、基板自体への製造プロセスを行なえず、また基板上のエピタキシャル層も同一材料からなる基板上への成長を行なえないため、一般にはエピタキシャル層と異なる材料を基板に用いたヘテロエピタキシャル成長を行なっている。

【0 0 0 5】

これまでに最も広く用いられ、最も優れたデバイス特性を示しているのがサファイアを基板として成長した GaN 系半導体である。サファイアの結晶構造は GaN 系半導体と同一の六方晶系であり、しかも熱的に極めて安定であるため、1000 以上という高温を必要とされる GaN 系半導体の結晶成長に適している。従って、従来は、主にサファイアからなる基板上に成長した GaN 系半導体層に対して発光ダイオード素子の高輝度化及び発光効率の改善が図られてきた。例えば、高輝度化を図るには、GaN 系半導体における結晶性を良好とし非発光再結合を抑制することにより内部量子効率を向上させることと、光の取り出し効率を改善することとの 2 点が重要である。

【0 0 0 6】

前述したように、近年結晶成長技術が大いに進展した結果、内部量子効率の向上は限界に近づきつつあるため、最近では光の取り出し効率の向上が重要な課題となってきた。

【0 0 0 7】

以下、従来の光の取り出し効率の改善を図る 2 つの手法について図面を参照しながら説明する。

10

20

20

30

40

50

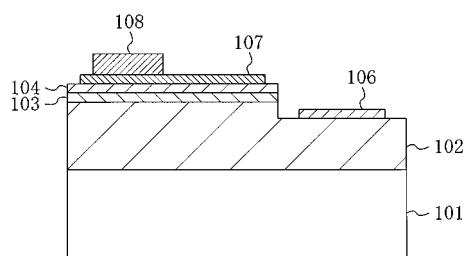

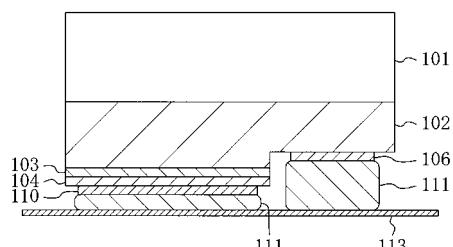

## 【0008】

(第1の従来例)

図18に示すように、第1の従来例に係る発光ダイオード素子は、例えばMOCVD法により、サファイアからなる基板101の上に、n型AlGaNからなるn型半導体層102と、InGaNからなる活性層103と、p型AlGaNからなるp型半導体層104とを順次成長する。続いて、ドライエッチングによりn型半導体層102の一部を選択的に露出し、露出したn型半導体層102の上に、Ti/Alからなるn側電極106を形成する。また、p型半導体層104の上には、厚さが10nm程度かそれ以下のNi/Auからなる透明p側電極107を形成し、透明p側電極107上の一部の領域にAlからなるボンディングパッド108を形成する(特許文献1参照)。

10

## 【0009】

このように、第1の従来例に係る発光ダイオード素子は、透明p側電極107を用いることにより、活性層103から出射される例えば波長が470nmの青色の発光光はその大部分が透明p側電極107を透過して外部へ取り出されるため、高輝度発光が可能である。それでも、基板101側への発光光は十分には取り出されないため、発光効率の改善には限界がある。

## 【0010】

(第2の従来例)

図19に示すように、第2の従来例に係る発光ダイオード素子は、保護ダイオード付きサブマウント113の上面に、p型半導体層104を対向させて実装する、いわゆるフリップチップ実装されてなり、サファイアからなる基板101を通して発光光を取り出している(特許文献2参照)。ここで、p型半導体層104のサブマウント113との対向面には、Niからなるp側電極110が形成されており、該p側電極110とサブマウント113との間、及びn側電極106とサブマウント113との間には、それぞれAgからなるバンプ111が形成されている。ここでは、サファイアからなる基板101が絶縁性材料であるため、静電耐圧が小さい。従って、サージ電圧が印加された場合に、サージ電流がチップを流れないように保護ダイオード付きのサブマウント113を用いている。

20

## 【0011】

また、バンプ111を構成するAgは青色光に対して高反射率を有するため、この高反射率を有する電極構造とフリップチップ実装とによって、活性層103からの例えば波長が470nmの青色の発光光はその大部分がバンプ111で反射された後に、基板101を透過して外部に取り出される。従って、高輝度発光が可能である。また、保護ダイオード付きサブマウント113を用いていることから、静電耐圧が大きくなっている。

30

## 【0012】

## 【特許文献1】

特開平07-94782号公報

## 【特許文献2】

特開平11-191641号公報

## 【特許文献3】

特開2001-274507号公報

40

## 【特許文献4】

特開2001-313422号公報

## 【0013】

## 【発明が解決しようとする課題】

しかしながら、前記第1の従来例及び第2の従来例に係る発光ダイオード素子は、そのいずれもがサファイアからなる基板101上に形成されており、サファイアは熱伝導性が比較的に低く放熱性が劣るため、高出力動作の限界点が低いという問題がある。

## 【0014】

また、サファイアは絶縁性であり静電耐圧が低いため、第2の従来例のようにサージ対策用の保護ダイオード素子を設ける必要がある等、実装コストが大きくなるという問題もあ

50

る。

【0015】

さらに、基板101が導電性を持たないことから、n側電極とp側電極とを基板101に對して同一面(上面)側に形成する構成しか採り得ず、両電極を基板101を挟んで互いに對向するように設けることができない。その結果、ダイオード素子として直列抵抗が大きくなってしまい、動作電圧が大きくなるという問題がある。

【0016】

本発明は、前記従来の問題に鑑み、化合物半導体、特にGaN系半導体からなる半導体発光素子に対して、その放熱性を良好とすると共に静電耐圧を増大し、さらに発光効率の向上と直列抵抗の低減とを図ることを目的とする。

10

【0017】

【課題を解決するための手段】

前記の目的を達成するため、本発明は、半導体発光素子を、活性層を含む化合物半導体からなる半導体積層膜の表面及び裏面に互いに對向する対向電極を形成し、対向電極の一方に比較的に厚膜の金属膜を設ける構成とする。さらに、対向電極のうち金属膜と接する一方の電極材料には活性層からの発光光に対する反射率が高い材料を選択し、且つ他方の電極材料には透光性材料を選択するか又はその平面寸法を可能な限り小さくする。

【0018】

具体的には、本発明に係る半導体発光素子は、互いに異なる導電型を持つ少なくとも2つの半導体層を含む半導体積層膜と、半導体積層膜の一方の面上に形成された第1の電極と、半導体積層膜の一方の面と對向する対向面上に形成された第2の電極と、第1の電極又は第2の電極と接するように形成され、半導体積層膜の膜厚よりも大きいか等しい膜厚を有する金属膜とを備えている。

20

【0019】

本発明の半導体発光素子によると、互いに異なる導電型を持つ少なくとも2つの半導体層を含む半導体積層膜が成長した基板を除去し、代わりに、半導体積層膜の膜厚よりも大きいか等しい膜厚を有する金属膜を設けることにより、基板を残した場合における該基板による発光光の吸収を抑制できる。その結果、半導体積層膜における金属膜の反対側の面からより多くの発光光を取り出すことが可能となる。また、基板を除去して比較的厚膜の金属膜を設けるため、直列抵抗を低減できる上に、放熱性が大幅に改善され且つ静電耐圧が大きくなる。その上、金属膜と接する電極に高反射材料を用いた場合には発光効率を増大することが可能となる。

30

【0020】

本発明の半導体発光素子において、半導体積層膜はV族元素に窒素を含むIII-V族化合物半導体からなることが好ましい。このようにすると、V族元素に窒素を含むIII-V族化合物半導体、すなわちIII-V族窒化物半導体は、サファイア等の異種基板を用いる場合が多いため、該異種基板を除去する効果は極めて大きい。

30

【0021】

本発明の半導体発光素子において、金属膜の膜厚は10μm以上であることが好ましい。

40

【0022】

本発明の半導体発光素子において、金属膜は金、銅又は銀からなることが好ましい。このようにすると、金、銅及び銀はいずれも熱伝導率が大きいため、放熱性がより向上するので、さらなる大出力動作を確実に行なえるようになる。

【0023】

本発明の半導体発光素子において、金属膜はめっきにより形成されていることが好ましい。このようにすると、金属膜を短時間で且つ再現性良く形成できるため、高出力動作が可能な半導体発光素子を低コストで実現できる。

【0024】

本発明の半導体発光素子において、金属膜は、半導体積層膜の反対側部分に融点が300以下である金属層を含むことが好ましい。このようにすると、半導体発光素子をパッケ

50

ージ又はリードフレームにダイスボンディングする場合に、融点が300℃以下の金属層は半田材として機能するため、わざわざ半田材を用いる必要がなくなるので、再現性良く且つ低コストで発光素子のダイスボンディングを行なうことができる。

## 【0025】

この場合に、金属層は錫を含むことが好ましい。

## 【0026】

本発明の半導体発光素子において、第1の電極及び第2の電極のうち金属膜と接するよう10

に形成された電極は、半導体積層膜から発光される光に対して90%以上の反射率を有していることが好ましい。このようにすると、光の取り出し効率が向上するため、発光素子の高輝度化を実現できる。

## 【0027】

本発明の半導体発光素子において、第1の電極及び第2の電極のうち金属膜と接するよう20

に形成された電極は、金、白金、銅、銀及びロジウムのうちの少なくとも1つからなる単層膜、又はこれらのうちの2つ以上を含む積層膜からなることが好ましい。このようにすると、半導体積層膜から発光される光に対して90%以上の反射率を有する電極を確実に形成することができる。

## 【0028】

本発明の半導体発光素子は、半導体積層膜と金属膜との間に形成され、誘電体又は半導体20

からなるミラー構造体をさらに備え、ミラー構造体は、半導体積層膜から発光される光に対して90%以上の反射率を有していることが好ましい。このようにすると、ミラー構造体は、反射率が大きい単体の材料からなる電極と比べて光の取り出し効率が高いため、発光素子の高輝度化を実現できる。

## 【0029】

この場合に、ミラー構造体は、酸化シリコン、酸化チタン、酸化ニオブ、酸化タンタル及び酸化ハフニウムのうちのいずれか、又は窒化アルミニウムガリウムインジウム( $\text{Al}_x\text{Ga}_y\text{In}_{1-x-y}\text{N}$ ) (但し、 $0 < x, y < 1$ 、 $0 < x+y < 1$ である。)を含み、半導体積層膜からの発光波長に対する屈折率が周期的に変化するように形成されていることが好ましい。このようにすると、ミラー構造体を構成する各層ごとの屈折率差が大きくなるため、層数を減らしても反射率が大きいミラー構造体を得ることができる。

## 【0030】

本発明の半導体発光素子において、第1の電極及び第2の電極のうち半導体積層膜に対して30

金属膜の反対側に設けられた電極は、透光性を有していることが好ましい。このようにすると、半導体積層膜から発光される発光光が透光性を有する電極を通して取り出されるので、光の取り出し効率が改善される。

## 【0031】

また、本発明の半導体発光素子において、第1の電極及び第2の電極のうち半導体積層膜に対して金属膜の反対側に設けられた電極は、インジウム錫酸化物からなるか、又は膜厚が20nm以下のニッケルを含む金属からなることが好ましい。このようにすると、透光性を有する電極を確実に形成することができる。

## 【0032】

本発明の半導体発光素子は、半導体積層膜と金属膜との間で且つその側部に形成され、誘電体からなる電流狭窄膜をさらに備えていることが好ましい。

## 【0033】

本発明に係る半導体発光素子の製造方法は、単結晶からなる基板上に、互いに異なる導電型を持つ少なくとも2つの半導体層を含む半導体積層膜を形成する工程(a)と、基板を半導体積層膜から分離する工程(b)と、半導体積層膜の一方の面上に第1の電極を形成し、半導体積層膜の一方の面と対向する対向面上に第2の電極を形成する工程(c)と、第1の電極及び第2の電極のうちの一方の上に金属膜を形成する工程(d)とを備えている。

## 【0034】

10

20

30

40

50

本発明の半導体発光素子の製造方法によると、基板上に互いに異なる導電型を持つ少なくとも2つの半導体層を含む半導体積層膜を形成し、続いて基板を半導体積層膜から分離した後、半導体積層膜の一方の面上に第1の電極を形成し、半導体積層膜の一方の面と対向する対向面上に第2の電極を形成し、さらに第1の電極及び第2の電極のうちの一方の上に金属膜を形成する。このように、半導体積層膜を形成した基板を半導体積層膜から分離するため、基板による発光光の吸収を抑制できるので、半導体積層膜における金属膜と反対側の面側からより多くの発光光を取り出すことができるようになる。また、基板に代えて半導体積層膜の上に電極を介在させて金属膜を設けるため、半導体積層膜における直列抵抗を低減できる上に、放熱性を大幅に改善でき且つ静電耐圧が大きくなる。

## 【0035】

10

本発明の半導体発光素子の製造方法において、半導体積層膜はV族元素に窒素を含むII - V族化合物半導体からなることが好ましい。

## 【0036】

本発明の半導体発光素子の製造方法は、工程(b)において、基板における半導体積層膜の反対側の面から、基板を透過し且つ半導体積層膜の一部に吸収される波長を有する照射光を照射して、半導体積層膜の内部に半導体積層膜の一部が分解してなる分解層を形成することにより、基板を半導体積層膜から分離することが好ましい。このようにすると、基板の面積が比較的に大きい場合であっても、基板と半導体積層膜とを再現性良く分離することができる。

## 【0037】

20

また、本発明の半導体発光素子の製造方法は、工程(b)において基板を研磨により除去することにより、基板を半導体積層膜から分離することが好ましい。このようにすると、基板の面積が比較的に大きい場合であっても、低コストで半導体積層膜を分離することができる。

## 【0038】

30

本発明の半導体発光素子の製造方法において、工程(a)は、半導体積層膜の一部を形成した後、基板における半導体積層膜の反対側の面から、基板を透過し且つ半導体積層膜に吸収される波長を有する照射光を照射することにより、半導体積層膜の一部の内部に半導体積層膜が分解してなる分解層を形成する工程と、分解層を形成した後、半導体積層膜の一部の上に半導体積層膜の残部を形成する工程とを含むことが好ましい。このようにすると、半導体積層膜と基板とは、該半導体積層膜の一部が分解してなる分解層を介在させて緩やかに結合されるようになる。このため、分解層を形成した後に、半導体積層膜の一部の上に半導体積層膜の残部を形成すると、半導体積層膜の残部に例えばデバイス構造(活性層)を含む場合には、基板と半導体積層膜との間の熱膨張係数の差や格子不整合の影響を受け難くなるので、デバイス構造の結晶性が良好となり、高輝度の半導体発光素子を得ることが可能となる。

## 【0039】

40

基板に照射する照射光はパルス状に発振するレーザ光であることが好ましい。また、照射光は水銀ランプの輝線であることが好ましい。このようにすると、光源にパルス状に発振するレーザ光を用いた場合には、光の出力パワーを著しく増大させることができるために、半導体積層膜の分離が容易となる。また、光源に水銀ランプの輝線を用いた場合には、光の出力パワーではレーザ光に劣るものの、スポットサイズをレーザ光の場合よりも大きくできるため、照射工程におけるスループットが向上する。

## 【0040】

また、照射光は基板の面内をスキャンするように照射することが好ましい。このようにすると、比較的に面積が大きい基板であっても、光源のビームサイズに影響されることなく半導体積層膜から基板を分離することができる。

## 【0041】

50

また、照射光は基板を加熱しながら照射することが好ましい。このようにすると、結晶成長後の冷却時に生じる半導体積層膜と基板との熱膨張係数の差、及び両者の格子不整合に

よる半導体積層膜中に生じるストレスが緩和されるため、基板を分離する際に半導体積層膜に生じるクラックを防止することができる。

【0042】

本発明の半導体発光素子の製造方法は、工程( a )と工程( b )との間に、半導体積層膜の上に誘電体又は半導体からなる積層膜を形成した後、形成した積層膜をパターニングする工程( e )をさらに備え、工程( c )において、第1の電極及び第2の電極のうちのいずれか一方を、パターニングされた積層膜の上に形成し、工程( d )において、金属膜はパターニングされた積層膜の上に形成した電極の上に形成することが好ましい。このようにすると、半導体積層膜から発光される発光光を高効率で反射するミラー構造体を形成することができる。その上、一般に低抵抗化が困難である誘電体又は半導体からなる積層膜により構成されるミラー構造体をパターニングするため、パターニングされたミラー構造体同士の隙間に電極及び金属膜が形成されるので、その隙間から十分な動作電流を確実に注入することができる。

【0043】

この場合に、工程( c )において、基板を半導体積層膜から分離した後に、第1の電極及び第2の電極のうちの他方を、半導体積層膜における積層膜の反対側の面上に形成することが好ましい。

【0044】

本発明の半導体発光素子の製造方法は、工程( a )と工程( b )との間に、半導体積層膜を構成する材料と異なる材料からなり、半導体積層膜を保持する膜状の第1の保持部材を半導体積層膜に貼り合わせる工程( f )と、工程( b )よりも後に、第1の保持部材を半導体積層膜から剥離する工程( g )とをさらに備えていることが好ましい。このようにすると、半導体積層膜の一部に分解層を形成する際ににおける膜中のストレスの緩和過程で、半導体積層膜に発生するクラックを抑制することができる。その結果、基板の面積が比較的大きい場合であっても、半導体積層膜にクラックを発生させることなく基板を分離することができる。

【0045】

この場合に、本発明の半導体発光素子の製造方法は、工程( g )の前に、第1の保持部材とは特性が異なる膜状の第2の保持部材を、半導体積層膜における第1の保持部材の反対側の面上に貼り合わせる工程( h )と、工程( g )よりも後に、第2の保持部材を半導体積層膜から剥離する工程( i )とをさらに備えていることが好ましい。このようにすると、半導体積層膜から基板を分離した後でも、半導体積層膜の任意の面上への電極形成や金属膜に対するパターニングが可能となる。

【0046】

また、この場合に、第1の保持部材又は第2の保持部材は、高分子材料フィルム、半導体からなる単結晶基板又は金属板であることが好ましい。このようにすると、高分子材料フィルム又は金属板の場合には可塑性に優れ、半導体からなる単結晶基板の場合には劈開性に優れるため、基板の分離をより容易に行なえる。

【0047】

この場合の高分子材料フィルムは、その貼り合わせ面に加熱により剥離可能な接着材層が設けられていることが好ましい。このようにすると、高分子材料フィルムを剥離する際に、半導体積層膜上に接着材層が残留するという不具合がなくなるため、半導体積層膜からの高分子材料フィルムの剥離を容易に且つ確実に行なえるようになる。

【0048】

本発明の半導体発光素子の製造方法は、工程( c )よりも前に、半導体積層膜の上に誘電体からなる電流狭窄膜を選択的に形成する工程( j )をさらに備えていることが好ましい。

【0049】

本発明に係る半導体発光素子の実装方法は、単結晶からなる基板上に、互いに異なる導電型を持つ少なくとも2つの半導体層を含む半導体積層膜を形成する工程( a )と、半導体

積層膜を構成する材料と異なる材料からなり、半導体積層膜を保持する膜状の保持部材を半導体積層膜に貼り合わせる工程( b )と、半導体積層膜を保持部材と共にダイシングを行なって、それぞれ個別化された保持部材に保持された状態の複数のチップを作製する工程( c )と、保持部材に保持された各チップに対してダイスボンディングを行なった後、保持部材を各チップから剥離する工程( d )とを備えている。

## 【 0 0 5 0 】

本発明の半導体発光素子の実装方法によると、半導体積層膜の膜厚が例えば数  $\mu\text{m}$  以下と極めて小さい場合でも、膜状の保持部材を半導体積層膜に貼った状態でダイスボンディングを行なえるため、極めて薄い半導体発光素子を実装することが可能となる。

## 【 0 0 5 1 】

本発明の半導体発光素子の実装方法において、保持部材は、高分子材料フィルムであることが好ましい。

## 【 0 0 5 2 】

本発明の半導体発光素子の実装方法において、高分子材料フィルムは、その貼り合わせ面に加熱により剥離可能な接着材層が設けられていることが好ましい。

## 【 0 0 5 3 】

## 【 発明の実施の形態 】

## ( 第 1 の実施形態 )

本発明の第 1 の実施形態について図面を参照しながら説明する。

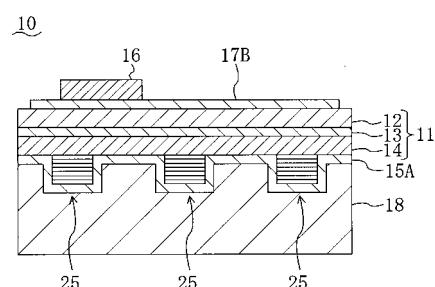

## 【 0 0 5 4 】

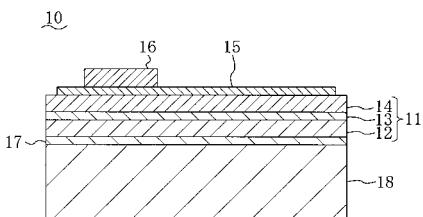

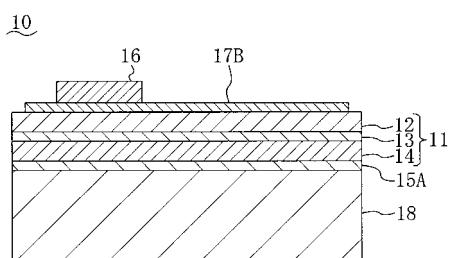

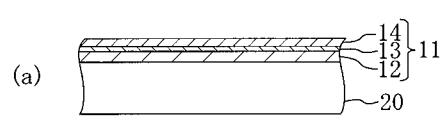

図 1 は本発明の第 1 の実施形態に係る半導体発光素子であって、青色又は緑色等の短波長発光が可能な発光ダイオード素子の断面構成を示している。

## 【 0 0 5 5 】

図 1 に示すように、第 1 の実施形態に係る発光ダイオード素子 10 は、複数の半導体層を含む素子構造体 11 を有している。

## 【 0 0 5 6 】

素子構造体 11 の上にはインジウム( In )と錫( Sn )とを含む酸化物( ITO )からなる透光性を有する p 側電極 15 が形成され、該 p 側電極 15 の上の一部の領域には金( Au )からなるボンディングパッド 16 が形成され、また、素子構造体 11 における p 側電極 15 の反対側の面上にはチタン( Ti )と金( Au )との積層体からなる n 側電極 17 が形成されている。

## 【 0 0 5 7 】

素子構造体 11 は、n 型の窒化アルミニウムガリウム( AlGaN )からなる n 型半導体層 12 と、該 n 型半導体層 12 の上に形成された窒化インジウムガリウム( InGaN )からなる活性層 13 と、該活性層 13 の上に形成された p 型の窒化アルミニウムガリウム( AlGaN )からなる p 型半導体層 14 とから構成されている。ここで、活性層 13 は例えば量子井戸構造を有していても良い。活性層 13 において生成された例えは波長が 470 nm の青色発光光は、Ti / Au からなる n 側電極 17 により反射され、ITO からなる p 側電極 15 を透過して外部に取り出される。

## 【 0 0 5 8 】

第 1 の実施形態の特徴として、n 側電極 17 における n 型半導体層 12 の反対側( 下側 )の Au 層を下地層として、厚さが約 50  $\mu\text{m}$  の金めっきによる金属膜 18 が形成されている。

## 【 0 0 5 9 】

このように、第 1 の実施形態によると、発光ダイオード素子 10 を構成する素子構造体 11 の n 型半導体層 12 に、活性層 13 からの発光光に対する反射率が 90 % 以上となるように設けられた金属からなる n 側電極 17 が形成されている。これにより、活性層 13 から出射される発光光は n 側電極 17 により反射され、透光性を有する p 側電極 15 を通して取り出されるため、光の取り出し効率を大幅に向上することができる。

## 【 0 0 6 0 】

10

20

30

40

50

その上、n側電極17における素子構造体11の反対側の面上には、単結晶からなる基板に代えてAuからなる金属膜18を設けているため、活性層13で生じた熱は金属膜18を介して外部に放熱される。このように、GaN系半導体からなる素子構造体11を成長させる単結晶基板に代えて金属膜18を設けていることにより、素子構造体11の放熱性が格段に向上するため、本実施形態に係る発光ダイオード素子10は高出力動作を確実に行なえるようになる。また、サファイアのような絶縁性基板を有さないため、静電耐圧性も向上する。

## 【0061】

なお、金属膜18の厚さは10μm以上であれば良く、またその材料も金(Au)に限られない。例えば、銅(Cu)又は銀(Ag)のような熱伝導率が高い材料であれば良く、またこれらの合金でもよい。10

## 【0062】

また、金属膜18と接するn側電極17は、チタン(Ti)と金(Au)との積層構造に限られず、金(Au)、白金(Pt)、銅(Cu)、銀(Ag)及びロジウム(Rh)のうちの少なくとも1つからなる単層膜、又はこれらのうちの2つ以上を含む積層構造としても良い。

## 【0063】

また、透光性を有するp側電極15はITOに限られず、ニッケル(Ni)と金(Au)とからなり、併せた厚さが20nm以下の積層体を用いてもよい。

## 【0064】

以下、前記のように構成された発光ダイオード素子10の製造方法について図面を参照しながら説明する。

## 【0065】

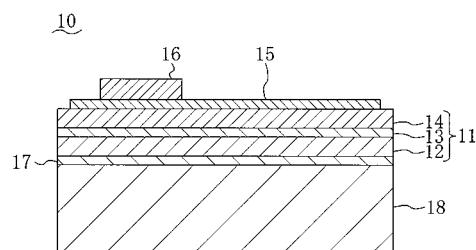

図2(a)～図2(d)及び図3(a)～図3(d)は本発明の第1の実施形態に係る発光ダイオード素子の製造方法の工程順の断面構成を示している。

## 【0066】

まず、図2(a)に示すように、例えば有機金属気相成長(MOCVD)法により、ウエハ状のサファイア(単結晶Al<sub>2</sub>O<sub>3</sub>)からなる基板20の主面上に、n型AlGaNからなるn型半導体層12、InGaNからなる活性層13及びp型AlGaNからなるp型半導体層14を順次成長することにより、n型半導体層12、活性層13及びp型半導体層14を含む素子構造体11を形成する。30

## 【0067】

ここで、[表1]に示すように、素子構造体11は、基板20とn型半導体層(n型クラッド層)12との間にバッファ層及びn型コンタクト層を設け、活性層13を量子井戸構造とし、p型半導体層(p型クラッド層)14の上にp型コンタクト層を設ける構成が好ましい。

## 【0068】

## 【表1】

| 名称                  | 組成                                      | 厚さ     |

|---------------------|-----------------------------------------|--------|

| p型コンタクト層            | p-GaN                                   | 0.5 μm |

| p型クラッド層<br>(p型半導体層) | p-Al <sub>0.1</sub> Ga <sub>0.9</sub> N | 100nm  |

| 活性層                 | In <sub>0.35</sub> Ga <sub>0.65</sub> N | 2nm    |

| n型クラッド層<br>(n型半導体層) | n-Al <sub>0.1</sub> Ga <sub>0.9</sub> N | 100nm  |

| n型コンタクト層            | n-GaN                                   | 3 μm   |

| バッファ層               | GaN                                     | 30nm   |

| 基板                  | サファイア                                   | —      |

10

20

## 【0069】

[表1]において、公知のように、基板20上に形成するGaNからなるバッファ層は、基板温度を比較的に低温の例えば550として、基板20とバッファ層の上に成長するn型コンタクト層等のエピタキシャル層との格子不整合を緩和する。なお、n型半導体層12等のエピタキシャル層の成長時には、基板温度を1020程度に設定する。また、n型ドーパントには、例えばシラン(SiH<sub>4</sub>)を原料とするシリコン(Si)を用い、p型ドーパントには、例えばビスシクロペンタジエニルマグネシウム(Cp<sub>2</sub>Mg)を原料とするマグネシウム(Mg)を用いる。

## 【0070】

続いて、素子構造体11の上に、例えばRFスパッタ法によりITO膜を堆積し、堆積したITO膜をパターニングしてp側電極15を形成する。さらに、形成したp側電極15の上に、例えば電子ビーム蒸着法により、Auからなる電極形成膜を蒸着し、蒸着した電極形成膜に対してp側電極15の一部分を覆うようにパターニングを行なって電極形成膜からボンディングパッド16を形成する。なお、ここでは、電極形成膜の膜厚は500nm以上とすることが好ましい。また、ITO膜と電極形成膜とのパターニングは同時に行なってもよい。

## 【0071】

次に、図2(b)に示すように、p側電極15及びボンディングパッド16を含む素子構造体11の上に、可塑性に優れる膜状の保持部材、例えば厚さが約100μmの高分子フィルムからなる保持膜41を接着する。ここで、保持膜41には、その保持面に加熱により発泡して接着力が低下する接着剤層を設けた、例えばポリエステルからなる高分子フィルムを用いる。このような保持膜41を用いることにより、後工程において、保持膜41を剥離する際に、素子構造体11上に接着剤層が残ってしまい、電気的な接触不良等が発生するという不具合を防止することができる。続いて、基板20に対して素子構造体11の反対側の面から、パルス状に発振する波長が355nmであるYAG(イットリウム、アルミニウム、ガーネット)レーザの第3高調波光を基板20をスキャンするように照射する。照射されたレーザ光は、基板20では吸収されず、素子構造体11、すなわちn型

40

50

半導体層 12 で吸収される。このレーザ光の吸収により、n 型半導体層 12 は局所的に発熱し、該 n 型半導体層 12 はその基板 20 との界面において原子同士の結合が切断され、基板 20 と n 型半導体層 12 との間に金属ガリウム (Ga) を含む熱分解層 (図示せず) が形成される。すなわち、レーザ光を n 型半導体層 12 に照射することにより、基板 20 の上に成長した n 型半導体層 12 は、基板 20 との間で原子間の結合が切断されながらも、熱分解層により基板 20 と接着された状態となる。なお、照射するレーザ光の光源は、YAG レーザの第 3 高調波光に限られず、波長が 248 nm である KrF エキシマレーザ光を用いてもよい。ここで、KrF は、エキシマレーザ装置に含まれるクリプトンとフッ素との混合ガスである。さらに、レーザ光源に代えて、波長が 365 nm である水銀ランプの輝線を用いてもよい。水銀ランプの輝線を用いた場合には、光の出力パワーではレーザ光に劣るもの、スポットサイズをレーザ光よりも大きくできるため、基板 20 の分離工程における照射時間を短縮することができる。

10

## 【0072】

次に、図 2 (c) に示すように、塩酸 (HCl) 等を用いたウエットエッチングによって熱分解層を溶融することにより、素子構造体 11 から基板 20 を分離して除去する。基板 20 の分離方法には、光照射による熱分解層を形成しその熱分解層を溶融して行なう方法以外にも、基板 20 を化学的機械研磨法により基板を除去する方法がある。

## 【0073】

続いて、基板 20 を除去された素子構造体 11 における n 型半導体層 12 の活性層 13 の反対側の面上に、例えば電子ビーム蒸着法により、Ti / Au からなる n 側電極 17 を形成する。続いて、金めっき法により、n 側電極 17 の上に、該 n 側電極 17 の Au 層を下地層として厚さが約 50 μm の金属膜 18 を成膜する。

20

## 【0074】

次に、図 2 (d) に示すように、金属膜 18 及び n 側電極 17 における素子構造体 11 のチップ分割領域と対応する部分を選択的にエッチングして、n 型半導体層 12 におけるチップ分割領域を露出する。第 1 の実施形態においては、基板 20 の分離工程、n 側電極 17 及び金属膜 18 の各成膜工程、及び該 n 側電極 17 及び金属膜 18 に対するエッチング工程は、素子構造体 11 の基板 20 の反対側の面上に保持膜 41 を設けた状態で行なうため、素子構造体 11 の膜厚が例えば 5 μm 程度と極めて薄い構成であっても、何ら不具合を生じることなく実施することができる。

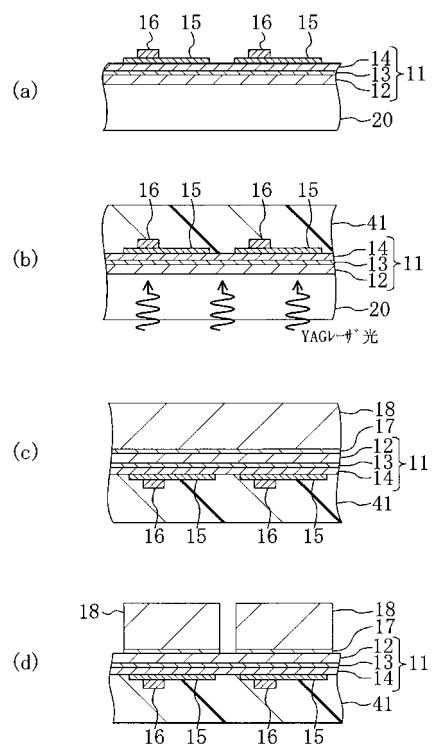

30

## 【0075】

次に、図 3 (a) に示すように、保持膜 41 に保持された素子構造体 11 における金属膜 18 からの露出領域 (ダイシング領域) をダイシングブレード 50 を用いて切断する。このとき、保持膜 41 をも同時に切断する。これにより、図 3 (b) に示すように、ウエハ状態の素子構造体 11 から、n 側電極 17 には比較的厚膜の金属膜 18 が設けられ、p 側電極 15 には保持膜 41 が接着された、例えば 300 μm 角の発光ダイオードチップを得る。

## 【0076】

次に、図 3 (c) に示すように、チップ状に分割された保持膜 41 の上面をコレット 51 により吸着し、鉛 (Pb) 及び錫 (Sn) からなる半田材 21 によりパッケージ 22 の実装位置にボンディングする。

40

## 【0077】

次に、図 3 (d) に示すように、ボンディングの際にチップを例えば 200 度に加熱する。これにより、保持膜 41 には加熱されて発泡する接着剤が塗布されており、加熱により保持膜 41 の接着剤の接着力が弱まるため、コレット 51 によって保持膜 41 は素子構造体 11 から容易に剥がすことができる。

## 【0078】

このように、第 1 の実施形態においては、加熱により剥離が容易となる保持膜 41 を接着した状態でダイスボンディングを行なうため、素子構造体 11 の厚さが約 50 μm 程度のチップであっても、ダイスボンディングを容易に且つ確実に行なうことができる。

50

## 【0079】

なお、金属膜18の少なくとも下部に、例えば融点が約280の金(Au)及び錫(Sn)からなる合金をめっきにより形成すると、半田材21を用いる必要がなくなる。

## 【0080】

以上説明したように、第1の実施形態に係る製造方法によると、高輝度で、放熱性及び静電耐圧に優れ且つ直列抵抗が小さい発光ダイオード素子10を得ることができる。

## 【0081】

## (製造方法の一変形例)

第1の実施形態においては、素子構造体11を作製した後に、レーザ光を照射して基板20と素子構造体11との間に金属ガリウムを含む熱分解層を形成したが、これに限られず、以下のような製造方法を用いてもよい。 10

## 【0082】

具体的には、基板20上にGaN系半導体からなる下地層を成長した後に光照射を行なって、基板20と下地層との間に熱分解層を形成する。続いて、熱分解層が形成された下地層の上に素子構造体11を再成長して形成する。

## 【0083】

このようにすると、素子構造体11は、下地層の上に該下地層と基板20との間に結晶構造を持たない熱分解層が介在した状態で成長するため、GaN系半導体からなる下地層及び素子構造体11は、基板20との熱膨張係数の差の影響を受けにくくなる。その結果、素子構造体11における結晶性が向上すると共に、クラック及び結晶欠陥等の発生が低減する。 20

## 【0084】

なお、基板20を下地層から分離して除去するには、下地層に対して再度レーザ光等を照射するか、又は熱分解層を例えばHCl等によりエッティングしてもよい。

## 【0085】

## (第2の実施形態)

以下、本発明の第2の実施形態について図面を参照しながら説明する。

## 【0086】

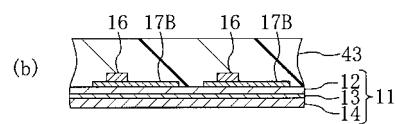

図4は本発明の第2の実施形態に係る半導体発光素子であって、青色又は緑色等の短波長発光が可能な発光ダイオード素子の断面構成を示している。図4において、図1に示す構成部材と同一の構成部材には同一の符号を付すことにより説明を省略する。 30

## 【0087】

図4に示すように、第2の実施形態に係る発光ダイオード素子10は、素子構造体11を構成するn型半導体層12における活性層13の反対側(上側)の面上に、チタン(Ti)とアルミニウム(Al)との積層体からなり、ポンディングパッドを兼ねるn側電極17Aが選択的に形成されている。p型半導体層14における活性層13の反対側(下側)には、白金(Pt)と金(Au)との積層体からなり、活性層13からの発光光に対する反射率が90%以上となるように設けられたp側電極15Aが形成されている。また、p側電極15Aにおける外側のAu層を下地層として、厚さが約50μmの金めっきされた金属膜18が形成されている。 40

## 【0088】

第2の実施形態の特徴として、素子構造体11の周縁部におけるp型半導体層14とp側電極15Aとの間には、例えば酸化シリコン(SiO<sub>2</sub>)からなる電流狭窄膜23を設けている。これにより、素子構造体11の側端面を通ってリークするリーク電流を低減できるため、発光素子の発光効率が向上する。

## 【0089】

このように、第2の実施形態によると、発光ダイオード素子10を構成する素子構造体11の下側に、活性層13からの発光光に対する反射率が90%以上となるように設けられた金属からなるp側電極15Aが形成されている。これにより、活性層13から出射される発光光はp側電極15Aにより反射され、n型半導体層12におけるn側電極17Aが 50

設けられていない部分を通して取り出されるため、光の取り出し効率を大幅に向上することができる。

#### 【0090】

その上、p側電極15Aにおける素子構造体11の反対側（下側）の面上には、単結晶からなる基板に代えて金属膜18を設けているため、活性層13で生じた熱は金属膜18を介して外部に放熱される。このように、GaN系半導体からなる素子構造体11を成長させる単結晶基板に代えて金属膜18を設けていることにより、放熱性が格段に向上するため、本実施形態に係る発光ダイオード素子10の高出力動作が可能となる。また、サファイアのような絶縁性基板を有さないため、静電耐圧性も向上する。

#### 【0091】

なお、金属膜18と接するp側電極15Aは、白金（Pt）と金（Au）との積層構造に限られず、金（Au）、白金（Pt）、銅（Cu）、銀（Ag）及びロジウム（Rh）のうちの少なくとも1つからなる単層膜、又はこれらのうちの2つ以上を含む積層構造としても良い。

#### 【0092】

以下、前記のように構成された発光ダイオード素子10の製造方法について図面を参照しながら説明する。

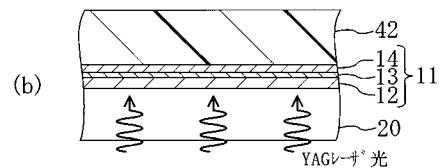

#### 【0093】

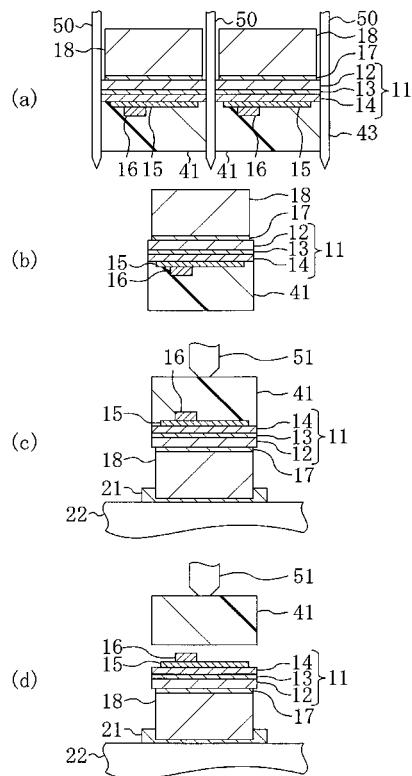

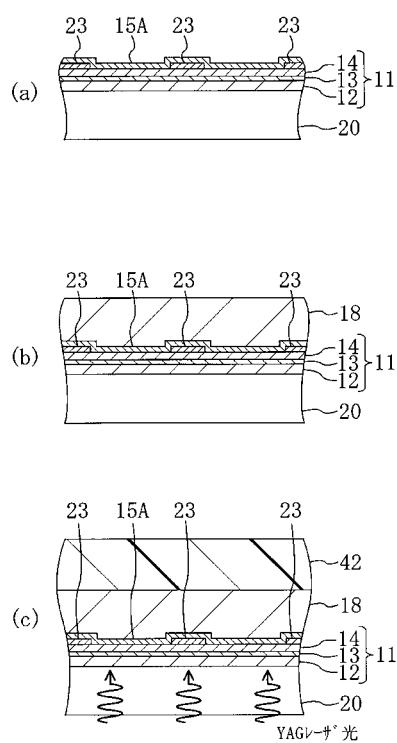

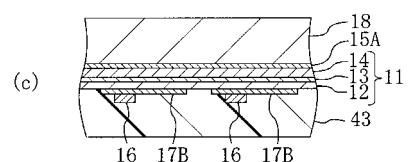

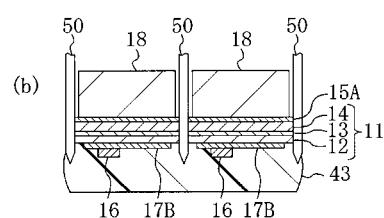

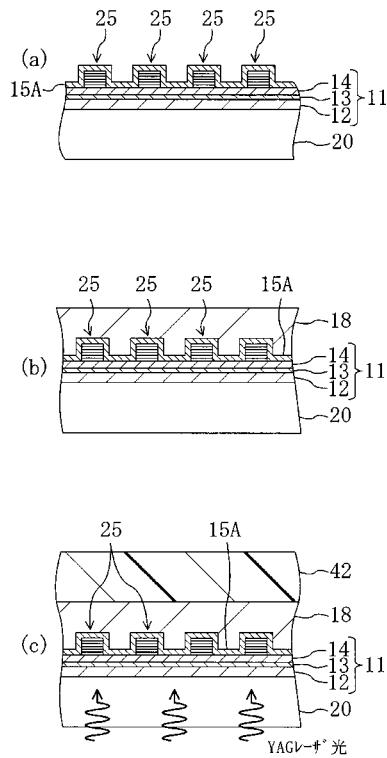

図5(a)～図5(c)乃至図7(a)～図7(c)は本発明の第2の実施形態に係る発光ダイオード素子の製造方法の工程順の断面構成を示している。

#### 【0094】

まず、図5(a)に示すように、第1の実施形態と同様に、MOCVD法により、ウエハ状のサファイアからなる基板20の主面上に、n型AlGaNからなるn型半導体層12、InGaNからなる活性層13及びp型AlGaNからなるp型半導体層14を順次成長することにより、n型半導体層12、活性層13及びp型半導体層14を含む素子構造体11を形成する。

#### 【0095】

続いて、素子構造体11、すなわちp型半導体層14の上に、例えば気相堆積(CVD)法により、膜厚が約300nmの酸化シリコンからなる電流狭窄形成膜を堆積する。続いて、堆積した電流狭窄形成膜に対して例えばフッ化水素酸(HF)を用いたウエットエッチングを行なって、電流狭窄形成膜から素子構造体11の発光領域を露出する開口部を持つ複数の電流狭窄膜23を形成する。その後、電子ビーム蒸着法により、各電流狭窄膜23及びp型半導体層14における電流狭窄膜23からの露出領域を含む全面にわたって、厚さが約50nmのPt層と厚さが約200nmのAu層とからなるp側電極15Aを形成する。

#### 【0096】

次に、図5(b)に示すように、金めっき法により、p側電極15Aの上に、該p側電極15AのAu層を下地層として厚さが約50μmの金属膜18を成膜する。

#### 【0097】

次に、図5(c)に示すように、金属膜18の上に、可塑性に優れる膜状の保持部材、例えば厚さが約100μmの高分子フィルムからなる第1の保持膜42を接着する。ここで、第1の保持膜42には、その保持面に約120°の加熱により発泡して接着力が低下する接着剤層を設けた、例えばポリエチレンからなる高分子フィルムを用いる。続いて、基板20に対して素子構造体11の反対側の面から、パルス状に発振する波長が355nmであるYAGレーザの第3高調波光を基板20をスキャンするように照射する。前述したように、照射されたレーザ光は、基板20では吸収されず、素子構造体11、すなわちn型半導体層12で吸収される。このレーザ光の吸収により、n型半導体層12は局所的に発熱し、該n型半導体層12はその基板20との界面において原子同士の結合が切断されて、基板20とn型半導体層12との間に金属ガリウムを含む熱分解層(図示せず)が形成される。なお、照射するレーザ光の光源には、YAGレーザの第3高調波光に代えて、

10

20

30

40

50

波長が 248 nm である KrF エキシマレーザ光を用いてもよい。さらには、レーザ光源に代えて、波長が 365 nm である水銀ランプの輝線を用いてもよい。

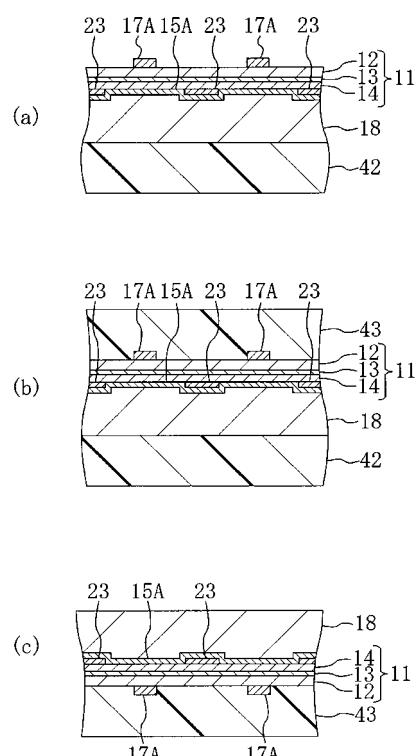

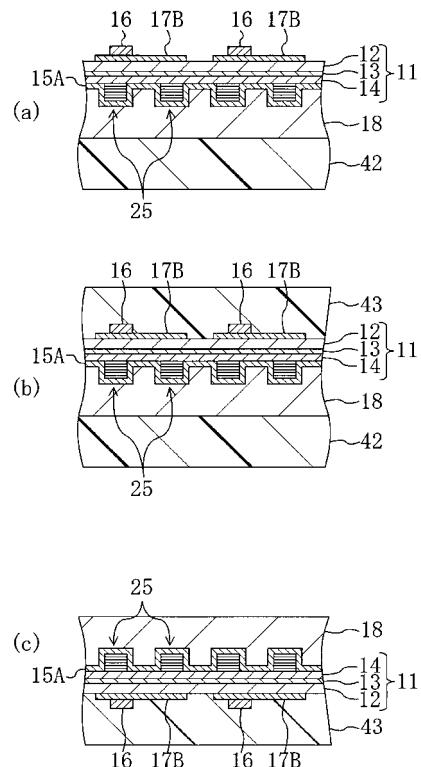

#### 【0098】

次に、図 6 (a) に示すように、塩酸等を用いたウェットエッティングによって熱分解層を溶融することにより、素子構造体 11 から基板 20 を分離して除去する。続いて、基板 20 を除去された素子構造体 11 における n 型半導体層 12 の活性層 13 の反対側の面上に、例えば電子ビーム蒸着法により、膜厚が約 50 nm の Ti と膜厚が約 800 nm の Al との積層膜を蒸着し、蒸着した積層膜に対して、素子構造体 11 の発光領域を部分的に覆うようにパターニングを行なって、積層膜からボンディングパッドとしても機能する n 側電極 17A を形成する。

#### 【0099】

次に、図 6 (b) に示すように、n 側電極 17A を含め n 型半導体層 12 の上に、例えば厚さが約 100 μm の高分子フィルムからなる第 2 の保持膜 43 を接着する。第 2 の保持膜 43 には、その保持面に約 170° の加熱により発泡して接着力が低下する接着剤層を設けた、例えばポリエチレンからなる高分子フィルムを用いる。

#### 【0100】

次に、第 1 の保持膜 42 及び第 2 の保持膜 43 により保持された素子構造体 11 を約 120° に加熱する。この約 120° の加熱により、第 1 の保持膜 42 に設けられた接着剤層が発泡して金属膜 18 との間の接着力が低下するため、図 6 (c) に示すように、第 1 の保持膜 42 は金属膜 18 から容易に分離される。このとき、金属膜 18 の表面には第 1 の保持膜 42 の接着剤が残るおそれはない。

#### 【0101】

次に、図 7 (a) に示すように、金属膜 18 における素子構造体 11 のチップ分割領域と対応する部分、すなわち電流狭窄膜 23 の上側部分を選択的にエッティングして、p 側電極 15A におけるチップ分割領域を露出する。第 2 の実施形態においても、基板 20 の分離工程、n 側電極 17A の各成膜工程は素子構造体 11 に第 1 の保持膜 42 を設けた状態で行ない、金属膜 18 に対するエッティング工程は、素子構造体 11 に第 2 の保持膜 43 を設けた状態で行なうため、素子構造体 11 の膜厚が例えば 5 μm 程度と極めて薄い構造であっても、何ら不具合を生じることなく実施することができる。

#### 【0102】

次に、図 7 (b) に示すように、第 2 の保持膜 43 に保持された p 側電極 15A における金属膜 18 からの露出領域（ダイシング領域）及びその下方をダイシングブレード 50 を用いて切断する。これにより、各素子構造体 11 は、平面サイズが例えば 300 μm 角の発光ダイオードチップを得る。このとき、第 2 の保持膜 43 に対してはその途中までを切断する。

#### 【0103】

次に、図 7 (c) に示すように、第 2 の保持膜 43 を約 170° に加熱することにより、第 2 の保持膜 43 に設けられた接着剤層が発泡して各チップとの間の接着力が低下するため、第 2 の保持膜 43 から各チップが容易に剥離する。その後は、後工程であるダイスボンディング等の組み立て工程で実装される。

#### 【0104】

以上説明したように、第 2 の実施形態に係る製造方法によると、高輝度で、放熱性及び静電耐圧に優れ且つ直列抵抗が小さい発光ダイオード素子 10 を得ることができる。

#### 【0105】

##### （第 2 の実施形態の一変形例）

以下、本発明の第 2 の実施形態の一変形例について図面を参照しながら説明する。

#### 【0106】

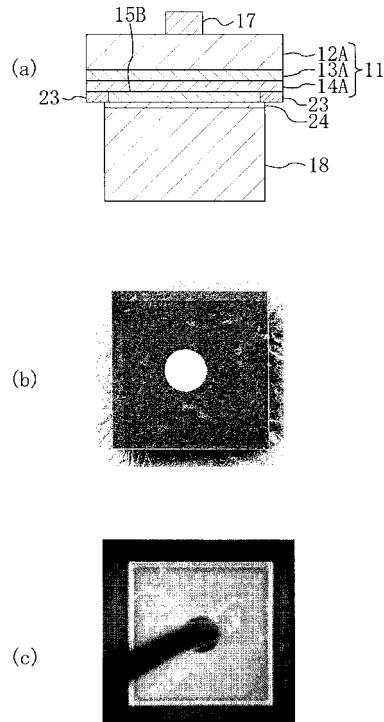

図 8 (a) ~ 図 8 (c) は本発明の第 2 の実施形態の一変形例に係る発光ダイオード素子であって、図 8 (a) は断面構成を示し、図 8 (b) はチップ表面の走査型電子顕微鏡（Scanning Electron Microscope : SEM）による顕微鏡写真

を示し、図 8 (c) は発光状態にあるチップ表面の写真を示している。また、図 8 (a)において、図 4 に示す構成部材と同一の構成部材には同一の符号を付すことにより説明を省略する。

#### 【0107】

本変形例は試作例であって、図 8 (a) に示すように、素子構造体 11 の n 型半導体層 12 A には n 型 GaN を用い、活性層 13 A には InGaN からなる多重量子井戸構造を用い、p 型半導体層 14 A には p 型 GaN を用いている。ここで、チップの平面サイズは 300 μm 角である。

#### 【0108】

n 型半導体層 12 A の上には、発光領域の中央部分に Ti / Au の積層体からなる n 側電極 17 が設けられている。p 側電極 15 B には Pt を用い、該 p 側電極 15 B の素子構造体 11 の反対側の面上には、Ti / Au からなるめっき下地層 24 を設けている。

#### 【0109】

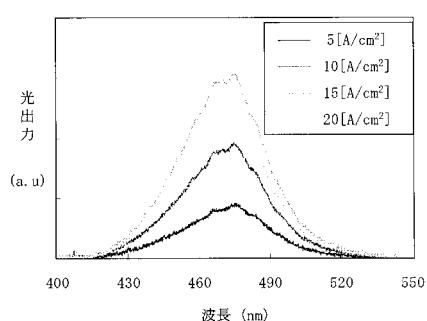

図 9 に本変形例に係る発光ダイオード素子 10 の発光スペクトルの測定結果を示す。図 9 のグラフに示すように、動作電流を増加させるにつれて、活性層 13 A に対して垂直な方向に共振するいわゆる垂直共振器作用による複数のピークが現われる。

#### 【0110】

##### (第 3 の実施形態)

以下、本発明の第 3 の実施形態について図面を参照しながら説明する。

#### 【0111】

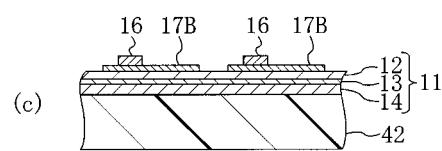

図 10 は本発明の第 3 の実施形態に係る半導体発光素子であって、青色又は緑色等の短波長発光が可能な発光ダイオード素子の断面構成を示している。図 10 において、図 4 に示す構成部材と同一の構成部材には同一の符号を付すことにより説明を省略する。

#### 【0112】

第 3 の実施形態に係る発光ダイオード素子を構成する素子構造体 11 は、n 型半導体層 12 における活性層 13 の反対側の面上に、例えばITO からなり透光性を有する n 側電極 17 B が設けられ、該 n 側電極 17 B 上の一部の領域には Au からなるボンディングパッド 16 が形成されている。

#### 【0113】

ここで、活性層 13 は例えば量子井戸構造を有していても良い。活性層 13 において生成された例えば波長が 470 nm の青色発光光は、Pt / Au からなる p 側電極 15 A により反射され、ITO からなる n 側電極 17 B を透過して外部に取り出される。

#### 【0114】

このように、第 3 の実施形態によると、発光ダイオード素子 10 を構成する素子構造体 11 の下側に、活性層 13 からの発光光に対する反射率が 90 % 以上となるように設けられた金属からなる p 側電極 15 A が形成されている。これにより、活性層 13 から出射される発光光は p 側電極 15 A により反射され、n 型半導体層 12 に設けられた透光性を持つ n 側電極 17 B を通して取り出されるため、光の取り出し効率を大幅に向上することができる。

#### 【0115】

その上、p 側電極 15 A における素子構造体 11 の反対側（下側）の面上には、単結晶からなる基板に代えて金属膜 18 を設けているため、活性層 13 で生じた熱は金属膜 18 を介して外部に放熱される。このように、GaN 系半導体からなる素子構造体 11 を成長させる単結晶基板に代えて金属膜 18 を設けていることにより、放熱性が格段に向上するため、本実施形態に係る発光ダイオード素子 10 の高出力動作が可能となる。また、サファイアのような絶縁性基板を有さないため、静電耐圧性も向上する。

#### 【0116】

以下、前記のように構成された発光ダイオード素子 10 の製造方法について図面を参照しながら説明する。

#### 【0117】

10

20

30

40

50

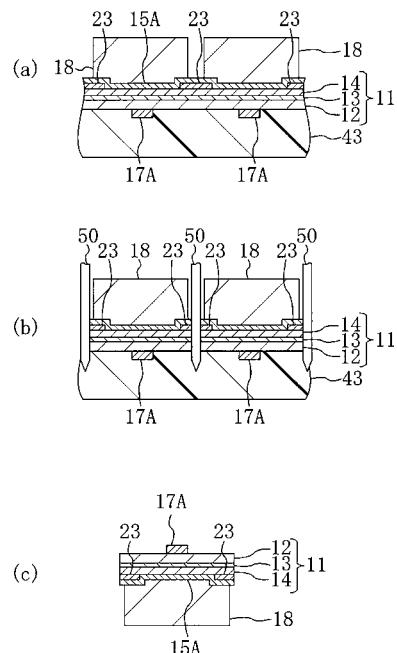

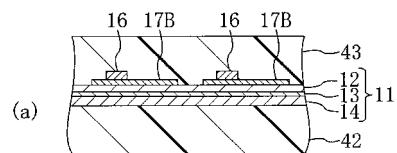

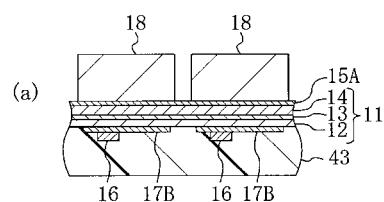

図11(a)～図11(c)乃至図13(a)～図13(c)は本発明の第3の実施形態に係る発光ダイオード素子の製造方法の工程順の断面構成を示している。

#### 【0118】

まず、図11(a)に示すように、MOCVD法により、ウエハ状のサファイアからなる基板20の主面上に、n型AlGaNからなるn型半導体層12、InGaNからなる活性層13及びp型AlGaNからなるp型半導体層14を順次成長することにより、n型半導体層12、活性層13及びp型半導体層14を含む素子構造体11を形成する。

#### 【0119】

次に、図11(b)に示すように、素子構造体の11のp型半導体層14の上に、例えば厚さが約100μmの高分子フィルムからなる第1の保持膜42を接着する。ここで、第1の保持膜42には、その保持面に約120°の加熱により発泡して接着力が低下する接着剤層を設けた、例えばポリエステルからなる高分子フィルムを用いる。続いて、基板20に対して素子構造体11の反対側の面から、パルス状に発振する波長が355nmであるYAGレーザの第3高調波光を基板20をスキャンするように照射する。前述したように、照射されたレーザ光は、基板20では吸収されず、素子構造体11、すなわちn型半導体層12で吸収される。このレーザ光の吸収により、n型半導体層12は局所的に発熱し、該n型半導体層12はその基板20との界面において原子同士の結合が切断されて、基板20とn型半導体層12との間に金属ガリウムを含む熱分解層(図示せず)が形成される。なお、照射するレーザ光の光源には、YAGレーザの第3高調波光に代えて、波長が248nmであるKrFエキシマレーザ光を用いてもよい。さらには、レーザ光源に代えて、波長が365nmである水銀ランプの輝線を用いてもよい。

#### 【0120】

次に、図11(c)に示すように、塩酸等を用いたウェットエッチングによって熱分解層を溶融することにより、素子構造体11から基板20を分離して除去する。続いて、基板20を除去された素子構造体11におけるn型半導体層12の活性層13の反対側の面上に、例えばRFスパッタ法によりITO膜を堆積し、堆積したITO膜をパターニングしてn側電極17Bを形成する。さらに、形成したn側電極17Bの上に、例えば電子ビーム蒸着法により、Auからなる電極形成膜を蒸着し、蒸着した電極形成膜に対してn側電極17B上的一部分を覆うようにパターニングを行なって、電極形成膜からボンディングパッド16を形成する。なお、電極形成膜の膜厚は500nm以上とすることが好ましい。また、ITO膜と電極形成膜とのパターニングは同時に行なってもよい。

#### 【0121】

次に、図12(a)に示すように、ボンディングパッド16及びn側電極17Bを含むn型半導体層12の上に、例えば厚さが約100μmの高分子フィルムからなる第2の保持膜43を接着する。第2の保持膜43には、その保持面に約170°の加熱により発泡して接着力が低下する接着剤層を設けた、例えばポリエステルからなる高分子フィルムを用いる。

#### 【0122】

次に、第1の保持膜42及び第2の保持膜43により保持された素子構造体11を約120°に加熱する。この約120°の加熱により、第1の保持膜42に設けられた接着剤層が発泡して素子構造体11のp型半導体層14との間の接着力が低下するため、図12(b)に示すように、第1の保持膜42はp型半導体層14から容易に分離される。このとき、p型半導体層14の表面には第1の保持膜42の接着剤が残るおそれはない。

#### 【0123】

次に、図12(c)に示すように、電子ビーム蒸着法により、p型半導体層14の上に全面にわたって、厚さが約50nmのPt層と厚さが約200nmのAu層とからなるp側電極15Aを形成する。続いて、金めっき法により、p側電極15Aの上に、該p側電極15AのAu層を下地層として厚さが約50μmの金属膜18を成膜する。

#### 【0124】

次に、図13(a)に示すように、金属膜18における素子構造体11のチップ分割領域

10

20

30

40

50

と対応する部分を選択的にエッティングして、p 側電極 15A におけるチップ分割領域を露出する。第3の実施形態においても、基板 20 の分離工程、n 側電極 17B 及びボンディングパッド 16 の各成膜工程は素子構造体 11 に第1の保持膜 42 を設けた状態で行ない、p 側電極 15A、金属膜 18 の各成膜工程及び金属膜 18 に対するエッティング工程は、素子構造体 11 に第2の保持膜 43 を設けた状態で行なうため、素子構造体 11 の膜厚が例えば 5 μm 程度と極めて薄い構造であっても、何ら不具合を生じることなく実施することができる。

## 【0125】

次に、図 13 (b) に示すように、第2の保持膜 43 に保持された p 側電極 15A における金属膜 18 からの露出領域（ダイシング領域）及びその下方をダイシングブレード 50 を用いて切断する。これにより、各素子構造体 11 は、平面サイズが例えば 300 μm 角の発光ダイオードチップを得る。このとき、第2の保持膜 43 に対してはその途中までを切断する。

## 【0126】

次に、図 13 (c) に示すように、第2の保持膜 43 を約 170 °C に加熱することにより、第2の保持膜 43 に設けられた接着剤層が発泡して各チップとの間の接着力が低下するため、第2の保持膜 43 から各チップが容易に剥離する。その後は、後工程であるダイスボンディング等の組み立て工程で実装される。

## 【0127】

以上説明したように、第3の実施形態に係る製造方法によると、高輝度で、放熱性及び静電耐圧に優れ且つ直列抵抗が小さい発光ダイオード素子 10 を得ることができる。

## 【0128】

## (第4の実施形態)

以下、本発明の第4の実施形態について図面を参照しながら説明する。

## 【0129】

図 14 は本発明の第4の実施形態に係る半導体発光素子であって、青色又は緑色等の短波長発光が可能な発光ダイオード素子の断面構成を示している。図 14 において、図 10 に示す構成部材と同一の構成部材には同一の符号を付すことにより説明を省略する。

## 【0130】

図 14 に示すように、第4の実施形態は、素子構造体 11 における p 型半導体層 14 と p 側電極 15A との間に、それぞれが、例えば酸化シリコン (SiO<sub>2</sub>) からなる第1誘電体層と酸化シリコンよりも屈折率が大きい酸化タンタル (Ta<sub>2</sub>O<sub>5</sub>) からなる第2誘電体層とが交互に積層されてなる複数のミラー構造体 25 が互いに間隔をおいて形成されていることを特徴とする。

## 【0131】

各ミラー構造体 25 は、第1誘電体層の厚さを 80 nm とし、第2誘電体層の厚さを 53 nm とし、これら第1誘電体層及び第2誘電体層を 1 周期としてその 10 周期分が積層されている。ここで、各誘電体層の厚さは、発光波長を 470 nm とし、光学波長を λ としたときに、その λ / 4 が反射率の最大となるように設計されている。

## 【0132】

ここで、活性層 13 は例えば量子井戸構造を有していても良い。活性層 13 において生成された例えば波長が 470 nm の青色発光光は、Pt / Au からなる p 側電極 15A 及び各ミラー構造体 25 により反射され、ITO からなる n 側電極 17B を透過して外部に取り出される。

## 【0133】

このように、第4の実施形態によると、発光ダイオード素子 10 を構成する素子構造体 11 の下側に、活性層 13 からの発光光に対する反射率が 90 % 以上となるように設けられた金属からなる p 側電極 15A と、該発光光に対する反射率が 90 % 以上の高反射率を有する誘電体からなるミラー構造体 25 が形成されている。これにより、活性層 13 から出射される発光光は p 側電極 15A 及びミラー構造体 25 により反射され、n 型半導体層 1

10

20

30

40

50

2に設けられた透光性を持つn側電極17Bを通して取り出されるため、光の取り出し効率を大幅に向ふことができる。

【0134】

その上、p側電極15Aにおける素子構造体11の反対側（下側）の面上には、単結晶からなる基板に代えて金属膜18を設けているため、活性層13で生じた熱は金属膜18を介して外部に放熱される。このように、GaN系半導体からなる素子構造体11を成長させる単結晶基板に代えて金属膜18を設けていることにより、放熱性が格段に向ふため、本実施形態に係る発光ダイオード素子10の高出力動作が可能となる。また、サファイアのような絶縁性基板を有さないため、静電耐圧性も向上する。

【0135】

なお、第4の実施形態においては、ミラー構造体25に積層した誘電体膜を用いたが、これに限らず、例えばエピタキシャル成長したGaN系半導体からなる積層膜を用い、互いに隣接する膜同士のアルミニウム（Al）やインジウム（In）の組成を変えて、互いに屈折率差を生じさせることにより、活性層13からの発光光を高い反射率で反射する構成としても良い。

【0136】

以下、前記のように構成された発光ダイオード素子10の製造方法について図面を参照しながら説明する。

【0137】

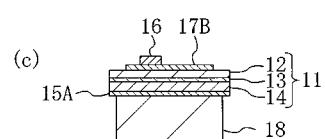

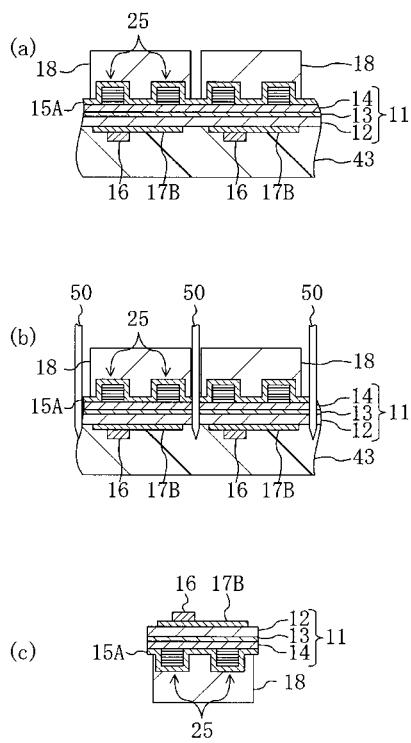

図15（a）～図15（c）乃至図17（a）～図17（c）は本発明の第4の実施形態に係る発光ダイオード素子の製造方法の工程順の断面構成を示している。

【0138】

まず、図15（a）に示すように、MOCVD法により、ウエハ状のサファイアからなる基板20の主面上に、n型AlGaNからなるn型半導体層12、InGaNからなる活性層13及びp型AlGaNからなるp型半導体層14を順次成長することにより、n型半導体層12、活性層13及びp型半導体層14を含む素子構造体11を形成する。

【0139】

続いて、素子構造体11、すなわちp型半導体層14の上に、例えばRFスパッタ法により、厚さが80nmのSiO<sub>2</sub>からなる第1誘電体層と厚さが53nmのTa<sub>2</sub>O<sub>5</sub>からなる第2誘電体層とを1周期とし、その10周期分からなる誘電体積層膜を堆積する。続いて、堆積した誘電体積層膜に対して例えばフッ化水素酸（HF）を用いたウェットエッチングを行なうことにより、誘電体積層膜から互いに間隔をおいた複数のミラー構造体25を形成する。その後、電子ビーム蒸着法により、各ミラー構造体25及びp型半導体層14におけるミラー構造体25からの露出領域を含む全面にわたって、厚さが約50nmのPt層と厚さが約200nmのAu層とからなるp側電極15Aを形成する。

【0140】

次に、図15（b）に示すように、金めっき法により、p側電極15Aの上に、該p側電極15AのAu層を下地層として厚さが約50μmの金属膜18を成膜する。

【0141】

次に、図15（c）に示すように、金属膜18の上に、例えば厚さが約100μmの高分子フィルムからなる第1の保持膜42を接着する。ここで、第1の保持膜42には、その保持面に約120°の加熱により発泡して接着力が低下する接着剤層を設けた、例えばポリエチレンからなる高分子フィルムを用いる。続いて、基板20に対して素子構造体11の反対側の面から、パルス状に発振する波長が355nmであるYAGレーザの第3高調波光を基板20をスキャンするように照射する。前述したように、照射されたレーザ光は、基板20では吸収されず、素子構造体11、すなわちn型半導体層12で吸収される。このレーザ光の吸収により、n型半導体層12は局所的に発熱し、該n型半導体層12はその基板20との界面において原子同士の結合が切断されて、基板20とn型半導体層12との間に金属ガリウムを含む熱分解層（図示せず）が形成される。なお、照射するレーザ光の光源には、YAGレーザの第3高調波光に代えて、波長が248nmであるKrF

エキシマレーザ光を用いてもよい。さらには、レーザ光源に代えて、波長が365nmである水銀ランプの輝線を用いてもよい。

#### 【0142】

次に、図16(a)に示すように、塩酸等を用いたウエットエッティングによって熱分解層を溶融することにより、素子構造体11から基板20を分離して除去する。続いて、基板20を除去された素子構造体11におけるn型半導体層12の活性層13の反対側の面上に、例えばRFスパッタ法によりITO膜を堆積し、堆積したITO膜をパターニングしてn側電極17Bを形成する。さらに、形成したn側電極17Bの上に、例えば電子ビーム蒸着法により、Auからなる電極形成膜を蒸着し、蒸着した電極形成膜に対してn側電極17B上的一部分を覆うようにパターニングを行なって、電極形成膜からボンディングパッド16を形成する。なお、電極形成膜の膜厚は500nm以上、例えば約800nmとすることにより、ボンディングパッド16にワイヤボンディングが確実に実施されるようとする。また、ITO膜と電極形成膜とのパターニングは同時に行なってもよい。

#### 【0143】

次に、図16(b)に示すように、ボンディングパッド16及びn側電極17Bを含めn型半導体層12の上に、例えば厚さが約100μmの高分子フィルムからなる第2の保持膜43を接着する。第2の保持膜43には、その保持面に約170°の加熱により発泡して接着力が低下する接着剤層を設けた、例えばポリエステルからなる高分子フィルムを用いる。

#### 【0144】

次に、第1の保持膜42及び第2の保持膜43により保持された素子構造体11を約120°に加熱する。この約120°の加熱により、第1の保持膜42に設けられた接着剤層が発泡して金属膜18との間の接着力が低下するため、図16(c)に示すように、第1の保持膜42は金属層18から容易に分離される。このとき、金属層18の表面には第1の保持膜42の接着剤が残るおそれはない。

#### 【0145】

次に、図17(a)に示すように、金属膜18における素子構造体11のチップ分割領域と対応する部分を選択的にエッティングして、p側電極15Aにおけるチップ分割領域を露出する。第4の実施形態においても、基板20の分離工程、n側電極17B及びボンディングパッド16の各成膜工程は素子構造体11に第1の保持膜42を設けた状態で行ない、p側電極15A、金属膜18の各成膜工程及び金属膜18に対するエッティング工程は、素子構造体11に第2の保持膜43を設けた状態で行なうため、素子構造体11の膜厚が例えば5μm程度と極めて薄い構造であっても、何ら不具合を生じることなく実施することができる。

#### 【0146】

次に、図17(b)に示すように、第2の保持膜43に保持されたp側電極15Aにおける金属膜18からの露出領域(ダイシング領域)及びその下方をダイシングブレード50を用いて切断する。これにより、各素子構造体11は、平面サイズが例えば300μm角の発光ダイオードチップを得る。このとき、第2の保持膜43に対してはその途中までを切断する。

#### 【0147】

次に、図17(c)に示すように、第2の保持膜43を約170°に加熱することにより、第2の保持膜43に設けられた接着剤層が発泡して各チップとの間の接着力が低下するため、第2の保持膜43から各チップが容易に剥離する。その後は、後工程であるダイスボンディング等の組み立て工程で実装される。

#### 【0148】

以上説明したように、第4の実施形態に係る製造方法によると、高輝度で、放熱性及び静電耐圧に優れ且つ直列抵抗が小さい発光ダイオード素子10を得ることができる。

#### 【0149】

なお、ミラー構造体25は、酸化シリコン(SiO<sub>2</sub>)と酸化タンタル(Ta<sub>2</sub>O<sub>5</sub>)

10

20

30

40

50

との積層構造に限られず、第2誘電体層を構成する高屈折率材料である酸化タンタルに代えて、酸化チタン( $TiO_2$ )、酸化ニオブ( $Nb_2O_5$ )又は酸化ハフニウム( $HfO_2$ )を用いてもよい。

#### 【0150】

また、誘電体からなる積層膜に代えて、窒化アルミニウムガリウムインジウム( $Al_xGa_yIn_{1-x-y}N$ ) (但し、 $0 < x, y < 1, 0 < x+y < 1$ である。)の組成を代えることにより高反射率を有するミラー構造を形成する場合には、図15(a)に示す素子構造体11の結晶成長に連続してエピタキシャル成長により成膜できるため、誘電体を成膜する成膜装置を用いる必要がなくなる。なお、成膜した半導体膜から複数のミラー構造体25を得るパターニング工程には、例えば塩素( $Cl_2$ )ガスを用いた反応性イオンエッチング(Reactive Ion Etching: RIE)法を用いれば良い。10

#### 【0151】

なお、第1～第4の実施形態において、基板20の正面の面方位は特に限定されず、例えばサファイアの場合には、典型的な(0001)面や、さらには典型的な面からわずかにずれた面方位(オフオリエンテーション)を持たせてもよい。

#### 【0152】

また、基板20上に成長する素子構造体11の結晶成長法は、MOCVD法に限られず、例えば、分子線エピタキシャル成長(MBE)法又はハイドライド気相成長(HVPE)法でもよい。また、これらの3つの成長法を各半導体層に応じて適宜使い分けてよい。20

#### 【0153】

また、GaN系半導体からなる素子構造体11は、照射光を吸収する層が素子構造体11に含まれていれば良く、必ずしも照射光を吸収する層が基板20と接している必要はない。また、照射光を吸収する半導体層の組成は、例えばAlGaN又はInGaN等の任意の組成を持つII-V族窒化物半導体であればよい。

#### 【0154】

また、基板20と素子構造体11との間に、InGaN又はZnOのように、GaNよりも禁制帯幅が小さい光吸収層を設けてよい。このようにすると、照射光の吸収が光吸収層により促進されるため、低出力の照射光でも光吸収層が分解される。

#### 【0155】

また、レーザ光等は、基板20を保持膜41等の接着力が低下しない程度に加熱しながら照射してもよい。このようにすると、基板20と素子構造体11との間の熱膨張係数の差によるストレスを緩和しながら素子構造体11の半導体層を熱分解できるため、素子構造体11に発生するクラックを防止することができる。30

#### 【0156】

さらには、光照射工程の前か後に、素子構造体11の上に基板20及び素子構造体11との扱いを容易とするように、高分子材料フィルムに代えて、例えばシリコン(Si)、ヒ化ガリウム(GaAs)、リン化インジウム(InP)、リン化ガリウム(GaP)等の半導体からなる保持基板、又は銅(Cu)等の金属からなる保持基板を貼り合わせ、さらには除去してもよい。

#### 【0157】

また、第2～第4の実施形態においても、第1の実施形態の一変形例と同様に、基板20と下地層との間に熱分解層を形成した後に、素子構造体11を再成長してもよい。

#### 【0158】

また、第1、第3及び第4の実施形態においても、第2の実施形態と同様に、チップの周縁部に電流狭窄膜を設けても良い。

#### 【0159】

#### 【発明の効果】

本発明に係る半導体発光素子及びその製造方法によると、素子構造を含む半導体積層膜が成長した基板を除去し、代わりに、比較的に厚膜の金属膜を設けるため、基板が残された40

状態と比べて該基板による発光光の吸収を抑制できる。その結果、半導体積層膜における金属膜の反対側の面からより多くの発光光を取り出すことが可能となる。また、基板を除去して金属膜を設けるため、直列抵抗を低減できる上に、放熱性が大幅に改善され且つ静電耐圧が大きくなる。

#### 【0160】

本発明に係る半導体発光素子の実装方法によると、半導体積層膜の膜厚が例えば数  $\mu\text{m}$  以下と極めて小さい場合でも、膜状の保持部材を半導体積層膜に貼った状態でダイスボンディングを行なえるため、極めて薄い半導体発光素子を実装することが可能となる。

#### 【図面の簡単な説明】

【図1】本発明の第1の実施形態に係る半導体発光素子を示す構成断面図である。 10

【図2】(a)～(d)は本発明の第1の実施形態に係る半導体発光素子の製造方法を示す工程順の構成断面図である。

【図3】(a)～(d)は本発明の第1の実施形態に係る半導体発光素子の製造方法を示す工程順の構成断面図である。

【図4】本発明の第2の実施形態に係る半導体発光素子を示す構成断面図である。

【図5】(a)～(c)は本発明の第2の実施形態に係る半導体発光素子の製造方法を示す工程順の構成断面図である。

【図6】(a)～(c)は本発明の第2の実施形態に係る半導体発光素子の製造方法を示す工程順の構成断面図である。 20

【図7】(a)～(c)は本発明の第2の実施形態に係る半導体発光素子の製造方法を示す工程順の構成断面図である。

【図8】(a)～(c)は本発明の第2の実施形態の一変形例に係る半導体発光素子を示し、(a)は構成断面図であり、(b)はSEMによるチップ表面の顕微鏡写真であり、(c)は発光状態にあるチップ表面の写真である。

【図9】本発明の第2の実施形態の一変形例に係る半導体発光素子の発光スペクトルを示すグラフである。

【図10】本発明の第3の実施形態に係る半導体発光素子を示す構成断面図である。

【図11】(a)～(c)は本発明の第3の実施形態に係る半導体発光素子の製造方法を示す工程順の構成断面図である。 30

【図12】(a)～(c)は本発明の第3の実施形態に係る半導体発光素子の製造方法を示す工程順の構成断面図である。

【図13】(a)～(c)は本発明の第3の実施形態に係る半導体発光素子の製造方法を示す工程順の構成断面図である。

【図14】本発明の第4の実施形態に係る半導体発光素子を示す構成断面図である。

【図15】(a)～(c)は本発明の第4の実施形態に係る半導体発光素子の製造方法を示す工程順の構成断面図である。 40

【図16】(a)～(c)は本発明の第4の実施形態に係る半導体発光素子の製造方法を示す工程順の構成断面図である。

【図17】(a)～(c)は本発明の第4の実施形態に係る半導体発光素子の製造方法を示す工程順の構成断面図である。

【図18】第1の従来例に係る発光ダイオード素子を示す構成断面図である。

【図19】第2の従来例に係る発光ダイオード素子を示す構成断面図である。

#### 【符号の説明】

10 発光ダイオード素子

11 素子構造体(半導体積層膜)

12 n型半導体層

12A n型半導体層

13 活性層

13A 活性層

14 p型半導体層

|       |                     |    |

|-------|---------------------|----|

| 1 4 A | p 型半導体層             |    |

| 1 5   | p 側電極 ( I T O )     |    |

| 1 5 A | p 側電極 ( P t / A u ) |    |

| 1 5 B | p 側電極 ( P t )       |    |

| 1 6   | ボンディングパッド           |    |

| 1 7   | n 側電極 ( T i / A u ) |    |

| 1 7 A | n 側電極 ( T i / A l ) |    |

| 1 7 B | n 側電極 ( I T O )     |    |

| 1 8   | 金属膜                 |    |

| 2 0   | 基板                  | 10 |

| 2 1   | 半田材                 |    |

| 2 2   | パッケージ               |    |

| 2 3   | 電流狭窄膜               |    |

| 2 4   | めっき下地層              |    |

| 2 5   | ミラー構造体              |    |

| 4 1   | 保持膜                 |    |

| 4 2   | 第 1 の保持膜            |    |

| 4 3   | 第 3 の保持膜            |    |

| 5 0   | ダイシングブレード           |    |

| 5 1   | コレット                | 20 |

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

$$\Delta \lambda = \frac{\lambda_0^2}{2n_{\text{eff}}L}$$

$\lambda_0$  : ピーク波長 (470nm)

$n_{\text{eff}}$  : 実効屈折率 (GaN: 3.27)

$L$  : 共振器長

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

---

フロントページの続き

(72)発明者 上田 哲三

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 油利 正昭

大阪府門真市大字門真1006番地 松下電器産業株式会社内

F ターム(参考) 5F041 AA03 AA31 AA33 CA04 CA05 CA12 CA22 CA34 CA49 CA57

CA65 CA74 CA76 CA77 CA83 CA88 CA92 CB02 CB15 CB36

DA07