(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7107810号**

**(P7107810)**

(45)発行日 令和4年7月27日(2022.7.27)

(24)登録日 令和4年7月19日(2022.7.19)

(51)国際特許分類

|        |                 |     |        |       |         |

|--------|-----------------|-----|--------|-------|---------|

| H 05 K | 3/34 (2006.01)  | F I | H 05 K | 3/34  | 5 0 5 C |

| H 05 K | 13/04 (2006.01) |     | H 05 K | 13/04 | B       |

| B 41 M | 1/12 (2006.01)  |     | B 41 M | 1/12  |         |

| B 41 M | 1/34 (2006.01)  |     | B 41 M | 1/34  |         |

| B 23 K | 1/00 (2006.01)  |     | B 23 K | 1/00  | U       |

請求項の数 4 (全22頁) 最終頁に続く

(21)出願番号 特願2018-197714(P2018-197714)

(22)出願日 平成30年10月19日(2018.10.19)

(65)公開番号 特開2020-65029(P2020-65029A)

(43)公開日 令和2年4月23日(2020.4.23)

審査請求日 令和3年9月24日(2021.9.24)

(73)特許権者 310021766

株式会社ソニー・インタラクティブエンタテインメント

東京都港区港南1丁目7番1号

(74)代理人 100105924

弁理士 森下 賢樹

(74)代理人 100109047

弁理士 村田 雄祐

(74)代理人 100109081

弁理士 三木 友由

(74)代理人 100134256

弁理士 青木 武司

(72)発明者 笹尾 和樹

東京都港区港南1丁目7番1号 株式会社ソニー・インタラクティブエンタテインメント

最終頁に続く

(54)【発明の名称】 半導体装置の製造方法およびスクリーン

**(57)【特許請求の範囲】****【請求項1】**

半導体装置の製造方法であって、

プリント基板の第1面に第1部品群を実装する第1ステップと、

前記プリント基板の第2面に第2部品群を実装する第2ステップと、

を備え、

前記プリント基板はパッド内ビアを有し、

前記第1ステップは、

前記第1面の複数のパッドにクリーム半田を塗布するステップと、

前記第1面に前記第1部品群にマウントするステップと、

前記プリント基板を加熱、冷却するステップと、

を含み、

前記第2ステップは、

前記第2面の複数のパッドの箇所に開口を有し、かつ前記パッド内ビアとオーバーラップする箇所に凹部を有するスクリーン(メタルマスク)を、前記第2面に載せるステップと、

前記スクリーンの上からクリーム半田を塗布し、前記スクリーンを外すステップと、

前記第2面に前記第2部品群をマウントするステップと、

前記プリント基板を過熱、冷却するステップと、

を備えることを特徴とする製造方法。

**【請求項2】**

前記第1部品群は、パワートランジスタを含み、

前記パッド内ビアは、前記パワートランジスタの裏面電極とオーバーラップする箇所に設けられることを特徴とする請求項1に記載の製造方法。

**【請求項3】**

パッド内ビアを有するプリント基板に部品を実装する際に使用されるスクリーンであって、前記プリント基板に形成される複数のパッドと対応する箇所に設けられた複数の開口と、前記パッド内ビアとオーバーラップする箇所に設けられた凹部と、を備えることを特徴とするスクリーン。

**【請求項4】**

電圧安定化モジュールを有する半導体装置の製造方法であって、

10

プリント基板の第1面に、少なくともひとつのパワートランジスタを含む第1部品群を実装する第1ステップと、

前記プリント基板の第2面に、少なくともひとつのインダクタを含む第2部品群を実装する第2ステップと、

を備え、

前記プリント基板は、前記パワートランジスタの裏面電極とオーバーラップする箇所に設けられたパッド内ビアを有し、

前記第1ステップは、

前記第1面の複数のパッドにクリーム半田を塗布するステップと、

前記第1面に前記第1部品群にマウントするステップと、

20

前記プリント基板を加熱、冷却するステップと、

を含み、

前記第2ステップは、

前記第2面の複数のパッドの箇所に開口を有し、かつ前記パッド内ビアとオーバーラップする箇所に凹部を有するスクリーンを、前記第2面に載せるステップと、

前記スクリーンの上からクリーム半田を塗布し、前記スクリーンを外すステップと、

前記第2面に前記第2部品群をマウントするステップと、

前記プリント基板を過熱、冷却するステップと、

を備えることを特徴とする製造方法。

**【発明の詳細な説明】**

30

**【技術分野】**

**【0001】**

本発明は、表面実装技術に関する。

**【背景技術】**

**【0002】**

電子機器は、プリント基板と、プリント基板上に実装される電子部品を備える。近年では、チップインダクタ、チップ抵抗、チップコンデンサ、トランジスタなどの表面実装型の部品(SMD:Surface Mount Device)が主流となっている。

**【0003】**

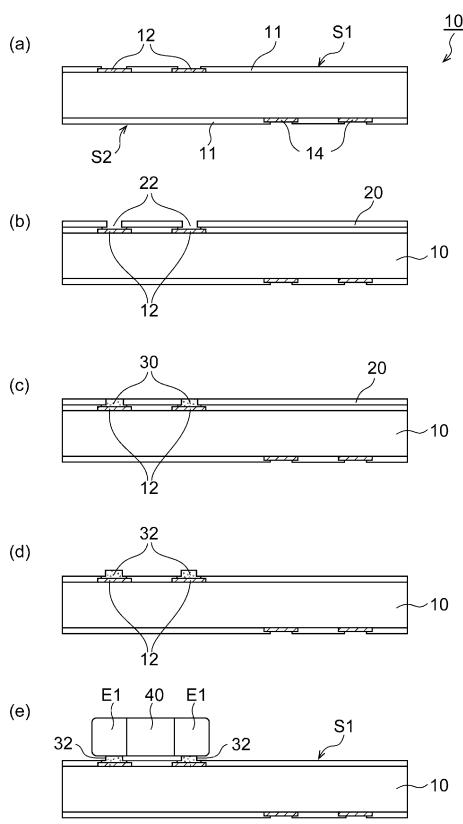

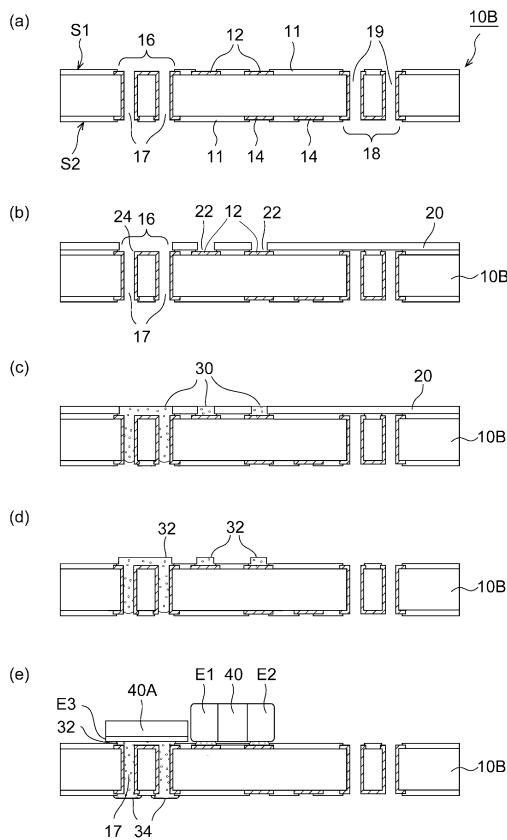

図1(a)～(e)および図2(a)～(e)は、電子機器の組み立て工程を説明する断面図である。図1(a)には、部品が実装される前のプリント基板10が示される。プリント基板10の第1面(先行実装面)S1および第2面S2(後行実装面)には、プリント配線(不図示)や、パッド(ランド)12, 14が形成されている。パッド12, 14は、部品の電極と対応する箇所に配置され、パッド12, 14以外の部分は、レジスト11によって覆われている。

40

**【0004】**

図1(b)に示すように、第1面S1の上に、スクリーン(メタルマスクあるいは半田マスクとも称する)20が載置される。スクリーン20には、第1面S1側のパッド12とオーバーラップする箇所に開口22が設けられる。続いて図1(c)に示すように、スクリーン20の上からクリーム半田(半田ペースト)30が塗布される。図1(d)に示す

50

ようにスクリーン 2 0 を取り外すと、パッド 1 2 の上にのみクリーム半田 3 2 が残留する。

#### 【 0 0 0 5 】

続いて図 1 ( e ) に示すように、マウンタによって第 1 面 S 1 に部品 4 0 がマウントされる。部品 4 0 の電極 E 1 , E 2 と、パッド 1 2 の間には、クリーム半田 3 2 が挟まれている。この状態でリフロー処理が行われ、部品 4 0 と基板 1 0 とが電気的、機械的に接続される。

#### 【 0 0 0 6 】

続いて、第 2 面 S 2 への部品実装を説明する。図 2 ( a ) に示すようにプリント基板 1 0 は、第 2 面 S 2 が上側となるように反転される。続いて図 2 ( b ) に示すように第 2 面 S 2 の上にスクリーン 5 0 が載置される。スクリーン 5 0 には、第 2 面 S 2 側のパッド 1 4 とオーバーラップする箇所に開口 5 2 が設けられる。続いて図 2 ( c ) に示すように、スクリーン 5 0 の上からクリーム半田 6 0 が塗布される。図 2 ( d ) に示すようにスクリーン 5 0 を取り外すと、パッド 1 4 の上にのみクリーム半田 6 2 が残留する。

10

#### 【 0 0 0 7 】

続いて図 2 ( e ) に示すように、マウンタによって第 2 面 S 2 に部品 7 0 がマウントされる。部品 7 0 の電極 E 1 , E 2 と、パッド 1 4 の間には、クリーム半田 6 2 が挟まれている。この状態でリフロー処理が行われ、部品 7 0 と基板 1 0 とが電気的、機械的に接続される。以上が表面実装の説明である。

20

#### 【 発明の概要 】

#### 【 発明が解決しようとする課題 】

#### 【 0 0 0 8 】

本発明者は表面実装について検討した結果、以下の課題を認識するに至った。プリント基板 1 0 は、複数の配線層を含み、異なる配線層の間はビアを介して接続される。ビアは、通常、パッドの位置を避けて配置されるが、放熱性を高めたり、寄生インピーダンスを削減したい場合には、パッド内に配置される場合もある。パッド内に配置されるビアを、パッド内ビアと称する。

#### 【 0 0 0 9 】

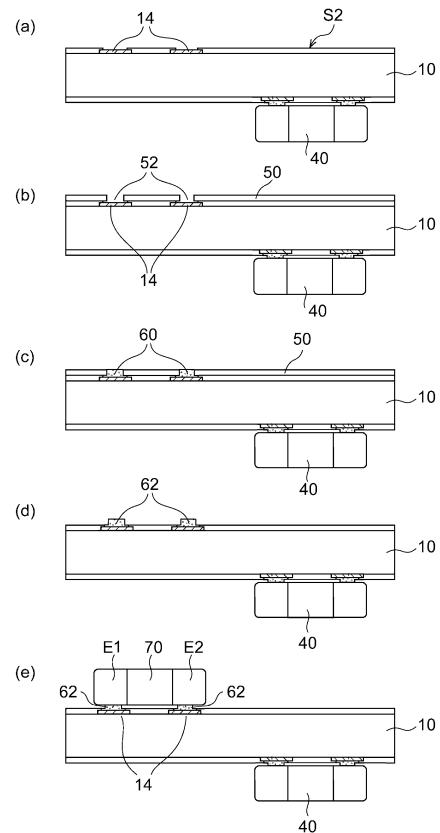

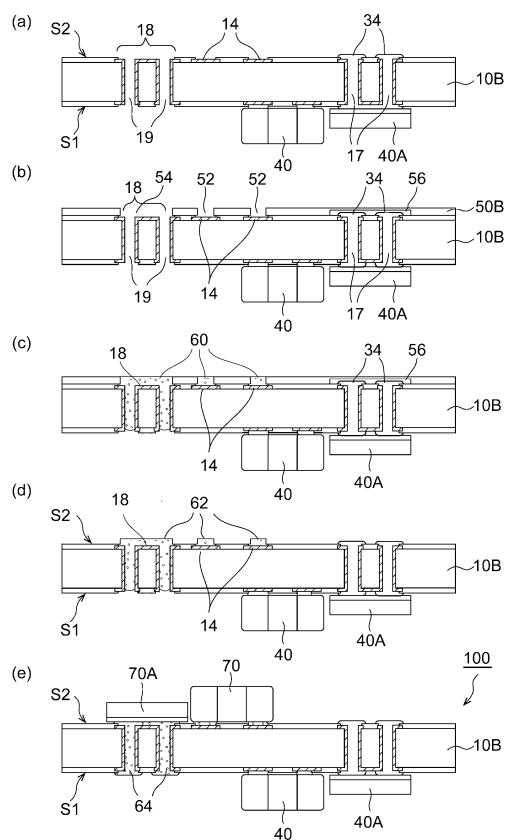

従来の表面実装では、先行実装面である第 1 面 S 1 にパッド内ビアを形成することが困難であった。図 3 ( a ) ~ ( e ) は、第 1 面 S 1 への部品実装を説明する図であり、図 4 ( a ) ~ ( e ) は、第 2 面 S 2 への部品実装を説明する図である。

30

#### 【 0 0 1 0 】

図 3 ( a ) には、部品が実装される前のプリント基板 1 0 A が示される。プリント基板 1 0 A の第 1 面 ( 先行実装面 ) S 1 には、パッド ( ランド ) 1 6 およびパッド内ビア 1 7 が形成される。

#### 【 0 0 1 1 】

第 1 面 S 1 の上にスクリーン 2 0 が載置され ( 図 3 ( b ) ) 、続いてスクリーン 2 0 の上からクリーム半田 3 0 が塗布される ( 図 3 ( c ) ) 。そしてスクリーン 2 0 を取り外すと、パッド 1 6 の上にクリーム半田 3 2 が残留する ( 図 3 ( d ) ) 。

#### 【 0 0 1 2 】

続いて、マウンタによって第 1 面 S 1 に部品 4 0 A がマウントされる ( 図 3 ( e ) ) 。部品 4 0 A は裏面電極 E 3 を有し、裏面電極 E 3 とパッド 1 6 の間には、クリーム半田 3 2 が挟まれている。この状態でリフロー処理が行われ、部品 4 0 A と基板 1 0 とが電気的、機械的に接続される。この工程においてクリーム半田 3 2 の一部は、パッド内ビア 1 7 ( スルーホール ) を貫通し、第 2 面 S 2 側から漏れ出る。この半田の漏れ 3 4 は、以下で説明するように実装不良を引き起こす。

40

#### 【 0 0 1 3 】

図 4 ( a ) ~ ( e ) を参照して第 2 面 S 2 への部品実装を説明する。図 4 ( a ) に示すようにプリント基板 1 0 A は、第 2 面 S 2 が上側となるように反転される。続いて図 4 ( b ) に示すように第 2 面 S 2 の上にスクリーン 5 0 が載置される。スクリーン 5 0 は、パッド 1 4 とオーバーラップする箇所に開口 5 2 を有する。

50

**【 0 0 1 4 】**

そして図4(c)に示すようにスクリーン50の上からクリーム半田60が塗布される。図4(d)は、スクリーン50を取り外した状態を示す。クリーム半田62は、パッド14以外の意図しない領域に塗布されている。この状態で第2面S2に部品70をマウントし、リフロー処理にかけると、隣接するパッド14同士がクリーム半田62によってショートするなどの不良が生ずるおそれがある。

**【 0 0 1 5 】**

以上が従来の表面実装の問題点である。先行実装面にパッド内ビアを形成したい場合、第2面の実装に、スクリーン印刷を用いず、ニードルディスペンサによって、パッド14の上に選択的にクリーム半田を塗布する方法が考えられる。この方法によれば、第1面S1へのクリーム半田30の影響を受けずに、第2面S2に部品を実装できる。しかしながら、ニードルディスペンサを用いたクリーム半田の塗布は、スクリーン印刷によるそれに比べてスループットが大幅に低下するため、第2面S2の部品点数が多い場合には採用できない。

10

**【 0 0 1 6 】**

別のアプローチとして、プリント基板10Aの製造工程において、予めビアホールの内部を金属あるいは樹脂で充填して穴を塞ぐという対策が考えられる。この対策によれば、図3(e)の工程において、第2面S2側へのクリーム半田30の漏れを防止できる。しかしながらこの解決方法では、プリント基板10Aの製造工程が増えるため、プリント基板10Aのコストが高くなる。

20

**【 0 0 1 7 】**

本発明は係る課題に鑑みてなされたものであり、そのある態様の例示的な目的のひとつは、パッド内ビアに起因する問題を解決可能な表面実装技術の提供にある。

**【課題を解決するための手段】****【 0 0 1 8 】**

本発明のある態様は、半導体装置の製造方法に関する。製造方法は、プリント基板の第1面に第1部品群を実装する第1ステップと、プリント基板の第2面に第2部品群を実装する第2ステップと、を備える。プリント基板はパッド内ビアを有する。第1ステップは、第1面の複数のパッドにクリーム半田を塗布するステップと、第1面に第1部品群にマウントするステップと、プリント基板を加熱、冷却するステップと、を含む。第2ステップは、第2面の複数のパッドの箇所に開口を有し、かつパッド内ビアとオーバーラップする箇所に凹部を有するスクリーン(メタルマスク)を、第2面に載せるステップと、スクリーンの上からクリーム半田を塗布し、スクリーンを外すステップと、第2面に第2部品群をマウントするステップと、プリント基板を過熱、冷却するステップと、を備える。

30

**【 0 0 1 9 】**

本発明の別の態様は、スクリーンである。このスクリーンは、パッド内ビアを有するプリント基板に部品を実装する際に使用されるスクリーンであって、プリント基板に形成される複数のパッドと対応する箇所に設けられた複数の開口と、パッド内ビアとオーバーラップする箇所に設けられた凹部と、を備える。

**【 0 0 2 0 】**

本発明のさらに別の態様は、電圧安定化モジュールを有する半導体装置の製造方法に関する。製造方法は、プリント基板の第1面に、パワートランジスタを含む第1部品群を実装する第1ステップと、プリント基板の第2面に、インダクタを含む第2部品群を実装する第2ステップと、を備える。プリント基板は、パワートランジスタの裏面電極とオーバーラップする箇所に設けられたパッド内ビアを有する。第1ステップは、第1面の複数のパッドにクリーム半田を塗布するステップと、第1面に第1部品群にマウントするステップと、プリント基板を加熱、冷却するステップと、を含む。第2ステップは、第2面の複数のパッドの箇所に開口を有し、かつパッド内ビアとオーバーラップする箇所に凹部を有するスクリーンを、第2面に載せるステップと、スクリーンの上からクリーム半田を塗布し、スクリーンを外すステップと、第2面に第2部品群をマウントするステップと、プリント

40

50

ト基板を過熱、冷却するステップと、を備える。

【0021】

なお、以上の構成要素の任意の組合せ、本発明の表現を、方法、装置、システムなどの間で変換したものもまた、本発明の態様として有効である。

【発明の効果】

【0022】

本発明によれば、パッド内ビアに起因する問題を解決できる。

【図面の簡単な説明】

【0023】

【図1】図1(a)～(e)は、電子機器の組み立て工程を説明する断面図である。 10

【図2】図2(a)～(e)は、電子機器の組み立て工程を説明する断面図である。

【図3】図3(a)～(e)は、第1面S1への部品実装を説明する図であり、図4(a)～(e)は、第2面S2への部品実装を説明する図である。

【図4】図4(a)～(e)は、第2面S2への部品実装を説明する図である。

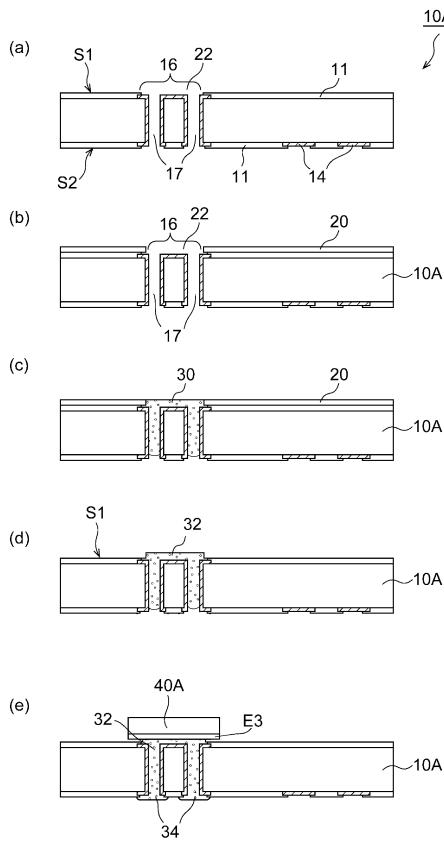

【図5】図5(a)～(e)は、実施の形態に係る電子機器の製造方法を説明する図である。

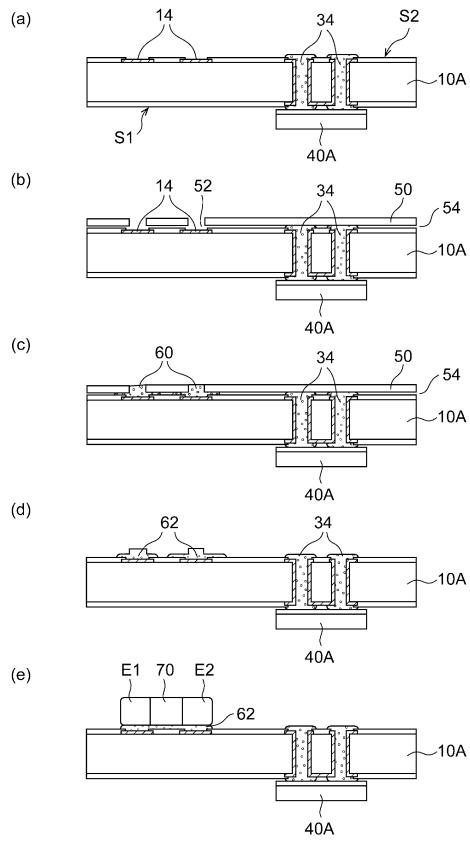

【図6】図6(a)～(e)は、実施の形態に係る電子機器の製造方法を説明する図である。

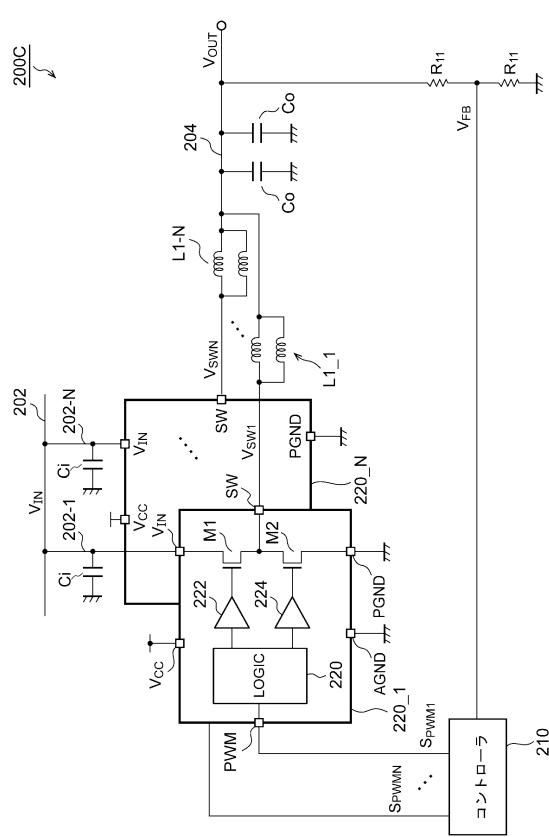

【図7】マルチフェーズの降圧DC/DCコンバータの構成例を示す回路図である。

【図8】図8(a)～(c)はそれぞれ、K=2、3、4のときのスイッチング電圧Vs 20

w1～Vs w4を示す波形図である。

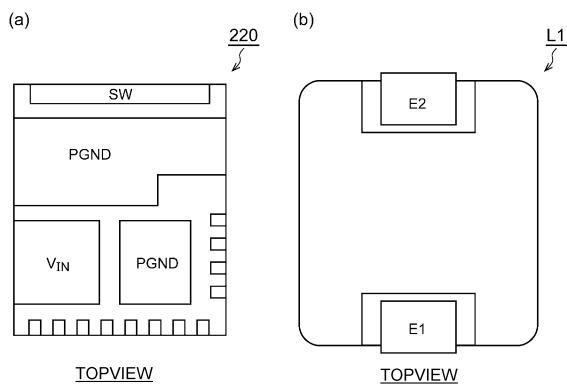

【図9】図9(a)は、パワーモジュールの裏面電極のレイアウト図であり、図9(b)は、インダクタの裏面電極のレイアウト図である。

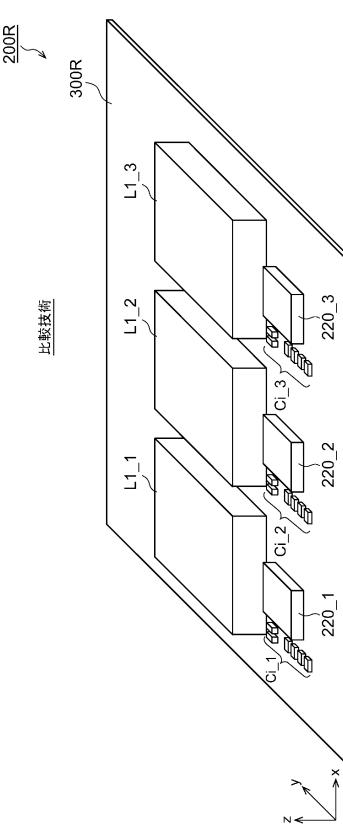

【図10】比較技術に係るDC/DCコンバータのレイアウト図である。

【図11】比較技術に係るプリント基板の配線パターンを示す図である。

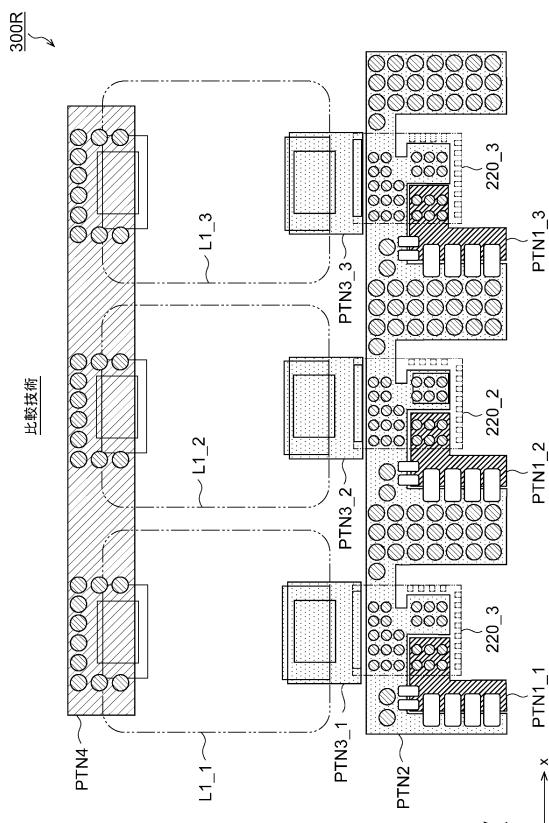

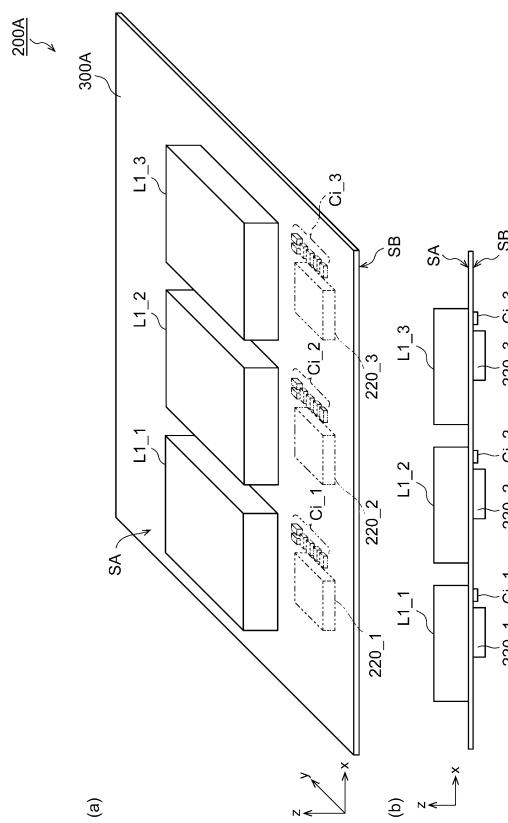

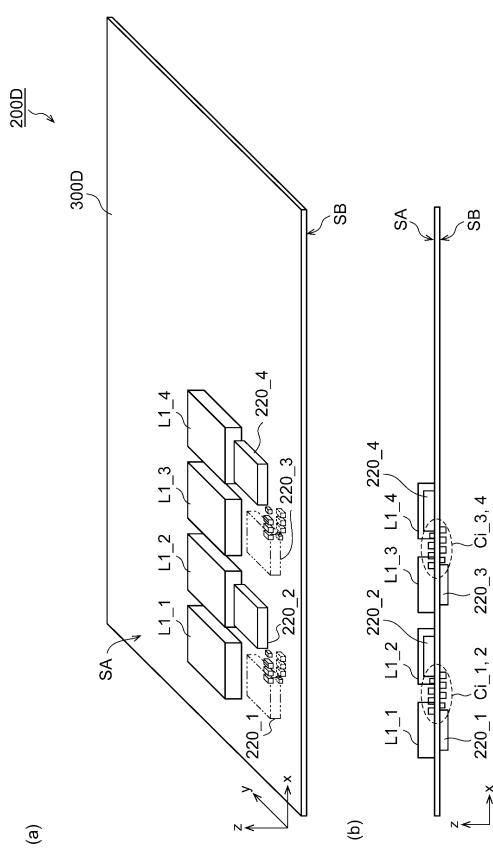

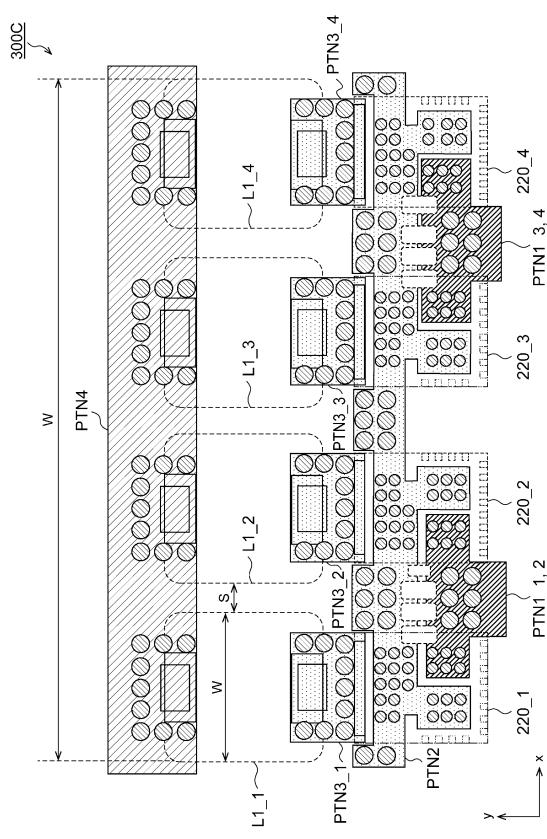

【図12】図12(a)、(b)は、実施例1-1に係るDC/DCコンバータのレイアウト図である。

【図13】実施例1-1に係るDC/DCコンバータの配線パターンを示す図である。

【図14】DC/DCコンバータを副実装面SB側からみた斜視図である。

【図15】図15(a)、(b)は、第1構成例に係るヒートシンクの断面図である。 30

【図16】図16(a)、(b)は、第2構成例に係るヒートシンクの断面図である。

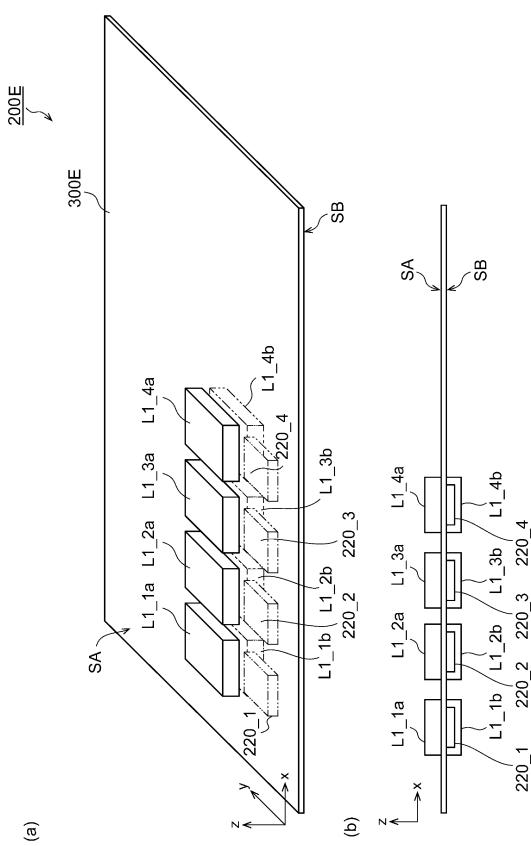

【図17】図17(a)、(b)は、実施例1-2に係るDC/DCコンバータのレイアウト図である。

【図18】実施例1-2に係るDC/DCコンバータの配線パターンを示す図である。

【図19】図19(a)、(b)は、実施例1-3に係るDC/DCコンバータのレイアウト図である。

【図20】図20(a)、(b)は、実施例1-4に係るDC/DCコンバータのレイアウト図である。

【図21】第2の実施の形態に係るDC/DCコンバータの等価回路図である。

【図22】図22(a)、(b)は、実施例2-1に係るDC/DCコンバータのレイアウト図である。 40

【図23】実施例2-1に係るDC/DCコンバータの配線パターンを示す図である。

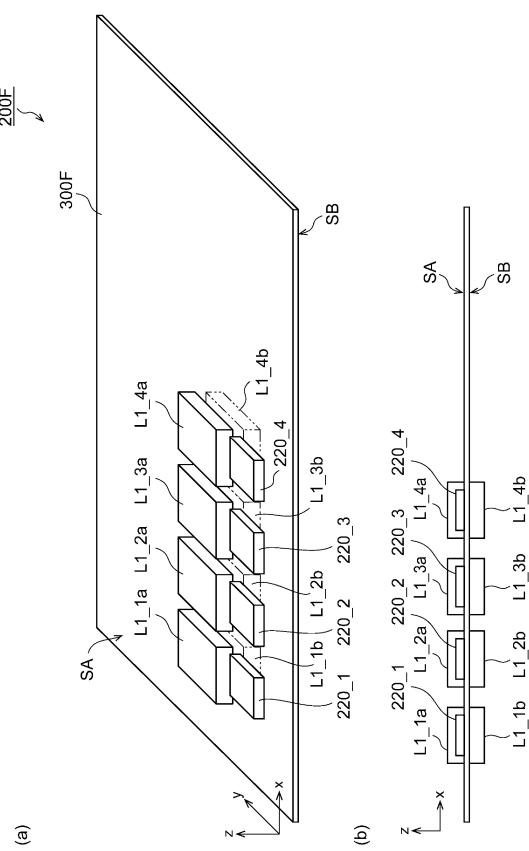

【図24】図24(a)、(b)は、実施例2-2に係るDC/DCコンバータのレイアウト図である。

【図25】図25(a)、(b)は、実施例2-3に係るDC/DCコンバータのレイアウト図である。

【発明を実施するための形態】

【0024】

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複

した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

#### 【0025】

また図面に記載される各部材の寸法（厚み、長さ、幅など）は、理解の容易化のために適宜、拡大縮小されている場合がある。さらには複数の部材の寸法は、必ずしもそれらの大小関係を表しているとは限らず、図面上で、ある部材Aが、別の部材Bよりも厚く描かれても、部材Aが部材Bよりも薄いこともあり得る。

#### 【0026】

図5(a)～(e)および図6(a)～(e)は、実施の形態に係る電子機器の製造方法を説明する図である。図5(a)～(e)および図6(a)～(e)には、表面実装による組み立て工程が示される。

10

#### 【0027】

図5(a)～(e)を参照して、第1面S1への部品実装を説明する。第1面S1への実装については、以下で説明するように図3と実質的に同様である。

#### 【0028】

図5(a)には、部品が実装される前のプリント基板10Bが示される。プリント基板10Bの第1面（先行実装面）S1には、いくつかのパッド（ランド）12, 16が形成される。パッド16には、パッド内ビア17が形成される。プリント基板10B第2面（後行実装面）S2にも同様に、いくつかのパッド14, 18が形成される。パッド18には、パッド内ビア19が形成される。

20

#### 【0029】

図5(b)に示すように、第1面S1の上にスクリーン20が載置される。スクリーン20には、パッド12, 16に対応する箇所に、開口22, 24が設けられる。続いてスクリーン20の上からクリーム半田30が塗布される（図5(c)）。

#### 【0030】

そしてスクリーン20を取り外すと、パッド12, 16の上にクリーム半田32が残留する（図5(d)）。

#### 【0031】

続いて、マウンタによって第1面S1に部品40, 40Aがマウントされる（図5(e)）。部品40の電極E1, E2と、パッド12の間には、クリーム半田32が挟まれている。部品40Aは裏面電極E3を有し、裏面電極E3とパッド16の間には、クリーム半田32が挟まれている。この状態でリフロー処理が行われ、部品40Aと基板10とが電気的、機械的に接続される。

30

#### 【0032】

この工程においてクリーム半田32の一部は、パッド内ビア17（スルーホール）を貫通し、第2面S2側から漏れ出る。

#### 【0033】

続いて図6(a)～(e)を参照して第2面S2への部品実装を説明する。図6(a)に示すようにプリント基板10Bは、第2面S2が上側となるように反転される。続いて図6(b)に示すように、第2面S2の上に、スクリーン50Bが載置される。

40

#### 【0034】

本実施の形態において、スクリーン50Bは、パッド14とオーバーラップする箇所に開口52を有する。それに加えてスクリーン50Bには、パッド内ビア19とオーバーラップする箇所に、凹部56が設けられている。この凹部56によって、スクリーン50Bが半田の漏れ34と干渉しないようになっており、スクリーン50Bを第2面S2に密着させることが可能となる。

#### 【0035】

図6(d)は、スクリーン50Bを取り外した状態を示す。クリーム半田62は、パッド14, 18の上にのみ塗布されており、余計なはみ出しが抑えられている。

50

**【 0 0 3 6 】**

続いて図6(e)のように、第2面S2に部品70, 70Aがマウントされ、リフロー処理にかけられる。これにより部品70に関して、電極E1, E2がパッド14と電気的、機械的に接続される。また部品70Aに関してても、裏面電極E3とパッド18とが電気的、機械的に接続され、半導体装置100が組み立てられる。

**【 0 0 3 7 】**

以上が実施の形態に係る半導体装置の製造方法である。

**【 0 0 3 8 】**

このように、本実施の形態によれば、第2面S2にクリーム半田を塗布する際に用いるスクリーン50に、半田の漏れ34との干渉を避けるための凹部56を設けることとした。これにより、半田の漏れ34によるスクリーン50Bの位置ズレを防止でき、またスクリーン50Bと第2面S2の間のギャップにクリーム半田60が侵入するのを防止できる。

10

**【 0 0 3 9 】**

なお第2面S2に部品70Aを実装する際に、パッド内ビア19から第1面S1側にも、半田の漏れ64が生じうるが、第1面S1側の部品の実装は完了しているため、悪影響はない。

**【 0 0 4 0 】**

続いて、実施の形態に係る製造方法の用途を説明する。実施の形態に係る製造方法は、以下で説明するDC/DCコンバータの製造工程に利用可能であり、上述の第1面S1に実装される部品40Aは、第1面S1に実装される後述のパワーモジュール220に対応付けられる。

20

**【 0 0 4 1 】**

パーソナルコンピュータやゲーム専用機などの電子機器において、電池、あるいはインバータから供給される直流電圧を、負荷に最適な電圧レベルに降圧するDC/DCコンバータ(スイッチングレギュレータ)が利用される。

**【 0 0 4 2 】**

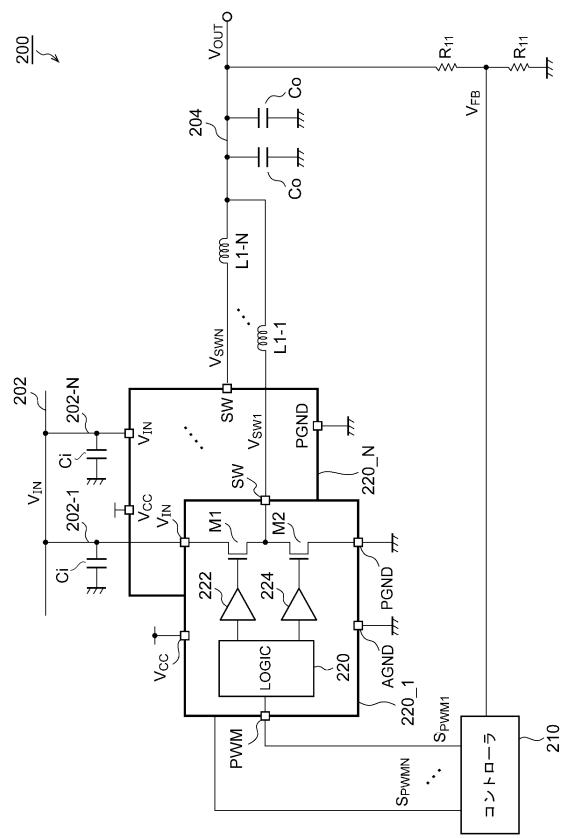

図7は、マルチフェーズの降圧DC/DCコンバータの構成例を示す回路図である。DC/DCコンバータ200は、Nフェーズ(N=2)で構成され、入力ライン202、出力ライン204、N個のインダクタL1\_1~L1\_N、入力キャパシタCi、出力キャパシタCo、コントローラ210、N個のパワーモジュール220\_1~220\_Nを備える。

30

**【 0 0 4 3 】**

出力ライン204には、消費電力(負荷電流IOUT)がダイナミックに変化する負荷(不図示)が接続される。DC/DCコンバータ200は、入力ライン202の入力電圧VINを受け、所定レベルに安定化された出力電圧VOUTを生成し、負荷に供給する。入力ライン202には、入力電圧VINを安定化させるための入力キャパシタCiが接続され、出力ライン204には、出力電圧VOUTを平滑化するための出力キャパシタCoが接続される。

**【 0 0 4 4 】**

パワーモジュール220は、主として、VINピン、PGNDピン、SWピン、VCCCピン、AGNDピン、PWMピンを備える。パワーモジュール220は、VINピンとSWピンの間に設けられたハイサイドスイッチ(スイッチングトランジスタ)M1と、SWピンとPGNDピンの間に設けられたローサイドスイッチ(同期整流トランジスタトランジスタ)M2と、ハイサイドドライバ222、ローサイドドライバ224、ロジック回路226を含む。

40

**【 0 0 4 5 】**

コントローラ210は、複数のインダクタL1\_1~L1\_Nそれぞれに流れる電流あるいは負荷電流IOUTを監視し、駆動フェーズ数Kを決定する。たとえばN=4の場合、Kは、1, 2, 3, 4の4つの値(あるいは1, 2, 4の3つの値)から選択可能とされる。

50

**【 0 0 4 6 】**

またコントローラ 210 は、出力電圧  $V_{OUT}$  に応じたフィードバック信号  $V_{FB}$  を受け、フィードバック信号  $V_{FB}$  が所定の目標電圧  $V_{REF}$  に近づくように、デューティ比が調節されるパルス信号  $S_{PWM}$  を生成し、N 個のパワーモジュール 220\_1 ~ 220\_N のうち、K 個に分配する。K 個のパワーモジュール 220\_1 ~ 220\_K には、(360/K) 度の位相差を有するパルス信号  $S_{PWM1} \sim S_{PWMK}$  が分配される。

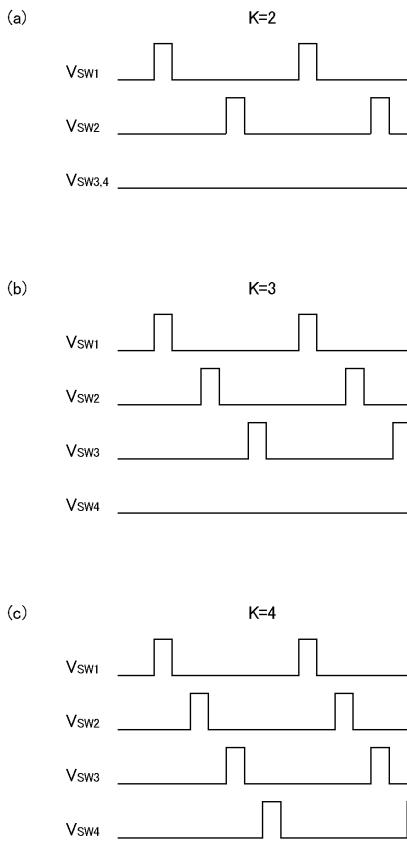

**【 0 0 4 7 】**

以上が DC / DC コンバータ 200 の構成である。続いてその動作を説明する。ここでは M = 4 であり、駆動フェーズ数 K は 2、3、4 を取りうる場合を説明する。図 8 (a) ~ (c) はそれぞれ、K = 2、3、4 のときのスイッチング電圧  $V_{SW1} \sim V_{SW4}$  を示す波形図である。

10

**【 0 0 4 8 】**

DC / DC コンバータ 200 の構成部品はプリント基板上に実装される。従来の DC / DC コンバータ 200 は、主要な構成部品であるインダクタ L1\_1 ~ L1\_N、パワーモジュール 220\_1 ~ 220\_N が、同一実装面にマウントされていた。ここでいう主要な構成部品とは、専有面積が大きく、また大電流が流れる部品である。

**【 0 0 4 9 】**

主要な構成部品を同一実装面に実装すると、DC / DC コンバータ 200 の専有面積が大きくなる。これはプリント基板の面積が大きくなることを意味し、コストアップの一因となり得る。

20

**【 0 0 5 0 】**

また、複数のパワーモジュール 220\_1 ~ 220\_N の発熱が大きいアプリケーションでは、複数のパワーモジュール 220\_1 ~ 220\_N をヒートシンクで冷却する必要がある。ところが複数のパワーモジュール 220\_1 ~ 220\_N が、複数のインダクタ L1\_1 ~ L1\_N などの他の部品と近接配置すると、ヒートシンクの形状が、他の部品によって制約され、冷却効果が犠牲になるおそれがある。

**【 0 0 5 1 】**

反対に、冷却効果を優先してレイアウトを決めると、パワーモジュールとインダクタの距離が遠くなり、DC / DC コンバータ 200 の専有面積が大きくなり、コストアップの要因となりうる。

30

**【 0 0 5 2 】****( 第 1 の実施の形態 )**

本発明の一側面は、DC / DC コンバータのレイアウトあるいは実装技術として把握される。本実施の形態において、DC / DC コンバータの機能あるいは等価回路については、図 7 と同様である。

**【 0 0 5 3 】**

いくつかの実施例で共通となるパワーモジュール 220 について説明する。パワーモジュール 220 自体は、公知であり、さまざまな IC メーカによって製造・販売されている。

**【 0 0 5 4 】**

パワーモジュール 220 の回路構成は、図 7 と同様であり、ハイサイドトランジスタ M1、ローサイドトランジスタ M2、ハイサイドドライバ 222、ローサイドドライバ 224、ロジック回路 226 を備える。またパワーモジュール 220 は、入力 (VIN) ピン、スイッチングピン (SW)、グランドピン (PGND, AGND)、電源 (VCC) ピン、制御 (PWM) ピンなどを備える。なお、パワーモジュール 220 は、ブートストラップ回路や、各種保護回路などを備え、またそれらに関連する複数のピンを備えるが、本発明と無関係であるため図示せず、説明を省略する。

40

**【 0 0 5 5 】**

ロジック回路 226 をはじめとする各回路ブロックには、VCC ピンを介して電源電圧 VCC が供給される。AGND ピンは、ハイサイドドライバ 222、ローサイドドライバ 224、ロジック回路 226 等のグランドである。VIN ピンには、直流の入力電圧 VIN

50

が供給され、P G N D ピンは、出力段のグランドである。

#### 【 0 0 5 6 】

ロジック回路 2 2 6 は、P W M ピンに入力される P W M 信号 S P W M に応じて、ハイサイドパルス、ローサイドパルスを生成する。ハイサイドドライバ 2 2 2 はハイサイドパルスにもとづいてハイサイドトランジスタ M 1 を駆動し、ローサイドドライバ 2 2 4 は、ローサイドパルスにもとづいてローサイドトランジスタ M 2 を駆動する。

#### 【 0 0 5 7 】

続いて主要な回路部品のパッケージのピン配置を説明する。図 9 ( a ) は、パワーモジュール 2 2 0 の裏面電極のレイアウト図である。上述のようパワーモジュール 2 2 0 は、V I N ピン、P G N D ピン、S W ピン、V C C ピン、A G N D ピンを備える。この中で、V I N ピンとG N D ピンは、相対的に他のパッドよりも面積が大きい。特にP G N D ピン、A G N D ピンはサーマルパッドとしての機能も有するため、面積が大きい。P W M ピンやその他の制御ピンは、残りのピンに割り当てられる。なお、図 9 の裏面電極のレイアウトは例示に過ぎず、チップベンダーや製品ごとに異なることは言うまでもない。10

#### 【 0 0 5 8 】

図 9 ( b ) は、インダクタ L 1 の裏面電極のレイアウト図である。インダクタ L 1 は、対向する 2 辺の中央に配置された第 1 電極 E 1 と第 2 電極 E 2 を有する。

#### 【 0 0 5 9 】

本実施の形態において解決しようとする課題のひとつは、レイアウトの改善である。そこではじめに、比較の基準となるレイアウト（以下、比較技術という）について説明する。20

#### 【 0 0 6 0 】

近年の電子回路は、表面実装技術（S D T : Surface Mount Technology）を用いて実装される。表面実装では、プリント基板上に形成されたパッド（ランド）に、クリーム半田を塗布し、マウンタを用いて部品を実装し、リフロー処理を行う。

#### 【 0 0 6 1 】

プリント基板の両面に表面実装により部品を実装する場合、一方の面（先行実装面）に部品を実装する。続いて、プリント基板を裏返した後に、他方の面（後行実装面）に部品を実装する。後行実装面をリフロー処理すると、先行実装面の半田が再加熱される。先行実装面に実装済みの部品が重かったり大きかったりすると、実装済みの部品が位置ズレを起こしたり、落下するおそれがある。この理由から、先行実装面に実装できる部品には、大きさや重さに制約があり、したがって先行実装面が副実装面となるのが一般的である。つまり副実装面には、相対的に少ない部品、軽い部品、小さい部品が実装され、主実装面には、相対的に多くの部品、重い部品、大きな部品が実装される。D C / D C コンバータについても例外ではなく、よって比較技術においても基本的にはすべての部品が主実装面に実装される。30

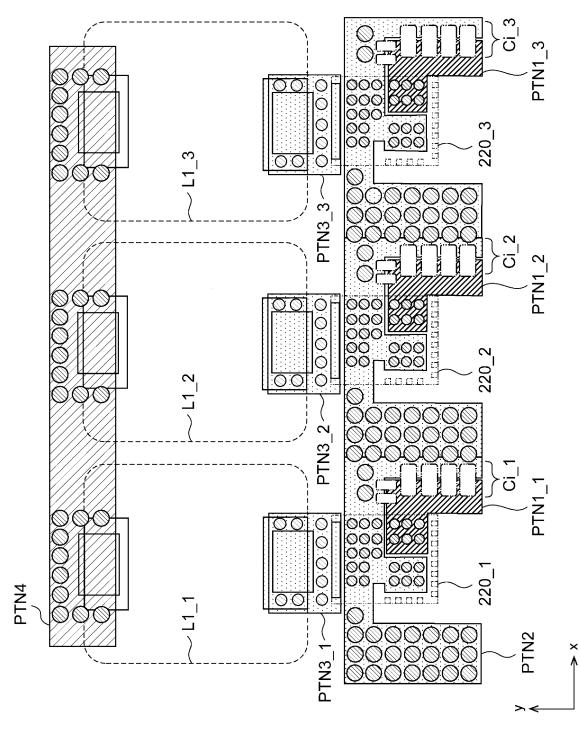

#### 【 0 0 6 2 】

図 1 0 は、比較技術に係る D C / D C コンバータのレイアウト図である。この例では、N = 3 とする。コントローラ 2 1 0 、パワーモジュール 2 2 0 \_ 1 ~ 2 2 0 \_ N 、入力キャパシタ C i 、出力キャパシタ C o （主要構成部品という）はすべて、プリント基板 3 0 0 R の主実装面 S A にレイアウトされている。40

#### 【 0 0 6 3 】

複数のインダクタ L 1 \_ 1 ~ L 1 \_ N は、プリント基板上の第 1 方向（x 方向）に並べて配置される。パワーモジュール 2 2 0 \_ # (# = 1 , 2 ... N ) は、対応するインダクタ L 1 \_ # と第 2 方向（y 方向）に隣接して配置される。これによりパワーモジュール 2 2 0 \_ # とインダクタ L 1 \_ # の間の寄生抵抗を下げることができる。

#### 【 0 0 6 4 】

図 1 1 は、比較技術に係るプリント基板 3 0 0 R の配線パターンを示す図である。図中、丸で示すのはビアホールである。プリント基板 3 0 0 には、複数のパターン配線（プリント配線）P T N 1 \_ 1 ~ P T N 1 \_ 3 , P T N \_ 2 , P T N 3 \_ 1 ~ P T N 3 \_ 3 , P T N 4 が形成される。第 1 パターン配線 P T N 1 \_ 1 ~ P T N 1 \_ 3 は、図 7 の入力ライン 2

10

20

30

40

50

02\_1 ~ 202\_3 に対応している。パワーモジュール 220\_## (# = 1, 2 ... N) の入力ピン V I N は、対応する第 1 パターン配線 P T N 1\_## のパッドと接続される。

#### 【0065】

第 2 パターン配線 P T N 2 は、グランドプレーンであり、インピーダンスを極力小さくするため、全フェーズ共通で形成されている。パワーモジュール 220\_## (# = 1, 2 ... N) の接地ピン P G N D は、対応するパターン配線 P T N 2 のパッドと接続される。

#### 【0066】

第 1 パターン配線 P T N 1\_## と第 2 パターン配線 P T N 2 の間には、入力キャパシタ C i\_## が設けられる。入力キャパシタ C i\_## は、M L C C (多層セラミックコンデンサ) や電解コンデンサであり、あるいはそれらの組み合わせでありうる。

10

#### 【0067】

第 3 パターン配線 P T N 3\_1 ~ P T N 3\_3 は、図 7 においてパワーモジュール 220 の S W ピンとインダクタ L 1 の一端を結ぶ配線である。パワーモジュール 220\_## (# = 1, 2 ... N) の S W ピン S W は、対応する第 3 パターン配線 P T N 3\_## のパッドと接続される。またインダクタ L 1\_## (# = 1, 2 ... N) の電極 E 1 は、対応する第 3 パターン配線 P T N 3\_## のパッドと接続される。

#### 【0068】

第 4 パターン配線 P T N 4 は、図 7 における出力ライン 204 に対応する。インダクタ L 1\_## (# = 1, 2 ... N) の電極 E 2 は、対応する第 4 パターン配線 P T N 4 のパッドと接続される。第 4 パターン配線 P T N 4 とグランドプレーンの間には、図 7 の出力キャパシタ C o (図 11 において不図示) が接続される。

20

#### 【0069】

第 1 パターン配線 P T N 1 ~ 第 4 パターン配線 P T N 4 は、大電流が流れるため、インピーダンスをなるべく小さくする必要がある。したがってこれらのパターン配線 P T N 1 ~ P T N 4 はそれぞれが多層配線を形成しており、図 11 に図示しない別の配線層の配線と、ビアホールを介して接続されている。

#### 【0070】

以上が比較技術に係る部品レイアウトである。続いて、実施の形態に係るレイアウトを説明する。本実施の形態では、N 個のパワーモジュール 220 の少なくともひとつをプリント基板 300 の主実装面 S A と反対側の副実装面 S B に実装することとした。以下、いくつかの実施例を説明する。

30

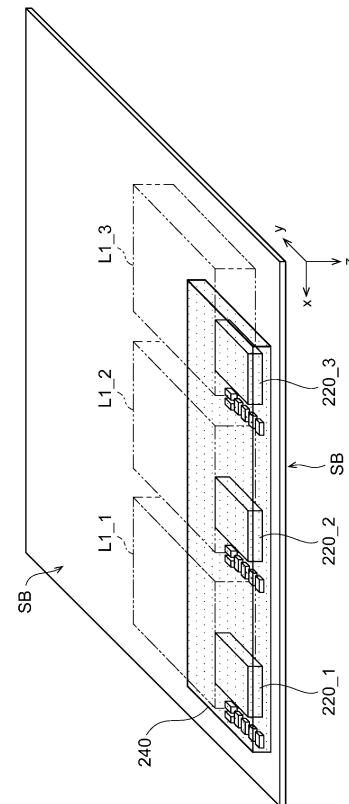

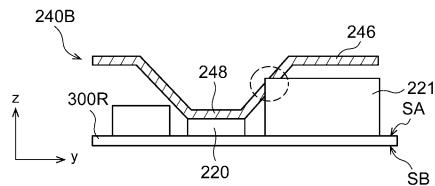

#### 【0071】

##### (実施例 1 - 1)

図 12 (a)、(b) は、実施例 1 - 1 に係る D C / D C コンバータ 200 A のレイアウト図である。図 12 (a) は斜視図を、図 12 (b) は断面図を示す。実施例 1 - 1 では、すべてのパワーモジュール 220\_1 ~ 220\_3 が、副実装面 S B に実装されている。入力キャパシタ C i\_## は、パワーモジュール 220\_## の V I N ピンの直近に接続することが好ましい。そこで実施例 1 - 1 では、入力キャパシタ C i\_## も副実装面 S B に実装される。

#### 【0072】

図 13 は、実施例 1 - 1 に係る D C / D C コンバータ 200 A の配線パターンを示す図である。図 13 において、主実装面 S A 側に実装される部品は破線で示し、副実装面 S B 側に実装される部品は二点鎖線で示す。パターン配線 P T N 1 ~ P T N 4 の機能は、図 11 と同様である。またパターン配線 P T N 1 ~ P T N 4 は多層配線であり、主実装面 S A、副実装面 S B の両面（および中間の配線層）にオーバーラップして形成され、それらは互いにビアホールで電気的に接続されている。

40

#### 【0073】

以上が実施例 1 - 1 に係る D C / D C コンバータ 200 A の構成である。副実装面 S B をパワーモジュール 220 の実装に利用することで、主実装面 S A あるいは副実装面 S B にスペース的な余裕が生ずる。このことによる利点を説明する。

50

**【 0 0 7 4 】**

図14は、DC / DCコンバータ200Aを副実装面SB側からみた斜視図である。DC / DCコンバータ200Aは、ヒートシンク240を備える。ヒートシンク240は、複数のパワーモジュール220\_1～220\_3それぞれの上面と共に接している。副実装面SB側には、パワーモジュール220\_1～220\_Nの周囲に、パワーモジュール220より背の高い部品は存在しないため、大きなヒートシンク240を設けることができ、冷却効率を高めることができる。

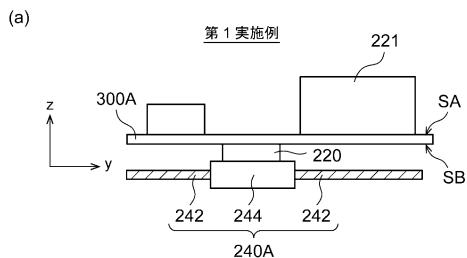

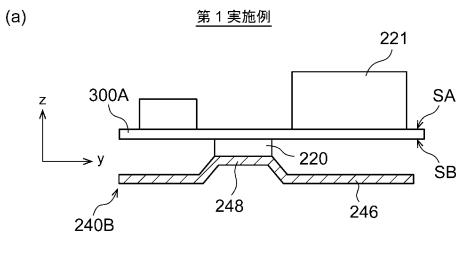

**【 0 0 7 5 】**

ヒートシンクの具体的な構成例を説明する。図15(a)、(b)は、第1構成例に係るヒートシンク240Aの断面図である。図15(a)は、実施例1-1にヒートシンク240Aを適用した様子を示し、図15(b)は、図10の比較技術に同じヒートシンク240Aを適用した様子を示す。

10

**【 0 0 7 6 】**

ヒートシンク240Aは、放熱部分242とコンタクト部分244を有する。放熱部分242には開口が設けられており、この開口にコンタクト部分244が嵌め込まれている。コンタクト部分244は、冷却対象のパワーモジュール220と接触する。

**【 0 0 7 7 】**

実施例1-1と比較技術を対比する。図15(b)に示すように、パワーモジュール220が主実装面SAに実装される比較技術では、パワーモジュール220の周辺に、背の高い部品221(たとえばインダクタ)が存在する。したがって放熱部分242をプリント基板表面に近づけることが難しくなり、コンタクト部分244のZ方向の高さが高くなる。これは熱抵抗の増加の要因となり、すなわち冷却性能の低下を意味する。

20

**【 0 0 7 8 】**

これに対してパワーモジュール220が副実装面SBに実装される実施例1-1では、図15(a)に示すように、パワーモジュール220の周辺に、背の高い部品が存在しないため、放熱部分242をプリント基板表面に近づけることができる。これにより、コンタクト部分244のZ方向の高さを低くできる。これにより熱抵抗を下げ、冷却性能の改善できる。

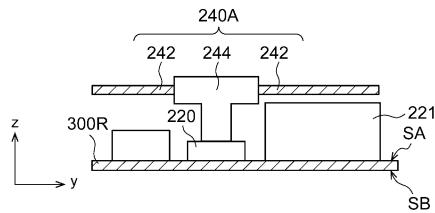

**【 0 0 7 9 】**

図16(a)、(b)は、第2構成例に係るヒートシンク240Bの断面図である。ヒートシンク240Bは、一枚の放熱板246で構成され、絞り加工により凸部248が設けられ、放熱板246は凸部248において、パワーモジュール220の表面と接触する。

30

**【 0 0 8 0 】**

実施例1-1と比較技術を対比する。図16(b)に示すように比較技術では、パワーモジュール220の周辺に、背の高い部品221(たとえばインダクタ)が存在する。凸部248が部品221と干渉するため、比較技術では、第2構成例を採用することが難しい。

**【 0 0 8 1 】**

これに対してパワーモジュール220が副実装面SBに実装される実施例1-1では、パワーモジュール220の周辺に、ヒートシンク240Bの凸部248と干渉する部品が存在しない。したがって、ヒートシンク240Bの設計の自由度が高まり、第2構成例に係るヒートシンク240Bを採用できる。

40

**【 0 0 8 2 】**

図16のヒートシンク240Bは、図15のヒートシンク240Aと比較して構造が簡素化されているため、コストを下げることができる。また開口が不要であることから、電磁ノイズの遮蔽性能が高く、EMC(Electro Magnetic Compatibility)を改善できる。

**【 0 0 8 3 】****(実施例1-2)**

実施例1-2では、N=4のDC / DCコンバータ200Bについて説明する。図17(a)、(b)は、実施例1-2に係るDC / DCコンバータ200Bのレイアウト図である。図17(a)は斜視図を、図17(b)は断面図を示す。実施例1-2では、N個の

50

パワーモジュール 220\_1 ~ 220\_N は、主実装面 S A と副実装面 S B に交互に実装される。具体的には奇数番目のパワーモジュール 220\_# (# = 1, 3, ...) は、副実装面 S B に実装され、偶数番目のパワーモジュール 220\_\* (\* = 2, 4, ...) は、主実装面 S A に実装される。もちろん逆であってもよい。

#### 【0084】

図 18 は、実施例 1 - 2 に係る D C / D C コンバータ 200B の配線パターンを示す図である。図 18 において、主実装面 S A 側に実装される部品は破線で示し、副実装面 S B 側に実装される部品は二点鎖線で示す。パターン配線 P T N 1 ~ P T N 4 の機能は、上述した通りである。またパターン配線 P T N 1 ~ P T N 4 は多層配線であり、主実装面 S A、副実装面 S B の両面（および中間の配線層）にオーバーラップして形成され、それらは互いにピアホールで電気的に接続されている。10

#### 【0085】

実施例 1 - 2 において、N 個のパワーモジュールは、1 番目と 2 番目、3 番目と 4 番目、... とペアをなしている。そしてペアをなす 2 個のパワーモジュール 220\_i, 220\_j は、共通の入力ライン（すなわち共通の第 1 パターン配線 P T N 1\_i, j ）と接続される。

#### 【0086】

実施例 1 - 1 あるいは比較技術のように、すべてのパワーモジュール 220 を同一実装面に実装すると、パワーモジュール 220 ごとに、第 1 パターン配線 P T N 1 を形成する必要がある。これに対して、実施例 1 - 2 のように、主実装面 S A と副実装面 S B に交互にパワーモジュール 220 を実装することで、V I N 端子同士が隣接することになるため、入力ラインを共通化できるという利点がある。20

#### 【0087】

加えて、入力ライン（第 1 パターン配線 P T N 1\_i, j ）が共通化されると、入力キャパシタ C\_i, j も共通化できるという利点がある。すなわち、主実装面 S A 側の入力キャパシタ C\_i, j は、パワーモジュール 220\_i の入力キャパシタとして機能すると同時に、副実装面 S B 側のパワーモジュール 220\_j の入力キャパシタとしても機能するため、入力キャパシタの効果を倍増することができる。あるいは、同じ入力キャパシタの効果を得るために必要なキャパシタの個数を減らすことができ、コストを削減できる。30

#### 【0088】

##### （実施例 1 - 3）

図 19 (a)、(b) は、実施例 1 - 3 に係る D C / D C コンバータ 200D のレイアウト図である。実施例 1 - 3 は、実施例 1 - 2 のインダクタのチップサイズを小さくしたものである。インダクタ L 1 に流れる電流が小さいアプリケーションでは、許容電流が小さい、すなわちチップサイズが小さい部品を選定でき、専有面積を小さくできる。

#### 【0089】

##### （実施例 1 - 4）

図 20 (a)、(b) は、実施例 1 - 4 に係る D C / D C コンバータ 200G のレイアウト図である。実施例 1 - 4 は、実施例 1 - 3 から、インダクタのレイアウトを変更したものであり、具体的には、各インダクタ L 1\_i は、それと対応するパワーモジュール 220\_i と同一面に実装される。これにより対応するインダクタ L 1\_i とパワーモジュール 220\_i を低インピーダンスで接続できる。40

#### 【0090】

より好ましくは、インダクタ L 1\_1 と L 1\_2 のペアは、プリント基板 300G の両面 S A, S B にオーバーラップして実装される。またインダクタ L 1\_3 と L 1\_4 のペアは、プリント基板 300G の両面 S A, S B にオーバーラップして実装される。これにより、隣接するインダクタの間隔を大きくすることができ、図 19 (a)、(b) のレイアウトに比べて熱的な集中を緩和できる。

#### 【0091】

(第2の実施の形態)

実施例1-3において説明したように、インダクタL1に流れるコイル電流が小さいアプリケーションでは、チップサイズを小さくすることができる。しかしながら、インダクタL1に流れるコイル電流が大きいアプリケーションでは、許容電流が大きな、したがってチップサイズの大きな部品を選定せざるをえず、DC/DCコンバータの占有サイズが、インダクタのチップサイズによって制約を受けることとなる。第2の実施の形態では、コイル電流が大きなアプリケーションにおいて、DC/DCコンバータの占有サイズを小さくする技術を説明する。

【0092】

図21は、第2の実施の形態に係るDC/DCコンバータ200Cの等価回路図である。

DC/DCコンバータ200Cにおいて、インダクタL1<sub>#</sub>（# = 1, 2 ... N）はそれぞれ、インダクタンス値が等しく、チップサイズが同一である2個のインダクタチップL1<sub>#a</sub>、L1<sub>#b</sub>の並列接続で構成される。

10

【0093】

2並列の場合のインダクタチップのインダクタンス値は、単一のインダクタチップの場合の1/2倍となる。一方、2並列の場合に、インダクタチップに流れる電流量は、単一のインダクタチップの場合の1/2倍となる。第2の実施の形態では、チップ当たりの電流量を減らすことで、電流容量の小さい、したがってパッケージサイズの小さいインダクタチップを選定することができる。たとえば、単一のインダクタチップの場合に10mm角のインダクタチップを採用する場合、第2の実施の形態の技術思想を導入して、2並列とすることにより、6mm角のインダクタチップを採用することができる。

20

【0094】

DC/DCコンバータ200を搭載した製品を量産する際には、チップ部品の入手性を考慮する必要がある。特に、長い期間にわたり大量に製造、販売される製品では、チップ部品が長期間にわたり安定的に供給される必要がある。現在、チップ部品の小型化が進められており、小さいサイズのインダクタチップのラインナップが増えている代わりに、大きなサイズのチップ部品の入手性が悪くなっている。この観点において、従来において大きなチップサイズのインダクタを、チップサイズの小さい複数のインダクタチップの並列接続に置換することで、入手性の問題を解決することができる。

30

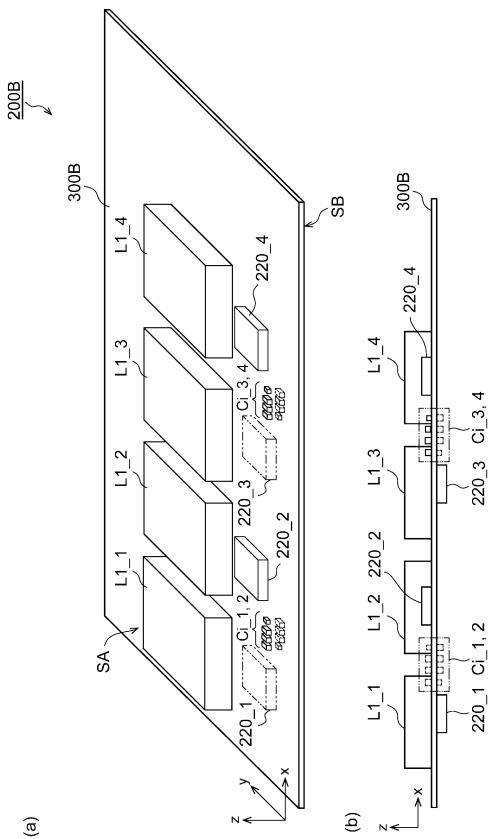

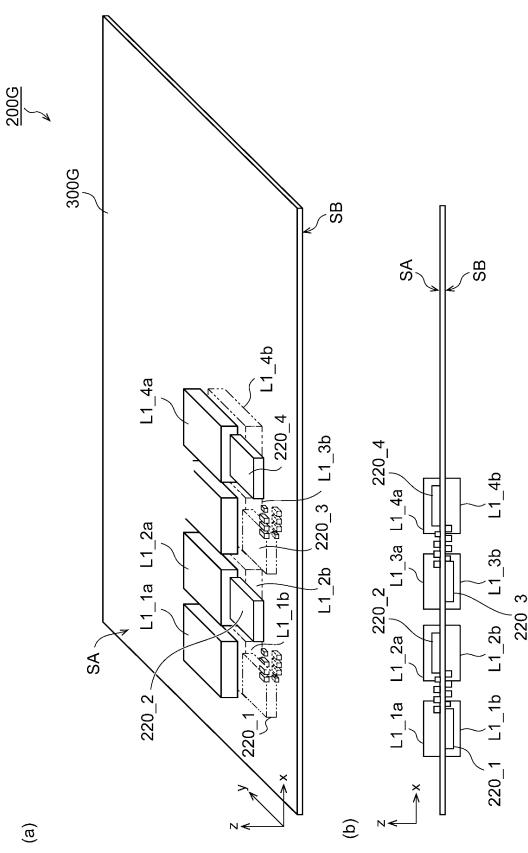

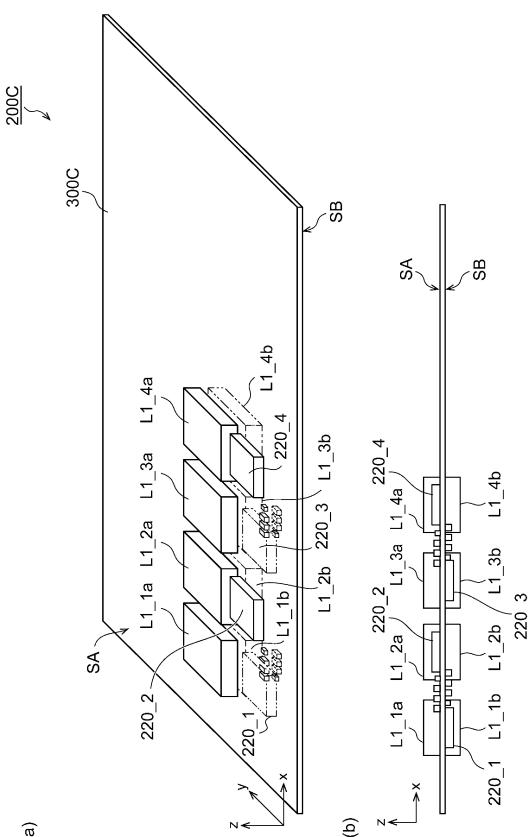

【0095】

(実施例2-1)

図22(a)、(b)は、実施例2-1に係るDC/DCコンバータ200Cのレイアウト図である。図22(a)は斜視図を、図22(b)は断面図を示す。

【0096】

電気的に並列に接続される2個のインダクタチップL1<sub>#a</sub>、L1<sub>#b</sub>は、プリント基板300Cの主実装面SAと副実装面SBに、互いにオーバーラップして実装される。

【0097】

実施例2-1では、N個のパワーモジュール220\_1~220\_Nは、第1の実施の形態の実施例1-2と同様に、主実装面SAと副実装面SBに交互に実装される。

40

【0098】

図23は、実施例2-1に係るDC/DCコンバータ200Cの配線パターンを示す図である。DC/DCコンバータの占有領域のX方向の長さ(全幅)Wは、インダクタチップの横幅wによって支配的に規定され、具体的には、 $W = w \times N + s \times (N - 1)$ となる。sは、インダクタチップのx方向の間隔である。たとえば10mm角のインダクタチップを、6mm角のインダクタチップに置き換えたとすれば、N=4の場合で、DC/DCコンバータの占有領域の全幅を、およそ $4\text{ mm} \times 4 = 16\text{ mm}$ 程度、小さくすることができる。

【0099】

加えて実施例2-1によれば、実施例1-2と同じ効果を得ることができる。すなわち、隣接する2フェーズで入力ラインを共通化でき、また入力キャパシタC<sub>i</sub>、jも共通

50

化できる。

#### 【0100】

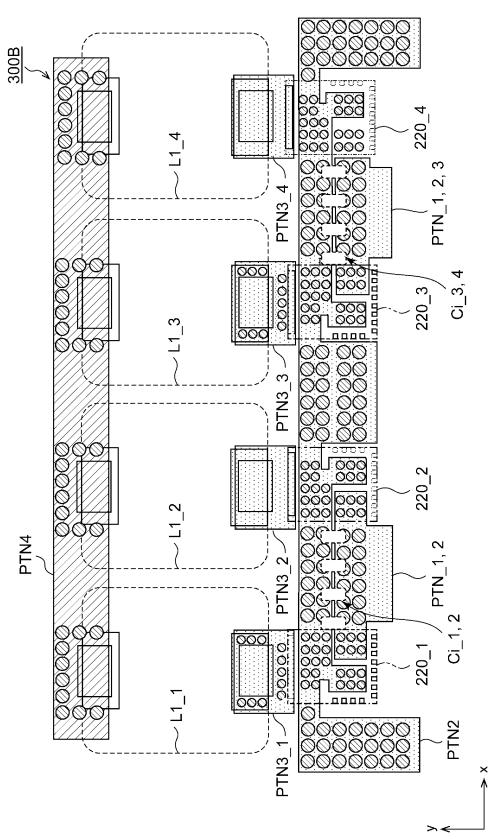

##### (実施例2-2)

図24(a)、(b)は、実施例2-2に係るDC/DCコンバータ200Eのレイアウト図である。図24(a)は斜視図を、図24(b)は断面図を示す。実施例2-2は、複数のパワーモジュール220\_1~220\_4が副実装面SBに実装される点において、図12の実施例1-1と共通する。図24では、入力キャパシタCiは省略するが、実施例1-1と同様に、副実装面SBに実装すればよい。

#### 【0101】

実施例2-2によれば、実施例2-1と同様に、DC/DCコンバータ200Eの専有面積を小さくできる。

10

#### 【0102】

##### (実施例2-3)

図25(a)、(b)は、実施例2-3に係るDC/DCコンバータ200Fのレイアウト図である。図25(a)は斜視図を、図25(b)は断面図を示す。実施例2-3では、複数のパワーモジュール220\_1~220\_4はすべて主実装面SA側に実装される。

#### 【0103】

実施例2-3によれば、実施例2-1、実施例2-2と同様に、DC/DCコンバータ200Fの専有面積を小さくできる。

#### 【0104】

20

##### (変形例2-1)

実施例2-1~2-3において、フェーズごとのインダクタL1を、2個のインダクタチップの並列接続としたが、チップの個数は2に限定されず、3個以上としてもよい。

#### 【0105】

##### (実装技術)

続いてパワーモジュール220の実装技術を説明する。

#### 【0106】

図7を参照する。DC/DCコンバータ200において、入力ライン202のインダクタ成分や抵抗成分は極力小さいことが望ましい。またPGNDピンについても、なるべく小さなインピーダンスで接地されることが望ましい。図11や図13に示したように、第1パターン配線PTN1には、VINピンを半田付けするためのパッド(ランド)が形成され、第2パターン配線PTN2には、PGNDピンを半田付けするためのパッド(ランド)が形成される。パターン配線PTN1, PTN2のインピーダンスを下げるために、多層配線が採用され、ビアホールが多数設けられるが、インピーダンスを可能な限り下げるためには、パッド(ランド)の内側に、ビアホールを形成することが要求される。このようなビアホールを、パッド内ビアと称する。

30

#### 【0107】

図11の比較技術では、パワーモジュール220が主実装面にのみ実装されるため、パッド内ビアの形成に格別の困難性はない。ところが、実施例1-1, 1-2, 1-3, 2-1, 2-2では、パワーモジュール220が副実装面に実装されるため、副実装面にパッド内ビアを形成する必要がある。コストを無視すれば、副実装面にパッド内ビアを形成することは不可能ではないが、コストを考慮した場合、従来の表面実装では、副実装面にパッド内ビアを設けることは容易ではない。実施の形態で説明した実装技術は、パッド内ビアを必要とするパワーモジュール220の実装に好適である。

40

#### 【0108】

以上、本発明を実施の形態をもとに説明した。実施の形態は例示であり、それらの各構成要素や各処理プロセスの組合せにいろいろな変形例が可能のこと、またそうした変形例も本発明の範囲にあることは当業者に理解されるところである。

#### 【符号の説明】

#### 【0109】

50

- 1 0 プリント基板

1 2 , 1 4 , 1 6 パッド

1 7 パッド内ビア

1 8 パッド

1 9 パッド内ビア

S 1 第1面

S 2 第2面

2 0 スクリーン

2 2 開口

3 0 クリーム半田

3 2 クリーム半田

3 4 半田の漏れ

4 0 部品

E 1 , E 2 電極

E 3 裏面電極

5 0 スクリーン

5 2 , 5 4 開口

5 6 凹部

6 0 クリーム半田

7 0 部品

10

## 【図面】

## 【図1】

## 【図2】

20

30

40

50

【図3】

【図4】

【図5】

【図6】

10

20

30

40

50

【図 7】

【図 8】

10

20

30

40

【図 9】

【図 10】

50

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

10

20

30

40

50

【図 15】

(b) 比較技術

【図 16】

(b) 比較技術

10

【図 17】

【図 18】

20

30

40

50

【図 19】

【図 20】

10

20

【図 21】

【図 22】

30

40

50

【図 2 3】

【図 2 4】

【図 2 5】

10

20

30

40

50

---

フロントページの続き

(51)国際特許分類

F I

B 2 3 K      1/00      3 3 0 E

ンメント内

(72)発明者 和田 克司

東京都港区港南1丁目7番1号 ソニーグローバルマニュファクチャリング&オペレーションズ株

式会社内

審査官 齊藤 健一

(56)参考文献 中国特許出願公開第1505456(CN,A)

特開平6-334323(JP,A)

特開2008-78271(JP,A)

特開平1-236693(JP,A)

米国特許第4739919(US,A)

米国特許第5373984(US,A)

(58)調査した分野 (Int.Cl., DB名)

B 2 3 K 1 / 0 0    3 / 0 8

B 4 1 M 1 / 1 2

B 4 1 M 1 / 2 6    1 / 3 8

H 0 5 K 1 / 0 0    3 / 4 6

H 0 5 K 1 3 / 0 4