(19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第5479249号 (P5479249)

(45) 発行日 平成26年4月23日 (2014.4.23)

(24) 登録日 平成26年2月21日 (2014.2.21)

(51) Int. CL. FL

HO3H 11/04 (2006, 01) HO3H 11/04

> 請求項の数 7 (全 15 頁)

特願2010-157703 (P2010-157703) (21) 出願番号

(22) 出願日 平成22年7月12日 (2010.7.12) (65) 公開番号 特開2012-23433 (P2012-23433A)

(43) 公開日 平成24年2月2日(2012.2.2) 審查請求日

平成25年3月27日 (2013.3.27)

||(73)特許権者 302062931

Н

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

|(74)代理人 100089071

弁理士 玉村 静世

(72) 発明者 勝部 勇作

> 神奈川県横浜市戸塚区吉田町292番地 株式会社日立製作所 コンシューマエレク

トロニクス研究所内

(72) 発明者 五十嵐 豊

神奈川県横浜市戸塚区吉田町292番地 株式会社日立製作所 コンシューマエレク

トロニクス研究所内

最終頁に続く

(54) 【発明の名称】カットオフ周波数自動調整回路及び携帯情報端末

#### (57)【特許請求の範囲】

## 【請求項1】

電圧電流変換回路、充電回路、放電回路、複数の静電容量を有するデジタル容量、上記 デジタル容量に入力される電圧と基準電圧との対比を行う比較器及び上記デジタル容量を 制御する容量制御回路を含み、

上記デジタル容量はスイッチによって上記充電回路及び上記放電回路に接続され、

上記スイッチ及び上記容量制御回路にはリセット信号が入力され、

上記デジタル容量は上記複数の静電容量の全部又は一部がスイッチングにより並列的に 接続され、

上記リセット信号が第1レベルのとき、上記デジタル容量が上記放電回路に接続され、

上記リセット信号が第2レベルのとき、上記デジタル容量が上記充電回路に接続され、

上記容量制御回路は、上記リセット信号が第2レベルになったときから、上記比較器に よって上記デジタル容量に入力される電圧が上記基準電圧より高くなったことが検知され るまでの時間を計測し、その計測結果と、上記デジタル容量の目標値と、上記デジタル容 量の現在の値とに基づいて上記デジタル容量の次の設定値を求める処理を、所定の条件下 で繰り返すことによって、上記デジタル容量を制御することを特徴とするカットオフ周波 数自動調整回路。

#### 【請求項2】

上記容量制御回路は、第1カウンタと、第2カウンタと、第1レジスタと、第2レジス タとを含み、

上記第2カウンタを用いて、上記リセット信号が第2レベルになったときから、上記比較器によって上記デジタル容量に入力される電圧が上記基準電圧より高くなったことが検知されるまでの時間が計測され、

上記第1レジスタには、上記デジタル容量の目標値が設定され、

上記第2レジスタには、上記デジタル容量の次の設定値が保持され、

上記第1カウンタを用いて、上記デジタル容量の次の設定値を求める処理が繰り返される請求項1記載のカットオフ周波数自動調整回路。

### 【請求項3】

上記容量制御回路は、上記比較器での比較結果に基づいて、上記デジタル容量の電位と 上記基準電圧との差分が所定の電位差以内になるように上記デジタル容量を制御する請求 項2記載のカットオフ周波数自動調整回路。

【請求項4】

上記容量制御回路は、上記デジタル容量の設定条件で、チャネルフィルタ回路内のデジタル容量を設定する請求項3記載のカットオフ周波数自動調整回路。

#### 【請求項5】

上記デジタル容量の最小容量ステップ幅を Cとし、上記電圧電流変換回路で直流電圧を電流に変換するための抵抗をR1としたとき、上記容量制御回路は、クロック信号に同期してチャネルフィルタ回路内のデジタル容量を設定し、上記クロック信号の周波数は、1/( C・R1)よりも大きく設定される請求項4記載のカットオフ周波数自動調整回路。

【請求項6】

上記チャネルフィルタ回路の複数のカットオフ周波数に対応した上記容量制御回路はターゲットとする複数の目標値を持ち、第1のカットオフ周波数に対応する第1の目標値で上記処理を繰り返すことで得られた第1のデジタル容量設定値を記憶し、第2のカットオフ周波数に対応する第2の目標値で上記処理を繰り返すことで得られた第2のデジタル容量設定値を記憶し、

第1のカットオフ周波数に設定する際は、上記容量制御回路により上記第1のデジタル容量設定値が用いられ、第2のカットオフ周波数に設定する際は、上記容量制御回路により上記第2のデジタル容量設定値が用いられる請求項4記載のカットオフ周波数自動調整回路。

【請求項7】

請求項1記載のカットオフ周波数自動調整回路を備える携帯情報端末。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、フィルタのカットオフ周波数自動調整技術にかかり、例えば携帯情報端末に搭載されるフィルタのカットオフ周波数自動調整回路に適用して有効な技術に関する。

【背景技術】

[0002]

従来、無線信号処理回路は、各機能ブロック(信号を増幅する増幅器、信号の周波数を変換するミキサ、信号の所望の帯域のみ通過させるフィルタなど)ごとに個別部品を用いて構成していた。これが近年の半導体技術の向上により、無線信号処理回路を構成する機能ブロックを複数、1つの半導体チップへ内蔵することが可能となってきた。半導体チップに内蔵された無線信号処理回路は、アンテナから受信した高周波信号を、高い品質(低雑音、所望信号帯域以外の帯域の信号を抑圧など)でより低い周波数帯の信号に変換する

[0003]

無線信号処理回路を低コストで実現するためには、より多くの無線信号処理回路を構成する機能ブロックを1つの半導体チップへ内蔵する必要がある。この目的に対する障害の一つが所望ではない帯域の信号を抑圧するフィルタ回路の半導体チップへの内蔵である。

10

20

40

30

このフィルタ回路は、SAW (Surface Acoustic Wave)フィルタ、誘電体フィルタなどが用いられる。これにより所望以外の帯域に存在する信号を抑圧するのであるが、SAWフィルタや誘電体フィルタは半導体チップへ内蔵できない。

#### [0004]

一般に、個別部品での無線信号処理回路はスーパーへテロダイン方式と呼ばれる構成で、SAWフィルタや誘電体フィルタを必要とする(スーパーへテロダイン方式に関しては、例えば、非特許文献 1 参照)が、SAWフィルタや誘電体フィルタは半導体チップへ内蔵することはできない。そこで、半導体で製造する無線信号処理回路をスーパーへテロダイン方式で構成する場合、半導体チップ外部にSAWフィルタや誘電体フィルタを外付けすることになる。そのため部品点数、実装面積が増大することになる。

[0005]

そこで、半導体回路の特徴(半導体チップ間の部品定数の絶対値はばらつくが、1つの半導体チップ内での部品定数の相対値は高精度で一致する)を利用して、SAWフィルタや誘電体フィルタが不要な無線信号処理回路方式が提案されている。これは、ゼロIF方式、低IF方式などである。いずれも外付けのSAWフィルタや誘電体フィルタを必要とせず、所望の帯域以外の帯域に存在する信号の抑圧は半導体へ内蔵可能なフィルタで行なう(無線方式、或いはシステム的な要求より一部のフィルタを外付けする必用が生ずることもある)。

[0006]

ゼロIF方式、低IF方式では、所望のチャネル以外の信号を除去するチャネルフィルタをミキサ回路で周波数変換した後の低周波数帯の信号を扱うステージに配置する。低周波数帯の信号を扱うステージにフィルタを配置することにより、SAWフィルタや誘電体フィルタの代わりにフィルタ処理を半導体回路、具体的には能動RCフィルタなどで実現することが可能となる。

[0007]

チャネルフィルタは、所望チャネルの隣接チャネル、隣々接チャネル等所望チャネル以外に存在する信号を抑圧するものである。しかし、チャネルフィルタの直流利得 - 3 d B の利得を有する周波数であるカットオフ周波数が、半導体の製造バラツキ、素子の温度、電源電圧特性等でずれこむと受信する信号品質が劣化する。

[00008]

例えば、カットオフ周波数が高いほうにずれると、隣接チャネル、隣々接チャネル等に存在する信号の抑圧度が劣化するし、カットオフ周波数が低いほうにずれると、所望チャネルの信号電力が下がるので、信号対雑音比が劣化し、受信感度が落ちる。また、デジタル変調された信号を受信する場合、シンボル間干渉特性が劣化するので、受信するデータ誤り率に影響が及ぶ。

[0009]

そこで、例えば特許文献1に記載されているように、チャネルフィルタのカットオフ周波数を自動調整する回路が必要となる。特許文献1によれば、チャネルフィルタ回路の帰還容量及び負帰還容量(接地容量)ごとにフィルタカットオフ周波数自動調整回路及び誤差修正用のレジスタを設け、これにより、帰還容量及び負帰還容量の容量差による誤差の拡大を招くことなく、フィルタカットオフ周波数の調整を可能にしている。

【先行技術文献】

【特許文献】

[0010]

【特許文献1】特開2009-94734号公報

【非特許文献】

[0011]

【非特許文献 1】Thomas H.Lee著、The Design of CMOS Radio-Frequency Integrated Circuits, CAMBRIDGE

【発明の概要】

10

20

30

40

#### 【発明が解決しようとする課題】

### [0012]

上記のように特許文献1によれば、チャネルフィルタ回路の帰還容量及び負帰還容量(接地容量)ごとにフィルタカットオフ周波数自動調整回路及び誤差修正用のレジスタを設け、これにより、帰還容量及び負帰還容量の容量差による誤差の拡大を招くことなく、フィルタカットオフ周波数の調整を可能にしている。それにより、使用する容量比の大きなフィルタカットオフ周波数を自動調整すること、並びにその自動調整にかかる時間を短縮することができる。

#### [0013]

様々なカットオフ周波数に対応するフィルタを形成する場合には、より広大な範囲で調整可能なデジタル容量が必要になる。そのようなデジタル容量を有するフィルタのカットオフ周波数自動調整技術について本願発明者が検討したところ、カットオフ周波数補正精度を更に向上させることによって、フィルタのカットオフ周波数を、その調整範囲内の任意の設定値に自動調整可能にする必要性が見いだされた。

#### [0014]

本発明の目的は、フィルタのカットオフ周波数を、その調整範囲内の任意の設定値に自動調整可能なカットオフ周波数自動調整回路、及びそのようなカットオフ周波数自動調整回路を備えた携帯情報端末を提供することにある。

#### [0015]

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

### 【課題を解決するための手段】

#### [0016]

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

## [0017]

すなわち、電圧電流変換回路、充電回路、放電回路、複数の静電容量を有するデジタル容量、上記デジタル容量に入力される電圧と基準電圧との対比を行う比較器及び上記デジタル容量を制御する容量制御回路を含んでカットオフ周波数自動調整回路を構成する。このとき、上記デジタル容量はスイッチによって上記充電回路及び上記放電回路に接続され、上記スイッチ及び上記容量制御回路にはリセット信号が入力され、上記デジタル容量は上記複数の静電容量の全部又は一部がスイッチングにより並列的に接続され、上記リセット信号が第1レベルのとき、上記デジタル容量が上記放電回路に接続され、上記リセット信号が第2レベルのとき、上記デジタル容量が上記充電回路に接続される。上記容量制御回路は、上記リセット信号が第2レベルになったときから、上記比較器によって上記デジタル容量に入力される電圧が上記基準電圧より高くなったことが検知されるまでの時間を計測し、その計測結果と、上記デジタル容量の目標値と、上記デジタル容量の現在の値とに基づいて上記デジタル容量の次の設定値を求める処理を、所定の条件下で繰り返すことによって、上記デジタル容量を制御する。

#### 【発明の効果】

[0018]

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

## [0019]

すなわち、フィルタのカットオフ周波数を、その調整範囲内の任意の設定値に自動調整可能なカットオフ周波数自動調整回路、及びそのようなカットオフ周波数自動調整回路を備えた携帯情報端末を提供することができる。

### 【図面の簡単な説明】

#### [0020]

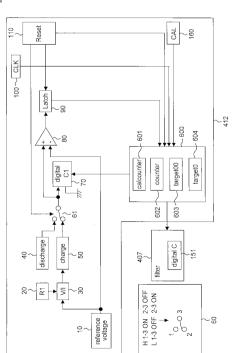

【図1】本発明の実施の形態1にかかるカットオフ周波数自動調整回路の構成例ブロック

10

20

30

40

10

20

30

40

50

図である。

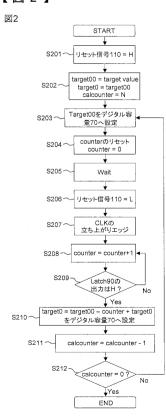

【図2】図1に示されるカットオフ周波数自動調整回路における主要処理のフローチャートである。

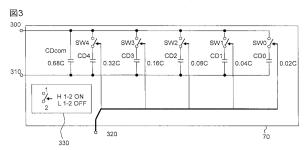

【図3】図1におけるカットオフ周波数自動調整回路に含まれるデジタル容量の構成例回路図である。

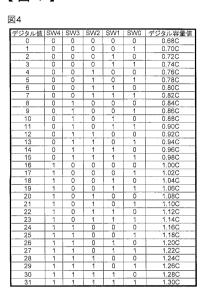

【図4】デジタル容量に入力されるデジタル値と、デジタル容量の入力端子と出力端子と の間における容量値との関係説明図である。

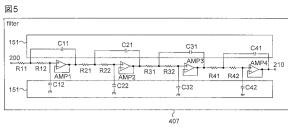

【図 5 】図 1 におけるカットオフ周波数自動調整回路に含まれるチャネルフィルタ回路の 構成例回路図である。

【図 6 】デジタル容量におけるデジタル値とデジタル容量値とカットオフ周波数との関係 説明図である。

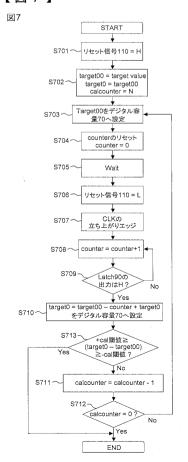

【図7】本発明の実施の形態2にかかるカットオフ周波数自動調整回路における主要処理のフローチャートである。

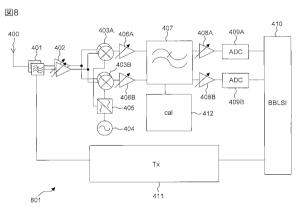

【図8】本発明にかかるカットオフ周波数自動調整回路を搭載する携帯情報端末の構成例 ブロック図である。

【発明を実施するための形態】

#### [0021]

1.実施の形態の概要

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。代表的な実施の形態についての概要説明で括弧を付して参照する図面中の参照符号はそれが付された構成要素の概念に含まれるものを例示するに過ぎない。

[0022]

【1】本発明の代表的な実施の形態に係るカットオフ周波数自動調整回路(412)は、電圧電流変換回路(30)、充電回路(50)、放電回路(40)、複数の静電容量を有するデジタル容量(70)、上記デジタル容量に入力される電圧と基準電圧との対比を行う比較器(80)及び上記デジタル容量を制御する容量制御回路(600)を含む。上記デジタル容量はスイッチによって上記充電回路及び上記放電回路に接続され、上記可以を量は上記複数でまる。上記でジタル容量がより立れ、上記でジタル容量は上記複数が1レベルのとき、上記でジタル容量が上記放電回路に接続され、上記リセット信号が第2レベルのとき、上記でジタル容量が上記充電回路に接続され、上記リセット信号が第2レベルのとき、上記でジタル容量が上記充電回路に接続される。上記容量制御回路は、上記リセット信号が第2レベルになったときから、上記比較器によって上記でジタル容量に入力される電圧が上記基準電圧より高くなったことが検知されるまでの時間を計測し、その計測結果と、上記でジタル容量の目標値と、上記でジタル容量の現在の値とに基づいたことによって、上記でジタル容量の次の設定値を求める処理を、所定の条件でに繰り返すことによって、上記でジタル容量を制御する。

## [0023]

上記の構成によれば、上記リセット信号が第2レベルになったときから、上記比較器によって上記デジタル容量に入力される電圧が上記基準電圧より高くなったことが検知されるまでの時間が計測され、その計測結果と、上記デジタル容量の目標値と、上記デジタル容量の現在の値とに基づいて上記デジタル容量の次の設定値を求める処理が、所定の条件下で繰り返されることによって、上記デジタル容量が制御される。このようにしてカットオフ周波数の自動調整が行われ、上記デジタル容量が上記目標値に調整される。上記目標値は、調整範囲内の任意の設定値とすることができる。

[0024]

[2]上記[1]において、上記容量制御回路は、第1カウンタ(calcounter;601)と、第2カウンタ(counter;602)と、第1レジスタ(target0;603)と、第2レジスタ(target0;604)とを含んで構成することができる。上記第2カウンタを用いて、上記リセット信号が第2レベルになったときから、上記比較器によって上記デジタル容量に入力される電圧が上記基準電圧より高くなっ

たことが検知されるまでの時間が計測され、上記第1レジスタには、上記デジタル容量の目標値が設定され、上記第2レジスタには、上記デジタル容量の次の設定値が保持され、上記第1カウンタを用いて、上記デジタル容量の次の設定値を求める処理が繰り返される。これにより、上記〔1〕における容量制御回路の機能を容易に実現することができる。

### [0025]

[3]上記[2]において、上記比較器での比較結果に基づいて、上記デジタル容量の電位と上記基準電圧との差分が所定の電位差以内になるように上記デジタル容量を制御するように上記容量制御回路を構成することができる。

#### [0026]

〔4〕上記〔3〕において、チャネルフィルタ回路のカットオフ周波数を自動調整する場合、上記容量制御回路は、上記デジタル容量の設定条件で、チャネルフィルタ回路内のデジタル容量を設定する。これにより、チャネルフィルタ回路のカットオフ周波数が自動調整される。

## [0027]

[5]上記[4]において、カットオフ周波数の補正精度を向上させるには、上記デジタル容量の最小容量ステップ幅を Cとし、上記電圧電流変換回路で直流電圧を電流に変換するための抵抗をR1としたとき、上記容量制御回路は、クロック信号に同期してチャネルフィルタ回路内のデジタル容量を設定し、上記クロック信号の周波数は、1/( C・R1)よりも大きく設定する。

## [0028]

〔6〕上記〔4〕において、上記チャネルフィルタ回路の複数のカットオフ周波数に対応した上記容量制御回路はターゲットとする複数の目標値を持ち、第1のカットオフ周波数に対応する第1の目標値で上記処理を繰り返すことで得られた第1のデジタル容量設定値を記憶し、第2のカットオフ周波数に対応する第2の目標値で上記処理を繰り返すことで得られた第2のデジタル容量設定値を記憶しておく。そして、第1のカットオフ周波数に設定する際は、上記容量制御回路により上記第1のデジタル容量設定値を使用し、第2のカットオフ周波数に設定する際は、上記容量制御回路により上記第2のデジタル容量設定値を使用する。このようにすることで、カットオフ周波数の切り替えを高速に行うことができる。

### [0029]

[7]上記[1]のカットオフ周波数自動調整回路は、携帯情報端末に搭載することができる。携帯情報端末(801)には、チャネルフィルタ回路(407)が搭載され、このチャネルフィルタ回路のカットオフ周波数を、上記カットオフ周波数自動調整回路によって自動調整するように構成することができる。

## [0030]

2.実施の形態の詳細

実施の形態について更に詳述する。

### [0031]

《実施の形態1》

図8には、本発明にかかる携帯情報端末の構成例が示される。

## [ 0 0 3 2 ]

この携帯情報端末801は、アンテナ400、デュプレクサ401、低ノイズアンプ(LNA)402、ミキサ403A,403B、局部発振回路404、90度移相回路405、第1の増幅回路406A,406B、チャネルフィルタ回路407、第2の増幅回路408A、408B、AD(アナログ・デジタル)変換回路409A,409B、ベースバンドLSI410、送信回路411、カットオフ周波数自動調整回路412を含む。

#### [0033]

デュプレクサ401は、アンテナ400からの信号から所望帯域のみ通過させる。LNA402は、デュプレクサ401の出力信号を低雑音で増幅する。局部発振回路404は、デュプレクサ401の出力信号のうち、所望のキャリア周波数の整数倍で発振する。9

20

10

30

40

0度移相回路405は、局部発振回路404の出力信号 I と、その位相を90度ずらした信号 Q とを出力する。ミキサ403A,403Bは、LNA402の出力信号と90度移相回路405の出力信号とを混合する。第1の増幅回路406A,406Bは、ミキサ403A,403Bの出力信号を増幅する。チャネルフィルタ回路407は、第1の増留の路406A,406Bの出力信号から所望のチャネル周波数帯域のみ通過させる。第1の増幅回路408A,408Bは、チャネルフィルタ回路407の出力信号を増幅する。インでは、第2の増幅回路408A,409Bは、第2の増幅回路408A,409Bの出力信号を増幅回路408A,409Bは、第2の増幅回路408A,409Bの出力信号をで、信号の受信を行う。信号の送信は送信回路411により行われる。すなわち送信回路411は、ベースバンドLSI410からの変調出力を増幅し、スインを増加まる。デュプレクサ401に出力する。デュプレクサ401では、タ処理し、周波数変換してデュプレクサ401に出力する。デュプレクサ401では401を通過した信号はアンテナ40のから送信帯域のみ通過させる。デュプレクサカットオフ周波数は、カットオフ周波数自動調整回路412により自動調整される。

[0034]

図1には、上記カットオフ周波数自動調整回路412の構成例が示される。

[0035]

カットオフ周波数自動調整回路 4 1 2 は、特に制限されないが、抵抗 2 0 、電圧電流変換回路 ( V / I ) 3 0 、放電回路 ( d i s c h a r g e ) 4 0 、充電回路 ( c h a r g e ) 5 0 、スイッチ 6 1 、デジタル容量 7 0 、コンパレータ 8 0 、ラッチ回路 ( L a t c h ) 9 0 、チャネルフィルタ回路 4 0 7 、演算回路 6 0 0 を含む。

[0036]

基準電圧源によって基準電圧(reference voltage)10が形成される。この基準電圧10は、温度や電源電圧に依存しない直流電圧VBGとされる。抵抗20の値はR1とされる。VBGは電圧電流変換回路30と抵抗20により直流電流Iに変換される。直流電流Iは次式によって示される。

[0037]

【数1】

数1

I = VBG/R1

### [0038]

[0039]

この直流電流Ⅰは充電回路50に伝達される。充電回路50と放電回路40とはスイッ チ 6 1 により選択的にデジタル容量 7 0 に結合される。スイッチ 6 1 は、リセット信号 1 10によって動作制御される。60はスイッチ61の極性図である。これに従えば、リセ ット信号 1 1 0 が H レベル ( 論理値 " 1 " に対応する ) の場合に、放電回路 4 0 が選択的 にデジタル容量70に結合され、リセット信号110がLレベル(論理値"0"に対応す る)の場合に、充電回路50が選択的にデジタル容量70に結合される。デジタル容量7 0は、演算回路600によって設定される。このような意味で演算回路600は、本発明 における容量制御回路の一例とされる。チャネルフィルタ回路407は、デジタル容量1 5 1 を含み、このデジタル容量 1 5 1 は、上記演算回路 6 0 0 によって、上記デジタル容 量70の値に等しくなるように設定される。コンパレータ80は、デジタル容量70の入 力端子のレベルと基準電圧10とを比較する。すなわち、デジタル容量70の端子間電圧 (VBG/R1/C1× t)と、基準電圧10(VBG)を対比する。この比較結果は ラッチ回路90に保持される。ラッチ回路90の出力は演算回路600に供給される。ラ ッチ回路90は、リセット信号110によって初期化される。演算回路600は、第1カ ウンタ(calcounter)601、第2カウンタ(counter)602、第1 レジスタ(target00)603、第2レジスタ(target0)604を含む。

10

20

30

40

デジタル容量70は、図3に示されるように構成される。

#### [0040]

図3に示されるデジタル容量70は、複数の静電容量(単に「容量」という)CDcom、CD0~CD4、スイッチSW0~SW4を含む。容量CD0~CD4は、対応するスイッチSW0~SW4に直列接続されている。スイッチSW0~SW4は、デジタル値入力端子320を介して伝達されたデジタル値によって動作制御される。300は入力端子、310は出力端子とされる。尚、330はスイッチSW0~SW4の極性図である。本例では、デジタル値入力端子320を介して伝達されたデジタル値が論理値"1"の場合に対応するスイッチSW0~SW4がオン(導通)されるようになっている。スイッチSW0~SW4のスイッチングにより、複数の容量CDcom、CD0~CD4の全部又は一部が並列的に接続されるようになっている。

[0041]

図3における太線は、5ビット分の5本の信号線をまとめて表現したものである。このデジタル容量は、デジタル値入力端子320から入力される5ビットのデジタル値に応じて、-32%~+30%の範囲で容量値を可変できるものとする。

#### [0042]

- 3 2 % ~ + 3 0 %の可変範囲を実現するため、容量 C D c o m は、スイッチ S W 0 ~ S W 4 が全てオフの時(スイッチ極性図 3 3 0 に従えば、デジタル値入力端子 3 2 0 からスイッチ S W 0 ~ S W 4 へ全てLレベルの信号が入力された時)の容量値となるので、容量 C D c o m の値は、 0 . 6 8 C となる。ここで、「C」はデジタル容量で実現したい容量の大きさの中心値を意味する。 5 ビットで、 - 3 2 % ~ + 3 0 %の可変範囲を実現するためには、 2 % 刻みとなるので、容量 C D 4 の値は 0 . 3 2 C 、容量 C D 3 の値は 0 . 1 6 C 、容量 C D 2 の値は 0 . 0 8 C 、容量 C D 1 の値は、 0 . 0 4 C となる。

[0043]

図4には、デジタル値入力端子320から入力される5ビットのデジタル値によってスイッチSW0~SW4へ与えられる値と、入力端子300と出力端子320との間における容量値との関係が示される。図4に示されるように、デジタル値入力端子320から入力される5ビットのデジタル値に応じてスイッチSW0~SW4の状態が制御されることにより、-32%~+30%の可変範囲でデジタル容量70の値が変更される。

[0044]

図5には、図1におけるチャネルフィルタ回路407の構成例が示される。

## [0045]

図5に示されるチャネルフィルタ回路407は、8次のバタワース低域通過フィルタを 正帰還型低域通過回路を用いて構成したものであり、容量C11~C42、抵抗R11~ R 4 2 、アンプ A M P 1 ~ A M P 4 を含む。 2 0 0 は入力端子、 2 1 0 は出力端子である 。アンプAMP1~AMP4は、それぞれ演算増幅器がボルテージホロワとして用いられ る。入力端子は、抵抗R11,R12を介してアンプAMP1の非反転入力端子(+)に 結合される。アンプAMP1の出力端子は、抵抗R21,R22を介してアンプAMP2 の非反転入力端子(+)に結合される。アンプAMP2の出力端子は、抵抗R21,R2 2 を介してアンプAMP3の非反転入力端子(+)に結合される。アンプAMP3の出力 端子は、抵抗R41,R42を介してアンプAMP4の非反転入力端子(+)に結合され る。アンプAMP4から出力端子210が引き出される。容量C11は、抵抗R12とア ンプAMP1に並列接続される。容量C21は、抵抗R22とアンプAMP2に並列接続 される。容量C31は、抵抗R32とアンプAMP3に並列接続される。容量C41は、 抵抗R42とアンプAMP4に並列接続される。容量C12は、アンプAMP1の非反転 入力端子(+)とグランドとの間に接続される。容量 C 2 2 は、アンプ A M P 2 の非反転 入力端子(+)とグランドとの間に接続される。容量 C 3 2 は、アンプ A M P 3 の非反転 入力端子(+)とグランドとの間に接続される。容量C42は、アンプAMP4の非反転 入力端子(+)とグランドとの間に接続される。

[0046]

10

20

30

入力端子200を介して入力された信号は、アンプAMP1~AMP4、容量C11~C42、抵抗R11~R42を含んで成る低域通過フィルタにより、所望のカットオフ周波数より高い周波数帯の信号が抑圧されてから、出力端子210を介して出力される。このチャネルフィルタ回路407のカットオフ周波数は、1/(2 抵抗変化量×容量変化量)に比例して変化する。

### [0047]

図5の容量C11~C42は、それぞれデジタル容量151となっており、演算回路600から与えられたデジタル値により容量値が変えられることで、フィルタのカットオフ周波数の調整が可能とされる。

[0048]

10

20

次に、図2に示されるフローチャートに従って上記構成の動作について説明する。

#### [0049]

まず、リセット信号 1 1 0 が H レベルとなり、ラッチ回路 9 0 と演算回路 6 0 0 とがリセットされる(S 2 0 1)。そして演算回路 6 0 0 内の第 1 レジスタ(target 0 0 ) 6 0 3 が初期値(目標値)「target value」に設定され、演算回路 6 0 0 内の第 2 レジスタ(target 0 ) 6 0 4 が第 1 レジスタ(target 0 0 ) 6 0 3 と等しく設定され、第 1 カウンタ(calcounter) 6 0 1 が N (Nは 1 以上の整数)に設定される(S 2 0 2)。

#### [0050]

第 2 レジスタ( t a r g e t 0 ) 6 0 4 の値は、デジタル容量 7 0 のスイッチ S W 0 ~ S W 4 へ設定される ( S 2 0 3 )。

[0051]

ステップ S 2 0 1 でリセット信号 1 1 0 がHレベルとされているので、スイッチ 6 1 を介して、放電回路 4 0 とデジタル容量 7 0 とが接続され、それにより、デジタル容量 7 0 の蓄積電荷が放電回路 4 0 によって放電され、デジタル容量 7 0 の端子間は 0 V になる。これにより、コンパレータ 8 0 の出力はLレベルとなる。

[0052]

次に第 2 カウンタ( c o u n t e r ) 6 0 2 の値が 0 にされ( S 2 0 4 )、デジタル容量 7 0 の放電時間に十分な時間待った後( S 2 0 5 )、リセット信号 1 1 0 が L レベルにされる( S 2 0 6 )。

30

[0053]

リセット信号 1 1 0 がLレベルとなると、スイッチ 6 1 を介して、充電回路 5 0 とデジタル容量 7 0 とが接続され、デジタル容量 7 0 には、電圧電流変換回路 3 0 の出力である直流電流(I=VBG/R1)が供給される。デジタル容量70の端子間には、次式で示されるように、リセット信号 1 1 0 がLレベルになってからの時間 tに比例した電圧 V が現れる。

[0054]

#### 【数2】

数2

40

50

$V = (VBG/R1/C1) \cdot \Delta t$

#### [0055]

ここで、С1はデジタル容量70の端子間の容量値である。

#### [0056]

上記電圧VがVBGより大きければ、コンパレータ80の出力はHレベルとなる。上記電圧VがVBGより小さければ、コンパレータ80の出力はLレベルとなる。

### [0057]

リセット信号 1 1 0 がLレベルになってからコンパレータ 8 0 の出力がHレベルとなるまでのクロック信号 1 0 0 の立ち上がりエッジ、または立ち下がりエッジが一つ観測されるたびに、演算回路 6 0 0 内の第 2 カウンタ(counter) 6 0 2 の値が 1 だけ増加す

る(S207,S208)。従って、コンパレータ80の出力がHレベルとなったときの 演算回路600内の第2カウンタ(counter)600の値は、リセット信号110 がLレベルになってからコンパレータ80の出力がHレベルとなるまでのクロック信号10 0の立ち上がリエッジ、または立ち下がリエッジの合計数に等しくなる。

## [0058]

ここで、デジタル容量 7 0 の最小容量ステップ幅を C とすると、クロック周波数 F c は次式で示され、十分な精度を得ることができる。

[0059]

#### 【数3】

数3

F c > 1 / (ΔC·R1)

#### [0060]

コンパレータ80の出力によってラッチ回路90の出力がHレベルになるまで、演算回路600内の第2カウンタ(counter)602がインクリメントされる(S208,S209)。コンパレータ80の出力によってラッチ回路90の出力がHレベルになった場合、演算回路600内の第2レジスタ(target0)604が次式で示される値に更新される。

[0061]

【数4】

20

10

数4

target0=target00-counter+target0

#### [0062]

そしてこの新たな t a r g e t 0 の値が、デジタル容量 7 0 のスイッチ S W 0 ~ S W 4 へ設定される(S 2 1 0)。これは、抵抗 2 0 の抵抗値 R 1 とデジタル容量 7 0 の端子間の容量値 C 1 の製造ばらつきを補正したもので、スイッチ S W 0 ~ S W 4 へ上記のデジタル値を与えれば、R 1 と C 1 との積は一定となる。

[0063]

30

次に演算回路600内の第1カウンタ(calcounter)601の値が1だけ減算され(S211)、第1カウンタ(calcounter)601の値が0になったか否かの判別が行われる(S212)。第1カウンタ(calcounter)601の値が0でなければ、上記ステップS203の処理に戻され、上記ステップS203以降の処理が繰り返される。上記ステップS203以降の処理は、第1カウンタ(calcounter)601の値が0となるまで繰り返される。第1カウンタ(calcounter)601の値が0になったら、キャリブレーション完了信号160がアサートされる。これにより、チャネルフィルタ回路407に上記デジタル値が供給され、デジタル容量151を含むフィルタ回路のカットオフ周波数を決定する抵抗と容量の積が補正されるように設定される。

[0064]

このように実施の形態1によれば、演算回路600でR1とC1との積が一定に補正されるためのデジタル値が定まり、同じデジタル値が図5の容量C11~C42に与えられることにより、チャネルフィルタ回路407のカットオフ周波数は目標値に設定される。

[0065]

図6には、容量や抵抗の製造ばらつきが無い状態における、図6のデジタル容量のデジタル値と容量値を図5に適用した場合のカットオフ周波数の一例が示される。

[0066]

例えば、カットオフ周波数を 5 M H z に設定したい場合、図 2 のステップ S 2 0 2 における初期値「target value」をデジタル値 1 6 に設定し、演算回路 6 0 0 で

50

R 1 と C 1 との積が一定に補正されるためのデジタル値が定まり、同じデジタル値が図 5 の容量 C 1 1 ~ C 4 2 に与えられると、カットオフ周波数は目標の 5 M H z に自動調整されることになる。

#### [0067]

同様に、カットオフ周波数を5.95MHzに設定したい場合、図2のステップS202における初期値「target value」をデジタル値8に設定し、演算回路600でR1とC1との積が一定に補正されるためのデジタル値が定まり、同じデジタル値が図5の容量C11~C42に与えられると、カットオフ周波数は目標の5.95MHzに自動調整されることになる。

## [0068]

複数のカットオフ周波数を切り替えたい場合、初期値「target value」をデジタル値16に設定したときの、演算回路600によって求められたデジタル値をCAとし、図2のステップS202における初期値「target value」をデジタル値16に設定したときの、演算回路600によって求められたデジタル値をCBとしてレジスタなどに予め記憶しておけば良い。図5に示される回路のカットオフ周波数を5MHzに設定したい場合は、図5の容量C11~C42に与えるデジタル値にCAを与えれば良く、図5の回路のカットオフ周波数を5.95MHzに切り替えることにより、高速にカットオフ周波数を切り替えることが可能となる。

### [0069]

《実施の形態2》

実施の形態2にかかるカットオフ周波数自動調整回路について説明する。

#### [0070]

実施の形態 2 にかかるカットオフ周波数自動調整回路が図 1 に示されるのと大きく相違するのはキャリブレーション完了信号 1 6 0 の発生の仕方にある。

## [0071]

図 7 には、実施の形態 2 にかかるカットオフ周波数自動調整回路における主要処理のフローチャートが示される。図 7 に示さされるフローチャートが図 2 に示されるのと大きく相違するのは、ステップ 7 1 3 の判別が追加された点である。図 7 に示さされるフローチャートにおけるステップ S 7 0 1 ~ S 7 1 2 は、図 2 に示されるフローチャートにおけるステップ S 2 0 1 ~ S 2 1 2 に対応しており、それについての詳細な説明を省略する。

## [0072]

ステップS710において、新たな target0の値が、デジタル容量70のスイッチSW0~SW4へ設定された後に、予め設定した+/-のcal(キャリプレーション) 閾値と、 <math>target0、 target0 0 を用いて、次式が成立するか否かの判別が行われる。

## [0073]

### 【数5】

数 5

+cal閾値≥(target0-target00)≥-cal閾値

### [0074]

cal閾値はキャリブレーションの精度と速度に関係し、 + / - のcal閾値の範囲が狭いほど精度は上がるが処理に時間がかかる。数5の式が成立する場合、本フローチャートによる処理が終了され、キャリブレーション完了信号160がアサートされて、チャネルフィルタ回路407へデジタル値が与えられる。また、数5の式が成立しない場合には、ステップS711での処理により、演算回路600内の第1カウンタ(calcounter)601の値が1だけ減算される(S711)。

## [0075]

10

20

30

このように、 c a 1 閾値を設け、ステップ713での判別により、数5の式が成立する場合には、本フローチャートによる処理が終了され、キャリプレーション完了信号160がアサートされて、チャネルフィルタ回路407へデジタル値が与えられるため、キャリプレーションの高速化が可能となる。例えば、製造ばらつきが無い場合は、数6に示される式が成立するので、コンパレータ80の出力がHレベルになったときの演算回路600の演算結果は、数7のようになる。

[0076]

#### 【数6】

数 6

counter=target00=(target value)

## [0077]

## 【数7】

数 7

target0=target00-counter+target0

= t a r g e t 0 0 - t a r g e t 0 0 + t a r g e t 0 0 = t a r g e t 0 0

#### [0078]

ここで、+/-のcal閾値を、それぞれ+cal閾値=+1、-cal閾値=-1と設定した場合、+/-のcal閾値との比較は、「target0-target00=0」より、数5の条件を満たすため、実施の形態2では、1回の容量設定でキャリブレーションを完了することができる。実施の形態1ではN回の容量設定が必要であるため、それに比べて実施の形態2では1回の容量設定でキャリブレーションを完了することができるため、高速なキャリブレーションが可能となる。

#### [0079]

また、target0-target00が数5の条件を満たさない場合でも、第1カウンタ(calcounter)601を持つため、実施の形態1の場合と同様に、N回の容量設定を行えば必ずキャリプレーションを完了することができる。

#### [0800]

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明 はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であ ることは言うまでもない。

## [0081]

例えば、図5のチャネルフィルタ回路407は、バタワースに限らず、チェビシェフフィルタなど任意の特性を持つフィルタでも図1のフィルタカットオフ周波数自動調整回路412でカットオフ周波数を自動調整可能である。また、図5のチャネルフィルタ回路407は、正帰還型低域通過回路に限らず、バイカッドフィルタなど他の校正においても図1のフィルタカットオフ周波数自動調整回路でカットオフ周波数を自動調整可能である。

#### [0082]

さらに基準電圧源によって形成される基準電圧10は、温度や電源電圧に依存しない直流電圧VBGとしたが、これに限定されない。例えば、電源電圧を抵抗により分圧して基準電圧10を形成しても良く、電源電圧が殆ど変わらない環境下では、温度や電源電圧に依存しない基準電圧10を形成できる。

### 【符号の説明】

## [0083]

- 10 基準電圧

- 2 0 抵抗

- 30 電圧電流変換回路

- 40 放電回路

- 50 充電回路

10

20

30

40

10

20

- 61 スイッチ

- 70 デジタル容量

- 80 コンパレータ

- 90 ラッチ回路

- 151 デジタル容量

- 400 アンテナ

- 401 デュプレクサ

- 402 低ノイズアンプ

- 403A,403B ミキサ

- 404 局部発振回路

- 4 0 5 9 0 度移相回路

- 406A,406B 第1の増幅回路

- 407 チャネルフィルタ回路

- 408A、408B 第2の増幅回路

- 409A,409B AD変換回路

- 4 1 0 ベースバンドLSI

- 4 1 1 送信回路

- 4 1 2 カットオフ周波数自動調整回路

- 600 演算回路

- 801 携帯情報端末

# 【図1】

<u>≫</u>

## 【図2】

## 【図3】

## 【図4】

## 【図7】

## 【図5】

## 【図6】

図6

| デジタル値 | デジタル容量値 | カットオフ周波数 |

|-------|---------|----------|

| 0     | 0.68C   | 7.35MHz  |

| 1     | 0.70C   | .7.14MHz |

| 2     | 0.72C   | 6.94MHz  |

| 3     | 0.74C   | 6.76MHz  |

| 4     | 0.76C   | 6.58MHz  |

| 5     | 0.78C   | 6.41MHz  |

| 6     | 0.80C   | 6.25MHz  |

| 7     | 0.82C   | 6.10MHz  |

| 8     | 0.84C   | 5.95MHz  |

| 9     | 0.86C   | 5.81MHz  |

| 10    | 0.88C   | 5.68MHz  |

| 11    | 0.90C   | 5.56MHz  |

| 12    | 0.92C   | 5.43MHz  |

| 13    | 0.94C   | 5.32MHz  |

| 14    | 0.96C   | 5.21MHz  |

| 15    | 0.98C   | 5.10MHz  |

| 16    | 1.00C   | 5.00MHz  |

| 17    | 1.02C   | 4.90MHz  |

| 18    | 1.04C   | 4.81MHz  |

| 19    | 1.06C   | 4.72MHz  |

| 20    | 1.08C   | 4.63MHz  |

| 21    | 1.10C   | 4.55MHz  |

| 22    | 1.12C   | 4.46MHz  |

| 23    | 1.14C   | 4.39MHz  |

| 24    | 1.16C   | 4.31MHz  |

| 25    | 1.18C   | 4.24MHz  |

| 26    | 1.20C   | 4.17MHz  |

| 27    | 1.22C   | 4.10MHz  |

| 28    | 1.24C   | 4.03MHz  |

| 29    | 1.26C   | 3.97MHz  |

| 30    | 1.28C   | 3.91MHz  |

| 31    | 1.30C   | 3.85MHz  |

## 【図8】

## フロントページの続き

## (72)発明者 山本 昭夫

神奈川県横浜市戸塚区吉田町292番地 株式会社日立製作所 コンシューマエレクトロニクス研究所内

## 審査官 高橋 徳浩

(56)参考文献 特表2003-516083(JP,A)

特開2006-287900(JP,A)

特開2009-94734(JP,A)

特開2009-224718(JP,A)

特開2010-16591(JP,A)

特開2010-141651(JP,A)

## (58)調査した分野(Int.CI., DB名)

H03H11/00-H03H11/54