US 20010004545A1

### (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2001/0004545 A1 Drobny et al. (43) Pub. Date: Jun. 21, 2001

(54) EPITAXIAL CLEANING PROCESS USING HCL AND N-TYPE DOPANT GAS TO REDUCE DEFECT DENSITY AND AUTO DOPING EFFECTS

(76) Inventors: Vladimir F. Drobny, Tucson, AZ (US); Kevin X. Bao, Tucson, AZ (US)

> Correspondence Address: W. Daniel Swayze, Jr. Texas Instruments Incorporated P. O. Box 655474, MS 3999 Dallas, TX 75265 (US)

(21) Appl. No.: 09/771,428

(22) Filed: Jan. 26, 2001

### Related U.S. Application Data

(60) Continuation-in-part of application No. 09/573,032, filed on May 17, 2000, which is a division of application No. 09/149,353, filed on Sep. 8, 1998, now Pat. No. 6,080,644, which is a non-provisional of provisional application No. 60/073,883, filed on Feb. 6, 1998.

#### **Publication Classification**

(51) **Int. Cl.**<sup>7</sup> ...... **H01L 21/20**; H01L 21/36 (52) **U.S. Cl.** ...... **438/507**; 438/508

### (57) ABSTRACT

An epitaxial layer is formed on a P type silicon substrate in which a plurality of P+ buried layer regions, a plurality of N+ buried layer regions, and a P+ field layer region occupying most of the substrate surface are diffused. The substrate is loaded in a reactor with a carrier gas. The substrate is pre-baked at a temperature of approximately 850° C. As the substrate is heated to a temperature of 1050° C., N+ dopant gas is injected into the carrier gas to suppress auto doping due to P+ atoms that escape from the P+ buried layer regions. The substrate is subjected to a high temperature bake cycle in the presence of the N+ dopant gas. A first thin intrinsic epitaxial cap layer is deposited on the substrate, which then is subjected to a high temperature gas purge cycle at 1080° C. A second thin intrinsic epitaxial cap layer then is deposited on the first, and a second high temperature gas purge cycle is performed at 1080° C. Then an Nepitaxial layer is deposited on the second cap layer at 1080° C. The harmful effects of a dip in the dopant concentration profile at the bottoms of the collectors of the NPN transistors are avoided by the process.

PNP COLLECTOR REGION FOR STANDARD EPI PROCESS AFTER FIELD OXIDATION

NPN COLLECTOR REGION FOR STANDARD EPI PROCESS AFTER FIELD OXIDATION

FIG. Z (PRIOR ART)

Fig. 3A

F16. 3B

DOPING PROFILE ON NPN COLLECTOR FOR EPI GROWN USING THE NOVEL N-TYPE DOPED PRE-BAKE CYCLE.

DOPING PROFILE OF PNP COLLECTOR FOR EPI GROWN USING THE NOYEL N-TYPE DOPED PRE-BAKE CYCLE.

F14.5

F14.8

### EPITAXIAL CLEANING PROCESS USING HCL AND N-TYPE DOPANT GAS TO REDUCE DEFECT DENSITY AND AUTO DOPING EFFECTS

### CROSS-REFERENCE TO RELATED APPLICATION

[0001] This application is a continuation-in-part of copending application "COMPLEMENTARY BIPOLAR/CMOS EPITAXIAL STRUCTURE AND PROCESS" by Vladimir F. Drobny and Kevin X. Bao, Ser. No. 09/573,032, filed May 17, 2000, which is a division of the application "COMPLEMENTARY BIPOLAR/CMOS EPITAXIAL STRUCTURE AND PROCESS", by Vladimir F. Drobny and Kevin X. Bao, Ser. No. 09/149,353, filed Sep. 8, 1998, now Pat. No. 6,080, 644 issued Jun. 27, 2000, which claims priority based on U.S. provisional application number 60/073,883 filed Feb. 6, 1998.

#### BACKGROUND OF THE INVENTION

[0002] The invention relates to a high speed complementary bipolar/CMOS process that provides a doping profile in the collectors of NPN transistors formed in an epitaxial layer so as to eliminate or reduce P-type auto doping and to avoid a "dip" in N type dopant concentration, which dip causes slow speed and other undesirable properties of the NPN transistors, and more specifically relates to further improvements of the high speed complementary/CMOS process to make it suitable for use in single-wafer reactors.

[0003] Those skilled in the art know that it is difficult to provide a process for manufacturing an epitaxial silicon layer that is satisfactory for use in a high speed complementary bipolar/CMOS process. In such a process a very thin, lightly doped N type epitaxial silicon layer must be grown on a silicon wafer including both pre-formed P+ boron doped buried layers and N+ arsenic doped buried layers formed in a P- substrate. In a typical prior art complementary bipolar/CMOS process the epitaxial layer is doped lightly in situ with arsenic to concentration of approximately 2×10<sup>15</sup> cm<sup>-3</sup> to achieve an optimal combination of characteristics of NPN, PNP and CMOS transistors to be formed. After the epitaxial deposition, the collector regions of the PNP and NPN transistors and the CMOS "wells" are further doped by a combination of low energy and high energy boron or phosphorous implants, with energies and doses tailored to the needs of various "families" of devices. During conventional epitaxial growth and subsequent conventional thermal processing, both the P type buried layers and the N type buried layers updiffuse into the epitaxial layer. That reduces the thickness of the useful portions of the collector regions for the transistors being fabricated. Since the P+ and N+ buried layers diffuse at significantly different rates, the PNP transistors end up having shallower collectors than the NPN transistor.

[0004] Since the diffusion of a P+ buried layer accelerates more rapidly than an N+ layer with respect to temperature, differences in the thicknesses of the collectors of the PNP transistors and the NPN transistors can be minimized by keeping the "Dt" of all high temperature process steps as low as possible. ("Dt" is a term referring to the cumulative amount of time and diffusivity that the wafer is subjected to high temperatures, usually exceeding 1000° C., after the epitaxial layer has been deposited.) The deep double

implants used to form the collectors of the required depth for the NPN and PNP transistors, respectively, eliminate the need for high Dt diffusions after the formation of the epitaxial layer.

[0005] Note that a drawback associated with the large differential dopant diffusivity of arsenic buried layers and boron buried layers remains even for "low Dt processing". For very low Dt processes, achieving the desirable PNP collector often results in producing an undesirable lightly doped N type subregion where an NPN collector region meets the N+ buried layer.

[0006] Furthermore, the value of N- dopant in the epitaxial layer must be selected to achieve the best characteristics of both the PNP and NPN transistors. If the Nconcentration is as high as would be desirable for the NPN collector regions, then it would be far too high for the collectors of the PNP transistors. Therefore, a lower Nepitaxial dopant level, indicated by numeral 14 in FIG. 2, is selected instead. Then an N type ion implantation is applied to the surface, raising the N type dopant concentration to a suitable level for the NPN collectors. Unfortunately, it is impractical to provide the dose and energies needed to produce the "flat" N type epitaxial dopant concentration profile at the bottoms of the NPN collector regions. Consequently, the failure of the implanted ions to reach the bottoms of the NPN collector regions is a partial cause of the "dip"20 in FIG. 2.

[0007] The problem of such light doping is further aggravated by boron autodoping, wherein a large number of P type boron atoms escape from the large P+ buried layer area and then diffuse into the surface of the P– substrate and into the lightly doped N type epitaxial layer being grown, reducing or "compensating" its dopant concentration. This results in increased collector resistance and corresponding increased  $V_{\rm CE(sat)}$  voltage, reduced  $f_{\rm T}$  (i.e., the unity gain frequency or cutoff frequency), lower NPN switching speeds, and higher power dissipation.

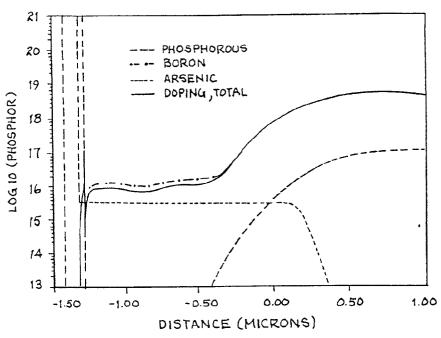

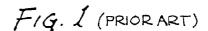

[0008] FIGS. 1 and 2 show typical dopant concentration profiles for the PNP and NPN collector regions, respectively, made by a conventional complementary bipolar process after completion of a field oxidation step, during which most of the dopant diffusion occurs.

[0009] The dopant profiles of FIGS. 1 and 2 were obtained from a simulation of the dopant diffusions for the conventional epitaxial deposition process. The process simulation was calibrated to match experimental results measured from a substrate with a large percentage (for example 80%) of the wafer surface area implanted with a dose of approximately  $1\times10^{15}$  cm<sup>-2</sup> of boron followed by a P+ buried layer diffusion. (As those skilled in the art will recognize, the reason the large percentage of the P+ wafer substrate area has P+"buried layer material" therein is to reduce substrate resistance and increase latch-up immunity of bipolar transistors and CMOS transistors.)

[0010] The prior art epitaxial process referred to above includes a high temperature  $H_2$  pre-bake followed by a high temperature purge and then by a 1.5 micron deposition of an epitaxial layer of lightly arsenic (N type) doped single crystal silicon. The large amount of P+ surface area of the substrate causes a large amount of boron auto-doping into the lightly doped N type epitaxial layer being formed. The

amount of corresponding boron P+ autodoping in the dopant concentration profile of prior art FIGS. 1 and 2 was computed using the TSUPREM-4. The simulated profiles were calibrated to match the measured experimental results. The TSUPREM-4 simulation program is a commercially available software package "Two-dimensional Process Simulation Program", sold by the TCAD division of Avant! Corporation, formerly Technology Modeling Associates.

[0011] For thin epitaxial layers (e.g., less than two microns in thickness), the auto doping strongly influences the transistor collector dopant concentration profiles. The large P+ substrate surface area mentioned above contributes a significant amount of boron autodoping during the epitaxial growth, which aggravates the above-mentioned problems with the performance of the NPN transistors, further reduces the depth of the PNP collector regions, and increases the difference between the breakdown characteristics of NPN and PNP transistors. The standard flat dopant profile epitaxial process techniques used to generate the profiles in prior art FIGS. 1 and 2 are not able to correct these problems.

[0012] Referring to FIGS. 1 and 2, the dopant concentration profiles of the prior art NPN and PNP collector regions are noticeably different when a standard epitaxial process is used. The differences between the depth of the peak of implant concentration (commonly referred to as Rp) for phosphorus and boron implants is another cause of the large difference in the dopant concentration profiles of the NPN and PNP collector regions when practical implant energies are used. This difference is further aggravated by the boron autodoping. The NPN collector region, doped by a combination of low and high energy implants, shows a significant dopant concentration dip at its bottom, indicated by reference arrows 20 in FIG. 2. This very lightly doped region adversely affects both the AC and DC performance of the NPN transistor by raising its collector region resistivity. This increases its collector resistance and thereby reduces  $f_T$ and increases the collector-to-emitter saturation voltages of the NPN transistor.

[0013] Prior experimentation in forming arsenic doped N+ epitaxial caps in the hope of increasing the doping concentration at the bottoms of the NPN collector regions has failed to adequately compensate for the boron autodoping at the epitaxial/substrate interface.

[0014] Recently, single-wafer reactors in which a single semiconductor wafer is processeed have been used, instead of using batch reactors in which a large number of semiconductor wafers are processed. Single wafer reactors provide much better reproducibility of complex dopant profiles in the wafer being processed than can be achieved with batch reactors, and also provide much better control over doping profiles of epitaxial layers than can be achieved with batch reactors. This is because single-wafer reactors have much chamber less interior surface area which can absorb the dopant and it is much easier and faster to remove dopant absorbed by smaller interior surface area. Single-wafer reactors also provide a much more rapid temperature stabilization than batch reactors. Single-wafer reactors have much less volume to pump down than batch reactors. The volume of a single-water reactor can be flushed much more rapidly than the volume of a batch reactor. Single-wafer reactors therefore have become widely used in the manufacture of extremely-thin epitaxial layers.

[0015] However, single-wafer reactor epi deposition cycles do not provide enough time at high temperature (i.e., do not provide enough Dt) to anneal out surface defects at the surface of the buried layer of the wafer being processed. These defects are the result of P+ buried layer implant operations and subsequent diffusions thereof.(Surface defects caused by formation of N+ buried layers are typically oxidized in sacrificial oxidation steps to consume the implant-caused defects. However, this approach can not work to consume surface defects caused by formation of P+ buried layers. That is because the P+ boron-implanted layers cannot be immediately oxidized after the implantation, since such oxidation would cause oxidation induced stacking faults (OISF).)

[0016] Another problem with use of single-wafer reactors is that it is not practical to perform slow rate temperature ramp-up procedures to heat a single wafer up to a high temperature, even though it is in fact practical and often unavoidable to perform slow rate temperature ramp-up procedures to heat up a large number of wafers in a batch reactor. Unfortunately, the fast temperature ramp-up procedures that are necessary to achieve an economically desired throughput for single-wafer reactors can not anneal out defects which are present in the semiconductor wafer. These defects would greatly reduce the yield of functional integrated circuits formed on the semiconductor wafer.

[0017] Thus, there is a need for an improved epitaxial process for complementary bipolar/CMOS for providing bipolar transistors, especially NPN transistors, with more ideal collector profiles leading to lower collector resistances and higher values of  $f_{\rm T}$  than has been previously achievable, and for providing such an epitaxial process in a single-wafer reactor without leaving a high density of crystal defects in integrated circuits.

### SUMMARY OF THE INVENTION

[0018] Accordingly, it is an object of the invention to provide a high speed complementary bipolar/CMOS epitaxial process that provides NPN transistors in which undesirable effects of a dip or decrease in the N type collector dopant concentration profile close to an N+ buried layer are avoided and to make the bipolar/CMOS epitaxial process suitable for use in a single-wafer reactor.

[0019] It is another object of the invention to provide a high speed complementary bipolar/CMOS epitaxial process in which the NPN and PNP transistors have similar performance characteristics, wherein the process is suitable for use in a single-wafer reactor.

[0020] It is another object of the invention to provide a high speed complementary bipolar/CMOS process in which the NPN transistors have higher  $f_T$ , lower collector resistance, and lower collector-to-emitter saturation voltage than has been previously achievable, wherein the process is suitable for use in a single-wafer reactor.

[0021] It is another object of the invention to provide a high speed complementary bipolar/CMOS process with a very uniform collector dopant concentration profile which leads to a high cutoff frequency  $f_{\rm T}$  that is higher than previously has been achieved, wherein the process is suitable for use in a single-wafer reactor.

[0022] It is another object of the invention to provide a high speed complementary bipolar/CMOS process wherein

process techniques that allow eliminating an undesirable dip in the dopant concentration profile of the collectors of the NPN transistors also allow optimization of the dopant concentration profile of the collectors of the PNP transistors, wherein the process is suitable for use in a single-wafer reactor.

[0023] Briefly described, and in accordance with one embodiment thereof, the invention provides a method of making an epitaxial layer on a P type silicon substrate having a P+ field layer region in most of a major surface of the substrate. The method includes loading the substrate in a reactor with a carrier gas therein, pre-baking the substrate, further heating the substrate, providing N+ dopant gas with the carrier gas, deoxidizing the substrate in the presence of the N+ dopant gas, depositing a first intrinsic epitaxial cap layer, performing a first bake cycle, depositing a second intrinsic epitaxial cap layer, performing a second bake cycle, and depositing an N- epitaxial layer having a thickness substantially greater than the thickness of either of the first and second cap layers. The process avoids an undesirable dip in the dopant concentration profile of the collector of PNP transistors formed in the epitaxial layer and results in higher f<sub>T</sub>, lower V<sub>SAT</sub> devices.

### BRIEF DESCRIPTION OF THE DRAWINGS

[0024] FIG. 1 is a doping profile of the collector region of a PNP transistor for a standard prior art epitaxial process.

[0025] FIG. 2 is a doping profile of the collector region of an NPN transistor fabricated using the standard prior art epitaxial process.

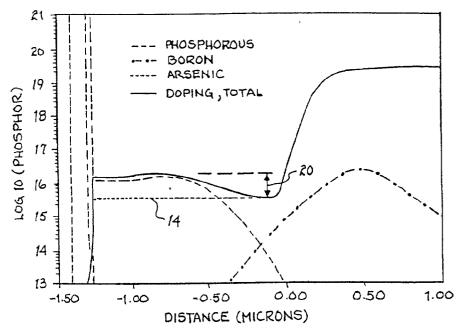

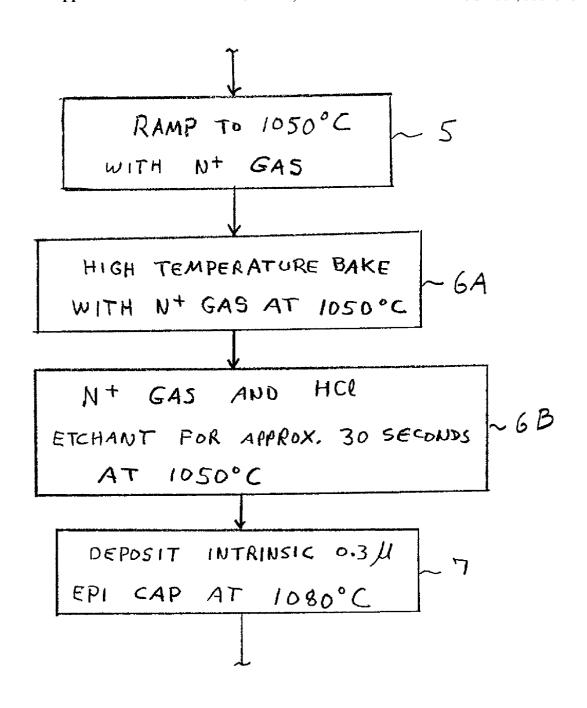

[0026] FIG. 3A is a flow chart useful in describing the process of the present invention.

[0027] FIG. 3B is a flow chart of a modified version of the process of FIG. 3A which is suitable for use in a single-wafer reactor.

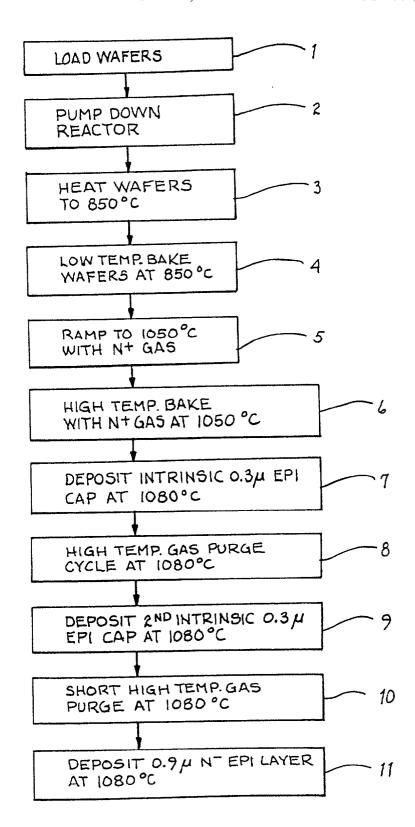

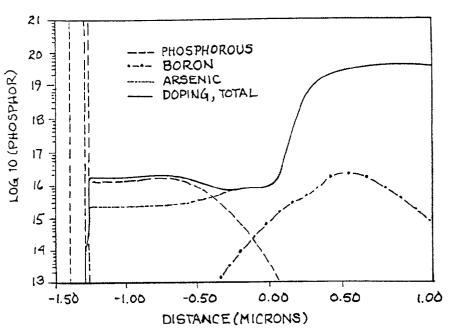

[0028] FIG. 4 is a doping profile of the collector region of an NPN transistor formed using the process of the present invention

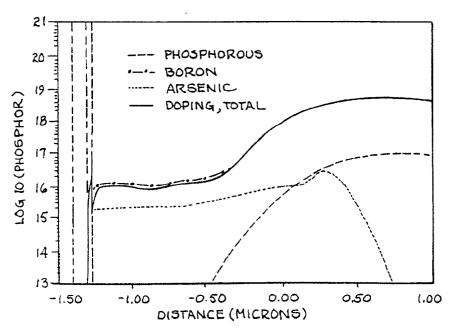

[0029] FIG. 5 is a doping profile of the collector region of a PNP transistor formed in an epitaxial region grown using the process of the present invention.

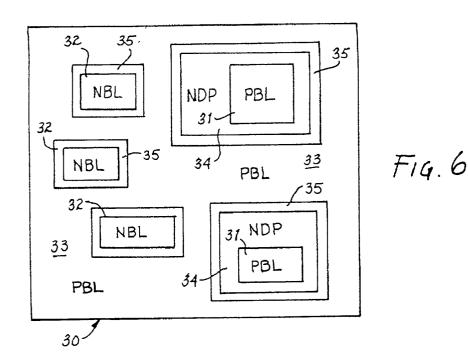

[0030] FIG. 6 is a plan view of a wafer showing locations of P+ and N+ buried layer regions and the deep N+ regions.

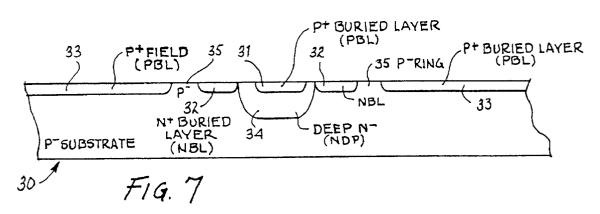

[0031] FIG. 7 is a partial section view of a wafer illustrating the structure of a chip manufactured using the complementary bipolar/CMOS process of the present invention.

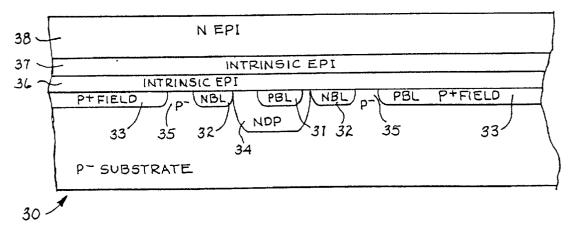

[0032] FIG. 8 is a partial section view of the wafer shown in FIG. 7 after deposition of the two intrinsic epi layers and a lightly doped N type epi layer in accordance with the invention.

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0033] In accordance with the present invention, numerous experiments have been performed to evaluate effects of the durations and temperatures of pre-bake cycles and HCl cycles on the amount of released or "escaped" boron dopant atoms from the P+ regions in an P- substrate and the

resulting P type autodoping of adjacent regions of the wafer. Intrinsic epitaxial "cap" layers and arsenic doped epitaxial cap layers were evaluated for their ability to reduce or suppress the P type autodoping and to increase the N type dopant concentration near the bottom of the NPN collectors. Low temperature purges and high temperature purges were evaluated with respect to their effectiveness in reducing the concentration of the undesired P type dopant during the epitaxial deposition.

[0034] As a result, the epitaxial growth cycle technique of the present invention was developed and was shown to reduce the amount of the previously mentioned "dip"20 (FIG. 2) in the NPN collector doping profile by selectively providing N type dopant ions at depths deeper than achieved during an N type implantation process, and also suppressing the P type autodoping. The technique developed introduces dopant during the H<sub>2</sub> high temperature bake cycle. That is followed by deposition of an intrinsic epitaxial cap layer, followed by a high temperature gas purging cycle. This technique proved to be the most effective in reducing the amount of autodoping and correcting the above mentioned dip in the NPN collector profile doping to thereby provide the desired NPN collector dopant concentration profile.

[0035] The basic epitaxial growth cycle of the present invention introduces an N type dopant (arsenic) into the H<sub>2</sub> high temperature bake cycle. Then an intrinsic epitaxial layer cap is deposited, followed with a high temperature purge and then completed with the final arsenic doped epitaxial layer deposition. This basic process suppresses the boron autodoping and at the same time tends to correct the NPN collector doping profile. The introduction of the N type dopant during the H<sub>2</sub> high temperature bake cycle proved to be very effective in correction of the NPN collector profile, as shown in FIG. 4 wherein the substantial dip 20 of prior art FIG. 1 has been corrected.

[0036] The process offers very good control over the dopant level at the bottom of the NPN collector. The epitaxial high temperature bake cycle of the present invention improves the NPN collector N type dopant concentration profile; this occurs without adversely affecting the P type dopant concentration profile of the PNP collectors. The described process also has a benefit in improving the PNP collector profile, especially when heavier N type compensation is required.

[0037] In the process flow chart of FIG. 3, blocks 1-4 of the illustrated process refer to conventional steps for growth of a lightly doped N type epitaxial silicon layer on a lightly doped P type silicon substrate. The low temperature step of block 4 is performed at 850° C. for roughly 10 minutes, including ramp-up. Steps 5-11 of FIG. 3 are performed at high temperatures in the presence of hydrogen which is used as a carrier gas.

[0038] Referring to FIGS. 3 and 6, note that the wafers referred to in block 1 include the numerous P+ buried layers 31 for the collectors of PNP transistors to be formed, N+ buried layers 32 of NPN transistors to be formed, and the "field" P+ region 33 such that the large (e.g., approximately 80%) of the surface area of each wafer contains a heavy concentration of P+ (boron) dopant atoms. FIG. 6 shows a single chip 30 of one of the silicon wafers. A number of P+ buried layers 31 and N+ buried layers 32 are formed in the P- substrate, as shown. An N+"ring" 32 around each N- well

34 and P+ buried layer 31 therein as it appears in FIG. 6 is formed by a "deep N+" regions 34 in which the P+ buried layer is found. Each of the N type layers 32 and 34 is surrounded by a "ring"35 of P- substrate material between that layer and the P+ layer 33.

[0039] FIG. 7 shows a cross sectional area of a portion of the wafer 30 before the beginning of the process of FIG. 3. Deep N- regions 34 and P- rings 35 separate and electrically isolate each P+ buried layer 31 from the rest of the P+ layer 33 of chip 30, which includes diffused P+ material identical to that of the P+ buried layers 31.

[0040] That means that when the wafers are raised to the processing temperatures of 1050° C. to 1080° C. shown in FIG. 3, many boron atoms escape from the large P+ surface area 33 of the wafer into the H<sub>2</sub> carrier gas and then act as a P+ dopant gas so as to "auto-dope" the N type epitaxial layer being grown, unless something is done to prevent that from occurring. If not for the present invention, the resulting decrease or dip in the collector dopant concentration profiles would increase the resistivities of the collector regions of the NPN transistors subsequently formed over the N+ buried layer regions, making them slower and causing the other above mentioned performance degradation.

[0041] The combination of steps indicated in blocks 5-9 of FIG. 3 is new in an epitaxial silicon growth process. Specifically, the step of block 5, to include N+ type dopant (arsenic) molecules in the  $H_2$  carrier gas during such a heating step in an epitaxial growth process is novel, and is necessary to counteract (i.e., compensate) the escaped "P+" boron atoms involved in the autodoping.

[0042] Although it is conventional to perform the high temperature bake step of a prior art epitaxial silicon growth process in the presence of hydrogen at high temperature, it is novel to include N+ dopant molecules in the hydrogen carrier gas during such high temperature bake step as indicated in blocks 6. This high temperature bake step is performed at 1050° C. for two minutes. In block 5 and 6 the amount of N+ dopant gas injected is approximately 280 sccm (standard cubic centimeters per minute) in a total H<sub>2</sub> flow of 280 slm (standard liters per minute).

[0043] As indicated in block 7 of FIG. 3, a very thin 0.3 micron layer or "cap" layer 36 of intrinsic, i.e., undoped, epitaxial silicon, shown in FIG. 8, is deposited over the entire surface of the wafer to form a "seal" or cap over the large percentage of the wafer which has P+"field" diffusion and P+ buried layers therein. This intrinsic "cap" layer 36 prevents the above mentioned P+ boron atoms from escaping from the large P+ area into the hydrogen carrier gas. Intrinsic cap layer 36 also inhibits P+ boron atoms in the carrier gas form entering the N+ buried layers 32. Thus, the intrinsic cap layer 36 inhibits above mentioned P type "auto-doping" that reduces N type dopant concentration in the collectors of the subsequently formed NPN transistors and reduces their operating speeds.

[0044] Block 8 refers to a high temperature gas purge cycle at 1080° C. for approximately 5-10 minutes, depending on the ratio of P+ field area 33 to the total wafer area to cause redistribution of the dopant molecules in the wafer in accordance with the above mentioned ratio of the P+ field diffusion area to the "non-P+" area. The high temperature gas purge cycle of block 8 also causes outgassing of arsenic

molecules previously diffused during the high temperature bake cycle of blocks 5 and 6 into the susceptor (on which the substrates are supported) and into other surfaces of the inside of the reactor. The high temperature gas purge cycle of block 8 prevents these outgassed N type dopant molecules from doping the next intrinsic cap layer 37, shown in FIG. 8, deposited according to block 9 of FIG. 3, and was found to be necessary to achieve the desired NPN collector dopant concentration profile without a substantial dip 20 (FIG. 2).

[0045] The second high temperature gas purge cycle at 1080° C. indicated in block 10 is not nearly as critical as the first high temperature gas purge cycle of block 8, because the first high temperature gas purge cycle eliminates a majority of the dopant molecules that otherwise would enter the carrier gas from the various inner surfaces of the reactor and susceptor and then reenter the wafer surface and therefore affect the dopant concentration profiles of the NPN and PNP transistors.

[0046] The main reason for depositing the second intrinsic cap layer 37 according to block 9 is to provide a "sharper" transition in the dopant concentration profile than would be achieved if only a single intrinsic cap layer were provided. The elimination of the undesired autodoping species by the first high temperature gas purge cycle of block 8 is what makes it possible for the second intrinsic cap layer 37 to continue the initial sharp transition that would be made into a more gradual transition if the extraneous dopant species from the inner surfaces of the reactor were not first removed.

[0047] Block 9 of FIG. 3 illustrates the growth of the above-mentioned second intrinsic 0.3 micron cap layer 37 of undoped epitaxial silicon at 1080° C. on top of the first 0.3 micron intrinsic layer 36 grown in step 7. Second cap layer 37 further helps to prevent undesired P type and N type auto-doping. Then, after a short, high temperature bake process at 1080° C. for 1 minute as indicated in block 10, a conventional 0.9 micron N- epitaxial deposition of silicon layer 38, shown in FIG. 8, is formed on the top of the second intrinsic cap at 1080° C., as indicated in block 11. The total thickness of the composite epitaxial silicon layer 36, 37, 38 formed on the wafer substrate therefore is 0.3+0.3+0.9=1.5 microns.

[0048] In accordance with the present invention, the presence of the N+ dopant during the steps of blocks 5 and 6 provides enough N+ atoms which, during the growth of the first and second intrinsic epitaxial layers 36 and 37, respectively, of FIG. 8 provides a graded increase in the N type concentration at the bottoms of the NPN collector regions to compensate for a decrease in N type concentration in the region which the implanted N type dopant ions failed to reach. This reduces the collector resistance, increasing the cutoff frequency  $f_{\rm T}$ .

[0049] It should be appreciated that those skilled in the art know that even if the ratio of area of P+"field" diffusion and P+ buried layer area on the surface of a wafer to the total area of the wafer amount both the P+ is substantially less than the 80% ratio in the above described example, a serious P+ autodoping problem nevertheless will exist and need to be compensated according to the present invention. If a higher number or "density" of transistors in the wafer surface is increased, the ratio of the P+"field" area 33 to the total wafer area may decrease to values far lower than 80%. Nevertheless, a sufficient number of P+ atoms may escape

and cause autodoping that, without the present invention, result in a significant dip in the N type dopant concentration profile at the "bottoms" of the NPN collector regions. Therefore, the high temperature bake cycle in the presence of N+ dopant to compensate such P+ autodoping and at least one, and preferably two, intrinsic epi cap layers will suppress the P- autodoping as described herein.

[0050] Note that the high temperature gas purge cycle of block 8 can be used to "fine tune" the shape of the N type dopant concentration profile for the NPN transistors as a function of the above-mentioned ratio of the P+"field" diffusion area 33 to the total area of the wafer surface in which the integrated circuit is formed by adjusting the duration and temperature of the temperature of that high temperature bake cycle.

[0051] As a result of the foregoing process, doping profiles shown in FIG. 4 for the collectors of NPN transistors formed in the 1.5 micron epitaxial layer are achieved. This doping profile avoids the "dip"20 in the N type dopant concentration shown in prior art FIG. 2 representing the previously described undesirably low concentration of N type impurities at the bottoms of the NPN collector regions.

[0052] Thus, the invention provides an epitaxial process engineered specifically to (1) reduce the boron autodoping effect and (2) correct the differences in profiles of the PNP and NPN collector regions. Thin, intrinsic epitaxial layers are formed on a lightly doped P type silicon substrate having a large percentage of its surface area occupied by P+ regions, and a smaller percentage by N+ regions, for the purpose of preventing outgassing of P type impurity atoms during growth of an epitaxial N- layer and preventing such P type atoms from auto-doping the bottom portions of the N-Epitaxial layers above N+ buried layer regions formed in the substrate.

[0053] By way of definition, the term "intrinsicly-formed" is used to refer to an epitaxial layer that is formed without dopant being introduced from an external or outside source into the reactant gas, even though dopant impurities are formed in the "intrinsicly-formed" epitaxial layers because such dopant impurities are introduced into the reactant gas from ambient internal sources. Such ambient internal sources include autodoping from heavily doped regions formed earlier in the substrate and also include N+ atoms introduced into surfaces of the system earlier during the temperature ramp up of block 5 of FIG. 3 in the presence of N+ gas and the high temperature bake of block 6 of FIG. 3 in the presence of N+ gas.

[0054] We have found that the above described process works well with batch epitaxial reactors which process a large number of semiconductor wafers in a single batch, but that the above described process does not work well with the above mentioned a single-wafer reactors. The process described in above-mentioned parent Pat. No. 6,080,644 is not able to repair the crystal defects caused by the P+ buried layer process if a significantly shorter high temperature ramp-up cycle is used than is normally used in batch reactors. It recently has been discovered that typical batch reactors, due to their long temperature ramp-up cycles, are capable of repairing defects produced in the semiconductor wafers by the above-mentioned buried layer implant process. However, this cannot be accomplished by single-wafer epitaxial reactors if they use their conventional shorter

temperature ramp-up cycles, without unacceptably reducing the efficiency of the single-wafer epitaxial reactors and increasing the cost of the process from an equipment utilization point of view.

[0055] To solve the foregoing problem, the invention provides a thin epitaxial layer growth process that is designed to reduce the effect of boron auto-doping, improve the doping profile of the deep portions of the collectors of NPN transistors, and at the same time remove crystal defects caused by the P+ buried layer implant process.

[0056] To accomplish this, a short HCl silicon etch cycle is introduced during the high temperature bake cycle in the presence of hydrogen carrier gas and also in the presence of 10-type dopant gas. The combination of gases used during the "pre-epi" growth part of the epitaxial cycle is crucial to the compensation or reduction or elimination of auto-doping and also to the removal or reduction of surface crystal defects in the silicon at the surface of the wafer prior to the beginning of the epitaxial growth portion of the epitaxial process. Examples of suitable N– type dopant gas include the precursors PH<sub>3</sub> and AsH<sub>3</sub>. It should be noted that the process including the HCl etch works well with batch epitaxial reactors as well as single-wafer epitaxial reactors. Other actions, such as flourine based etchants also could work.

[0057] Referring to FIG. 3B, when a single-wafer reactor is used, the process of FIG. 3A is modified by replacing block 6 of FIG. 3A by blocks 6A and 6B of FIG. 3B. That is, after completing the ramp-up to 1050 degrees Centigrade in the presence of N+ gas as indicated in block 5, part of the high temperature bake cycle is performed without HCl etchant gas present, as indicated in block 6A. then the high temperature bake in the presence of N+ dopant gas at 1050 degrees Centigrade is continued while introducing HCl into the carrier gas and the N+ dopant gas for approximately 30 seconds, as indicated in block 6B, followed with a short gas flush cycle to remove any residual HCl gas.

[0058] The high temperature cycle removes all of any residual oxide from silicon surface, and the HCl introduced into the hydrogen carrier gas (with N+ gas present) therein typically removes approximately 100 Angstroms to 1000 Angstroms of silicon with the crystal defects previously caused at the surface of the buried layer regions by by the buried layer implantation process and subsequent diffusion.

[0059] The above process described above with reference to FIG. 3B also can be utilized to remove semiconductor crystal surface damage in batch reactors as well as single-wafer reactors.

[0060] While the invention has been described with reference to several particular embodiments thereof, those skilled in the art will be able to make the various modifications to the described embodiments of the invention without departing from the true spirit and scope of the invention. It is intended that all elements or steps which are insubstantially different or perform substantially the same function in substantially the same way to achieve the same result as what is claimed are within the scope of the invention.

What is claimed is:

- 1. A method of making an epitaxial layer on a silicon substrate having in a major surface thereof a P+ field layer region in a substantial portion of the major surface, comprising:

- (a) loading the substrate in a reactor and providing a carrier gas therein;

- (b) performing a low temperature bake cycle on the substrate at a temperature of approximately 850° C.;

- (c) further heating the substrate while providing N+ dopant gas in the the carrier gas;

- (d) performing a high temperature bake cycle on the substrate in the presence of N+ dopant gas;

- (e) introducing an etchant gas into the carrier gas and N+ dopant gas for a predetermined amount of time;

- (f) depositing a first intrinsic epitaxial cap layer on the substrate;

- (g) performing a first high temperature gas purge cycle;

- (h) depositing a second intrinsic epitaxial cap layer on the first intrinsic epitaxial cap layer;

- (i) performing a second high temperature gas purge cycle; and

- (j) depositing an N- epitaxial layer having a thickness substantially greater than the thickness of either of the first and second intrinsic cap layers on the second intrinsic epitaxial cap layer.

- 2. The method of claim 1 wherein the etchant gas includes Hcl.

- 3. The method of claim 1 including the removing all of any residual oxide on the major surface before performing step (e).

- **4.** The method of claim 1 wherein the predetermined amount of time is approximately 30 seconds.

- 5. The method of claim 1 including performing steps (a)-(j) in a single-wafer reactor.

- 6. The method of claim 1 wherein step (c) includes ramping the temperature of the substrate up to approximately  $1050^{\circ}$  C.

- 7. The method of claim 1 wherein step (f) includes depositing the first intrinsic epitaxial cap layer with a thickness of approximately 0.3 microns.

- **8**. The method of claim 5 wherein step (h) includes depositing the second intrinsic epitaxial cap layer with a thickness of approximately 0.3 microns.

- 9. The method of claim 8 wherein step (j) includes depositing the N- epitaxial layer with a thickness of approximately 0.9 microns.

- 10. The method of claim 1 including performing an N type ion implantation in the N- epitaxial layer to increase the conductivity thereof, the implantation dopant concentration causing a reduction of a dip in the N type dopant concentration in the N- epitaxial layer at a depth beyond the implant depth, the method including providing the N+ dopant gas in steps (c) and (d) in sufficient amounts to provide enough N type dopant ions to create a graded increase in the first and second intrinsic epitaxial cap layers and the N- epitaxial layer to at least partially compensate the dip.

- 11. A method of making an epitaxial layer on a P type silicon substrate having in a major surface thereof a plurality of P+ buried layer regions, a plurality of N+ buried layer regions, and also having a P+ field layer region in most of the major surface, comprising:

- (a) loading the substrate in a reactor and providing a carrier gas therein;

- (b) performing a low temperature bake cycle on the substrate at a first temperature;

- (c) heating the substrate to a second temperature substantially higher than the first temperature while providing N+ dopant gas with the carrier gas;

- (d) performing a high temperature bake cycle on the substrate in the presence of the N+ dopant gas at the second temperature;

- (e) introducing an etchant gas into the carrier gas and N+ dopant gas for a predetermined amount of time;

- (f) depositing an intrinsic first epitaxial cap on the substrate:

- (g) performing a first high temperature gas purge cycle at a temperature approximately equal to the second temperature;

- (h) depositing an intrinsic second epitaxial cap layer on the first intrinsic epitaxial cap layer; and

- (i) depositing an N- epitaxial layer to having a thickness substantially greater than the thickness of either of the intrinsic first and second epitaxial cap layers.

- 12. The method of claim 11 wherein the etchant gas includes Hcl.

- 13. The method of claim 11 including the removing all of any residual oxide on the major surface before performing step (e).

- **14.** The method of claim 11 wherein the predetermined amount of time is approximately 30 seconds.

- 15. The method of claim 11 including performing steps (a)-(i) in a single-wafer reactor.

- 16. The method of claim 11 including performing a second high temperature gas purge after step (h), wherein the temperature of the first high temperature gas purge cycle is higher than the temperature of the second high temperature gas purge cycle.

- 17. The method of claim 11 including performing a second high temperature bake cycle at a temperature approximately equal to the second temperature between steps (h) and (I).

- **18**. A method of making an epitaxial layer on a substrate having in a major surface thereof a P+ field layer region in a substantial portion of the major surface, comprising:

- (a) loading the substrate in a reactor and providing a carrier gas therein;

- (b) heating the substrate while providing N+ dopant gas with the carrier gas;

- (c) performing a high temperature bake cycle on the substrate in the presence of N+ dopant gas;

- (d) introducing an etchant gas into the carrier gas and N+ dopant gas for a predetermined amount of time;

- (e) depositing a first intrinsic epitaxial cap layer on the substrate;

- (f) performing a first high temperature gas purge cycle; and

- (g) depositing an N- epitaxial layer having a thickness substantially greater than the thickness of the first intrinsic cap layer on the substrate.

- 19. The method of claim 18 wherein the etchant gas includes Hcl.

- **20**. The method of claim 18 including the removing all of any residual oxide on the major surface before performing step (d).

- 21. The method of claim 18 wherein the predetermined amount of time is approximately 30 seconds.

- 22. The method of claim 18 including performing steps (a)-(g) in a single-wafer reactor.

- 23. The method of claim 18 including depositing a second intrinsic epitaxial cap layer on the first intrinsic epitaxial cap layer, and performing a second high temperature gas purge cycle, wherein step (g) includes depositing the N- epitaxial layer on the second intrinsic cap layer.

- 24. The method of claim 18 wherein step (b) includes ramping the temperature of the substrate up to approximately 1050° C.

- 25. The method of claim 18 including performing an N type ion implantation in the N- epitaxial layer to increase the conductivity thereof, the implantation dopant concentration causing a portion of a dip in the N type dopant concentration in the N- epitaxial layer at a depth beyond the implant depth, the method including providing the N+ dopant gas in steps (b) and (c) in sufficient amounts to provide enough N type dopant ions to create a graded

- increase in the first and second intrinsic epitaxial cap layers and the N- epitaxial layer to at least partially compensate the dip.

- **26.** A method of making an epitaxial layer on a substrate having in a major surface thereof a P+ field layer region in a substantial portion of the major surface, comprising:

- (a) loading the substrate in a reactor and providing the carrier gas therein;

- (b) performing a high temperature bake cycle on the substrate in the presence of N+ dopant gas;

- (c) introducing an etchant gas into the carrier gas and N+ dopant gas for a predetermined amount of time;

- (d) depositing a first intrinsic epitaxial cap layer on the substrate;

- (e) performing a first high temperature gas purge cycle; and

- (f) depositing an N- epitaxial layer having a thickness substantially greater than the thickness of the first intrinsic cap layer on the substrate.

- 27. The method of claim 26 wherein the etchant gas includes Hcl.

- **28**. The method of claim 26 including the removing all of any residual oxide on the major surface before performing step (c).

- **29**. The method of claim 26 wherein the predetermined amount of time is approximately 30 seconds.

- **30.** The method of claim 26 including performing steps (a)-(f) in a single-wafer reactor.

\* \* \* \* \*