(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6208818号

(P6208818)

(45) 発行日 平成29年10月4日(2017.10.4)

(24) 登録日 平成29年9月15日(2017.9.15)

(51) Int.Cl.

F 1

|              |           |             |        |      |

|--------------|-----------|-------------|--------|------|

| HO1L 21/8238 | (2006.01) | HO1L 27/092 | 27/092 | G    |

| HO1L 27/092  | (2006.01) | HO1L 29/78  | 29/78  | 613Z |

| HO1L 29/786  | (2006.01) | HO1L 29/78  | 29/78  | 613A |

| HO3K 19/00   | (2006.01) | HO1L 29/78  | 29/78  | 618B |

| HO1L 21/8234 | (2006.01) | HO3K        | 19/00  | 108  |

請求項の数 3 (全 60 頁) 最終頁に続く

|              |                                     |

|--------------|-------------------------------------|

| (21) 出願番号    | 特願2016-121643 (P2016-121643)        |

| (22) 出願日     | 平成28年6月20日 (2016.6.20)              |

| (62) 分割の表示   | 特願2012-105174 (P2012-105174)<br>の分割 |

| 原出願日         | 平成24年5月2日 (2012.5.2)                |

| (65) 公開番号    | 特開2016-208039 (P2016-208039A)       |

| (43) 公開日     | 平成28年12月8日 (2016.12.8)              |

| 審査請求日        | 平成28年6月29日 (2016.6.29)              |

| (31) 優先権主張番号 | 特願2011-112957 (P2011-112957)        |

| (32) 優先日     | 平成23年5月20日 (2011.5.20)              |

| (33) 優先権主張国  | 日本国 (JP)                            |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 大嶋 和晃<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| 審査官       | 市川 武宜                                          |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

p型の導電性を示す第1のトランジスタとn型の導電性を示す第2のトランジスタを含むインバータと、

第3のトランジスタと、

第4のトランジスタと、を有し、

前記第1のトランジスタのゲートは、前記第2のトランジスタのゲートに電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのソース又はドレインの一方に電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、前記第3のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第1トランジスタのソース又はドレインの他方は、第1の電位を供給することができる機能を有する配線に電気的に接続され、

前記第3のトランジスタのゲートは、前記第4のトランジスタのゲートに電気的に接続され、

前記第2のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのソース又はドレインの他方に電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、前記第1の電位よりも低い第2の電位を供給することができる機能を有する配線に電気的に接続され、

10

20

前記第3のトランジスタ及び前記第4のトランジスタには少なくとも酸化物半導体が用いられ、

基板上又は前記基板に前記第1のトランジスタ及び前記第2のトランジスタが設けられ、前記第1のトランジスタ及び前記第2のトランジスタ上に重なって前記第3のトランジスタ及び前記第4のトランジスタが設けられることを特徴とする半導体装置。

【請求項2】

p型の導電性を示す第1のトランジスタとn型の導電性を示す第2のトランジスタを含むインバータと、

第3のトランジスタと、

第4のトランジスタと、を有し、

10

前記第1のトランジスタのゲートは、前記第2のトランジスタのゲートに電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのソース又はドレインの一方に電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第3トランジスタのソース又はドレインの他方は、第1の電位を供給することができる機能を有する配線に電気的に接続され、

前記第3のトランジスタのゲートは、前記第4のトランジスタのゲートに電気的に接続され、

20

前記第2のトランジスタのソース又はドレインの一方は、前記第4のトランジスタのソース又はドレインの他方に電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、前記第1の電位よりも低い第2の電位を供給することができる機能を有する配線に電気的に接続され、

前記第3のトランジスタ及び前記第4のトランジスタには少なくとも酸化物半導体が用いられ、

基板上又は前記基板に前記第1のトランジスタ及び前記第2のトランジスタが設けられ、前記第1のトランジスタ及び前記第2のトランジスタ上に重なって前記第3のトランジスタ及び前記第4のトランジスタが設けられることを特徴とする半導体装置。

【請求項3】

30

p型の導電性を示す第1のトランジスタとn型の導電性を示す第2のトランジスタを含むインバータと、

第3のトランジスタと、

第4のトランジスタと、を有し、

前記第1のトランジスタのゲートは、前記第2のトランジスタのゲートに電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方に電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、前記第3のトランジスタのソース又はドレインの他方と電気的に接続され、

40

前記第1トランジスタのソース又はドレインの他方は、第1の電位を供給することができる機能を有する配線に電気的に接続され、

前記第3のトランジスタのゲートは、前記第4のトランジスタのゲートに電気的に接続され、

前記第4のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの他方に電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第1の電位よりも低い第2の電位を供給することができる機能を有する配線に電気的に接続され、

前記第3のトランジスタ及び前記第4のトランジスタには少なくとも酸化物半導体が用いられ、

50

基板上又は前記基板に前記第1のトランジスタ及び前記第2のトランジスタが設けられ、前記第1のトランジスタ及び前記第2のトランジスタ上に重なって前記第3のトランジスタ及び前記第4のトランジスタが設けられることを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置に関する。特に、インバータ回路を有する半導体装置に関する。また、半導体装置を具備する電子機器に関する。

【背景技術】

【0002】

近年、電子機器の低消費電力化のために電子機器に用いられる部品として低消費電力の半導体装置が利用されるようになってきた。電子機器は、CPU、インターフェイス回路、メモリ素子等の様々な回路から構成されている。そして、各回路間は、入力回路、出力回路又は入出力回路によって接続されている。

【0003】

入力回路、出力回路、入出力回路としてバッファ回路やスリーステートインバータ（「トライステートインバータ」ともいう。）回路が用いられている。スリーステートインバータ回路は、出力が、”ハイ（H I）”、“ロー（L O）”、“ハイインピーダンス（H I Z）”の3つの状態に設定される回路である。

【0004】

スリーステートインバータ回路のハイとは、出力端子が最も高い電源電圧端子側の電位に設定され、ローとは、出力端子が最も低い電位に設定され、ハイインピーダンスとは出力端子がフローティング状態に設定されるものである。

【0005】

スリーステートインバータを構成する各トランジスタにはリーク電流が存在し、トランジスタが選択されていない状況でも電荷の流出又は流入が生じてしまう。そのため、スリーステートインバータをハイインピーダンス状態とした時でも、リーク電流がスリーステートインバータを構成するトランジスタを介して出力端子に流れてしまい、低消費電力化が十分ではなかった。また、電圧降下が生じ誤動作の原因となっていた。

【0006】

特許文献1に示すように、スリーステートインバータを用いたフリップフロップ回路において、スリーステートインバータに用いるトランジスタのしきい値電圧の高いトランジスタと低いトランジスタを混載してフリップフロップ回路の非動作時に流れるリーク電流を小さくするものがある。

【0007】

しかしながら、特許文献1では、高しきい値電圧のトランジスタの動作を確保すべく、高しきい値電圧のトランジスタを考慮して高い電源電圧を用意する必要がある。また、各トランジスタはシリコン材料を用いたトランジスタであると考えられ、各トランジスタをオフにしたとしても各トランジスタにはリーク電流が依然として存在しており、低消費電力化は十分とはいえない。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2001-223563号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

上記課題に鑑み、開示する発明の一態様では、ハイインピーダンス時のリーク電流を抑制して消費電力を低減できる半導体装置を提供することを目的のーとする。

【0010】

10

20

30

40

50

また、開示する発明の一態様では、回路規模の拡大を抑制しつつリーク電流を抑制できる半導体装置を提供することを目的の一とする。

【0011】

また、開示する発明の一態様では、回路の小型化を図りつつリーク電流を抑制できる半導体装置を提供することを目的の一とする。

【課題を解決するための手段】

【0012】

開示する発明では、高純度化された酸化物半導体を用いて半導体装置を構成する。高純度化された酸化物半導体を用いて構成されたトランジスタは、リーク電流が極めて小さいため、低消費電力化を図ることができる。また、リーク電流に基づくハイインピーダンス時<sup>10</sup>の半導体装置の誤作動を防止することができる。

【0013】

開示する発明の一態様では、半導体装置はp型の第1のトランジスタと、n型の第2のトランジスタと、第3のトランジスタと、第4のトランジスタを有する。第1のトランジスタのゲートは、第2のトランジスタのゲートに電気的に接続され、第1のトランジスタのソース又はドレインの一方は、第2のトランジスタのソース又はドレインの一方に電気的に接続される。第3のトランジスタのソース又はドレインの一方は、第1のトランジスタのソース又はドレインの他方と電気的に接続され、第3のトランジスタのソース又はドレインの他方は、高電位配線に電気的に接続され、第3のトランジスタのゲートは、第4のトランジスタのゲートに電気的に接続される。第4のトランジスタのソース又はドレインの一方は、第2のトランジスタのソース又はドレインの他方に電気的に接続され、第4のトランジスタのソース又はドレインの他方は、低電位配線に電気的に接続される。そして、第3のトランジスタ及び第4のトランジスタのチャネル形成領域には酸化物半導体材料が用いられる。<sup>20</sup>

【0014】

上記において、第3のトランジスタと第4のトランジスタは、第1のトランジスタと第2のトランジスタ上に重なって設けることができる。

【0015】

開示する発明の一態様では、半導体装置は、p型の第1のトランジスタと、n型の第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、容量素子とを有する。第1のトランジスタのゲートは、第2のトランジスタのゲートに電気的に接続され、第1のトランジスタのソース又はドレインの一方は、第2のトランジスタのソース又はドレインの一方に電気的に接続される。第3のトランジスタのソース又はドレインの一方は、第1のトランジスタのソース又はドレインの他方と電気的に接続され、第3のトランジスタのソース又はドレインの他方は、高電位配線に電気的に接続され、第3のトランジスタのゲートは、容量素子の第1の端子と前記第5のトランジスタのソース又はドレインの一方とに電気的に接続される。第4のトランジスタのソース又はドレインの一方は、第2のトランジスタのソース又はドレインの他方に電気的に接続され、第4のトランジスタのソース又はドレインの他方は、低電位配線に電気的に接続され、第4のトランジスタのゲートは、容量素子の第2の端子と第1の配線とに電気的に接続される。第5のトランジスタのソース又はドレインの他方は高電位配線に電気的に接続され、第5のトランジスタのゲートは、第2の配線に電気的に接続される。そして、第3のトランジスタ、第4のトランジスタ及び第5のトランジスタには少なくとも酸化物半導体が用いられる。<sup>30</sup>

【0016】

開示する発明の一態様では、半導体装置は、p型の第1のトランジスタと、n型の第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、容量素子とを有する。第1のトランジスタのゲートは、第2のトランジスタのゲートに電気的に接続され、第1のトランジスタのソース又はドレインの一方は、第2のトランジスタのソース又はドレインの一方<sup>40</sup>に電気的に接続される。第3のトランジスタのソース又はドレインの一方は、第1のトランジスタのソース又はドレインの一方と電気的に接続される。第4のトランジスタのソース又はドレインの一方は、第2のトランジスタのソース又はドレインの他方に電気的に接続され、第4のトランジスタのソース又はドレインの他方は、低電位配線に電気的に接続され、第4のトランジスタのゲートは、容量素子の第2の端子と第1の配線とに電気的に接続される。第5のトランジスタのソース又はドレインの一方は、第2のトランジスタのソース又はドレインの他方に電気的に接続され、第5のトランジスタのゲートは、第2の配線に電気的に接続される。そして、第3のトランジスタ、第4のトランジスタ及び第5のトランジスタには少なくとも酸化物半導体が用いられる。

開示する発明の一態様では、半導体装置は、p型の第1のトランジスタと、n型の第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第5のトランジスタと、第6のトランジスタと、容量素子とを有する。第1のトランジスタのゲートは、第2のトランジスタのゲートに電気的に接続され、第1のトランジスタのソース又はドレインの一方は、第2のトランジスタのソース又はドレインの一方<sup>50</sup>に電気的に接続される。第3のトランジスタのソース又はドレインの一方は、第1のトランジスタのソース又はドレインの一方と電気的に接続される。第4のトランジスタのソース又はドレインの一方は、第2のトランジスタのソース又はドレインの他方に電気的に接続され、第4のトランジスタのソース又はドレインの他方は、低電位配線に電気的に接続され、第4のトランジスタのゲートは、容量素子の第2の端子と第1の配線とに電気的に接続される。第5のトランジスタのソース又はドレインの一方は、第2のトランジスタのソース又はドレインの他方に電気的に接続され、第5のトランジスタのゲートは、第2の配線に電気的に接続される。そして、第3のトランジスタ、第4のトランジスタ及び第5のトランジスタには少なくとも酸化物半導体が用いられる。

のトランジスタのソース又はドレインの一方は、第1のトランジスタのソース又はドレインの他方と電気的に接続され、第3のトランジスタのソース又はドレインの他方は、高電位配線に電気的に接続され、第3のトランジスタのゲートは、容量素子の第1の端子と、第5のトランジスタのソース又はドレインの一方と、第6のトランジスタのソース又はドレインの一方とに電気的に接続される。第4のトランジスタのソース又はドレインの一方は、第2のトランジスタのソース又はドレインの他方に電気的に接続され、第4のトランジスタのソース又はドレインの他方は、低電位配線に電気的に接続され、第4のトランジスタのゲートは、容量素子の第2の端子と第1の配線とに電気的に接続される。第5のトランジスタのソース又はドレインの他方は高電位配線に電気的に接続され、第5のトランジスタのゲートは、第2の配線に電気的に接続される。第6のトランジスタのソース又はドレインの他方は低電位配線に電気的に接続され、第6のトランジスタのゲートは、第3の配線に電気的に接続される。そして、第3のトランジスタ、第4のトランジスタ、第5のトランジスタ及び第6のトランジスタには少なくとも酸化物半導体が用いられる。

【0017】

上記において、第3のトランジスタと第4のトランジスタは、第1のトランジスタと第2のトランジスタ上に重なって設けることができる。さらに容量素子を重ねて設けることもできる。

【0018】

上記において、酸化物半導体を用いたトランジスタ以外のトランジスタには酸化物半導体以外の材料を用いることができる。

【0019】

なお、本明細書等において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、液晶表示装置、発光装置、半導体回路および電子機器は全て半導体装置である。

【0020】

また、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

【0021】

なお、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。

【0022】

例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を有する素子などが含まれる。

【発明の効果】

【0023】

本発明の一態様は、半導体装置を構成する各トランジスタのチャネル領域の少なくとも一に酸化物半導体材料を用いる。これにより、リーク電流を抑制でき、半導体装置の消費電力の低減を実現することができる。

【0024】

また、開示する発明の一態様では、第1乃至第4のトランジスタを有するスリーステートインバータの高電位配線側に接続される酸化物半導体を用いた第1のトランジスタのゲートに別途、電圧印加手段を備えることにより、第1のトランジスタのソースの電位がV<sub>dd</sub>から第1のトランジスタのしきい値電圧分低下してしまうことを抑制することができる。

【0025】

10

20

30

40

50

本発明の一態様は、スリーステートインバータを構成する各トランジスタのチャネル領域の少なくとも一に酸化物半導体材料を用いる。そして、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタとを重ねて設けることにより、半導体装置の小型化を図ることができる。

【図面の簡単な説明】

【0026】

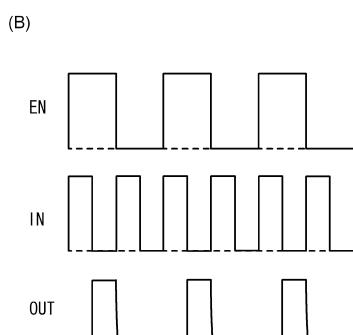

【図1】半導体装置及びそのタイミングチャートの一例を示す図。

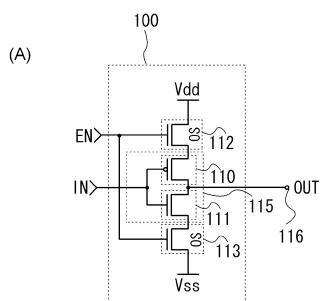

【図2】半導体装置の一例を示す図。

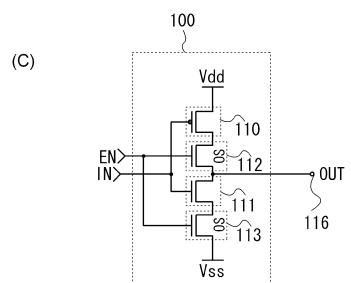

【図3】半導体装置及びそのタイミングチャートの一例を示す図。

【図4】半導体装置及びそのタイミングチャートの一例を示す図。

10

【図5】半導体装置の一例を示す図。

【図6】半導体装置の一例を示す図。

【図7】半導体装置の作製工程の一例を示す図。

【図8】半導体装置の作製工程の一例を示す図。

【図9】半導体装置の作製工程の一例を示す図。

【図10】酸化物半導体を用いたトランジスタの構成を示す断面図。

【図11】酸化物半導体を用いたトランジスタの構成を示す断面図。

【図12】酸化物材料の構造を示す図。

【図13】酸化物材料の構造を示す図。

20

【図14】酸化物材料の構造を示す図。

【図15】酸化物材料の構造を示す図。

【図16】CPUを示す図。

【図17】携帯用の電子機器を示す図。

【図18】電子書籍を示す図。

【図19】ゲート電圧と電界効果移動度の関係を示す図。

【図20】ゲート電圧とドレイン電流の関係を示す図。

【図21】ゲート電圧とドレイン電流の関係を示す図。

【図22】ゲート電圧とドレイン電流の関係を示す図。

【図23】トランジスタの特性を示す図。

【図24】トランジスタの特性を示す図。

30

【図25】トランジスタの特性を示す図。

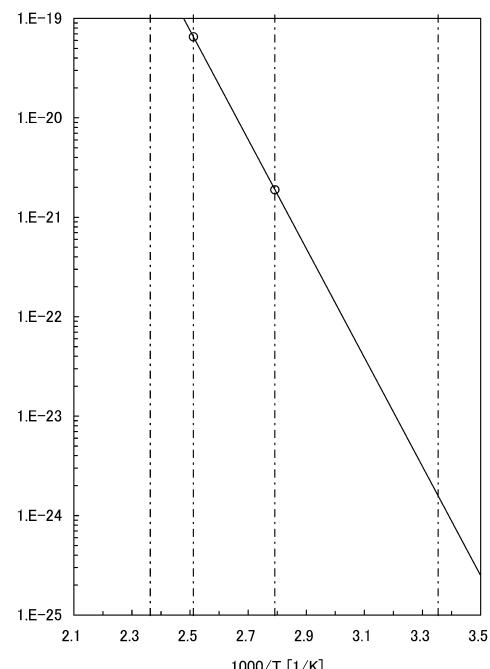

【図26】トランジスタのオフ電流の温度依存性を示す図。

【図27】移動度算出のための式。

【発明を実施するための形態】

【0027】

本発明の実施の形態の一例について、図面を用いて詳細に説明する。なお、以下に説明する構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略することができる。

【0028】

本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

40

【0029】

なお、図面等において示す各構成の、位置、大きさ、範囲などは、理解の簡単のため、実際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必ずしも、図面等に開示された位置、大きさ、範囲などに限定されない。

【0030】

なお、本明細書等における「第1」、「第2」、「第3」などの序数は、構成要素の混同を避けるために付すものであり、数的に限定するものではないことを付記する。

【0031】

50

なお、本明細書等において「電圧」と「電位」を同義で用いることがある。

【0032】

(実施の形態1)

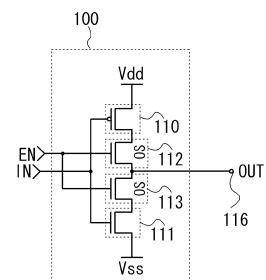

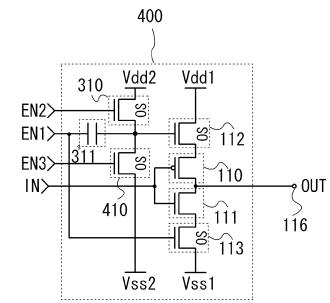

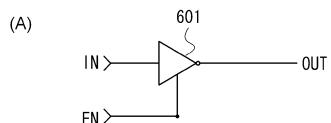

本実施の形態では、開示する発明の一態様に係る半導体装置の構成について、図1を参考して説明する。なお、回路図において、酸化物半導体を用いたトランジスタであることを示すために、「OS」の符号を付す場合がある。

【0033】

図1(A)に本実施の形態に係る半導体装置を示す。半導体装置100は、トランジスタ110、トランジスタ111、トランジスタ112、トランジスタ113を具備する。トランジスタ110はp型の導電性を示し、トランジスタ111、トランジスタ112、及びトランジスタ113はn型の導電性を示す。ここで示す半導体装置100は「スリーステートインバータ回路」、「トライステートインバータ回路」、「信号処理回路」とも呼ぶことができる。

【0034】

トランジスタ110のゲートは、トランジスタ111のゲートに電気的に接続され、トランジスタ110のソース又はドレインの一方は、トランジスタ111のソース又はドレインの一方に電気的に接続されている。

【0035】

トランジスタ112のソース又はドレインの一方は、トランジスタ110のソース又はドレインの他方と電気的に接続され、トランジスタ112のソース又はドレインの他方は、高電位配線（「高電位線」、「電源電圧線」、「電圧線」、「電源」、「電源線」、「Vdd」、「配線」、「第1の電位が供給される配線」、「第1の電位を供給することができる機能を有する配線」等ともいう。図1においては「Vdd」で示す。）に電気的に接続され、トランジスタ112のゲートは、トランジスタ113のゲートに電気的に接続されている。

【0036】

トランジスタ113のソース又はドレインの一方は、トランジスタ111のソース又はドレインの他方に電気的に接続され、トランジスタ113のソース又はドレインの他方は、低電位配線（「低電位線」、「グラウンド配線」、「GND」、「Vss」、「接地配線」、「配線」、「第2の電位が供給される配線」、「第2の電位を供給することができる機能を有する配線」、「第1の電位よりも低い第2の電位が供給される配線」、「第1の電位よりも低い第2の電位を供給することができる機能を有する配線」等ともいう。図1においては「Vss」で示す。）に電気的に接続されている。低電位配線は高電位配線に対して低い電位が供給されている配線であり、接地されていてもよい。

【0037】

トランジスタ112とトランジスタ113のゲートには配線が電気的に接続され、イネーブル信号（EN）が供給される。

【0038】

トランジスタ110のゲートとトランジスタ111のゲートには配線が電気的に接続され、入力信号（IN）が供給される。また、トランジスタ110のソース又はドレインの一方とトランジスタ111のソース又はドレインの一方は、出力端子116に電気的に接続され、出力信号を出力する。

【0039】

イネーブル信号が「ハイ」レベルであるとすると、トランジスタ112とトランジスタ113はともにオンとなり、トランジスタ110とトランジスタ111は、トランジスタ110とトランジスタ111とで構成された単なるインバータ115とみなすことができる。

【0040】

図1(B)に図1(A)のタイミングチャートを示す。

【0041】

10

20

30

40

50

出力端子 116 に「ハイ」の信号を出力する場合、イネーブル信号として「ハイ」の信号を入力し、トランジスタ 112、113 をオンにする。また、入力信号 (IN) に「ロー」の信号を入力することで、トランジスタ 111 はオフになり、トランジスタ 110 はオンになる。トランジスタ 110、112 は導通状態となるため、Vdd から「ハイ」レベルの信号が出力端子 116 に供給される。

#### 【0042】

出力端子 116 に「ロー」の信号を出力する場合、イネーブル信号として「ハイ」の信号を入力し、トランジスタ 112、113 をオンにする。また、入力信号 (IN) に「ハイ」の信号を入力することで、トランジスタ 111 はオンになり、トランジスタ 110 はオフになる。トランジスタ 111、113 は導通状態となるため、Vss から「ロー」レベルの信号が出力端子 116 に供給される。 10

#### 【0043】

ハイインピーダンス状態にする場合、イネーブル信号として「ロー」の信号を入力し、トランジスタ 112、113 をオフにする。これにより、Vdd と出力端子 116 及び Vss と出力端子 116 はそれぞれ電位の供給が遮断され、ハイインピーダンス状態となる。 。

#### 【0044】

トランジスタ 112 とトランジスタ 113 にはオフ電流が極めて小さいトランジスタを用いる。オフ電流が小さいトランジスタとして酸化物半導体を用いることができる。酸化物半導体を用いたトランジスタは結晶性を有するシリコンを用いたトランジスタのオフ電流に比べて著しく低いものとすることができます。トランジスタ 112、トランジスタ 113 のオフ電流は、室温 (25°C) において単位チャネル幅 (1 μm) 当たり、100 zA (ゼプトアンペア) 以下、好ましくは 10 zA 以下、より好ましくは 1 zA (1 × 10⁻²¹ A) 以下であればよい。そのためイネーブル信号が「ロー」レベルであって、出力がハイインピーダンス状態である場合、高電位配線と低電位配線からの電位がトランジスタ 110、トランジスタ 111 を介して出力端子 116 に供給されるのを遮断できるため、リーク電流の発生を防止することができる。これにより半導体装置の低消費電力化を図ることができる。なお、トランジスタ 112 及びトランジスタ 113 は、エンハンスマント型 (ノーマリオフ型) の n チャネル型のトランジスタである。 20

#### 【0045】

なお、上記において、トランジスタの代わりに MEMS スイッチを用いて配線間の接続を物理的に切り離すことにより、電源電位からのリーク電流を防止する構成としてもよい。 。

#### 【0046】

図 1において、トランジスタ 110、111 は、酸化物半導体以外の半導体でなる層または基板にチャネル領域が形成されるトランジスタとすることができます。例えば、シリコン層またはシリコン基板にチャネル領域が形成されるトランジスタとすることができます。

#### 【0047】

なお、トランジスタ 110 をトランジスタ 112、113 と同様に酸化物半導体材料を用いて形成することもできる。また、トランジスタ 111 をトランジスタ 112、113 と同様に酸化物半導体材料を用いて形成することもできる。 40

#### 【0048】

例えば、トランジスタ 110 及び / 又はトランジスタ 111 に酸化物半導体材料を用いる場合、トランジスタ 110 及び / 又はトランジスタ 111 は電界効果移動度が高い In-Sn-Zn 系酸化物半導体を用いて形成すると好ましい。また、トランジスタ 112 及びトランジスタ 113 はオフ電流が著しく小さい In-Ga-Zn 系酸化物半導体を用いて形成すると好ましい。

#### 【0049】

本実施の形態に係る半導体装置を図 1 を用いて説明したが、半導体装置の構成は図 1 の構成に限定されない。図 2 にトランジスタ 110 ~ 113 の配置を変更した半導体装置を 50

示す。

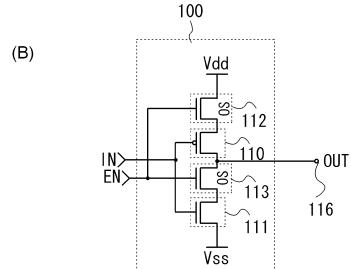

【0050】

図2(A)では、高電位配線Vddにpチャネル型であるトランジスタ110のソース又はドレインの一方が電気的に接続され、nチャネル型であるトランジスタ111のソース又はドレインの一方が低電位配線に電気的に接続されている。トランジスタ110のソース又はドレインの他方は酸化物半導体材料を用いたトランジスタ112を介して出力端子116と電気的に接続され、トランジスタ111のソース又はドレインの他方は酸化物半導体材料を用いたトランジスタ113を介して出力端子116に電気的に接続されている。

【0051】

トランジスタ112及びトランジスタ113のゲートに配線が電気的に接続され、当該配線にイネーブル信号(EN)が供給される。トランジスタ112及びトランジスタ113がオン状態であるときトランジスタ110及びトランジスタ111は単にインバータを構成するとみなすことができる。

【0052】

図2(A)では、トランジスタ112及びトランジスタ113を酸化物半導体材料を用いて形成しているため、トランジスタ112及びトランジスタ113をオフとしハイインピーダンス状態とするとき、高電位配線Vddまたは低電位配線Vssから出力端子にリーク電流が出力されるのを抑制することができる。

トランジスタ110、111よりも出力側に酸化物半導体を用いたトランジスタ112、113が備えられることにより、図1と比較してトランジスタ112、トランジスタ113をオフとした直後に異常信号が出力端子116に出力されるのを防止することができる。

【0053】

図2(B)では、高電位配線Vddに、酸化物半導体を用いたトランジスタ112を介してpチャネル型であるトランジスタ110のソース又はドレインの一方が電気的に接続され、nチャネル型であるトランジスタ111のソース又はドレインの一方が低電位配線Vssに電気的に接続されている。トランジスタ111のソース又はドレインの他方は酸化物半導体を用いたトランジスタ113を介して出力端子116とトランジスタ110のソース又はドレインの他方に電気的に接続されている。

【0054】

トランジスタ112及びトランジスタ113のゲートに配線が電気的に接続され、当該配線にイネーブル信号が供給される。トランジスタ112及びトランジスタ113がオン状態であるときトランジスタ110及びトランジスタ111は単にインバータを構成するとみなすことができる。

【0055】

図2(B)では、トランジスタ112及びトランジスタ113を酸化物半導体材料を用いて形成しているため、トランジスタ112及びトランジスタ113をオフとしハイインピーダンス状態とするとき、高電位配線Vddまたは低電位配線Vssから出力端子にリーク電流が出力されるのを抑制することができる。

また、トランジスタ112はトランジスタ110よりも高電位配線Vdd側に設けられるため、トランジスタ110を介して流れうるリーク電流をトランジスタ112により、適確に防止することができる。

また、トランジスタ111をオンにして出力端子116にローの信号を出力した後にイネーブル信号としてローの信号を出力しトランジスタ112、113をオフに切り替える場合、トランジスタ111を介して出力端子116にリーク電流が流れるおそれがある。しかし、図2(B)のような配置とすることでトランジスタ111からリークする電流をトランジスタ113によって確実に遮断することができる。

【0056】

図2(C)では、低電位配線Vssに、酸化物半導体を用いたトランジスタ113を介

10

20

30

40

50

してnチャネル型であるトランジスタ111のソース又はドレインの一方が電気的に接続され、pチャネル型であるトランジスタ110のソース又はドレインの一方は高電位配線Vddに電気的に接続されている。トランジスタ110のソース又はドレインの他方は酸化物半導体を用いたトランジスタ112を介して出力端子116とトランジスタ111のソース又はドレインの他方に電気的に接続されている。

【0057】

トランジスタ112及びトランジスタ113のゲートに配線が電気的に接続され、当該配線にイネーブル信号が供給される。トランジスタ112及びトランジスタ113がオン状態であるときトランジスタ110及びトランジスタ111は単にインバータを構成するとみなすことができる。

10

【0058】

図2(C)では、トランジスタ112及びトランジスタ113を酸化物半導体材料を用いて形成しているため、トランジスタ112及びトランジスタ113をオフとしハイインピーダンス状態とするとき、高電位配線Vddまたは低電位配線Vssから出力端子にリーク電流が出力されるのを抑制することができる。

また、トランジスタ113はトランジスタ111よりも低電位配線Vss側に設けられるため、トランジスタ111を介して流れうるリーク電流をトランジスタ113により、適確に防止することができる。また、トランジスタ110をオンにして出力端子116にハイの信号を出力した後にイネーブル信号としてローの信号を出力しトランジスタ112、113をオフに切り替える場合、トランジスタ110を介して出力端子116にリーク電流が流れるおそれがある。しかし、図2(C)のような配置とすることでトランジスタ110からリークする電流をトランジスタ112によって確実に遮断することができる。

20

【0059】

以上のように、トランジスタ110～113の接続関係を適宜変更することができる。なお、図1に示すように電源電位Vdd、Vssに各々近い側に酸化物半導体を用いたトランジスタ112、トランジスタ113を設ける構成が好ましい。また、トランジスタ110に酸化物半導体を用いてもよく、トランジスタ111に酸化物半導体を用いてもよい。

【0060】

本実施の形態に係る半導体装置は、半導体装置を構成するトランジスタのチャネル領域に酸化物半導体を用いることにより、電源から酸化物半導体以外の材料を用いたトランジスタあるいは出力端子に流れるリーク電流を抑制することができる。これにより、半導体装置の消費電力を低減することができる。

30

【0061】

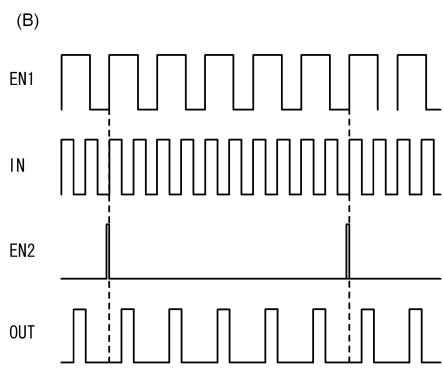

(実施の形態2)

本実施の形態では、実施の形態1で示した半導体装置とは異なる構成の半導体装置について、図3を参照して説明する。

【0062】

半導体装置300は、トランジスタ110、トランジスタ111、トランジスタ112、トランジスタ113、トランジスタ310、容量素子311、抵抗素子312を具備する。トランジスタ110はp型の導電性を示し、トランジスタ111、トランジスタ112、トランジスタ113及びトランジスタ310はn型の導電性を示す。

40

【0063】

トランジスタ110のゲートは、トランジスタ111のゲートに電気的に接続され、トランジスタ110のソース又はドレインの一方は、トランジスタ111のソース又はドレインの一方電気的に接続されている。

【0064】

トランジスタ112のソース又はドレインの一方は、トランジスタ110のソース又はドレインの他方と電気的に接続され、トランジスタ112のソース又はドレインの他方は、高電位配線Vdd1に電気的に接続され、トランジスタ112のゲートは、トランジス

50

タ310のソース又はドレインの一方と容量素子311の一方の端子と抵抗素子312の一方の端子に電気的に接続されている。

【0065】

トランジスタ113のソース又はドレインの一方は、トランジスタ111のソース又はドレインの他方に電気的に接続され、トランジスタ113のソース又はドレインの他方は、低電位配線Vss1に電気的に接続されている。トランジスタ113のゲートは容量素子311の他方の端子に電気的に接続されている。

【0066】

トランジスタ310のソース又はドレインの他方は高電位配線Vdd2に電気的に接続される。Vdd1とVdd2は共通の電源であってもよく、異なる電源であってもよい。10 例えば、Vdd2は、Vdd1より高い電位でも低い電位としてもよく、Vdd1とトランジスタ112のしきい値電圧を加算した電位よりも高い電位、あるいはVdd1とトランジスタ112のしきい値電圧を加算した電位よりも低い電位に設定してもよい。

【0067】

抵抗素子312の他方の端子は低電位配線Vssに電気的に接続されている。Vss1とVss2は共通の電源であるが、異なる電源であってもよい。

【0068】

トランジスタ113のゲートと容量素子311の他方の端子には配線が電気的に接続され、第1のイネーブル信号(EN1)が供給される。

【0069】

トランジスタ310のゲートには配線が電気的に接続され、第2のイネーブル信号(EN2)が供給される。

【0070】

次に、図3(A)の動作について説明する。図3(B)に図3(A)に示す半導体装置のタイミングチャートを示す。

【0071】

最初に、出力端子116に「ハイ」又は「ロー」の信号を出力する場合について説明する。

【0072】

まず、第2のイネーブル信号として「ハイ」の信号を入力し、トランジスタ310をオンにする。このとき、ノード313にはトランジスタ310と抵抗素子312の抵抗値の比率に基づいて分圧された電位が供給される。

【0073】

その後、第1のイネーブル信号として「ハイ」の信号を入力し、トランジスタ112、トランジスタ113をオンにして導通状態にする。このとき、トランジスタ112のゲートには、ノード313の電位に第1のイネーブル信号の「ハイ」レベルの信号が上乗せされた電位が供給される。

【0074】

出力端子116にハイの信号を出力する場合、入力信号(IN)として「ロー」の信号を入力することで、トランジスタ111はオフになり、トランジスタ110はオンになる。トランジスタ110及びトランジスタ112は導通状態となるため、Vddから「ハイ」レベルの信号が出力端子116に供給される。

【0075】

出力端子116にローの信号を出力する場合、入力信号として「ハイ」の信号を入力することで、トランジスタ111はオンになり、トランジスタ110はオフになる。トランジスタ111及びトランジスタ113は導通状態となるため、Vssから「ロー」レベルの信号が出力端子116に供給される。

【0076】

ハイインピーダンス状態にする場合、第2のイネーブル信号として「ロー」の信号を入力してトランジスタ310をオフにし、第1のイネーブル信号に「ロー」の信号を入力し

10

20

30

40

50

てトランジスタ 112 及びトランジスタ 113 をオフにする。これにより、高電位配線 V<sub>dd1</sub> と出力端子 116 及び低電位配線 V<sub>ss1</sub> と出力端子 116 はそれぞれ電位の供給が遮断され、ハイインピーダンス状態となる。

【0077】

以上により、ハイ、ロー、ハイインピーダンスの 3 つの状態の信号を出力端子 116 に出力することができる。

【0078】

なお、図 3 (B) では、第 2 のイネーブル信号として「ハイ」の信号を入力しトランジスタ 310 をオンにした後、直ちに「ロー」の信号を入力している。これに対し、第 2 のイネーブル信号として「ハイ」の信号を入力し続けた状態で、第 1 のイネーブル信号として「ハイ」の信号を入力し、トランジスタ 112 及びトランジスタ 113 をオンにして導通状態にしてもよい。この場合においても、トランジスタ 112 のゲートには、ノード 313 の電位に第 1 のイネーブル信号の「ハイ」レベルの信号が上乗せされた電位が供給される。ハイインピーダンス状態にするときは、「ハイ」の信号を入力し続けている第 2 のイネーブル信号を「ロー」の信号にしてトランジスタ 310 をオフにする。その後、第 1 のイネーブル信号として「ロー」の信号を入力し、トランジスタ 112 及びトランジスタ 113 をオフにするとよい。これにより、高電位配線 V<sub>dd1</sub> と出力端子 116 及び低電位配線 V<sub>ss1</sub> と出力端子 116 はそれぞれ電位の供給が遮断され、ハイインピーダンス状態となる。

【0079】

本実施の形態に係る半導体装置では、トランジスタ 112、トランジスタ 113、トランジスタ 310 にオフ電流が極めて小さい酸化物半導体が用いられ、トランジスタ 110 とトランジスタ 111 に酸化物半導体以外の材料が用いられる。

【0080】

第 1 のイネーブル信号として「ロー」の信号を入力してトランジスタ 112、トランジスタ 113 をオフにして出力をハイインピーダンス状態とする場合、酸化物半導体を用いたトランジスタ 112 によって、高電位配線 V<sub>dd1</sub> から出力端子 116 へのパスを遮断できる。これにより、リーク電流を無くすことができ、消費電力の低減を実現することができる。また、リーク電流に基づく異常信号の出力を抑制することができる。

【0081】

また、酸化物半導体を用いたトランジスタ 113 によって、低電位配線 V<sub>ss1</sub> から出力端子 116 へのパスを遮断できる。これにより、リーク電流を無くすことができ、消費電力の低減を実現することができる。また、リーク電流に基づく異常信号の出力を抑制することができる。

【0082】

また、トランジスタ 310 にも酸化物半導体を用いるため、V<sub>dd2</sub> からのリーク電流も防止できる。

【0083】

さらに、本実施の形態に係る半導体装置では出力端子 116 から「ハイ」の信号を出力する場合、トランジスタ 112 のソースの電位が、V<sub>dd1</sub> からトランジスタ 112 のしきい値電圧分低下してしまうことを抑制し、V<sub>dd1</sub> の電位を有効にトランジスタ 110 に供給することができる。

【0084】

具体的には例えば、第 2 のイネーブル信号として「ハイ」の信号を入力してトランジスタ 310 をオンにして直ちに信号を「ロー」にすることで、ノード 313 の電位が V<sub>ss2</sub> まで下がりきる前の所定の電位を利用してトランジスタ 112 のソースの電位を V<sub>dd1</sub> からトランジスタ 112 のしきい値電圧分低い電圧とならないようにすることができる。

【0085】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

10

20

30

40

50

## 【0086】

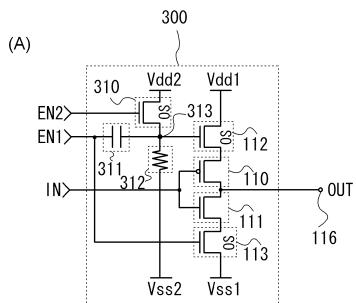

(実施の形態3)

本実施の形態では、実施の形態1、2で示した半導体装置とは異なる構成の半導体装置について、図4を参照して説明する。

## 【0087】

図4(A)示す半導体装置400は、トランジスタ110、トランジスタ111、トランジスタ112、トランジスタ113、トランジスタ310、トランジスタ410、容量素子311を具備する。

## 【0088】

トランジスタ110はp型の導電性を示し、トランジスタ111、トランジスタ112、トランジスタ113、トランジスタ310及びトランジスタ410はn型の導電性を示す。

10

## 【0089】

トランジスタ110のゲートは、トランジスタ111のゲートに電気的に接続され、トランジスタ110のソース又はドレインの一方は、トランジスタ111のソース又はドレインの一方電気的に接続されている。

## 【0090】

トランジスタ112のソース又はドレインの一方は、トランジスタ110のソース又はドレインの他方と電気的に接続され、トランジスタ112のソース又はドレインの他方は、高電位配線Vdd1に電気的に接続される。トランジスタ112のゲートは、トランジスタ310のソース又はドレインの一方と、トランジスタ410のソース又はドレインの一方と、容量素子311の一方の端子に電気的に接続されている。

20

## 【0091】

トランジスタ113のソース又はドレインの一方は、トランジスタ111のソース又はドレインの他方に電気的に接続され、トランジスタ113のソース又はドレインの他方は、低電位配線Vss1に電気的に接続されている。トランジスタ113のゲートは容量素子311の他方の端子に電気的に接続されている。

## 【0092】

トランジスタ310のソース又はドレインの他方は高電位配線Vdd2に電気的に接続される。Vdd1とVdd2は共通の電源であってもよく、異なる電源であってもよい。

30 例えば、Vdd2は、Vdd1より高い電位でも低い電位としてもよく、Vdd1とトランジスタ112のしきい値電圧を加算した電位よりも高い電位、あるいはVdd1とトランジスタ112のしきい値電圧を加算した電位よりも低い電位に設定してもよい。

## 【0093】

トランジスタ410のソース又はドレインの他方は低電位配線Vss2に電気的に接続される。Vss1とVss2は共通の電源であるが、異なる電源であってもよい。

## 【0094】

トランジスタ113のゲートと容量素子311の他方の端子には配線が電気的に接続され、第1のイネーブル信号(EN1)が供給される。

## 【0095】

トランジスタ310のゲートには配線が電気的に接続され、第2のイネーブル信号(EN2)が供給される。

## 【0096】

トランジスタ410のゲートには配線が電気的に接続され、第3のイネーブル信号(EN3信号)が供給される。

## 【0097】

トランジスタ110のゲートとトランジスタ111のゲートには入力信号(IN)が供給される。

## 【0098】

図4(B)に図4(A)のタイミングチャートを示す。

## 【0099】

最初に、出力端子116に「ハイ」又は「ロー」の信号を出力する場合について説明する。

## 【0100】

まず、第3のイネーブル信号として「ロー」の信号を入力し、トランジスタ410をオフにし、第2のイネーブル信号として「ハイ」の信号を入力し、トランジスタ310をオンにする。

## 【0101】

トランジスタ112のゲートに高電位配線Vdd2に供給される電位からトランジスタ310のしきい値電圧を引いた電位が供給される。

10

## 【0102】

その後、第2のイネーブル信号として「ロー」の信号を入力し、トランジスタ310をオフすることでトランジスタ112のゲートと容量素子311の一方の端子間に電荷が保持される。

## 【0103】

次に、第1のイネーブル信号として「ハイ」の信号を入力し、トランジスタ112、113を導通状態にする。

## 【0104】

出力端子116に「ハイ」の信号を出力する場合、入力信号として「ロー」の信号を入力することで、トランジスタ111はオフになり、トランジスタ110はオンになる。トランジスタ110、112は導通状態となるため、Vddから「ハイ」レベルの信号が出力端子116に供給される。

20

## 【0105】

出力端子116にローの信号を出力する場合、入力信号として「ハイ」の信号を入力することで、トランジスタ111はオンになり、トランジスタ110はオフになる。トランジスタ111、113は導通状態となるため、Vssから「ロー」レベルの信号が出力端子116に供給される。

## 【0106】

ハイインピーダンス状態にする場合、第2のイネーブル信号として「ロー」を入力し、トランジスタ310をオフにし、第3のイネーブル信号として「ハイ」の信号を入力し、トランジスタ410をオンにする。これにより、容量素子311の一方の端子に保持されていた電荷がトランジスタ410を介してVss2に流れる。

30

## 【0107】

その後、第1のイネーブル信号として「ロー」の信号を入力し、トランジスタ112、113をオフとする。これにより、高電位配線Vdd1と出力端子116及び低電位配線Vss1と出力端子116はそれぞれ電位の供給が遮断され、ハイインピーダンス状態となる。

## 【0108】

以上により、ハイ、ロー、ハイインピーダンスの3つの状態の信号を出力端子116に出力することができる。

40

## 【0109】

なお、容量素子311に電荷を蓄積させるために、第2のイネーブル信号として「ハイ」の信号を入力し、第3のイネーブル信号として「ロー」の信号を入力する際、第1のイネーブル信号は「ハイ」の信号でも「ロー」の信号であってもよい。

## 【0110】

本実施の形態に係る半導体装置では、トランジスタ112、トランジスタ113、トランジスタ310、トランジスタ410にオフ電流が極めて小さい酸化物半導体が用いられ、トランジスタ110とトランジスタ111に酸化物半導体以外の材料が用いられる。

## 【0111】

第1のイネーブル信号として「ロー」の信号を入力してトランジスタ112、トランジ

50

スタ 1 1 3 をオフにして出力をハイインピーダンス状態とする場合、酸化物半導体を用いたトランジスタ 1 1 2 によって、高電位配線 V d d 1 から出力端子 1 1 6 へのパスを遮断できる。これにより、リーク電流を無くすことができ、消費電力の低減を実現することができる。また、リーク電流に基づく異常信号の出力を抑制することができる。

【 0 1 1 2 】

また、酸化物半導体を用いたトランジスタ 1 1 3 によって、低電位配線 V s s 1 から出力端子 1 1 6 へのパスを遮断できる。これにより、リーク電流を無くすことができ、消費電力の低減を実現することができる。また、リーク電流に基づく異常信号の出力を抑制することができる。

【 0 1 1 3 】

また、トランジスタ 3 1 0 及びトランジスタ 4 1 0 にも酸化物半導体を用いるため、V d d 2 、V s s 2 からのリーク電流も防止できる。

【 0 1 1 4 】

本実施の形態に係る半導体装置では出力端子 1 1 6 から「ハイ」の信号を出力する場合、トランジスタ 1 1 2 のソースの電位が V d d 1 からトランジスタ 1 1 2 のしきい値電圧分低下してしまうことを抑制し、V d d 1 の電位を有効にトランジスタ 1 1 0 に供給することができる。

【 0 1 1 5 】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。例えば、図 2 ( A ) ~ ( C ) に示すようにトランジスタ 1 1 0 ~ 1 1 3 の配置を変更することもできる。

【 0 1 1 6 】

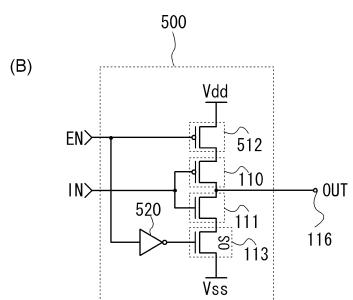

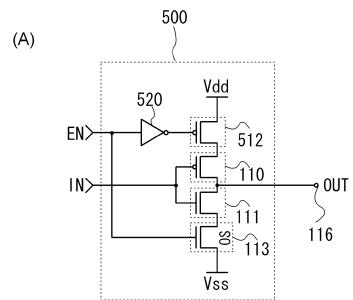

( 実施の形態 4 )

本実施の形態では、実施の形態 1 ~ 3 で示した半導体装置とは異なる構成の半導体装置について、図 5 を参照して説明する。

【 0 1 1 7 】

半導体装置 5 0 0 は、トランジスタ 1 1 0 、トランジスタ 1 1 1 、トランジスタ 5 1 2 、トランジスタ 1 1 3 、インバータ 5 2 0 を具備する。

【 0 1 1 8 】

図 1 との相違は、高電位配線 V d d と接続される酸化物半導体を用いたトランジスタ 1 1 2 の代わりに酸化物半導体以外の材料を用いた p チャネル型のトランジスタ 5 1 2 と、インバータ 5 2 0 を設けた点である。

【 0 1 1 9 】

図 5 ( A ) では、 p チャネル型であるトランジスタ 5 1 2 のソース又はドレインの一方は、トランジスタ 1 1 0 のソース又はドレインの一方と電気的に接続され、トランジスタ 5 1 2 のソース又はドレインの他方は、高電位配線 V d d に電気的に接続され、トランジスタ 5 1 2 のゲートは、インバータ 5 2 0 の出力端子に電気的に接続されている。トランジスタ 1 1 3 のゲートはインバータ 5 2 0 の入力端子に電気的に接続されている。

【 0 1 2 0 】

図 5 ( B ) では、トランジスタ 5 1 2 のゲートは、インバータ 5 2 0 の入力端に電気的に接続されている。トランジスタ 1 1 3 のゲートはインバータ 5 2 0 の出力端に電気的に接続されている。

【 0 1 2 1 】

以下では、図 5 ( A ) を用いて説明する。インバータ 5 2 0 の入力端とトランジスタ 1 1 3 のゲートには配線が電気的に接続され、イネーブル信号 ( E N ) が供給される。

【 0 1 2 2 】

イネーブル信号が「ハイ」レベルであるとすると、トランジスタ 5 1 2 とトランジスタ 1 1 3 はともにオンとなり、トランジスタ 1 1 0 とトランジスタ 1 1 1 は、トランジスタ 1 1 0 とトランジスタ 1 1 1 とで構成された単なるインバータ 1 1 5 とみなすことができる。

10

20

30

40

50

## 【0123】

トランジスタ110のゲートとトランジスタ111のゲートには配線が電気的に接続され、入力信号(IN)が供給される。また、トランジスタ110のソース又はドレインの一方とトランジスタ111のソース又はドレインの一方は、出力端子116に電気的に接続されており、出力信号を出力する。

## 【0124】

出力端子116に「ハイ」の信号を出力する場合、イネーブル信号として「ハイ」の信号を入力し、トランジスタ512、113をオンにする。また、入力信号(IN)に「ロー」の信号を入力することで、トランジスタ111はオフになり、トランジスタ110はオンになる。トランジスタ110、112は導通状態となるため、Vddから「ハイ」レベルの信号が出力端子116に供給される。

10

## 【0125】

出力端子116に「ロー」の信号を出力する場合、イネーブル信号として「ハイ」の信号を入力し、トランジスタ512、113をオンにする。また、入力信号(IN)に「ハイ」の信号を入力することで、トランジスタ111はオンになり、トランジスタ110はオフになる。トランジスタ111、113は導通状態となるため、Vssから「ロー」レベルの信号が出力端子116に供給される。

## 【0126】

ハイインピーダンス状態にする場合、イネーブル信号として「ロー」の信号を入力し、トランジスタ512、113をオフにする。これにより、Vddと出力端子116及びVssと出力端子116はそれぞれ電位の供給が遮断され、ハイインピーダンス状態となる。

20

## 【0127】

トランジスタ113にはオフ電流が極めて小さいトランジスタを用いる。オフ電流が小さいトランジスタには酸化物半導体を用いることができる。酸化物半導体を用いたトランジスタは結晶性を有するシリコンを用いたトランジスタのオフ電流に比べて著しく低いものとすることができます。出力がハイインピーダンス状態である場合、酸化物半導体を用いたトランジスタ113により低電位配線Vssと出力端子116間のリーク電流の発生を無くすことができる。

## 【0128】

30

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

## 【0129】

## (実施の形態5)

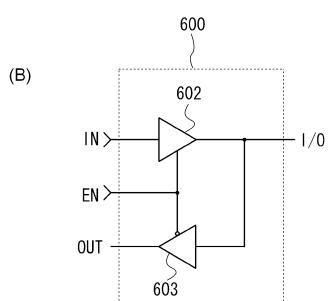

本実施の形態では、半導体装置を双方向バッファ回路に適用した例について図6を参照して説明する。

## 【0130】

図6(A)にスリーステートインバータ回路601を示す。このスリーステートインバータ回路に実施の形態1~4で示した構成を適用することができる。

## 【0131】

図6(B)に2つのスリーステート回路を組み合わせた双方向バッファ回路である半導体装置600を示す。半導体装置600はスリーステートインバータ回路602と、スリーステートインバータ回路603の出力端子が入力端子に電気的に接続されたスリーステートインバータ回路603とを有する。スリーステートインバータ回路602、603には実施の形態1~4で示した構成を適宜適用することができる。例えば、スリーステートインバータ回路602に、図1で示す構成を適用し、スリーステートインバータ回路603に図4で示す構成を適用することができる。

40

## 【0132】

本実施の形態で示す双方向バッファ回路に本実施の形態1~4で示す構成を適用することにより、半導体装置のリーク電流を抑制して消費電力を小さくすることができる。

## 【0133】

50

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

【0134】

(実施の形態6)

本実施形態では、チャネルが酸化物半導体層に形成されるトランジスタと、チャネルが酸化物半導体以外の材料で形成されるトランジスタを例に挙げて、半導体装置の作製方法について説明する。ここで、酸化物半導体以外の材料で形成されるトランジスタは、チャネルがシリコン層に形成されるトランジスタである場合を例に挙げる。

【0135】

なお、実施の形態1乃至5で示した酸化物半導体を用いて形成されたトランジスタは、本実施の形態で示すトランジスタ11と同様に作製することができる。また、実施の形態1乃至5で示した酸化物半導体以外の材料を用いて形成されたトランジスタは、本実施形態のトランジスタ133と同様に形成することができる。また、半導体装置が有する容量素子(図3、図4における容量素子311)は、本実施の形態で示す容量素子12と同様に作製することができる。

【0136】

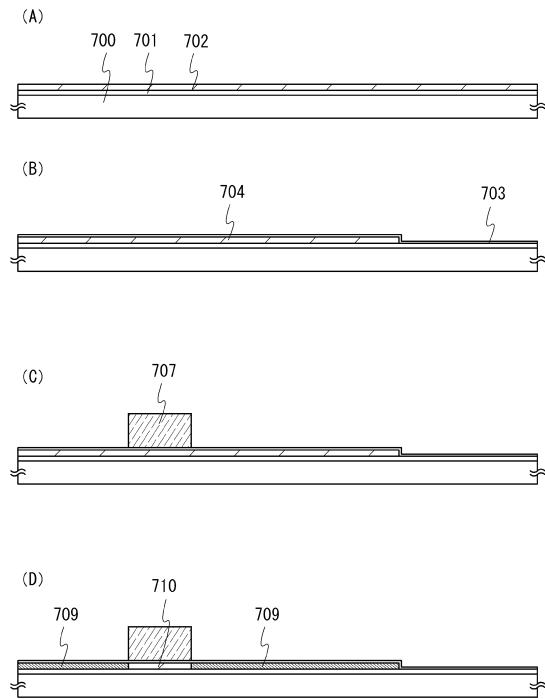

まず、図7(A)に示すように、基板700上に絶縁膜701と、単結晶の半導体基板から分離された半導体膜702とを形成する。

【0137】

基板700として使用することができる素材に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。例えば、基板700には、フュージョン法やフロート法で作製されるガラス基板、石英基板、半導体基板、セラミック基板等を用いることができる。ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が730以上の中を用いると良い。

【0138】

また、本実施の形態では、半導体膜702が単結晶のシリコンである場合を例に挙げて、以下、トランジスタ133の作製方法について説明する。

【0139】

なお、具体的な単結晶の半導体膜702の作製方法の一例について、簡単に説明する。まず、単結晶の半導体基板であるボンド基板に、電界で加速されたイオンでなるイオンビームを注入し、ボンド基板の表面から一定の深さの領域に、結晶構造が乱されることで局所的に脆弱化された脆化層を形成する。

【0140】

脆化層が形成される領域の深さは、イオンビームの加速エネルギーとイオンビームの入射角によって調節することができる。

【0141】

そして、ボンド基板と、絶縁膜701が形成された基板700とを、間に当該絶縁膜701が挟まるように貼り合わせる。

【0142】

貼り合わせは、ボンド基板と基板700とを重ね合わせた後、ボンド基板と基板700の一部に、 $1\text{ N/cm}^2$ 以上 $500\text{ N/cm}^2$ 以下、好ましくは $11\text{ N/cm}^2$ 以上 $20\text{ N/cm}^2$ 以下程度の圧力を加える。圧力を加えると、その部分からボンド基板と絶縁膜701とが接合を開始し、最終的には密着した面全体に接合がおよぶ。

【0143】

次いで、加熱処理を行うことで、脆化層に存在する微小ボイド同士が結合して、微小ボイドの体積が増大する。

【0144】

その結果、脆化層においてボンド基板の一部である単結晶半導体膜が、ボンド基板から分離する。

【0145】

上記加熱処理の温度は、基板700の歪み点を越えない温度とする。そして、上記単結

10

20

30

40

50

晶半導体膜をエッティング等により所望の形状に加工することで、半導体膜 702 を形成することができる。

【0146】

半導体膜 702 には、閾値電圧を制御するために、硼素、アルミニウム、ガリウムなどの p 型の導電性を付与する不純物元素、若しくはリン、砒素などの n 型の導電性を付与する不純物元素を添加しても良い。閾値電圧を制御するための不純物元素の添加は、所定の形状にエッティング加工する前の半導体膜に対して行っても良いし、所定の形状にエッティング加工した後の半導体膜 702 に対して行っても良い。また、閾値電圧を制御するための不純物元素の添加を、ボンド基板に対して行っても良い。若しくは、不純物元素の添加を、閾値電圧を大まかに調整するためにボンド基板に対して行った上で、閾値電圧を微調整するために、所定の形状にエッティング加工する前の半導体膜に対して、又は所定の形状にエッティング加工した後の半導体膜 702 に対して行っても良い。

10

【0147】

なお、本実施の形態では、単結晶の半導体膜を用いる例について説明しているが、本発明はこの構成に限定されない。例えば、S T I ( S h a l l o w T r e n c h I s o l a t i o n ) 等により素子分離したバルクの半導体基板を用いてもよい。例えば、絶縁膜 701 上に気相成長法を用いて形成された多結晶、微結晶、非晶質の半導体膜を用いても良いし、上記半導体膜を公知の技術により結晶化しても良い。公知の結晶化方法としては、レーザ光を用いたレーザ結晶化法、触媒元素を用いる結晶化法がある。或いは、触媒元素を用いる結晶化法とレーザ結晶化法とを組み合わせて用いることもできる。また、石英のような耐熱性に優れている基板を用いる場合、電熱炉を使用した熱結晶化方法、赤外光を用いたランプ加熱結晶化法、触媒元素を用いる結晶化法、950 度の高温加熱法を組み合わせた結晶化法を用いても良い。

20

【0148】

次に、図 7 ( B ) に示すように、半導体膜 702 を用いて半導体層 704 を形成する。そして、半導体層 704 上にゲート絶縁膜 703 を形成する。

【0149】

ゲート絶縁膜 703 は、例えば、プラズマ C V D 法又はスパッタリング法などを用い、酸化珪素、窒化酸化珪素、酸化窒化珪素、窒化珪素、酸化ハフニウム、酸化アルミニウム又は酸化タンタル、酸化イットリウム、ハフニウムシリケート ( H f S i <sub>x</sub> O <sub>y</sub> ( x > 0 、 y > 0 ) ) 、窒素が添加されたハフニウムシリケート ( H f S i <sub>x</sub> O <sub>y</sub> N z ( x > 0 、 y > 0 、 z > 0 ) ) 、窒素が添加されたハフニウムアルミネート ( H f A l <sub>x</sub> O <sub>y</sub> N z ( x > 0 、 y > 0 、 z > 0 ) ) 等を含む膜を、単層で、又は積層させることで、形成することができる。

30

【0150】

なお、本明細書において酸化窒化物とは、その組成として、窒素よりも酸素の含有量が多い物質であり、また、窒化酸化物とは、その組成として、酸素よりも窒素の含有量が多い物質を意味する。

【0151】

ゲート絶縁膜 703 の厚さは、例えば、1 nm 以上 100 nm 以下、好ましくは 10 nm 以上 50 nm 以下とすることができます。本実施の形態では、プラズマ C V D 法を用いて、酸化珪素を含む単層の絶縁膜を、ゲート絶縁膜 703 として用いる。

40

【0152】

次いで、図 7 ( C ) に示すように、ゲート電極 707 を形成する。

【0153】

ゲート電極 707 は、導電膜を形成した後、該導電膜を所定の形状に加工することで、形成することができる。上記導電膜の形成には C V D 法、スパッタリング法、蒸着法、スピニコート法等を用いることができる。また、導電膜は、タンタル ( T a ) 、タンゲステン ( W ) 、チタン ( T i ) 、モリブデン ( M o ) 、アルミニウム ( A l ) 、銅 ( C u ) 、クロム ( C r ) 、ニオブ ( N b ) 等を用いることができる。上記金属を主成分とする合金

50

を用いても良いし、上記金属を含む化合物を用いても良い。又は、半導体膜に導電性を付与するリン等の不純物元素をドーピングした、多結晶珪素などの半導体を用いて形成しても良い。

【0154】

なお、本実施の形態ではゲート電極707を単層の導電膜で形成しているが、本実施の形態はこの構成に限定されない。ゲート電極707は積層された複数の導電膜で形成されても良い。

【0155】

2つの導電膜の組み合わせとして、1層目に窒化タンタル又はタンタルを、2層目にタンゲステンを用いることができる。上記例の他に、2つの導電膜の組み合わせとして、窒化タンゲステンとタンゲステン、窒化モリブデンとモリブデン、アルミニウムとタンタル、アルミニウムとチタン等が挙げられる。タンゲステンや窒化タンタルは、耐熱性が高いため、2層の導電膜を形成した後の工程において、熱活性化を目的とした加熱処理を行うことができる。また、2層の導電膜の組み合わせとして、例えば、n型の導電性を付与する不純物元素がドーピングされた珪素とニッケルシリサイド、n型の導電性を付与する不純物元素がドーピングされた珪素とタンゲステンシリサイド等も用いることができる。

【0156】

3つの導電膜を積層する3層構造の場合は、モリブデン膜とアルミニウム膜とモリブデン膜の積層構造を採用するとよい。

【0157】

また、ゲート電極707に酸化インジウム、インジウムスズ酸化物、インジウム亜鉛酸化物、酸化亜鉛、酸化亜鉛アルミニウム、酸窒化亜鉛アルミニウム、又は酸化亜鉛ガリウム等の透光性を有する酸化物導電膜を用いることもできる。

【0158】

なお、マスクを用いずに、液滴吐出法を用いて選択的にゲート電極707を形成しても良い。液滴吐出法とは、所定の組成物を含む液滴を細孔から吐出又は噴出することで所定のパターンを形成する方法を意味し、インクジェット法などがその範疇に含まれる。

【0159】

また、ゲート電極707は、導電膜を形成後、ICP (Inductively Coupled Plasma) エッチング法を用い、エッチング条件（コイル型の電極層に印加される電力量、基板側の電極層に印加される電力量、基板側の電極温度等）を適宜調節することにより、所望のテーパー形状を有するようにエッチングすることができる。また、テーパー形状は、マスクの形状によても角度等を制御することができる。なお、エッチング用ガスとしては、塩素、塩化硼素、塩化珪素もしくは四塩化炭素などの塩素系ガス、四弗化炭素、弗化硫黄もしくは弗化窒素などのフッ素系ガス又は酸素を適宜用いることができる。

【0160】

次に、図7(D)に示すように、ゲート電極707をマスクとして一導電性を付与する不純物元素を半導体層704に添加することで、ゲート電極707と重なるチャネル形成領域710と、チャネル形成領域710を間に挟む一対の不純物領域709とが、半導体層704に形成される。

【0161】

本実施の形態では、半導体層704にp型を付与する不純物元素（例えばボロン）を添加する場合を例に挙げる。

【0162】

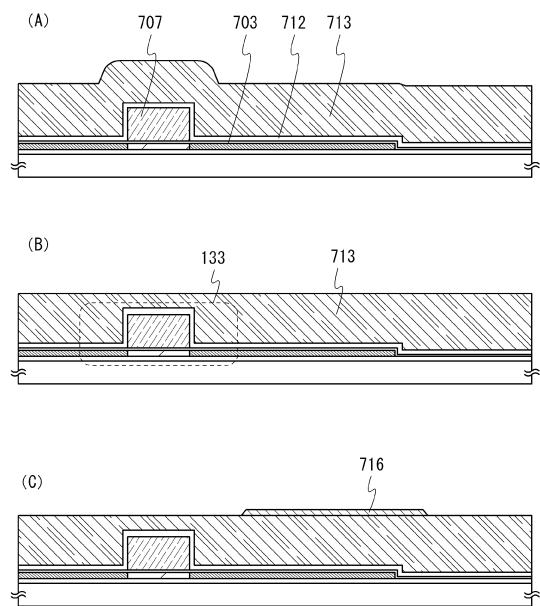

次いで、図8(A)に示すように、ゲート絶縁膜703、ゲート電極707を覆うように、絶縁膜712、絶縁膜713を形成する。具体的に、絶縁膜712、絶縁膜713は、酸化珪素、窒化珪素、窒化酸化珪素、酸化窒化珪素、窒化アルミニウム、窒化酸化アルミニウムなどの無機の絶縁膜を用いることができる。特に、絶縁膜712、絶縁膜713に誘電率の低い（low-k）材料を用いることで、各種電極や配線の重なりに起因する

10

20

30

40

50

容量を十分に低減することが可能になるため好ましい。なお、絶縁膜712、絶縁膜713に、上記材料を用いた多孔性の絶縁膜を適用しても良い。多孔性の絶縁膜では、密度の高い絶縁膜と比較して誘電率が低下するため、電極や配線に起因する寄生容量を更に低減することが可能である。

【0163】

本実施の形態では、絶縁膜712として酸化窒化珪素、絶縁膜713として窒化酸化珪素を用いる場合を例に挙げる。また、本実施の形態では、ゲート電極707上に絶縁膜712、絶縁膜713を形成している場合を例示しているが、本発明はゲート電極707上に絶縁膜を1層だけ形成していても良いし、3層以上の複数の絶縁膜を積層するように形成していても良い。

10

【0164】

次いで、図8(B)に示すように、絶縁膜713にCMP(化学的機械研磨)処理やエッチング処理を行うことにより、絶縁膜713の上面を平坦化する。なお、後に形成されるトランジスタ11の特性を向上させるために、絶縁膜713の表面は可能な限り平坦にしておくことが好ましい。

【0165】

以上の工程により、トランジスタ133を形成することができる。

【0166】

次いで、トランジスタ11の作製方法について説明する。まず、図8(C)に示すように、絶縁膜713上に酸化物半導体層716を形成する。

20

【0167】

酸化物半導体層としては、少なくともインジウム(In)あるいは亜鉛(Zn)を含むことが好ましい。特にInとZnを含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Ga)を有することが好ましい。また、スタビライザーとしてスズ(Sn)を有することが好ましい。また、スタビライザーとしてハフニウム(Hf)を有することが好ましい。また、スタビライザーとしてアルミニウム(Al)を有することが好ましい。

【0168】

また、他のスタビライザーとして、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロビウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)のいずれか一種あるいは複数種を有してもよい。

30

【0169】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるIn-Zn系酸化物、Sn-Zn系酸化物、Al-Zn系酸化物、Zn-Mg系酸化物、Sn-Mg系酸化物、In-Mg系酸化物、In-Ga系酸化物、三元系金属の酸化物であるIn-Ga-Zn系酸化物(IGZOとも表記する)、In-Al-Zn系酸化物、In-Sn-Zn系酸化物、Sn-Ga-Zn系酸化物、Al-Ga-Zn系酸化物、Sn-Al-Zn系酸化物、In-Hf-Zn系酸化物、In-La-Zn系酸化物、In-Ce-Zn系酸化物、In-Pr-Zn系酸化物、In-Nd-Zn系酸化物、In-Sm-Zn系酸化物、In-Eu-Zn系酸化物、In-Gd-Zn系酸化物、In-Tb-Zn系酸化物、In-Dy-Zn系酸化物、In-Ho-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Lu-Zn系酸化物、四元系金属の酸化物であるIn-Sn-Ga-Zn系酸化物、In-Hf-Ga-Zn系酸化物、In-Al-Ga-Zn系酸化物、In-Sn-Al-Zn系酸化物、In-Sn-Hf-Zn系酸化物、In-Hf-Al-Zn系酸化物を用いることができる。また、上記酸化物半導体にInとGaとSnとZn以外の元素、例えばSiO<sub>2</sub>を含ませてもよい。

40

50

## 【0170】

なお、ここで、例えば、In-Ga-Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。In-Ga-Zn系酸化物は、無電界時の抵抗が十分に高くオフ電流を十分に小さくすることが可能であり、また、電界効果移動度も高いため、半導体装置に用いる半導体材料としては好適である。

## 【0171】

また、例えば、In-Sn-Zn系酸化物とは、In、Sn、Znを主成分として有する酸化物という意味であり、InとSnとZnの比率は問わない。また、InとSnとZn以外の金属元素が入っていてもよい。

10

## 【0172】

また、酸化物半導体層として、化学式 $InM O_3 (ZnO)_m$  ( $m > 0$ 、且つ、 $m$ は整数でない)で表記される材料を用いてもよい。ここで、Mは、Ga、Fe、Mn及びCoから選ばれた一の金属元素または複数の金属元素を示す。また、酸化物半導体として、 $In_3 SnO_5 (ZnO)_n$  ( $n > 0$ 、且つ、 $n$ は整数)で表記される材料を用いてもよい。

## 【0173】

例えば、 $In : Ga : Zn = 1 : 1 : 1$  ( $= 1/3 : 1/3 : 1/3$ ) あるいは  $In : Ga : Zn = 2 : 2 : 1$  ( $= 2/5 : 2/5 : 1/5$ ) の原子数比のIn-Ga-Zn系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、 $In : Sn : Zn = 1 : 1 : 1$  ( $= 1/3 : 1/3 : 1/3$ )、 $In : Sn : Zn = 2 : 1 : 3$  ( $= 1/3 : 1/6 : 1/2$ ) あるいは  $In : Sn : Zn = 2 : 1 : 5$  ( $= 1/4 : 1/8 : 5/8$ ) の原子数比のIn-Sn-Zn系酸化物やその組成の近傍の酸化物を用いるとよい。

20

## 【0174】

しかし、これらに限られず、必要とする半導体特性(移動度、しきい値、ばらつき等)に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間結合距離、密度等を適切なものとすることが好ましい。

## 【0175】

酸化物半導体は単結晶でも、非単結晶でもよい。

30

## 【0176】

非単結晶の場合、非晶質でも、多結晶でもよい。また、非晶質中に結晶性を有する部分を含む構造でもよい。なお、アモルファスは欠陥が多いため、非アモルファスが好ましい。

## 【0177】

なお、酸化物半導体層716は、電子供与体(ドナー)となる水分又は水素などの不純物が低減されて高純度化される(i型化又はi型に限りなく近い状態にされる)ことが好ましい。これにより、酸化物半導体層716にチャネルが形成されない状態において生じる電流を低減することが可能となるからである。具体的には、高純度化された酸化物半導体層716は、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectrometry)による水素濃度の測定値が、 $5 \times 10^{-9} / \text{cm}^3$ 以下、好ましくは $5 \times 10^{-8} / \text{cm}^3$ 以下、より好ましくは $5 \times 10^{-7} / \text{cm}^3$ 以下、更に好ましくは $1 \times 10^{-6} / \text{cm}^3$ 以下である。また、ホール効果測定により測定できる酸化物半導体層のキャリア密度は、 $1 \times 10^{-4} / \text{cm}^3$ 未満、好ましくは $1 \times 10^{-2} / \text{cm}^3$ 未満、更に好ましくは $1 \times 10^{-1} / \text{cm}^3$ 未満である。

40

## 【0178】

ここで、酸化物半導体層中の、水素濃度の分析について触れておく。半導体層中の水素濃度測定は、二次イオン質量分析法で行う。SIMS分析は、その原理上、試料表面近傍や、材質が異なる層との積層界面近傍のデータを正確に得ることが困難であることが知られている。そこで、層中における水素濃度の厚さ方向の分布をSIMSで分析する場合、

50

対象となる層が存在する範囲において、値に極端な変動がなく、ほぼ一定の値が得られる領域における平均値を、水素濃度として採用する。また、測定の対象となる層の厚さが小さい場合、隣接する層内の水素濃度の影響を受けて、ほぼ一定の値が得られる領域を見いだせない場合がある。この場合、当該層が存在する領域における、水素濃度の極大値又は極小値を、当該層中の水素濃度として採用する。更に、当該層が存在する領域において、極大値を有する山型のピーク、極小値を有する谷型のピークが存在しない場合、変曲点の値を水素濃度として採用する。

#### 【0179】

酸化物半導体層716は、絶縁膜713上に形成した酸化物半導体膜を所望の形状に加工することで、形成することができる。上記酸化物半導体膜の膜厚は、2nm以上200nm以下、好ましくは3nm以上50nm以下、更に好ましくは3nm以上20nm以下とする。酸化物半導体膜は、酸化物半導体をターゲットとして用い、スパッタリング法により成膜する。また、酸化物半導体膜は、希ガス（例えばアルゴン）雰囲気下、酸素雰囲気下、又は希ガス（例えばアルゴン）及び酸素混合雰囲気下においてスパッタリング法により形成することができる。

10

#### 【0180】

スパッタリング法を用いて酸化物半導体層716を作製する場合には、ターゲット中の水素濃度のみならず、チャンバー内に存在する水、水素を極力低減しておくことが重要である。具体的には、当該形成以前にチャンバー内をベークする、チャンバー内に導入されるガス中の水、水素濃度を低減する、及びチャンバーからガスの排気する排気系における逆流を防止するなどを行うことが効果的である。

20

#### 【0181】

また、酸化物半導体膜をスパッタリング法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタリングを行い、絶縁膜713の表面に付着している塵埃を除去してもよい。逆スパッタリングとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウムなどを用いてもよい。また、アルゴン雰囲気に酸素、亜酸化窒素などを加えた雰囲気で行ってもよい。また、アルゴン雰囲気に塩素、四フッ化炭素などを加えた雰囲気で行ってもよい。

#### 【0182】

30

また、酸化物半導体膜に水素、水酸基及び水分がなるべく含まれないようにするために、成膜の前処理として、スパッタリング装置の予備加熱室で絶縁膜712及び絶縁膜713までが形成された基板700を予備加熱し、基板700に吸着した水分又は水素などの不純物を脱離し排気してもよい。なお、予備加熱の温度は、100以上400以下、好ましくは150以上300以下である。また、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。また、この予備加熱は、後に行われるゲート絶縁膜721の成膜前に、導電層719、導電層720まで形成した基板700にも同様に行ってもよい。

#### 【0183】

本実施の形態では、In（インジウム）、Ga（ガリウム）、及びZn（亜鉛）を含むターゲットを用いたスパッタリング法により得られる膜厚30nmのIn-Ga-Zn-O系酸化物半導体の薄膜を、酸化物半導体膜として用いる。上記ターゲットとして、例えば、各金属の組成比がIn:Ga:Zn=2:2:1、In:Ga:Zn=1:1:1、又はIn:Ga:Zn=1:1:2であるターゲットを用いることができる。また、In、Ga、及びZnを含むターゲットの充填率は90%以上100%以下、好ましくは95%以上100%未満である。充填率の高いターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。その他にもIn-Ga-Zn系酸化物において、各金属の組成比がIn:Ga:Zn=2:1:3、In:Ga:Zn=3:1:2、In:Ga:Zn=4:2:3又はIn:Ga:Zn=3:1:4であるターゲットを用いると好ましい。Gaに対しInの組成比を高めることで、In-Ga-Zn系酸化物の電界効果移動

40

50

度をさらに高めることができる。なお、金属元素の組成比は完全に上記整数比でなくともよい。上記整数比から多少ずれていってもその傾向が見られるならば許容されうる。

【0184】

または、In、Sn及びZnを含むターゲットを用いたスパッタリング法により酸化物半導体膜を形成してもよい。かかる場合、ターゲットの組成比は、In:Sn:Znが原子数比で、1:2:2、2:1:3、1:1:1、または20:45:35などとなる酸化物ターゲットを用いる。

【0185】

本実施の形態では、減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタリングガスを導入し、上記ターゲットを用いて酸化物半導体膜を成膜する。成膜時に、基板温度を100以上600以下、好みしくは200以上400以下としても良い。基板を加熱しながら成膜することにより、成膜した酸化物半導体膜に含まれる不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減される。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好みしい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好みしい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて処理室を排気すると、例えば、水素原子、水(H<sub>2</sub>O)など水素原子を含む化合物(より好みしくは炭素原子を含む化合物も)等が排気されるため、当該処理室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

10

20

【0186】

成膜条件の一例としては、基板とターゲットの間との距離を100mm、圧力0.6Pa、直流(DC)電源0.5kW、酸素(酸素流量比率100%)雰囲気下の条件が適用される。なお、パルス直流(DC)電源を用いると、成膜時に発生する塵埃が軽減でき、膜厚分布も均一となるために好みしい。

【0187】

また、スパッタリング装置の処理室のリーケートを $1 \times 10^{-10} \text{ Pa} \cdot \text{m}^3 / \text{秒}$ 以下とすることで、スパッタリング法による成膜途中における酸化物半導体膜への、アルカリ金属、水素化物等の不純物の混入を低減することができる。また、排気系として上述した吸着型の真空ポンプを用いることで、排気系からのアルカリ金属、水素原子、水素分子、水、水酸基、または水素化物等の不純物の逆流を低減することができる。

30

【0188】

また、ターゲットの純度を、99.99%以上とすることで、酸化物半導体膜に混入するアルカリ金属、水素原子、水素分子、水、水酸基、または水素化物等を低減することができる。また、当該ターゲットを用いることで、酸化物半導体膜において、リチウム、ナトリウム、カリウム等のアルカリ金属の濃度を低減することができる。

【0189】

なお、酸化物半導体層は非晶質であっても良いが、結晶性を有していても良い。結晶性を有する酸化物半導体層としては、c軸配向を有した結晶性酸化物半導体(C Axis Aligned Crystalline Oxide Semiconductor: CAAAC-OSともいう)であっても、トランジスタの信頼性を高めるという効果を得ることができるので、好みしい。

40

【0190】

具体的に、CAAAC-OSは、広義に、非単結晶であって、そのab面に垂直な方向から見て、三角形、六角形、正三角形、または正六角形の原子配列を有する。なおかつ、CAAAC-OSは、c軸に垂直な方向に金属原子が層状に配列した相、または、金属原子と酸素原子が層状に配列した相を、含む。

【0191】

CAAAC-OSは、非晶質の酸化物半導体と比較して、金属と酸素の結合が秩序化している。すなわち、酸化物半導体が非晶質の場合は、個々の金属原子によって配位数が異な

50

ることも有り得るが、 C A A C - O S では金属原子の配位数はほぼ一定となる。そのため、微視的な酸素の欠損が減少し、水素原子（水素イオンを含む）やアルカリ金属原子の脱着による電荷の移動や不安定性を減少させる効果がある。

【 0 1 9 2 】

C A A C - O S は単結晶ではないが、非晶質のみから形成されているものでもない。また、 C A A C - O S は結晶化した部分（結晶部分）を含むが、1つの結晶部分と他の結晶部分の境界を明確に判別できることもある。

【 0 1 9 3 】

C A A C - O S に酸素が含まれる場合、酸素の一部は窒素で置換されてもよい。また、 C A A C - O S を構成する個々の結晶部分の c 軸は一定の方向（例えば、 C A A C - O S が形成される基板面、 C A A C - O S の表面などに垂直な方向）に揃っていてもよい。または、 C A A C - O S を構成する個々の結晶部分の a b 面の法線は一定の方向（例えば、 C A A C - O S が形成される基板面、 C A A C - O S の表面などに垂直な方向）を向いていてもよい。

【 0 1 9 4 】

C A A C - O S は、その組成などに応じて、導体であったり、半導体であったり、絶縁体であったりする。また、その組成などに応じて、可視光に対して透明であったり不透明であったりする。

【 0 1 9 5 】

例えば、膜状に形成された C A A C - O S を、膜表面または C A A C - O S が形成される基板面に垂直な方向から電子顕微鏡で観察すると三角形または六角形の原子配列が認められる。

【 0 1 9 6 】

さらに、電子顕微鏡で膜断面を観察すると金属原子または金属原子および酸素原子（または窒素原子）の層状配列が認められる。

【 0 1 9 7 】

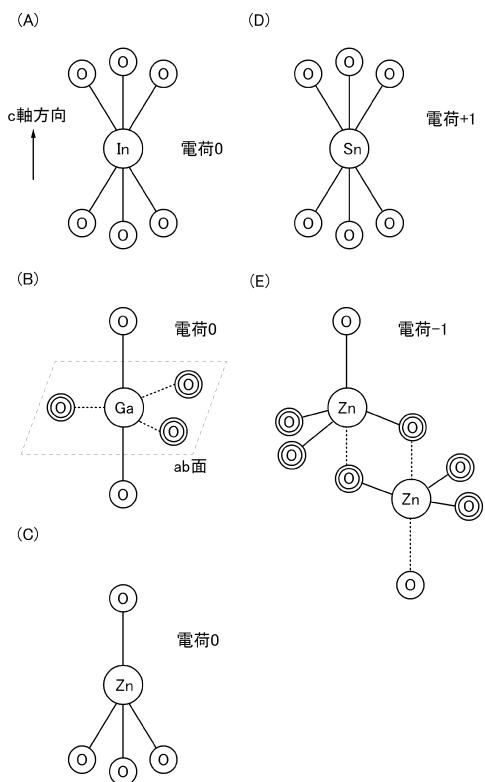

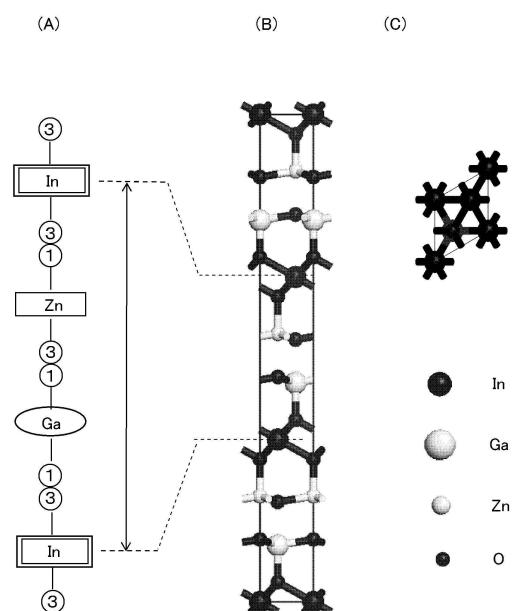

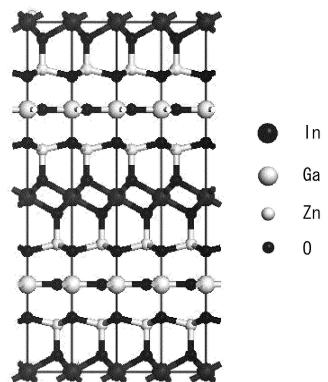

図 1 2 乃至図 1 4 を用いて、 C A A C - O S に含まれる結晶構造の一例について説明する。

【 0 1 9 8 】

なお、図 1 2 乃至図 1 4 において、上方向が c 軸方向であり、 c 軸方向と直交する面が a b 面である。本実施の形態において、上半分、下半分とは、 a b 面を境にした場合の上半分、下半分をいう。また、図 1 2 において、丸で囲まれた O は 4 配位の O を示し、二重丸で囲まれた O は 3 配位の O を示す。

【 0 1 9 9 】

図 1 2 ( A ) に、1個の 6 配位の I n と、 I n に近接の 6 個の 4 配位の酸素原子（以下 4 配位の O ）と、を有する構造を示す。ここでは、金属原子が 1 個に対して、近接の酸素原子のみ示した構造を小グループと呼ぶ。

【 0 2 0 0 】

図 1 2 ( A ) の構造は、八面体構造をとるが、簡単のため平面構造で示している。

【 0 2 0 1 】

なお、図 1 2 ( A ) の構造は上半分および下半分にはそれぞれ 3 個ずつ 4 配位の O がある。図 1 2 ( A ) の構造に示す小グループは電荷が 0 である。

【 0 2 0 2 】

図 1 2 ( B ) に、1個の 5 配位の G a と、 G a に近接の 3 個の 3 配位の酸素原子（以下 3 配位の O ）と、 G a に近接の 2 個の 4 配位の O と、を有する構造を示す。

【 0 2 0 3 】

3 配位の O は、いずれも a b 面に存在する。図 1 2 ( B ) の構造の上半分および下半分にはそれぞれ 1 個ずつ 4 配位の O がある。また、 I n も 5 配位をとるため、図 1 2 ( B ) の構造をとりうる。図 1 2 ( B ) の構造の小グループは電荷が 0 である。

【 0 2 0 4 】

10

20

30

40

50

図12(C)に、1個の4配位のZnと、Znに近接の4個の4配位のOと、を有する構造を示す。

【0205】

図12(C)の構造の上半分には1個の4配位のOがあり、下半分には3個の4配位のOがある。または、図12(C)の上半分に3個の4配位のOがあり、下半分に1個の4配位のOがあつてもよい。図12(C)の構造の小グループは電荷が0である。

【0206】

図12(D)に、1個の6配位のSnと、Snに近接の6個の4配位のOと、を有する構造を示す。図12(D)の構造の上半分には3個の4配位のOがあり、下半分には3個の4配位のOがある。

10

【0207】

図12(D)の構造の小グループは電荷が+1となる。

【0208】

図12(E)に、2個のZnを含む構造を示す。

【0209】

図12(E)の構造の上半分には1個の4配位のOがあり、下半分には1個の4配位のOがある。図12(E)の構造の小グループは電荷が-1となる。

【0210】

本実施の形態では複数の小グループの集合体を中グループと呼び、複数の中グループの集合体を大グループ(ユニットセルともいう。)と呼ぶ。

20

【0211】

ここで、これらの小グループ同士が結合する規則について説明する。

【0212】

図12(A)に示す6配位のInの上半分の3個のOは下方向にそれぞれ3個の近接Inを有し、下半分の3個のOは上方向にそれぞれ3個の近接Inを有する。

【0213】

図12(B)に示す5配位のGaの上半分の1個のOは下方向に1個の近接Gaを有し、下半分の1個のOは上方向に1個の近接Gaを有する。

【0214】

図12(C)に示す4配位のZnの上半分の1個のOは下方向に1個の近接Znを有し、下半分の3個のOは上方向にそれぞれ3個の近接Znを有する。

30

【0215】

この様に、金属原子の上方向の4配位のOの数と、そのOの下方向にある近接金属原子の数は等しく、同様に金属原子の下方向の4配位のOの数と、そのOの上方向にある近接金属原子の数は等しい。

【0216】

Oは4配位なので、下方向にある近接金属原子の数と、上方向にある近接金属原子の数の和は4になる。従って、金属原子の上方向にある4配位のOの数と、別の金属原子の下方向にある4配位のOの数との和が4個のとき、金属原子を有する二種の小グループ同士は結合することができる。

40

【0217】

その理由を以下に示す。例えば、6配位の金属原子(InまたはSn)が上半分の4配位のOを介して結合する場合、4配位のOが3個であるため、5配位の金属原子(GaまたはIn)の上半分の4配位のO、5配位の金属原子(GaまたはIn)の下半分の4配位のOまたは4配位の金属原子(Zn)の上半分の4配位のOのいずれかと結合することになる。

【0218】

これらの配位数を有する金属原子は、c軸方向において、4配位のOを介して結合する。

【0219】

50

また、このほかにも、層構造の合計の電荷が 0 となるように複数の小グループが結合して中グループを構成する。

【0220】

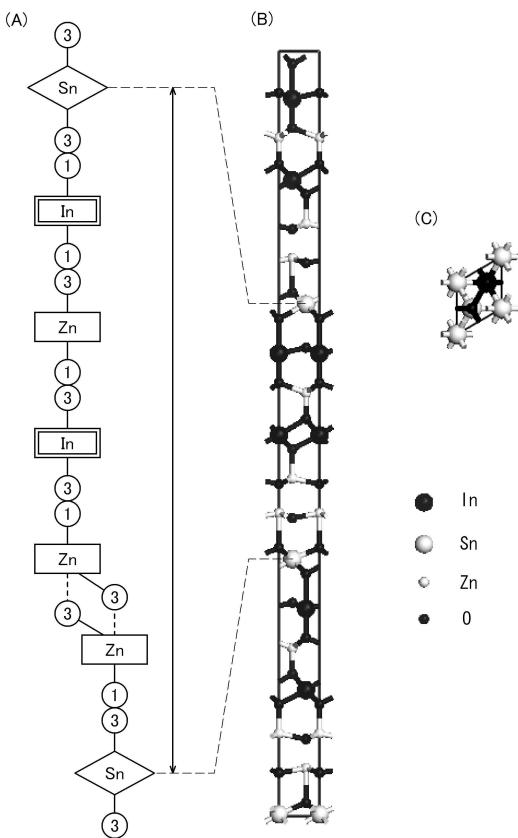

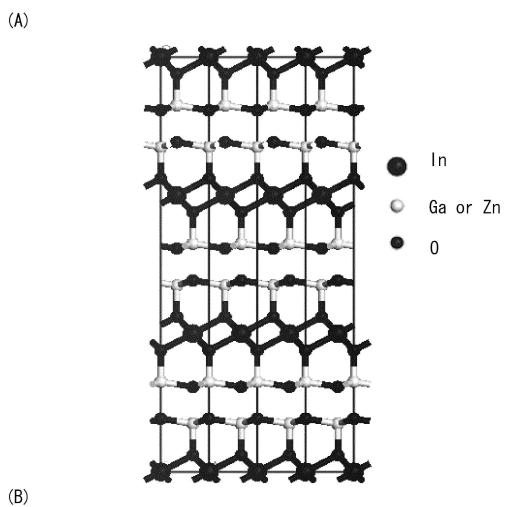

図 13 (A) に、  $I_n - S_n - Z_n - O$  系の層構造を構成する中グループのモデル図を示す。図 13 (B) に、 3 つの中グループで構成される大グループを示す。

【0221】

なお、図 13 (C) は、図 13 (B) の層構造を  $c$  軸方向から観察した場合の原子配列を示す。

【0222】

図 13 (A) に示した中グループでは、 3 配位の  $O$  は省略し、 4 配位の  $O$  は個数のみである。例えば、  $S_n$  の上半分および下半分にはそれぞれ 3 個ずつ 4 配位の  $O$  があることを丸枠の 3 として示している。

【0223】

同様に、図 13 (A) に示した中グループにおいて、  $I_n$  の上半分および下半分にはそれぞれ 1 個ずつ 4 配位の  $O$  があり、丸枠の 1 として示している。

【0224】

また、図 13 (A) に示した中グループにおいて、下半分には 1 個の 4 配位の  $O$  があり、上半分には 3 個の 4 配位の  $O$  がある  $Z_n$  と、上半分には 1 個の 4 配位の  $O$  があり、下半分には 3 個の 4 配位の  $O$  がある  $Z_n$  とを示している。

【0225】

図 13 (A) に示した中グループにおいて、  $I_n - S_n - Z_n - O$  系の層構造を構成する中グループは、上から順に 4 配位の  $O$  が 3 個ずつ上半分および下半分にある  $S_n$  が、 4 配位の  $O$  が 1 個ずつ上半分および下半分にある  $I_n$  と結合する。

【0226】

その  $I_n$  が、上半分に 3 個の 4 配位の  $O$  がある  $Z_n$  と結合する。

【0227】

その  $Z_n$  の下半分の 1 個の 4 配位の  $O$  を介して 4 配位の  $O$  が 3 個ずつ上半分および下半分にある  $I_n$  と結合する。

【0228】

その  $I_n$  が、上半分に 1 個の 4 配位の  $O$  がある  $Z_n$  2 個からなる小グループと結合する。

【0229】

この小グループの下半分の 1 個の 4 配位の  $O$  を介して 4 配位の  $O$  が 3 個ずつ上半分および下半分にある  $S_n$  と結合している構成である。

【0230】

この中グループが複数結合して大グループを構成する。

【0231】

ここで、 3 配位の  $O$  および 4 配位の  $O$  の場合、結合 1 本当たりの電荷はそれぞれ -0.667、 -0.5 と考えることができる。

【0232】

例えば、  $I_n$  (6 配位または 5 配位)、  $Z_n$  (4 配位)、  $S_n$  (5 配位または 6 配位) の電荷は、それぞれ +3、 +2、 +4 である。従って、  $S_n$  を含む小グループは電荷が +1 となる。そのため、  $S_n$  を含む層構造を形成するためには、電荷 +1 を打ち消す電荷 -1 が必要となる。

【0233】

電荷 -1 をとる構造として、図 12 (E) の構造に示すように、 2 個の  $Z_n$  を含む小グループが挙げられる。

【0234】

例えば、  $S_n$  を含む小グループが 1 個に対し、 2 個の  $Z_n$  を含む小グループが 1 個あれば、電荷が打ち消されるため、層構造の合計の電荷を 0 とすることができます。

10

20

30

40

50

## 【0235】

具体的には、大グループBが繰り返されることで、 $In - Sn - Zn - O$ 系の結晶( $In_2SnZn_3O_8$ )を得ることができる。

## 【0236】

得られる $In - Sn - Zn - O$ 系の層構造は、 $In_2SnZn_2O_7 (ZnO)_m$ ( $m$ は0または自然数。)とする組成式で表すことができる。

## 【0237】

$In - Sn - Zn - O$ 系以外の酸化物半導体を用いた場合も同様である。

## 【0238】

例えば、図14(A)に、 $In - Ga - Zn - O$ 系の層構造を構成する中グループのモデル図を示す。

10

## 【0239】

図14(A)に示した中グループにおいて、 $In - Ga - Zn - O$ 系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にある $In$ が、4配位のOが1個上半分にある $Zn$ と結合する。

## 【0240】

その $Zn$ の下半分の3個の4配位のOを介して、4配位のOが1個ずつ上半分および下半分にある $Ga$ と結合する。

## 【0241】

その $Ga$ の下半分の1個の4配位のOを介して、4配位のOが3個ずつ上半分および下半分にある $In$ と結合する。

20

## 【0242】

この中グループが複数結合して大グループを構成する。

## 【0243】

図14(B)に3つの中グループで構成される大グループを示す。なお、図14(C)は、図14(B)の層構造をc軸方向から観察した場合の原子配列を示している。

## 【0244】

ここで、 $In$ (6配位または5配位)、 $Zn$ (4配位)、 $Ga$ (5配位)の電荷は、それぞれ+3、+2、+3であるため、 $In$ 、 $Zn$ および $Ga$ のいずれかを含む小グループは、電荷が0となる。

30

## 【0245】

そのため、これらの小グループの組み合わせであれば中グループの合計の電荷は常に0となる。

## 【0246】

また、 $In - Ga - Zn - O$ 系の層構造を構成する中グループは、図14(A)に示した中グループに限定されず、 $In$ 、 $Ga$ 、 $Zn$ の配列が異なる中グループを組み合わせた大グループも取りうる。

## 【0247】

具体的には、図14(B)に示した大グループが繰り返されることで、 $In - Ga - Zn - O$ 系の結晶を得ることができる。なお、得られる $In - Ga - Zn - O$ 系の層構造は、 $InGaO_3 (ZnO)_n$ ( $n$ は自然数。)とする組成式で表すことができる。

40

## 【0248】

$n = 1$ ( $InGaZnO_4$ )の場合は、例えば、図15(A)に示す結晶構造を取りうる。なお、図15(A)に示す結晶構造において、図12(B)で説明したように、 $Ga$ 及び $In$ は5配位をとるため、 $Ga$ が $In$ に置き換わった構造も取りうる。

## 【0249】

また、 $n = 2$ ( $InGaZn_2O_5$ )の場合は、例えば、図15(B)に示す結晶構造を取りうる。なお、図15(B)に示す結晶構造において、図12(B)で説明したように、 $Ga$ 及び $In$ は5配位をとるため、 $Ga$ が $In$ に置き換わった構造も取りうる。

## 【0250】

50

以上のように、C A A C - O S で構成された酸化物半導体膜を用いてトランジスタを作製することで、トランジスタへの光照射またはバイアス - 熱ストレス ( B T ) の付加を行った後に生じる、トランジスタのしきい値電圧の変化量を、低減することができる。よって、安定した電気的特性を有するトランジスタを作製することができる。

#### 【 0 2 5 1 】

C A A C - O S で構成された酸化物半導体膜（以下、C A A C - O S 膜ともいう）は、スパッタリング法によって作製することができる。スパッタリング法を用いてC A A C - O S 膜を成膜する場合には、雰囲気中の酸素ガス比が高い方が好ましい。例えば、アルゴン及び酸素の混合ガス雰囲気中でスパッタリング法を行う場合には、酸素ガス比を30%以上とすることが好ましく、40%以上とすることがより好ましい。雰囲気中からの酸素の補充によって、C A A C - O S の結晶化が促進されるからである。10

#### 【 0 2 5 2 】

また、スパッタリング法を用いてC A A C - O S 膜を成膜する場合には、C A A C - O S 膜が成膜される基板を150℃以上に加熱しておくことが好ましく、170℃以上に加熱しておくことがより好ましい。基板温度の上昇に伴って、C A A C - O S の結晶化が促進されるからである。

#### 【 0 2 5 3 】

また、C A A C - O S 膜に対して、窒素雰囲気中又は真空中において熱処理を行った後には、酸素雰囲気中又は酸素と他のガスとの混合雰囲気中において熱処理を行うことが好ましい。先の熱処理で生じる酸素欠損を後の熱処理における雰囲気中からの酸素供給によって復元することができるからである。20

#### 【 0 2 5 4 】

また、C A A C - O S 膜が成膜される膜表面（被成膜面）は平坦であることが好ましい。C A A C - O S 膜は、当該被成膜面に概略垂直となるc軸を有するため、当該被成膜面に存在する凹凸は、C A A C - O S 膜における結晶粒界の発生を誘発することになるからである。よって、C A A C - O S 膜が成膜される前に当該被成膜表面に対して化学機械研磨（Chemical Mechanical Polishing: CMP）などの平坦化処理を行うことが好ましい。また、当該被成膜面の平均ラフネスは、1nm以下が好ましく、0.3nm以下であることがより好ましく、0.1nm以下であることがさらにより好ましい。30

#### 【 0 2 5 5 】

上述のように形成した酸化物半導体である膜をエッティングして酸化物半導体層716を形成する。酸化物半導体層716を形成するためのエッティングは、ドライエッティングでもウェットエッティングでもよく、両方を用いてもよい。ドライエッティングに用いるエッティングガスとしては、塩素を含むガス（塩素系ガス、例えば塩素（Cl<sub>2</sub>）、三塩化硼素（BCl<sub>3</sub>）、四塩化珪素（SiCl<sub>4</sub>）、四塩化炭素（CCl<sub>4</sub>）など）が好ましい。また、フッ素を含むガス（フッ素系ガス、例えば四弗化炭素（CF<sub>4</sub>）、六弗化硫黄（SF<sub>6</sub>）、三弗化窒素（NF<sub>3</sub>）、トリフルオロメタン（CHF<sub>3</sub>）など）、臭化水素（HBr）、酸素（O<sub>2</sub>）、これらのガスにヘリウム（He）やアルゴン（Ar）などの希ガスを添加したガス、などを用いることができる。40

#### 【 0 2 5 6 】

ドライエッティング法としては、平行平板型RIE（Reactive Ion Etching）法や、ICP（Inductively Coupled Plasma: 誘導結合型プラズマ）エッティング法を用いることができる。所望の形状にエッティングできるように、エッティング条件（コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等）を適宜調節する。

#### 【 0 2 5 7 】

ウェットエッティングに用いるエッティング液として、磷酸と酢酸と硝酸を混ぜた溶液、クエン酸やシュウ酸などの有機酸を用いることができる。本実施の形態では、ITO-07N（関東化学社製）を用いる。

10

20

30

40

50

## 【0258】

酸化物半導体層716を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

## 【0259】

なお、次工程の導電膜を形成する前に逆スパッタリングを行い、酸化物半導体層716及び絶縁膜713の表面に付着しているレジスト残渣などを除去することが好ましい。

## 【0260】

なお、スパッタリング等で成膜された酸化物半導体膜中には、不純物としての水分又は水素（水酸基を含む）が含まれていることがある。水分又は水素はドナー準位を形成しやすいため、酸化物半導体にとっては不純物である。そこで、本発明の一態様では、酸化物半導体膜中の水分又は水素などの不純物を低減（脱水化または脱水素化）するために、酸化物半導体層716に対して、減圧雰囲気下、窒素や希ガスなどの不活性ガス雰囲気下、酸素ガス雰囲気下、又は超乾燥工ア（CRDS（キャビティリングダウンレーザー分光法）方式の露点計を用いて測定した場合の水分量が20 ppm（露点換算で-55）以下、好ましくは1 ppm以下、好ましくは10 ppb以下の空気）雰囲気下で、酸化物半導体層716に加熱処理を施す。

10

## 【0261】

酸化物半導体層716に加熱処理を施すことで、酸化物半導体層716中の水分又は水素を脱離させることができる。具体的には、250以上750以下、好ましくは400以上基板の歪み点未満の温度で加熱処理を行えば良い。例えば、500、3分間以上6分間以下で行えばよい。加熱処理にRTA法を用いれば、短時間に脱水化又は脱水素化が行えるため、ガラス基板の歪点を超える温度でも処理することができる。

20

## 【0262】

本実施の形態では、加熱処理装置の一つである電気炉を用いる。

## 【0263】

なお、加熱処理装置は電気炉に限らず、抵抗発熱体などの発熱体からの熱伝導又は熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA（Gas Rapid Thermal Anneal）装置、LRTA（Lamp Rapid Thermal Anneal）装置等のRTA（Rapid Thermal Anneal）装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光（電磁波）の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、又は窒素のような、加熱処理によって被処理物と反応しない不活性ガスが用いられる。

30

## 【0264】

加熱処理においては、窒素、又はヘリウム、ネオン、アルゴン等の希ガスに、水分又は水素などが含まれないことが好ましい。又は、加熱処理装置に導入する窒素、又はヘリウム、ネオン、アルゴン等の希ガスの純度を、6N（99.9999%）以上、好ましくは7N（99.99999%）以上、（即ち不純物濃度を1 ppm以下、好ましくは0.1 ppm以下）とすることが好ましい。

40

## 【0265】

なお、酸化物半導体は不純物に対して鈍感であり、膜中にはかなりの金属不純物が含まれていても問題がなく、ナトリウム（Na）のようなアルカリ金属が多量に含まれる廉価なソーダ石灰ガラスも使えると指摘されている（神谷、野村、細野、「アモルファス酸化物半導体の物性とデバイス開発の現状」、固体物理、2009年9月号、Vol.44、pp.621-633.）。しかし、このような指摘は適切でない。アルカリ金属は酸化物半導体を構成する元素ではないため、不純物である。アルカリ土類金属も、酸化物半導体を構成する元素ではない場合において、不純物となる。特に、アルカリ金属のうちNa

50

は、酸化物半導体層に接する絶縁膜が酸化物である場合、当該絶縁膜中に拡散して  $\text{Na}^+$  となる。また、 $\text{Na}$  は、酸化物半導体層内において、酸化物半導体を構成する金属と酸素の結合を分断する、或いは、その結合中に割り込む。その結果、例えば、閾値電圧がマイナス方向にシフトすることによるノーマリオン化、移動度の低下等の、トランジスタの特性の劣化が起こり、加えて、特性のばらつきも生じる。この不純物によりもたらされるトランジスタの特性の劣化と、特性のばらつきは、酸化物半導体層中の水素濃度が十分に低い場合において顕著に現れる。従って、酸化物半導体層中の水素濃度が  $1 \times 10^{-8} / \text{cm}^3$  以下、より好ましくは  $1 \times 10^{-7} / \text{cm}^3$  以下である場合には、上記不純物の濃度を低減することが望ましい。具体的に、二次イオン質量分析法による  $\text{Na}$  濃度の測定値は、 $5 \times 10^{-6} / \text{cm}^3$  以下、好ましくは  $1 \times 10^{-6} / \text{cm}^3$  以下、更に好ましくは  $1 \times 10^{-5} / \text{cm}^3$  以下とするとよい。同様に、 $\text{Li}$  濃度の測定値は、 $5 \times 10^{-5} / \text{cm}^3$  以下、好ましくは  $1 \times 10^{-5} / \text{cm}^3$  以下とするとよい。同様に、 $\text{K}$  濃度の測定値は、 $5 \times 10^{-5} / \text{cm}^3$  以下、好ましくは  $1 \times 10^{-5} / \text{cm}^3$  以下とするとよい。

#### 【0266】

以上の工程により、酸化物半導体層 716 中の水素の濃度を低減し、高純度化することができる。それにより酸化物半導体層の安定化を図ることができる。また、ガラス転移温度以下の加熱処理で、キャリア密度が極端に少なく、バンドギャップの広い酸化物半導体層を形成することができる。このため、大面積基板を用いてトランジスタを作製することができ、量産性を高めることができる。また、当該水素濃度が低減され高純度化された酸化物半導体層を用いることで、耐圧性が高く、オフ電流の著しく低いトランジスタを作製することができる。上記加熱処理は、酸化物半導体層の成膜以降であれば、いつでも行うことができる。

#### 【0267】

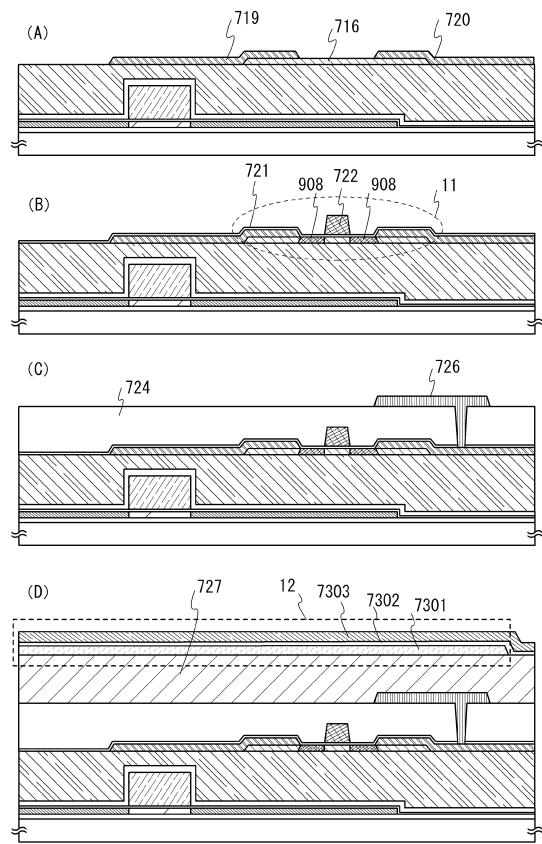

次いで、図 9 (A) に示すように、酸化物半導体層 716 と接する導電層 719 と、酸化物半導体層 716 と接する導電層 720 を形成する。導電層 719 及び導電層 720 は、ソース電極又はドレイン電極として機能する。

#### 【0268】

具体的に、導電層 719 及び導電層 720 は、スパッタリング法や真空蒸着法で導電膜を形成した後、該導電膜を所定の形状に加工することで、形成することができる。

#### 【0269】

なお、導電層 719 及び導電層 720 となる導電膜を形成する前にゲート絶縁膜 703、絶縁膜 712、絶縁膜 713 に開口部を形成し、半導体層 704 の一部を露出させ、該半導体層 704 に接続されるように導電膜を形成することができる。導電膜を所定の形状に加工することで、導電層 719 及び導電層 720 は、半導体層 704 の一対の不純物領域 709 に接続されるソース電極又はドレイン電極としても機能させることができる。または、導電層 719 及び導電層 720 とは別の導電膜によりトランジスタ 133 のソース電極及びドレイン電極を形成し、導電層 719 又は導電層 720 と接続させるようにしてもよい。

#### 【0270】

導電層 719 及び導電層 720 となる導電膜は、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンから選ばれた元素、又は上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、アルミニウム、銅などの金属膜の下側もしくは上側にクロム、タンタル、チタン、モリブデン、タングステンなどの高融点金属膜を積層させた構成としても良い。また、アルミニウム又は銅は、耐熱性や腐食性の問題を回避するために、高融点金属材料と組み合わせて用いると良い。高融点金属材料としては、モリブデン、チタン、クロム、タンタル、タングステン、ネオジム、スカンジウム、イットリウム等を用いることができる。

#### 【0271】

また、導電層 719 及び導電層 720 となる導電膜は、単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜

10

20

30

40

50

上にチタン膜を積層する2層構造、チタン膜と、そのチタン膜上に重ねてアルミニウム膜を積層し、更にその上にチタン膜を成膜する3層構造などが挙げられる。また、Cu-Mg-Al合金、Mo-Ti合金、Ti、Mo、は、酸化膜との密着性が高い。よって、下層にCu-Mg-Al合金、Mo-Ti合金、Ti、或いはMoで構成される導電膜、上層にCuで構成される導電膜を積層し、上記積層された導電膜を導電層719及び導電層720に用いることで、酸化膜である絶縁膜と、導電層719及び導電層720との密着性を高めることができる。

【0272】

また、導電層719及び導電層720となる導電膜としては、導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム、酸化スズ、酸化亜鉛、インジウムスズ酸化物、インジウム亜鉛酸化物又は前記金属酸化物材料にシリコン若しくは酸化シリコンを含ませたものを用いることができる。

【0273】

導電膜形成後に加熱処理を行う場合には、この加熱処理に耐える耐熱性を導電膜に持たせることができが好ましい。

【0274】

なお、導電膜のエッチングの際に、酸化物半導体層716がなるべく除去されないようにそれぞれの材料及びエッチング条件を適宜調節する。エッチング条件によっては、酸化物半導体層716の露出した部分が一部エッチングされることで、溝部(凹部)が形成されることもある。

【0275】

本実施の形態では、導電膜にチタン膜を用いる。そのため、アンモニアと過酸化水素水を含む溶液(アンモニア過水)を用いて、選択的に導電膜をウェットエッチングすることができる。具体的には、31重量%の過酸化水素水と、28重量%のアンモニア水と水とを、体積比5:2:2で混合したアンモニア過水を用いる。或いは、塩素(Cl<sub>2</sub>)、塩化硼素(BCl<sub>3</sub>)などを含むガスを用いて、導電膜をドライエッチングしても良い。

【0276】

なお、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光に多段階の強度をもたせる多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッチングを行うことで更に形状を変形することができるため、異なるパターンに加工する複数のエッチング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

【0277】

また、酸化物半導体層716と、ソース電極又はドレイン電極として機能する導電層719及び導電層720との間に、ソース領域及びドレイン領域として機能する酸化物導電膜を設けるようにしても良い。酸化物導電膜の材料としては、酸化亜鉛を成分として含むものが好ましく、酸化インジウムを含まないものであることが好ましい。そのような酸化物導電膜として、酸化亜鉛、酸化亜鉛アルミニウム、酸窒化亜鉛アルミニウム、酸化亜鉛ガリウムなどを適用することができる。

【0278】

例えば、酸化物導電膜を形成する場合、酸化物導電膜を形成するためのエッチング加工と、導電層719及び導電層720を形成するためのエッチング加工とを一括で行うようにしても良い。

【0279】

ソース領域及びドレイン領域として機能する酸化物導電膜を設けることで、酸化物半導体層716と導電層719及び導電層720の間の抵抗を下げる所以で、トランジスタの高速動作を実現させることができる。また、ソース領域及びドレイン領域とし

10

20

30

40

50

て機能する酸化物導電膜を設けることで、トランジスタの耐圧を高めることができる。

【0280】

次いで、N<sub>2</sub>O、N<sub>2</sub>、又はArなどのガスを用いたプラズマ処理を行うようにしても良い。このプラズマ処理によって露出している酸化物半導体層の表面に付着した水などを除去する。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を行ってもよい。

【0281】

なお、プラズマ処理を行った後、図9(B)に示すように、導電層719及び導電層720と、酸化物半導体層716とを覆うように、ゲート絶縁膜721を形成する。そして、ゲート絶縁膜721上において、酸化物半導体層716と重なる位置にゲート電極722を形成する。

10

【0282】

そして、ゲート電極722が形成された後にゲート電極722をマスクとして酸化物半導体層716にn型の導電性を付与するドーパントを添加し、一対の高濃度領域908を形成する。なお、酸化物半導体層716のうち、ゲート絶縁膜721を間に挟んでゲート電極722と重なる領域がチャネル形成領域となる。酸化物半導体層716では、一対の高濃度領域908の間にチャネル形成領域が設けられている。高濃度領域908を形成するためのドーパントの添加は、イオン注入法を用いることができる。ドーパントは、例えばヘリウム、アルゴン、キセノンなどの希ガスや、窒素、リン、ヒ素、アンチモンなどの15族原子などを用いることができる。例えば、窒素をドーパントとして用いた場合、高濃度領域908中の窒素原子の濃度は、 $5 \times 10^{19} / \text{cm}^3$ 以上 $1 \times 10^{22} / \text{cm}^3$ 以下であることが望ましい。n型の導電性を付与するドーパントが添加されている高濃度領域908は、酸化物半導体層716中の他の領域に比べて導電性が高くなる。よって、高濃度領域908を酸化物半導体層716に設けることで、ソース電極とドレイン電極(導電層719と導電層720)の間の抵抗を下げることができる。

20

【0283】

そして、ソース電極とドレイン電極(導電層719と導電層720)の間の抵抗を下げることで、トランジスタ11の微細化を進めても、高いオン電流と、高速動作を確保することができる。また、トランジスタ11の微細化により、半導体装置300を小型化することができる。

【0284】

30

また、In-Ga-Zn-O系酸化物半導体を酸化物半導体層716に用いた場合、窒素を添加した後、300以上600以下で1時間程度加熱処理を施すことにより、高濃度領域908中の酸化物半導体はウルツ鉱型の結晶構造を有するようになる。高濃度領域908中の酸化物半導体がウルツ鉱型の結晶構造を有することで、さらに高濃度領域908の導電性を高め、ソース電極とドレイン電極(導電層719と導電層720)の間の抵抗を下げることができる。なお、ウルツ鉱型の結晶構造を有する酸化物半導体を形成して、ソース電極とドレイン電極(導電層719と導電層720)の間の抵抗を効果的に下げるためには、窒素をドーパントとして用いた場合、高濃度領域908中の窒素原子の濃度を、 $1 \times 10^{20} / \text{cm}^3$ 以上7atoms%以下とすることが望ましい。しかし、窒素原子が上記範囲よりも低い濃度であっても、ウルツ鉱型の結晶構造を有する酸化物半導体が得られる場合もある。

40

【0285】

ゲート絶縁膜721は、ゲート絶縁膜703と同様の材料、同様の積層構造を用いて形成することが可能である。

【0286】

なお、ゲート絶縁膜721は、水分や、水素などの不純物を極力含まないことが望ましく、単層の絶縁膜であっても良いし、積層された複数の絶縁膜で構成されていても良い。ゲート絶縁膜721に水素が含まれると、その水素が酸化物半導体層716へ侵入し、又は水素が酸化物半導体層716中の酸素を引き抜き、酸化物半導体層716が低抵抗化(n型化)してしまい、寄生チャネルが形成されるおそれがある。

50

## 【0287】

よって、ゲート絶縁膜721はできるだけ水素を含まない膜になるように、成膜方法に水素を用いないことが重要である。

## 【0288】

上記ゲート絶縁膜721には、バリア性の高い材料を用いるのが望ましい。例えば、バリア性の高い絶縁膜として、窒化珪素膜、窒化酸化珪素膜、窒化アルミニウム膜、又は窒化酸化アルミニウム膜などを用いることができる。複数の積層された絶縁膜を用いる場合、窒素の含有比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜を、上記バリア性の高い絶縁膜よりも、酸化物半導体層716に近い側に形成する。そして、窒素の含有比率が低い絶縁膜を間に挟んで、導電層719及び導電層720及び酸化物半導体層716と重なるように、バリア性の高い絶縁膜を形成する。バリア性の高い絶縁膜を用いることで、酸化物半導体層716内、ゲート絶縁膜721内、或いは、酸化物半導体層716と他の絶縁膜の界面とその近傍に、水分又は水素などの不純物が入り込むのを防ぐことができる。

## 【0289】

また、酸化物半導体層716に接するように窒素の比率が低い酸化珪素膜、酸化窒化珪素膜などの絶縁膜を形成することで、バリア性の高い材料を用いた絶縁膜が直接酸化物半導体層716に接するのを防ぐことができる。

## 【0290】

本実施の形態では、スパッタリング法で形成された膜厚200nmの酸化珪素膜上に、スパッタリング法で形成された膜厚100nmの窒化珪素膜を積層させた構造を有する、ゲート絶縁膜721を形成する。成膜時の基板温度は、室温以上300以下とすればよく、本実施の形態では100とする。

## 【0291】

なお、ゲート絶縁膜721を形成した後に、加熱処理を施しても良い。加熱処理は、窒素、超乾燥空気、又は希ガス（アルゴン、ヘリウムなど）の雰囲気下において、好ましくは200以上400以下、例えば250以上350以下で行う。上記ガスは、水の含有量が20ppm以下、好ましくは1ppm以下、より好ましくは10ppb以下であることが望ましい。

## 【0292】

本実施の形態では、例えば、窒素雰囲気下で250、1時間の加熱処理を行う。或いは、導電層719及び導電層720を形成する前に、水分又は水素を低減させるための酸化物半導体層に対して行った先の加熱処理と同様に、高温短時間のRTA処理を行っても良い。酸素を含むゲート絶縁膜721が設けられた後に、加熱処理が施されることによって、酸化物半導体層716に対して行った先の加熱処理により、酸化物半導体層716に酸素欠損が発生していたとしても、ゲート絶縁膜721から酸化物半導体層716に酸素が供与される。そして、酸化物半導体層716に酸素が供与されることで、酸化物半導体層716において、ドナーとなる酸素欠損を低減し、化学量論的組成比を満たすことが可能である。酸化物半導体層716には、化学量論的組成比を超える量の酸素が含まれていることが好ましい。その結果、酸化物半導体層716をi型に近づけることができ、酸素欠損によるトランジスタの電気特性のばらつきを軽減し、電気特性の向上を実現することができる。この加熱処理を行うタイミングは、ゲート絶縁膜721の形成後であれば特に限定されず、他の工程、例えば樹脂膜形成時の加熱処理や、透明導電膜を低抵抗化させるための加熱処理と兼ねることで、工程数を増やすことなく、酸化物半導体層716をi型に近づけることができる。

## 【0293】

また、酸素雰囲気下で酸化物半導体層716に加熱処理を施すことで、酸化物半導体に酸素を添加し、酸化物半導体層716中においてドナーとなる酸素欠損を低減させても良い。加熱処理の温度は、例えば100以上350未満、好ましくは150以上250未満で行う。上記酸素雰囲気下の加熱処理に用いられる酸素ガスには、水、水素など

10

20

30

40

50

が含まれないことが好ましい。又は、加熱処理装置に導入する酸素ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち酸素中の不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

#### 【0294】

或いは、イオン注入法又はイオンドーピング法などを用いて、酸化物半導体層716に酸素を添加することで、ドナーとなる酸素欠損を低減させても良い。例えば、2.45GHzのマイクロ波でプラズマ化した酸素を酸化物半導体層716に添加すれば良い。

#### 【0295】

また、ゲート電極722は、ゲート絶縁膜721上に導電膜を形成した後、該導電膜をエッティング加工することで形成することができる。ゲート電極722は、ゲート電極707、或いは導電層719及び導電層720と同様の材料を用いて形成することができる。

10

#### 【0296】

ゲート電極722の膜厚は、10nm~400nm、好ましくは100nm~200nmとする。本実施の形態では、タンゲステンターゲットを用いたスパッタリング法により150nmのゲート電極用の導電膜を形成した後、該導電膜をエッティングにより所望の形状に加工することで、ゲート電極722を形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

#### 【0297】

20

以上の工程により、トランジスタ11が形成される。

#### 【0298】

トランジスタ11は、ソース電極及びドレイン電極(導電層719及び導電層720)と、ゲート電極722とが重なっていない。すなわち、ソース電極及びドレイン電極(導電層719及び導電層720)とゲート電極722との間には、ゲート絶縁膜721の膜厚よりも大きい間隔が設けられている。よって、トランジスタ11は、ソース電極及びドレイン電極とゲート電極との間に形成される寄生容量を小さく抑えることができるので、高速動作を実現することができる。

#### 【0299】

なお、トランジスタ11として、チャネルが酸化物半導体層に形成されるトランジスタに限定されず、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体材料を、チャネル形成領域に含むトランジスタを用いることもできる。このような半導体材料としては、酸化物半導体の他に、例えば、炭化シリコン、窒化ガリウムなどが挙げられる。このような半導体材料をチャネル形成領域に含むことで、オフ電流が極めて低いトランジスタを実現することができる。

30

#### 【0300】

また、トランジスタ11はシングルゲート構造のトランジスタを用いて説明したが、必要に応じて、電気的に接続された複数のゲート電極を有することで、チャネル形成領域を複数有する、マルチゲート構造のトランジスタも形成することができる。

#### 【0301】

40

なお、酸化物半導体層716に接する絶縁膜(本実施の形態においては、ゲート絶縁膜721が該当する。)は、第13族元素及び酸素を含む絶縁材料を用いるようにしても良い。酸化物半導体材料には第13族元素を含むものが多く、第13族元素を含む絶縁材料は酸化物半導体との相性が良く、これを酸化物半導体層に接する絶縁膜に用いることで、酸化物半導体層との界面の状態を良好に保つことができる。

#### 【0302】

第13族元素を含む絶縁材料とは、絶縁材料に一又は複数の第13族元素を含むことを意味する。第13族元素を含む絶縁材料としては、例えば、酸化ガリウム、酸化アルミニウム、酸化アルミニウムガリウム、酸化ガリウムアルミニウムなどがある。ここで、酸化アルミニウムガリウムとは、ガリウムの含有量(原子%)よりアルミニウムの含有量(原

50

子% ) が多いものを示し、酸化ガリウムアルミニウムとは、ガリウムの含有量 ( 原子% ) がアルミニウムの含有量 ( 原子% ) 以上のものを示す。

【 0 3 0 3 】

例えば、ガリウムを含有する酸化物半導体層に接して絶縁膜を形成する場合に、絶縁膜に酸化ガリウムを含む材料を用いることで酸化物半導体層と絶縁膜の界面特性を良好に保つことができる。例えば、酸化物半導体層と酸化ガリウムを含む絶縁膜とを接して設けることにより、酸化物半導体層と絶縁膜の界面における水素のパイルアップを低減することができる。なお、絶縁膜に酸化物半導体の成分元素と同じ族の元素を用いる場合には、同様の効果を得ることが可能である。例えば、酸化アルミニウムを含む材料を用いて絶縁膜を形成することも有効である。なお、酸化アルミニウムは、水を透過させにくいという特性を有しているため、当該材料を用いることは、酸化物半導体層への水の侵入防止という点においても好ましい。

【 0 3 0 4 】

また、酸化物半導体層 716 に接する絶縁膜は、酸素雰囲気下による熱処理や、酸素ドープなどにより、絶縁材料を化学量論的組成比より酸素が多い状態とすることが好ましい。酸素ドープとは、酸素をバルクに添加することをいう。なお、当該バルクの用語は、酸素を薄膜表面のみでなく薄膜内部に添加することを明確にする趣旨で用いている。また、酸素ドープには、プラズマ化した酸素をバルクに添加する酸素プラズマドープが含まれる。また、酸素ドープは、イオン注入法又はイオンドーピング法を用いて行ってもよい。

【 0 3 0 5 】

例えば、酸化物半導体層 716 に接する絶縁膜として酸化ガリウムを用いた場合、酸素雰囲気下による熱処理や、酸素ドープを行うことにより、酸化ガリウムの組成を  $\text{Ga}_2\text{O}_x$  ( $X = 3 + , 0 < X < 1$ ) とすることができます。

【 0 3 0 6 】

また、酸化物半導体層 716 に接する絶縁膜として酸化アルミニウムを用いた場合、酸素雰囲気下による熱処理や、酸素ドープを行うことにより、酸化アルミニウムの組成を  $\text{Al}_2\text{O}_x$  ( $X = 3 + , 0 < X < 1$ ) とすることができます。

【 0 3 0 7 】

また、酸化物半導体層 716 に接する絶縁膜として酸化ガリウムアルミニウム ( 酸化アルミニウムガリウム ) を用いた場合、酸素雰囲気下による熱処理や、酸素ドープを行うことにより、酸化ガリウムアルミニウム ( 酸化アルミニウムガリウム ) の組成を  $\text{Ga}_x\text{Al}_2\text{-}_x\text{O}_3+$  ( $0 < X < 2 , 0 < X < 1$ ) とすることができます。

【 0 3 0 8 】

酸素ドープ処理を行うことにより、化学量論的組成比より酸素が多い領域を有する絶縁膜を形成することができる。このような領域を備える絶縁膜と酸化物半導体層が接することにより、絶縁膜中の過剰な酸素が酸化物半導体層に供給され、酸化物半導体層中、又は酸化物半導体層と絶縁膜の界面における酸素欠陥を低減し、酸化物半導体層を  $i$  型化又は  $i$  型に限りなく近くすることができる。

【 0 3 0 9 】

なお、化学量論的組成比より酸素が多い領域を有する絶縁膜は、酸化物半導体層 716 に接する絶縁膜のうち、上層に位置する絶縁膜又は下層に位置する絶縁膜のうち、どちらか一方のみに用いても良いが、両方の絶縁膜に用いる方が好ましい。化学量論的組成比より酸素が多い領域を有する絶縁膜を、酸化物半導体層 716 に接する絶縁膜の、上層及び下層に位置する絶縁膜に用い、酸化物半導体層 716 を挟む構成とすることで、上記効果をより高めることができる。

【 0 3 1 0 】

また、酸化物半導体層 716 の上層又は下層に用いる絶縁膜は、上層と下層で同じ構成元素を有する絶縁膜としても良いし、異なる構成元素を有する絶縁膜としても良い。例えば、上層と下層とも、組成が  $\text{Ga}_2\text{O}_x$  ( $X = 3 + , 0 < X < 1$ ) の酸化ガリウムとしても良いし、上層と下層の一方を組成が  $\text{Ga}_2\text{O}_x$  ( $X = 3 + , 0 < X < 1$ ) の酸化ガ

10

20

30

40

50

リウムとし、他方を組成が  $Al_2O_x$  ( $X = 3 +$  、  $0 < X < 1$ ) の酸化アルミニウムとしても良い。

【0311】

また、酸化物半導体層716に接する絶縁膜は、化学量論的組成比より酸素が多い領域を有する絶縁膜の積層としても良い。例えば、酸化物半導体層716の上層に組成が  $Ga_2O_x$  ( $X = 3 +$  、  $0 < X < 1$ ) の酸化ガリウムを形成し、その上に組成が  $Ga_xAl_{2-x}O_{3+}$  ( $0 < X < 2$  、  $0 < X < 1$ ) の酸化ガリウムアルミニウム(酸化アルミニウムガリウム)を形成してもよい。なお、酸化物半導体層716の下層を、化学量論的組成比より酸素が多い領域を有する絶縁膜の積層としても良いし、酸化物半導体層716の上層及び下層の両方を、化学量論的組成比より酸素が多い領域を有する絶縁膜の積層としても良い。

10

【0312】

次に、図9(C)に示すように、ゲート絶縁膜721、ゲート電極722を覆うように、絶縁膜724を形成する。絶縁膜724は、PVD法やCVD法などを用いて形成することができる。また、酸化珪素、酸化窒化珪素、窒化珪素、酸化ハフニウム、酸化ガリウム、酸化アルミニウム等の無機絶縁材料を含む材料を用いて形成することができる。なお、絶縁膜724には、誘電率の低い材料や、誘電率の低い構造(多孔性の構造など)を用いることが望ましい。絶縁膜724の誘電率を低くすることにより、配線や電極などの間に生じる寄生容量を低減し、動作の高速化を図ることができるためである。なお、本実施の形態では、絶縁膜724を単層構造としているが、本発明の一態様はこれに限定されず、2層以上の積層構造としても良い。

20

【0313】

次に、ゲート絶縁膜721、絶縁膜724に開口部を形成し、導電層720の一部を露出させる。その後、絶縁膜724上に、上記開口部において導電層720と接する配線726を形成する。

【0314】

配線726は、PVD法や、CVD法を用いて導電膜を形成した後、当該導電膜をエッチング加工することによって形成される。また、導電膜の材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンクスチタンから選ばれた元素や、上述した元素を成分とする合金等を用いることができる。マンガン、マグネシウム、ジルコニウム、ベリリウム、ネオジム、スカンジウムのいずれか、又はこれらを複数組み合わせた材料を用いてもよい。

30

【0315】

より具体的には、例えば、絶縁膜724の開口を含む領域にPVD法によりチタン膜を薄く形成し、PVD法によりチタン膜を薄く(5nm程度)形成した後に、開口部に埋め込むようにアルミニウム膜を形成する方法を適用することができる。ここで、PVD法により形成されるチタン膜は、被形成面の酸化膜(自然酸化膜など)を還元し、下部電極など(ここでは導電層720)との接触抵抗を低減させる機能を有する。また、アルミニウム膜のヒロックを防止することができる。また、チタンや窒化チタンなどによるバリア膜を形成した後に、メッキ法により銅膜を形成してもよい。

40

【0316】

次に、図9(D)に示すように、配線726を覆うように絶縁膜727を形成する。更に絶縁膜727上に導電膜を形成し、当該導電膜をエッチング加工することによって導電層7301を形成する。その後、導電層7301を覆うように絶縁膜7302を形成し、絶縁膜7302上に導電膜7303を形成する。こうして容量素子12を形成することができる。容量素子12の一対の電極のうちの一方が導電層7301に対応し、一対の電極のうちの他方が導電膜7303に対応し、誘電体層が絶縁膜7302に対応する。ここで、絶縁膜727、導電層7301、絶縁膜7302、導電膜7303の材料は、その他絶縁膜や導電層と同様の材料を用いることができる。なお、容量素子12の一対の電極のうちの一方を、トランジスタ11のソース若しくはドレイン又はゲートと電気的に接続させ

50

ることができる。

【0317】

上述した一連の工程により、半導体装置を作製することができる。

【0318】

上述の工程を用いることによって、半導体装置が有する、酸化物半導体を用いたトランジスタ11を酸化物半導体以外の材料を用いたトランジスタ133上に重ねて配置することができる。これにより半導体装置を小型化することができる。また、容量素子を有する場合には、さらに容量素子12を重ねて配置することにより、半導体装置を小型化することができる。

【0319】

容量素子にソース又はドレインが接続されるトランジスタ（図3のトランジスタ310、図4のトランジスタ310、トランジスタ410）の半導体層に酸化物半導体を用いたトランジスタを採用することにより、容量素子に保持された電荷のリークを無くすことができるため、容量素子12の面積が小さくても十分に電荷保持機能を維持でき、相乗的に半導体装置を小型化することができる。

【0320】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

【0321】

（実施の形態7）

本実施の形態では、実施の形態6とは異なる構造を有した、酸化物半導体層を用いたトランジスタ11について説明する。なお、図9と同じ部分は同じ符号を用いて示し、説明は省略する。

【0322】

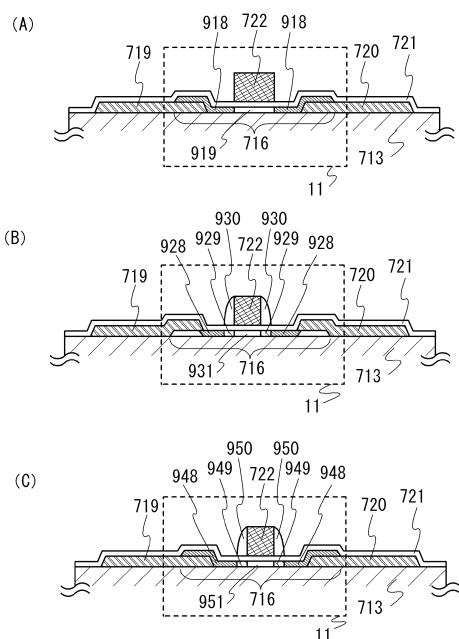

図10（A）に示すトランジスタ11は、ゲート電極722が酸化物半導体層716の上に形成されているトップゲート型であり、なおかつ、ソース電極及びドレイン電極（導電層719及び導電層720）が酸化物半導体層716の下に形成されているボトムコンタクト型である。

【0323】

また、酸化物半導体層716は、ゲート電極722が形成された後に酸化物半導体層716にn型の導電性を付与するドーパントを添加することで得られる、一対の高濃度領域918を有する。また、酸化物半導体層716のうち、ゲート絶縁膜721を間に挟んでゲート電極722と重なる領域がチャネル形成領域919である。酸化物半導体層716では、一対の高濃度領域918の間にチャネル形成領域919が設けられている。

【0324】

高濃度領域918は、実施の形態6において説明した高濃度領域908と同様に形成することができる。

【0325】

図10（B）に示すトランジスタ11は、ゲート電極722が酸化物半導体層716の上に形成されているトップゲート型であり、なおかつ、ソース電極及びドレイン電極（導電層719及び導電層720）が酸化物半導体層716の上に形成されているトップコンタクト型である。そして、ゲート電極722の側部に設けられた、絶縁膜で形成されたサイドウォール930を有する。

【0326】

また、酸化物半導体層716は、ゲート電極722が形成された後に酸化物半導体層716にn型の導電性を付与するドーパントを添加することで得られる、一対の高濃度領域928と、一対の低濃度領域929とを有する。また、酸化物半導体層716のうち、ゲート絶縁膜721を間に挟んでゲート電極722と重なる領域がチャネル形成領域931である。酸化物半導体層716では、一対の高濃度領域928の間に一対の低濃度領域929が設けられ、一対の低濃度領域929の間にチャネル形成領域931が設けられている。そして、一対の低濃度領域929は、酸化物半導体層716中の、ゲート絶縁膜72

10

20

30

40

50

1を間に挟んでサイドウォール930と重なる領域に設けられている。

【0327】

高濃度領域928及び低濃度領域929は、実施の形態6において説明した高濃度領域908と同様に形成することができる。

【0328】

図10(C)に示すトランジスタ11は、ゲート電極722が酸化物半導体層716の上に形成されているトップゲート型であり、なおかつ、ソース電極及びドレイン電極(導電層719及び導電層720)が酸化物半導体層716の下に形成されているボトムコンタクト型である。そして、ゲート電極722の側部に設けられた、絶縁膜で形成されたサイドウォール950を有する。

10

【0329】

また、酸化物半導体層716は、ゲート電極722が形成された後に酸化物半導体層716にn型の導電性を付与するドーパントを添加することで得られる、一対の高濃度領域948と、一対の低濃度領域949とを有する。また、酸化物半導体層716のうち、ゲート絶縁膜721を間に挟んでゲート電極722と重なる領域がチャネル形成領域951である。酸化物半導体層716では、一対の高濃度領域948の間に一対の低濃度領域949が設けられ、一対の低濃度領域949の間にチャネル形成領域951が設けられている。そして、一対の低濃度領域949は、酸化物半導体層716中の、ゲート絶縁膜721を間に挟んでサイドウォール950と重なる領域に設けられている。

【0330】

20

高濃度領域948及び低濃度領域949は、実施の形態6において説明した高濃度領域908と同様に形成することができる。

【0331】

なお、酸化物半導体を用いたトランジスタにおいて、ソース領域またはドレイン領域として機能する高濃度領域をセルフアラインプロセスにて作製する方法の一つとして、酸化物半導体層の表面を露出させて、アルゴンプラズマ処理をおこない、酸化物半導体層のプラズマにさらされた領域の抵抗率を低下させる方法が開示されている(S. Jeon et al. "180 nm Gate Length Amorphous InGaZnO Thin Film Transistor for High Density Image Sensor Applications", IEDM Tech. Dig., pp. 504-507, 2010.)。

30

【0332】

しかしながら、上記作製方法では、ゲート絶縁膜を形成した後に、ソース領域またはドレイン領域となるべき部分を露出するべく、ゲート絶縁膜を部分的に除去する必要がある。よって、ゲート絶縁膜が除去される際に、下層の酸化物半導体層も部分的にオーバーエッキングされ、ソース領域またはドレイン領域となるべき部分の膜厚が小さくなってしまう。その結果、ソース領域またはドレイン領域の抵抗が増加し、また、オーバーエッキングによるトランジスタの特性不良が起こりやすくなる。

【0333】

40

トランジスタの微細化を進めるには、加工精度の高いドライエッキング法を採用する必要がある。しかし、上記オーバーエッキングは、酸化物半導体層とゲート絶縁膜の選択比が十分に確保できないドライエッキング法を採用する場合に、顕著に起こりやすい。

【0334】

例えば、酸化物半導体層が十分な厚さであればオーバーエッキングも問題にはならないが、チャネル長を200 nm以下とする場合には、短チャネル効果を防止する上で、チャネル形成領域となる部分の酸化物半導体層の厚さは20 nm以下、好ましくは10 nm以下であることが求められる。そのような薄い酸化物半導体層を扱う場合には、酸化物半導体層のオーバーエッキングは、上述したような、ソース領域またはドレイン領域の抵抗が増加し、トランジスタの特性不良を生じさせるため、好ましくない。

【0335】

50

しかし、本発明の一態様のように、酸化物半導体層へのドーパントの添加を、酸化物半導体層を露出させず、ゲート絶縁膜を残したまま行うことで、酸化物半導体層のオーバーエッチングを防ぎ、酸化物半導体層への過剰なダメージを軽減することができる。また、加えて、酸化物半導体層とゲート絶縁膜の界面も清浄に保たれる。従って、トランジスタの特性及び信頼性を高めることができる。

【0336】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

【0337】

(実施の形態8)

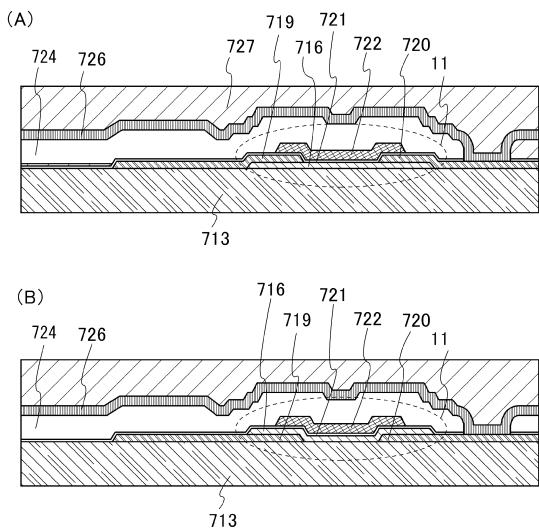

本実施の形態では、実施の形態6や実施の形態7とは異なる構造を有した、酸化物半導体層を用いたトランジスタについて説明する。なお、図9と同じ部分は同じ符号を用いて示し、説明は省略する。本実施の形態において示すトランジスタ11は、ゲート電極722が導電層719及び導電層720と重なる様に設けられている。また、実施の形態6や実施の形態7に示したトランジスタ11とは異なり、酸化物半導体層716に対して、ゲート電極722をマスクとした導電型を付与する不純物元素の添加が行われていない点が異なる。

10

【0338】

図11(A)に示すトランジスタ11は、導電層719及び導電層720の下方に酸化物半導体層716が設けられる例であり、図11(B)に示すトランジスタ11は、導電層719及び導電層720の上方に酸化物半導体層716が設けられる例である。なお、図11(A)及び図11(B)において、絶縁膜724の上面が平坦化されていない構成を示したがこれに限定されない。絶縁膜724の上面が平坦化されていてもよい。

20

【0339】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

【0340】

(実施の形態9)

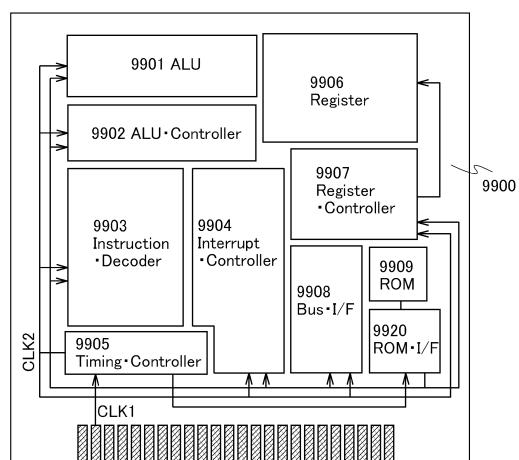

本実施の形態では、本発明の一態様に係る半導体装置の一つである、CPUの構成について説明する。

【0341】

図16に、本実施の形態のCPUの構成を示す。図16に示すCPUは、基板9900上に、ALU9901、ALU・Controller9902、Instruction・Decoder9903、Interrupt・Controller9904、Timing・Controller9905、Register9906、Register・Controller9907、Bus・I/F9908、書き換え可能なROM9909、ROM・I/F9920と、を主に有している。なお、ALUはArithmetic logic unitであり、Bus・I/Fはバスインターフェースであり、ROM・I/FはROMインターフェースである。ROM9909及びROM・I/F9920は、別チップに設けても良い。勿論、図16に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。

30

【0342】

Bus・I/F9908を介してCPUに入力された命令は、Instruction・Decoder9903に入力され、デコードされた後、ALU・Controller9902、Interrupt・Controller9904、Register・Controller9907、Timing・Controller9905に入力される。

40

【0343】

ALU・Controller9902、Interrupt・Controller9904、Register・Controller9907、Timing・Controller9905は、デコードされた命令に基づき、各種制御を行なう。具体的にA

50

LU・Controller9902は、ALU9901の動作を制御するための信号を生成する。また、Interrupt・Controller9904は、CPUのプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。Register・Controller9907は、Register9906のアドレスを生成し、CPUの状態に応じてRegister9906の読み出しや書き込みを行なう。

【0344】

またTiming・Controller9905は、ALU9901、ALU・Controller9902、Instruction・Decoder9903、Interrupt・Controller9904、Register・Controller9907の動作のタイミングを制御する信号を生成する。例えばTiming・Controller9905は、基準クロック信号CLK1を元に、内部クロック信号CLK2を生成する内部クロック生成部を備えており、クロック信号CLK2を上記各種回路に入力する。

10

【0345】

本実施の形態のCPUでは、ALU9901、ALU・Controller9902、Instruction・Decoder9903、Interrupt・Controller9904、Timing・Controller9905、Register9906、Register・Controller9907、Bus・I/F9908、書き換え可能なROM9909、ROM・I/F9920の少なくともいずれかの入力部、出力部又は入出力部に上記実施の形態で示した構成を有する半導体装置を設けることができる。例えば、Register9906に上記実施の形態で示した構成を有する半導体装置を設ける場合、Register・Controller9907は、ALU9901からの指示に従い、Register9906が有する半導体装置において、リーク電流を抑制したハイインピーダンス状態を維持することができる。その結果、消費電力を低減できる。

20

【0346】

この様にして、一時的にCPUの動作を停止し、電源電圧の供給を酸化物半導体を用いたトランジスタによって停止することによりリーク電流を防止でき、消費電力の低減を行うことができる。

30

【0347】

本実施の形態では、CPUを例に挙げて説明したが、開示する発明の一態様に係る半導体装置はCPUに限定されず、マイクロプロセッサ、画像処理回路、DSP(Digital Signal Processor)、FPGA(Field Programmable Gate Array)等のLSIにも応用可能である。

【0348】

また、開示する発明の一態様に係る半導体装置が有する、酸化物半導体を用いたトランジスタによって、不揮発性のランダムアクセスメモリを実現することも可能である。

【0349】

ところで、不揮発性のランダムアクセスメモリとして磁気トンネル接合素子(MTJ素子)が知られている。MTJ素子は、絶縁膜を介して上下に配置している膜中のスピンの向きが平行であれば低抵抗状態、反平行であれば高抵抗状態となることで情報を記憶する素子である。したがって、本実施の形態で示す酸化物半導体を用いたメモリとは原理が全く異なっている。表1にMTJ素子と、本実施の形態に係る半導体装置との対比を示す。

40

【0350】

【表1】

|                  | スピントロニクス(MTJ 素子)                                                        | OS/Si                                        |

|------------------|-------------------------------------------------------------------------|----------------------------------------------|

| 1) 耐熱性           | キュリー温度                                                                  | プロセス温度500°C<br>(信頼性150°C)                    |

| 2) 駆動方式          | 電流駆動                                                                    | 電圧駆動                                         |

| 3) 書き込み原理        | 磁性体の спинの向きを変える                                                        | FET のオン／オフ                                   |

| 4) Si LSI        | バイポーラ LSI 向き<br>(バイポーラは高集積化には不向きなため、高集積化回路では MOS の方が好ましい。ただし、W が大きくなる。) | MOSLSI 向き                                    |

| 5) オーバーヘッド       | 大きい<br>(ジュール熱が大きいため)                                                    | 2~3桁以上小さい<br>(寄生容量の充放電)                      |

| 6) 不揮発性          | スピンを利用                                                                  | オフ電流が小さいことを利用                                |

| 7) 読み出し回数        | 無制限                                                                     | 無制限                                          |

| 8) 3D 化          | 難(できても二層まで)                                                             | 容易(何層でも可)                                    |

| 9) 集積化度( $F^2$ ) | $4F^2 \sim 15F^2$                                                       | 3D 化の積層数で決まる<br>(上層 OSFET 工程のプロセス耐熱性の確保が必要)  |

| 10) 材料           | 磁性を有する希土類                                                               | OS 材料                                        |

| 11) ビットコスト       | 高い                                                                      | 低い<br>(OS を構成する材料によっては (In など)、多少コスト高の可能性有り) |

| 12) 磁界耐性         | 弱い                                                                      | 強い                                           |

10

20

30

## 【0351】

MTJ 素子は磁性材料を使用するためキュリー温度以上にすると磁性が失われてしまうという欠点がある。また、MTJ 素子は電流駆動であるため、シリコンのバイポーラデバイスと相性が良いが、バイポーラデバイスは集積化に不向きである。そして、MTJ 素子は書き込み電流が微少とはいえメモリの大容量化によって消費電力が増大してしまうといった問題がある。

## 【0352】

原理的にMTJ 素子は磁界耐性に弱く強磁界にさらされるとスピノの向きが狂いやすい。また、MTJ 素子に用いる磁性体のナノスケール化によって生じる磁化揺らぎを制御する必要がある。

## 【0353】

さらに、MTJ 素子は希土類元素を使用するため、金属汚染を嫌うシリコン半導体のプロセスに組み入れるには相当の注意を要する。MTJ 素子はビット当たりの材料コストから見ても高価であると考えられる。

## 【0354】

一方、本実施形態で示す酸化物半導体を用いたトランジスタは、チャネルを形成する半導体材料が金属酸化物であること以外は、素子構造や動作原理がシリコン MOSFET と同様である。また、酸化物半導体を用いたトランジスタは磁界の影響を受けず、ソフトエラーも生じ得ないといった特質を有する。このことからシリコン集積回路と非常に整合性が良いといえる。

## 【0355】

その他、酸化物半導体を用いたトランジスタとシリコンを用いたトランジスタを組み合

40

50

わせるメモリは、表1に示したように、スピントロニクスデバイスに比べて、耐熱性、3D化（3層以上の積層構造化）、磁界耐性など多くの点で有利である。

【0356】

なお、オーバーヘッドとはデータの待避及び復帰により消費される電力のことをいう。

【0357】

このように、スピントロニクスデバイスに比べて有利な点の多い酸化物半導体を用いたメモリを利用することで、CPUの省電力化が実現可能となる。

【0358】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

【0359】

（実施の形態10）

本発明の一態様に係る半導体装置を利用することで、リーク電流を抑制した消費電力の低い電子機器を提供することが可能である。特に電力の供給を常時受けることが困難な携帯用の電子機器の場合、本発明の一態様に係る消費電力の低い半導体装置をその構成要素に追加することにより、連続使用時間が長くなるといったメリットが得られる。

【0360】

本発明の一態様に係る半導体装置は、表示装置、パーソナルコンピュータ、記録媒体を備えた画像再生装置（代表的にはDVD：Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置）に用いることができる。その他に、本発明の一態様に係る半導体装置を用いることができる電子機器として、携帯電話、携帯型を含むゲーム機、携帯情報端末、電子書籍、ビデオカメラ、デジタルスチルカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、デジタルオーディオプレイヤー等）、複写機、ファクシミリ、プリンター、プリンター複合機、現金自動預け入れ払い機（ATM）、自動販売機などが挙げられる。

【0361】

本発明の一態様に係る半導体装置を、携帯電話、スマートフォン、電子書籍などの携帯用の電子機器に応用した場合について説明する。

【0362】

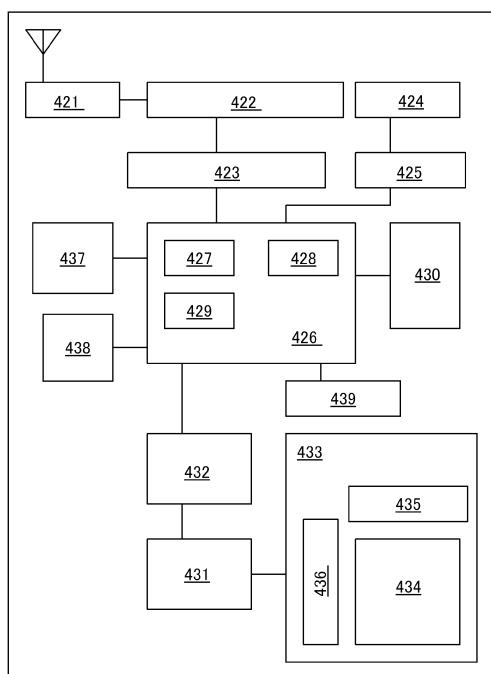

図17は、携帯用の電子機器のブロック図である。図17に示す携帯用の電子機器はRF回路421、アナログベースバンド回路422、デジタルベースバンド回路423、バッテリー424、電源回路425、アプリケーションプロセッサ426、フラッシュメモリ430、ディスプレイコントローラ431、メモリ回路432、ディスプレイ433、タッチセンサ439、音声回路437、キーボード438などより構成されている。ディスプレイ433は表示部434、ソースドライバ435、ゲートドライバ436によって構成されている。アプリケーションプロセッサ426はCPU427、DSP428、インターフェース429を有している。例えば、CPU427、デジタルベースバンド回路423、メモリ回路432、DSP428、インターフェース429、ディスプレイコントローラ431、音声回路437のいずれかまたは全てに上記実施の形態で示した半導体装置を採用することによって、リーク電流を抑制し、消費電力を低減することができる。

【0363】

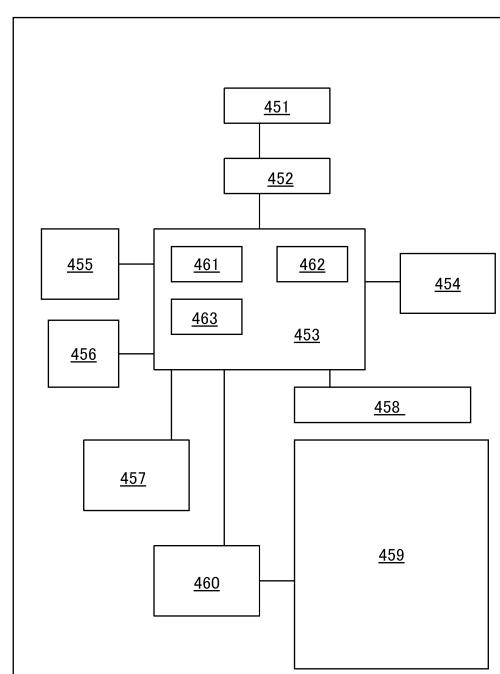

図18は電子書籍のブロック図である。電子書籍はバッテリー451、電源回路452、マイクロプロセッサ453、フラッシュメモリ454、音声回路455、キーボード456、メモリ回路457、タッチパネル458、ディスプレイ459、ディスプレイコントローラ460によって構成される。マイクロプロセッサ453はCPU461、DSP462、インターフェース463を有している。例えば、CPU461、音声回路455、メモリ回路457、ディスプレイコントローラ460、DSP462、インターフェース463のいずれかまたは全てに上記実施の形態で示した半導体装置を採用することで、リーク電流を抑制し、消費電力を低減することができる。

【0364】

10

20

30

40

50

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

【0365】

(実施の形態11)

酸化物半導体に限らず、実際に測定される絶縁ゲート型トランジスタの電界効果移動度は、さまざまな理由によって本来の移動度よりも低くなる。

【0366】

移動度を低下させる要因としては半導体内部の欠陥や半導体と絶縁膜との界面の欠陥があるが、Levinsonモデルを用いると、半導体内部に欠陥がないと仮定した場合の電界効果移動度を理論的に導き出せる。

【0367】

半導体本来の移動度を $\mu_0$ 、測定される電界効果移動度を $\mu$ とし、半導体中に何らかのポテンシャル障壁(粒界等)が存在すると仮定すると、図27(A)の式Aで表される。

【0368】

$E$ はポテンシャル障壁の高さであり、 $k$ がボルツマン定数、 $T$ は絶対温度である。

【0369】

また、ポテンシャル障壁が欠陥に由来すると仮定すると、Levinsonモデルでは、図27(B)の式Bで表される。

【0370】

$e$ は電気素量、 $N$ はチャネル内の単位面積当たりの平均欠陥密度、 $\alpha$ は半導体の誘電率、 $n$ は単位面積当たりのチャネルに含まれるキャリア数、 $C_{ox}$ は単位面積当たりの容量、 $V_g$ はゲート電圧、 $t$ はチャネルの厚さである。

【0371】

なお、厚さ30nm以下の半導体層であれば、チャネルの厚さは半導体層の厚さと同一として差し支えない。

【0372】

線形領域におけるドレイン電流 $I_d$ は、図27(C)の式Cで表される。

【0373】

ここで、 $L$ はチャネル長、 $W$ はチャネル幅であり、ここでは、 $L = W = 10 \mu m$ である。

【0374】

また、 $V_d$ はドレイン電圧である。

【0375】

式Cの両辺を $V_g$ で割り、更に両辺の対数を取ると、図27(D)の式Dで表される。

【0376】

式Cの右辺は $V_g$ の関数である。

【0377】

上式のからわかるように、縦軸を $\ln(I_d/V_g)$ 、横軸を $1/V_g$ として実測値をプロットして得られるグラフの直線の傾きから欠陥密度 $N$ が求められる。

【0378】

すなわち、トランジスタの $I_d - V_g$ 特性から、欠陥密度を評価できる。

【0379】

酸化物半導体としては、インジウム(Indium)、スズ(Silver)、亜鉛(Zinc)の比率が、 $I_n : S_n : Z_n = 1 : 1 : 1$ のものでは欠陥密度 $N$ は $1 \times 10^{12} / cm^2$ 程度である。

【0380】

このようにして求めた欠陥密度等をもとに $\mu_0 = 120 cm^2 / Vs$ が導出される。

【0381】

欠陥のある $I_n - S_n - Z_n$ 酸化物で測定される移動度は $35 cm^2 / Vs$ 程度である。

【0382】

10

20

30

40

50

しかし、半導体内部および半導体と絶縁膜との界面の欠陥が無い酸化物半導体の移動度  $\mu_0$  は  $120 \text{ cm}^2 / \text{Vs}$  となると予想できる。

【0383】

ただし、半導体内部に欠陥がなくても、チャネルとゲート絶縁膜との界面での散乱によってトランジスタの輸送特性は影響を受ける。すなわち、ゲート絶縁膜界面から  $x$  だけ離れた場所における移動度  $\mu_1$  は、図27(E)の式Eで表される。

【0384】

Dはゲート方向の電界、B、Gは定数である。BおよびGは、実際の測定結果より求めることができ、上記の測定結果からは、 $B = 4.75 \times 10^7 \text{ cm/s}$ 、 $G = 10 \text{ nm}$ （界面散乱が及ぶ深さ）である。

10

【0385】

Dが増加する（すなわち、ゲート電圧が高くなる）と式Eの第2項が増加するため、移動度  $\mu_1$  は低下することがわかる。

【0386】

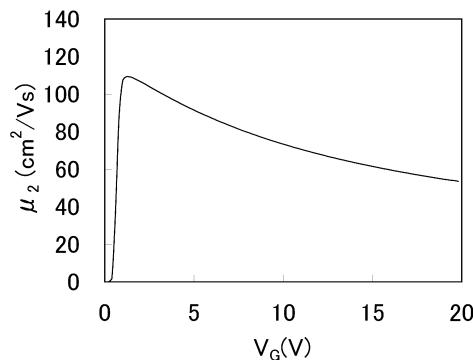

半導体内部の欠陥が無い理想的な酸化物半導体をチャネルに用いたトランジスタの移動度  $\mu_2$  の計算結果Eを図19に示す。

【0387】

なお、計算にはシノプシス社製のソフトである S e n t a u r u s D e v i c e を使用した。

20

【0388】

計算において、酸化物半導体のバンドギャップ、電子親和力、比誘電率、厚さをそれぞれ、 $2.8$  電子ボルト、 $4.7$  電子ボルト、 $15$ 、 $15 \text{ nm}$ とした。

【0389】

これらの値は、スパッタリング法により形成された薄膜を測定して得られたものである。

【0390】

さらに、ゲート、ソース、ドレインの仕事関数をそれぞれ、 $5.5$  電子ボルト、 $4.6$  電子ボルト、 $4.6$  電子ボルトとした。

【0391】

また、ゲート絶縁膜の厚さは  $100 \text{ nm}$ 、比誘電率は  $4.1$  とした。チャネル長およびチャネル幅はともに  $10 \mu\text{m}$ 、ドレイン電圧  $V_d$  は  $0.1 \text{ V}$  である。

30

【0392】

計算結果Eで示されるように、ゲート電圧  $1 \text{ V}$  強で移動度  $100 \text{ cm}^2 / \text{Vs}$  以上のピークをつけるが、ゲート電圧がさらに高くなると、界面散乱が大きくなり、移動度が低下する。

【0393】

なお、界面散乱を低減するためには、半導体層表面を原子レベルで平坦にすること（A t o m i c L a y e r F l a t n e s s）が望ましい。

【0394】

このような移動度を有する酸化物半導体を用いて微細なトランジスタを作製した場合の特性を計算した。

40

【0395】

なお、計算に用いたトランジスタは酸化物半導体層に一対のn型半導体領域にチャネル形成領域が挟まれたものを用いた。

【0396】

一対のn型半導体領域の抵抗率は  $2 \times 10^{-3} \text{ cm}$  として計算した。

【0397】

また、チャネル長を  $33 \text{ nm}$ 、チャネル幅を  $40 \text{ nm}$  として計算した。

【0398】

また、ゲート電極の側壁にサイドウォールを有する。

50

## 【0399】

サイドウォールと重なる半導体領域をオフセット領域として計算した。

## 【0400】

計算にはシノプシス社製のソフト、S e n t a u r u s D e v i c e を使用した。

## 【0401】

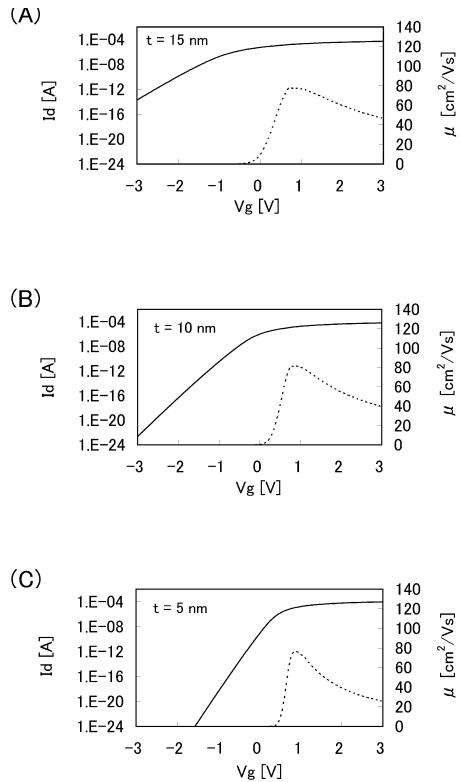

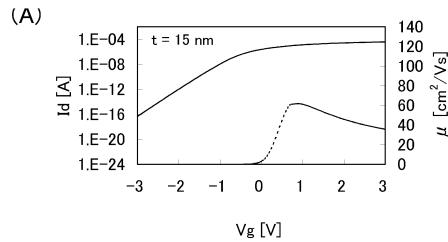

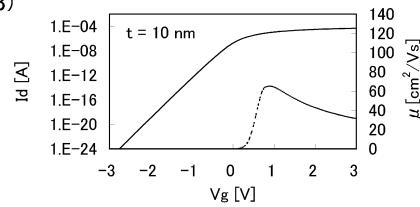

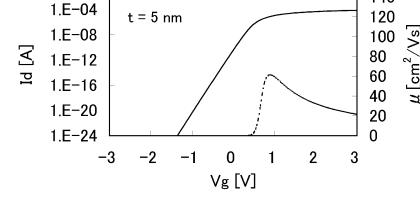

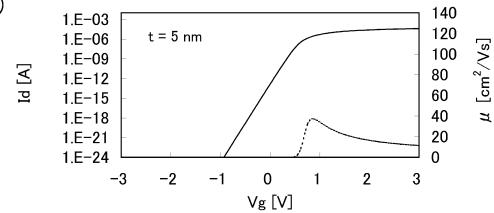

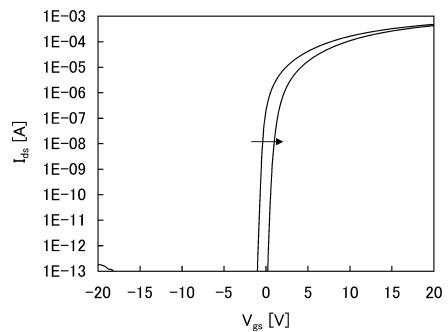

図20は、トランジスタのドレイン電流 ( $I_d$ 、実線) および移動度 ( $\mu$ 、点線) のゲート電圧 ( $V_g$ 、ゲートとソースの電位差) 依存性の計算結果である。

## 【0402】

ドレイン電流  $I_d$  は、ドレイン電圧 (ドレインとソースの電位差) を +1 V とし、移動度  $\mu$  はドレイン電圧を +0.1 V として計算したものである。

10

## 【0403】

図20(A)はゲート絶縁膜の厚さを 15 nm として計算したものである。

## 【0404】

図20(B)はゲート絶縁膜の厚さを 10 nm と計算したものである。

## 【0405】

図20(C)はゲート絶縁膜の厚さを 5 nm と計算したものである。

## 【0406】

ゲート絶縁膜が薄くなるほど、特にオフ状態でのドレイン電流  $I_d$  (オフ電流) が顕著に低下する。

## 【0407】

一方、移動度  $\mu$  のピーク値やオン状態でのドレイン電流  $I_d$  (オン電流) には目立った変化が無い。

20

## 【0408】

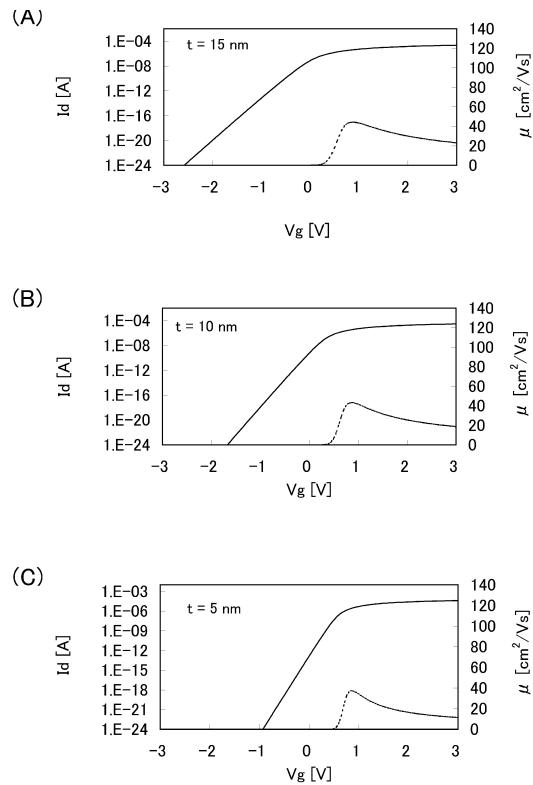

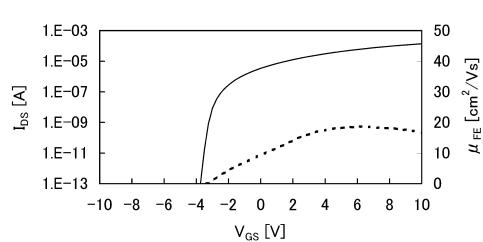

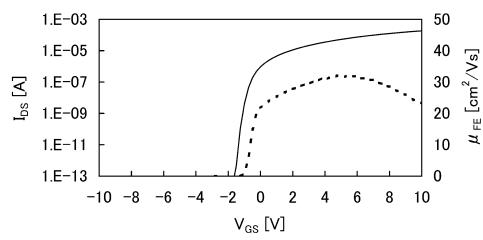

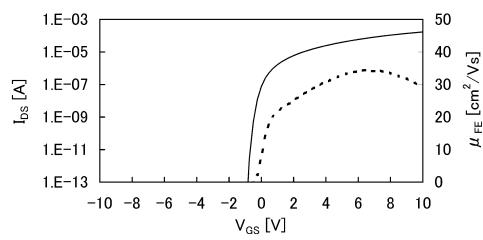

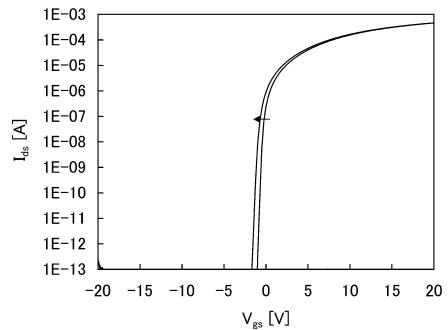

図21は、オフセット長 (サイドウォール長)  $L_{o f f}$  を 5 nm としたもののドレイン電流  $I_d$  (実線) および移動度  $\mu$  (点線) のゲート電圧  $V_g$  依存性を示す。

## 【0409】

ドレイン電流  $I_d$  は、ドレイン電圧を +1 V とし、移動度  $\mu$  はドレイン電圧を +0.1 V として計算したものである。

## 【0410】

図21(A)はゲート絶縁膜の厚さを 15 nm として計算したものである。

30

## 【0411】

図21(B)はゲート絶縁膜の厚さを 10 nm と計算したものである。

## 【0412】

図21(C)はゲート絶縁膜の厚さを 5 nm と計算したものである。