(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5172330号

(P5172330)

(45) 発行日 平成25年3月27日(2013.3.27)

(24) 登録日 平成25年1月11日(2013.1.11)

(51) Int.Cl.

F 1

H01L 29/861 (2006.01)

H01L 29/91

C

H01L 29/868 (2006.01)

H01L 29/91

A

H01L 21/329 (2006.01)

請求項の数 6 (全 9 頁)

(21) 出願番号 特願2007-510745 (P2007-510745)

(86) (22) 出願日 平成17年4月6日 (2005.4.6)

(65) 公表番号 特表2007-535812 (P2007-535812A)

(43) 公表日 平成19年12月6日 (2007.12.6)

(86) 國際出願番号 PCT/US2005/011276

(87) 國際公開番号 WO2005/111817

(87) 國際公開日 平成17年11月24日 (2005.11.24)

審査請求日 平成20年4月4日 (2008.4.4)

(31) 優先権主張番号 10/836,170

(32) 優先日 平成16年4月30日 (2004.4.30)

(33) 優先権主張国 米国(US)

(73) 特許権者 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 テキサス州 78735

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100140109

弁理士 小野 新次郎

(74) 代理人 100075270

弁理士 小林 泰

(74) 代理人 100080137

弁理士 千葉 昭男

(74) 代理人 100096013

弁理士 富田 博行

最終頁に続く

(54) 【発明の名称】半導体デバイスおよびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の伝導タイプの基板と、

前記第1の伝導タイプのアノードとを有し、

前記アノードが、

前記基板上に横たわるエピタキシャル層からなる低ドーパント濃度の第2の部分と、

前記エピタキシャル層に形成された高ドーパント濃度の第1の部分と、

前記エピタキシャル層に形成された中間のドーパント濃度の第3の部分と、

前記第1の部分に形成され第1の部分よりもドーパント濃度が高いオーミック

接触を作る領域とからなり、

前記エピタキシャル層に形成された前記第1の伝導タイプとは異なる第2の伝導タイプのカソードとを有し、

前記第3の部分はカソードと隣接して配設され、アノード/カソード接合インターフェースを形成し、

前記第2の伝導タイプの伝導絶縁機構とを有し、

前記伝導絶縁機構が、埋設層と、前記埋設層と電気的に結合する伝導垂直部分と含み、

前記埋設層が、前記基板と前記エピタキシャル層との間に配置されるとともに、前記第3の部分と隣接して配置され、

前記伝導垂直部分が、前記アノード及びカソードの領域の側面から前記アノード及びカソードの領域を取り囲み、

10

20

前記伝導絶縁機構が、前記基板との接合を形成し、前記伝導絶縁機構が、前記カソード、前記第3の部分、前記埋設層から構成される垂直NPN、および、前記第3の部分、前記埋設層、前記基板から構成される垂直PNP領域によって形成される寄生トランジスタから生じる前記基板内に注入される寄生電流の量を低減させるように電気的にバイアスをかけられ、

前記オーム接触を作る領域と、前記伝導絶縁機構の伝導垂直部分の頂部との間の前記エピタキシャル層中に配置された誘電絶縁領域と、

を有することを特徴とする半導体デバイス。

**【請求項2】**

前記伝導垂直部分が、前記領域の表面から、埋設層まで下がるように延びる、ことを特徴とする請求項1に記載の半導体デバイス。 10

**【請求項3】**

前記伝導垂直部分の幅が、垂直NPN及び垂直PNP領域によって形成される寄生トランジスタから生じる基板内に注入される寄生電流の量を制御することを特徴とする、請求項2に記載の半導体デバイス。

**【請求項4】**

伝導垂直部分が、基板の寄生電流を実質的に除去するように選択されたことを特徴とする請求項3に記載の半導体デバイス。

**【請求項5】**

前記伝導絶縁機構が、前記アノードと前記カソードの一方に電気的に接続されたことを特徴とする請求項4に記載の半導体デバイス。 20

**【請求項6】**

複数のドーパント濃度が、高ドーパント濃度、低ドーパント濃度、及び、中間のドーパント濃度の別々の部分を含み、

前記高ドーパント濃度が、 $2 \times 10^{17}$ 乃至 $5 \times 10^{17}$ のオーダーであり、前記低ドーパント濃度が、 $1 \times 10^{15}$ 乃至 $5 \times 10^{15}$ のオーダーであり、前記中間のドーパント濃度が、 $2 \times 10^{16}$ 乃至 $5 \times 10^{16}$ のオーダーであることを特徴とする請求項5に記載の半導体デバイス。

**【発明の詳細な説明】**

**【技術分野】**

30

**【0001】**

本発明は全体的に半導体に関し、特に、半導体デバイスおよびその製造方法に関する。

**【背景技術】**

**【0002】**

集積回路に関し、その半導体基板内に半導体デバイスによって注入される電流を制限することはしばしば重要である。これは、より高い電圧および電流で作動するパワー集積回路では特に重要である。また、パワー集積回路で使用される最大電圧を増大させることが望まれる。

**【発明の開示】**

**【課題を解決するための手段】**

40

**【0003】**

本発明のある実施形態の半導体デバイスは、第1の伝導タイプの基板と、前記第1の伝導タイプのアノードとを有し、該アノードが複数のドーパント濃度を含み、第1の部分のドーパント濃度が、第2の部分のドーパント濃度よりも高いオーダーの大きさであり、第1の部分又は第2の部分のいずれもが、オーム接触を作るよう用いられ、前記第1の伝導タイプとは異なる第2の伝導タイプのカソードとを有し、アノードは、カソードと隣接して配設され、アノード/カソード接合インターフェースを形成し、前記第2の伝導タイプの伝導絶縁機構とを有し、前記伝導絶縁機構が、埋設層と、前記埋設層と電気的に結合する伝導垂直部分と含み、前記埋設層が、気マント、アノード及びカソードの領域との間に配置され、前記伝導垂直部分が、前記アノード及びカソードの領域の側面から前記

50

アノード及びカソードの領域を取り囲み、アノードの頂部と、前記伝導絶縁機構の伝導垂直部分の頂部との間の半導体デバイスの一部の中に配置された誘電絶縁領域と、を有することを特徴とする。

【0004】

本発明の他の実施形態では、前記基板が、P型基板を含み、前記P型基板が、基板の上に横たわるP型エピタキシャル層を含み、前記第1の伝導タイプが、P型を含み、前記第2の伝導タイプが、N型を含むことを特徴とする。

【0005】

更に、複数のドーパント濃度が、高ドーパント濃度、低ドーパント濃度、及び、中間のドーパント濃度の別々の部分を含み、前記高ドーパント濃度が、 $2 \times 10^{17}$ 乃至 $5 \times 10^{17}$ のオーダーであり、前記低ドーパント濃度が、 $1 \times 10^{15}$ 乃至 $5 \times 10^{15}$ のオーダーであり、前記中間のドーパント濃度が、 $2 \times 10^{16}$ 乃至 $5 \times 10^{16}$ のオーダーであり、カソードが、 $3 \times 10^{16}$ 乃至 $6 \times 10^{16}$ のオーダーのドーパント濃度を有することを特徴とする。

10

【0006】

また、前記伝導垂直部分が、前記領域の表面から、埋設層まで下がるように延び、前記伝導垂直部分の幅が、垂直NPN及び垂直PNP領域によって形成される寄生トランジスタから生じる基板内に注入される寄生電流の量を制御し、伝導垂直部分が、基板の寄生電流を実質的に除去するように選択し、前記埋設層が、N+埋設層を含み、前記伝導垂直部分がN+伝導シンカーを含むことを特徴とする。

20

【0007】

また、前記伝導絶縁機構が、前記アノードに電気的に接続されたことを特徴とし、前記伝導絶縁機構が、前記カソードに電気的に接続され、前記伝導絶縁機構が、電気的に浮遊し、アノード/カソード接合にわたる部分を少なくとも含む前記アノードとカソードとの間の領域の上に横たわる誘電体と、前記誘電体の上に横たわる伝導層とを更に有し、前記伝導層が前記アノードと電気的に接続され、伝導絶縁機構が、前記アノードと電気的に接続され、前記誘電体が、酸化物からなることを特徴とし、前記伝導層がポリシリコンからなることを特徴とする。

【0008】

また、前記半導体デバイスが、高電圧及び高電流で作動可能なパワー集積回路内に組み込まれることを特徴とする。

30

更に、前記カソードがオーミック領域と、前記オーミック領域だけの垂直側面のまわりに前記オーミック領域を取り囲む誘電絶縁領域とを含み、前記オーミック領域と誘電絶縁領域とが、前記カソードの頂部部分に配置され、更に、前記オーミック領域が、オーミック接触のために適当なヘビードープ領域を有し、前記アノードが、前記アノードの頂部部分に配置されたオーミック領域を更に含み、前記オーミック領域が、オーミック接触のために適当なヘビードープ領域を有し、前記伝導絶縁機構の側面から前記伝導絶縁機構を取り囲むトレンチ誘電絶縁領域を更に有し、前記トレンチ誘電絶縁領域が、前記基板内に下がるように前記伝導絶縁機構の表面から延びることを特徴とする。

40

【0009】

本発明のある実施形態の半導体デバイスを形成する方法は、第1の伝導タイプの基板を用意するステップと、第2の伝導タイプの埋設層を埋め込むステップと、を有し、前記埋設層が伝導絶縁機構の一部を形成し、前記埋設層の上に横たわる前記第1の伝導タイプのエピタキシャル層を堆積させるステップと、を有し、前記エピタキシャル層の一部がアノードの第1の部分を形成し、前記第1の伝導タイプ及び前記第2の伝導タイプをそれぞれ備えた第1及び第2の領域を注入するステップと、を有し、前記第1の領域が前記アノードの第1の部分に対応し、前記第2の領域がカソードの第1の部分に対応し、酸化絶縁体のための領域をエッチングし、エッチングされた領域内に酸化物を堆積させるステップと、前記第1の伝導タイプに第3の領域を注入するステップとを有し、前記第3の領域が、前記アノードの第3の部分に対応し、前記第2の伝導タイプに第4の領域を注入するステ

50

ップとを有し、前記第4の領域が、前記伝導絶縁機構の第2の部分を形成することを特徴とする。

【0010】

また、前記アノードが、複数のドーパント濃度を含み、ある部分のドーパント濃度が、他の部分のドーパント濃度よりも高い大きさのオーダーであり、いずれの部分もオーミック接触を作るのに使用されないことを特徴とし、前記アノードが前記カソードに隣接して配置され、アノード／カソード接合インターフェースを形成し、前記伝導絶縁機構が前記埋設層に電気的に接続された伝導シンカーと埋設層とを含み、前記埋設層が基板とアノード及びカソードの領域との間に配置され、前記伝導シンカーがアノード及びカソードの領域の側面からアノード及びカソードの領域を取り囲むことを特徴とする。

10

【0011】

更に、前記伝導絶縁機構の第2の部分が、伝導シンカーを含み、前記伝導シンカーが前記第2の部分の表面から前記埋設層の下に延び、酸化絶縁物のための領域をエッチングし、前記エッチングされた領域内に酸化物を堆積し、アノードの頂部と前記伝導絶縁機構の前記伝導シンカーの頂部との間の半導体デバイスの一部に堆積された誘電絶縁領域を形成することを含むことを特徴とする。

【発明を実施するための最良の形態】

【0012】

本発明を例示によって図示するが、添付の図によって限定されるものではない。また同様の参照番号は同じエレメントを示す。

20

図におけるエレメントは簡略化されており、正確なスケールで図示されていないことは、当業者には理解されるであろう。例えば、図におけるいくつかのエレメントの寸法は、本発明の実施形態の理解の向上を助けるために、他のエレメントに対して誇張されている。

【0013】

同じチップ上にアナログ及びCMOS (complementary metal-oxide-semiconductor) に沿ってパワーデバイスを集積するためのSMARTMOS技術の急速な発展は、システム・オン・チップ・ソリューションに関する機会を生み出す。自動車、ポータブル、及び、コンピュータ周辺アプリケーションにおけるパワー管理は、数十ボルトの高電圧までの全ての方法で、低いバッテリー電圧から動作を可能にする多用途のスマートパワー技術に関する必要性を駆動する。しかしながら、ダイオードのような在来の半導体デバイスのいくつかは、所定の状況において寄生基板注入の問題から被害をこうむる。基板注入を抑圧する目的のためにスマートパワー技術内に、ダイオードデバイスを絶縁する高電圧を注入することは、新しい構造及び製造方法を要求する。

30

【0014】

図1は、本発明のある実施形態による半導体デバイスの断面図を図示する。図1で用いられている、「P-、P、P+及びP++」は、P型伝導を備えた半導体材料を現し、ドーパント濃度は、最も低いドーパント濃度P-から、より高いドーパント濃度P、次いで、さらに高いドーパント濃度P+、及び最も高いドーパント濃度P++まで変化する。同様に、「N、N+及びN++」は、N型伝導を備えた半導体材料を現し、ドーパント濃度は、最も低いドーパント濃度Nから、より高いドーパント濃度N+、及び最も高いドーパント濃度N+まで変化する。

40

【0015】

図1に示した本発明の実施形態では、半導体デバイス10はダイオードであり、アノード42はP++領域30、P+領域20、P-領域24及びP領域26から形成され、カソード40は、N++領域32及びN領域22から形成される。P領域12は、半導体基板であり、N+領域13は、埋設された層であり、又は、別の実施形態では、何らかの仕方で形成されたN+層であってよい。N+領域16は、伝導シンカーとして実装されうる。N+層13と共同してN+領域16は、集積回路の残りからダイオード10を伝導的に絶縁するために使用され得る絶縁特性又は絶縁タブを形成する。誘電層14は、ダイオード10を

50

取り囲むように使用されうる。誘電層 14 は、集積回路の残りからダイオード 10 を絶縁するように使用されうる絶縁バリアを形成する。誘電層 14 は、いかなる誘電材料から形成されても良い。酸化物は、使用されうるたった一つの誘電材料に過ぎない。例えば、酸化物とポリシリコンとの組み合わせのような、他のいかなる適切な材料を使用することができ得る。

#### 【 0 0 1 6 】

アノード 42 は、P++領域 30 を含み、カソード 40 は、N++領域 32 を含み、絶縁領域 16 は、N++領域 34 を含む。これらの領域 30, 32 及び 34 は、良好なオーミック接触するために全て多量にドープされ、かくして、ここをオーミック領域と呼ぶこともある。本発明のいくつかの実施形態では、金属接触（図示せず）は、領域 30, 32 及び 34 のそれぞれの上に横たわるように形成されうる。

#### 【 0 0 1 7 】

本発明の図示した実施形態では、誘電層 27 は、アノード 42 とカソード 40 との間の接合の上に横たわるように形成される。誘電層 27 は、いかなる誘電材料から形成されても良いことに注意すべきである。ある実施形態では、薄い酸化物層は、誘電層 27 を形成するのに用いられる。伝導層 28 は、誘電層 27 の上に横たわるように形成される。伝導層 28 は、いかなる伝導、又は、半導材料から形成されても良いことに注意すべきである。ある実施形態では、ポリシリコン層が、伝導層 28 を形成するのに用いられる。誘電層 27 及び伝導層 28 の各々は、複数の層を使用して形成されうることに注意すべきである。

10

20

#### 【 0 0 1 8 】

本発明の図示した実施形態では、誘電層 19 が、アノード 42 とN+領域 16 との間に形成される。誘電層 19 は、いかなる誘電材料から形成されても良いことに注意すべきである。

ある実施形態では、電界酸化膜層（field oxide layer）が、誘電層 19 を形成するのに用いられる。酸化物は、使用されうる可能性のある一例としての誘電材料に過ぎない。他の如何なる適当な誘電材料をも使用することができ得る。

#### 【 0 0 1 9 】

本発明の図示した実施形態では、誘電層 18 は、N++領域 32 を取り囲むリングとして形成される。誘電層 18 が、いかなる誘電材料から形成されても良いことに注意すべきである。ある実施形態では、電界酸化膜層（field oxide layer）が、誘電層 18 を形成するのに用いられる。酸化物は、使用されうる可能性のある一例としての誘電材料に過ぎない。他の如何なる適当な誘電材料をも使用することができ得る。ある実施形態では、誘電層 18 は、浅いトレンチ絶縁領域であってよい。誘電層の目的の 1 つは、N++領域 32 と、伝導層又は伝導プレート 28 との間の高い電位差をサポートすることである。本発明の他の実施形態では、誘電層 18 は用いられず、代わりに表面平面まで他の領域が延びることができうる（即ち、表面平面が、層 27 の底部表面と近接する）。

30

#### 【 0 0 2 0 】

本発明のある実施形態では、アノード 42 は、伝導層 44 の道によって伝導層 28 と電気的に結合される。伝導層 44 は、所望のトポロジーを用いることができ、簡潔にするために特定のトポロジーでは図示されていない。誘電層 44 は、半導体デバイス 10 の上に形成されるができるいかなる伝導材料を使用して形成されうる。

40

#### 【 0 0 2 1 】

本発明の別の実施形態では、垂直寄生NPN及びPNPデバイスから基板 12 内に注入された寄生電流を低減させるために、N++領域 34、N+領域 16 及びN+領域 13 によって形成されたN絶縁領域に電気的にバイアスをかけ得る。図示された実施形態では、垂直寄生NPNトランジスタは、領域 32 及び 22 から形成された第 1 のN領域を有し、領域 30, 20, 24 及び 26 から形成されたP領域を有し、領域 13 から形成された第 2 のN領域を有することに注意すべきである。同様に、垂直寄生PNPトランジスタは、領域 30, 20, 24 及び 26 から形成された第 1 のP領域を有し、領域 13 から形成された

50

N領域を有し、領域12から形成された第2のP領域を有する。

【0022】

N++領域34がアノード42に電気的に結合されている（即ち、ショートしている）ならば、垂直寄生PNPトランジスタのベース及びエミッタは、おおよそ同じ電圧であり、かくして、エミッタ／ベース・バイアスは存在しない。従って、垂直寄生PNPトランジスタは、P基板12内に注入される非常に小さなコレクタ電流を生成する。また、N++領域34が、アノード42に電気的に結合されている（即ち、ショートしている）ならば、垂直寄生NPNトランジスタのコレクタ及びベースは、おおよそ同じ電圧であり、かくして、負電圧までグランドを下げるようなコレクタ電圧のための道はない。コレクタが、負電圧まで下げられることが許容されるならば、N+領域13とP基板12との間の接合は、伝導ダイオード接合を形成し、かくして、基板12内に電流を注入する。

10

【0023】

N++領域34がカソード40に電気的に結合されている（即ち、ショートしている）ならば、カソード40で高い電圧を支持することが可能である。N++領域34とカソード40とを電気的に結合することにより、N領域22とP領域26との間の接合、並びに、P領域26とN+領域13との間の接合にも負バイアスを生成する。これらの2つのリバースバイアス接合は、N領域22、特に、P領域24に最も近いN領域22、及び、誘電層18に最も近いN領域22の電界を一緒に低減させる。この低減された電界により、より高い最大電圧がカソード40で支持される。

20

【0024】

N++領域34がアノード42又はカソード40のいずれにも電気的に接続されおらず、電気的に浮遊することが可能であれば、カソード40でより高い電圧を支持することが可能である。N+領域13の電圧を浮遊させることができるとならば、カソード40で支持される最大電圧は、P+領域20とN+領域13との間の物理的な拒理によって制限されないが、デバイス10の他の特性（例えば、N+領域13及びP領域12の領域のドーピング濃度）によって制限される。

【0025】

本発明のある実施形態では、アノード42は、複数のドーパント濃度を含む。ある実施形態では、P++領域30は、 $1 \times 10^{20}$  (cm<sup>-3</sup>) オーダーのドーパント濃度を有し、P+領域20は、 $2 \times 10^{17}$  乃至  $4 \times 10^{17}$  (cm<sup>-3</sup>) のレンジのドーパント濃度を有し、P-領域24は、 $1 \times 10^{15}$  乃至  $5 \times 10^{15}$  (cm<sup>-3</sup>) のレンジのドーパント濃度を有し、P領域26は、 $2 \times 10^{16}$  乃至  $5 \times 10^{16}$  (cm<sup>-3</sup>) のレンジのドーパント濃度を有する。これらのドーパント濃度は、例示目的だけのものである。本発明の別の実施形態では、他の適当なドーパント濃度を使用することができ得る。P++領域30のヘビードーパント濃度は、上に横たわる伝導層（図示せず）と良好なオーミック接合を形成するための目的による。かくして、P++領域30は、ここではオーミック領域と呼ぶ。本発明のある実施形態では、アノード42で使用される最低のP型ドーパント濃度と、アノード42で使用される最高のP型ドーパント濃度との間の、少なくとも1桁の差の大きさ（即ち、10の1乗）があることに注意すべきである。本発明の別の実施形態では、アノード42で使用される最低のP型ドーパント濃度と、アノード42で使用される最高のP型ドーパント濃度との間の、少なくとも2桁の差の大きさ（即ち、10の2乗、又は、100倍）がありうる。本発明の別の実施形態では、集積回路製造技術によって許容される0（即ち、無差）と最大の差との間のどんな所望のポイントでも、最低と最高のドーパント濃度の間の差を示す。

30

【0026】

本発明のある実施形態では、カソード40は、複数のドーパント濃度を含む。ある実施形態では、N++領域32は、 $5 \times 10^{20}$  のオーダーのドーパント濃度を有し、N領域22は、 $3 \times 10^{16}$  乃至  $6 \times 10^{16}$  のレンジのドーパント濃度を有する。これらのドーパント濃度は、例示の目的だけのために与えられたものである。本発明の別の実施形態では、他のいかなるドーパント濃度を使用することもでき得る。N++領域32の高いドーパント濃度

40

50

は、上に横たわる伝導層（図示せず）と良好なオーミック接触を形成する目的のためであることに注意すべきである。かくして、N++領域32は、ここではオーミック領域とも呼ばれる。インターフェース49は、アノード42とカソード40との間に、アノード/カソード接合インターフェースを形成する。

【0027】

本発明のある実施形態では、絶縁領域（34, 16, 13）は、複数のドーパント濃度を含む。ある実施形態では、N++領域34は、 $5 \times 10^{20}$ のオーダーのドーパント濃度を有し、N+領域16は、 $5 \times 10^{17}$ 乃至 $8 \times 10^{17}$ のレンジのドーパント濃度を有し、N+領域は、 $1 \times 10^{18}$ 乃至 $5 \times 10^{18}$ のレンジのドーパント濃度を有する。これらのドーパント濃度は、例示の目的のためだけに与えられたものである。本発明の別の実施形態では、他のいかなるドーパント濃度を使用することもでき得る。N++領域34の高いドーパント濃度は、上に横たわっている伝導層（図示せず）と良好なオーミック接触を形成する目的であることに注意すべきである。かくして、N++領域34は、ここではオーミック領域とも呼ばれうる。

【0028】

本発明の他の実施形態では、P基板12は、P+基板12からドープされうる。本発明の別の実施形態では、基板12は、そこに形成された上に横たわるP型エピタキシャル層を備えたP++基板であって良い。次いで、図1で図示されたN+領域13として同様に機能するように、N型埋設層を形成するように、インプランテーション及び拡散が使用され得る。次いで、第2のP型エピタキシャル層が、N型埋設層の上に横たわるように堆積されうる。この第2のP型エピタキシャル層は、図1に図示したようにP領域24として同様な機能として役立つ。次いで、P領域26及びN領域22を形成するようにインプランテーションが使用されうる。ある実施形態では、同じインプランテーションマスクが、領域26及び22を形成するのに使用されうる。次いで、層14, 18及び19を形成するために、エッティング及び酸化物体積が実施されうる。次いで、P+領域20を形成するためにインプランテーションが用いられ、N+領域16を形成するために別のインプランテーションを用いることができ得る。本発明の別の実施形態では、N+領域16を形成するための複数のインプラ・ステップとマスクを使用することができ得る。次いで、層27を形成するために酸化物堆積が実行され、層28を形成するためにポリシリコン堆積が実行されうる。次いで、N++領域32及び34を形成するためにインプランテーションが用いられ、P++領域30を形成するために別のインプランテーションが用いられ得る。本発明の別の実施形態では、半導体デバイス10の種々の実施形態を形成するために適当なオーダーの別のいかなる適当なステップを使用することもでき得る。

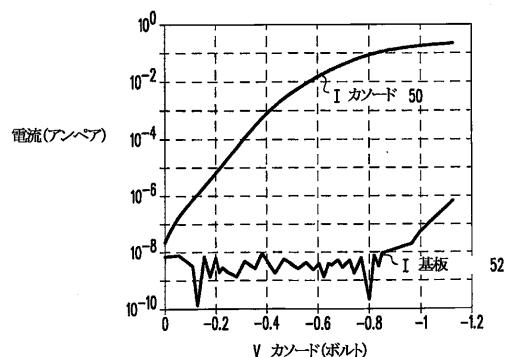

【0029】

図2は、図1の半導体デバイス10によって生成された基板電流（I基板52）とカソード電流（Iカソード50）とを図示する、電流対電圧（カソード-アノード間電圧）をグラフ形式で図示する。基板12（図1参照）内に注入された寄生電流（I基板52）は、カソード電流（Iカソード50）よりもおおよそ6桁オーダー小さい大きさであることに注意すべきである。図2は、N++領域34（絶縁領域）がアノード42にショートされており、両者はおおよそ0ボルトであり、カソード40の電圧は0ボルトより下に引き下げられ、基板12は-10ボルトにバイアスされ、半導体デバイス10の温度はおおよそ摂氏150°であると仮定する。10マイクロメータを超えたN+領域16の幅を増やすことにより、基板12内に注入されるカソード電流を低減させるが；半導体デバイス10を形成するのに要求される半導体面積の量と、半導体デバイス10の電子性能との間にトレードオフが生じうる。在来の非絶縁ダイオードに関しては、基板内に注入された寄生電流は、カソード電流のおおよそ10%であることに注意すべきである。かくして、在来の非絶縁ダイオードは、非常に大きな寄生電流を基板内に注入し、同じ集積回路に形成された隣接する回路の潜在的な誤作動を生じさせる。

【0030】

本発明が、潜在的な極性又は特定の伝導タイプに関して記載されているけれども、潜在

10

20

30

40

50

的な極性及び伝導タイプを評価する当業者は反対にすることができる。また、半導体デバイス 10 の種々の部分を形成するのに使用された半導体材料は、いかなる適当な材料であって良い。例えば、基板 12 は、シリコン又はいかなる他の適切な半導体材料であって良い。また、半導体デバイス 10 は、高電圧及び高電流で作動可能なパワー集積回路内に組み込まれても良い。

#### 【0031】

先の明細書では、本発明は特定の実施形態を参照して記載されている。しかしながら、当業者は、添付の特許請求の範囲の本発明の範囲から逸脱することなく、種々の修正及び変更をすることができうる。従って、明細書及び図面は、觀念を制限するのではなく例示であり、係る全ての修正は、本発明の範囲内に含まれるものである。

10

#### 【図面の簡単な説明】

#### 【0032】

【図1】本発明の一つの実施形態による半導体デバイスの断面図を図示したものである。

【図2】図1の半導体デバイスによって生成された基板電流とカソード電流とを図示する電流対電圧(カソード-アノード電圧)グラフをグラフ形式で図示したものである。

【図1】

【図2】

---

フロントページの続き

(72)発明者 ジュー, ロンファ

アメリカ合衆国アリゾナ州85248, チャンドラー, ウエスト・ノラン・ウェイ 953

(72)発明者 ボーズ, アミタヴァ

アメリカ合衆国アリゾナ州85283, テンペ, サウス・ケンウッド・レーン 6820

(72)発明者 クヘムカ, ヴィシュヌ・ケイ

アメリカ合衆国アリゾナ州85048, フェニックス, イースト・マウンテン・スカイ・アベニュー

— 315

(72)発明者 パルササラシ, ヴィジャイ

アメリカ合衆国アリゾナ州85048, フェニックス, イースト・ヒドゥンビュー・ドライブ 2

325

審査官 村岡 一磨

(56)参考文献 特開平01-194369 (JP, A)

特開2003-092414 (JP, A)

特開昭52-082081 (JP, A)

特開2002-198541 (JP, A)

特開2004-031576 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/861

H01L 21/329

H01L 29/868