(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4166305号

(P4166305)

(45) 発行日 平成20年10月15日(2008.10.15)

(24) 登録日 平成20年8月8日(2008.8.8)

|                     |            |

|---------------------|------------|

| (51) Int.Cl.        | F 1        |

| HO3M 7/36 (2006.01) | HO3M 7/36  |

| HO4N 7/30 (2006.01) | HO4N 7/133 |

| HO4N 7/32 (2006.01) | HO4N 7/137 |

請求項の数 9 (全 17 頁)

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願平9-257156                  |

| (22) 出願日     | 平成9年9月22日(1997.9.22)         |

| (65) 公開番号    | 特開平10-224804                 |

| (43) 公開日     | 平成10年8月21日(1998.8.21)        |

| 審査請求日        | 平成16年9月22日(2004.9.22)        |

| 審判番号         | 不服2007-28120(P2007-28120/J1) |

| 審判請求日        | 平成19年10月15日(2007.10.15)      |

| (31) 優先権主張番号 | 60/026,933                   |

| (32) 優先日     | 平成8年9月20日(1996.9.20)         |

| (33) 優先権主張国  | 米国(US)                       |

| (31) 優先権主張番号 | 60/026,963                   |

| (32) 優先日     | 平成8年9月20日(1996.9.20)         |

| (33) 優先権主張国  | 米国(US)                       |

| (31) 優先権主張番号 | 60/038,019                   |

| (32) 優先日     | 平成9年2月14日(1997.2.14)         |

| (33) 優先権主張国  | 米国(US)                       |

|           |                                                                                                                         |

|-----------|-------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 390035493<br>エイ・ティ・アンド・ティ・コーポレーション<br>A T & T C O R P.<br>アメリカ合衆国 10013-2412<br>ニューヨーク ニューヨーク アヴェニュー<br>- オブ ジ アメリカズ 32 |

| (74) 代理人  | 100075258<br>弁理士 吉田 研二                                                                                                  |

| (74) 代理人  | 100096976<br>弁理士 石田 純                                                                                                   |

| (72) 発明者  | バリン ジオフリー ハスケル<br>アメリカ合衆国 ニュージャージー州 ティントン フォールズ グレンウッド ドライブ 82                                                          |

|           | 最終頁に続く                                                                                                                  |

(54) 【発明の名称】ビデオの画像コーディング及びイントラコーディングのための暗黙の係数予測及び走査適合化を提供するビデオコーダー

## (57) 【特許請求の範囲】

## 【請求項 1】

符号化方法であって、

(1) 画像データをブロック配列に構成し、

(2) 各ブロックのデータを離散コサイントランസフォームにしたがって変換して、各ブロックについて少なくとも1つのDC係数と少なくとも1つのAC係数を得て、

(3) 画像データ内の各ブロックXについて、

(a) ブロックXの上方で左側にあるブロックBと、ブロックXのすぐ左側にあるブロックAとの間のDC係数の垂直勾配を検出し、

(b) ブロックBと、ブロックXの直ぐ上方にあるブロックCとの間のDC係数の水平勾配を検出し、

(c) 垂直勾配が水平勾配より小さい場合には、ブロックXのDC係数はブロックCのDC係数の値になると予測し、

(d) そうでない場合は、ブロックXのDC係数はブロックAのDC係数の値になると予測し、

(e) 予測されたDC係数とブロックXのDC係数とに基づいてブロックXに対する残留DC係数を生成し、

(4) 各ブロックXに対する少なくとも1つのDC係数の代わりに各ブロックXの残留DC係数を使って各ブロックに対する係数を可変長符号化する、

ステップを有し、

10

20

この時、任意のブロック A、B、C が画像データの境界の外側であれば、当該ブロックの DC 係数を予め定められた値に設定するとともに、

前記ブロック A に基づいて予測する場合は、ブロック X に対する可変長符号化を垂直方向および対角方向の走査で行い、ブロック C に基づいて予測する場合は、ブロック X に対する可変長符号化を水平方向および対角方向の走査で行う、

ことを特徴とする符号化方法。

【請求項 2】

ブロック X の DC 係数をブロック A からとった場合、

前記 DC 係数に対応する位置のブロック X 内の AC 係数縦行を、ブロック A 内の対応する AC 係数縦行に基づいて予測し、

予測された AC 係数縦行およびブロック A に対する AC 係数に基づいて残留 AC 係数を生成し、

ブロック X の DC 係数をブロック C からとった場合、

前記 DC 係数に対応する位置のブロック X 内の AC 係数横列を、ブロック C 内の対応する AC 係数横列に基づいて予測し、

予測された AC 係数横列およびブロック C に対する AC 係数に基づいて残留 AC 係数を生成する、請求項 1 に記載の符号化方法。

【請求項 3】

ブロック X に対する AC 係数の可変長符号化が、ブロック X に対する残留 AC 係数の可変長符号化より小さい帯域幅を使用するかを検出し、

もしそうであれば、ブロック X に対する AC 係数に基づいてブロック X の可変長符号化を出力する、

ステップを更に有する、請求項 2 に記載の符号化方法。

【請求項 4】

可変長符号化された係数が残留 AC 係数を含むかどうかを示すフラグ信号を出力するステップを更に有する、請求項 2 に記載の符号化方法。

【請求項 5】

可変長符号化を垂直方向および対角方向の走査で行う場合には、可変長符号化の走査が表 4 に記載の番号の順によって与えられる、請求項 2 に記載の符号化方法。

【請求項 6】

可変長符号化を水平方向および対角方向の走査で行う場合には、可変長符号化の走査が表 3 に記載の番号の順によって与えられる、請求項 1 に記載の符号化方法。

【請求項 7】

復号化方法であって、

( 1 ) 符号化された画像データの複数のブロックの各々を識別し、

( 2 ) 各ブロックの符号化されたデータを可変長復号化して、各ブロックについて DC 係数と少なくとも 1 つの AC 係数を得て、

( 3 ) 画像データ内の各ブロック X について、

( a ) ブロック X の上方で左側にある以前に復号化されたブロック B と、ブロック X のすぐ左にある以前に復号化されたブロック A との間の DC 係数の垂直勾配を検出し、

( b ) ブロック B と、ブロック X のすぐ上方にある以前に復号化されたブロック C との間の DC 係数の水平勾配を検出し、

( c ) 垂直勾配が水平勾配より小さい場合には、ブロック X の DC 係数はブロック C の DC 係数の値になると予測し、そうでない場合は、ブロック X の DC 係数はブロック A の DC 係数の値になると予測し、

( d ) ブロック X に対する復号化された DC 係数とブロック X に対する予測された DC 係数とに基づいてブロック X に対する DC 係数を生成し、

( 4 ) 当該ブロックに対する復号化された DC 係数の代わりに、生成された DC 係数を使って逆離散コサイントランスフォームにしたがって各ブロックの画像データを生成する、

ステップを有し、

10

20

30

40

50

画像データの境界の外にある任意のブロック A、B、または C に対する D C 係数は予め定められた値に設定されるとともに、

前記ブロック A に基づいて予測する場合は、ブロック X に対する可変長復号化を垂直方向および対角方向の走査で行い、ブロック C に基づいて予測する場合は、ブロック X に対する可変長復号化を水平方向および対角方向の走査で行う、

ことを特徴とする復号化方法。

#### 【請求項 8】

前記可変長復号化を垂直方向および対角方向の走査で行う場合には、可変長復号化の走査が表 4 に記載の番号の順によって与えられ、

前記可変長復号化を水平方向および対角方向の走査で行う場合には、可変長復号化の走査が表 3 に記載の番号の順によって与えられる、請求項 7 に記載の復号化方法。10

#### 【請求項 9】

ビデオ符号器であって、

ビデオデータのブロックに対する入力と、当該ブロックの D C T 係数に対する出力とを有し、離散コサイントランスフォームを行う離散コサイントランスフォーム回路と、

前記離散コサイントランスフォーム回路の出力に連結された入力と、当該ブロックの量子化係数データに対する出力とを有し、量子化を行う量子化器と、

前記量子化器の出力に連結された入力と、当該ブロックの予測された係数データに対する出力とを有し、 $| D C_A - D C_B | < | D C_B - D C_C |$  の場合には、ブロック X の D C 係数を近所のブロック C に基づいて予測し、そうでない場合は、ブロック X の D C 係数を別の近所のブロック A に基づいて予測する勾配分析器と、20

前記勾配分析器に連結された入力と、当該ブロックの可変長符号化されたデータに対する出力とを有し、可変長符号化を行う可変長符号器と、

を有し、

$D C_A$ 、 $D C_B$ 、および  $D C_C$  の各々は、ブロック A、B、および C の D C 係数をそれぞれ表し、

ブロック A はブロック X の水平方向の左側にあり、

ブロック C はブロック X の垂直方向の上方にあり、

ブロック B はブロック X の上方の左側にあり、

前記ブロック A に基づいて予測する場合は、ブロック X に対する可変長符号化を垂直方向および対角方向の走査で行い、ブロック C に基づいて予測する場合は、ブロック X に対する可変長符号化を水平方向および対角方向の走査で行う、30

ことを特徴とするビデオ符号器。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本出願は、1996年9月20日付けで提出された米国仮出願第 60/026,933 号及び 1997 年 2 月 14 付けで提出された米国仮出願第 60/038,019 号によって付与された優先権に基づくものである。

##### 【0002】

##### 【従来の技術】

ビデオ画像の通信、記憶及び検索のためのプロトコルとしては様々なものが知られている。プロトコルは、常に信号帯域幅を低減させることを特に重視して開発されている。信号帯域幅を低減させることにより、記憶デバイスはより多くの画像を記憶することができ、通信システムは、一定の与えられた通信速度でより多くの画像を送ることができる。信号帯域幅の減少は、信号を用いるシステム全体の容量を増大させる。

##### 【0003】

しかしながら、帯域幅の減少には特定の欠点が付随する可能性がある。例えば、或る種の既知のコーディングシステムは損失が大きく、又復号された画像の知覚的品質に影響を及ぼしうる誤差を導く。他のコーディングシステムは、或る種のタイプの画像について大幅

10

20

30

40

50

な帯域幅減少を達成できるが、他のタイプの画像については全く帯域幅減少を達成できない。従って、コーディング体系の選択については注意深い配慮が求められる。

#### 【0004】

##### 【発明が解決しようとする課題】

従って、当該技術分野においては、知覚的に有意な誤差を導くことなく信号帯域幅を低減させる画像コーディング体系に対するニーズが存在する。

#### 【0005】

##### 【課題を解決するための手段】

新しいブロックに先行する3つの画像データブロックから新しい画像データブロックを予測する予測式コーディング体系によって、先行技術の欠点は、大幅に軽減される。この新しいブロックについて、符号器は、新しいブロックに対し水平方向及び垂直方向に隣接するブロックの画像データを検査する。符号器は、2つの隣接するブロックの各々の画像データを、垂直方向に隣接するブロックに対し水平方向に隣接して位置付けられている（新しいブロックより対角線方向に上）第3のブロックの画像データに対し比較する。これらの比較から、水平及び垂直の勾配が決定される。勾配の値に基づき、符号器は、それに最も類似する水平又は垂直方向に隣接するブロックの画像データとなるべき新しいブロックの画像データを予測する。その後、符号器は、新しいブロックについての画像データの実際値と画像データの予測値の間の残留差を決定し、残余を符号化する。復号器は、水平及び垂直勾配に基づき新しいブロックのための画像データを予測しそれに残余を加算して新しいブロックの実際の画像データを再構築する逆予測を実行する。このプロセスには損失が無い。

10

#### 【0006】

##### 【発明の実施の形態】

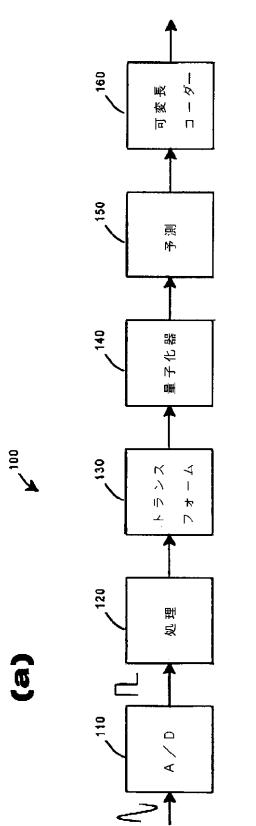

図1(a)は、本発明の第1の実施形態に従って構築された符号器100を示す。アナログ画像信号が符号器100に供給される。画像信号は、当該技術分野において既知の技術を用いてサンプリングされ、アナログ-デジタル（「A/D」）変換器110によりデジタル信号に変換される。A/D変換器110は、画像の複数の画素に対してデジタル画像信号を生成する。代替的には、画像信号は、デジタル画像信号として符号器に供給することもできる。この場合、A/D変換器110は削除される。

20

#### 【0007】

30

デジタル画像信号は、処理回路120に入力される。処理回路120は、多数の機能を実行することができる。標準的には、処理回路120は、画像データをフィルタリングし、画像データを1つの輝度信号成分と2つの色信号成分に分割する。付加的には、処理回路120は、画像データをデータブロックの形にまとめる。デジタル入力信号が、走査方向における複数の画素についての情報を表す場合、処理回路120のデジタル入力は画素ブロックを表し、例えば、データを画像データの8画素×8画素のアレイの形にブロック化することができる。処理回路120は、マクロブロックベースで画像データを出力する。マクロブロックは、標準的に4つの輝度データブロックと2つの色データブロックで構成されている。処理回路120は同様に、個々の設計基準に適合するよう、フィルタリングといったような付加的な機能も実行する。

40

#### 【0008】

処理回路120の出力は、トランスフォーム回路130に入力される。トランスフォーム回路130は、画素ドメインから係数のドメインへの、離散コサイントランスフォーム（「DCT」）コーディング又は副帯域コーディングといったような画像データのトランスフォームを実行する。画素ブロックが、等価のサイズを持つ係数ブロックへとトランスフォームされる。DCTコーディングにより出力された係数は一般に、単一のDC係数を内含する。残りは、一部が非ゼロであるAC係数である。同様にして、副帯域コーディングによって出力された係数は、様々な周波数での画像の特性を表す：標準的には、副帯域コーディングからの数多くの係数は非常に小さいものである。トランスフォーム回路130は、係数ブロックを出力する。

50

## 【0009】

量子化器 140 が、一定の又は可変的スカラー値 (Qp) に従って、トランスフォーム回路 130 により生成された信号を基準化(scale)する。量子化器 140 は、信号を符号化するのに利用可能な量子化レベルの数を低減させることによって、画像信号の帯域幅を減少させる。量子化プロセスは損失が大きい。量子化器 140 に入力された数多くの小さい係数は細分されゼロまで打ち切られる。基準化された信号は、量子化器 140 から出力される。

## 【0010】

予測回路 150 は、各ブロックの基準化された DC 係数を予測するため、勾配予測解析を実行する。予測回路 150 は、基準化された AC 係数を通過させることもできるし、代替的にはブロックの AC 係数を予測することもできる。好ましい動作モードでは、予測回路 150 は、AC 係数の予測モード又は通過モードの間での選択を行う。この場合、予測回路 150 は、動作モードを識別するべく AC 予測フラグを生成する。予測回路 150 は、DC 残留信号、AC 信号 (AC 係数又は AC 残余のいずれかを表す) 及び AC 予測フラグを出力する。

10

## 【0011】

可変長コーダー 160 が予測回路 150 の出力を符号化する。可変長コーダー 160 は、標準的に、基準化された信号に対しランレンジス (run length) コーディングを実行するハフマン符号器である。可変長コーダー 160 から出力されたビットストリームは、伝送するか、記憶するか、又は当該技術分野において既知の通りのその他の目的で使用することができる。

20

## 【0012】

符号器 100 の中で、予測回路 150 及び量子化器 140 は、互いに独立した機能を実行する。従ってその動作順序は重要でない。図 1 は、予測回路 150 に対する入力としての量子化器 140 の出力を例示しているが、回路の順序を逆転することも可能である。予測回路 150 の出力は、量子化器 140 に入力できる。

## 【0013】

図 1 (b) において、復号器 200 は、上述の符号化動作を元に戻す動作を実行する。可変長復号器 260 が、基準化された信号を回復するための相補的プロセスを用いて、ビットストリームを解析する。符号器 100 の可変長コーダー 160 がハフマン符号器を使用していた場合は、ハフマン復号器 260 が用いられる。

30

## 【0014】

復元回路 250 は、予測回路 150 内で実行されるものと同一の勾配解析を実行する。DC 残留信号は識別され、DC 係数を得るべく予測された係数に加算される。任意には、復元回路 250 は、AC 予測フラグを識別することができ、このフラグの状態に基づいて AC 情報を AC 係数情報又は AC 残留情報のいずれかとして解釈する。AC 残留情報が存在する場合、復元回路 250 は、残留信号を対応する予測信号に付加して AC 係数を得る。復元回路 250 は係数信号を出力する。

## 【0015】

スカラー回路 240 が、量子化回路 140 内の除算のためのベースとして用いられたものと同じスカラーを、回復された信号に乗じる。当然のことながら、ゼロまで分割されたこれらの係数は回復されない。

40

## 【0016】

逆トランスフォーム回路 230 は、符号器 100 のトランスフォーム回路 130 によって応用されたトランスフォームの逆を実行する。DCT トランスフォームが実行された場合、逆 DCT トランスフォームが応用される。副帯域コーディングの場合も同様である。逆トランスフォーム回路 230 は、係数情報を画素ドメインにトランスフォームし戻す。

## 【0017】

処理回路 220 は、輝度信号及び色信号を組み合わせ、特定のアプリケーションにおいて望まれるような任意の機能を実行することができる。処理回路 220 は、いつでも表示で

50

きる状態にある画素のデジタル信号を出力する。この時点で、信号は、デジタルモニター上に表示するのに適合した状態にある。特定のアプリケーションに適合させることが必要である場合、アナログ表示装置上での表示のためデジタル - アナログ変換器 210 で信号を変換することができる。

【0018】

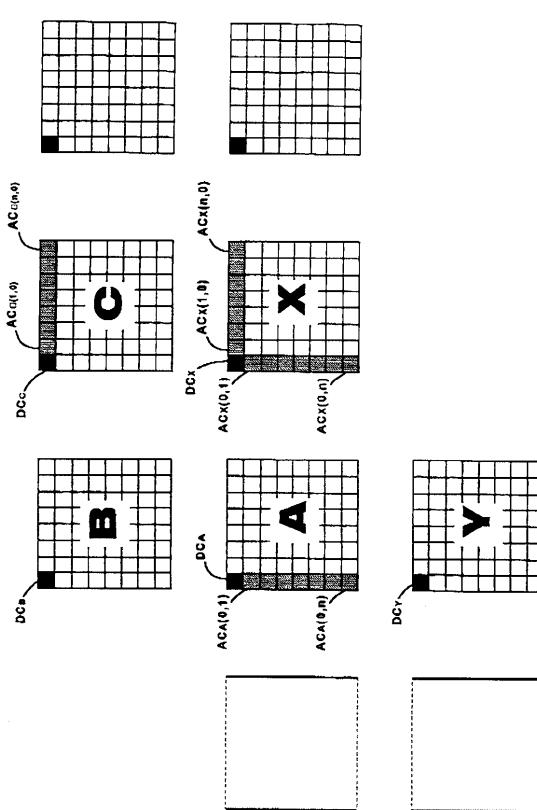

図 2 は、予測回路によって処理されたとおりのデータ構造を例示している。トランスマルチフォーム回路から出力されたデータは、マクロブロックの形に組織された複数のブロックを表す。各々のマクロブロックは、標準的には、マクロブロックの輝度成分を表す 4 つのブロックとマクロブロックの色成分を表す 2 つのブロックによって占有されている。

【0019】

各ブロックは、ブロックがそこから誘導された空間的領域の係数を表す。DCTトランスマルチフォームが応用された場合、ブロックの  $D C_x$  の  $D C$  係数が、左上コーナーのブロックの原点にて提供される。水平方向には  $D C$  係数が占有している横列上に又垂直方向には  $D C$  係数が占有している縦行上に最上位係数が提供されている状態で、ブロック全体を通して  $A C$  係数が提供されている。

【0020】

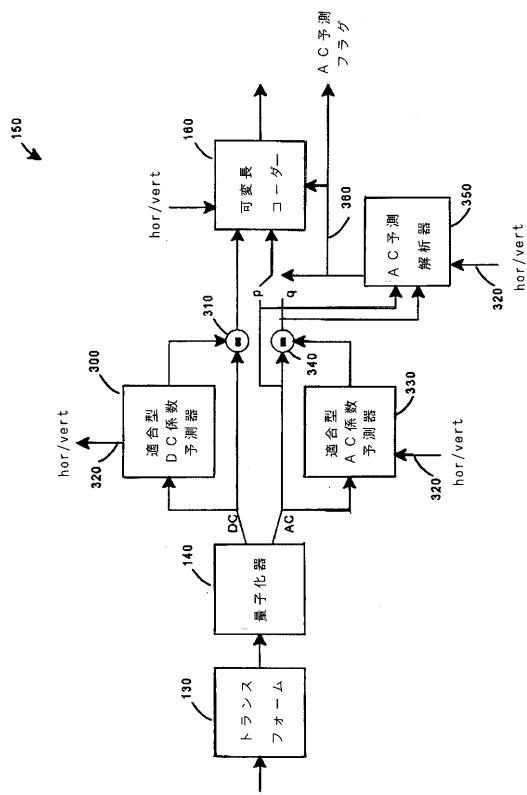

図 3 は、予測回路 150 の詳細なブロックダイヤグラムを示す。量子化器 140 は、基準化された  $D C$  及び  $A C$  係数を生成する。 $D C$  係数は基準化することができ ( $D C = D C / Q p$ 、標準的には  $Q p = 8$ )、 $D C$  係数予測器 300 に入力される。 $D C$  係数予測器は勾配解析を実行する。

【0021】

任意のブロック X について、 $D C$  係数予測器 300 は、図 2 に示されているブロック X に対し水平方向に隣接するブロック A、ブロック X に対し垂直方向に隣接するブロック C 及び、即ちブロック C に対し水平方向に隣接しブロック A に対し垂直方向に隣接するブロックであるブロック B のデータを、メモリ内に維持する。 $D C$  係数予測器は、ブロック A ( $D C_A$ ) の  $D C$  係数をブロック B の  $D C$  係数 ( $D C_B$ ) と比較する。ブロック A 及びブロック B の  $D C$  係数の間の差は、垂直勾配である。 $D C$  係数予測器 300 は同様に、ブロック B の  $D C$  係数 ( $D C_B$ ) とブロック C の  $D C$  係数 ( $D C_C$ ) を比較する。ブロック C 及びブロック B の係数の間の差は水平勾配である。

【0022】

ブロック B からの最高の勾配と結び付けられたブロックは、予測のベースとして使用される。垂直勾配が水平勾配よりも大きい場合、ブロック A がブロック X と高い相関関係をもつことになると予想され、従って、 $D C$  係数予測器 300 は、ブロック X の予測のためのベースとしてそれがブロック A を用いる水平予測を利用する。水平勾配が垂直勾配よりも大きい場合、従って、 $D C$  係数予測器 300 は、ブロック X の予測のためのベースとしてそれがブロック C を用いる垂直予測を利用する。 $D C$  係数予測器 300 は、減算器 310 に対し予測のために使用されたブロックの  $D C$  係数 ( $D C_A$  又は  $D C_C$ ) を出力する。 $D C$  係数予測器 300 は、同様に、水平予測又は垂直予測のいずれが実行されるかを示す  $h o r / v e r t$  信号 320 も生成する。

【0023】

減算器 310 は、ブロック X についての  $D C$  残留信号を得るためにブロック X の  $D C$  係数から  $D C$  係数予測器 300 によって生成された  $D C$  係数を減算する。 $D C$  残余は、予測回路 150 から可変長コーダー 160 へ出力される。

【0024】

上述のプロセスは、コーディングすべき画像の内部でのブロックの係数を予測するために利用される。しかしながら、ビデオオブジェクト平面の新しい横列の開始点で係数を予測する場合、予測のための先行ブロックは、通常のプロセスのもとで上にあるラインの最後のブロックである。標準的にはこれらのブロック間にはほとんど相関関係がない。

【0025】

図 2 中のブロック Y がビデオオブジェクト平面の開始縁にあると仮定する。走査方向では

10

20

30

40

50

、いかなるブロックも水平方向にブロックYと隣接していない。上にある横列内の最終ブロックの画像データは、「水平方向に隣接する」ブロックとして使用されるべく利用可能な状態にあるものの、これは予測のためには用いられない。その代わり、DC係数予測器300は、水平方向に隣接するブロック及びその上にあるブロックのためのDC係数値を、人工的に半強度信号にセットする。DC係数が8ビットのワードによって表される場合、これらのゴーストブロックのDC係数は、128にセットされる。このとき、DC係数予測器300は、上述のプロセスに従って勾配予測を実行する。

#### 【0026】

上述の通り、予測回路150は、予測無しでAC係数を通過させることができる。しかしながら、好ましい一実施形態においては、予測回路150は、AC係数を予測するために勾配解析を用いる。

10

#### 【0027】

予測回路150がAC係数を予測した時点で、AC係数の一部分のみがブロック間の高い相関関係を示し得る。DCTトランスフォームコーディング及び水平予測の場合においては、予測解析に値するほど十分に高い相関関係を示す可能性の高い唯一のAC係数は、DC係数と同じ縦行内にあるものである（ブロックA内で影のついたもの）。従って、DC係数と同じ縦行内のブロックXの各々のAC係数（ $AC_X(0, 1) \sim AC_X(0, n)$ ）について、AC係数予測器330は、ブロックA（ $AC_A(0, 1) \sim AC_A(0, n)$ ）の同じ場所に配置されたAC係数に対応する予測を生成する。予測されたAC係数は、AC予測残留信号を得るべく、減算器340においてブロックXの実際のAC係数から減算される。

20

#### 【0028】

DCTトランスフォームコーディング及び垂直予測の場合では、予測解析に値するほどの充分高い相関関係を示す確率の高い唯一のAC係数は、DC係数と同じ横列内にあるものである（ブロックC内で影がついたもの）。DC係数と同じ横列内のブロックXの各々のAC係数（ $AC_X(1, 0) \sim AC_X(n, 0)$ ）について、AC係数予測器330は、ブロックCのAC係数（ $AC_C(1, 0) \sim AC_C(n, 0)$ ）に対応する予測を生成する。予測されたAC係数は、AC係数残留信号を得るべく減算器340においてブロックXの実際のAC係数から減算される。AC係数予測器は、水平予測モードと垂直予測モードの間で、hor/ver t信号320によって切り替えられる。上述のもの以外のAC係数の勾配予測は実行する必要がない。

30

#### 【0029】

ブロック間のAC係数の相関関係は、発生する可能性はあるものの、必ず発生するわけではない。従って、AC係数の予測は常に帯域幅効率化を導くわけではない。従って好ましい実施形態においては、予測回路150は、AC係数予測が実行されるモードとAC係数予測が実行されない第2のモードの間の動作モードの選択を可能にする。後者のケースでは、トランスフォーム回路からのAC係数は、変化無く予測回路の中を通過する。

#### 【0030】

残余がわかった時点で、AC予測解析器350は、予測無しでマクロブロックのAC係数を伝送することによって消費されるはずの帯域幅と、マクロブロックのAC残余信号を伝送することによって消費されるはずの帯域幅を比較する。予測解析器350は、比較的小さい帯域幅を消費する伝送モードを選択する。予測解析器350は、その選択を表示するべくAC予測フラグ信号360を生成する。

40

#### 【0031】

「類似種」ブロックに基づいて予測が実行される。輝度データブロックの予測のためのブロックを識別する場合には、輝度データの隣接ブロックのみが考慮される。予測の目的では、介在する色データブロックは全て無視される。色ブロックの係数を予測する場合には、予測のため、類似種の色信号のみが考慮される。色信号の1つのタイプであるC<sub>r</sub>データのブロックのためのデータを予測するときには、C<sub>r</sub>データの隣接ブロックが考慮されるが、介在する輝度ブロック及び第2のタイプの色信号C<sub>D</sub>データは無視される。同様に

50

して、色信号の第2のタイプであるC<sub>D</sub>データのブロックのためのデータを予測するときには、C<sub>D</sub>データの隣接ブロックが考慮されるが、介在する輝度ブロック及びC<sub>A</sub>データは無視される。

【0032】

予測回路150は、DC残留信号、AC係数又はAC残余のいずれかを表す信号及びAC予測フラグ信号を出力することができる。

【0033】

図4に示されている復元回路250の中で逆予測動作が実行される。全てのブロックXについて、DC係数予測器400は、ブロックXに先行する隣接ブロックAのデータ、ブロックXより上の隣接ブロックCのデータ及びブロックXより上のブロックであるブロックCに先行するブロックBのデータをメモリ内に保持する。DC係数予測器400は、ブロックAのDC係数をブロックBのDC係数と比較して、垂直勾配を決定する。更に、DC係数予測器400は、ブロックCのDC係数をブロックBのDC係数と比較して水平勾配を決定する。水平勾配が垂直勾配よりも大きい場合、DC係数予測器400は、予測のためのベースとしてブロックCのDC係数を生成する。そうでなければ、DC係数予測器400はブロックAのDC係数を生成する。DC係数予測400は同様に、水平又は垂直のいずれの予測が使用されているかを識別するhor/vert信号420をも生成する。

10

【0034】

復元回路250は、入力ビットストリームからのDC残留信号を識別する。加算器410は、DC係数予測器400によって生成されたDC係数に対してDC残余を加算する。加算器410は、ブロックXのDC係数を出力する。

20

【0035】

好ましい実施形態においては、復元回路250は、入力ビットストリームからAC予測フラグ360を識別する。AC予測フラグ360が、AC予測が使用されたことを表示した場合、復元回路は、入力ビットストリームからのAC残余信号を識別し、AC係数予測器430を動作させる。DC係数予測器からのhor/vert信号420が、ブロックA又はブロックCのいずれが予測のベースとして用いられるかを識別する。これに応えて、AC係数予測器430は、予測器150のAC係数予測器330と同じ要領でブロックA又はブロックCのAC係数に対応する信号を生成する。加算器440が、予測されたAC係数を、対応する残余に加算し、復元されたAC係数を出力する。

30

【0036】

AC予測フラグが、AC予測が使用されなかったことを表示したならば、復元回路250は、ビットストリームからのAC係数信号を識別する。AC係数を復元するのにいかなる算術演算も不要である。

【0037】

DC予測の高度化は、好ましい実施形態において、予測ブロックからの知覚的に優位なAC係数の一部分のブロックXの、DC係数に対する寄与を誘発することによって達成することができる。例えば、予測ベースとしてブロックAが使用される場合、ブロックXの予測されたDC係数は、次のものとしてセットされる：

$$DC_X = DC_A + (4Q_p / 3) * (AC_{02A} - AC_{01A} / 4)$$

40

尚、式中Q<sub>p</sub>は量の基準化因子であり、AC<sub>02A</sub>及びAC<sub>01A</sub>はDCTトランスマームによって生成されるブロックAのAC係数である。

【0038】

同様にして、予測のためのベースとしてブロックCが使用される時、ブロックXの予測されたDC係数は次のようにセットされ得る：

$$DC_X = DC_C + (4Q_p / 3) * (AC_{20C} - AC_{10C} / 4)$$

尚、式中Q<sub>p</sub>は量の基準化因子であり、AC<sub>20C</sub>及びAC<sub>10C</sub>はDCTトランスマームによって生成されるブロックCのAC係数である。

【0039】

本書に記述されている予測及び復元プロセスは、予測のためにどのブロックが使用されて

50

いるかを識別するのにいかなるオーバーヘッド信号も必要とされないことから、「暗黙の(implicit)」方法と呼ばれる。動作中、ブロックA、B及びCの係数値は、符号器100と復号器200の両方で知られている。かくして、復号器200は、付加的な信号伝送無く符号器の予測動作を復元することができる。予測回路がAC予測のモード間の選択を行わなかった実施形態では、AC予測及び復元は純粋に暗黙のものである。第2の実施形態においてはAC予測フラグの付加に伴って、予測プロセスはもはや純粋に暗黙のものではなくなる。

#### 【0040】

予測及び復元回路の符号化／復号化動作は、プログラミングされたマイクロプロセッサ又はデジタル信号プロセッサによってソフトウェア内でも実行され得る。

10

#### 【0041】

図5は、ソフトウェアで実行された予測回路の動作を例示している。プロセッサは、ブロックAのDC係数をブロックBのDC係数に比較して垂直勾配を決定する(ステップ1000)。プロセッサは同様に、ブロックCのDC係数をブロックBのDC係数に比較して水平勾配を決定する(ステップ1010)。

#### 【0042】

プロセッサは、垂直勾配が水平勾配よりも大きいか否かを決定する(ステップ1020)。そうである場合、プロセッサは、ブロックXのDC残余を、ブロックXの実際のDC係数からブロックAのDC係数を引いたものとして定義づける(ステップ1030)。そうでなければ、プロセッサは、ブロックXのDC残余を、ブロックXの実際のDC係数からブロックCのDC係数を引いたものとして定義づける(ステップ1040)。

20

#### 【0043】

プロセッサがAC予測も実行する場合、プロセッサは、図6に示されているように作動する。ステップ1000～1040が、図5に関して前述したとおりに行われる。垂直勾配が水平勾配よりも大きい場合、DC係数と同じ縦行の中にあるブロックAからのAC係数は、ブロックXの対応するAC係数を予測するためのベースとして用いられる。従って、ブロックXのこのようなAC係数( $AC_X(0, 1) \sim AC_X(0, n)$ )の各々について、プロセッサは、ブロックX内の実際のAC係数からブロックA内の対応するAC係数( $AC_A(0, 1) \sim AC_A(0, n)$ )を引いたものにセットされたAC残余を計算する(ステップ1035)。

30

#### 【0044】

ブロックCが予測のベースとして用いられる場合、DC係数の同じ横列内のAC係数は、ブロック間の相関関係を示す可能性がある。従って、ブロックXの横列内の各々のAC係数 $AC(i)$ について、プロセッサは、ブロックX内の実際のAC係数からブロックC内の対応するAC係数を引いたものにセットされた残余( $i$ )を計算する(ステップ1045)。

#### 【0045】

プロセッサは同様に、AC係数を予測することによって帯域幅節減が達成されたか否かをも決定する。1つのマクロブロックについて全ての予測がひとたび行われると、プロセッサは、より小さい帯域幅が、符号化された係数又は残余のいずれによって達成されているか否かを決定する(ステップ1050)。残余がより小さい帯域幅を有しているならば、プロセッサは残余を出力する(ステップ1060)。そうでなければ、プロセッサは、係数を出力する(ステップ1070)。

40

#### 【0046】

好みしい実施形態においては、勾配予測に対し可変長コーダー160の走査方向を拘束することによって、付加的な帯域幅係数が得られる。符号器は、VLCコーディングされたランレベル事象(run-level events)を生成するため、係数ブロックを走査する。しかしながら、自然の画像では、優勢な好みしい走査方向が往々にして存在する。本発明は、ランレンジスコーディングを実行するための3つの走査方向の内の1つを選択するべく、勾配予測解析を用いる。

50

【0047】

【表1】

|    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|

| 0  | 1  | 2  | 3  | 8  | 9  | 10 | 11 |

| 4  | 5  | 6  | 7  | 16 | 17 | 18 | 19 |

| 12 | 13 | 14 | 15 | 24 | 25 | 26 | 27 |

| 20 | 21 | 22 | 23 | 32 | 33 | 34 | 35 |

| 28 | 29 | 30 | 31 | 40 | 41 | 42 | 43 |

| 36 | 37 | 38 | 39 | 48 | 49 | 50 | 51 |

| 44 | 45 | 46 | 47 | 56 | 57 | 58 | 59 |

| 52 | 53 | 54 | 55 | 60 | 61 | 62 | 63 |

水平交互

【表2】

|    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|

| 0  | 4  | 12 | 20 | 28 | 36 | 44 | 52 |

| 1  | 5  | 13 | 21 | 29 | 37 | 45 | 53 |

| 2  | 6  | 14 | 22 | 30 | 38 | 46 | 54 |

| 3  | 7  | 15 | 23 | 31 | 39 | 47 | 55 |

| 8  | 16 | 24 | 32 | 40 | 48 | 56 | 60 |

| 9  | 17 | 25 | 33 | 41 | 49 | 57 | 61 |

| 10 | 18 | 26 | 34 | 42 | 50 | 58 | 62 |

| 11 | 19 | 27 | 35 | 43 | 51 | 59 | 63 |

垂直交互

走査方向の内の第1のものは、上の表1に示されている水平交互走査である。水平交互サーチは、好ましい走査方向が水平方向である場合に利用される。走査は、ブロックのDC残余の位置である原点から開始する。原点から、走査は水平方向に3つの位置を横断する(0~3)。4番目の位置から、走査は、第2横列の第1の位置まで下方に飛び越す。第2横列の第1の位置から、走査は水平方向に3位置を横断する。その後、走査は、ブロックの第1横列まで飛び越して戻り、横列の残りを横断する。第1横列が終結した時点で、走査は、第3横列へと飛び越す。

【0048】

水平交互走査は、同一の要領で、次の5回のバス(横列3~8)を横断する。i番目の横列内の第1の位置から、走査は水平走査方向に3つの位置を横断する。次に走査は(i-1)横列まで飛び越し、第5の位置から横列の終わりまで走査する。5番目のバスの終結時点で、走査は、第8横列の第5の位置まで飛び越え、その横列の終わりまで横断する。

【0049】

走査方向の内の第2のものは、表2に示されている垂直交互走査である。垂直交互サーチは、好ましい走査方向が垂直方向であるとき利用される。垂直交互走査は、水平交互走査に対する相補的プロセスである。

【0050】

10

20

30

40

50

原点から、走査は、垂直方向に3つの位置を横断する(0~3)。第4の位置から、走査は、第2縦行の第1の位置まで飛び越える。第2縦行の第1の位置から、走査は垂直方向に3つの位置を縦断する。その後、走査はブロックの第1縦行まで飛び越えて戻り、縦行の残りを縦断する。第1縦行の終結時点で、走査は、第3横列まで飛び越す。

【0051】

垂直交互走査は、同じ要領で次の5回のパス(縦行3~8)を縦断する。i番目の横列の中の第1の位置から、走査は垂直走査方向に3つの位置を縦断する。走査はその後、(i-1)縦行まで飛び越え、第5の位置から縦行の終わりまで走査する。5番目のパスの終結時点で、走査は8番目の縦行の第5の位置まで飛び越え、縦行の終わりまで横断する。

【0052】

第3の走査方向は、当該技術分野において周知のものである従来のジグザグ走査である。

【0053】

可変長コーダー160は、実行されたAC予測のタイプに従って、走査タイプを選ぶ。いかなるAC予測も実行されていないことをAC予測フラグ360が表示した場合、可変長コーダー160は、従来のジグザク走査を実行する。AC予測が実行されていることをAC予測フラグが表示した場合、可変長コーダー160は、従来のジグザグ走査を実行する。AC予測が実行されていることをAC予測フラグが表示した場合、可変長コーダー160はhor/vert信号320を参照して、水平予測又は垂直予測のいずれが用いられているかを見極める。水平予測の場合には、垂直対角線方向の走査が利用される。垂直予測が用いられる場合、可変長コーダー160は水平-対角線方向走査を利用する。

【0054】

走査方向を決定するのに付加的なオーバーヘッドは全く必要でない。可変長復号器260は、走査方向を決定する。AC予測フラグ360及びhor/vert信号420は、復元回路250から出力する。AC予測が実行されなかつたことをAC予測フラグ360が表示した場合、可変長復号器260は、ジグザクパターンに従って係数をアセンブルする。AC予測が実行されたことをAC予測フラグが表示した場合、可変長復号器260は、勾配予測に基づいて残余をアセンブルする。残余は、水平予測の場合には垂直-対角線走査に従って、又垂直予測の場合には水平-対角線方向走査によってアセンブルされる。もう1つの実施形態では、水平交互及び垂直交互走査は、以下の表3及び4の中にそれぞれ示されているように展開することができる。

【0055】

【表3】

|    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|

| 0  | 1  | 2  | 3  | 4  | 9  | 10 | 11 |

| 5  | 6  | 7  | 8  | 16 | 17 | 18 | 19 |

| 12 | 13 | 14 | 15 | 24 | 25 | 26 | 27 |

| 20 | 21 | 22 | 23 | 32 | 33 | 34 | 35 |

| 28 | 29 | 30 | 31 | 40 | 41 | 42 | 43 |

| 36 | 37 | 38 | 39 | 48 | 49 | 50 | 51 |

| 44 | 45 | 46 | 47 | 56 | 57 | 58 | 59 |

| 52 | 53 | 54 | 55 | 60 | 61 | 62 | 63 |

水平交互

10

20

30

40

50

【表4】

|    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|

| 0  | 5  | 12 | 20 | 28 | 36 | 44 | 52 |

| 1  | 6  | 13 | 21 | 29 | 37 | 45 | 53 |

| 2  | 7  | 14 | 22 | 30 | 38 | 46 | 54 |

| 3  | 8  | 15 | 23 | 31 | 39 | 47 | 55 |

| 4  | 16 | 24 | 32 | 40 | 48 | 56 | 60 |

| 9  | 17 | 25 | 33 | 41 | 49 | 57 | 61 |

| 10 | 18 | 26 | 32 | 42 | 50 | 58 | 62 |

| 11 | 19 | 27 | 35 | 43 | 51 | 59 | 63 |

垂直交互

さらにもう1つの実施形態では、水平交互及び垂直交互走査は、それぞれ以下の表5及び6に示されているように展開することができる。

【0056】

【表5】

|    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|

| 0  | 1  | 2  | 3  | 10 | 11 | 12 | 13 |

| 4  | 5  | 8  | 9  | 17 | 16 | 15 | 14 |

| 6  | 7  | 19 | 18 | 26 | 27 | 28 | 29 |

| 20 | 21 | 24 | 25 | 30 | 31 | 32 | 33 |

| 22 | 23 | 34 | 35 | 42 | 43 | 44 | 45 |

| 36 | 37 | 40 | 41 | 46 | 47 | 48 | 49 |

| 38 | 39 | 50 | 51 | 56 | 57 | 58 | 59 |

| 52 | 53 | 54 | 55 | 60 | 61 | 62 | 63 |

水平交互

【表6】

10

20

30

40

|    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|

| 0  | 4  | 6  | 20 | 22 | 36 | 38 | 52 |

| 1  | 5  | 7  | 21 | 23 | 37 | 39 | 53 |

| 2  | 8  | 19 | 24 | 34 | 40 | 50 | 54 |

| 3  | 9  | 18 | 25 | 35 | 41 | 51 | 55 |

| 10 | 17 | 26 | 30 | 42 | 46 | 56 | 60 |

| 11 | 16 | 27 | 31 | 43 | 47 | 57 | 61 |

| 12 | 15 | 28 | 32 | 44 | 48 | 58 | 62 |

| 13 | 14 | 29 | 33 | 45 | 49 | 59 | 63 |

**垂直交互**

表5の水平交互走査は、ブロックのDC残余の位置（位置0）である原点で始まる。この原点から、走査は、水平方向に3つの位置をステップする（位置0～3）。走査は、原点の下の第2横列の第1の位置まで飛び越す（位置4）。位置4から、水平交互走査は、水平方向に1段ステップし（位置5）、次に、第3横列の第1の位置（位置6）まで飛び越す。走査は水平方向に1位置ステップし（位置7）、第3の位置で第2横列まで戻り（位置8）、横列を横断して1位置だけステップする（位置9）。

**【0057】**

位置9から、水平交互走査は第5の位置で最初の横列まで戻る（位置10）。走査は、第1横列の終わりまで横断してステップする（位置11～13）。走査は横列の最後で（位置14）第2横列に戻り、第2横列が完了するまで内部に向かって横列を横断して水平方向に走査する（位置15～17）。位置17から、水平交互走査は、第4の位置で第3横列に戻り（位置18）、原点に向かって水平方向に1ステップ走査し（位置19）、第4横列の最初の位置まで飛び越す（位置20）。

**【0058】**

第4横列の第1の位置から、水平交互走査は水平方向に1位置だけステップし（位置21）、次に第5横列の第1の位置まで飛び越し（位置22）、再び水平に1位置だけステップする（位置23）。走査は、第3の位置で第4横列まで戻り（位置24）、1ステップを横断して走査し（位置25）、次に、第5の位置で第3横列まで戻る（位置26）。走査は、第3横列を横断して水平にステップし、横列を完了する（位置27～29）。

**【0059】**

第3横列の終わりから、水平交互走査は、第5の位置で第4横列まで戻る（位置30）。走査は、第4横列を横切って水平にステップして横列を完了する（位置31～33）。

**【0060】**

第4横列の終わりから、水平交互走査は第3の位置で第5横列まで戻る（位置34）。走査は、水平方向に1位置だけステップし（位置35）、次に、第6横列の第1の位置まで飛び越す（位置36）。走査は、1位置を横切ってステップし（位置37）、次に、第7横列の第1の位置まで飛び越す（位置38）。水平交互走査は1位置を横断してステップし（位置39）、次に、第3の位置で第6横列まで戻る（位置40）。走査は、1位置だけ横切ってステップし（位置41）、次に第5の位置で第5横列まで戻る（位置42）。水平交互走査は水平に第5横列を横断してステップしてこの横列を完了する（位置43～45）。

**【0061】**

第5横列の終わりから、水平交互走査は第5の位置で第6横列まで戻り（位置46）、水平方向に横断してステップしてその横列を完了する（位置47～49）。

#### 【0062】

第6横列の終わりから、水平交互走査は、第7横列の第3の位置まで戻る（位置50）。走査は水平方向に1位置だけステップし（位置51）、次に、第8横列の最初の位置まで飛び越す（位置52）。走査は、水平方向に3位置ステップし（位置53～55）、次に、第5の位置で第7横列まで戻る（位置56）。水平交互走査は、水平に横断してその横列を完了する（位置57～59）。第7横列の終わりから、走査は、第8横列の第5の位置まで飛び越し（位置60）、水平方向に横切ってステップしてその横列を完了する（位置61～63）。

10

#### 【0063】

表6の垂直交互走査は、ブロックのDC残余の位置である原点で始まる（位置0）。走査は、垂直方向に3つの場所だけステップする（位置0～3）。走査は、原点から縦断して第2縦行の第1の位置まで飛び越す（位置4）。位置4から、垂直交互走査は、垂直方向に1段ステップし（位置5）、次に第3縦行の第1の位置まで飛び越す（位置6）。走査は、垂直方向に1位置だけステップし（位置7）、次に、第3の位置で第2縦行まで戻り（位置8）、垂直方向に1位置だけステップする（位置9）。

#### 【0064】

位置9から、垂直交互走査は、第1縦行の第5位置まで戻る（位置10）。走査は、第1縦行の終わりまでステップする（位置11～13）。走査は、縦行の終わりで第2縦行まで戻り（位置14）、第2縦行が完了するまで縦行の内部に向かって縦行を通って垂直に走査する（位置15～17）。位置17から、垂直交互走査は、第3縦行、第4位置まで戻り（位置18）、縦行の最上部に向かって垂直方向に1段走査し（位置19）、第4縦行の第1の位置まで飛び越す（位置20）。

20

#### 【0065】

第4縦行の中の第1の位置から、垂直交互走査は垂直方向に1位置だけステップし（位置21）、次に第5縦行内の最初の位置まで飛び越し（位置22）、再び垂直方向に1位置ステップする（位置23）。走査は第3の位置で第4縦行（位置24）まで戻り、垂直方向に1段ステップし（位置25）、次に、第5の位置で第3縦行まで戻る（位置26）。走査は、垂直に第3縦行を通ってステップしてその縦行を完了する（位置27～29）。

30

#### 【0066】

第3縦行の終わりから、垂直交互走査は、第5の位置で第4縦行まで戻る（位置30）。走査は、垂直に第4縦行を通してステップしてその縦行を完了する（位置31～33）。

#### 【0067】

第4縦行の終わりから、垂直交互走査は、第3の位置で第5縦行まで戻る（位置34）。走査は垂直方向に1位置だけステップし（位置35）、次に、第6縦行の最初の位置まで飛び越す（位置36）。走査は垂直に1位置ステップし（位置37）、次に、第7縦行の最初の位置まで飛び越す（位置38）。垂直交互走査は、垂直方向に1位置だけステップし（位置39）、次に、第3の位置で第6縦行まで戻る（位置40）。走査は垂直方向に1位置ステップし（位置41）、次に、第5縦行の第5の位置（位置42）まで戻り、垂直方向に第5縦行を縦断してステップしてその縦行を完了する（位置43～45）。

40

#### 【0068】

第5縦行の終わりから、垂直交互走査は、第6縦行の第5の位置まで戻り（位置46）、垂直方向に第6縦行を縦断してステップしてその縦行を完了する（位置47～49）。

#### 【0069】

第6縦行の終わりから、垂直交互走査は、第7縦行の第3の位置まで戻る（位置50）。走査は垂直方向に1位置だけステップし（位置51）、次に、第8縦行の第1の位置まで飛び越す（位置52）。走査は3つの位置を垂直にステップし（位置53～55）、次に、第7縦行の第5の位置まで戻る。走査は、第7縦行を通って垂直にステップして縦行を完了する（位置57～59）。第7縦行の終わりから、垂直交互走査は、第8縦行の第5

50

の位置まで飛び越し（位置 60）、垂直に第 8 縦行を通過してステップしてその縦行を完了する（位置 61 ~ 63）。

【0070】

【発明の効果】

本発明に従うと、係数データのビデオコーディングは、暗黙的勾配予測によって、及び勾配予測方法により得られた結果を利用する走査技術によって、更に効率よく行うことができる。現時点では、本発明のコーディング体系は、MPEG-4 ビデオ検証モデル内に採用されており、MPEG-4 ビデオ規格のために考慮されつつある。

【図面の簡単な説明】

【図 1】（a）は、本発明の実施形態に従った符号器の概略図であり、（b）は、本発明の一実施形態に従った復号器の概略図である。

【図 2】本発明によって処理された画像データの一例を示す図である。

【図 3】図 1 の予測ブロックダイヤグラムである。

【図 4】図 1 の復元回路のブロックダイヤグラムである。

【図 5】ソフトウェアの中で実現された予測回路の流れ図である。

【図 6】ソフトウェアの中で実現された予測回路の第 2 の実施形態の流れ図である。

【符号の説明】

100 符号器、110 アナログ - デジタル変換器、120 処理回路、130 トランスマルチплексор、140 量子化器、150 予測回路、160 可変長コーダー、200 復号器、210 デジタル - アナログ変換器、220 処理回路、230 逆トランスマルチплексор、240 スカラー回路、250 復元回路、320 適合型 DC 係数予測器、330 適合型 AC 係数予測器、350 AC 予測解析器、400 DC 係数予測器、430 AC 係数予測器。

【図 1】

【図 2】

【図3】

---

フロントページの続き

(31)優先権主張番号 08/908,044

(32)優先日 平成9年8月11日(1997.8.11)

(33)優先権主張国 米国(US)

早期審理対象出願

(72)発明者 アタル プリ

アメリカ合衆国 ニューヨーク州 リバーデール シャープ1エイ ヴァルド アベニュー 36

60

(72)発明者 ロバート ルイス シュミット

アメリカ合衆国 ニュージャージー州 ホウェル オーク グレン ロード 333

合議体

審判長 新宮 佳典

審判官 乾 雅浩

審判官 岩井 健二

(56)参考文献 特開昭63-197185(JP,A)

特開平6-165155(JP,A)

特開平8-205180(JP,A)

国際公開第97/46021(WO,A1)

A. Ploysongsang and K.R. Rao, DCT/DPCM Processing of NTSC Composite Video Signal, IEEE Transactions on Communications, 1982年3月, Vol 30, No. 3, p. 541-549

A.N. Netravali and J.O. Limb, Picture Coding: A Review, Proceedings of the IEEE, 1980年3月, Vol. 68, No. 3, p. 366-406