323/22 T

323/22 T

| [72]                  | Inventors            | Robert C. Dobkin<br>Menlo Park;<br>Robert J. Widlar, Mountain View, both of<br>Calif.                |

|-----------------------|----------------------|------------------------------------------------------------------------------------------------------|

| [21]                  | Appl. No.            | 21,968                                                                                               |

| [22]                  | • •                  | Mar. 23, 1970                                                                                        |

| [45]                  | Patented             | Nov. 2, 1971                                                                                         |

| [73]                  | Assignee             | National Semiconductor Corporation<br>Santa Clara, Calif.                                            |

| [54]                  | INCLUDIN<br>COEFFICE | CAL REGULATOR APPARATUS<br>IG A ZÉRO TEMPERATURE<br>ENT VOLTAGE REFERENCE CIRCUIT<br>4 Drawing Figs. |

| [52]                  | U.S. Cl              |                                                                                                      |

|                       |                      | 323/22 T, 323/38, 323/69, 330/23                                                                     |

| [51]                  | Int. Cl              |                                                                                                      |

| [50]                  | Field of Sea         | rch 307/296,                                                                                         |

|                       | 297;                 | 330/23; 317/131; 323/1, 4, 16, 19, 22 T, 38, 68, 69                                                  |

| [56]                  |                      | References Cited                                                                                     |

| UNITED STATES PATENTS |                      |                                                                                                      |

| 3,205                 | ,458 <b>9</b> /19    | 65 Geery 330/23 X                                                                                    |

ABSTRACT: An integrated circuit regulator including a temperature stable constant voltage reference wherein the negative temperature coefficient of the base-to-emitter voltage a first transistor in conjunction with the positive temperature coefficient of the base-to-emitter voltage differential between two additional transistors operating at different current densities is used to achieve a zero temperature coefficient reference potential. The constant voltage reference is combined with a voltage follower and provides a source of constant current which is passed through an external variable resistance to develop a selectable and predictable adjustment voltage for driving the voltage follower so as to cause an unregulated input voltage applied thereto to be regulated at an output terminal.

6/1968 Birman..... 8/1970 Lloyd.....

8/1970 Berger et al. .....

Attorneys-Harvey G. Lowhurst and A. S. Claude Hamrick

3,388,317

3,522,521

3,524,125

Primary Examiner—A. D. Pellinen Assistant Examiner—A. D. Pellinen

SHEET 2 OF 2

ROBERT C. DOBKIN

ROBERT J. WIDLAR

ATTORNEY

# **ELECTRICAL REGULATOR APPARATUS INCLUDING A** ZERO TEMPERATURE COEFFICIENT VOLTAGE REFERENCE CIRCUIT

### **BACKGROUND OF THE INVENTION**

### 1. Field of The Invention

The present invention relates generally to electrical regulator apparatus and, more specifically, to a novel floating voltage regulator circuit suitable for integrated circuit applications and capable of providing regulation over substantially any voltage range. The regulator can also be modified in accordance with the invention to provide a current regulator.

### 2. Discussions of The Prior Art

Standard voltage regulators usually consist of an internal voltage reference, an error amplifier and a power output stage. The error amplifier compares the internal reference with a fraction of the output voltage and drives the output stage to keep the two voltages equal. One of the disadvantages of this type of regulator configuration for integrated circuits is that the minimum input voltage is equal to the internal reference voltage. Since the reference is typically provided by a zener diode, the minimum input voltage is limited by the 7volt breakdown of integrated zener diodes. Most regulators thus cannot operate at very low voltages unless they employ 25 age. two separate power supplies.

Prior art voltage regulators of the integrated circuit type usually have a reference voltage which is generated by a zener diode voltage reference source. The zener diode, however, is still not well understood either mathematically or theoretically 30 and consequently, obtaining a stable zener diode is primarily a matter of chance based on cut-and-try methods of careful selection and measurement. Once a suitable zener is obtained, the only available voltage range for zero temperature coefficient is that of 6 or 7 volts and upward.

Integrated circuit floating voltage regulators have been provided in the prior art which utilize an ordinary zener diode as an external reference. Such circuits, however, require that the input voltage must be at least 6 or more greater than the output voltage. This makes for an inefficient regulator in that 40 there is always a wide variation between the required supply voltage and the regulated voltage. For example, if one requires a 10-volt regulator, he will need at least 16 volts input to supply it. Zener diodes having low temperature coefficients at 6 or 7 volts are readily available but there is no available 45 accordance with the present invention. reference that has a a zero temperature coefficient at voltages much less than 6 volts.

A practical floating regulator should have a reference of less than 6 to eliminate the disadvantages associated with a 6-volt or greater input-output voltage differential.

# **OBJECTS OF THE INVENTION**

It is therefore a primary object of the present invention to provide a novel general purpose electrical regulator having a regulatable output voltage which is adjustable down to 0 volts.

Another object of the present invention is to provide a novel three-terminal voltage regulator suitable for integrated circuit applications and capable of providing voltage regulation at any output voltage.

Still another object of the present invention is to provide a novel voltage regulator circuit suitable for integrated circuits and including a new type of internal voltage reference circuit having a zero temperature coefficient.

Still another object of the present invention is to provide a 65 novel adjustable floating voltage regulator that can be made in monolithic integrated circuit form and encapsulated in a standard three-terminal transistor package, thus avoiding the problems of multilead IC power packages.

# SUMMARY OF THE PRESENT INVENTION

In accordance with the present invention, a novel electrical regulator circuit is provided which can be used to regulate either voltage or current. The regulator includes a zero temperature coefficient transistorized reference circuit and 75 circuit 14 having a zero temperature coefficient is provided

operational amplifier circuit which cooperate in such a manner as to provide a general purpose floating regulator circuit having an output voltage regulation level that is adjustable down to 0 volts. The circuit is well suited for integrated circuit applications and can be provided in a standard three-terminal transistor power package.

One of the principal advantages of the present invention is that the internal voltage reference is provided by a temperature stable transistorized circuit which forms an integral part of the regulator. The reference circuit uses certain basic properties of transistors in a particular combination to provide a stable low voltage reference for the circuit.

Another advantage of the present invention is that the entire circuit can be monolithically fabricated and encapsulated in a standard three-terminal power transistor package such that the unregulated input voltage can be applied to one of the terminals, a variable adjustment resistance can be connected to another of of he three terminals for use in setting the regulated voltage level, and the regulated voltage can be obtained at the third terminal.

Still another advantage of the present invention is that no zener diodes, reverse punch-through transistors, varistors or batteries are required to provide the internal reference volt-

Still another advantage of the present invention is that the internal reference has lower noise, better long term stability and can be better explained theoretically than the reference in other prior art regulators.

These and other advantages of the present invention will be apparent to those skilled in the art after having read the following detailed disclosure of preferred embodiments which are illustrated in he several figures of the drawing.

### IN THE DRAWING

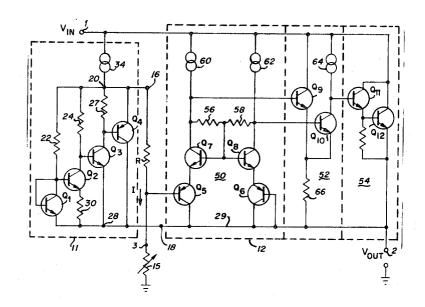

FIG. 1 is a block diagram showing a three-terminal floating voltage regulator device in accordance with the present inven-

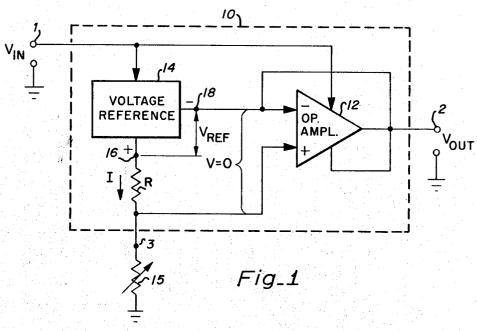

FIG. 2 is a diagram illustrating in detail the voltage reference circuit of the present invention.

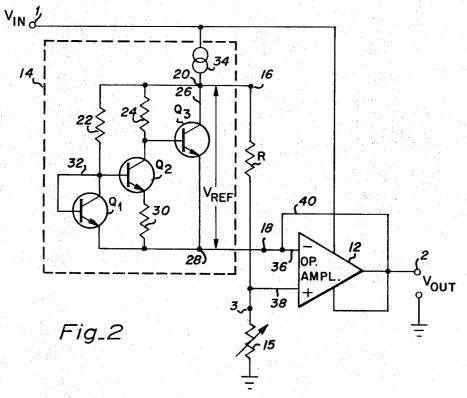

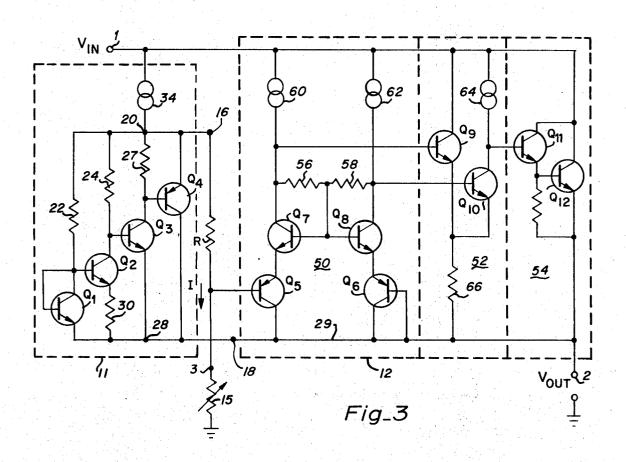

FIG. 3 is a schematic circuit showing a preferred embodiment of the present invention.

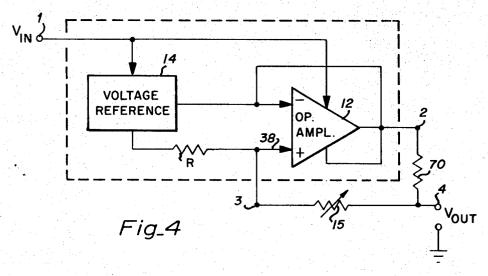

FIG. 4 is a diagram illustrating a current regulator circuit in

## DETAILED DESCRIPTION OF THE PREFERRED **EMBODIMENTS**

Turning now to FIG. 1 of the drawing, a simplified block diagram of the present invention is shown to illustrate that the invention provides a three-terminal floating voltage regulator which can be packaged in the standard three-terminal transistor power package. The circuit 10 includes an input terminal 1, an output terminal 2 and an adjustment terminal 3 which correspond to the three terminals of the standard power transistor package. Connected between the input terminal 1 and the output terminal 2 is an operational amplifier 12 which is adapted to operate as a voltage follower for regulating an 60 input voltage V<sub>in</sub>, applied at terminal 1 to provide a regulated output voltage Vout, at output terminal 2. The op-amp 12 causes the voltage  $V_{out}$  at terminal 2 to be the same as the voltage appearing at terminal 3 in accordance with the normal operating characteristics of a voltage follower circuit, i.e., that the output voltage is identical to the input voltage.

The potential appearing at terminal 3 is generated by causing a current 1 to flow through an external variable resistance 15 which is connected between terminal 3 and ground. Since the output voltage of a voltage follower must be identical to 70 the input voltage, the potential Vont must be identical to the voltage drop across resistor 15. However, in order to render the voltage drop across resistor 15 predictable for a given resistive setting, a constant current must be generated and caused to flow therethrough. Accordingly, a voltage reference 3

which is capable of generating a constant voltage V<sub>ref</sub> across its output terminals 16 and 18 as indicated. The terminal 18 is then coupled to the negative input and the output of the opamp 12 and the more positive output terminal 16 is coupled through a resistance R to the positive input of op-amp 12.

One of the characteristics of op-amp 12 is that the potential across the positive and negative inputs must also be equal to 0 volts. Therefore, since the positive input of op-amp 12 draws negligible current, it will be seen that

(1)

$$V_{ref}$$

-IR=0

and since the voltage  $V_{rer}$  is a constant and the resistance of resistor R is constant, the current I flowing through resistor R must also be constant. The positive input to the op-amp 12 draws negligible current, so substantially all of the current I must necessarily flow out of the terminal 3 and through the adjustment resistor 15.

The adjustment voltage  $V_{adj}$  at the positive input of the opamp 12, i.e., terminal 3, is

$$(2) V_{adj} = V_{ref} R_{15} / R$$

where

R is the resistance of resistor R, and  $R_{15}$  is the resistance of the adjustment resistor 15.

Since the input voltage to op-amp 12 is equal to the output voltage thereof,

$$(3) \qquad V_{out} = V_{ref} R_{15} / R$$

Turning now to Figure 2 of the drawing, the invention is again illustrated showing a preferred embodiment of the voltage reference circuit in detail. The voltage reference circuit 14 includes three matched transistors Q1, Q2 and Q3. In an in- 30 tegrated circuit embodiment, transistors Q1, Q2 and Q3 are matched by virtue of their having been made at the same time in a single integrated circuit. The collectors of transistors Q1 and Q2 are connected to the circuit point 20 through resistors 22 and 24 respectively, while the collector of transistor  $Q_3$  is 35 directly connected thereto. The emitters of transistors Q1 and Q<sub>3</sub> are directly connected to a circuit point 28, while the emitter of Q<sub>2</sub> is connected thereto through a resistance 30. The base and collector of transistor Q1 are shorted together by lead 32. Circuit point 20 is coupled to input terminal 1 through a current source 34 and is also coupled to output terminal 3 through the resistor R. Terminal 28 is connected to the negative input terminal 36 of op-amp 12 and the output of the op-amp while terminal 3 is connected to the positive terminal 38 of op-amp 12.

Voltage reference circuit 14 uses the negative temperature coefficient of the base-to-emitter voltage V<sub>BE</sub> of transistor Q<sub>3</sub> in conjunction with the positive temperature coefficient of the base-to-emitter differential  $\Delta V_{BE}$  of transistors  $Q_1$  and  $Q_2$ , which are operated at different current densities, to achieve a zero temperature coefficient reference voltage  $V_{ref}$  across points 20 and 28. The base-to-emitter voltage  $V_{BE}$  for transistor Q3 is given by

$V_{\mathbf{g}_0}$  is the extrapolated energy band-gap voltage of the semiconductor material at absolute zero (about 1.205 volts), q is the charge of an electron,

n is a constant dependent on the type of transistor (about 1.5 for IC transistors),

k is Boltzmann's constant,

T is absolute temperature,

$I_C$  is collector current, and  $V_{BE_0}$  is the base-to-emitter voltage at  $T_0$  and  $I_{C_0}$ .

The base-to-emitter differential  $\Delta V_{BE}$  between transistors Q1 and Q2 which are operated at different current densities is given by

$$(5) \qquad \Delta V_{BE} = (kT/q) \ln(J_1 J_2)$$

where J is current density.

Since transistors Q1 and Q2 are operated at different current densities, the voltage drop across resistor 30 is proportional to the base-to-emitter differential  $\Delta V_{BE}$ , and if the current gains 75 of the transistors are high, then the voltage drop across resistor 24 is also proportional to  $\Delta V_{BE}$ . Consequently, the volt4

age V<sub>ref</sub> appearing across terminals 16 and 18 (between circuit points 20 and 28) can be expressed as the sum of the voltage drop across resistor 24 (or a voltage proportional thereto, i.e.,  $\Delta V_{BE}$ ) and the voltage drop  $(V_{BE})$  across the base-to-emitter junction of transistor Q3. Thus, by adding equation 4 (with the last two terms deleted since they are insignificant) to equation 5,  $V_{ref}$  can be expressed as:

$$_{10}\ V_{\rm ref} \! = \! V_{\rm g_0}(1 \! - \! T/T_0) \! + \! V_{\rm BE_0}(T/T_0)$$

$$+\frac{R_{24}}{R_{24}}(kT/q)\ln{(J_1/J_2)}$$

$+\frac{R_{24}}{R_{30}}(kT/q)\ln{(J_1/J_2)}$  Differentiating with respect to temperature gives (7)

$$\delta V_{\rm ref}/\delta T = -V_{\rm g_0}/T_0 + V_{\rm BE_0}/T_0 + \frac{R_{24}}{R_{30}} \left(K/q\right) \ln\left(J_1/J_2\right)$$

For zero temperature coefficient, this expression is equal

to zero. Setting the equation equal to zero and substituting 20 into equation (6) gives

$$(8) V_{\text{ref}} = V_{g_0}$$

Hence, if the sum of  $V_{BE}$  and the voltage proportional to  $\Delta V_{BE}$  equal the energy band gap of the semiconductor material, a zero temperature coefficient reference voltage between terminals 20 and 28 results. More generally, the reference voltage  $V_{ref}$  can be expressed as

(9)

$$V_{\text{ref}} = a \left[ b V_{BE} + c \Delta V_{BE} \right] = a V_{y_0}$$

where a, b and c are constants.

As indicated above, current caused to flow through transistor  $Q_2$  will be proportional to the  $\Delta V_{BE}$  between transistors Q1 and q2 since the base-to-emitter circuits thereof are connected in parallel. If, for example, resistors 22 and 30 are of 600 ohms and resistor 24 is of 6,000 ohms transistor Q1 will run at 1 milliamp and transistor q2 will run at a current of 100 microamps. The  $\Delta V_{BE}$  is caused by the fact that transistor Q2 also has a certain base-to-emitter voltage, but since the resistor 30 is provided in its emitter circuit its base-to-emitter voltage  $V_{BE}$  is less than that of transistor  $Q_1$  by an amount determined by the voltage drop across the resistor 30.

When two transistors such as  $Q_{1 \text{ and } Q_2}$  are used in this configuration, a  $\Delta V_{BE}$  is generated between them which, at room temperature, is approximately 60 millivolts for a 10-1 current difference through the respective transistors. Transistor Q2 then has 60 millivolts less  $V_{BE}$  than transistor  $Q_1$  and this 60 millivolts thus appears across resistor 30. Since the  $\Delta V_{BE}$ between transistors Q1 and Q2 has a positive temperature coefficient, the voltage across resistor 30 increases with temperature at a rate which is directly proportional to absolute temperature and is quite linear. The collector current of transistor  $Q_2$  is approximately equal to its emitter current if the  $\beta$  of the the transistor is high. Thus, the voltage produced across resistor 24 is also directly proportional to temperature and increases therewith.

For changes of current in transistor Q1, the collector current of transistor Q2 varies as the log of that change so as to produce an attenuation of current change between transistors  $Q_1$  and  $Q_2$ . For example, this means that if the current through transistor Q1 changes by a factor of 2, the current through transistor Q<sub>2</sub> will change by only a factor of 0.3. Thus, to the 65 first approximation, the current through transistor Q2 is relatively well stabilized against initial current variations in transistor O1.

Transistor Q<sub>3</sub> is connected directly across the circuit points 20 and 28 with its base coupled to the collector of Q2. Since 70 the  $V_{BE}$  of  $Q_3$  decreases as temperature increases, and a feedback loop is formed from the collector of Q2 back through resistor 30 and down to its base, a constant current applied at point 20 by means of the source 34, causes the base-to-emitter voltage of transistor Q3 to change only with temperature because its collector current is constant. The collector voltage of transistor Q<sub>3</sub> is equal to its base-to-emitter voltage plus the voltage drop across resistor 24 caused by the collector current

6

of transistor Q2. By appropriately selecting the value of resistor 24 a net zero temperature coefficient can be obtained for the voltage across points 20 and 28. In other words, the negative coefficient voltage across the base-to-emitter of transistor Q<sub>3</sub> and the positive coefficient voltage due to the current from transistor Q2 across resistance 24 thus balance each other to provide a net zero temperature coefficient. This relationship is explained by the equations above. The reference voltage V<sub>ref</sub> for the illustrated preferred embodiment is 1.205 volts.

Equation (7) sets the voltage relationships for zero temperature coefficients. However, the relationship remains if both sides are multiplied by a constant. Understandably, a zero temperature coefficient reference can also be made at twice  $V_{B_0}$  by using two series transistors for  $V_{BE}$  and a proportionately larger amount of  $\Delta V_{BE}$ . The output voltage of the reference is not limited to integer values of  $V_{\alpha_0}$ . By using fractional parts of  $V_{BE}$  with a proportional part of  $\Delta V_{BE}$ , any output voltage is obtainable.

The operational amplifier 12 is connected as a voltage follower having the characteristics that the input voltage and output voltage are exactly the same. Since the emitter of transistor Q<sub>3</sub> is connected to the input terminal 36 of op-amp 12, and the collector thereof is connected to the input ter- 25 minal 38 through the resistor R, the collector of transistor  $Q_3$ is going to be 1.205 volts above the output of the op-amp 12 no matter what the output is since the output terminal 2 is coupled directly to the input 36 by the line 40. The amplifier 12 is a high-gain amplifier and has a high accuracy in terms of 30 keeping its input and output voltages the same.

In the voltage follower configuration, the voltage between the plus and minus input must always be nearly zero. Therefore, by connecting the resistor R between the circuit point 20 voltage impressed across the resistor R. Thus, the current flowing from the voltage reference 14 into the terminal 3 must necessarily be equal to 1.205 volts divided by the resistance r; and, since the plus input of the voltage follower 12 draws a negligible amount of current, it can be said that all of the current flowing through resistor R also flows through the variable resistance 15 to ground. The variable resistance 15 thereby serves as an adjustment resistor for controlling the voltage appearing at the output terminal 2.

For example, with a constant 100 microamps flowing through resistor R, there will necessarily be 100 microamps flowing through the adjustment resistor 15 to ground. The voltage at the plus input 38 of the voltage follower 12 will thus be a function of the resistance of resistor 15 and the 100 microamps current. And since the 100-microamps current is constant, the voltage at the plus input will be directly related to the resistance of resistor 15. Moreover, since the voltage at output terminal 2 is directly related to the input voltage applied at terminal 3, it will be seen that the voltage applied across the entire regulator is equal to  $V_{in}-V_{out}$  and is in no way referenced to ground. It is thus a floating voltage regulator and is capable of regulating any voltage so long as  $V_{in}-V_{out}$  is less than the breakdown potential of the circuit elements.

tion of the regulator is that a constant current is provided which is directed through an adjustment resistor in order to obtain the desired regulated voltage and the only requirement insofar as what voltage may be regulated at output terminal 2, is that the difference between the output voltage and the un- 65 regulated input voltage must not exceed the voltage handling capabilities of the regulator circuit 10.

Turning now to Figure 3 of the drawing, a simplified schematic diagram of a preferred embodiment of the invention is illustrated. It will be noted, however, that in the voltage reference circuit 11 an additional transistor Q4 has been connected across circuit points 20 and 28 and a resistor 27 has been added to the collector circuit of transistor Q<sub>3</sub>.

Since the reference voltage at circuit point 20 is proportional to the base-to-emitter voltage of transistor Q<sub>3</sub> plus the voltage across resistor 27, the base-to-emitter voltage of transistor Q<sub>3</sub> should be 5, as as possible. One way of doing this to put in the extra transistor Q4 which absorbs current changes from the current source 34, and since its base current changes a small friction of the amount of any current change (i.e., the base current change of transistor Q4 is equal to the change in current to Q4 divided by the transistor Q3 sees a very small change in collector current. Transistor Q4 increases the gain of the reference against changes in current flow. Although it is not necessary to the invention, one would normally add such a transistor in practice in order to make the reference more stable with respect to input voltage changes. As in the Figure 2 embodiment, the resistor R sets the value of the current flowing into the adjustment terminal 3.

The voltage follower 12 is made up of three stages, namely a first differential amplifier 50, a second differential amplifier 52 and an emitter follower 54. The amplifier 50 is comprised of the transistors Q5, Q6, Q7 and Q8 along with the resistors 56 and 58. The base of transistor Q<sub>5</sub> forms the positive input to op-amp 12 and is coupled to the adjustment terminal 3. The base of transistor Q6 forms a negative input to op-amp 12 and is coupled to the lead 29 which is common with the output terminal 2 and circuit point 28. Current sources 60 and 62 are provided as indicated for energizing the amplifier. A voltage difference across the collectors of transistor Q<sub>7</sub> and Q<sub>8</sub> (i.e., across resistors 56 and 58) is proportional to the difference in voltage between the base of transistor Q5 and the base of transistor Q<sub>6</sub>. The circuit is balanced if the inputs to transistor Q5 and Q6 are the same and no difference voltage is generated between the collector of transistors q<sub>7</sub> and q<sub>8</sub>. Because of the resistors 56 and 58, the amplifier 50 forms a differential gain stage the output of which is coupled into the differential amplifier 52.

The base of transistor Q<sub>9</sub> is coupled to the collector of and input terminal 3, there must necessarily be a constant 35 transistor  $Q_7$  and the base of transistor  $Q_{10}$  is coupled to the collector of transistor Q<sub>8</sub> so that the second differential amplifier 52 is also balanced when the collector voltages of transistors Q7 and Q8 are the same. In other words, the amplifier 52 responds to voltage differentials across the collectors of transistors Q7 and Q8. A current source 64 couples the collector of transistor Q<sub>10</sub> to the input terminal and a resistor 66 couples the emitter of transistors Q9 and Q10 to the common line

> The output of amplifier 52 is taken at the collector of transistor Q10 and feeds the emitter follower circuit 54 which is comprised of the transistors Q11 and Q12, and which provides current gain in the output for the circuit. Since the emitter of Q<sub>12</sub> is tied to the common line 29, it will be noted that the output thereof is coupled back to the base of transistor Q6 to provide negative feedback for the circuit.

The operation of the circuit can be explained as follows: Suppose the voltage at the base of transistor Q5 is caused to go positive as would be the case if one were to increase the resistance of resistor 15. This would reduce the base-to-emitter voltage of transistor Q5 causing it to turn off. The turning off of transistor Q5 accordingly reduces the base-to-emitter voltage of transistor Q<sub>7</sub> causing it to turn off. When this happens, the differential amplifier Q<sub>8</sub> turns on. Since Q<sub>7</sub> is turning off, As will be understood from the above, the basis for opera- 60 its voltage will rise and the voltage at the collector of transistor Q<sub>8</sub> will decrease since it is turning on. The resultant current flow through resistors 56 and 58 will then provide a differential voltage at the bases of transistors Q9 and Q10 which tends to turn transistor Q10 off causing more current from the current source 64 to go to the base of transistor Q11 turning the emitter follower 54 harder on so as to bring the potential of  $V_{out}$  at terminal 2 up.

Since terminal 2 is connected through common lead 29 to the base of transistor Q6, a servo loop is completed which terminates the increase in potential at terminal 2 when the base of transistor Q6 reaches the same potential as the base of transistor Q<sub>5</sub>. This is to say that the output of emitter follower 54 acts to turn off the source which drives it so as to effectively keep the potential at the output terminal 2 exactly equal to the potential at terminal 3. Although the differential stage 52 is added to increase the gain and provide greater accuracy in

the voltage follower 54, as well as providing greater isolation between the adjustment and the output, it could actually be eliminated, in which case the base of transistor Q11 would be coupled to the collector of transistor Q7. The preferred embodiment however, uses both stages for the reasons described 5 above.

This circuit can regulate any voltages from 0 volts upwards since the regulator is completely floating and sees only the difference in potential across terminals 1 and 2. As mentioned above, the only requirement is that the difference between the  $\ ^{10}$ voltage applied to the input terminal 1 and the output voltage at output terminal 2 be kept less than the breakdown potential of the transistors in the circuit. Appropriate modifications of the transistors  $Q_{11}$  and  $Q_{12}$  can be made to accommodate the various load requirements which might be encountered. In other words, the circuit as described will regulate very high voltages as well as very low voltages. For instance, a 300-volt output at terminal 2 could be regulated with the circuit described. However, since the breakdown potential of the in- 20 tegrated circuit transistors in the circuit is about 50 volts, this would mean that the maximum input voltage would have to be less than 350 volts in order to prevent damage to the circuit.

Turning now to Figure 4 of the drawing, a current regulator is shown which utilizes the same three-terminal circuit as is 25 shown in the voltage regulator embodiments above, except that the bottom side of the adjustment resistor 15 is no longer connected to ground but is instead connected to an external output terminal 4 which is connected to the output terminal 2 by a resistor 70. A current flowing through resistor 15 to ter- 30 minal 4 and generating a 1-volt drop thereacross causes the positive input 38 of the amplifier 12 to see a voltage which is due to the resistance 15. However, since the potentials at the input and output of amplifier 12 must be identical, there must be a one volt rise across resistor 70 from terminal 4 to terminal 2 so as to cancel any difference in potential between terminals 2 and 3. Therefore, the current flowing through resistor 70 and available at the output terminal 4 will be independent of the load receiving the current flow but will be directly propor- 40 tional to the resistive value of resistor 15.

Whereas, previous regulators have required that zener diodes be used in the voltage reference, the present invention requires no zener diodes whatsoever and all active comtransistors. In addition, the fact that the present invention utilizes transistors which are well behaved and understood, means that the invention can be designed to be quite stable and substantially less noisy than a zener diode circuit in terms of small have a noise level of less than 20 microvolts whereas most zener diode circuits have noise levels which exceed a millivolt. The regulator as shown is for positive voltages. For negative voltages, complementary transistors can be used in a similar

After having read the above disclosure, it is contemplated that many alterations and modifications of the invention will be apparent to those skilled in the art. It is therefore to be understood that this is a description of a preferred embodiment and is made solely for purposes of illustration rather than limitation. Accordingly, it is intended that the appended claims be interpreted as covering all modifications which fall within the true spirit and scope of the invention.

What is claimed is:

1. An electrical regulator circuit, comprising:

an input terminal for receiving an unregulated input voltage;

an output terminal;

an adjustment terminal:

means for developing a reference voltage having a substantially zero temperature coefficient and including,

- a first terminal coupled to said input terminal,

- a second terminal,

- a third terminal,

- a first transistor having a first emitter coupled to said second terminal, a first collector coupled to said third

terminal, and a first base coupled to said first collector, a second transistor having a second base coupled to said first collector, a second collector coupled to said third terminal, and a second emitter coupled to said second terminal, said first and second transistors having different current densities  $J_1$  and  $J_2$  respectively, whereby the base-to-emitter differential  $\Delta V_{BE}$  therebetween has a positive temperature coefficient and may be expressed as

$\Delta V_{BE} = (kT/q) \ln(J_1 J_2)$

where k is Boltzmann's constant, T is absolute temperature, and q is the charge on an electron, and

circuit means having a negative temperature coefficient operatively combined with said first and second transistors to develop said reference voltage between said second and third terminals,

a resistive impedance coupling said third terminal to said adjustment terminal; and

voltage follower means operatively coupling said input terminal to said output terminal and having a first input terminal coupled to said second terminal and a second input terminal coupled to said adjustment terminal, said voltage follower means being responsive to a voltage developed at said adjustment terminal when said adjustment terminal is resistively coupled to a circuit ground and said unregulated input voltage is applied between said input terminal and said circuit ground, said voltage follower means being operative to develop a regulated voltage at said output terminal.

2. An electrical regulator circuit as recited in claim 1 wherein said circuit means includes a third transistor having a third base coupled to said second collector, a third emitter coupled to said second terminal and a third collector coupled to said third terminal, said negative temperature coefficient being a function of the base-to-emitter voltage  $V_{BE}$  of said third transistor.

3. An electrical regulator circuit as recited in claim 2 wherein said reference voltage may be expressed as

$$V_{ref} = a(bV_{BE} + c\Delta V_{BE})$$

where a, b and c are constants.

4. An electrical regulator circuit as recited in claim 2 and ponents may be comprised of simple integrated circuit 45 further comprising a fourth transistor having a fourth base coupled to said third collector, a fourth emitter coupled to said third terminal, and a fourth collector coupled to said second terminal.

5. An electrical regulator circuit as recited in claim 1 variations in voltage. For example, a circuit of this type will 50 wherein said voltage follower means includes, a first differential amplifier responsive to the voltage developed between said second terminal and said adjustment terminal and operative to develop a control signal, and an emitter follower amplifier responsive to said control signal and operative to control current flow between said input terminal and said output terminal thereby developing a regulated voltage at said output terminal.

6. An electrical regulator circuit as recited in claim 5 and further comprising a second differential amplifier operatively coupling said first differential amplifier to said emitter follower amplifier

7. An electrical regulator circuit as recited in claim 1 and further comprising an external terminal, a variable resistive 65 impedance coupling said adjustment terminal to said external terminal, and an external resistive impedance coupling said external terminal to said output terminal whereby a regulated current is provided at said external terminal.

8. An electrical regulator circuit as recited in claim 1 and 70 further comprising a variable resistive impedance for coupling said adjustment terminal to the circuit ground, the regulated voltage being selectable by varying said variable resistive impedance.

9. A voltage reference circuit, comprising:

a first terminal and a second terminal;

75

first circuit means for developing a first voltage which increases with temperature and including,

- a first transistor having a first emitter coupled to said second terminal, a first collector coupled to said first terminal, and a first base coupled to said first collector, and

- a second transistor having a second base coupled to said 5 first collector, a second emitter coupled to said second terminal, and a second collector coupled to said first terminal; and

- second circuit means for developing a second voltage which decreases with temperature and including, a third 10 transistor having a third base coupled to said second collector, a third emitter coupled to said second terminal and a third collector coupled to said first terminal, said first and second voltages being combined to develop a reference voltage across said first and second terminals.

- 10. A voltage reference circuit as recited in claim 9 wherein said reference voltage may be expressed as

$V_{ref} = a(bV_{BE} + c\Delta V_{BE})$

#### where

a, b and c are constants,

- $V_{BE}$  is the base-to-emitter voltage of said third transistor, and

- $\Delta V_{BE}$  is the base-to-emitter differential between said first and second transistors.

- 11. A voltage reference as recited in claim 9 and further 25 comprising a fourth transistor having a fourth base coupled to said third collector, a fourth emitter coupled to said first terminal, and a fourth collector coupled to said second terminal.

- An electrical regulator circuit, comprising:

an input terminal for receiving an unregulated input voltage;

an output terminal;

an adjustment terminal;

means for developing a reference voltage having a substantially zero temperature coefficient and including,

- a first terminal coupled to said input terminal,

- a second terminal,

- a third terminal,

- a first transistor having a first emitter coupled to said second terminal, a first collector coupled to said third terminal, and a first base coupled to said first collector,

- a second transistor having a second base coupled to said first collector, a second collector coupled to said third terminal, and a second emitter coupled to said second terminal, and

- circuit means having a negative temperature coefficient operatively combined with said first and second transistors to develop said reference voltage between said second and third terminals,

- a resistive impedance coupling said third terminal to said adjustment terminal; and

- voltage follower means operatively coupling said input terminal to said output terminal and having a first input terminal coupled to said second terminal and a second input terminal coupled to said adjustment terminal, said voltage follower means being responsive to a voltage developed at said adjustment terminal when said adjustment terminal is resistively coupled to a circuit ground and said unregulated input voltage is applied between said input terminal and said circuit ground, said voltage follower means being operative to develop a regulated voltage at said output terminal.

35

20

-

40

45

50

55

60

65

70