(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2015-56549

(P2015-56549A)

(43) 公開日 平成27年3月23日(2015.3.23)

(51) Int.Cl.

H01L 29/786 (2006.01)

H01L 21/3065 (2006.01)

F 1

H01L 29/78

H01L 29/78

H01L 21/302

テーマコード(参考)

5 F 004

5 F 110

審査請求 未請求 請求項の数 6 O L (全 10 頁)

(21) 出願番号

(22) 出願日特願2013-189652 (P2013-189652)

平成25年9月12日 (2013.9.12)(71) 出願人 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100112210

弁理士 稲葉 忠彦

(74) 代理人 100108431

弁理士 村上 加奈子

(74) 代理人 100153176

弁理士 松井 重明

(74) 代理人 100109612

弁理士 倉谷 泰孝

(72) 発明者 園田 武司

熊本県合志市御代志997番地 メルコ・

ディスプレイ・テクノロジー株式会社内

最終頁に続く

(54) 【発明の名称】薄膜トランジスタおよびその製造方法

(57) 【要約】 (修正有)

【課題】半導体層を覆う配線の断線とリーク電流の発生とを抑制し、TFT基板の信頼性と製造歩留りを向上させる。

【解決手段】 - Si層を2段テーパー形状に加工する。これにより、-Si(i)層のソース・ドレインとの接触面積が小さくなり、リーク電流の発生を抑えることができ、かつ、-Si(n)層のテーパー角度を小さくすることでソース・ドレイン層のカバレッジにも問題がなく、断線、高抵抗化の不良発生が抑えられる。ひいては、ムラ等の表示異常がなく安定した表示装置を提供することができる。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

基板上に形成されたゲート電極と、前記ゲート電極を覆うゲート絶縁膜と、

前記ゲート絶縁膜上に形成された半導体層と、

前記半導体層上に形成されたオームикコンタクト層と、

前記オームикコンタクト層上に形成されて対向するソース電極とドレイン電極とを有し

、

前記ソース電極とドレイン電極の少なくとも一方は、前記半導体層のパターン端部と前記

オームикコンタクト層のパターン端部を覆い、

前記半導体膜のパターン端部のテーパー角が前記オームикコンタクト層のテーパー角よ

りも大きいことを特徴とする薄膜トランジスタ。

10

**【請求項 2】**

前記オームикコンタクト層のパターン端部が丸みを帯びていることを特徴とする請求項

1に記載の薄膜トランジスタ。

**【請求項 3】**

基板上にゲート電極を形成する工程と、

前記ゲート電極を覆うようにしてゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上に半導体層とオームикコンタクト層とを成膜した後にパターン端部

がテーパー形状を有するようにエッチングを行いパターニング形成する工程と、

前記オームикコンタクト層の上層に導電膜を成膜して、少なくとも前記テーパー形状を

覆うようにしてパターニングすることによりソース電極とドレイン電極とを形成する工程

と、

20

を備えており、

前記半導体膜と前記オームикコンタクト層とのパターニングの際のエッチングにおいて

、前記半導体膜のパターン端部のテーパー角が前記オームикコンタクト層のパターン端部

のテーパー角よりも大きくなるように加工することを特徴とする薄膜トランジスタの製

造方法。

**【請求項 4】**

前記半導体膜と前記オームикコンタクト層とのパターニングの際のエッチングは 2 段階

で行い、

30

第 1 エッチング工程においては、フッ素原子と塩素原子と酸素ガスを含む混合ガスを用い

、

第 2 エッチング工程においては、酸素ガスを含まずにフッ素原子と塩素原子を含んだガス

を用いることを特徴とする請求項 3 に記載の薄膜トランジスタの製造方法。

**【請求項 5】**

前記半導体膜と前記オームикコンタクト層とのパターニングの際のエッチングにおいて

前記第 2 エッチング工程の後にアッシングを行った後に、

再度、前記第 2 エッチング工程を行うことを特徴とする請求項 4 に記載の薄膜トランジス

タの製造方法。

**【請求項 6】**

前記第 1 エッチング工程には RIE モードを用い、前記第 2 エッチング工程には PE モー

ドを用いることを特徴とする請求項 4 に記載の薄膜トランジスタの製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、液晶表示装置やエレクトロルミネセンス表示装置等に用いられる薄膜トランジ

スタに関する。

**【背景技術】****【0002】**

薄膜トランジスタ (Thin-Film Transistor、以下、TFT と記す) は、スイッチング素

40

50

子のひとつであり、たとえば液晶表示装置やエレクトロルミネセンス表示装置等のアレイ基板上にマトリクス状に複数形成されている。TFTの構造にはいくつかの種類があるが、半導体膜を用いたMOS型であってゲートが最下層にある逆スタガ型が一般的であり、その中でも半導体膜として非晶質シリコン（以下、-Siと記すこともある）を用いたTFTが多数量産されている。

#### 【0003】

-Si層をパターニングする際に、-Si層パターンのエッヂ部の仕上がり断面形状を順テーパー形状にすることにより、その上層に形成するソース・ドレン電極配線層の被覆性（カバレッジ）を向上させ、ソース・ドレン電極配線層の断線や電気的抵抗の増大を防止する方法が開示されている。（特許文献1）

10

#### 【先行技術文献】

#### 【特許文献】

#### 【0004】

【特許文献1】特開平6-196451号公報（図6）

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0005】

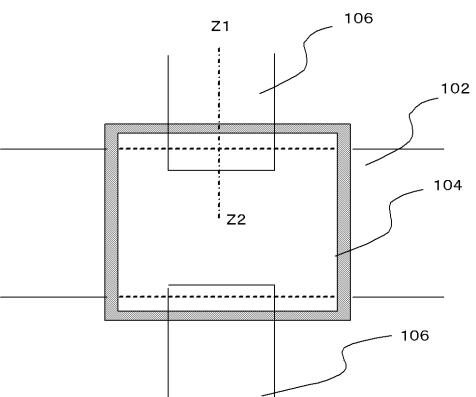

図8に、逆スタガ型TFTの平面配置の一例を示す。また、図9は、図8中においてZ1-Z2として示す部分の断面を示す図であり、バックライト等の光源からの光照射を受けている状況も図示している図である。

20

#### 【0006】

図8、9において、ゲート電極102上を覆うゲート絶縁膜103上に半導体層である-Si層104とオームックコンタクト層105とが形成されている。-Si層104とオームックコンタクト層105上にはその両端を覆うようにしてソース・ドレン電極106が形成されている。ここで、ソース・ドレン電極106と-Si層104とが接触する領域をA1とし、領域A1を上面視から見た際の幅に相当する長さを底辺距離B1とする。光源BLからはゲート絶縁膜103、-Si層104、ソース・ドレン電極106の順で光が到達するように光が照射される。

#### 【0007】

特許文献1に記載された技術においては、-Si層104のエッヂ部の断面形状をテーパー角度11を有する順テーパー形状にすることにより、上層であるソース・ドレン電極106のカバレッジを向上させる効果を奏しているが、そのテーパー角度についてはさらに詳細な検討が必要となる。

30

#### 【0008】

具体的には、-Si層エッヂ部の断面形状のテーパー角度11が小さくなると、-Si層とソース・ドレン電極との接触領域A1の面積と底辺距離B1とが大きくなる。底辺距離B1が大きくなることで、光源BLからの光エネルギーを受ける面積が大きくなり光リーク電流が増大し、さらに接触領域A1の面積が大きいことで、ソース・ドレン電極と-Si層との間の接合リーク電流が増大することとなる。

#### 【0009】

一方、逆にテーパー角度11を大きくすることで、A1とB1とを小さくする方法があるが、これについてはすでに記載したとおり、上層であるソース・ドレン層のカバレッジが悪くなるため、ソース・ドレンの断線や高抵抗化という問題が生じることとなる。本発明はこのような問題を解消するためのものである。

40

#### 【課題を解決するための手段】

#### 【0010】

本発明においては、基板上に形成されたゲート電極と、前記ゲート電極を覆うゲート絶縁膜と、前記ゲート絶縁膜上に形成された半導体層と、前記半導体層上に形成されたオームックコンタクト層と、前記オームックコンタクト層上に形成されて対向するソース電極とドレン電極とを有し、前記ソース電極とドレン電極の少なくとも一方は、前記半導

50

体層のパターン端部と前記オーミックコンタクト層のパターン端部を覆い、前記半導体膜のパターン端部のテーパー角が前記オーミックコンタクト層のテーパー角よりも大きいことを特徴としている。

**【発明の効果】**

**【0011】**

半導体層を覆う配線の断線とリーク電流の発生とを抑制し、TFT基板の信頼性と製造歩留りを向上させる。

**【図面の簡単な説明】**

**【0012】**

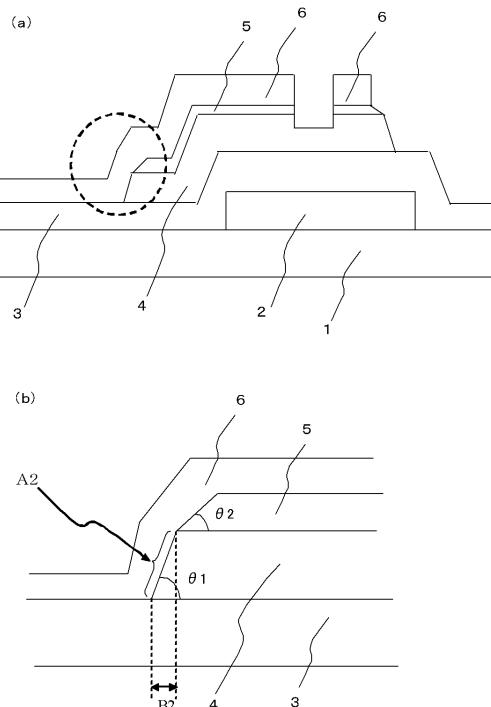

**【図1】TFTの断面図と、端面の拡大図**

10

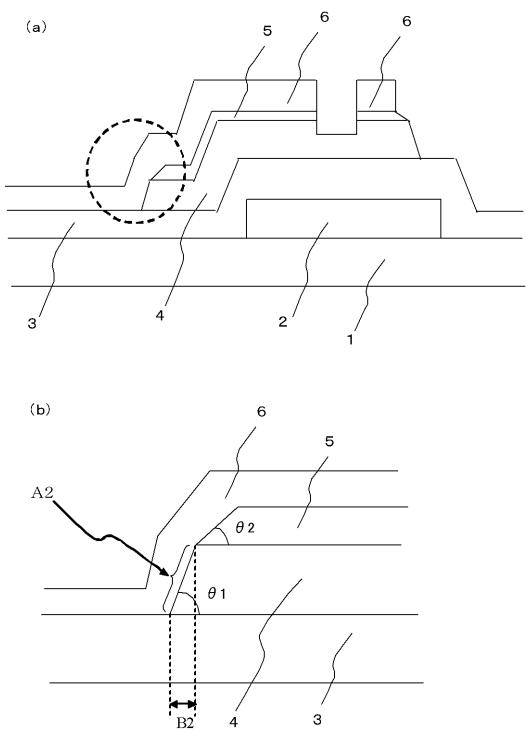

**【図2】実施の形態1のドライエッチング方法に用いる装置の模式説明図**

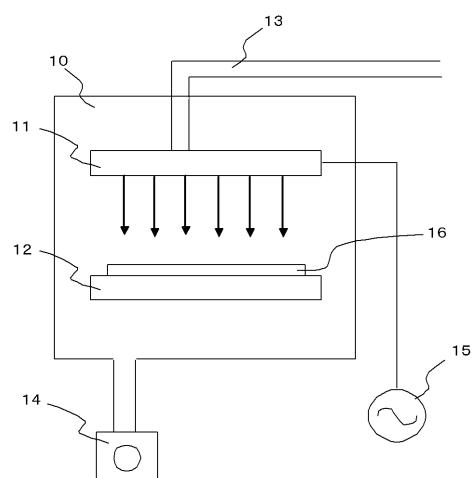

**【図3】実施の形態1に係るTFTのエッチング工程図**

**【図4】実施の形態2に係るTFTのエッチング工程図**

**【図5】実施の形態2に係るTFTのエッチング工程図**

**【図6】実施の形態3のドライエッチング方法に用いる装置の模式説明図**

**【図7】実施の形態4に係るFFSの半導体層の断面図**

**【図8】従来例に係るTFTの平面配置図**

**【図9】従来例に係るTFTの-Si形状**

**【発明を実施するための形態】**

**【0013】**

20

実施の形態1.

**< TFTの構造 >**

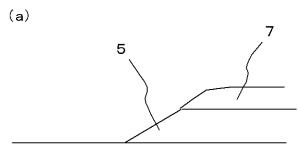

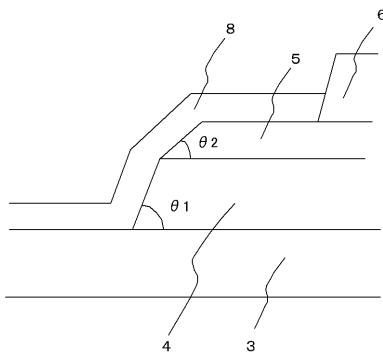

図1(a)は本発明に係るTFTの断面図であり、図1(b)は図1(a)の一部を拡大した図である。図1(a)において、基板1上にゲート電極2が形成され、ゲート電極2を覆うようにしてゲート絶縁膜3が形成されている。ゲート絶縁膜3上に-Si等からなる半導体層4とオーミックコンタクト層5が形成され、その上層にソース・ドレイン電極6が形成されている。なお、ソース電極とドレイン電極との間のオーミックコンタクト層5は除去されている。

**【0014】**

次に、破線の円で囲んだ箇所について図1(b)を用いて説明する。図1(b)において、半導体層4のパターン端部がゲート絶縁膜3と接する箇所において、半導体層4はテーパー角1のテーパー形状になるように形成されている。同様に、オーミックコンタクト層5のパターン端部が下層の半導体層4と接する箇所において、オーミックコンタクト層5はテーパー角2のテーパー形状になるように形成されている。

30

**【0015】**

また、ソース・ドレイン電極6と半導体層4とがテーパー形状において面として接触する領域をA2とし、領域A2を上面視から見た際の幅に相当する長さを底辺距離B2とする。領域A2は言いかえれば、半導体層4のパターンの端部である。本発明に係るTFTにおいては、テーパー角1よりもテーパー角2を小さくすることを特徴としている。たとえば、テーパー角1を65°～75°にし、テーパー角2を30°～45°の形状にしてもいい。

40

**【0016】**

ここで、半導体層4の領域A2におけるテーパー角1は、図7で示したテーパー角1よりも大きくすることができますが、その分、接触領域A2の面積やドレイン電極6と接触する底辺距離B2を図7に示す形態よりも小さくできる。そのため、ソース・ドレイン電極と半導体層との間の接合リーク電流や、光リーク電流を減らすことができる。

**【0017】**

一方、このようにテーパー角1を大きくするとドレイン電極6の被覆性は悪化するが、2の角度を1よりも小さくしているため、被覆性の悪化は最小限に抑制される。これにより、接合リーク電流や光リーク電流を低減でき、かつ被覆性(カバレッジ)にも問

50

題がなく、断線、高抵抗化の不良発生が抑えられる。また、2を低くするとドレイン電極6とオーミックコンタクト層5との接合面積が増えるので、ソース・ドレイン電極と半導体層との間の電気的な抵抗を下げることができる。

#### 【0018】

##### < TFT の製造方法 >

次に、以上説明したTFTの構造に関する製造方法について説明する。ガラス等の透明絶縁材料からなる基板1上に、Al、Mo、Cr、Cu等の金属薄膜を成膜し、パターニングすることによりゲート電極2を形成する。ゲート電極2上にプラズマCVD等の方法によりSiNやSiO<sub>2</sub>等のゲート絶縁膜3と-n-Si(i)等の半導体層4と-n-Siにリン等の元素を添加した-n-Si(n)であるオーミックコンタクト層5を成膜した後、半導体層4とオーミックコンタクト層5とをパターニングする。半導体層として-n-Siを用いた場合、パターニングの際にはエッチングを行うが、一般にドライエッチング法が用いられる。ここで、ドライエッチング法の詳細については、本発明の特徴であるテーパー形状との関連があるので後に詳細に説明する。

#### 【0019】

次に、オーミックコンタクト層5上にAl、Mo、Cr、Cu等の金属薄膜を成膜し、パターニングすることによりソース・ドレイン電極6を形成する。その後、ソース・ドレイン電極6で被覆されていないオーミックコンタクト層5を除去する。このようにして形成されたTFTに適宜、画素電極(図示せず)をドレイン電極6に接続した画素素子をマトリクス状に配置したうえで、電界により光学的な変化を生じる液晶やELのような材料を介して対向基板と接合することにより、液晶表示装置やエレクトロルミネセンス表示装置を形成する。

#### 【0020】

##### < ドライエッチング方法 >

本実施の形態に係るTFTの形成において、半導体層とオーミックコンタクト層とのパターニングに用いるドライエッチング法とパターニングのテーパー形状とを関連させながら以下説明する。

#### 【0021】

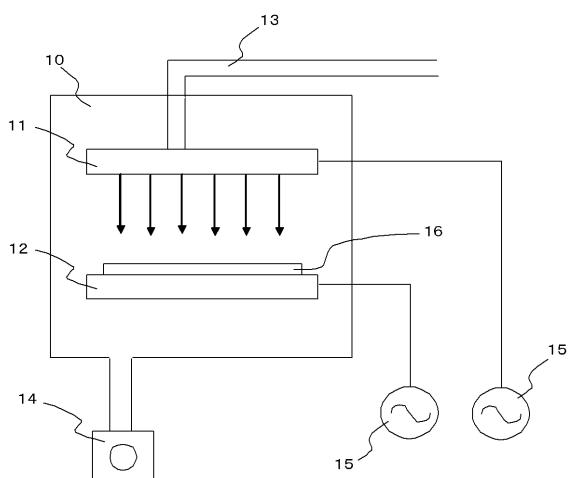

まず、図2に、エッチングを行う平行平板型反応性イオンエッチング装置の主要部を模式的に示した断面図を示す。図2において、10はエッチング室、11は上部電極、12は基板ステージとなる下部電極、13はエッチングガスの導入管、14は真空ポンプ、15は高周波電源(13.56MHz)、16はエッチング処理される基板を示す。

#### 【0022】

エッチングの方法について説明する。まず、処理される基板16がエッチング室10内に搬送されて下部電極12上に配置される。ついで、真空ポンプ14により10<sup>-3</sup>Pa以下の圧力に排気されているエッチング室10内にエッチングガスが導入される。エッチングガスはエッチング室10外に設置したガス供給系(図示せず)より流量調節器(図示せず)を通じ、導入管13を通ってから上部電極11に設けられた多数の微小な穴を介してシャワー状にエッチング室10内に拡散して導入される。

#### 【0023】

その後、高周波電源15によって上部電極11と下部電極12との間に周波数13.56MHzの交流電圧が印加されてプラズマが生じ、基板16上の膜がエッチングされる。なお、上部電極11と下部電極12は基板16の温度上昇を防止するために水冷等で冷却が可能な構造となっている。

#### 【0024】

以上説明したようなドライエッチング装置を用いて、本実施の形態では以下説明するように2段階のエッチングを行った。まず、第1エッチング工程のパラメータについて説明をする。ここで用いた混合ガスは、塩素原子とフッ素原子と酸素原子を含むガスである。具体的には、SF<sub>6</sub>:240sccm、HCl:210sccm、O<sub>2</sub>(酸素):65sccmの混合ガスであり、ガス圧力は30Pa、高周波電力が800Wである。

10

20

30

40

50

## 【0025】

次に、第2エッティング工程のパラメータについて説明をする。ここで用いた混合ガスは、塩素原子とフッ素原子を含むガスである。具体的には、SF<sub>6</sub> : 240 sccm、HC1 : 210 sccmの混合ガスであり、ガス圧力は30Pa、高周波電力が800Wである。

## 【0026】

エッティングは下部電極12の上に基板16を載置し、上記混合ガスの高周波プラズマ中で実施した。また、第1エッティング工程と第2エッティング工程との間にはエッティングガスの供給を停止して、エッティング室10内を真空排気する時間を適宜設けている。

## 【0027】

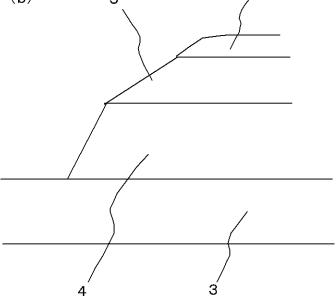

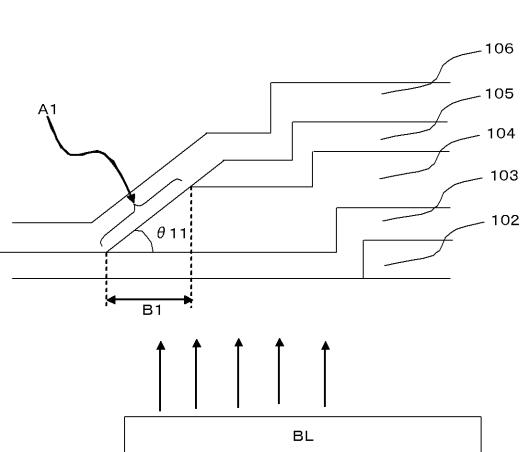

このような条件でエッティングした場合の半導体層4およびオーミックコンタクト層5のエッティング加工断面を図3(a)、図3(b)に示す。図3(a)は、第1エッティング工程のエッティングを行った後の半導体層とオーミックコンタクト層の断面形状である。図3(b)は、第2エッティング工程のエッティングを行った後の半導体層とオーミックコンタクト層の断面形状である。

## 【0028】

図3(a)においては、半導体層4の上層のオーミックコンタクト層5がレジスト7をエッティングマスクとしてエッティングされた後の断面を示している。第1エッティング工程で用いるエッティング用の混合ガスにはO<sub>2</sub>が含まれているため、オーミックコンタクト層5をエッティングする間にレジスト7もエッティングされることによりレジスト7の端部が後退し、オーミックコンタクト層5の端部のテーパー角度は比較的低く加工される。

## 【0029】

一方、図3(b)においては、レジスト7をエッティングマスクとして半導体層4をエッティングした状況を示している。第2エッティング工程で使用する混合ガスにおけるO<sub>2</sub>の流量や分圧は、第1エッティング工程のそれよりも低いほうが望ましく、O<sub>2</sub>を含まないのがなおよい。この場合、第2エッティング工程においては、第1エッティング工程に比べ、レジストに対するエッティングレートは低くなる。そのため、第2エッティング工程のエッティングにおけるレジストの後退スピードも遅くなり、半導体層4は膜厚方向にエッティングされやすく、その結果、半導体層4の端部は高いテーパー角度で加工される。

## 【0030】

このように製造することにより図1で示したようなTFTが得られ、接合リーケ電流や光リーケ電流を低減でき、かつ被覆性(カバレッジ)にも問題がなく、断線、高抵抗化の不良発生が抑えられる。

## 【0031】

実施の形態2.

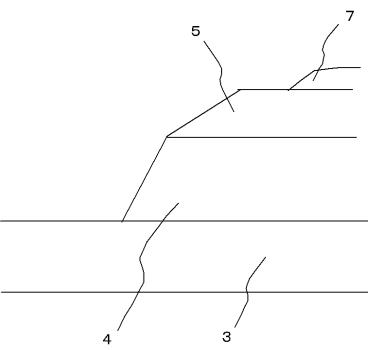

実施の形態1では、半導体層のテーパー角度よりもオーミックコンタクト層のテーパー角度を小さくしたが、さらに被覆性を高めたのが実施の形態2である。

## 【0032】

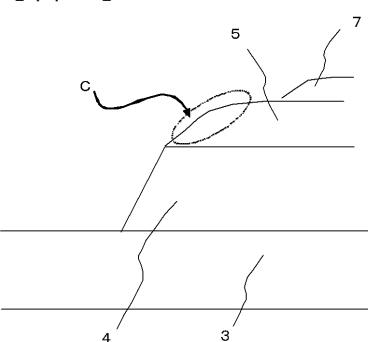

実施の形態2に係るTFTの半導体層の断面形状を図4に示す。

図4に示すように、オーミックコンタクト層5の端部Cに丸みを持たせることで、カバレッジが更に向上する。

## 【0033】

このような形状を実現するために、図3(b)において半導体層4のエッティングが完了した後、アッシング時間を通常より長めに実施する。かかるアッシングを行った後の断面図を図5に示す。図5において、オーミックコンタクト層5上のレジスト7のパターン端部は後退し、オーミックコンタクト層5が露出している。その後、再度、実施の形態1の第2エッティング工程を短時間行うことで、露出したオーミックコンタクト層5がエッティングされ、その結果オーミックコンタクト層5の端部Cが丸みを持つこととなる。

## 【0034】

実施の形態3.

10

20

30

40

50

実施の形態 1 ではドライエチング工程のエッチングモードを特定しなかったが、かかるドライエッチング工程では、反応性イオンエッチング( R I E )とプラズマエッチング( P E )を使い分けて半導体層を目的の形状にエッチングするのが実施の形態 3 に係る T F T の製造方法である。

#### 【 0 0 3 5 】

R I E はパターンが微細化したいときに、レジスト寸法通りにレジストよりも下層にある材料をエッチングするために用いられるエッチング方法であり、エッチングされた材料の断面形状は矩形に近い形状、つまりパターン端部のテーパー角度はほぼ 90° となる。

#### 【 0 0 3 6 】

一方、P E モードは R I E モードに比べると等方性の影響が大きいエッチング方法である。10

この二つのエッチング方法を組み合わせることで、本発明に係るエッチング断面形状を実現することができる。

#### 【 0 0 3 7 】

図 6 は、実施の形態 3 で使用するエッチング装置の主要部を模式的に示した断面図であり、平行平板型で上部電極 1 1 、下部電極 1 2 ともに高周波電源 1 5 と接続されているのが特徴である。それ以外の構造や付番については図 2 と同様であるので説明は省略する。

#### 【 0 0 3 8 】

まず第 1 エッチング工程を R I E モードで行い、図 3 ( a ) に示したような形状に加工する。その後、第 2 エッチング工程を P E モードで行うことで、図 3 ( b ) に示すようにテーパー角度が 1 > 2 となるような半導体層とオーミックコンタクト層の断面形状を形成できる。すなわち、このようにエッチングモードをエッチングの途中で変更しても実施の形態 1 と同様の効果を得ることができる。この製造方法は、R I E モードの異方性エッチングと P E モードの等方性を利用したものである。20

#### 【 0 0 3 9 】

なお、本実施の形態 3 におけるエッチング条件は、第 1 エッチング工程では R I E モードであり、ガス流量 : S F<sub>6</sub> : 9 0 s c c m 、 H C l : 5 0 0 s c c m 、 H e : 2 3 0 s c c m でガス圧力が 3 3 P a 、 R F パワーが 9 6 0 W である。第 2 エッチング工程では、P E モードであり、ガス流量が C F<sub>4</sub> : 3 0 0 s c c m 、 O<sub>2</sub> : 3 0 s c c m でガス圧が 1 0 P a 、 R F パワーが 1 8 0 0 W である。30

#### 【 0 0 4 0 】

実施の形態 4 。

実施の形態 1 ~ 3 で説明した半導体層の形状は、バックチャネルエッチ型 T F T であれば適用できるものであり、さらにたとえば F F S であっても半透過であっても適用が可能である。F F S の場合で例えば特開 2 0 1 0 - 1 9 1 4 1 0 号公報に記載しているように、半導体層パターン上にソース・ドレイン電極が当該パターンからはみ出さないように形成されている構造であっても、半導体層のテーパー加工部の上層を画素電極が覆うような F F S であれば、適用することは可能である。

#### 【 0 0 4 1 】

このような構造でも半導体層のテーパー加工部やパターン端部から、下地に半導体層が無い領域にまで画素電極が延在して形成されているため、本発明の実施の形態に示す形状を適用することにより、画素電極の断線を防ぐことができる。すなわち、断線が懸念される対象としてはソース・ドレイン電極には限定されない。40

#### 【 0 0 4 2 】

このように F F S に適用した場合の半導体層の断面図を図 6 に示す。図 6 においては、透明導電膜等からなる画素電極 8 がテーパー角 1 、 2 を有する半導体層 4 やオーミックコンタクト層 5 のテーパー部を覆っており、画素電極 8 の被覆性が改善されていることがわかる。

#### 【 0 0 4 3 】

また、本願発明においては、 1 と 2 の 2 種類のテーパー角度を例にとって説明した

50

が、2種類には限らない。3種類以上としてもよい。その際においても、上層のテーパー角度を下層のテーパー角度よりも小さくすると本発明の実施の形態と同様の効果が得られる。

【符号の説明】

【0044】

- 1 基板、2 ゲート配線、3 ゲート絶縁層、4 半導体層、

5 オーミックコンタクト層、6 ソース・ドレイン層、7 レジスト、8 画素電極

11 上部電極、12 下部電極、13 ガスの導入管、14 真空ポンプ、

15 高周波電源、16 エッチング処理される基板、

A - Si(i)層とソース・ドレイン電極の接触距離、

B - Si(i)層の底辺距離

C オーミックコンタクト層の端部、

1、2、11 テーパー角度

10

【図1】

【図2】

【図3】

(b)

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 日野 輝重

熊本県合志市御代志997番地 メルコ・ディスプレイ・テクノロジー株式会社内

Fターム(参考) 5F004 AA11 DA18 DA26 DA29 DB01 DB02 EA28 EA29 EB08

5F110 AA14 AA26 BB01 CC07 DD02 EE02 EE03 EE04 FF02 FF03

GG02 GG15 GG22 HK02 HK03 HK04 HK09 HM03