(19) **日本国特許庁(JP)**

## (12) 特 許 公 報(B2)

(11)特許番号

特許第3695614号 (P3695614)

(45) 発行日 平成17年9月14日(2005.9.14)

(24) 登録日 平成17年7月8日 (2005.7.8)

(51) Int.C1.7

FI

G11C 29/00 G11C 11/413 G11C 29/00 603K G11C 11/34 341C

請求項の数 20 (全 15 頁)

(21) 出願番号 特願平8-335959

(22) 出願日 平成8年12月16日 (1996.12.16)

(65) 公開番号 特開平9-185897

(43) 公開日 平成9年7月15日 (1997.7.15) 審査請求日 平成14年7月11日 (2002.7.11)

(31) 優先権主張番号 1995 P 51503

(32) 優先日 平成7年12月18日 (1995.12.18)

(33) 優先権主張国 韓国(KR)

(73)特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区梅灘洞416 416, Maetan-dong, Yeo ngtong-gu, Suwon-si Gyeonggi-do, Republi c of Korea

(74)代理人 100076428

弁理士 大塚 康徳

(74)代理人 100112508

弁理士 高柳 司郎

(74)代理人 100115071

弁理士 大塚 康弘

最終頁に続く

(54) 【発明の名称】半導体メモリ装置の冗長用ヒューズ回路

## (57)【特許請求の範囲】

#### 【請求項1】

不良セルに代わる冗長セルを駆動するための冗長アドレシング信号を出力する半導体メモリ装置の冗長用ヒューズ回路において、

冗長アドレシング信号の論理状態を決定する第1のノードと、この第1のノードと第2のノードとの間に並列に設けられた複数のヒューズと、これらヒューズに直列接続され、アドレス信号に応じてオンオフする第1のスイッチ回路と、アドレス入力に関した制御信号が第1状態の時に前記第1のノードをプリチャージするプリチャージ回路と、前記制御信号が第2状態の時に前記第2のノードからの電流路を形成する第2のスイッチ回路と、冗長アドレシング信号を発生するために、前記制御信号が前記第2状態の時に前記第1のノードの論理状態を出力端へ伝達する<u>導通状態になり、前記制御信号が前記第1状態の時</u>に非導通状態になる転送回路と、を備えることを特徴とする冗長用ヒューズ回路。

## 【請求項2】

転送回路の伝達出力をラッチするラッチ回路をさらに備える請求項1記載の冗長用ヒュー ズ回路。

#### 【請求項3】

第1のスイッチ回路は、それぞれヒューズと直列接続され、各ゲート電極にそれぞれアドレス信号を受けるMOSトランジスタで構成される請求項1又は請求項2記載の冗長用ヒューズ回路。

【請求項4】

20

第2のスイッチ回路は、第2のノードと接地との間に設けられ、ゲート電極に制御信号を受けるMOSトランジスタで構成される請求項1~3のいずれか1項に記載の冗長用ヒューズ回路。

#### 【請求項5】

転送回路は、制御信号により制御されるCMOS伝達ゲートで構成される請求項1~4のいずれか1項に記載の冗長用ヒューズ回路。

#### 【請求項6】

不良セルを指定するアドレスにおける高レベルとなるアドレス信号に対応するヒューズを 切断する請求項1~5のいずれか1項に記載の冗長用ヒューズ回路。

#### 【請求項7】

制御信号が同期クロックである請求項1~6のいずれか1項に記載の冗長用ヒューズ回路

## 【請求項8】

不良セルに代わる冗長セルを駆動するための冗長アドレシング信号を出力する半導体メモリ装置の冗長用ヒューズ回路において、

冗長アドレシング信号の論理状態を決定する第1のノードと、メモリ動作状態に関した第1の制御信号に応じ、冗長が行われる場合にマスター信号を発生するマスター信号発生回路と、前記マスター信号及びアドレス入力に関した第2の制御信号に従い前記第1のノードをプリチャージするプリチャージ回路と、前記第1のノードと第2のノードとの間に並列に設けられた複数のヒューズと、これらヒューズに直列接続され、アドレス信号に応じてオンオフする第1のスイッチ回路と、前記第2の制御信号に従い前記第2のノードからの電流路を形成する第2のスイッチ回路と、前記マスター信号に従い前記第1のノードからの電流路を形成する第3のスイッチ回路と、前記第2の制御信号に従い前記第1のノードの論理状態を出力端へ伝達する転送回路と、を備えることを特徴とする冗長用ヒューズ回路。

#### 【請求項9】

転送回路の伝達出力をラッチするラッチ回路をさらに備える請求項8記載の冗長用ヒューズ回路。

#### 【請求項10】

第1の制御信号に従いラッチ回路の初期化を行う第4のスイッチ回路をさらに備える請求項9記載の冗長用ヒューズ回路。

## 【請求項11】

第4のスイッチ回路は、ラッチ回路の入力端と接地との間に設けられて第1の制御信号により制御されるMOSトランジスタで構成される請求項10記載の冗長用ヒューズ回路。

## 【請求項12】

マスター信号発生回路は、第1の制御信号に従い相補的にオンオフする第1のMOSトランジスタ及び第2のMOSトランジスタと、これら第1のMOSトランジスタと第2のMOSトランジスタとの間に直列接続されたマスターヒューズと、前記第2のMOSトランジスタと並列に設けられ、前記マスターヒューズが切断されたときにマスター信号を一定論理に固定する第3のMOSトランジスタと、を有してなる請求項8~11のいずれか1項に記載の冗長用ヒューズ回路。

#### 【請求項13】

プリチャージ回路は、マスター信号により制御されプリチャージ電圧を供給する第1のMOSトランジスタと、この第1のMOSトランジスタに直列接続され、第2の制御信号により制御されて第1のノードへプリチャージ電圧を提供する第2のMOSトランジスタと、を有してなる請求項8~12のいずれか1項に記載の冗長用ヒューズ回路。

#### 【請求項14】

プリチャージ回路は、第2のMOSトランジスタに並列接続され、第1のノードの反転論理で制御される第3のMOSトランジスタをさらに有する請求項13記載の冗長用ヒューズ回路。

10

20

30

40

#### 【請求項15】

第1のスイッチ回路は、それぞれヒューズと直列接続され、アドレス信号によりそれぞれ制御されるMOSトランジスタで構成される請求項8~14のいずれか1項に記載の冗長用ヒューズ回路。

#### 【請求項16】

第2のスイッチ回路は、第2のノードと接地との間に設けられ、第2の制御信号により制御されるMOSトランジスタで構成される請求項8~15のいずれか1項に記載の冗長用ヒューズ回路。

#### 【請求項17】

第3のスイッチ回路は、第1のノードと接地との間に設けられ、マスター信号により制御されるMOSトランジスタで構成される請求項8~16のいずれか1項に記載の冗長用ヒューズ回路。

#### 【請求項18】

転送回路は、第2の制御信号により制御されるCMOS伝達ゲートで構成される請求項8~17のいずれか1項に記載の冗長用ヒューズ回路。

#### 【請求項19】

不良セルを指定するアドレスにおける高レベルとなるアドレス信号に対応するヒューズを 切断する請求項8~18のいずれか1項に記載の冗長用ヒューズ回路。

#### 【請求項20】

第 2 の制御信号が同期クロックである請求項 8 ~ 1 9 のいずれか 1 項に記載の冗長用ヒュ 20 ーズ回路。

#### 【発明の詳細な説明】

#### [0001]

#### 【発明の属する技術分野】

本発明は半導体メモリ装置の冗長回路に関するもので、特に、外部クロックに同期して動作し、高速アドレス指定が可能な同期型(synchronous) DRAM、SRAM等の同期型半導体メモリ装置の冗長回路に採用されるヒューズ回路に関するものである。

#### [0002]

## 【従来の技術】

よく知られているように、半導体メモリ装置は行方向と列方向にマトリックス配列された多数のメモリセルを持っており、一般的には複数のアレイ形態で集積される。高集積化によってメモリセルアレイが高密度化されると、各メモリセルに割当てられる単位面積は減少し、その分不良率も上がる。そこで歩留りを上げるために、冗長技術が採用されている。すなわち、予め余分の冗長セル(スペアセル)を設けておき、不良セルに置換してリペアするものである。たとえば、カラム冗長(列冗長)の場合には、不良セルのカラムアドレスをデコーディングする際に冗長セルのカラムアドレスを代替指定し、列単位でリペアが行われる。

#### [0003]

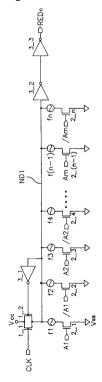

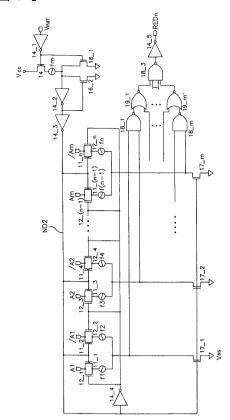

この冗長に際して、入力アドレスが不良セルを指定するアドレスかどうかを識別するために、冗長回路においてヒューズ回路が使用される。これには大きく分けて、図 1 に示すようなダイナミック型ヒューズ回路と、図 3 に示すようなスタティック型ヒューズ回路がある。

#### [0004]

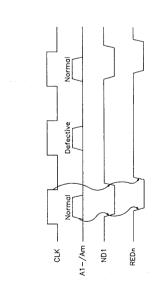

図1のヒューズ回路は、クロックCLKに同期する同期型半導体メモリ装置、あるいは非同期型メモリ装置(この装置でもローアドレスはローアドレスストローブ信号RASに同期して発生される)の両方で、ローアドレスをデコーディングするロー冗長回路に使用される。一方、図3のヒューズ回路は、同じく非同期型と同期型のメモリ装置の両方で、ローあるいはカラムアドレスをデコーディングするローあるいはカラム冗長回路に使用される。

## [0005]

40

30

40

50

図1を参照すれば、ダイナミック型ヒューズ回路は、同期型メモリの場合であれば外部クロックCLK(非同期型メモリの場合はRAS信号)が低レベルを維持する期間にノードND1を高レベル(たとえばVcc)にプリチャージするプリチャージ回路となる2つのPMOSトランジスタ1・1,1・2及びインバータ3・1と、ノードND1に並列接続された複数のヒューズ f 1~fnと、これらヒューズ f 1~fnと接地Vssとの間に設けられ、各ゲートにそれぞれノーマルメモリセルのローアドレス信号A1,/A1~Am,/Am("/"は反転の意味)を受けて導通する複数のNMOSトランジスタ2・1~2・nを使用したスイッチ回路と、ノードND1の信号をバッファリング(あるいは増幅)して冗長セルに対するアドレシング (addressing)、すなわち冗長セルのローアドレス信号発生のための冗長ローアドレシング信号REDnを出力する縦列インバータ3・2,3・3を使用した出力駆動回路と、を備えている。

[0006]

図2には、上記ダイナミック型ヒューズ回路の動作タイミングを図示してある。まず、図1のヒューズ回路に対応した冗長セルが不良セルの代わりに使用される場合、複数のヒューズf1~fnのうち、不良セルのアドレスに相当するヒューズを切断する。たとえば、不良セルのローアドレス信号 A1, A2, …, Am="0,1,…,1"とすれば、A2, A="1"、そして A1="0"なら/A1="1"なので、その"1"すなわち高レベル入力該当のヒューズf2,f3,…,f(n-1)が切断される。つまり、不良セルを指定するアドレスの論理"1"になるアドレス信号に対応したヒューズを切断する。これにより、アドレスが入力されてもノードND1がVssへ接地されずにノードND1の高レベルが保たれることになる。またこのとき、ノードND1は、インバータ3-1及びPMOSトランジスタ1-2によって高レベルを維持する。

[0007]

図 2 の信号波形に示すように、クロックCLK(あるいはRAS信号)が低レベル(論理ロウ)の際にPMOSトランジスタ1-1がターンオンし、ノードND1が高レベル(論理ハイ)、この例ではVccレベルにプリチャージされる。この後に、クロックCLKが高レベルになって、アクセスのために不良セルのローアドレス信号A1,/A1~Am,/Am(=repaired address: RA)がNMOSトランジスタ2-1~2-nの各ゲートにされると、この場合には、該アドレスに応じてオンするNMOSトランジスタ2-1~2-nにつながるヒューズ f 1~ f n が切断されているのでノードND1は高レベルを維持する。したがって、当該冗長セルのローアドレス指定を示す冗長ローアドレシング信号REDnが高レベル出力され、これにより当該冗長セルの冗長ワードラインが駆動される。

[0008]

この逆に、図1のヒューズ回路に対応した冗長セルが選択されない場合にはヒューズ f1~ fnが切断されず、したがって、クロックCLKが高レベルになって不良ではないノーマルメモリセルを指定するローアドレス信号A1,/A1~Am,/Am(= unrepair ed address: URA)が入力されれば、NMOSトランジスタ2-1~2-nのいずれかがターンオンしてノードND1が低レベル(Vss)になるので、出力駆動回路3-2、3-3からは低レベルのロー冗長アドレシング信号REDnが出力される。この場合には当該冗長セルの冗長ワードラインは選択されない。

[0009]

図3を参照すれば、スタティック型ヒューズ回路は、ノードND2に各ゲートが接続されて接地接続を制御するNMOSトランジスタ17・1~17・mによる接地接続制御用のスイッチ回路と、これらNMOSトランジスタ17・1~17・mのそれぞれに1対ずつ並列接続された複数のヒューズ f 1~fnと、これら各ヒューズ f 1~fnにそれぞれ接続され、ノードND2に従い導通してアドレス信号A1,/A1,A2,/A2,…,Am,/Amを伝送する複数のCMOS伝達ゲート11・1,12・1,11・2,12・2,…,11・n,12・nと、マスターヒューズ f m、PMOSトランジスタ14、NMOSトランジスタ16・1,16・2、及びインバータ14・1,14・2,14・3,14・4からなる伝達ゲート制御回路と、ヒューズ f 1~fnの各対ごとの出力を論理

30

40

50

演算し、それらが全て高レベルであれば高レベルのローあるいはカラム冗長アドレシング信号REDn(すなわち、当該冗長セルのビットラインあるいはワードラインの駆動のためのローあるいはカラムアドレス信号を発生することを示す信号)を出力し、1つでも低レベルであれば低レベルの冗長アドレシング信号REDnを出力する出力ロジック回路14-5,18-1~18-m,19-1~19-m 'と、を備えている。CMOS伝達ゲートをなすPMOSトランジスタ11-1~11-nのゲートはノードND2に接続され、またそのNMOSトランジスタ12-1~12-nのゲートはノードND2の電圧を反転させるインバータ14-4により制御される。

[0010]

このスタティック型ヒューズ回路に対応した冗長セルが不良セルの代わりに選択される場合は、上述のダイナミック型ヒューズ回路とは反対に、アドレス信号A1,/A1,A2, / A2,…,Am,/Amの中で'0'の値をもつ信号に相当するヒューズf1~fnを切断する。たとえば、ローアドレスA1,A2,…,Am="0,1,…,1"であれば、ヒューズf1,f4,…,fnが切断される。すなわち、不良セルを指定するアドレスの論理"0"のアドレス信号が入力される伝達ゲートに接続したヒューズを切断する。マスターヒューズfmは、このスタティック型ヒューズ回路に対応した冗長セルが使用されないときにアドレス信号の相補対(たとえばA1と/A1)が相互に衝突することを防止するために設けられており、該マスターヒューズfmを切断することでノードND2が低レベルになって当該ヒューズ回路が動作する。

[0011]

[0012]

[0013]

図 4 に示すように内部電源電圧  $V_{INT}$  が低レベルのときには、伝達ゲート制御回路の NM O S トランジスタ 1 6 - 1 , 1 6 - 2 のターンオンでノード ND 2 は低レベルになり、したがって伝達ゲートがターンオンすると共にスッチ用 NM O S トランジスタ 1 7 - 1 , 1 7 - 2 , ... , 1 7 - m がターンオフとなり得るが、これはメモリ動作前である。

[0014]

一方、内部電源電圧 V<sub>INT</sub> が高レベル(適正レベルで供給)になれば、伝達ゲート制御回路のNMOSトランジスタ16-1がターンオフする。しかしこの場合、マスターヒューズ f mが切断された状態にあるのでインバータ14-2及びNMOSトランジスタ16-2のラッチによって、ノードND2は低レベルのままとされる。したがって、伝達ゲート11-1~11-n,12-1~12-nはターンオンで、NMOSトランジスタ17-1~17-m)はターンオフとなる。

[0015]

そして、正常なノーマルメモリセル(normal)を指定するアドレス(URA)、たとえば" 1,0,…,0が入力された場合は、非切断のヒューズを通じて低レベルのアドレスビッ トが出力されるので、出力ロジック回路 1 8 - 1 ~ 1 8 - m , 1 9 - 1 ~ 1 9 - m ' , 1 4 - 5 から低レベルの冗長アドレシング信号 R E D n が出力される。

#### [0016]

一方、不良セル(defective)を指定するアドレス(RA)、上記の例でいえば"0,1,…,1が入力された場合は、低レベルのアドレス信号は一切伝達されず、高レベルのアドレス信号/A1,A2,…,Amだけがヒューズを通して出力されるので、この結果、出力ロジック回路18-1~18-m,19-1~19-m,14-5は高レベルの冗長アドレシング信号REDnを出力する。

#### [0017]

## 【発明が解決しようとする課題】

上記のようなダイナミック型ヒューズ回路は、レイアウト面積が小さくてすみ集積性に優れるが、一方で、動作特性上、アドレスのリセットに応じてノードND1のプリチャージを遂行しなければならないので、アドレスのリセット時間が非常に短かったり存在しないようなアドレスの高速入力が可能とされたメモリ装置への適用には、限界がある。

#### [0018]

また、上記のようなスタティック型ヒューズ回路は、ダイナミック型ヒューズ回路のようにアドレスリセットでプリチャージする必要がなく、したがってアドレス指定を高速にした半導体メモリ装置(同期型 DRAM、SRAM等)に適しているが、一方で、そのレイアウト面積がダイナミック型ヒューズ回路に比べて大きくなるため、集積性に劣るという短所をもつ。

#### [0019]

そこで、高速アドレス指定が可能な半導体メモリ装置の冗長回路として適し且つレイアウト面積が小さく集積性に優れる冗長用ヒューズ回路の提供を本発明の目的とする。

#### [0020]

#### 【課題を解決するための手段】

この目的のために本発明では、レイアウト面積が小さくてすむダイナミック型ヒューズ回路を同期型メモリの冗長回路に適するように改良する。そしてさらに、そのようなダイナミック型ヒューズ回路をカラム冗長にも適用可能にするものである。

## [0021]

すなわち、本発明の冗長用ヒューズ回路は、冗長アドレシング信号の論理状態を決定する第1のノードと、この第1のノードと第2のノードとの間に並列に設けられた複数のヒューズと、これらヒューズに直列接続され、アドレス信号に応じてオンオフする第1のスイッチ回路と、アドレス入力に関した制御信号が第1状態の時に前記第1のノードをプリチャージするプリチャージ回路と、前記制御信号が第2状態の時に前記第2のノードからの電流路を形成する第2のスイッチ回路と、冗長アドレシング信号を発生するために、前記制御信号が前記第2状態の時に前記第1のノードの論理状態を出力端へ伝達する導通状態になり、前記制御信号が前記第1状態の時に非導通状態になる転送回路と、を備えることを特徴とする。

#### [0022]

この冗長用ヒューズ回路では、転送回路の伝達出力をラッチするラッチ回路をさらに備えるのが好ましい。第1のスイッチ回路は、それぞれヒューズと直列接続され、各ゲート電極にそれぞれアドレス信号を受けるMOSトランジスタで構成することができ、第2のスイッチ回路は、第2のノードと接地との間に設けられ、ゲート電極に制御信号を受けるMOSトランジスタで構成することができる。また、転送回路は、制御信号により制御されるCMOS伝達ゲートで構成することができる。制御信号は同期式メモリの同期クロックにすることが可能である。

#### [0023]

あるいは、本発明の冗長用ヒューズ回路は、冗長アドレシング信号の論理状態を決定する 第1のノードと、メモリ動作状態に関した第1の制御信号に応じ、冗長が行われる場合に マスター信号を発生するマスター信号発生回路と、前記マスター信号及びアドレス入力に 10

20

30

40

20

30

40

50

関した第2の制御信号に従い前記第1のノードをプリチャージするプリチャージ回路と、前記第1のノードと第2のノードとの間に並列に設けられた複数のヒューズと、これらヒューズに直列接続され、アドレス信号に応じてオンオフする第1のスイッチ回路と、前記第2の制御信号に従い前記第2のノードからの電流路を形成する第2のスイッチ回路と、前記マスター信号に従い前記第1のノードからの電流路を形成する第3のスイッチ回路と、前記第2の制御信号に従い前記第1のノードの論理状態を出力端へ伝達する転送回路と、を備えることを特徴とする。

[0024]

この冗長用ヒューズ回路では、転送回路の伝達出力をラッチするラッチ回路をさらに備え るのが好ましく、また、第1の制御信号に従いラッチ回路の初期化を行う第4のスイッチ 回路をさらに備えるとよい。この第4のスイッチ回路は、ラッチ回路の入力端と接地との 間に設けられて第1の制御信号により制御されるMOSトランジスタで構成することがで きる。マスター信号発生回路は、第1の制御信号に従い相補的にオンオフする第1のMO Sトランジスタ及び第2のMOSトランジスタと、これら第1のMOSトランジスタと第 2のMOSトランジスタとの間に直列接続されたマスターヒューズと、前記第2のMOS トランジスタと並列に設けられ、前記マスターヒューズが切断されたときにマスター信号 を一定論理に固定する第3のMOSトランジスタと、を有してなるものとすることができ る。プリチャージ回路は、マスター信号により制御されプリチャージ電圧を供給する第1 のMOSトランジスタと、この第1のMOSトランジスタに直列接続され、第2の制御信 号により制御されて第1のノードへプリチャージ電圧を提供する第2のMOSトランジス タと、を有してなるものとすることができる。さらにプリチャージ回路は、第2のMOS トランジスタに並列接続され、第1のノードの反転論理で制御される第3のMOSトラン ジスタを有するものとしてもよい。第1のスイッチ回路は、それぞれヒューズと直列接続 され、アドレス信号によりそれぞれ制御されるMOSトランジスタで構成することができ 、第2のスイッチ回路は、第2のノードと接地との間に設けられ、第2の制御信号により 制御されるMOSトランジスタで構成することができる。また、第3のスイッチ回路は、 第1のノードと接地との間に設けられ、マスター信号により制御されるMOSトランジス 夕で構成することができる。転送回路は、第2の制御信号により制御されるCMOS伝達 ゲートで構成することができる。この場合の第2の制御信号も同期式メモリの同期クロッ クとすることが可能である。

[0025]

【発明の実施の形態】

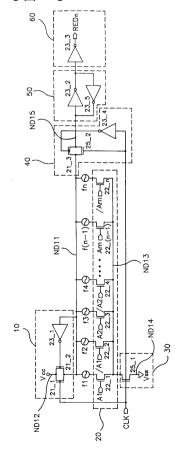

図5にはヒューズ回路の第1実施形態、図6にはその動作タイミングを示してある。

[0026]

この図 5 に示すヒューズ回路は、第1のノードND11と電源電圧Vccが印加される電源 ノードND12との間に設けられ、制御信号としてのクロック信号CLKが低レベル(V ss)になるときにPMOSトランジスタ21-1が導通して第1のノードND11を高レ ベル(プリチャージ電圧)にプリチャージするプリチャージ回路10と、第1のノードN D 1 1 に並列接続された複数のヒューズ f 1 ~ f n と、第 2 のノードN D 1 3 とヒューズ f 1 ~ f n との間に設けられ、それぞれアドレス信号 A 1 , / A 1 , A 2 , / A 2 , ... , Am, / Amに応答して各ヒューズ f 1 ~ f n を第 2 のノード N D 1 3 へ接続する第 1 の スイッチ回路 2 0 と、第 2 のノード N D 1 3 と接地 V ssが印加される接地ノード N D 1 4 との間に設けられ、クロック信号CLKの高レベルに応答して導通する第2のスイッチ回 路30と、第1のノードND11と出力ノードND15との間に設けられ、クロック信号 CLKの高レベルに応答して導通する転送回路40と、出力ノードND15に設けられた ラッチ回路50と、ラッチ回路50の出力をドライブして冗長アドレシング信号REDn を出力する出力駆動回路60と、を備えている。このうちラッチ回路40は、転送回路4 0のオフで第1のノードND11と出力ノードND15の間の連絡が断たれた場合にその 直前の状態をラッチし、これに従い出力駆動回路60が冗長アドレシング信号REDnを 出力する。

30

40

50

#### [0027]

図1に比べると分かるように、この実施形態は、従来の回路構成(10,f1~fn,20,60)に加えて、接地接続制御用の第2のスイッチ回路30、転送回路40、及びラッチ回路50を設けた構成をもつ。具体的には、第2のスイッチ回路30は、第1のスイッチ回路20をなす各NMOSトランジスタ22-1~22-nへ共通に接続したドレインとVssへ接続したソースとを有し、クロック信号CLKでゲート制御されるNMOSトランジスタ25-1から構成されている。また転送回路40は、第1のノードND11と出力ノードND15との間に設けられてオンオフするCMOS伝達ゲート21-3,21-3とインバータ23-4とから構成され、クロック信号CLKによりNMOSゲート25-2が制御され且つインバータ23-4で反転したクロック信号CLKによりPMOSゲート21-3が制御される。そしてラッチ回路50は、出力ノードND15を入力側とするインバータ23-2と、出力ノードND15を出力側とするインバータ23-5と、の対向並列接続から構成されている。

## [0028]

このヒューズ回路に対応した冗長セルが使用される場合、複数のヒューズ f 1 ~ f n のうち、不良セルアドレスの論理ハイビットに相当するヒューズが切断される。たとえば、不良セルのアドレス信号 A 1 , A 2 , ... , A m = "0 , 1 , ... , 1"であれば、このうち"1"を受ける N M O S トランジスタ 2 2 - 2 , 2 2 - 3 , ... , 2 2 - (n - 1)に接続したヒューズ f 2 , f 3 , ... , f (n - 1)を切断する。すなわち、不良セルを指定するアドレス入力に応じて第1のノード N D 1 1 の接地接続を断つためである。

#### [0029]

これとは反対に、不良の無い場合や図 5 のヒューズ回路に対応した冗長セルが使用されない場合は、ヒューズ f 1 ~ f n のいずれも切断されない。

#### [0030]

この第1実施形態のヒューズ回路において、クロック信号CLKが低レベルである場合は、プリチャージ回路10のPMOSトランジスタ21-1がターンオンし、第1のノードND11は高レベルのVccレベルにプリチャージされる。これは従来同様である。

#### [0031]

クロック信号 CLKが高レベルになり、これに同期して正常なノーマルメモリセルのアドレス信号 A1 、/ A1 ~ Am 、/ Am (URA)が入力される場合は、これに応じてオンする第1のスイッチ回路 20のトランジスタ 22 - 1 ~ 22 - nにつながる切断されてないヒューズ f1 ~ fnが少なくとも1つ存在するので、第1のノードND11は低レベル(Vss)になる。そして、このときには転送回路 40のトランジスタ 21 - 3 、25 - 2がクロック信号 CLKに従いターンオンするので、第1のノードND11の論理状態が転送されて出力ノードND15は低レベルになる。その結果、出力駆動回路 60からは低レベル(非活性状態)の冗長アドレシング信号 REDnが出力される。

## [0032]

続いてクロック信号CLKが低レベルへ遷移すると、このメモリはクロック信号CLKの低レベル遷移に際するアドレスリセットのないタイミングであるが(図6)、プリチャージ回路10のトランジスタ21-1がターンオンする一方、第2のスイッチ回路30のトランジスタ25-1がターンオフするので、第1のノードND11のプリチャージが実行される。またこのとき、転送回路40のトランジスタ21-3,25-2もクロック信号CLKに従いターンオフするので、第1のノードND11のプリチャージ高レベルが出力ノードND15へ伝達されることは防止される。

#### [0033]

また本例では、出力ノードND15の状態をラッチするラッチ回路50が設けられ、クロック信号CLKが低レベルになったときでも、その直前の高レベル時の論理状態が維持されるようになっており、したがって、低レベルの冗長アドレシング信号REDnが継続して出力される。これにより、当該冗長セルのワードラインあるいはビットラインは駆動されない。

#### [0034]

一方、クロック信号 C L K が高レベルになり、当該ヒューズ回路に対応した冗長セルでリペアされる不良セルのアドレス信号 A 1 , / A 1 ~ A m , / A m (R A) が入力される場合は、当該アドレス信号中の"1"になるビットに応じてオンする第1のスイッチ回路20のトランジスタ22-1~22-nにつながるヒューズf1~fnが切断されているので、第2のスイッチ回路30がオンして接地接続されても第1のノードND11の高レベルが保持される。そして、プリチャージ回路10のトランジスタ21-2及び転送回路40がターンオンするので、第1のノードND11の高レベルは出力ノードND15へ伝達され、その結果、出力駆動回路60は高レベルの冗長アドレシング信号REDnを出力し、当該冗長セルのワードラインあるいはビットラインが駆動される。

[0035]

このように出力駆動回路 6 0 が高レベル(活性状態)の冗長アドレシング信号 R E D n を出力している状態で、アドレスリセットされることなくクロック信号 C L )が低レベルへ遷移すると、プリチャージ回路 1 0 のトランジスタ 2 1 - 1 がターンオンする一方、第 2 のスイッチ回路 2 0 のトランジスタ 2 5 - 1 がターンオフするので、第 1 のノード N D 1 1 のプリチャージが遂行される。またこのとき、転送回路 4 0 のトランジスタ 2 1 - 3 , 2 5 - 2 がターンオフしているので、第 1 のノード N D 1 1 と出力ノード N D 1 5 とは電気的に分離される。したがって、出力ノード N D 1 5 は第 1 のノード N D 1 1 の電圧変化に影響されることはない。

[0036]

さらに、出力ノードND15の状態はクロック信号CLKの低レベル期間でもラッチ回路50により維持されるので、出力駆動回路60から高レベルの冗長アドレシング信号REDnが継続出力される。すなわち、当該冗長セルのワードラインあるいはビットラインの駆動が継続される。つまり、この例のヒューズ回路は、ロー冗長、カラム冗長のどちらへも適用可能である。

[0037]

第1のノードND11がプリチャージされ、そして出力ノードND15が「高レベルである状態で、クロック信号CLKが高レベルに遷移し、正常なノーマルメモリセルのアドレス(URA)が第1のスイッチ回路20に入力されると、切断されていないヒューズ f 1~f n、第1のスイッチ回路20のトランジスタ22-1~22-n、そして第2のスイッチ回路30のトランジスタ25-1を通じる接地ルートが形成されるため、第1のノードND11は低レベルになる。また、転送回路40が導通することにより、その第1のノードND11の低レベルが転送されて出力ノードND15が低レベルになる。この結果、冗長アドレシング信号REDnは低レベルになり、当該冗長セルのワードラインあるいはビットラインは非駆動状態とされる。

[0038]

以上のように、第1実施形態によると、アドレスリセットがなくともクロック信号CLKの低レベル遷移に応じてプリチャージが行われ、しかも、次のクロックまで前クロックの冗長アドレシング信号REDnの状態が維持される。したがって、高速アドレシングの半導体メモリ装置に適しており、且つ高速アドレス指定のメモリ装置における冗長ヒューズ回路のレイアウト面積減少に貢献する。

[0039]

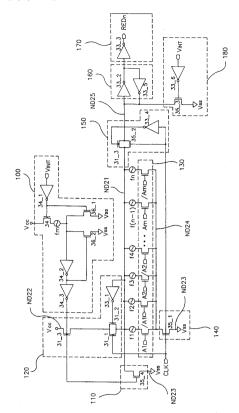

図 7 は、ヒューズ回路の第 2 実施形態を示している。この例のヒューズ回路は、図 5 の構成に加えてマスター制御回路 1 0 0 及び 2 つのさらなるスイッチ回路 1 1 0 , 1 8 0 を有し、そして若干異なる構成のプリチャージ回路 1 2 0 を有している。

[0040]

マスターヒューズ f m を備えたマスター制御回路 1 0 0 は、入力信号として内部電源電圧  $V_{INT}$  が印加されると、マスターヒューズ f m がつながっていれば V ccレベルのマスター信号を発生し、マスターヒューズ f m が切断されていれば V ssレベルのマスター信号を発生する。第 3 のスイッチ回路 1 1 0 は、マスター制御回路 1 0 0 によるマスター信号に応

10

20

30

40

30

40

50

じてオンオフし、第1のノードND21と接地ノードND23との間を接続する。また、第4のスイッチ回路180は、内部電源電圧V<sub>INT</sub>の入力に応答し、V<sub>INT</sub>の発生前に導通して出力ノードND25を接地させる。

#### [0041]

第1のノードND21と電源ノードND22との間に設けられるプリチャージ回路120は、マスター制御回路100からのマスター信号とクロック信号CLKの両方に応じて、マスター信号及びクロック信号ともに低レベルのときに第1のノードND21をプリチャージする。

#### [0042]

第1のノードND21に並列接続された複数のスレイブヒューズ f 1 ~ f n と第2のノードND24との間に設けられた第1のスイッチ回路130は、アドレス信号A1,/A1,A2,/A2,...,Am,/Amに応じて各スレイブヒューズと第2のノードND24とを電気的に接続する。そして、接地ノードND23と第2のノードND24との間に設けられた第2のスイッチ回路140は、クロック信号CLKに応答して接地ノードND23と第2のノードND24とを電気的に接続する。

#### [0043]

第1のノードND21と出力ノードND25との間に設けられる転送回路150は、クロック信号CLKに応答して第1のノードND21と出力ノードND25とを電気的に接続する。そして、出力ノードND25に接続されたラッチ回路160は、第1のノードND21から伝送された信号をラッチし、出力駆動回路170がラッチ回路160の出力に従い冗長アドレシング信号REDnを出力する。

#### [0044]

この第2実施形態のヒューズ回路に対応した冗長セルが使用されない場合、マスターヒューズ f mとスレイブヒューズ f 1~fnは、全部つながったままである。したがって、マスターヒューズ f mが切られていないので、チップの内部電源電圧 V<sub>INT</sub> (あるいは高レベルの制御信号)が供給されるとマスター制御回路100は高レベルのマスター信号を発生し、プリチャージ回路180のPMOSトランジスタ31-3はターンオフ、第3のスイッチ回路110のNMOSトランジスタ35-4はターンオンとなる。これにより、第1のノードND21はVssの低レベルになる。またこの場合、クロック信号CLKが高レベルになってもPMOSトランジスタ31-3がオフのままなので第1のノードND21へVccは提供されず、したがって、冗長アドレシング信号REDnは論理ロウの非活性状態を維持する。

#### [0045]

一方、このヒューズ回路に対応した冗長セルが使用される場合には、まず、スレイブヒューズ f 1 ~ f n の半数とマスターヒューズ f m が切断される。たとえば、不良セルのアドレス A 1 , A 2 , ... , A m = " 0 , 1 , ... , 1 " であれば、スレイブヒューズ f 1 , f 4 , ... , f n とマスターヒューズ f m を切断する。

#### [0046]

この状態の回路に、内部電源電圧 V<sub>INT</sub> が供給されると、 PMO Sトランジスタ3 4 がオンしてもマスターヒューズ f mが切断されているのでトランジスタ3 6 - 2 によりマスター制御回路 1 0 0 の低レベル出力が保たれ、したがって、プリチャージ回路 1 2 0 のトランジスタ3 1 - 3 はオン、第3のスイッチ回路 1 1 0 はオフとなり、クロック信号 C L K が低レベルであれば、プリチャージ回路 1 2 0 のトランジスタ3 1 - 1 がターンオンし且つ第2のスイッチ回路 1 4 0 のトランジスタ3 5 - 1 がターンオフするので、第1のノードND2 1 は高レベルにプリチャージされる。また、クロック信号 C L K の低レベルに応じ、転送回路 1 5 0 のトランジスタ3 1 - 3 ,35 - 2 はターンオフしているので、第1のノードND2 1 と出力ノードND2 5 とが電気的に分離される。そして、内部電源電圧 V<sub>INT</sub> の印加前に第4のスイッチ回路 1 8 0 のトランジスタ3 5 - 3 がターンオンして初期化が行われるので、出力ノードND2 5 は必ず最初に低レベルで、その結果、出力駆動回路 1 7 0 はから低レベルの冗

長アドレシング信号REDnが出力される。

#### [0047]

続いてアドレスがリセットされることなくクロック信号CLKが高レベルへ遷移すると、 第2のスイッチ回路140のトランジスタ35-1及び転送回路150のトランジスタ3 1 - 3 , 3 5 - 2 がターンオンするので、アドレス入力に応じた第1のノードND21の 状態が出力ノードND25へ伝達され、ラッチ回路160にラッチされる。

#### [0048]

このときに、当該ヒューズ回路によるリペア対象の不良セルアドレス(RA)が入力され る場合、第1のノードND21はVssへの接続経路が断たれて高レベルを維持し、これが 出力ノードND25に伝達される結果、冗長アドレシング信号REDnは高レベルの活性 状態になる。一方、正常なノーマルメモリセルを選択するアドレス(URA)が入力され る場合は、第1のノードND21はVssへ接地されて低レベルとなり、これが出力ノード ND25に伝達される結果、冗長アドレシング信号REDnは低レベルの非活性状態にな る。

#### [0049]

高レベルのクロック信号CLKに応答して出力駆動回路170が低レベルの冗長アドレシ ング信号REDnを出力している状態から、アドレスがリセットされることなくクロック 信号CLKが再び低レベルに遷移すると、転送回路150により第1のノードND21と 出力ノードND25とが電気的に分離されたうえで、第2のスイッチ回路140がオフす ると共にプリチャージ回路120がオンとなるので、第1のノードND21がプリチャー ジされる。しかしながらこのときに、直前のクロック信号CLKの高レベル時の出力ノー ドND25の状態をラッチ回路160がラッチしているので、出力駆動回路170は、低 レベルの冗長アドレシング信号REDnを継続出力することになる。したがって、当該冗 長セルのワードラインあるいはビットラインが駆動されることはない。

## [0050]

また、クロック信号CLKの低レベル時に第1のノードND21及び出力ノードND25 が高レベルにある状態から、該当不良セルのアドレス(RA)ではない他のアドレス(U RA)が第1のスイッチ回路130に入力された場合、クロック信号CLKが高レベルへ 遷移すると、第1のスイッチ回路130及びヒューズf1~fnを通じた接地経路ができ るために第1のノードND21は低レベルとなり、これが、導通した転送回路150を通 じて出力ノードND25へ伝えられる。その結果、迅速に冗長アドレシング信号REDn が低レベルへ遷移することになる。したがって、当該冗長セルのワードラインあるいはビ ットラインの駆動は抑止される。

### 【図面の簡単な説明】

- 【図1】従来のダイナミック型ヒューズ回路を示した回路図。

- 【図2】図1の回路における信号波形図。

- 【図3】従来のスタティック型ヒューズ回路を示した回路図。

- 【図4】図3の回路における信号波形図。

- 【図5】本発明によるヒューズ回路の第1実施形態を示した回路図。

- 【図6】図5の回路における信号波形図。

- 【図7】 本発明によるヒューズ回路の第2実施形態を示した回路図。

#### 【符号の説明】

- 10,120 プリチャージ回路

- 20,130 第1のスイッチ回路

- 30,140 第2のスイッチ回路

- 40,150 転送回路

- 50,160 ラッチ回路

- 60,170 出力駆動回路

- 100 マスター制御回路

- 1 1 0 第 3 のスイッチ回路

30

20

1 8 0 第 4 のスイッチ回路(初期化回路) f 1 ~ f n スレイブヒューズ f m マスターヒューズ

# 【図1】

# 【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

## フロントページの続き

(74)代理人 100116894

弁理士 木村 秀二

(72)発明者 李 昇勳

大韓民国京畿道水原市八達区梅灘4洞208-1番地

審査官 小松 正

(56)参考文献 特開平05-041096(JP,A)

特開平05-334897(JP,A)

(58)調査した分野(Int.CI.<sup>7</sup>, DB名)

G11C 29/00

G11C 11/401-11/4099