(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5642970号

(P5642970)

(45) 発行日 平成26年12月17日(2014.12.17)

(24) 登録日 平成26年11月7日(2014.11.7)

(51) Int.Cl.

F 1

H01L 35/34 (2006.01)

H01L 35/34

H01L 35/16 (2006.01)

H01L 35/16

H01L 21/205 (2006.01)

H01L 21/205

請求項の数 22 (全 25 頁)

(21) 出願番号 特願2009-548319 (P2009-548319)

(86) (22) 出願日 平成20年2月1日 (2008.2.1)

(65) 公表番号 特表2010-518600 (P2010-518600A)

(43) 公表日 平成22年5月27日 (2010.5.27)

(86) 國際出願番号 PCT/US2008/001395

(87) 國際公開番号 WO2008/097484

(87) 國際公開日 平成20年8月14日 (2008.8.14)

審査請求日 平成23年1月20日 (2011.1.20)

(31) 優先権主張番号 60/887,964

(32) 優先日 平成19年2月2日 (2007.2.2)

(33) 優先権主張国 米国(US)

(73) 特許権者 509219132

ネクストリーム・サーマル・ソリューションズ、インコーポレイテッド

アメリカ合衆国ノースカロライナ州277

03-8031, ダーラム、ペイトリオット・ドライブ 3908, スウィート 1

40

(74) 代理人 100099623

弁理士 奥山 尚一

(74) 代理人 100096769

弁理士 有原 幸一

(74) 代理人 100107319

弁理士 松島 鉄男

(74) 代理人 100114591

弁理士 河村 英文

最終頁に続く

(54) 【発明の名称】 クラックおよび／または表面欠陥密度が減少したエピタキシャル熱電膜を堆積させる方法および関連する装置

## (57) 【特許請求の範囲】

## 【請求項1】

熱電素子を製造する方法において、成長表面を備える基板を設けるステップであって、前記成長表面が、前記基板の結晶方位によって画定された面に対して、5°から45°の範囲内のオフカット角でオフカットされている、ステップと、

前記成長表面上に、熱電膜をエピタキシャル成長させるステップと、

を含み、前記熱電膜が、ビスマス(Bi)、アンチモン(Sb)、鉛(Pb)、テルル(Te)、またはセレン(Se)を含む化合物を含んでいることを特徴とする方法。

## 【請求項2】

前記基板の前記結晶方位によって画定された前記面が、{100}面であり、前記成長表面が、前記{100}面から<110>方向に向かってオフカットされた微傾斜成長表面を含んでいることを特徴とする請求項1に記載の方法。

## 【請求項3】

前記オフカット角が、5°から30°の範囲内にあることを特徴とする請求項2に記載の方法。

## 【請求項4】

前記オフカット角が、10°から20°の範囲内にあることを特徴とする請求項3に記載の方法。

## 【請求項5】

10

20

前記オフカット角が、{100}面に対して<110>方向に向かう15°であることを特徴とする請求項3に記載の方法。

**【請求項6】**

前記熱電膜の結晶方位が、前記成長表面に対して5°から30°の範囲内の角度で傾斜していることを特徴とする請求項1に記載の方法。

**【請求項7】**

前記熱電膜の前記結晶方位によって画定された面が、(0015)面であることを特徴とする請求項6に記載の方法。

**【請求項8】**

前記熱電膜の前記結晶方位が、10°から25°の範囲内の角度で傾斜していることを特徴とする請求項6に記載の方法。 10

**【請求項9】**

前記基板が、ガリウムヒ素(GaAs)、シリコン(Si)、フッ化バリウム(BaF)、炭化ケイ素(SiC)、窒化ガリウム(GaN)、窒化アルミニウム(AlN)、サファイア、またはガラスを含んでいることを特徴とする請求項1に記載の方法。

**【請求項10】**

前記熱電膜をエピタキシャル成長させる前に、前記基板の前記成長表面を、前記成長表面から突出する複数のメサを画定するように、パターン化するステップをさらに含んでいることを特徴とする請求項1に記載の方法。

**【請求項11】**

前記熱電膜が、1クラック/mm未満のクラック密度を有していることを特徴とする請求項1に記載の方法。 20

**【請求項12】**

前記熱電膜が、1クラック/cm未満のクラック密度を有していることを特徴とする請求項11に記載の方法。

**【請求項13】**

前記熱電膜を前記基板の前記成長表面上にエピタキシャル成長させる前に、前記基板の前記成長表面上に少なくとも1つの中間層を形成することをさらに含んでいることを特徴とする請求項1に記載の方法。

**【請求項14】**

前記中間層が、歪層超格子を含んでいることを特徴とする請求項13に記載の方法。 30

**【請求項15】**

熱電素子を製造する方法において、

基板を、前記基板から突出する複数のメサを有する成長表面を画定するように、パターン化するステップと、

前記成長表面上に、熱電膜をエピタキシャル成長させるステップと

を含み、前記熱電膜が、ビスマス(Bi)、アンチモン(Sb)、鉛(Pb)、テルル(Te)、またはセレン(Se)を含む化合物を含んでいることを特徴とする方法。

**【請求項16】**

前記熱電膜のエピタキシャル成長が、前記成長表面から突出する複数のメサを備える前記熱電膜をエピタキシャル成長させることを含んでおり、前記熱電膜の前記複数のメサが、200μm以下の直径または幅を有しており、前記熱電膜のメサが、1クラック/mm未満のクラック密度を有していることを特徴とする請求項15に記載の方法。 40

**【請求項17】**

結晶方位を有する熱電膜を備える熱電要素であって、前記結晶方位が、前記熱電膜の表面に対して5°から30°の範囲内の角度で傾斜している、熱電要素を備えており、前記熱電膜が、ビスマス(Bi)、アンチモン(Sb)、鉛(Pb)、テルル(Te)、またはセレン(Se)を含む化合物を含んでいることを特徴とする熱電素子。

**【請求項18】**

前記熱電膜が、5μmから100μmの範囲内の厚みを有していることを特徴とする請 50

求項 1 7 に記載の素子。

**【請求項 1 9】**

前記熱電膜が、 $40 \mu m$  以下の厚みを有していることを特徴とする請求項 1 8 に記載の素子。

**【請求項 2 0】**

前記熱電膜が、 $1 \text{ クラック} / mm$  未満のクラック密度を有していることを特徴とする請求項 1 7 に記載の素子。

**【請求項 2 1】**

結晶方位を有する第 2 の熱電膜を備える第 2 の熱電要素であって、前記結晶方位が、前記第 2 の熱電膜の表面に対して $5^\circ$ から $30^\circ$ の範囲内の角度で傾斜している、第 2 の熱電要素と、

10

第 1 のヘッダーおよび第 2 のヘッダーと、

をさらに備え、

第 1 の熱電要素および前記第 2 の熱電要素が、電気的に直列結合され、前記第 1 のヘッダーと前記第 2 のヘッダーとの間に熱的に平行に結合されていることを特徴とする請求項 1 7 に記載の素子。

**【請求項 2 2】**

$100 \mu m$  未満の厚みおよび $1 \text{ クラック} / mm$  未満のクラック密度を有する熱電材料層を備え、前記熱電材料層の結晶方位が、前記熱電材料層の表面に対して $5^\circ$ から $30^\circ$ の範囲内の角度で傾斜しており、前記熱電材料層が、ビスマス (Bi)、アンチモン (Sb)

20、鉛 (Pb)、テルル (Te)、またはセレン (Se) を含む化合物を含んでいることを特徴とする熱電膜。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

**[関連出願]**

本出願は、2007年2月2日に「クラックおよび／または表面欠陥密度が減少したエピタキシャル膜を GaAs 上に改良された堆積率で堆積させる方法」と題して出願された米国仮出願第 60/887,964 号の優先権の利益を主張するものであり、この開示内容は、参照することによって、その全体がここに含まれるものとする。

30

**【0 0 0 2】**

**[発明の分野]**

本発明は、薄膜熱電材料を製造する方法および関連する熱電素子に関するものである。

**【背景技術】**

**【0 0 0 3】**

熱電材料は、ペルチエ効果による冷却および／または発電をもたらすために、用いられている。熱電材料は、例えば、「フォノンブロッキング／電子伝達構造」と題するヴェンカタスブラマニアン (Venkatasubramanian) らによる文献 (第 18 回熱電国際会議、1999 年) (非特許文献 1) において検討されている。この開示内容は、参照することによって、その全体がここに含まれるものとする。

40

**【0 0 0 4】**

固体状態の熱電冷却を応用することによって、電子機器およびセンサ、例えば、RF 受信機のフロントエンド、赤外線 (IR) 撮像器、超高感度磁気センサ、および／または超電導電子機器の性能を改良することができる、と期待されている。

**【0 0 0 5】**

熱電素子の性能は、その素子に用いられる 1 つまたは複数の熱電材料の性能指数 (ZT)

) の関数とことができ、該性能指数は、

$$ZT = (\frac{\sigma^2 T}{K_T}) \quad (式 1)$$

によって、表わされる。ここで、 $\sigma$ 、 $T$ 、 $K_T$  は、それぞれ、ゼーベック係数、絶対温度、電導率、および全熱伝導率である。材料係数 Z は、所定のキャリア密度 ( ) およ

50

び対応する に対して、格子熱伝導率 ( $K_L$ ) 、電子熱伝導率 ( $K_e$ ) 、およびキャリア移動度 ( $\mu$ ) を用いて、以下の式(2)、すなわち、

$$Z = \frac{2}{(K_L + K_e)} = \frac{2}{[K_L / ((\mu q) + L_0 T)]} \quad \text{式(2)}$$

によって、表わされる。ここで、 $L_0$ は、ローレンツ数(非縮退半導体では、略  $1.5 \times 10^{-8} V^2 / K^2$ )である。最新式の熱電素子は、 $200^\circ K$ から $400^\circ K$ の温度範囲に對して、 $p - Bi_xSb_{2-x}Te_{3-y}Se_y$  ( $x = 0.5$ 、 $y = 0.12$ ) および  $n - Bi_2(Se_yTe_{1-y})_3$  ( $y = 0.05$ ) のような合金を用いる場合がある。合金によっては、 $K_L$ を  $\mu$ に對してさらに著しく減少させることができ、これによつて、 $ZT$ を高めることができる。

#### 【0006】

加えて、薄膜熱電材料が開発されてきている。例えば、ガリウムヒ素 ( $GaAs$ ) 基板上に成長したビスマステルル ( $Bi_2Te_3$ ) 系および / またはアンチモンテルル ( $Sb_2Te_3$ ) 系エピタキシャル膜が、薄膜熱電材料の製造に用いられている。しかし、これらの膜の成長形態は、膜内のクラックおよび表面欠陥によつて損なわれることがある。例えば、 $2^\circ$  オフカット  $GaAs$  基板上に成長した熱電膜は、約  $5 \sim 20$  クラック / mm、場合によつては、 $10$  クラック / mm よりも大きいクラック密度を有することがある。これらのクラックおよび欠陥は、信頼性の問題および後続の膜処理の困難さをもたらし、その結果、これらの膜から得られる 1 つまたは複数の利得が損なわれる可能性がある。

#### 【先行技術文献】

#### 【非特許文献】

#### 【0007】

【非特許文献 1】ヴェンカタスブラマニアン (Venkatasubramanian) ら：「フォノンプロッキング / 電子伝達構造」、第 18 回熱電国際会議、1999 年

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

従つて、当技術分野において、改良された熱電素子製造方法および構造が、引き続き必要とされている。

#### 【課題を解決するための手段】

#### 【0009】

本発明のいくつかの実施形態によれば、熱電素子を製造する方法は、成長表面を備える基板を設けるステップであつて、該成長表面が、基板の結晶方位によつて画定された面に對して、約  $5^\circ$  から約  $45^\circ$  の範囲内のオフカット角でオフカットされている、ステップを含んでいる。次いで、該成長表面上に、熱電膜がエピタキシャル成長されるようになつてゐる。

#### 【0010】

いくつかの実施形態では、基板の結晶方位によつて画定された面は、 $\{100\}$  面であるとよく、成長表面は、 $\{100\}$  面から  $<110>$  方向に向かってオフカットされた微傾斜成長表面であるとよい。

#### 【0011】

他の実施形態では、オフカット角は、約  $5^\circ$  から約  $30^\circ$  の範囲内、さらに他の実施形態では、約  $10^\circ$  から約  $20^\circ$  の範囲内にあるとよい。例えば、オフカット角は、 $\{100\}$  面に對して  $<110>$  方向に向かう約  $15^\circ$  であるとよい。

#### 【0012】

いくつかの実施形態では、熱電膜の結晶方位は、成長表面に對して約  $5^\circ$  から約  $30^\circ$  の範囲内の角度で傾斜しているとよい。例えば、熱電膜の結晶方位は、約  $10^\circ$  から約  $25^\circ$  の範囲内の角度で傾斜しているとよい。さらに具体的には、いくつかの実施形態において、熱電膜の結晶方位は、成長表面に對して約  $11.5^\circ$  の角度で傾斜しているとよい。他の実施形態では、熱電膜の結晶方位は、成長表面に對して約  $18^\circ$  から約  $24^\circ$  の範囲内の角度で傾斜しているとよい。例えば、熱電膜の結晶方位は、成長表面に對して約  $2$

10

20

30

40

50

0°の角度で傾斜しているとよい。熱電膜の結晶方位によって画定された面は、(001)面であるとよい。

#### 【0013】

他の実施形態では、熱電膜は、ビスマス(Bi)、アンチモン(Sb)、鉛(Pb)、テルル(Te)、および/またはセレン(Se)を含む化合物であるとよい。

#### 【0014】

他の実施形態では、基板は、ガリウムヒ素(GaAs)、シリコン(Si)、フッ化バリウム(BaF)、炭化ケイ素(SiC)、窒化ガリウム(GaN)、窒化アルミニウム(AlN)、サファイア、および/またはガラスであるとよい。

#### 【0015】

いくつかの実施形態では、熱電膜をエピタキシャル成長させる前に、基板の成長表面は、成長表面から突出する複数のメサを画定するように、パターン化されてもよい。いくつかの実施形態では、基板の成長表面をパターン化する前に、熱電膜種層が、基板の成長表面上にエピタキシャル成長されてもよい。

#### 【0016】

他の実施形態では、熱電膜をエピタキシャル成長させる前に、マスクパターンが、成長表面の複数の部分を露出させるように、基板の成長表面上に形成され、熱電膜が、成長表面の複数の露出部分上にエピタキシャル成長されてもよい。いくつかの実施形態では、マスクパターンを成長表面上に形成する前に、熱電膜種層が、成長表面上にエピタキシャル成長されてもよい。

#### 【0017】

いくつかの実施形態では、熱電膜を基板の成長表面上にエピタキシャル成長させる前に、少なくとも1つの中間層が、基板の成長表面上に形成されてもよい。中間層として、炭化ケイ素(SiC)層、窒化アルミニウム(AlN)層、ガリウムヒ素(GaAs)層、および/または核生成を助長し、および/または、成長表面と熱電膜との間の歪を吸収するように構成された歪層超格子が挙げられる。例えば、中間層は、基板の格子定数と熱電膜の格子定数との間の格子定数を有する層であってもよく、いくつの実施形態では、基板と熱電膜との間の格子不整合を補うように構成された勾配層であってもよい。

#### 【0018】

他の実施形態では、熱電膜は、約5μmから約100μmの範囲内の厚みにエピタキシャル成長されるとよい。例えば、熱電膜は、約40μm以下の厚みに成長されるとよい。熱電膜は、約1クラック/mm未満、いくつかの実施形態では、約1クラック/cm未満のクラック密度を有しているとよい。

#### 【0019】

本発明のさらに他の実施形態によれば、熱電素子を製造する方法は、基板を、その基板から突出する複数のメサを有する成長表面を画定するように、パターン化するステップを含んでいる。次いで、該成長表面上に、熱電膜がエピタキシャル成長されるようになっている。

#### 【0020】

いくつかの実施形態によれば、熱電膜は、成長表面から突出する複数のメサを備えるように、エピタキシャル成長されるよい。熱電膜の複数のメサは、平面視で橢円または矩形であるとよい。

#### 【0021】

いくつかの実施形態では、熱電膜の複数のメサは、熱電膜内の少なくとも1つのクラックと実質的に平行の方向に延在する細長の矩形メサであるとよい。

#### 【0022】

他の実施形態では、熱電膜の複数のメサは、約200μm以下の直径または幅を有しているとよい。

#### 【0023】

いくつかの実施形態では、熱電膜のメサは、約1クラック/mm未満のクラック密度を

10

20

30

40

50

有しているとよい。

【0024】

他の実施形態では、熱電膜の結晶方位は、成長表面に対して約5°から約30°の範囲内の角度で傾斜しているとよい。熱電膜の複数のメサは、約400μm以下、いくつかの実施形態では、約300μm以下の直径または幅を有しているとよい。

【0025】

他の実施形態では、基板は、基板の結晶方位によって画定された面に対して、約5°から約45°の範囲内のオフカット角でオフセットされた微傾斜成長表面であるとよい。例えば、基板の結晶方位によって画定された面は、{100}面であるとよく、微傾斜成長表面は、{100}面から<110>方向に向かってオフセットされているとよい。また、オフカット角は、約5°から約30°の範囲内にあるとよい。10

【0026】

いくつかの実施形態では、基板をパターン化する前に、熱電膜種層が、基板上にエピタキシャル成長されてもよい。

【0027】

本発明のさらに他の実施形態によれば、熱電素子は、熱電膜を備える熱電要素を備えている。熱電膜は、熱電膜の表面に対して約5°から約30°の範囲内の角度で傾斜した結晶方位を有している。

【0028】

いくつかの実施形態では、熱電膜の結晶方位は、熱電膜の表面に対して約10°から約25°の範囲内の角度で傾斜しているとよい。例えば、いくつかの実施形態では、熱電膜の結晶方位は、熱電膜の表面に対して約11.5°の角度で傾斜しているとよい。他の実施形態では、熱電膜の結晶方位は、熱電膜の表面に対して約20°の角度で傾斜しているとよい。20

【0029】

他の実施形態では、熱電膜は、化合物A Bであるとよく、成分Aは、ビスマス(Bi)、アンチモン(Sb)、および/または鉛(Pb)であるとよく、成分Bは、テルル(Te)および/またはセレン(Se)であるとよい。

【0030】

いくつかの実施形態では、熱電膜は、約5μmから約100μmの範囲内の厚みを有しているとよい。例えば、熱電膜は、約40μm以下の厚みを有しているとよい。熱電膜は、約1クラック/mm未満のクラック密度を有しているとよい。30

【0031】

他の実施形態では、熱電素子は、第1のヘッダーおよび第2のヘッダー、および第2の熱電膜を備える第2の熱電素子をさらに備えているとよい。第2の熱電膜は、第2の熱電膜の表面に対して約5°から約30°の範囲内の角度で傾斜した結晶方位を有しているとよい。第1の熱電要素および第2の熱電素子は、異なる伝導型を有しているとよい。第1の熱電素子および第2の熱電素子は、電気的に直列結合され、第1のヘッダーと第2のヘッダーとの間に熱的に平行に結合されているとよい。

【0032】

本発明のさらに他の実施形態によれば、熱電膜は、約100μm未満の厚みおよび約1クラック/mm未満のクラック密度を有する熱電材料層を備えている。

【0033】

いくつかの実施形態では、熱電材料層の結晶方位は、熱電材料層の表面に対して約5°から約30°の範囲内の角度で傾斜しているとよい。熱電材料層の結晶方位によって画定された面は、(0015)面であるとよい。

【0034】

他の実施形態では、熱電材料層は、約5μmから約100μmの範囲内の厚みを有しているとよい。熱電材料層は、ビスマス(Bi)、アンチモン(Sb)、鉛(Pb)、テルル(Te)、および/またはセレン(Se)を含む化合物であるとよい。50

**【図面の簡単な説明】**

**【0035】**

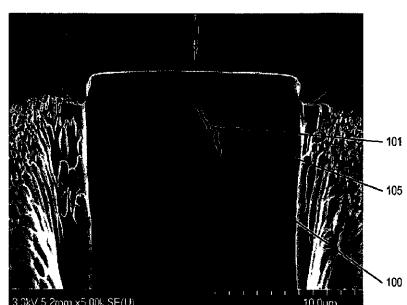

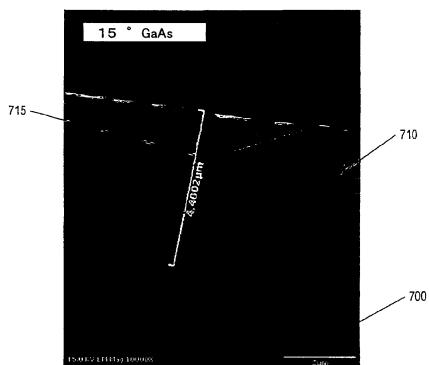

【図1】エピタキシャル成長した熱電膜を示す集束イオンビーム断面画像である。

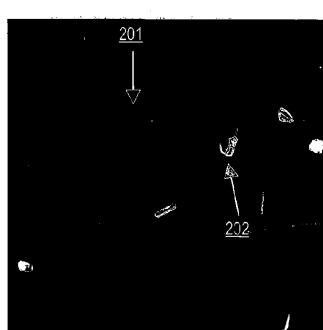

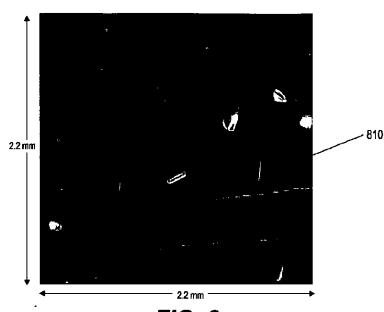

【図2】エピタキシャル成長した熱電膜のクラックおよび表面欠陥を示す光学顕微鏡写真である。

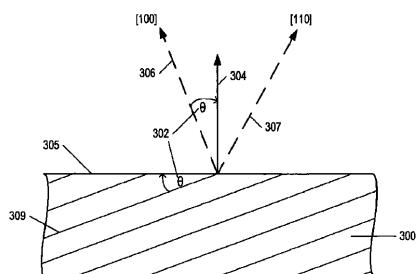

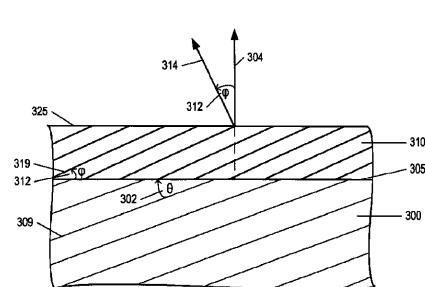

【図3】本発明のいくつかの実施形態による熱電膜をオフカット基板上に作製する方法を示す断面図である。

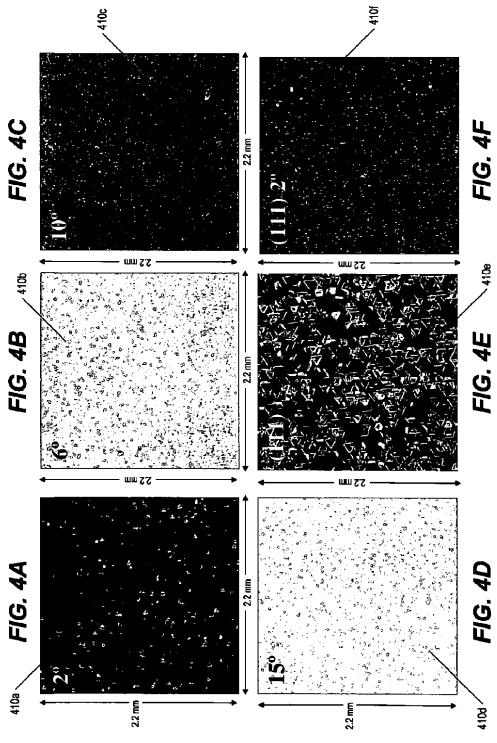

【図4】本発明のいくつかの実施形態による基板を含む種々の結晶方位のガリウムヒ素基板上にエピタキシャル成長したn型熱電膜を示す光学顕微鏡写真である。 10

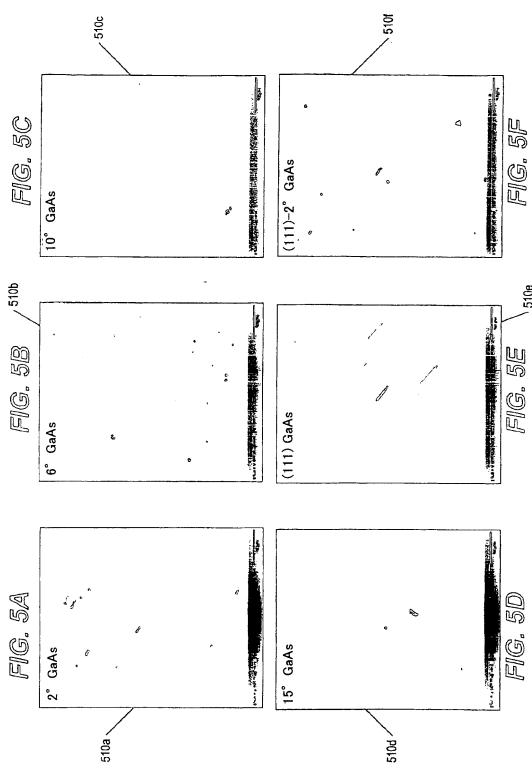

【図5】本発明のいくつかの実施形態による基板を含む種々の結晶方位のガリウムヒ素基板上にエピタキシャル成長したn型熱電膜を示す走査電子顕微鏡(SEM)写真である。

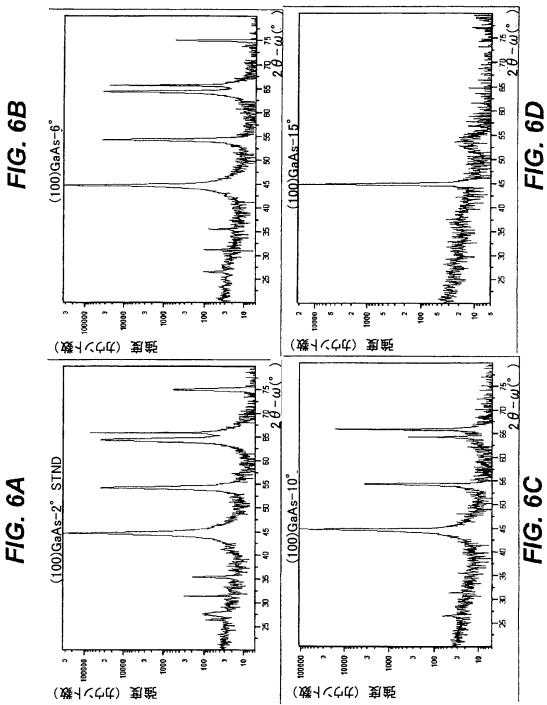

【図6A-6D】本発明のいくつかの実施形態による基板を含む種々の結晶方位のガリウムヒ素基板上にエピタキシャル成長したn型熱電膜のX線回折(XRD)を示すグラフである。

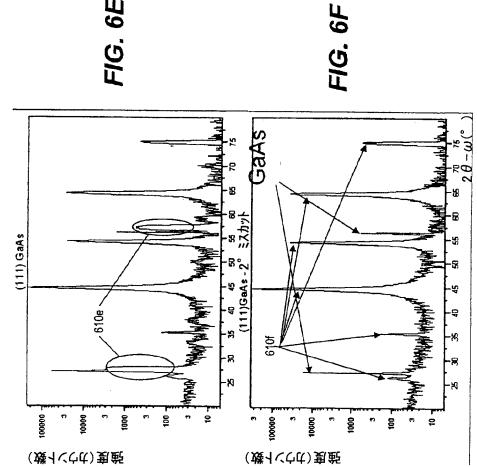

【図6E-6F】本発明のいくつかの実施形態による基板を含む種々の結晶方位のガリウムヒ素基板上にエピタキシャル成長したn型熱電膜のX線回折(XRD)を示すグラフである。

【図7】本発明のいくつかの実施形態によるガリウムヒ素基板上に成長した熱電膜を示す断面図である。

【図8】ガリウムヒ素基板上にエピタキシャル成長した熱電膜を示す光学顕微鏡写真である。 20

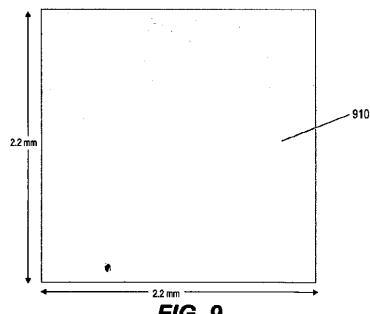

【図9】本発明のいくつかの実施形態によるガリウムヒ素基板上にエピタキシャル成長した熱電膜を示す光学顕微鏡写真である。

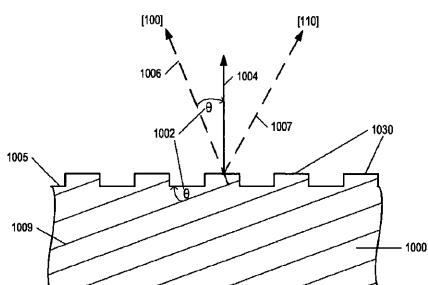

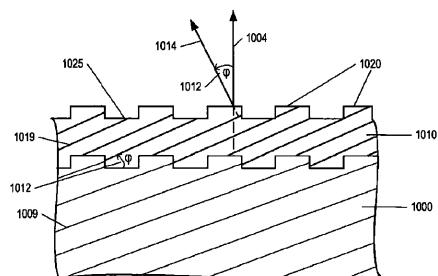

【図10】本発明の他の実施形態によるパターン化された基板上に熱電膜を作製する方法を示す断面図である。

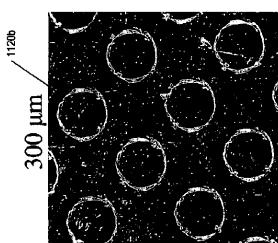

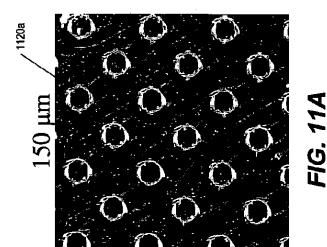

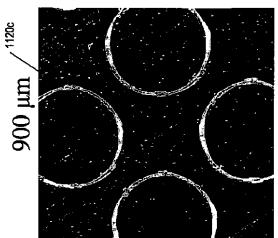

【図11】本発明の他の実施形態による種々のパターン化された基板上にエピタキシャル成長した熱電膜を示す光学顕微鏡写真である。

【図12】本発明のいくつかの実施形態による基板上にエピタキシャル成長した熱電膜を備える熱電素子を製造する方法を示す断面図である。

**【発明を実施するための形態】**

**【0036】**

以下、本発明の実施形態が示されている添付の図面を参照して、本発明をさらに詳細に説明する。しかし、本発明は、多くの異なる形態で実施されてもよく、ここに述べる実施形態に制限されると解釈されるべきではない。むしろ、これらの実施形態は、この開示内容が、綿密かつ完全であり、本発明の範囲を当業者に十分に知らしめるために、設けられている。図面において、層および領域の寸法および相対的な寸法は、明瞭にするために、誇張されている場合がある。なお、全体を通して、同様の番号は、同様の要素を指すものとする。

**【0037】**

ある要素または層が、他の要素または層の「上に(on)」に位置している、または他の要素または層に「接続(connected to)」または「連結(coupled to)」されている、と記述されているとき、ある要素または層は、他の要素または層の上に直接位置していてよいし、または他の要素または層に直接接続または直接連結されていてよいが、介在する1つまたは複数の要素または層が存在していてよいことを理解されたい。対照的に、ある要素が、他の要素または層の「上に直接(directly on)」位置している、または他の要素または層に「直接接続(directly connected to)」または「直接連結(directly coupled to)」されている、と記述されているとき、介在する1つまたは複数の要素または層は、存在しないことになる。また、ここで用いられる「および/または(and/or)」という用語は、1つまたは複数の関連して列挙された項目のいずれかおよび全ての組合せを含むものとする。 40 50

## 【0038】

種々の要素、構成部品、領域、層、および／または区分を記述するために、第1、第2、第3、などの用語がここで用いられることがあるが、これらの要素、構成部品、領域、層、および／または区分は、これらの用語に制限されるべきではないことを理解されたい。これらの用語は、1つの要素、構成部品、領域、層、または区分を他の領域、層、または区分から区別するためにのみに用いられるものである。従って、以下に述べる第1の要素、第1の構成部品、第1の領域、第1の層、または第1の区分は、本発明の示唆から逸脱することなく、第2の要素、第2の構成部品、第2の領域、第2の層、または第2の区分と呼ばれることがあってもよい。

## 【0039】

「真下に（beneath）」、「下方に（below）」、「下側の（lower）」、「上方に（above）」、「上側の（upper）」、などの空間的な相対用語は、図面に示されているような1つの要素または特徴と他の1つまたは複数の要素または特徴との関係を説明するための記述を容易にするために、ここで用いられることがある。これらの空間に関連する用語は、図面に示されている方位に加えて、使用時または操作時の装置の異なる方位を含むことが意図されていることを理解されたい。例えば、もし図面における装置が上下反転された場合、他の要素または特徴の「下方」または「真下」に位置すると記載されている要素は、他の要素または特徴の「上方」に配向されることになるだろう。従って、「下方」という例示的な用語は、上方および下方の両方の方位を含むことができる。装置は、別の方位に配向されることもあるが（例えば、90°または他の方位に回転されることもあるが）、その場合、ここに用いられる空間的な相対用語も、それに応じて解釈されるとよい。また、ここで用いられる「横方向」という用語は、垂直方向と実質的に直交する方向を指している。

10

## 【0040】

ここに用いられる専門用語は、特定の実施形態を説明することのみを目的とし、本発明を制限することを意図するものではない。ここで用いられる単数形の「a」、「an」、および「the」は、文脈が他の解釈を明瞭に示さない限り、複数形も含むものとする。「備える（comprises）」および／または「備えている（comprising）」という用語は、本明細書において用いられる場合、記述された特徴、完全体、ステップ、操作、要素、および／または構成部品の存在を特定するが、1つまたは複数の他の特徴、完全体、ステップ、操作、要素、構成部品、および／またはそれらの群の存在または追加を排除するものではなくことをさらに理解されたい。

20

## 【0041】

本発明の例示的な実施形態は、本発明の理想的な実施形態（および中間的な構造）を概略的に示す断面図を参照して、ここに記載されることになる。従って、例えば、製造技術および／または製造許容値の結果として生じる図示の形状からの差異は、あらかじめ見込まれている。それ故、本発明の実施形態は、ここに示される領域の特定の形状に制限されると解釈されるべきではなく、例えば、製造に起因する形状の寸法誤差も含んでいると解釈されるべきである。例えば、矩形状に示される注入領域は、典型的には、その両縁において、丸みのあるまたは湾曲した特徴部および／または注入濃度の勾配を有している。すなわち、注入濃度は、注入領域から非注入領域に2値的に（不連続に）変化しないことになる。同様に、注入によって形成される埋設領域は、その埋設領域と表面との間の注入が生じる領域にいくらかの注入をもたらす可能性がある。従って、図示される領域は、本質的に概略的であり、それらの形状は、素子の領域の実際の形状を示すことを意図するものではなく、本発明の範囲を制限することを意図するものでもない。

30

## 【0042】

別段の定めがない限り、ここで用いられる（技術用語および科学用語を含む）全ての用語は、本発明が属する技術分野の当業者によって一般的に理解されるのと同一の意味を有している。従って、これらの用語は、この後に創り出される等価の用語を含むことができる。一般的に用いられている辞書に定義されているような用語は、本明細書および関連技

40

50

術の文脈におけるそれらの意味と矛盾しない意味を有すると解釈されるべきであり、ここに別段の定めが明示されていない限り、理想化された意味または過度に形式的な意味に解釈されるべきはないことをさらに理解されたい。ここに記載される全ての刊行物、特許出願、特許、および他の参考文献は、参照することによって、それらの全てがここに含まれるものとする。

#### 【0043】

以下、金属有機化学蒸着（MOCVD）に関連して、いくつかの実施形態を説明することになるが、熱電膜蒸着の他の方法が本発明の実施形態に用いられてもよいことを理解されたい。例えば、分子ビームエピタキシ（MBE）、熱蒸着または電子ビーム蒸着、スパッタリング、蒸気相エピタキシ、交替層エピタキシ、レーザ融除、および／または薄膜結晶成長に用いられる他の技術が用いられてもよい。

10

#### 【0044】

本発明のいくつかの実施形態による熱電膜および／または成長基板の結晶方位は、ミラー指数に基づいて記述されることになる。ここに用いられる[100]のように角括弧で示されるミラー指数は、方向を示し、<100>のような山括弧またはV字状括弧は、結晶対称による等価の方向の群を示している。例えば、立方晶系では、<100>は、[100], [010], [001]方向および／またはこれらの方向のいずれかの逆、すなわち、[-100], [0-10], [00-1]方向を示している。（100）のような丸括弧で示されるミラー指数は、面を示している。立方晶系では、（100）面の法線は、方向[100]である。{100}のような波括弧または中括弧は、山括弧が方向群を示すのと同様に、結晶対称による等価の面の群を示している。

20

#### 【0045】

図1, 2は、エピタキシャル薄膜熱電材料に生じる得るクラックおよび表面欠陥の例を示している。図1の断面に示されているように、ガリウムヒ素（GaAs）基板100上のビスマス・アンチモン・テルル・セレン（BiSbTeSe）系エピタキシャル膜105内に、クラック101が延在している。図2は、BiSbTeSe系エピタキシャル膜205内のクラック201および表面欠陥202をさらに示している。図1, 2に示されている膜105および／または205膜内のクラック生成の推定原因として、GaAs基板とBiSbTeSe系エピタキシャル膜との間の不充分な格子整合、および／またはGaAs基板とBiSbTeSe系エピタキシャル膜との間の熱膨張係数（CTE）の不一致が挙げられる。

30

#### 【0046】

フッ化バリウム（BaF）基板は、BiSbTeSe系エピタキシャル膜用の良好な候補となる基板である。何故なら、この基板は、BiSbTeSe系エピタキシャル膜に対して、良好なCTEおよび格子整合をもたらすからである。シリコン（Si）基板も、BiSbTeSe系エピタキシャル膜用の良好な候補となる基板である。何故なら、この基板は、比較的大きい寸法のものが低コストで入手できるからである。しかし、サファイア基板、炭化ケイ素（SiC）基板、窒化ガリウム（GaN）基板、窒化アルミニウム（AlN）基板、ガラス基板、および／または熱電膜を成長させるのに十分な種をもたらす他の基板が、用いられてもよい。炭化ケイ素（SiC）、窒化アルミニウム（AlN）、GaAsおよび／または歪層超格子のような中間層が、成長核生成を助長し、および／または歪に吸収するために、基板上に形成されてもよい。

40

#### 【0047】

本発明のいくつかの実施形態では、GaAs基板上にエピタキシャル成長したBiSbTeSe系膜のような熱電膜内のクラックの密度に及ぼす2つのパラメータ、すなわち、(1) GaAs結晶方位、および(2)エピタキシー前のGaAsのパターン化の影響を検討している。

#### 【0048】

図3A, 3Bは、本発明のいくつかの実施形態による成長基板上に熱電膜を作製する方法を示している。図3Aを参照すると、成長表面305を備える基板300が設けられて

50

いる。例えば、基板 300 は、ガリウムヒ素 (GaAs) 基板、シリコン (Si) 基板、フッ化バリウム (BaF) 基板、サファイア基板、炭化ケイ素 (SiC) 基板、窒化ガリウム (GaN) 基板、窒化アルミニウム (AlN) 基板、および / または、ガラス基板であればよい。結晶表面 305 は、基板 300 の結晶方位 (斜線 309 によって示されている) によって画定された面に対してオフカットされている。ここで用いられる「オフカット (offcut)」という用語は、他の表面または面に対する基板表面の不整合切断 (mis cut)、不整合方位 (misorientation)、および / または、傾斜 (tilt) を指している。例えば、基板 300 が立方晶構造を有する GaAs 基板の場合、成長表面 305 は、基板 300 の (100) 面に沿った結晶方位 309 に対してオフカットされることになる。また、前述したように、表面または面の方向は、その表面または面と垂直の方向または直交する方向によって画定されている。従って、「オフカット」表面または「微傾斜 (vicinal)」表面は、特定の表面または面の法線に対して軸外配向 (off-axis) したまたは傾斜した法線を有する表面として記述されることもある。具体的には、GaAs 基板の場合、成長表面 305 の法線 304 は、(100) 面の方向 306、すなわち、[100] 方向に対して軸外配向されていることになる。

#### 【0049】

本発明の実施形態によるオフカットウエハは、種々の異なる方法によって、作製することができる。例えば、長い GaAs ブール (元結晶) を、GaAs 格子の c 面に対してオフカット角を有するウエハ表面をもたらすように、配向させ、次いでスライスすることができる。また、微傾斜 GaAs を微傾斜テンプレート上に成長させ、微傾斜 GaAs 材料が堆積した後、微傾斜テンプレートを取り外し、これによって、独立した微傾斜 GaAs 基板を生じさせることもできる。オフカット成長表面 305 をもたらす他の技術は、当業者によく知られているので、ここでは、これ以上の説明を省略することにする。

#### 【0050】

図 3A をさらに参照すると、本発明のいくつかの実施形態による基板 300 の成長表面 305 は、{100} 面から <110> 方向に向かって約 5° から約 45° の範囲内の角度 (以後、「オフカット角」302 と呼ぶ) でオフカットされた微傾斜表面である。例えば、いくつかの実施形態では、(100) 面に対する成長表面 305 のオフカット角 302 は、約 10° から約 30° の範囲内にあるとよい。さらに詳細には、オフカット角 302 は、<110> 方向に向かって約 15° であるとよい。このような成長表面 305 は、ここでは、15° オフ (100) 面とも呼ばれる。従って、図 3A に示されているように、成長表面 305 の法線 304 は、[100] 方向 306 から [110] 方向 307 に向かって約 5° から約 30° のオフカット角 302 で軸外傾斜していることになる。意図的にオフカットされた成長表面 305 を用いることによって、図 3B に示されているように、成長表面 305 に沿って、原子的なステップ縁および / またはキンク (図示せず) が生じるが、このようなステップ縁および / またはキンクは、成長表面 305 上への熱電層 310 の成長に対して優先的な核生成サイトとして機能することになる。オフカット角 302 の選択によって、結晶表面 305 におけるステップの横方向周期性を画定することができる。何故なら、微傾斜表面のオフカット角が、ステップ間の平均間隔を決定することになるからである。

#### 【0051】

図 3B を参照すると、熱電 (TE) 膜 310 が、基板 300 の成長表面 305 上にエピタキシャル成長されている。熱電膜 310 は、(ビスマス (Bi)、アンチモン (Sb)、および / または鉛 (Pb) のような) V 族元素および (テルル (Te) および / またはセレン (Se) のような) VI 族元素を含む化合物であるとよい。例えば、いくつかの実施形態では、熱電膜 310 は、(反応炉内において、トリメチルビスマス (TMBi) およびジイソプロピルテルル (DIPTe) の熱分解反応によって、約 350 の成長温度および約 350 トールの成長圧力で行われる) 金属有機化学蒸着 (MOCVD) によって、GaAs 基板上に成長した  $\text{Bi}_2\text{Te}_3$  のエピタキシャル膜であるとよい。このようなエピタキシャル成長の技術は、例えば、ヴェンカタスプラマニアンらによる以下の刊行物、

10

20

30

40

50

すなわち、「薄膜熱電用途用の  $\text{Bi}_2\text{Te}_3$  および / または  $\text{Sb}_2\text{Te}_3$  およびそれらの超格子構造の MOCVD (MOCVD of  $\text{Bi}_2\text{Te}_3$  and/or  $\text{Sb}_2\text{Te}_3$  and their superlattice structures for thin-film thermoelectric applications)」(Journal of Crystal Growth, 170、1997年) および「低温有機金属エピタキシおよび熱電材料における超格子構造へのその応用(Low-temperature organometallic epitaxy and its application to superlattice structures in thermoelectrics)」(Applied Physics Letters, 75巻、第8号、1999年)にさらに記載されている。これらの開示内容は、参照することによって、それらの全体がここに含まれるものとする。熱電膜 310 は、単一合金層、多層、および / または勾配層を備えることができ、定常ガス流れ、交替流れ、中断、などを用いて、前述した V 族元素および / または V I 族元素の 1 つを成長させることによって、得られるとい。10

#### 【0052】

図 3B をさらに参考すると、成長表面 305 のオフカットによって、熱電膜 310 の c 軸に沿った結晶方向は、成長表面 305 と直交していない。さらに詳細には、熱電膜 310 の c 面は、(斜線 319 によって示されている) 結晶方位を有している。この結晶方位 319 は、成長表面 305 によって画定された面および膜 310 の表面 325 によって画定された面に対して、約 5° から約 30° だけ傾斜している。従って、図 3B に示されているように、熱電膜 310 の c 軸 314 は、成長表面 305 の法線 304 に対して約 5° から約 30° の範囲内の角度 312 だけ軸外傾斜している。例えば、角度 312 は、約 10° から約 25° の範囲内、さらに具体的には、約 18° から約 24° の範囲内にあるとよい。いくつかの実施形態では、熱電膜 310 の結晶方位 319 は、成長表面 305 の面に対して約 11.5° の角度 312 で傾斜しているとよく、従って、膜 310 の c 軸 314 は、法線 304 から約 11.5° の角度で軸外配向されているとよい。他の実施形態では、結晶方位 319 は、成長表面 305 の面に対して約 20° の角度 312 で傾斜しているとよい。従って、成長表面 305 のオフカット角 302 は、成長表面 305 上に成長する熱電膜 310 の結晶傾斜角 312 に影響を及ぼしていることになる。成長表面 305 のオフカット角 302 は、いくつかの実施形態では、成長表面 305 上に成長する熱電膜 310 の結晶傾斜角 312 よりも大きくなっているとよいが、他の実施形態では、オフカット角 302 は、結晶傾斜角 312 より小さいかまたは等しくなっていてもよい。20

#### 【0053】

熱電膜 310 は、約 5  $\mu\text{m}$  から約 100  $\mu\text{m}$  の厚みに成長されるとよい。例えば、いくつかの実施形態では、熱電膜 310 は、約 40  $\mu\text{m}$  以下の厚みを有しているとよい。加えて、本発明のいくつかの実施形態による基板上にエピタキシャル成長した熱電膜では、従来の基板、例えば、{100} 面に対して約 2° のオフカット角でオフカットされた成長表面を有する基板上に成長した熱電膜と比べて、クラックおよび / または表面欠陥の発生率を減少させることができる。例えば、いくつかの実施形態では、熱電膜 310 は、約 1 クラック / mm よりも少ないクラック密度を有することができる。ここで用いられる「クラック密度」または「クラック / mm」という用語は、熱電膜を横切って引かれた所定長さの線と交差する熱電膜のクラックの数を該線の所定長さで割ることに基づく直線的測定値を指している。30

#### 【0054】

図 3A, 3B では、約 5° から約 30° の間で変化するオフカット角を主に参考して説明したが、他の基板材料、他の基板方位、他のオフカット角、および他のオフカット方向が、本発明の範囲から逸脱することなく、用いられてもよい。さらに、本発明のいくつかの実施形態によるオフカット角および / またはオフカット方向に基づいて作製された基板は、製造許容差によって、意図されたオフカット角およびオフカット方向に対してわずかな量だけ変動してもよい。換言すれば、ここに述べるオフカット角およびオフカット方向は、意図された値を指し、本発明の範囲から逸脱しない限り、わずかな差異が生じることも想定されている。加えて、製造公差に起因して、熱電層の堆積は、必ず、微傾斜表面上に生じることになる。従って、本発明の範囲は、基板のオフカットが改良された材料4050

特性および／または装置特性をもたらすように意図的に制御された条件下での熱電層の堆積を含んでいる。

#### 【0055】

図4A～4Fは、本発明のいくつかの実施形態による基板と関連して定められたいいくつかの異なる結晶方位を有するGaAs基板上にエピタキシャル成長したn型熱電膜の例を示している。さらに詳細には、図4Aは、(100)面から<110>方向に向かって約2°の角度でオフカットされた成長表面を有するGaAs基板上に成長したn型エピタキシャル膜410a(以後、2°膜とも呼ぶ)を示す光学顕微鏡写真である。図4Bは、(100)面から<110>方向に向かって約6°の角度でオフカットされた成長表面を有するGaAs基板上に成長したn型エピタキシャル膜410b(以後、6°膜とも呼ぶ)を示す光学顕微鏡写真である。図4Cは、(100)面から<110>方向に向かって約10°の角度でオフカットされた成長表面を有するGaAs基板上に成長したn型エピタキシャル膜410c(以後、10°膜とも呼ぶ)を示す光学顕微鏡写真である。図4Dは、(100)面から<110>方向に向かって約15°の角度でオフカットされた成長表面を有するGaAs基板上に成長したn型エピタキシャル膜410d(以後、15°膜とも呼ぶ)を示す光学顕微鏡写真である。図4Eは、(111)面と平行の成長表面を有するGaAs基板上に成長したn型エピタキシャル膜410e(以後、(111)膜とも呼ぶ)を示す光学顕微鏡写真である。図4Fは、(111)面から<2-1-1>方向に向かって約2°の角度でオフカットされた成長表面を有するGaAs基板上に成長したn型エピタキシャル膜410f(以後、(111)2°膜とも呼ぶ)を示す光学顕微鏡写真である。図4A～4Fの光学顕微鏡写真は、2.2mm×2.2mmの膜寸法を示している。

10

20

30

#### 【0056】

図4A～4Fの実施形態では、2～4μm厚みのn型膜をまず成長させ、次いで、このn型膜に対して、X線回折、光学および電子顕微鏡検査、およびゼーベック測定およびホール測定を行った。全ての膜は、実質的に同様の成長条件下で成長させている。図4A～4Fに示されているように、図4Eの(111)膜410eおよび図4Aの2°膜410aでは、他の膜410b、410c、410d、および410fにおけるよりも、表面欠陥が大きくなっている。また、光学顕微鏡検査によって、クラックが2°膜410a(約6クラック/mm)および(111)2°膜410f(約4クラック/mm)に生じていることが、明らかである。従って、(100)面から<110>方向に向かって約5°から約30°の範囲内のオフカット角度でオフカットされた基板上に成長した図4B、4C、4Dの膜410b、410c、410dでは、膜410a、410eと比較して、表面欠陥が比較的少なく、肉眼で見えるクラックが殆ど存在しない(すなわち、約0.45クラック/mm未満にすぎない)ことが、明らかにされたことになる。なお、<110>方向15°オフ(100)面上のより厚いn型膜およびより厚いp型膜に対して、追加的な成長実験も行った。これについては、以下、図7、9および表2を参照して、さらに詳細に説明する。

#### 【0057】

図5A～5Fは、本発明のいくつかの実施形態による基板と関連して定められたいいくつかの異なる結晶方位を有するGaAs基板上にエピタキシャル成長したn型熱電膜の走査電子顕微鏡(SEM)写真を示している。さらに詳細には、図5Aは、(100)面から<110>方向に向かって約2°の角度でオフカットされた成長表面を有するGaAs基板上に成長したn型エピタキシャル膜510a(以後、2°膜とも呼ぶ)を示している。図5Bは、(100)面から<110>方向に向かって約6°の角度でオフカットされた成長表面を有するGaAs基板上に成長したn型エピタキシャル膜510b(以後、6°膜とも呼ぶ)を示している。図5Cは、(100)面から<110>方向に向かって約10°の角度でオフカットされた成長表面を有するGaAs基板上に成長したn型エピタキシャル膜510c(以後、10°膜とも呼ぶ)を示している。図5Dは、(100)面から<110>方向に向かって約15°の角度でオフカットされた成長表面を有するGaA

40

50

s 基板上に成長した n 型エピタキシャル膜 510d (以後、15°膜とも呼ぶ) を示している。図 5 E は、(111)面と平行の成長表面を有する GaAs 基板上に成長した n 型エピタキシャル膜 510e (以後、(111)膜とも呼ぶ) を示している。図 5 F は、(111)面から <2-1-1> 方向に向かって約 2° の角度でオフカットされた成長表面を有する GaAs 基板上に成長した n 型エピタキシャル膜 510f (以後、(111)2°膜とも呼ぶ) を示している。

#### 【0058】

図 5 A ~ 5 F の SEM 顕微鏡写真に示されているように、2°膜 510a、(110)膜 510e、および(111)2°膜 510f では、表面欠陥が明らかに認められる。しかし、6°膜 510b、10°膜 510c、および 15°膜 510d では、表面欠陥が殆ど認められない。また、クラックが、2°膜 510a (約 16 クラック/mm) および(111)2°膜 510f (約 10 クラック/mm) において明らかに認められる。一方、図 5 D に示されているように、15°膜 510d では、図 5 B の 6°膜 510b におけるのと同様に、他の膜 510a、510e、510f におけるよりもクラックが減少している。従って、(100)面から <110> 方向に向かって約 5° から約 30° の範囲内のオフカット角度でオフカットされた基板上に成長した膜 510b ~ 510d は、膜 510a、510e、510f と比較して、クラック密度が少なく、表面欠陥もほとんど存在しないことが、明らかにされたことになる。

#### 【0059】

図 6 A ~ 6 F は、本発明のいくつかの実施形態による基板と関連して定められたいつかの異なる結晶方位を有する GaAs 基板上にエピタキシャル成長した n 型熱電膜の X 線回折 (XRD) を示している。さらに詳細には、図 6 A は、(100)面から <110> 方向に向かって約 2° の角度でオフカットされた成長表面を有する GaAs 基板上に成長した n 型エピタキシャル膜 (以後、2°膜とも呼ぶ) の X 線回折を示している。図 6 B は、(100)面から <110> 方向に向かって約 6° の角度でオフカットされた成長表面を有する GaAs 基板上に成長した n 型エピタキシャル膜 (以後、6°膜とも呼ぶ) の X 線回折を示している。図 6 C は、(100)面から <110> 方向に向かって約 10° の角度でオフカットされた成長表面を有する GaAs 基板上に成長した n 型エピタキシャル膜 (以後、10°膜とも呼ぶ) の X 線回折を示している。図 6 D は、(100)面から <110> 方向に向かって約 15° の角度でオフカットされた成長表面を有する GaAs 基板上に成長した n 型エピタキシャル膜 (以後、15°膜とも呼ぶ) の X 線回折を示している。図 6 E は、(111)面と平行の成長表面を有する GaAs 基板上に成長した n 型エピタキシャル膜 (以後、(111)膜とも呼ぶ) の X 線回折を示している。図 6 F は、(111)面から <2-1-1> 方向に向かって約 2° の角度でオフカットされた成長表面を有する GaAs 基板上に成長した n 型エピタキシャル膜 (以後、(111)2°膜とも呼ぶ) の X 線回折を示している。

#### 【0060】

図 6 A ~ 6 D に示されているように、(100)面から微傾斜した GaAs 上に堆積された膜では、Bi<sub>2</sub>Te<sub>3</sub>の(0015)面の主ピークが、2 = 略 45°において観察されるだろう。他の観察可能な主なピークは、GaAs 基板に関連するピーク、または Bi<sub>2</sub>Te<sub>3</sub>の(00?) (? = 9, 12, 15, 18, 21, 24)の反射に関連するピークであり、これは、結晶 c 軸に沿った膜の成長を示している。

#### 【0061】

図 6 E, 6 F にさらに示されているように、(111)2°膜において観察されるピーク 610f は、(00?) (? = 9, 12, 15, 18, 21, 24) と関連している。(111)膜の場合、非 c 面方位を示すいくつかの他の未確認のピーク 610e が、観察されるだろう。クラックが観察されるが、(111)2°膜の結晶構造は、比較的良好であるように見受けられる。

#### 【0062】

表 1 は、図 4 A ~ 4 F, 5 A ~ 5 F, 6 A ~ 6 F を参照して前述したような種々の Ga

10

20

30

40

50

A s 基板上にエピタキシャル成長した n 型熱電膜の特性をさらに示している。表 1 に示されている試料は、実質的に同様の成長条件を用いて、成長させたものである。

### 【0063】

【表 1】

| 試料            | 厚み<br>( $\mu$<br>m) | 堆積率<br>( $\text{Å}/\text{m in}$ ) | 抵抗率<br>( $\Omega \text{ cm}$ ) | 移動度<br>( $\text{cm}^2/\text{Vs}$ ) | キャリア<br>( $\text{cm}^{-3}$ ) | ゼーベ<br>ック<br>( $\mu \text{V/K}$ ) | P F<br>( $\mu \text{WK-2 cm}^{-1}$ ) |

|---------------|---------------------|-----------------------------------|--------------------------------|------------------------------------|------------------------------|-----------------------------------|--------------------------------------|

| 2° 膜          | 2. 5                | 188                               | 2. 38<br>E - 0 3               | 178                                | 1. 48 E<br>+ 1 9             | -371                              | 58                                   |

| 6° 膜          | 3. 1                | 238                               | 2. 11<br>E - 0 3               | 220                                | 1. 34 E<br>+ 1 9             | -304                              | 44                                   |

| 10° 膜         | 4. 2                | 329                               | 3. 41<br>E - 0 3               | 185                                | 9. 91 E<br>+ 1 8             | -287                              | 24                                   |

| 15° 膜         | 4. 4                | 346                               | 2. 87<br>E - 0 3               | 191                                | 1. 41 E<br>+ 1 9             | -278                              | 27                                   |

| (111) 膜       | 1. 1                | 71                                | 1. 06<br>E - 0 3               | 215                                | 2. 74 E<br>+ 1 9             | -329                              | 102                                  |

| (111) 2°<br>膜 | 2. 2                | 163                               | 1. 76<br>E - 0 3               | 188                                | 1. 88 E<br>+ 1 9             | -318                              | 57                                   |

### 【0064】

表 1 に示されているように、本発明のいくつかの実施形態による 6° 热電膜、10° 热电膜、および 15° 热电膜は、2° 热电膜、(111) 热电膜、および / または (111) 2° 热电膜と比較して、低いゼーベック係数、従って、低い热电出力因子 (P F) を示している。しかし、本発明のいくつかの実施形態によってオフカットされた成長表面を有する基板に対して、条件が改良され、および / または最適化されたとき、6° 热电膜、10° 热电膜、および 15° 热电膜の出力因子を、2° 热电膜、(111) 热电膜、および / または (111) 2° 热电膜の出力因子と同程度とすることができるに留意されたい。従って、本発明のいくつかの実施形態による (100) 面に対して約 5° から約 30° の範囲内のオフカット角でオフカットされた成長表面を有する基板上に成長した热电膜は、クラックが少ない改良された热电性能をもたらすことができる。

### 【0065】

図 7 は、本発明のいくつかの実施形態による GaAs 基板の膜特性を示している。図 7 を参照すると、GaAs の (100) 面から 15° 軸外配向された表面 700 上に成長した热电膜 710 の SEM 断面が示されている。膜 710 は、略 4.4  $\mu\text{m}$  の厚み 715 を有している。X 線回折測定によれば、膜 710 の c 面の格子方位は、基板表面 700 によって画定された面に対して、約 11.5° である。対照的に、基板の (100) 面から 2° 軸外配向された表面上に成長した従来のエピタキシャル膜の c 面の格子方位は、基板表面によって画定された面に対して、約 1° である。また、基板表面 700 のオフカット角が大きくなると、例えば、核生成キンクサイトの数の増加によって、成長率が増大することになる。この後、本発明のいくつかの実施形態による 15° 軸外配向された基板上に、n 型膜を堆積させている。この場合、著しいクラックが存在しない 6  $\mu\text{m}$  の膜および 10.8  $\mu\text{m}$  の膜が観察された。本発明のいくつかの実施形態による热电膜の堆積率は、2° 軸外配向された基板上に堆積された従来のエピタキシャルの略 2 倍であることが見出されている。

### 【0066】

図 8 は、(100) 面に対して <100> 方向に向かって 2° の角度でオフカットされた GaAs 成長表面上にエピタキシャル成長した p 型热电膜 810 の光学顕微鏡写真を示し、図 9 は、(100) 面に対して <110> 方向に向かって 15° の角度でオフカットされた GaAs 成長表面上にエピタキシャル成長した p 型热电膜 910 の光学顕微鏡写真を示している。図 8, 9 の p 型膜は、それぞれの基板上に略 6  $\mu\text{m}$  の厚みに成長させたも

10

20

30

40

50

のである。図9に示されているように、15°軸外配向された基板上に成長したp型熱電膜910では、n型膜と同様、クラックが実質的に存在せず、表面形態が比較的良好である（すなわち、表面欠陥を殆どまたは全く有していない）。

### 【0067】

<110>方向に向かって15°の角度でオフカットされたGaAs上に成長した上記のp型熱電膜およびn型熱電膜に対するホール測定およびゼーベック測定のデータが、以下の表2に示されている。

### 【0068】

【表2】

| 膜の伝導型 | 厚み<br>(μm) | 抵抗率<br>(Ω cm) | 移動度<br>(cm <sup>2</sup> /V s) | キャリア<br>(cm <sup>-3</sup> ) | ゼーベック<br>(μV/K) | P F<br>(μWK <sup>-2</sup> cm <sup>-1</sup> ) |

|-------|------------|---------------|-------------------------------|-----------------------------|-----------------|----------------------------------------------|

| p型    | 3.9        | 2.25E<br>-03  | 219                           | 1.27E<br>+19                | 275             | 34                                           |

| p型    | 5.6        | 1.25E<br>-03  | 254                           | 1.96E<br>+19                | 268             | 57                                           |

| p型    | 6.2        | 8.32E<br>-04  | 299                           | 2.51E<br>+19                | 262             | 83                                           |

| n型    | 6.3        | 1.84E<br>-03  | 252                           | 1.35E<br>+19                | -347            | 65                                           |

| n型    | 10.8       | 1.71E<br>-03  | 265                           | 1.38E<br>+19                | -350            | 72                                           |

10

20

30

40

### 【0069】

図10A, 10Bは、本発明の他の実施形態によるパターン化された基板上に熱電膜を作製する方法を示している。図10Aを参照すると、基板1000は、基板1000の表面1005から突出する複数のメサ1030を画定するように、パターン化され、次いでエッティングされている。例えば、マスクパターン（図示せず）が基板1000の表面1005上に形成され、エッティングプロセスを用いて、マスクによって覆われていない表面1000の部分を除去し、次いで、マスクパターンが取り外され、メサ1030を画定するようにされているとよい。メサ1030は、平面視で実質的に円形であるとよく、いくつかの実施形態では、約200μm未満の直径を有しているとよい。しかし、他の実施形態では、メサ1030は、平面視で橢円または矩形であってもよい。さらに他の実施形態では、メサ1030は、平面視で「ストライプ(stripes)」を画定するように基板1000に沿って延在する細長の矩形であってもよい。これらのストライプは、クラックが典型的に形成される方向と平行であるように、配向されているとよい。例えば、(100)GaAsまたは他の特定の基板上のn型BiTeでは、クラックが特定の方向に形成されることが知られているが、メサ1030は、名目上のクラック間隔よりも小さい間隔で、この方向と平行に延在するように形成されているとよい。従って、熱電膜1010が図10Bを参照して以下に述べるように基板1000の表面1005上にエピタキシャル成長したとき、実質的にクラックのないストライプ状の熱電膜メサ1020を作製することができる。

### 【0070】

いくつかの実施形態では、基板1000の表面1005は、例えば、基板1000の結晶方位1009によって画定された{100}面からオフカットされた微傾斜成長表面であるとよい。具体的に、基板1000の表面1005は、{100}面から<110>方向に向かって約30°以下のオフカット角でオフカットされているとよい。さらに具体的には、図10Aに詳細には示されているように、成長表面1005の法線1004は、[100]方向1006から[110]方向1007に向かって、約0°から約45°の範囲内のオフカット角1002で傾斜している。例えば、オフカット角1002は、約5°から約30°の範囲内、いくつかの実施形態では、約10°から約25°の範囲内に

50

あるとよい。本発明の特定の実施形態では、オフカット角 1002 は、(100)面から<110>方向に向かう約15°であるとよい。

#### 【0071】

図10Bを参照すると、熱電(TE)膜1010が、基板1000の表面1005上にエピタキシャル成長されている。熱電膜1010は、(ビスマス(Bi)、アンチモン(Sb)、および/または鉛(Pb)のような)V族元素、および(テルル(Te)および/またはセレン(Se)のような)VI族元素を含む化合物であるとよい。熱電膜1010は、図3A, 3Bを参照して前述したのと実質的に同様の方法によって、基板1000の成長表面1005上にc軸1014に沿って成長されるとよく、従って、これ以上の説明は、省略する。膜1010の成長の前に行われる図10Aを参照して前述した基板1000のパターン化によって、熱電膜メサ1020が、成長表面1005から突出して形成されることになる。メサ1020は、同様に、平面視で実質的に円形、楕円、または矩形であってもよい。例えば、基板1000のメサ1030が実質的に円形である場合、実質的に円形のメサ1020が、成長表面1005から同様に突出して形成され、いくつかの実施形態では、これらのメサ1020は、同様に、約200μm以下の直径を有することができます。同様に、基板1000のメサ1030が実質的に矩形である場合、メサ1020も実質的に矩形であり、いくつかの実施形態では、同様に、クラックが典型的に形成される周知の方向と平行に延在することになる。膜1010の厚みに依存して、メサ1020の寸法が変化することがあり、および/または、メサ1020の鮮明度が、例えば、パターンが押し流されることによって、低下することがある。

10

20

#### 【0072】

図10Bをさらに参照すると、基板1000の表面1005が微傾斜(100)表面である場合、c軸1014に沿った熱電膜1010の結晶成長方向は、表面1005と直交していない。さらに詳細には、熱電膜1010のc面は、(斜線1019によって示されている)結晶方位を有しているが、この結晶方位1019は、表面1005によって画定された面および/または膜1010の表面1025によって画定された面に対して約30°以下の角度で傾斜している。換言すると、図10Bに詳細に示されているように、熱電膜1010のc軸1014は、表面1005の法線1004に対して約0°から約30°の角度1012で軸外傾斜している。いくつかの実施形態では、熱電膜1010の結晶傾斜角1012は、約5°から約30°の範囲内にあるとよい。例えば、熱電膜1010の結晶傾斜角1012は、約10°から約30°の範囲内、特定の実施形態では、約15°から約25°の範囲内にあればよい。クラックは、メサ1020間の熱電膜1010の表面1025の部分に生じる可能性があるが、メサ1020の突出している表面によって画定された熱電膜1010の部分は、以下に述べるように、メサ1020の大きさにもよるが、クラックを実質的に有していない。

30

#### 【0073】

図10A, 10Bでは、基板上の熱電膜のエピタキシャル成長を促進する楕円状および/または矩形状のメサを画定するように、基板をエッチングする方法に関連して、本発明を説明したが、本発明は、基板の特定の部分に熱電膜を選択的にエピタキシャル成長させる他の方法を含んでいてもよい。例えば、二酸化ケイ素(SiO<sub>2</sub>)マスクのようなマスクが、基板1000の楕円状および/または矩形状の部分を露出させるように、基板1000上に形成されてもよい。このマスクパターンは、マスクで覆われた領域における成長を防ぎ、および/または阻止するものである。従って、このような実施形態では、「メサ」は、基板1000から突出せず、むしろ、熱電膜がエピタキシャル成長される基板1000のエッチングされていない領域またはマスクで覆われていない領域を概して指すことになる。加えて、熱電膜の選択エピタキシャル成長を行うために、基板をマスキングし、および/またはエッチングする前に、種層を基板の表面上に成長させてもよい。例えば、基板をエッチングする前に、BiTe(または他のV族-VI族合金)の種層を基板1000上に成長させ、これによって、基板1000から突出するメサ1030をもたらすようにしてもよい。また、基板にマスクを形成する前に、このようなBiTe(または他の

40

50

V族 - VI族合金)の種層を基板1000上に成長させ、これによって、マスク領域における成長を防ぎ、および/または阻止するようにしてもよい。種層は、核成長を助長し、マスク材料は、直接的な成長を防ぎ、基板表面の面内に高品質の横方向成長を可能にするものである。このような横方向成長は、合体してもよいし、または合体しなくてもよい。マスクの寸法は、クラックの発生率を低減し、阻止しおよび/または最小限に抑えるように選択され、また選択される基板に依存して変更されてもよい。

#### 【0074】

図11A～11Cは、本発明の他の実施形態による種々のパターン化された基板上にエピタキシャル成長した熱電膜を示す光学顕微鏡写真である。図11A～11Cを参照すると、実質的に円形のメサ1120a～1120cは、パターン化され、次いで、(100)面の2°軸外配向された成長表面を有するGaAs基板内への反応性イオンエッティング(RIE)によって、エッティングされたものである。角度および寸法の変動を調べるために、種々の直径のメサをエッティングによって形成し、次いで、2.7μm厚みの膜を各ウエハ上に成長させている。さらに詳細には、図11Aは、約150μmの直径を有するメサ1120aによってパターンされたGaAs基板上に熱電膜を成長させた結果を示している。同様に、図11Bは、約300μmの直径を有するメサ1120bによってパターンされたGaAs基板上に熱電膜を成長させた結果を示し、図11Cは、約900μmの直径を有するメサ1120cによってパターン化されたGaAs基板上に熱電膜を成長させた結果を示している。図11Aに示されているように、150μmメサ1120a内には、比較的小さいクラックが観察されている。具体的には、150μmのメサ1120aは、約1クラック/mm未満、いくつかの実施形態では、約0.1クラック/mmのクラック密度を有している。しかし、図11Bの300μmのメサ1120bでは、いくらかのクラック(約1.7クラック/mm)が観察されている。さらに、図11Cの900μmのメサ1120cでは、かなり多くのクラック(約2.5クラック/mm)が観察されている。従って、本発明のいくつかの実施形態では、約200μ以下の直径を有するメサによってパターン化された基板上に成長した熱電膜が用いられるといよい。

#### 【0075】

しかし、パターン化された基板の成長表面が約5°から約45°の範囲内のオフカット角で傾斜している実施形態では、前述したように、クラック生成が減少するので、所望のクラック密度を維持しながら、より大きい直径のメサが設けられてもよい。例えば、(100)面の6°または15°軸外配向された結晶面を有するGaAs基板を用いて、約400μm未満、いくつかの実施形態では、約300μm未満の直径を有する実質的にクラックのない(すなわち、約1クラック/mm未満)のメサを成長させることができる。また、メサが平面視で四辺形および/または実質的に矩形である実施形態では、メサは、前述した直径に対応する幅を有しているとよい。従って、本発明のいくつかの実施形態では、パターン化された基板と大きい角度でオフカットされた成長表面を有する基板の組合せを用いて、クラックが少ない熱電膜をもたらすことができる。

#### 【0076】

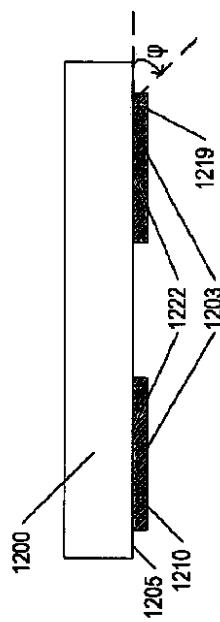

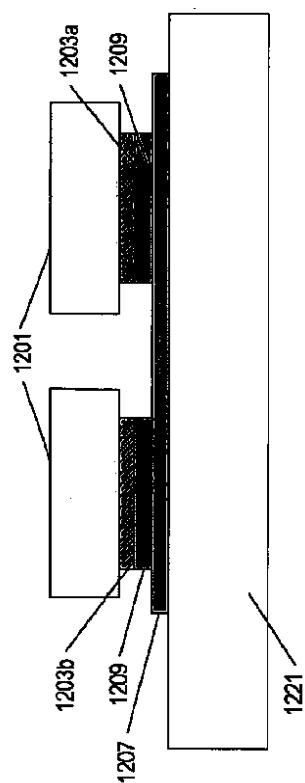

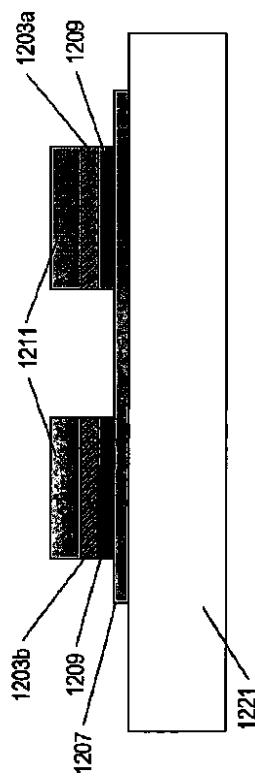

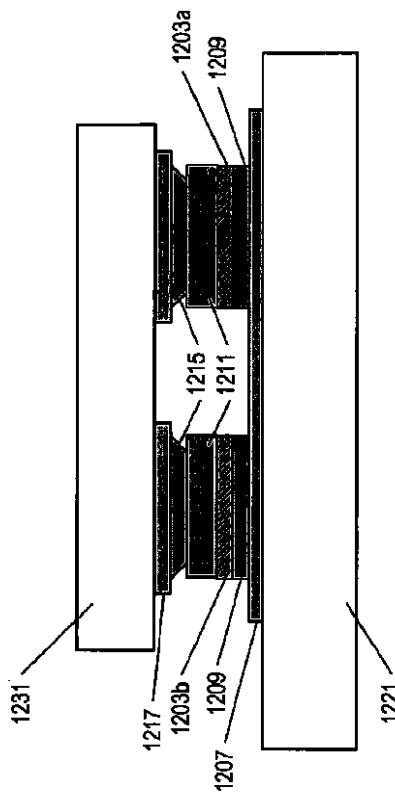

図12A～12Dは、本発明のいくつかの実施形態による熱電素子に用いられるP-N熱電対のアセンブリを示す断面図である。ここで用いられる「熱電要素」という用語は、通流する電流に応答する熱電作用の熱ポンピング(加熱または冷却)および/または熱電素子の両端の温度勾配に応答する発電をもたらすのに十分なゼーベック係数を有する(Bi<sub>2</sub>Te<sub>3</sub>のような)本発明のいくつかの実施形態による熱電膜の層を有する構造を指している。熱電要素は、例えば、1つまたは複数のP-N対を備えているとよい。ここで、P-N対は、P型熱電要素およびN型熱電要素を有し、これらのP型熱電要素およびN型熱電要素は、電気的に直列結合されると共に、熱的に平行に結合され、熱電加熱/冷却、および/または発電をもたらすように構成されている。

#### 【0077】

図12Aに示されているように、(ビスマステルルまたはBi<sub>2</sub>Te<sub>3</sub>のような)熱電材料1210の薄膜層が、例えば、図3A, 3Bを参照して前述したように、(GaAs基

10

20

30

40

50

板のような)犠牲基板1200上にエピタキシャル成長されている。基板1200の成長表面1205は、前述したように、{100}面に対して<100>方向に向かって約5°から約45°の範囲内のオフカット角でオフカットされているとよい。従って、薄膜熱電材料1210のc軸に沿った(斜線1219によって示されている)結晶成長方向は、基板1200の成長表面1205と直交せず、むしろ、成長表面1205の法線から約5°から約30°の範囲内の角度で傾斜している。換言すると、薄膜熱電材料1210は、基板1200のオフカット表面1205に隣接する熱電材料1210の表面1222に対して約5°から約30°の結晶傾斜角を有している。次いで、基板1200が、個別の熱電要素1203をもたらすように、パターン化され、切断され、または他の方法によって整形されることになる。P型熱電要素およびn型熱電要素は、異なる基板上に別々に形成されてもよい。p型熱電要素を有する基板が、個別のp型熱電要素をもたらすようにダイシングされてもよく、n型熱電要素を有する基板が、個別のn型熱電要素をもたらすようにダイシングされてもよい。結晶傾斜角は、n型熱電要素およびp型熱電要素に対して同一にする必要がないことを理解されたい。

#### 【0078】

図12Bに示されているように、(熱伝導性セラミック板のような)第1のヘッダー1221は、その上に導電性金属トレース1207を備えている。p型熱電要素1203aおよびn型熱電要素1203bが、例えば、半田層1209を用いて、金属トレース1207に接合されている。1つまたは複数の犠牲基板1200の部分1201は、それぞれの熱電要素1203aおよび1203bが金属トレース1207に接合された後、熱電要素1203aおよび1203b上に保持されるようになっているとよい。ヘッダー1221が基板1200の成長表面と平行に延在しているので、接合された熱電要素1203aおよび1203bは、ヘッダー1221に対して、約5°から約30°の範囲内の結晶傾斜角を有していることになる。図12Cに示されているように、犠牲基板1201の残りの部分が取り除かれ、金属接点1211が、(例えば、電気メッキによって)、熱電要素1203aおよび1203b上に形成されるとよい。図12Dに示されているように、相補的なトレース1217を有する第2のヘッダー1231が、例えば、半田層1215を用いて、金属接点1211に接合されるとよい。このようにして、本発明のいくつかの実施形態による熱電素子は、図3A, 3Bおよび/または図10A, 10Bを参照して前述した方法によって作製された熱電要素1203a, 1203bを備えることができる。

#### 【0079】

本発明のいくつかの実施形態によれば、第1のヘッダー1221は、集積回路(IC)半導体チップであるとよく、第2のヘッダー1231は、パッケージ基板、例えば、印刷回路基板、積層キャリア基板、チップキャリア、ボールグリッドアレイ基板、ピングリッドアレイ基板、フリップチップパッケージ基板、印刷ワイヤ基板、および/または集積回路チップまたは他の電子素子がチップスケールパッケージをもたらすように接合される他の基板であるとよい。さらに詳細には、(第1のヘッダー1221としての)集積回路半導体は、1つまたは複数の金属トレース1207に隣接して電子素子を有する能動側、および能動側と反対の裏側を備えているとよい。逆に、他の実施形態では、第2のヘッダー1231がIC半導体チップであってもよく、第1のヘッダー1221がパッケージ基板であってもよい。P型熱電要素1203aおよびN型熱電要素1203bは、電気的に互いに直列接続されたP-N対を画定し、これによって、ペルチェ冷却および/またはゼーベック発電のいずれかをもたらすことができる。本発明のいくつかの実施形態によれば、第1のヘッダー1221が、半導体電子素子の基板または加熱/冷却されるように構成された他の素子であるとよく、第2のヘッダー1231が、熱質量、熱シンク、熱拡散板、ヒートパイプ、などのような熱伝達構造体であるとよい。

#### 【0080】

熱電冷却装置となる熱電要素1203をフリップチップIC半導体素子とパッケージ基板との間に設けることによって、IC半導体素子を介してその背後に熱伝達させることなく、IC半導体素子の能動側の熱発生回路のごく近傍に、熱電冷却をもたらすことができ

10

20

30

40

50

る。加えて、熱電冷却素子を形成する加工をフリップチップパッケージの加工と一体化させることができる。さらに、熱電冷却装置とIC半導体チップの能動側の既知のホットスポットとの位置合せが、熱電冷却をIC半導体チップの背後で行う場合よりも、さらに一層容易になる。もしパッケージ基板が熱伝導性を有しているなら、さらなる修正を行う必要がない。もしパッケージ基板が熱伝導を有していないなら（例えば、印刷回路基板、積層キャリア基板などの場合）、1つまたは複数の熱伝導性ビアホール（例えば、銅ビアホール）を、熱電要素1203に隣接する箇所にパッケージ基板を貫通して設けることによって、パッケージ基板を通る熱伝導を高めることができる。

#### 【0081】

従って、本発明のいくつかの実施形態は、GaAs基板上にエピタキシャル成長する熱電膜を堆積させる方法および関連する装置を含んでいる。具体的に、いくつかの実施形態では、GaAs基板は、(100)面から<110>方向に向かって、約5°から約45°の範囲内のオフカット角で成長表面を画定するように、軸外カットされるようになっている。いくつかの実施形態では、オフカット角は、約10°から約30°の範囲内にあるとよい。従って、基板表面に対する多数のオフカット角の1つが用いられるとよい。例えば、いくつかの実施形態では、オフカット角は、約15°であるとよい。従って、このオフカットされた成長表面上に、クラックが減少した熱電膜および/または実質的にクラックの存在しない熱電膜をエピタキシャル成長させることができる。クラックおよび/または表面欠陥を減少させることに加えて、前述の方法は、(100)面から<110>方向に向かって約2°の角度でカットされた基板上に成長した膜と比較して、堆積率を増すことができる。

#### 【0082】

エピタキシャル成長する熱電膜を堆積させる前述の方法は、GaAs基板上に形成された熱電膜の面外の表面欠陥を減少させ、および/または排除させることに適用されてもよい。いくつかの実施形態では、(100)面から<100>方向に向かって約15°の角度で軸外配向されたGaAs基板を用いることによって、改良された結果を見出すことができる。

#### 【0083】

(100)面から<110>方向に向かって軸外カットされたGaAs基板上に実質的にクラックの存在しないおよび/または実質的にクラック生成を減少させた熱電エピタキシャル膜を成長させる方法は、熱電膜のc軸がGaAs基板の成長表面と直交していない点に特徴がある。c軸は、多くの異なる角度を取ることができる。いくつかの実施形態では、c軸は、約5°から約30°の範囲内、特定の実施形態では、約10°から約25°の範囲内の角度で、GaAs成長表面の法線から軸外配向されているとよい。例えば、GaAs成長表面のオフカット角が約15°の場合、熱電膜のc軸は、GaAs成長表面の法線から約11.5°の角度で軸外配向されているとよい。

#### 【0084】

本発明のいくつかの実施形態によるクラック生成が減少し、実質的にクラックが存在せず、および/または殆どクラックが存在しない膜の堆積が、複数の突出するメサを画定するようにパターン化されたGaAs基板上にも得られることが、実証されている。GaAsのメサは、例えば、GaAsウエハをプラズマエッティングすることによって、生成されるとよい。また、GaAs基板の成長表面は、(100)面から<110>方向に向かって約30°以下のオフカット角でオフカットされるとよい。例えば、いくつかの実施形態では、熱電膜成長のために、約5°から約30°の範囲内のオフカット角を有するGaAs成長表面が、約150μm以下の直径を有するメサを画定するように、パターン化されるとよい。これらの突出しているメサが、実質的にクラックを有しないようにすることができる。

#### 【0085】

オフカットされた基板および/またはパターン化された基板上に直接的に成長するオフカット熱電膜を主に参照して、本発明の実施形態を説明してきたが、いくつかの実施形態

10

20

30

40

50

では、オフカットされた基板および／またはパターン化された基板上に高品質の熱電膜を生成するのを助長するために、1つまたは複数の中間層が、その基板上に形成されてもよいことを理解されたい。例えば、シリコン(Si)基板は、無極性材料と呼ばれることがある。何故なら、シリコン基板は、二次元成長せず、二次元成長または三次元成長に方位優先を有している。この場合、熱電膜の成長の前に、炭素(C)、窒素(N)、炭化ケイ素(SiC)、および／または窒化ケイ素(SiN)の1つまたは複数の層を成長基板上に導入することによって、比較的弱い極性が得られ、これによって、改良された熱電膜の核を生成することができる。また、このような中間層は、成長基板と、比較的高い格子定数を有し、および／または熱的に整合しない熱電材料と、の間の歪みを減少させ、分散させ、および／または吸収させることもできる。例えば、GaAs成長表面とBiTe熱電膜との間に、それらの中間の格子定数を有する層を堆積させることができる。BiPbSbTeSeの合金層が、不整合を補うために用いられてもよく、これによって、所望の熱電特性を有する構造をもたらすように改良することができる。このような中間層は、犠牲層であってもよく、従って、基板と共に除去されてもよく、および／または基板が除去された後に除去されてもよい。歪層超格子が、歪みを吸収するために、中間層として用いられてもよい。例えば、GaAs成長基板の場合、GaAs材料系用に開発されたAlAs／InAsおよび／または他の超格子技術が、GaAs／熱電膜界面における歪に対処するために、用いられてもよい。また、比較的柔軟な中間層、例えば、比較的薄い金属層が、格子歪の一部を吸収するために、用いられてもよい。

## 【0086】

10

実施形態を参照して、本発明を具体的に図示し、かつ説明してきたが、以下の請求項に定義される本発明の精神および範囲から逸脱することなく、形態および細部における種々の変更がなされてもよいことが、当業者によって理解されるだろう。

## 【符号の説明】

## 【0087】

100、300、1000 基板

20

101、201 クラック

105、205 エピタキシャル膜

202 表面欠陥

302、1002 オフカット角

30

304、1004 法線

305、1205 成長表面

306、307、1006, 1007 方向

309 斜線、結晶方位

310 热電層

312、1012 結晶傾斜角

314、1014 c軸

319 斜線、結晶方位

325、700、1005、1025、1222 表面

410a 410f, 510a - 510f n型エピタキシャル膜

40

610f ピーク

610e 未確認のピーク

710 膜

715 厚み

810、910 p型热電膜

1009、1019 結晶方位

1010 热電膜

1020 热电層メサ

1030、1120a, 1120b, 1120c メサ

1200 犠牲基板

50

- 1 2 0 1 部分

1 2 0 3 热電要素

1 2 0 3 a p型热电要素

1 2 0 3 b n型热电要素

1 2 0 7、1 2 1 7 トレス

1 2 0 9、1 2 1 5 半田层

1 2 1 0 热电材料

1 2 1 1 金属接点

1 2 1 9 斜线、结晶成长方向

1 2 2 1 第1のヘッダー

1 2 3 1 第2のヘッダー

10

【図1】

FIG. 1

【図2】

FIG. 2

【図3A】

FIG. 3A

【図3B】

FIG. 3B

【図 4 A - 4 F】

【図 5】

【図 6 A - 6 D】

【図 6 E . 6 F】

【図7】

FIG. 7

【図8】

FIG. 8

【図9】

FIG. 9

【図10A】

FIG. 10A

【図10B】

FIG. 10B

【図11B】

FIG. 11B

【図11A】

FIG. 11A

【図11C】

FIG. 11C

【図 12 A】

FIG. 12A

【図 12 B】

FIG. 12B

【図 12 C】

FIG. 12C

【図 12 D】

FIG. 12D

---

フロントページの続き

(74)代理人 100118407

弁理士 吉田 尚美

(74)代理人 100125380

弁理士 中村 綾子

(74)代理人 100125036

弁理士 深川 英里

(74)代理人 100142996

弁理士 森本 聰二

(74)代理人 100154298

弁理士 角田 恭子

(74)代理人 100156443

弁理士 松崎 隆

(74)代理人 100162330

弁理士 広瀬 幹規

(72)発明者 ピアース , ジョナサン・エム

アメリカ合衆国ニュージャージー州 08854 , ピスカタウェイ , ランカスター・コート 435

(72)発明者 ヴァウド , ロバート・ピー

アメリカ合衆国ノースカロライナ州 27519 , ケアリー , フロントゲイト・ドライヴ 502

審査官 工藤 一光

(56)参考文献 米国特許出願公開第 2004 / 0102051 ( U S , A 1 )

特公平 05 - 079163 ( J P , B 2 )

特開平 02 - 243593 ( J P , A )

Yu. A. Boikov, V. A. Danilov, T. Claeson, D. Ertz, Layer by layer growth of Bi<sub>2</sub>Te<sub>3</sub> epitaxial thermoelectric heterostructures , 16th International Conference on Thermoelectrics , 米国 , IEEE , 1997年 , p. 89-92

Jeong-Hun Kim, Sung-Do Kwon, Dae-Yong Jeong, Byeong-Kwon Ju, Seok-Jin Yoon, Jin-Sang Kim , Structural Characteristics of Bi<sub>2</sub>Te<sub>3</sub> and Sb<sub>2</sub>Te<sub>3</sub> films on (001) GaAs Substrates grown by MOCVD , 2006 International Conference on Thermoelectrics , 米国 , IEEE , 2006年

8月 , P. 411 - 413

(58)調査した分野(Int.Cl. , DB名)

H 01 L 35 / 00 - 35 / 34

H 01 L 21 / 205