(12)发明专利

(10)授权公告号 CN 106935604 B

(45)授权公告日 2019.04.26

(21)申请号 201611254173.1

(74)专利代理机构 北京市柳沈律师事务所

(22)申请日 2013.03.28

11105

(65)同一申请的已公布的文献号

代理人 邱军

申请公布号 CN 106935604 A

(51)Int.Cl.

(43)申请公布日 2017.07.07

H01L 27/146(2006.01)

(30)优先权数据

2012-085666 2012.04.04 JP

(56)对比文件

CN 1527393 A, 2004.09.08,

JP 2012015400 A, 2012.01.19,

CN 101523602 A, 2009.09.02,

CN 1543060 A, 2004.11.03,

CN 101794800 A, 2010.08.04,

(62)分案原申请数据

201310104772.5 2013.03.28

审查员 张弘

(73)专利权人 索尼公司

地址 日本东京都

(72)发明人 小林实希子 山下和芳

权利要求书2页 说明书12页 附图12页

(54)发明名称

固态成像装置和电子设备

(57)摘要

本发明提供了一种固态成像装置和电子设备。这里所披露的是固态成像装置,其包括:半导体基体;光敏二极管,形成在半导体基体上,并且用于执行光电转换;像素部,提供有像素,该像素的每一个具有光敏二极管;第一配线,形成为通过接触部电连接到像素部的半导体基体,并且在第一方向上延伸到像素部之外;第二配线,由与第一配线不同的配线层制作,并且形成为在与第一方向不同的第二方向上延伸到像素部之外;以及接触部,用于将第一配线和第二配线彼此电连接。

1. 一种成像装置,包括:

半导体基体;

第一光敏二极管;

第二光敏二极管;

放大晶体管;

复位晶体管;

选择晶体管;

第一配线,形成在第一配线层中并且由第一接触部电连接到所述半导体基体;

第二配线,形成在第二配线层中并且由第二接触部电连接到所述第一配线;

第三配线,形成在第三配线层中并且由第三接触部电连接到所述选择晶体管;和

第四配线,形成在第四配线层中并且由第四接触部电连接到所述放大晶体管,

其中所述第一光敏二极管和所述第二光敏二极管在第一方向上排布并且共享所述放大晶体管,

其中所述第一配线在所述第一方向上延伸,并且其中所述第二配线在与所述第一方向不同的第二方向上延伸。

2. 根据权利要求1所述的成像装置,其中所述第三配线在所述第一方向上延伸。

3. 根据权利要求1所述的成像装置,其中所述第四配线具有网孔形状。

4. 根据权利要求1所述的成像装置,其中所述第一光敏二极管和所述第二光敏二极管共享所述放大晶体管和所述复位晶体管。

5. 根据权利要求1所述的成像装置,其中所述第一光敏二极管和所述第二光敏二极管共享所述放大晶体管、所述复位晶体管和所述选择晶体管。

6. 根据权利要求1所述的成像装置,

其中所述第二配线层形成在所述第一配线层上,

其中所述第三配线层形成在所述第二配线层上,

其中所述第四配线层形成在所述第三配线层上。

7. 根据权利要求1所述的成像装置,

其中所述第一配线延伸到所述第一光敏二极管和所述第二光敏二极管之外,以及

其中所述第二配线延伸到所述第一光敏二极管和所述第二光敏二极管之外。

8. 根据权利要求1所述的成像装置,其中所述第三配线由形成在所述第二配线层中的配线电连接到所述选择晶体管。

9. 根据权利要求1所述的成像装置,其中所述第四配线电连接到所述放大晶体管和所述复位晶体管。

10. 根据权利要求1所述的成像装置,其中所述第四配线由形成在所述第三配线层中的配线和形成在所述第二配线层中的配线电连接到所述放大晶体管。

11. 根据权利要求1所述的成像装置,还包括连接到所述复位晶体管的栅极的复位线,

其中所述复位线形成在所述第二配线层中。

12. 根据权利要求1所述的成像装置,还包括连接到所述选择晶体管的栅极的选择线,

其中所述选择线形成在所述第二配线层中。

13. 根据权利要求1所述的成像装置,还包括:

第一传输晶体管,连接到所述第一光敏二极管;

第二传输晶体管,连接到所述第二光敏二极管;

第一控制线,连接到所述第一传输晶体管的栅极;和

第二控制线,连接到所述第二传输晶体管的栅极。

14. 根据权利要求13所述的成像装置,其中所述第一控制线和所述第二控制线形成在所述第二配线层中。

15. 根据权利要求1所述的成像装置,

其中所述第二配线层形成在所述第一配线层上,

其中所述第三配线层形成在所述第二配线层上,

其中所述第四配线层形成在所述第三配线层上。

其中所述第三配线由形成在所述第二配线层中的第一互连电连接到所述选择晶体管,

以及

其中所述第四配线由形成在所述第三配线层中的第二互连和形成在所述第二配线层

中的第三互连电连接到所述放大晶体管。

16. 根据权利要求15所述的成像装置,还包括:

复位线,连接到所述复位晶体管的栅极;和

选择线,连接到所述选择晶体管的栅极,

其中所述复位线形成在所述第二配线层中,以及

其中所述选择线形成在所述第二配线层中。

17. 根据权利要求16所述的成像装置,还包括:

第一传输晶体管,连接到所述第一光敏二极管;

第二传输晶体管,连接到所述第二光敏二极管;

第一控制线,连接到所述第一传输晶体管的栅极;和

第二控制线,连接到所述第二传输晶体管的栅极。

18. 根据权利要求17所述的成像装置,其中所述第四配线具有网孔形状。

19. 根据权利要求18所述的成像装置,其中所述第一光敏二极管和所述第二光敏二极

管共享所述放大晶体管和所述复位晶体管。

## 固态成像装置和电子设备

[0001] 本申请是2013年3月28日提交的、申请号为201310104772.5、发明名称为“固态成像装置和电子设备”的发明专利申请的分案申请。

### 技术领域

[0002] 本发明涉及固态成像装置和采用该固态成像装置的电子设备。

### 背景技术

[0003] 在CMOS(互补金属氧化物半导体)固态成像装置中,用于给像素提供电压的配线形成在延伸在纵向或横向上的第一配线层中。对于更多的信息,参见诸如日本专利申请特开第2004-104203号公报。

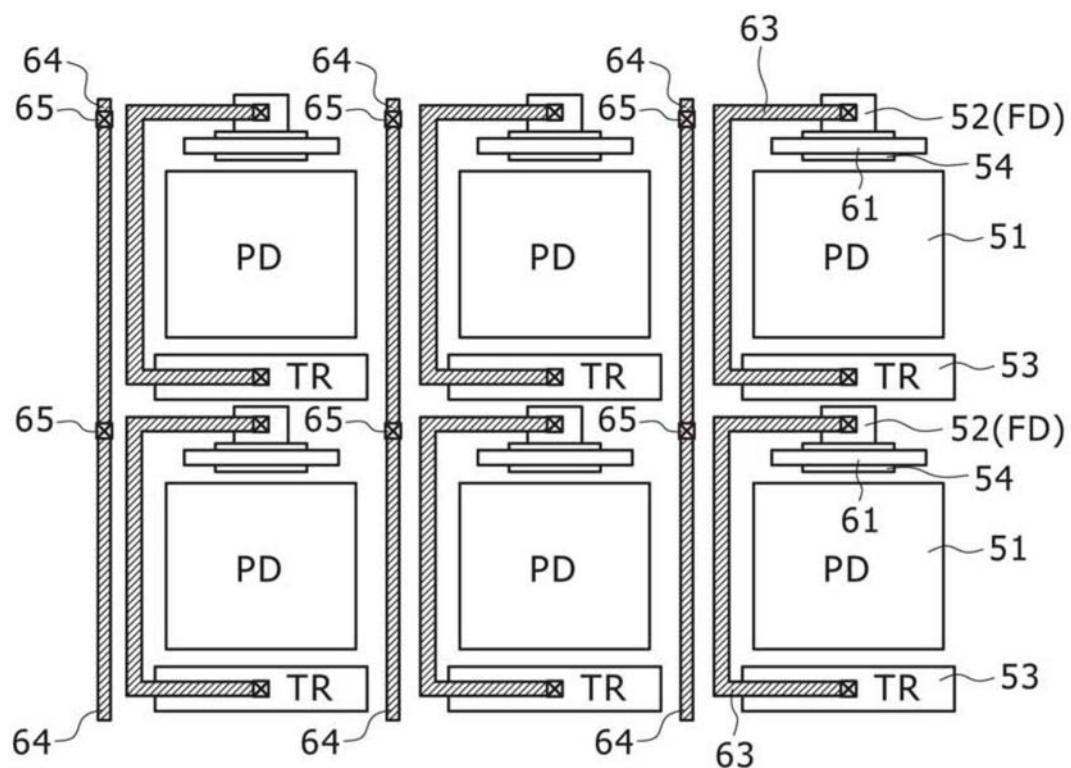

[0004] 图13为粗略示出了具有现有技术构造的CMOS固态成像装置的典型俯视图的示意图。

[0005] 如图13所示,每个像素包括光敏二极管(PD)51、浮置扩散(FD)52和晶体管(TR)部53。很多这样的像素排布在纵、横方向上以形成一种构造。晶体管部53包括放大晶体管、选择晶体管和复位晶体管。

[0006] 在光敏二极管51和浮置扩散52之间,提供读取栅极54。配线61形成在读取栅极54上。

[0007] 浮置扩散52和晶体管部53由配线63彼此连接,配线63提供在光敏二极管51的左侧。在配线63的左侧,提供延伸在纵向上的接地配线64。接地配线64由接触部65连接到半导体基体。

[0008] 接地配线64从外部源接收接地电位(也称为地电位),从而呈现在半导体基体上的电位固定在地电位。

[0009] 配线61和63以及接地配线64形成为第一配线层,该第一配线层为金属配线层。第一配线层通过接触部连接到也是金属配线层的第二配线层。然而,图中没有示出第一配线层到第二配线层的连接。

### 发明内容

[0010] 在图13所示的构造中,接地配线64延伸在纵向上。与如图所示的构造的情况一样,在包括延伸在横向上的接地配线的构造和包括延伸在纵向的接地配线的构造中,当一部分接地配线非故意断开时,该构造不希望包括其中半导体基体的电位非固定在地电位的像素行和/或像素列。

[0011] 因此,在某些情况下可能在图像上产生纵向线或横向线。另外,在某些情况下,由于半导体基体被固定在地电位的状态被弱化,可能在屏幕上产生阴影(shading)等。在发生这些现象时,该现象会成为使图像质量变坏和降低产率的原因。

[0012] 因此,所希望的是提供能改善图像质量且提高产率的固态成像装置。还希望提供采用该固态成像装置的电子设备。

[0013] 根据本发明实施例的固态成像装置包括:半导体基体;光敏二极管,形成在半导体基体上且用于执行光电转换;以及像素部,提供有像素,每一个像素具有光敏二极管。

[0014] 另外,固态成像装置还包括第一配线,其形成为通过接触部电连接到用于像素部的半导体基体,并且在第一方向上延伸到像素部之外。

[0015] 重要的是,固态成像装置还包括由与第一配线不同的配线层制作的第二配线,并且形成为在与第一方向不同的第二方向上延伸到像素部之外。

[0016] 固态成像装置还包括接触部,用于将第一配线和第二配线彼此电连接。

[0017] 根据本发明另一个实施例的电子设备包括光学系统、上述的固态成像装置和用于处理固态成像装置输出信号的信号处理电路。

[0018] 如上所述,根据本发明实施例的固态成像装置的构造包括:第一配线,形成为在第一方向上延伸到像素部之外,并且由接触部电连接到半导体基体;以及第二配线,形成为在与第一方向不同的第二方向上延伸到像素部之外,并且由接触部电连接到第一配线。

[0019] 因此,即使第一配线或第二配线断开,也能通过第一配线和第二配线的另一个提供电位到半导体基体。

[0020] 另外,因为第一和第二配线彼此电连接,所以减小了用于给半导体基体提供电位的这些配线的电阻。

[0021] 如上所述,根据本发明实施例的电子设备的构造包括根据本发明实施例的固态成像装置。因此,即使固态成像装置的第一或第二配线的任何一个断开,也能通过第一配线和第二配线的另一个给半导体基体提供电位。另外,因为第一和第二配线彼此电连接,所以可减小用于给半导体基体提供电位的这些配线的电阻。

[0022] 如上所述,根据本发明的实施例,所提供的构造包括:第一配线,形成为在第一方向上延伸到像素部之外,并且由接触部电连接到半导体基体;以及第二配线,由与第一配线不同的配线层制作,并且形成为在与第一方向不同的第二方向上延伸到像素部之外,并且由接触部电连接到第一配线。

[0023] 因此,即使第一配线或第二配线的任何一个断开,也能通过第一配线和第二配线的另一个给半导体基体提供电位。

[0024] 结果,半导体基体的电位可保持在固定的水平,从而能改善图像质量且提高产率。

[0025] 另外,根据本发明的实施例,可减小用于给半导体基体提供电位的这些配线的电阻。因此,能加强半导体基体的电位。因此,能消除屏幕上像素到像素间的特性变化且去除屏幕的阴影,从而改善图像质量且提高产率。

## 附图说明

[0026] 图1是示出根据第一实施例的固态成像装置的粗略构造的示意图,或者示出固态成像装置中采用的主要部件的电路构造的示意图;

[0027] 图2A和2B分别是示出图1所示的各第一和第二接地配线的排布的俯视图的示意图;

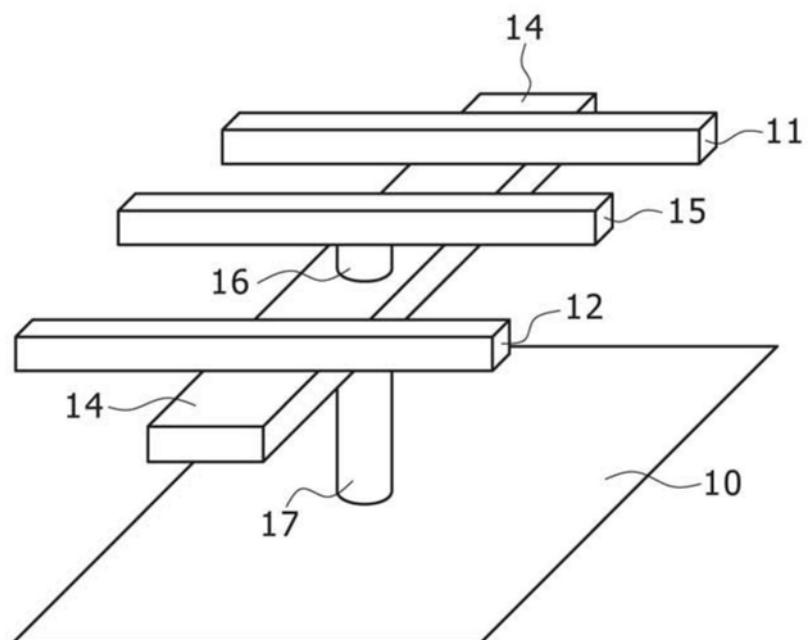

[0028] 图3是示出将第一和第二接地配线彼此连接的部分的透视图(俯视图)的示意图;

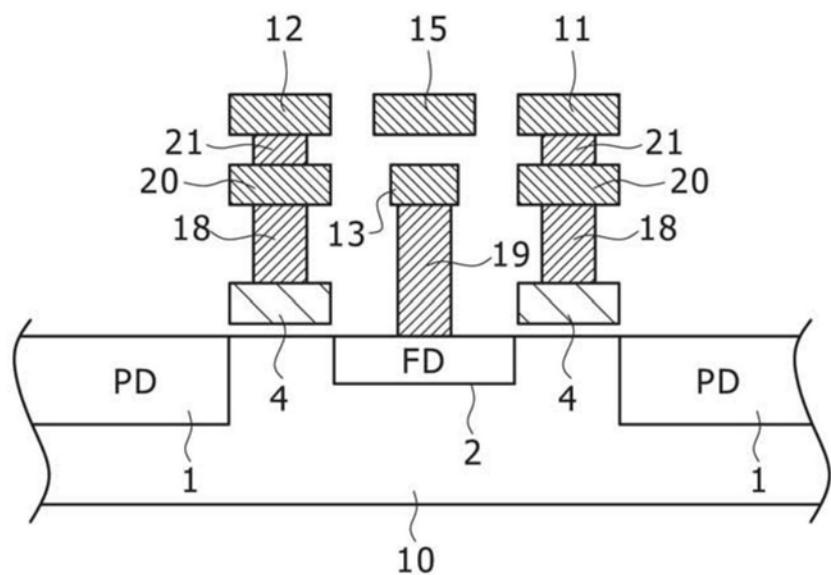

[0029] 图4是示出在根据第一实施例的固态成像装置中浮置扩散的附近的截面的示意图;

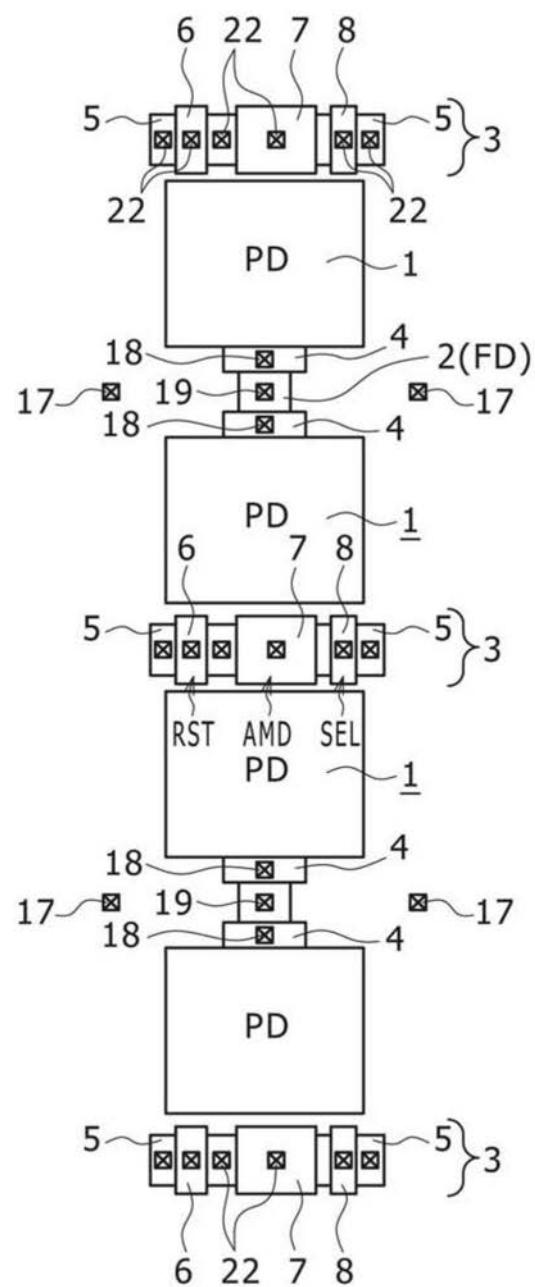

- [0030] 图5是示出根据第一实施例的固态成像装置中采用的主要部件的俯视图；

- [0031] 图6是示出根据第一实施例的固态成像装置中采用的主要部件的俯视图；

- [0032] 图7是示出根据第一实施例的固态成像装置中采用的主要部件的俯视图；

- [0033] 图8是示出根据第一实施例的固态成像装置中采用的主要部件的俯视图；

- [0034] 图9是示出根据第一实施例的固态成像装置中采用的主要部件的俯视图；

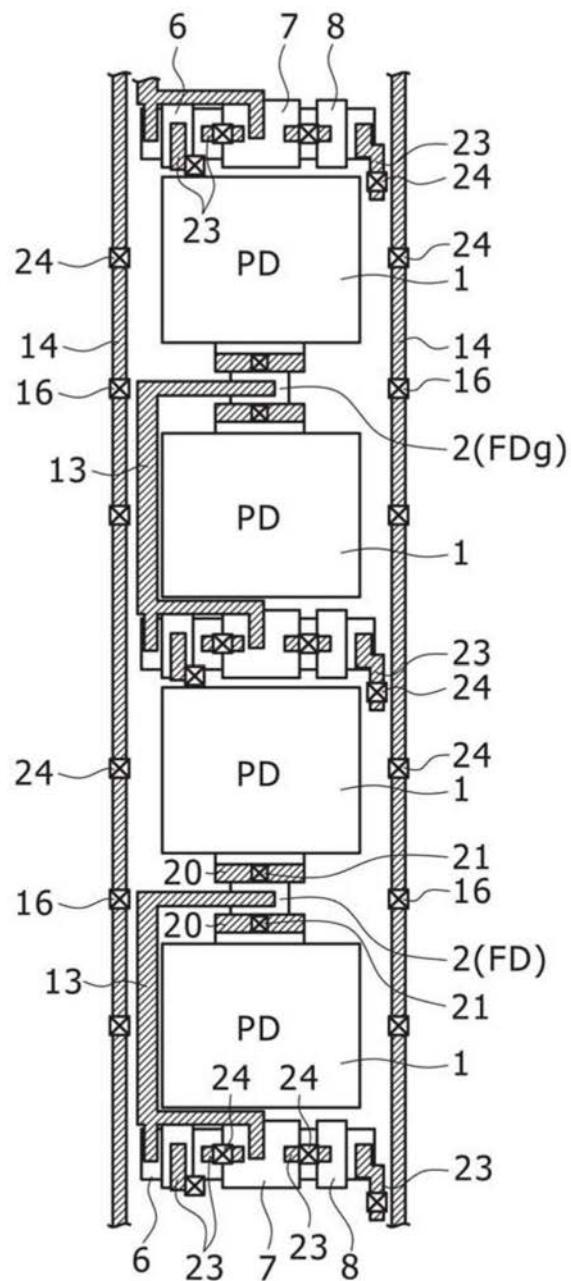

- [0035] 图10是示出根据第二实施例的固态成像装置的粗略构造的示意图，或者示出固态成像装置中采用的主要部件的电路构造的示意图；

- [0036] 图11是示出根据第三实施例的固态成像装置的粗略构造的示意图，或者示出固态成像装置中采用的主要部件的电路构造的示意图；

- [0037] 图12是示出根据第四实施例的电子设备的粗略构造的方框图；

- [0038] 图13是粗略地示出具有现有技术构造的CMOS固态成像装置的典型俯视图的示意图；以及

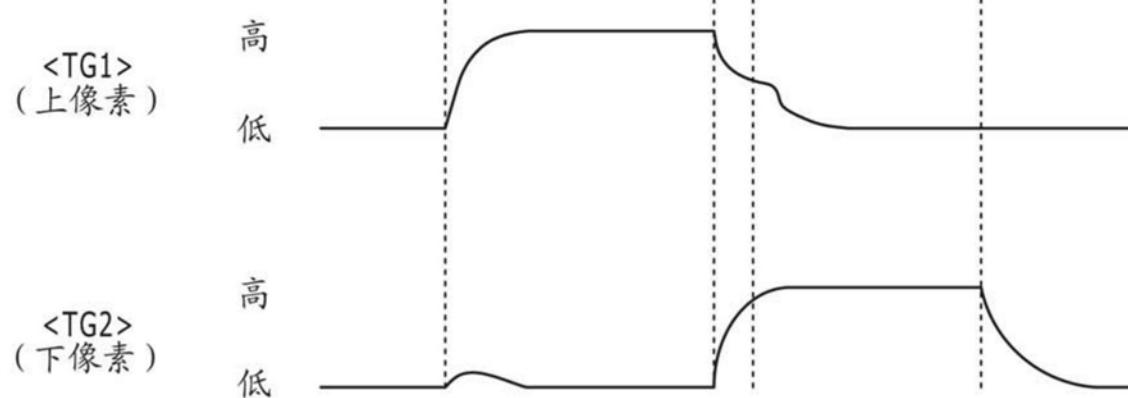

- [0039] 图14A是示出矩形输入脉冲的波形的示意图，而图14B是示出实际脉冲的波形的示意图。

## 具体实施方式

- [0040] 下面描述本发明的优选实施例。应注意，描述分成下面的主题：

- [0041] 1. 第一实施例(固态成像装置)

- [0042] 2. 第二实施例(固态成像装置)

- [0043] 3. 第三实施例(固态成像装置)

- [0044] 4. 第四实施例(电子设备)

- [0045] <1. 第一实施例>

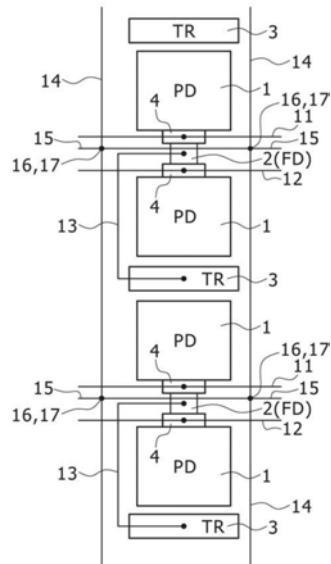

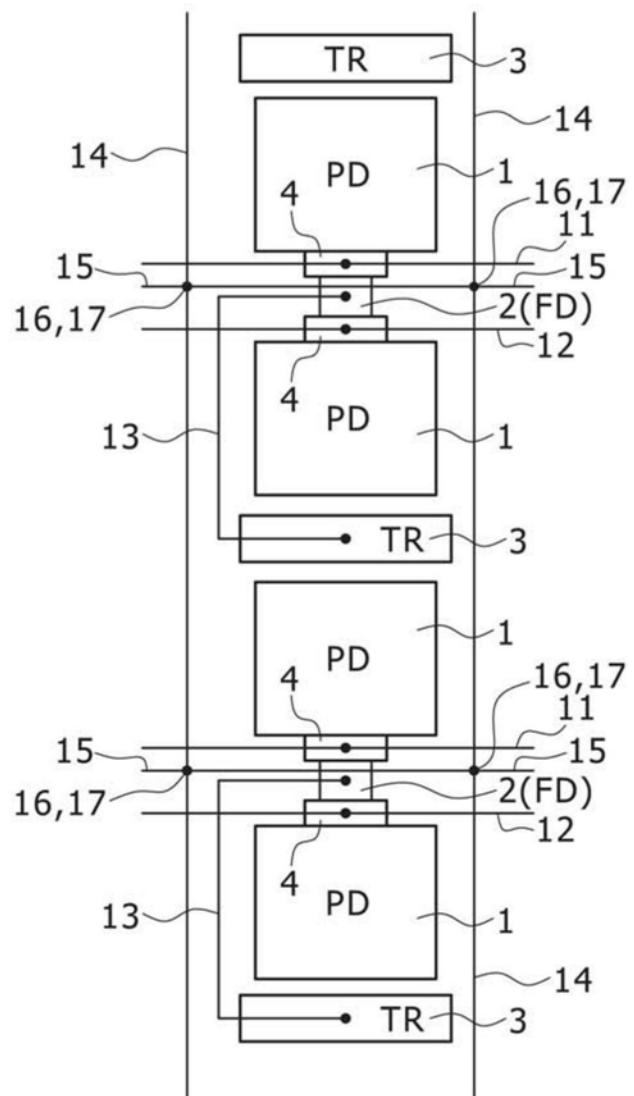

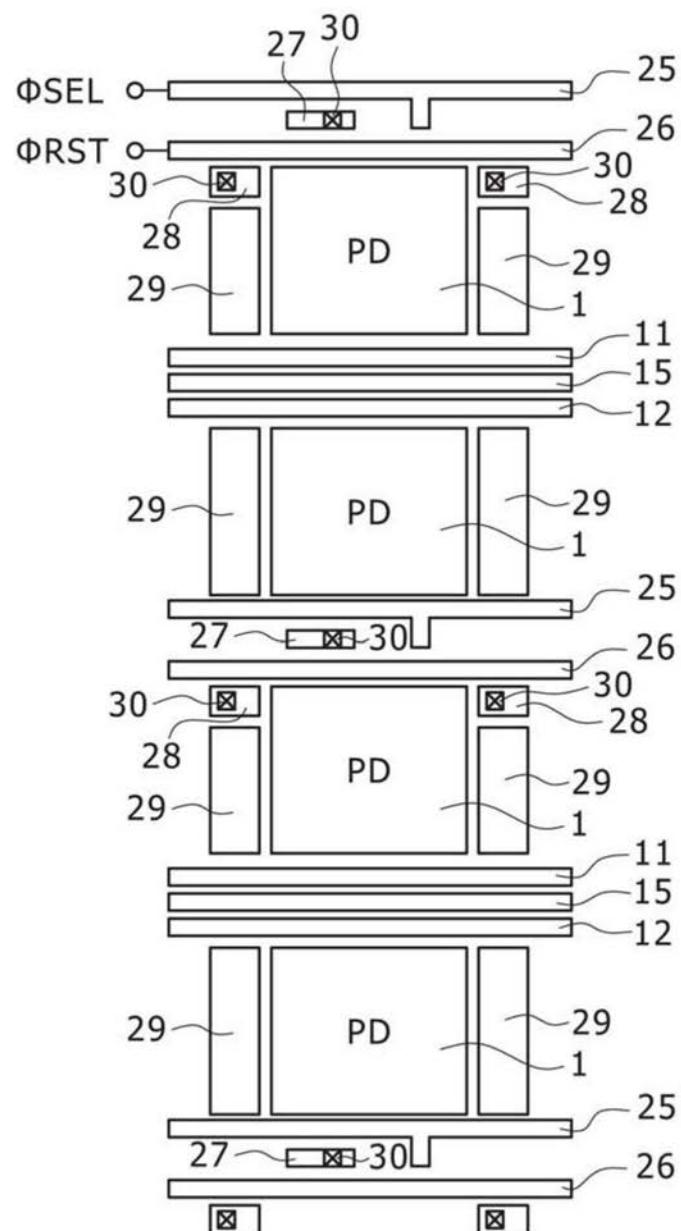

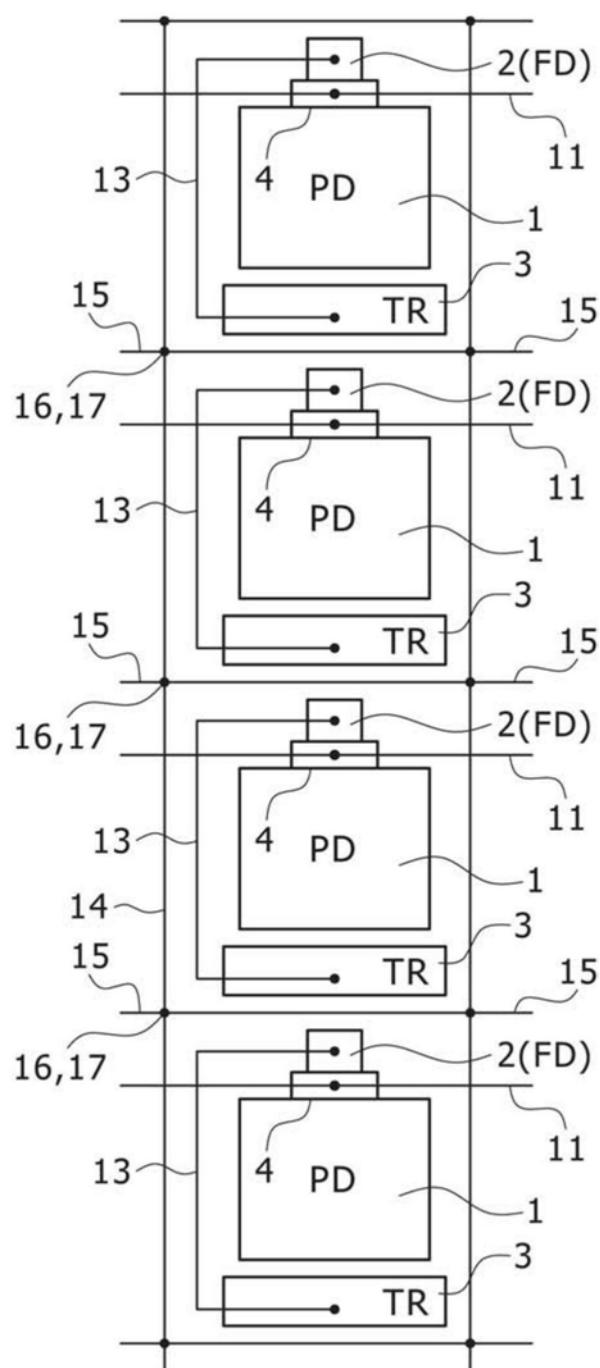

- [0046] 图1是示出根据第一实施例的固态成像装置的粗略构造的示意图，或者是示出固态成像装置中采用的主要部件的电路构造的示意图。图1示出了包括在固态成像装置的像素部中像素的一个纵列的电路构造。实施例将本技术应用于CMOS固态成像装置。

- [0047] 如图1所示，根据第一实施例的固态成像装置构造为包括像素，每个像素包括光敏二极管(PD)1、浮置扩散(FD)2和晶体管(TR)部3，晶体管(TR)部3具有每一个都为MOS晶体管的像素晶体管。

- [0048] 光敏二极管1形成在由诸如硅的半导体材料制作的半导体基体中。光敏二极管1用作光电转换部，用于实现将入射光转换成电荷的光电转换过程。

- [0049] 典型的半导体基体具有以下任一构造：半导体基体的单体、外延层形成其上的半导体基体以及形成在另一个基体上的半导体层。

- [0050] 浮置扩散2典型地为形成在半导体基体中的N型杂质区域。浮置扩散2用作电荷累积部，用于累积作为光敏二极管1执行光电转换过程的结果而获得的电荷。

- [0051] 传输栅极4提供在光敏二极管1和浮置扩散2之间。传输栅极4是用于传输作为光敏二极管1执行光电转换过程的结果而获得的电荷到浮置扩散2的栅极。

- [0052] 晶体管部3典型地包括诸如复位晶体管、放大晶体管和选择晶体管的至少一个像素晶体管。

- [0053] 在该实施例中，每一个具有光敏二极管1的两个相邻像素共享共用于光敏二极管1

的浮置扩散2和晶体管部3。两个相邻像素在下文分别称为上侧像素和下侧像素。

[0054] 浮置扩散2提供在被分别包括在上侧像素和下侧像素中的两个光敏二极管1之间。

[0055] 晶体管部3提供在由上下侧像素各自包括的上下光敏二极管1的下侧，并且由配线13电连接到浮置扩散2。

[0056] 两个相邻像素的上侧像素的传输栅极4连接到第一控制线11，而两个相邻像素的下侧像素的传输栅极4连接到第二控制线12。

[0057] 以与图13所示现有技术构造的接地配线63相同的方式提供第一接地配线14，且伸展在图1中的纵向上。

[0058] 在该实施例中，还提供第二接地配线15且伸展在图1中的横向。第二接地配线15电连接到第一接地配线14以形成接地线。

[0059] 接地电位在下文也称为地电位，被提供到第一接地配线14和第二接地配线15。

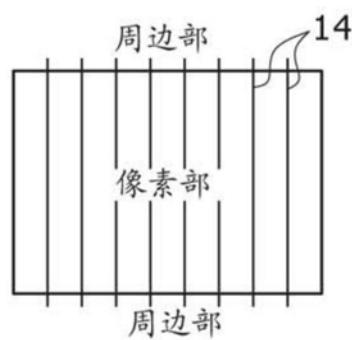

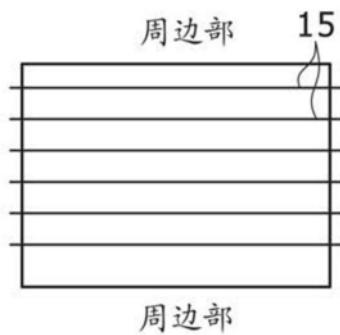

[0060] 图2A和2B是分别示出图1所示的第一接地配线14和第二接地配线15的排布的俯视图。更具体而言，图2A示出了第一接地配线14的排布，而图2B示出了第二接地配线15的排布。

[0061] 如图2A所示，第一接地配线14从像素部纵向伸展到像素部之外的上周边部和下周边部，并且连接到周边部。

[0062] 如图2B所示，另一方面，第二接地配线15从像素部横向伸展到像素部之外的左周边部和右周边部，并且连接到周边部。

[0063] 因为第一接地配线14和第二接地配线15构造为如上所述，所以当从第一接地配线14和第二接地配线15之上的位置看时，第一接地配线14和第二接地配线15呈现为伸展的配线以形成网孔。

[0064] 另外，如上所述，接地电位也称为地电位，其从像素部外部的源被提供到第一接地配线14和第二接地配线15。

[0065] 应注意，图2A和2B所示的周边部具有包括信号处理电路的电路，用于处理来自像素部的电信号。第一接地配线14和第二接地配线15连接到周边部中的电路。

[0066] 另外，图3是示出将第一和第二接地配线彼此连接的部分的透视图(俯视图)的示意图。

[0067] 如图1和3所示，第二接地配线15与第一控制线11和第二控制线12形成在相同的层中，并且第二接地配线15设置在第一控制线11和第二控制线12之间。

[0068] 第一接地配线14形成为第一配线层，该第一配线层是金属配线层并用作下层。另一方面，第二接地配线15形成为与第一配线层不同的第二配线层。第二配线层是金属配线层并用作上层。

[0069] 第一接地配线14由接触部17电连接到半导体基体10，接触部17利用绝缘层中提供的通路层且由半导体材料制作。

[0070] 第一接地配线14由接触部16电连接到第二接地配线15，接触部16利用绝缘层中提供的通路层且由半导体材料制作。

[0071] 另外，图4是示出根据第一实施例的固态成像装置中的浮置扩散2附近的截面示意图。

[0072] 更具体而言，图4是示出共享浮置扩散2的两个相邻像素和位于像素之间的部分的

截面图。

[0073] 如图4所示,接触部18、配线层20和接触部21从传输栅极4和第一控制线11之间的下层开始顺序形成在向上的方向上。接触部18、配线层20和接触部21将传输栅极4和第一控制线11彼此连接。同样,接触部18、配线层20和接触部21从传输栅极4和第二控制线12之间的下层开始顺序形成在向上的方向上。接触部18、配线层20和接触部21将传输栅极4和第二控制线12彼此连接。接触部18和接触部21的每一个均利用通路层。

[0074] 另外,浮置扩散2通过利用通路层的接触部19连接到图1所示的配线13。

[0075] 第二接地配线15提供在配线13之上,与配线13绝缘。

[0076] 以与第一接地配线14相同的方式,配线层20和配线13的每一个均由第一配线层形成,第一配线层为金属配线层。

[0077] 应注意,图4的截面图没有示出第一控制线11、第二控制线12和第二接地配线15之上的构造。

[0078] 因为第二接地配线15设置在第一控制线11和第二控制线12之间,所以第二接地配线15也起屏蔽配线的作用,用于防止第一控制线11和第二控制线12之间的耦合。

[0079] 具体而言,为了开启和关闭传输栅极4,脉冲电压提供到第一控制线11和第二控制线12的每一个。如果第一控制线11和第二控制线12提供在彼此相邻的位置,则在某些情况下第一控制线11和第二控制线12之间可能发生耦合。

[0080] 接地电位也称为地电位,被提供到第二接地配线15用作固定电位,然而,第二接地配线15也起屏蔽配线的作用,用于防止第一控制线11和第二控制线12之间的耦合。

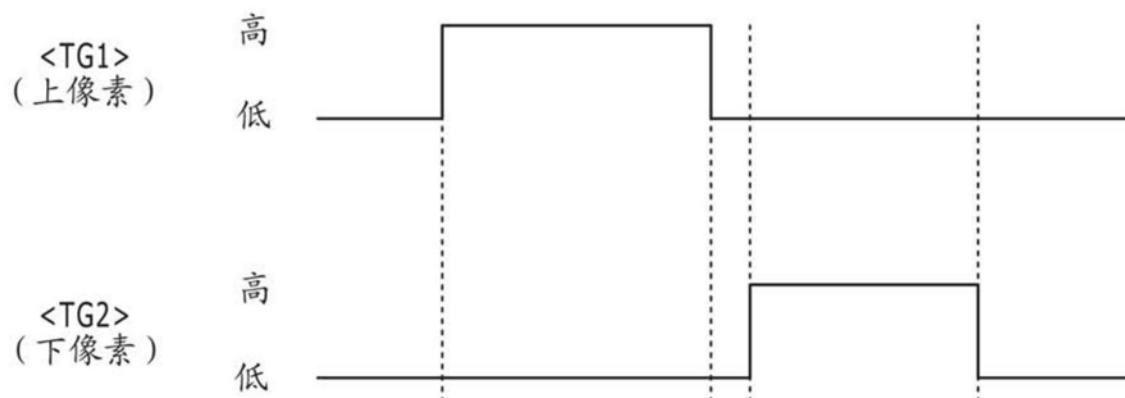

[0081] 下面的描述说明了由于防止第一控制线11和第二控制线12之间的耦合而改善了传输栅极4上的脉冲波形的技术效果。

[0082] 假设这样的情况,其中图14A所示的矩形输入脉冲顺序提供到共享浮置扩散的两个相邻像素的传输栅极。在下面的描述中,两个相邻像素也分别称为上像素和下像素。

[0083] 如图14A所示,首先,矩形输入脉冲提供到上像素的传输栅极TG1。然后,在提供到上像素的传输栅极TG1的矩形输入脉冲的下落边缘之后,另外的矩形输入脉冲5提供到下像素的传输栅极TG2。

[0084] 在其中接地配线形成为一层的现有技术的构造中,对于其中两个像素共享浮置扩散的情况,每一个用于提供电压给像素之一的传输栅极的两个控制线彼此相邻地伸展。因此在某些情况下这两个控制线之间可能发生耦合。当这样的耦合发生时,实际获得的脉冲波形被扭曲,如图14B所示。更具体而言,因为用于上像素的波形的下落边缘受到用于下像素的矩形脉冲的上升边缘的影响,使该下落边缘发生了变化。另一方面,由于用于上像素的矩形脉冲的上升边缘的影响,下像素的电位摆动。

[0085] 如上所述,当耦合发生在两个控制线之间时,电压脉冲的波形变坏。因此会担心不能正确地执行驱动。另外,为了减小耦合在电压脉冲的波形上的影响,必须增加电压脉冲的宽度和电压脉冲之间的间隙。因此,难以执行高速驱动。

[0086] 在根据该实施例的构造中,另一方面,第二接地配线15防止第一控制线11和第二控制线12之间的耦合。就是说,第二接地配线15用作屏蔽配线。因此,能大大减小由如图14A所示的输入脉冲波形到实际脉冲波形的变化。

[0087] 结果,能获得与图14所示的输入脉冲波形大致相同的实际脉冲波形。

[0088] 接下来,通过参见图5至9的俯视图,下面的描述将说明根据该实施例的固态成像装置的典型立体结构。

[0089] 图5是示出半导体基体10的半导体区域、半导体基体10上的多晶硅层和在该层上提供的接触部的俯视图。半导体基体10如图3和4所示。

[0090] 传输栅极4由多晶硅层形成。如图4所示的接触部18形成在传输栅极4上。

[0091] 如图4所示的接触部19形成在浮置扩散2上。

[0092] 图3所示的接触部17形成在浮置扩散2的左右、且比光敏二极管1更靠外的外侧上。接触部17将半导体基体10和第一接地配线14彼此连接。

[0093] 晶体管部3包括复位晶体管RST、放大晶体管AMP和选择晶体管SEL,它们在从左到右的方向上形成且排列。

[0094] 复位晶体管RST构造为包括复位栅电极6和源/漏区域。用作复位晶体管RST的栅电极的复位栅电极6由多晶硅层制作,而源/漏区域由半导体基体10中的杂质区域5制作。

[0095] 出于同样的原因,放大晶体管AMP构造为包括放大栅电极7和源/漏区域。用作放大晶体管AMP的栅电极的放大栅电极7由多晶硅层制作,而源/漏区域由半导体基体10中的杂质区域5制作。

[0096] 同样,选择晶体管SEL构造为包括选择栅电极8和源/漏区域。用作选择晶体管SEL的选择栅电极8由多晶硅制作,而源/漏区域由半导体基体10中的杂质区域5制作。

[0097] 复位晶体管RST和放大晶体管AMP共享源/漏区域之一。

[0098] 出于同样的原因,放大晶体管AMP和选择晶体管SEL也共享源/漏区域之一。为分配到除放大晶体管AMP和选择晶体管SEL共享源/漏区域之外的源/漏区域的杂质区域5以及为栅电极6、7和8形成连接到上层配线的接触部22。

[0099] 图6是示出了为金属配线层的第一配线层和形成在该层上的接触部的俯视图的示意图。应注意,图6还示出了光敏二极管1和浮置扩散2以便易于理解与其它图的位置关系。另外,给每个配线加上阴影线以便区别于其它配线和其它部件。

[0100] 在光敏二极管1的左侧和右侧,第一接地配线14在纵向上形成且伸展。在第一接地配线14的浮置扩散2的左右位置,形成要连接到第二接地配线15的接触部16。另外,在光敏二极管1的中央的左右位置,形成要连接到上配线层的接触部24。

[0101] 浮置扩散2的配线13通过光敏二极管1的左侧延伸到晶体管部3且通过图5所示的连接部22连接到晶体管部3中的放大栅电极7。另外,该配线13还通过图5所示的接触部22连接到晶体管部3的复位晶体管RST的左侧源/漏区域。

[0102] 由复位晶体管RST和放大晶体管AMP共享的源/漏区域通过图5所示的接触部22连接到配线层23。应注意,连接到由复位晶体管RST和放大晶体管AMP共享的源/漏区域的配线层23形成为在右侧上到达放大栅电极7之上的位置。然而,配线层23不连接到放大栅电极7。

[0103] 选择栅电极8通过图5所示的接触部22连接到另一个配线层23。应注意,连接到选择栅电极8的另一个配线层23形成为在左侧上到达放大栅电极7之上的位置。然而,另一个配线层23不连接到放大栅电极7和与放大晶体管AMP共享的源/漏区域。

[0104] 复位栅电极6连接到再一个配线层23。出于同样的原因,选择晶体管SEL的右侧源/漏区域连接到再另一个配线层23。

[0105] 对于每一个配线层23,形成连接到上配线层的接触部24。

[0106] 在传输栅极4上,形成图4所示的配线层20和在配线层20上的接触部21。应注意,在图6所示的构造中,配线层20的左侧长度和右侧长度的总和大约等于传输栅极4的长度。然而,配线层20也可形成为具有与传输栅极4的长度不同的总长度。形成配线层20且与第一接地配线14和配线13绝缘。

[0107] 图7是示出为金属配线层的第二配线层和形成在该层上的接触部的俯视图的示意图。应注意,图7还示出了光敏二极管1以便易于理解与其它图的位置关系。

[0108] 两个共享浮置扩散2的相邻像素包括上像素和下像素。在上像素的光敏二极管1的左侧和右侧上,形成配线层28和配线层29。在下像素的光敏二极管1的左侧和右侧上,仅形成配线层29。

[0109] 配线层28连接到图6所示的配线层23,以用作通过接触部24连接到选择晶体管SEL的右侧源/漏区域的配线层。在该配线层28中,形成用于连接到上配线层的接触部30。

[0110] 配线层29通过接触部24连接到图6所示的第一接地配线14。配线层29提供在光敏二极管1的左侧和右侧上,用作阻挡从相邻像素辐射的光的屏蔽层。

[0111] 如图3和4所示,在上层和下层之间的部分中,第一控制线11、第二接地配线15和第二控制线12彼此平行地提供。

[0112] 在晶体管部3中,选择线25和复位线26的每一个由第二配线层形成。另外,配线层27形成在选择线25和复位线26之间。

[0113] 通过接触部24,选择线25连接到图6所示的配线层23以用作连接到选择栅电极8的配线层,并且从外部源接收脉冲电位 $\varphi_{SEL}$ 。

[0114] 出于同样的原因,通过接触部24,复位线26连接到图6所示的配线层23以用作连接到复位栅电极6的配线层,并且从外部源接收脉冲复位电位 $\varphi_{RST}$ 。

[0115] 另一方面,通过接触部24,配线层27连接到图6所示的配线层23用作连接到由复位晶体管RST和放大晶体管AMP共享的源/漏区域的配线层。在配线层27中,形成用于连接到上配线层的接触部30。

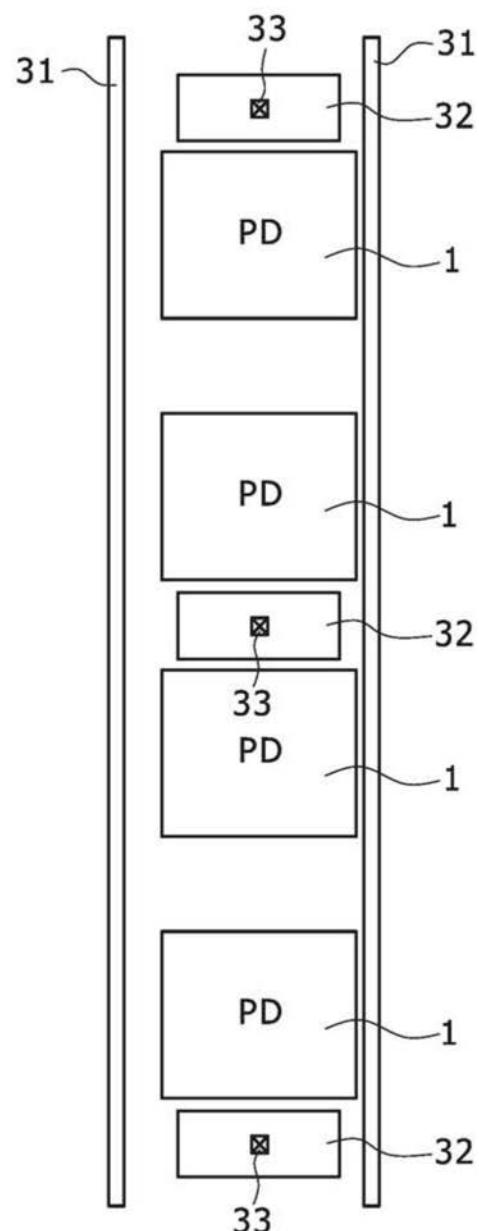

[0116] 图8是示出为金属配线层的第三配线层和该层上形成的接触部的俯视图的示意图。应注意,图8还示出了光敏二极管1以便易于理解与其它图的位置关系。

[0117] 在光敏二极管1的左侧和右侧,垂直信号线31形成且伸展在纵向上。垂直信号线31通过接触部30连接到图7所示的配线层28。

[0118] 在晶体管部3中,配线层32形成为具有相对大的横向长度的矩形的平面图案。配线层32通过接触部30连接到图7所示的配线层27。配线层32还提供用作屏蔽层,用于阻挡从上下侧的相邻像素辐射至光敏二极管1的光。在配线层32中,形成用于连接到上配线层的接触部33。

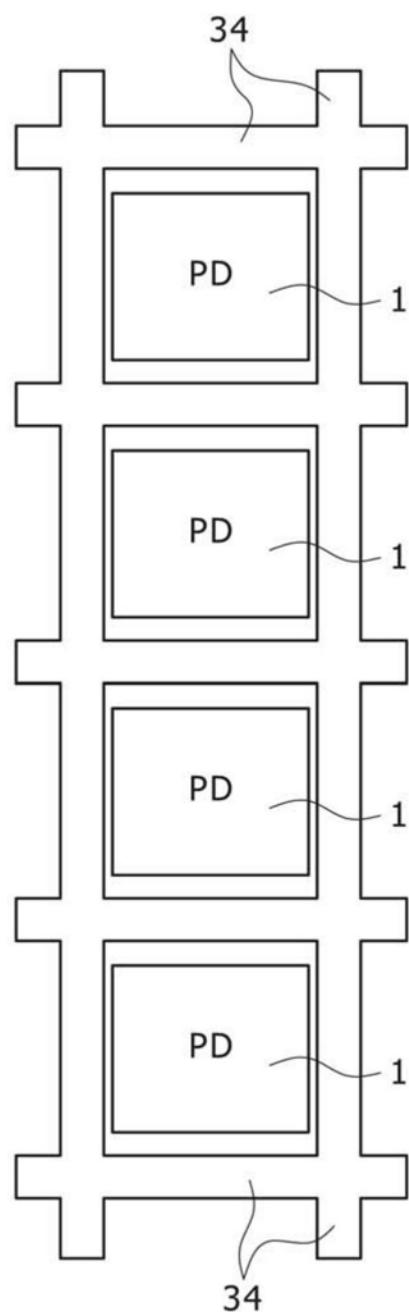

[0119] 图9是示出为金属配线层的第四配线层的俯视图的示意图。应理解,图9还示出了光敏二极管1以便易于理解与其它图的位置关系。

[0120] 如图9所示,电源线34由第四配线层形成以形成网孔形状,方式为电源线34在上下左右侧上围绕光敏二极管1。电源线34通过接触部33连接到图8所示的配线层32。

[0121] 该电源线34从外部源接收电源电位VDD。

[0122] 通过形成电源线34以形成网孔形状,能阻挡来自上下左右侧的相邻像素的光到光敏二极管1。

[0123] 应注意,图5至9的俯视图是根据该实施例的固态成像装置的所谓表面照射型结构的俯视图。在表面照射型结构中,其上形成有诸如晶体管的电路元件的半导体基体10的形成面提供在与传播到半导体基体10的光敏二极管1的光入射表面相同的侧上。

[0124] 另一方面,在固态成像装置的所谓里面照射型结构中,形成有诸如晶体管的电路元件的半导体基体10的形成面提供在与传播到半导体基体10的光敏二极管1的光入射表面相反的侧上。在里面照射型结构中,即使配线位于光敏二极管1之上,也不能防止光的入射。

[0125] 另外,也可提供这样的构造,其中去掉图8所示的配线层32和图9所示的电源线34,而是让电源线由第三配线层形成,提供在光敏二极管1之上,并且平行于垂直信号线31地在纵向上伸展。

[0126] 在这样构造的里面照射型结构的情况下,可任意提供与第二金属配线层在相同水平上或在第二金属配线层之上的配线层,只要该配线层不与其它层相交。

[0127] 根据该实施例的固态成像装置可通过采用通常已知的制造方法制造。

[0128] 通过采用用于形成金属配线层和通路层的通常已知的方法,可形成第一接地配线14、第二接地配线15以及连接第一接地配线14到第二接地配线15的接触部16。

[0129] 根据该实施例实施的固态成像装置,提供形成且伸展在纵向上的第一接地配线14、形成且伸展在横向上的第二接地配线15,并且第一接地配线14和第二接地配线15通过利用接触部16彼此电连接。

[0130] 因此,即使第一接地配线14或第二接地配线15的任何一个断开,也能通过第一接地配线14和第二接地配线15的另一个给半导体基体10提供电位。

[0131] 结果,半导体基体10的电位可保持在固定的接地电平,从而能够改善图像质量,并且提高产率。

[0132] 另外,因为形成为两层的第一接地配线14和第二接地配线15彼此电连接,所以可减小第一接地配线14和第二接地配线15的电阻。因此,能够加强半导体基体10的接地电位。因此,能消除屏幕上像素间的特性变化,并且去除屏幕的阴影,从而改善图像质量,并且提高产率。

[0133] 另外,根据由该实施例实施的固态成像装置,第二接地配线15由为金属配线层的第一配线层形成。该第一配线层与第一控制线11和第二控制线12为相同层。另外,第二接地配线15提供在第一控制线11和第二控制线12之间。

[0134] 因此,接收用作固定电位的接地电位的第二接地配线15屏蔽接收各自脉冲电位的第一控制线11和第二控制线12。结果,能够防止第一控制线11和第二控制线12之间的耦合。

[0135] 从而,能够防止出现在第一控制线11和第二控制线12上的电压脉冲的波形因耦合而变坏。结果,能减小脉冲宽度,执行高速驱动,并且提高帧率。

[0136] 另外,根据该实施例实施的固态成像装置,两个相邻像素共享浮置扩散2和晶体管部3。因此,与非共享构造相比,可使连接到晶体管部3的配线数变少。

[0137] 出于上述原因,即使第二接地配线15设置在第一控制线11和第二控制线12之间,与浮置扩散2和晶体管部3不被像素共享的构造相比,也可使横向伸展的配线总数变小。

[0138] 特别是,在表面照射型结构的情况下,与浮置扩散2和晶体管部3不由像素共享的构造相比,也可使横向伸展的配线总数变少。因此,在横向伸展的配线少的情况下,能把至少与此构造所需的相同面积作为光敏二极管1上的开口面积。结果,在不降低灵敏度的

情况下,能保持半导体基体10的接地电位,并且防止第一控制线11和第二控制线12之间的耦合。

[0139] <2.第二实施例>

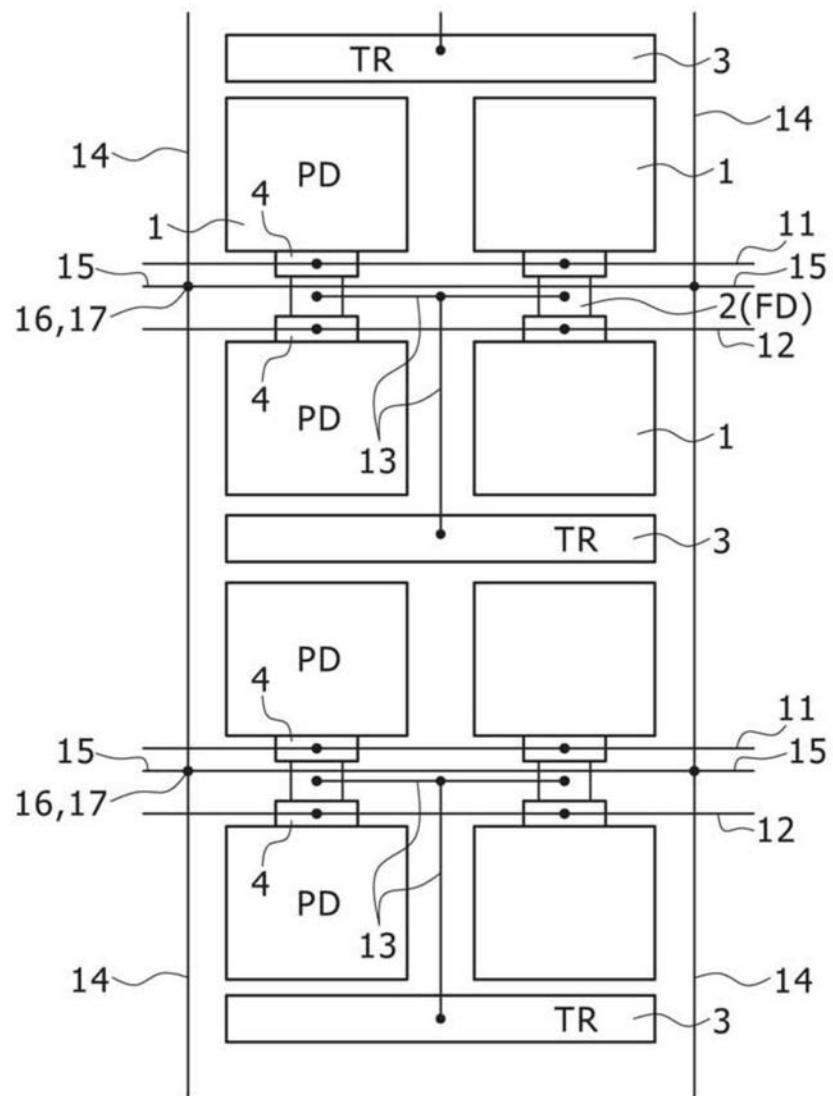

[0140] 图10是示出根据第二实施例的固态成像装置的粗略构造的示意图,或者是示出固态成像装置中采用的主要部件的电路构造的示意图。

[0141] 图10是示出固态成像装置的像素部中两个纵向像素列的电路构造的示意图。

[0142] 该实施例将本技术应用于CMOS固态成像装置。

[0143] 在根据该实施例的固态成像装置中,浮置扩散2由彼此纵向相邻的两个像素共享,而晶体管部3由彼此横向相邻的两个浮置扩散2共享。就是说,像素部设计成这样的构造,其中晶体管部3由排布成具有两行和两列的矩阵的四个像素共享。

[0144] 在该实施例中,每一个都用于彼此连接第一接地配线14和第二接地配线15的接触部16形成在共享晶体管部3的两列像素的光敏二极管1的左右外侧。

[0145] 所形成的晶体管部3的数量被调整为使每一个晶体管部3由列上提供的两个相邻像素共享。晶体管部3形成为与图1所示的第一实施例相比具有横向长的形状。

[0146] 用于彼此连接浮置扩散2和晶体管部3的配线13也彼此连接横向彼此相邻的两个浮置扩散2。配线13通过在横向彼此相邻的两个光敏二极管1之间的间隙延伸到晶体管部3。

[0147] 因为其它构造与图1所示的第一实施例相同,所以为了避免说明上的重复,在下面的描述中不再说明其它构造。

[0148] 根据由该实施例实施的固态成像装置的构造,以与第一实施例相同的方式,形成且伸展在纵向上的第一接地配线14由接触部16电连接到在横向形成且伸展的第二接地配线15。

[0149] 因此,即使第一接地配线14或第二接地配线15的任何一个断开,也能通过第一接地配线14和第二接地配线15的另一个给半导体基体10提供接地电位。

[0150] 结果,半导体基体10的电位可保持在固定的接地电平,从而能够改善图像质量,并且提高产率。

[0151] 另外,因为第一接地配线14和第二接地配线15彼此电连接,所以可减小第一接地配线14和第二接地配线15的电阻。因此,能加强半导体基体10的接地电位。因此,能消除屏幕上像素间的特性变化,并且去除屏幕的阴影,从而改善图像质量,并且提高产率。

[0152] 另外,在该实施例的构造中,第二接地配线15以与第一实施例相同的方式提供在第一控制线11和第二控制线12之间。

[0153] 因此,接收用作固定电位的接地电位的第二接地配线15屏蔽接收它们各自的脉冲电位的第一控制线11和第二控制线12。结果,能防止第一控制线11和第二控制线12之间的耦合。

[0154] 从而,能防止出现在第一控制线11和第二控制线12上的电压脉冲的波形因耦合而变坏。结果,能减小电压脉冲的宽度,执行高速驱动,并且提高帧率。

[0155] 另外,根据该实施例中实施的固态成像装置,四个相邻像素共享晶体管部3。因此,与非共享构造相比,可使连接到晶体管部3的配线数变少。

[0156] 为了上述的原因,即使第二接地配线15提供在第一控制线11和第二控制线12之

间,与晶体管部3不由像素共享的构造相比,也可使在横向伸展的总配线数变少。

[0157] 特别是,在表面照射型结构的情况下,与晶体管部3不由像素共享的构造相比,也可使横向延伸的配线总数变少。因此,在横向伸展的配线少的情况下,能把至少与此构造所需的相同面积作为光敏二极管1上的开口面积。结果,在不降低灵敏度的情况下,能保持半导体基体10的接地电位,并且防止第一控制线11和第二控制线12之间的耦合。

[0158] <3.第三实施例>

[0159] 图11是示出根据第三实施例的固态成像装置的粗略构造的示意图,或者是示出固态成像装置中采用的主要部件的电路构造的示意图。

[0160] 图11是示出固态成像装置的像素部中像素的一个纵列的电路构造的示意图。

[0161] 该实施例将本技术应用于CMOS固态成像装置。

[0162] 在根据第三实施例的固态成像装置中,浮置扩散2和晶体管部3不被多个像素共享。替代为,每个像素构造为包括浮置扩散2和晶体管部3。

[0163] 因此,连接到传输栅极4的控制线仅为第一控制线11。该第一控制线11和传输栅极4提供在如图所示的光敏二极管1的上侧。

[0164] 以与图1和13所示构造相同的方式,用于彼此连接浮置扩散2和晶体管部3的配线13伸展通过光敏二极管1的左侧。

[0165] 第二接地配线15在横向伸展通过由上侧上提供的像素所包括的晶体管部3和由下侧上提供的像素所包括的浮置扩散2之间的位置。第二接地配线15形成为平行于第一控制线11的配线。

[0166] 在该实施例中,第一控制配线11提供在彼此分开的位置。因此,第二接地配线15没有表现出用以防止两个控制线之间的耦合的效果。

[0167] 然而,第二接地配线15提供在第一控制线11和连接到晶体管部3的配线之间以用作选择线和复位线。因此,具有防止第一控制线11和配线之间耦合的效果。

[0168] 因为其它构造与图1所示的第一实施例的相同,所以为了避免说明上的重复,在下面的描述中不再说明其它构造。

[0169] 根据由上述的该实施例实施的固态成像装置的构造,以与第一实施例相同的方式,形成且伸展在纵向上的第一接地配线14由接触部16电连接到形成且伸展在横向上的第二接地配线15。

[0170] 因此,即使第一接地配线14或第二接地配线15的任何一个断开,也能通过第一接地配线14和第二接地配线15的另一个给半导体基体10提供电位。

[0171] 结果,半导体基体10的电位可保持在固定的接地电平,从而能改善图像质量,并且提高产率。

[0172] 另外,因为第一接地配线14和第二接地配线15彼此电连接,所以可减小第一接地配线14和第二接地配线15的电阻。因此,能加强半导体基体10的接地电位。因此,能消除屏幕上像素间的特性变化,并且消除屏幕上的阴影,从而改善图像质量,并且提高产率。

[0173] 根据该实施例的固态成像装置可应用于表面照射型结构或里面照射型结构。

[0174] 在上述的实施例中,用于彼此连接半导体基体10和第一接地配线14的接触部17与用于彼此连接第一接地配线14和第二接地配线15的接触部16形成在相同的平面位置。

[0175] 然而,本发明的实施不意味着限于其中接触部17形成在与接触部16相同的平面位

置的构造。例如,接触部16和接触部17可形成在图1的纵向上彼此分开的位置。

[0176] 上述实施例的每一个具有这样的构造,其中接地配线是由第一配线层构造且伸展在纵向上的第一接地配线14和由第二配线层构造且伸展在横向上的第二接地配线15。

[0177] 然而,根据本发明,两层的接地配线可具有另外的构造。例如,接地配线是由第一配线层构造且伸展在横向上的接地配线和由第二配线层构造且伸展在纵向上的另一个接地配线。

[0178] 上述实施例的每一个具有这样的构造,其中第一接地配线14和第二接地配线15电连接到半导体基体10,以给半导体基体10提供也称为地电位的接地电位。

[0179] 然而,根据本发明,电连接到半导体基体的第一和第二接地配线不意味着限于给半导体基体提供接地电位的构造。例如,电连接到半导体基体的第一和第二接地配线也可具有给半导体基体提供另外电位的构造。

[0180] 另外,上述实施例的每一个具有这样的构造,其中像素排布在纵向上和横向上,而两层的接地配线分别在纵向和横向伸展。

[0181] 然而,根据本发明,也可提供这样的构造,其中像素排布在倾斜方向上,而两层的接地配线分别在第一和第二方向上伸展。在此情况下,第一和第二方向为彼此倾斜地交叉。

[0182] 另外,根据本发明,像素不意味着限于矩形(或四角形)形状。就是说,像素也可构造为具有诸如六角形的另外的形状。

[0183] 另外,配线不必为直线。例如,也可提供这样的构造,其中六角形的像素提供在彼此不同的位置,而Z字形的配线沿着像素提供,并且总体上在一个方向上伸展。

[0184] 根据本发明的固态成像装置可应用于各种电子设备,例如,相机系统、具有成像功能的移动电话和具有成像功能的其它装置。相机系统的典型示例是数字相机和摄像机。

[0185] <4.第四实施例(电子设备)>

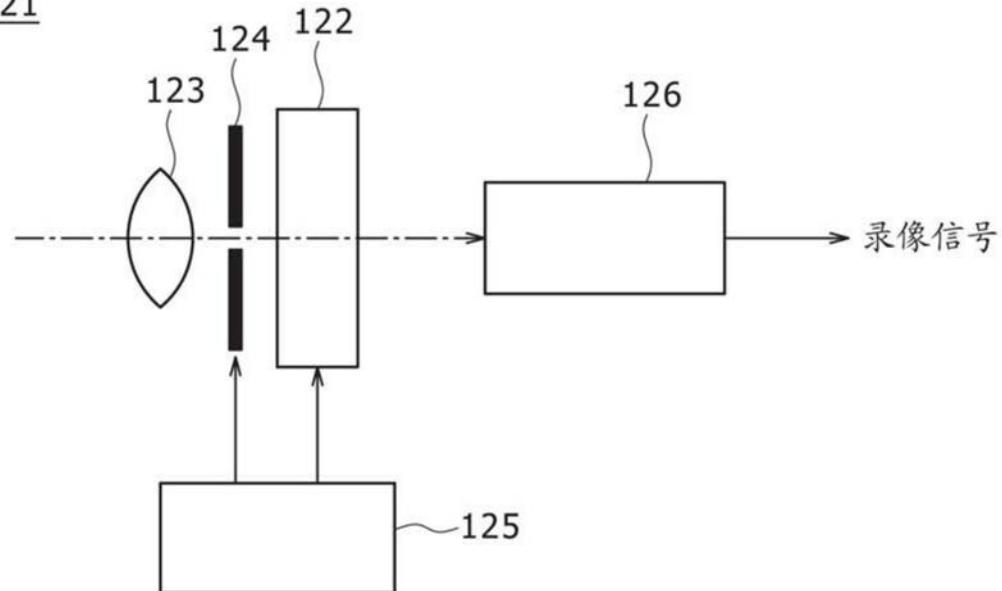

[0186] 图12是示出根据第四实施例的电子设备121的粗略构造的方框图。

[0187] 该实施例将本发明应用于具有能摄取静态图像和/或运动图像的相机的电子设备121。

[0188] 如图12所示,电子设备121包括固态成像装置122、光学系统123、快门装置124、驱动电路125和信号处理电路126。

[0189] 光学系统123构造为包括光学透镜。光学系统123根据来自成像物体的图像光的入射光在固态成像装置122的像素部上形成图像。因此,信号电荷在一段固定时间内在固态成像装置122中累积。光学系统123可为包括多个光学透镜的光学透镜系统。

[0190] 固态成像装置122是由本发明提供的固态成像装置。如上所述,本发明提供的固态成像装置是根据前面说明的任何一个实施例的固态成像装置。

[0191] 快门装置124为固态成像装置122控制光照射时间和光遮挡时间。

[0192] 驱动电路125给固态成像装置122提供驱动信号以控制由固态成像装置122执行的信号传输操作。另外,驱动电路125还给快门装置124提供驱动信号以控制由快门装置124执行的快门操作。根据由驱动电路125施加到固态成像装置122的用作定时信号的驱动信号,信号从固态成像装置122传输到信号处理电路126。

[0193] 信号处理电路126执行各种信号处理。作为执行信号处理的结果而获得的视频信号存储在诸如存储器的记录介质中或输出到监视器。

[0194] 根据如上所述的该实施例实施的电子设备121的构造,固态成像装置122是由本发明提供的固态成像装置。如前所述,本发明提供的固态成像装置是根据前面说明的任何一个实施例的固态成像装置。因此,能改善固态成像装置122产生的图像质量,并且提高固态成像装置122的产率。

[0195] 本发明提供的电子设备的构造不意味着限于图12所示的构造。就是说,本发明提供的电子设备可具有图12所示之外的构造,只要该构造包括本发明提供的固态成像装置。

[0196] 应注意,本发明也可实施成下面的实施方式:

[0197] (1)一种固态成像装置,包括:

[0198] 半导体基体;

[0199] 光敏二极管,形成在所述半导体基体上并且用于执行光电转换;

[0200] 像素部,提供有像素,所述像素的每一个具有所述光敏二极管;

[0201] 第一配线,形成为通过接触部电连接到所述像素部的所述半导体基体,并且在第一方向上延伸到所述像素部之外;

[0202] 第二配线,由与所述第一配线不同的配线层制作,并且形成为在与所述第一方向不同的第二方向上延伸到所述像素部之外;和

[0203] 接触部,用于将所述第一配线和所述第二配线彼此电连接。

[0204] (2)根据实施方式(1)的固态成像装置,其中多个所述像素共享电荷累积部和晶体管部。

[0205] (3)根据实施方式(2)的固态成像装置,所述固态成像装置还包括:

[0206] 传输栅极,设置在所述电荷累积部和所述光敏二极管之间;和

[0207] 控制线,电连接到所述传输栅极,

[0208] 其中所述第二配线在与所述控制线相同的高度上设置在多个控制线的任意相邻的控制线之间,所述多个控制线的每一个电连接至其中一个所述像素的所述传输栅极。

[0209] (4)根据实施方式(1)至(3)任何一项的固态成像装置,其中所述像素的外部的源给所述第一配线和所述第二配线提供地电位。

[0210] (5)一种电子设备,包括光学系统、根据实施方式(1)至(4)任何一项的固态成像装置以及用于处理固态成像装置输出信号的信号处理电路。

[0211] 本发明的实施方式不意味着限于前面描述的实施例。就是说,在不偏离本发明实质的范围内,可提供各种构造。

图1

图2A

图2B

图3

图4

图5

图6

图7

图8

图9

图10

图11

121

图12

图13

图 14A

图 14B