(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5631354号

(P5631354)

(45) 発行日 平成26年11月26日(2014.11.26)

(24) 登録日 平成26年10月17日(2014.10.17)

(51) Int.Cl.

F 1

|                    |                  |                    |             |

|--------------------|------------------|--------------------|-------------|

| <b>H01L 21/822</b> | <b>(2006.01)</b> | <b>H01L 27/04</b>  | <b>H</b>    |

| <b>H01L 27/04</b>  | <b>(2006.01)</b> | <b>H03K 19/003</b> | <b>E</b>    |

| <b>H03K 19/003</b> | <b>(2006.01)</b> | <b>H01L 27/06</b>  | <b>311C</b> |

| <b>H01L 27/06</b>  | <b>(2006.01)</b> |                    |             |

請求項の数 17 外国語出願 (全 26 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2012-103853 (P2012-103853)  |

| (22) 出願日     | 平成24年4月27日 (2012.4.27)        |

| (65) 公開番号    | 特開2012-253326 (P2012-253326A) |

| (43) 公開日     | 平成24年12月20日 (2012.12.20)      |

| 審査請求日        | 平成26年5月9日 (2014.5.9)          |

| (31) 優先権主張番号 | 13/152,867                    |

| (32) 優先日     | 平成23年6月3日 (2011.6.3)          |

| (33) 優先権主張国  | 米国 (US)                       |

早期審査対象出願

|           |                                                          |

|-----------|----------------------------------------------------------|

| (73) 特許権者 | 505274818<br>アナログ デバイシス、 インコーポレイ<br>テッド                  |

|           | アメリカ合衆国 マサチューセッツ 02<br>062-9106, ノーウッド, ワン<br>テクノロジー ウェイ |

| (74) 代理人  | 100078282<br>弁理士 山本 秀策                                   |

| (74) 代理人  | 100062409<br>弁理士 安村 高明                                   |

| (74) 代理人  | 100113413<br>弁理士 森下 夏樹                                   |

| (72) 発明者  | コルム ドノバン<br>スペイン国 バレンシア 46022,<br>ポエタ マス イ ロス 111-3      |

最終頁に続く

(54) 【発明の名称】金属酸化物半導体出力回路およびそれを形成する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板の表面上に配置されている第一のパッドと、

該基板の第一の金属酸化物半導体(MOS)トランジスタであって、該第一のMOSトランジスタは、第一の型であり、該第一のMOSトランジスタは、ゲート、ソースおよびドレインを含み、該ドレインは、該第一のパッドに電気的に接続されており、該ソースは、第一の供給電圧に電気的に接続されている、第一のMOSトランジスタと、

該基板の第二のMOSトランジスタであって、該第二のMOSトランジスタは、該第一の型とは反対の第二の型であり、該第二のMOSトランジスタは、ゲート、ソース、ドレインおよび本体を含み、該ゲートは、制御信号を受信するように構成されており、該ドレインは、該第一のMOSトランジスタのゲートに電気的に接続されている、第二のMOSトランジスタと、

該基板の第三のMOSトランジスタであって、該第三のMOSトランジスタは、該第一の型であり、該第三のMOSトランジスタは、ゲート、ドレイン、ソースおよび本体を含み、該ゲートは、バイアス信号を受信するように構成されており、該ドレインは、第二の供給電圧に電気的に接続されており、該ソースは、該第二のMOSトランジスタのソースに電気的に接続されており、該本体は、第一の参照電圧に電気的に接続されている、第三のMOSトランジスタと、

該基板の第四のMOSトランジスタであって、該第四のMOSトランジスタは、該第一の型であり、該第四のMOSトランジスタは、ゲート、ドレインおよびソースを含み、該

10

20

ゲートは、該制御信号に電気的に接続されており、該ドレインは、該第一のMOSトランジスタのゲートに電気的に接続されている、第四のMOSトランジスタと、

第五のMOSトランジスタおよびフィルタ回路であって、該フィルタ回路は、該第二の供給電圧をフィルタリングして、フィルタリングされた出力を生成するように構成されており、該第五のMOSトランジスタは、該基板のトランジスタであり、該第一の型であり、該第五のMOSトランジスタは、ゲート、ドレインおよびソースを含み、該ゲートは、該フィルタリングされた出力に電気的に接続されており、該ドレインは、該第四のMOSトランジスタのソースに電気的に接続されており、該ソースは、該第一の供給電圧に電気的に接続されている、第五のMOSトランジスタおよびフィルタ回路と

を含み、該第二のMOSトランジスタの本体は、該第三のMOSトランジスタのソースに電気的に接続されていることにより、一時的な信号イベントが該第一のパッド上で受け取られた場合に、該第二のMOSトランジスタのドレインから該第二の供給電圧まで該第二のMOSトランジスタの本体を通り流れる電流を妨げる、集積回路。10

#### 【請求項2】

前記フィルタ回路は、抵抗器およびコンデンサーを含み、該抵抗器は、前記第二の供給電圧に電気的に接続されている第一の端、および該コンデンサーの第一の端と前記第五のMOSトランジスタのゲートとに前記フィルタリングされた出力において電気的に接続されている第二の端を含み、該コンデンサーは、前記第一の供給電圧に電気的に接続されている第二の端をさらに含み、該抵抗器およびコンデンサーは、前記一時的な信号イベントが前記第一のパッド上で受け取られた場合に、該第二の供給電圧をフィルタリングするよう構成されている、請求項1に記載の集積回路。20

#### 【請求項3】

前記抵抗器は、150k ~ 300k の範囲の抵抗を有しており、前記コンデンサーは、1.5pF ~ 2.5pF の範囲の静電容量を有している、請求項2に記載の集積回路。

#### 【請求項4】

前記第一のMOSトランジスタは、高電圧二重拡散MOS(DMOS)トランジスタである、請求項1に記載の集積回路。

#### 【請求項5】

前記バイアス信号は、前記第三のMOSトランジスタのゲートとソースとの間の電圧の大きさが該第三のMOSトランジスタの最大定格ゲート-ソース電圧の1.0 ~ 1.5倍となるように選択された電圧レベルを有している、請求項1に記載の集積回路。30

#### 【請求項6】

前記第一の型は、p型であり、前記第二の型は、n型である、請求項1に記載の集積回路。

#### 【請求項7】

前記第一の型は、n型であり、前記第二の型は、p型である、請求項1に記載の集積回路。

#### 【請求項8】

前記第一の供給電圧は、接地供給であり、前記第二の供給電圧は、正の供給電圧である、請求項7に記載の集積回路。40

#### 【請求項9】

前記第一の参照電圧は、前記第一の供給電圧である、請求項1に記載の集積回路。

#### 【請求項10】

一時的な信号イベントからの保護を提供する方法であって、

該方法は、

第一のパッドを基板の表面の上方に形成することと、

第一の金属酸化物半導体(MOS)トランジスタを該基板上に形成することであって、該第一のMOSトランジスタは、第一の型であり、該第一のMOSトランジスタは、ゲート、ソースおよびドレインを含み、該ドレインは、該第一のパッドに電気的に接続されて50

おり、該ソースは、第一の供給電圧に電気的に接続されている、ことと、

第二のMOSトランジスタを該基板上に形成することであって、該第二のMOSトランジスタは、該第一の型の反対の第二の型であり、該第二のMOSトランジスタは、ゲート、ソース、ドレインおよび本体を含み、該ゲートは、制御信号を受信するように構成されており、該ドレインは、該第一のMOSトランジスタのゲートに電気的に接続されていることと、

第三のMOSトランジスタを該基板上に形成することであって、該第三のMOSトランジスタは、該第一の型であり、該第三のMOSトランジスタは、ゲート、ドレイン、ソースおよび本体を含み、該ゲートは、バイアス信号を受信するように構成されており、該ドレインは、第二の供給電圧に電気的に接続されており、該ソースは、該第二のMOSトランジスタのソースに電気的に接続されており、該本体は、第一の参照電圧に電気的に接続されていることと、10

第四のMOSトランジスタを該基板上に形成することであって、該第四のMOSトランジスタは、該第一の型であり、該第四のMOSトランジスタは、ゲート、ドレインおよびソースを含み、該ゲートは、該制御信号に電気的に接続されており、該ドレインは、該第一のMOSトランジスタのゲートに電気的に接続されていることと、

第五のMOSトランジスタを該基板上に形成することであって、該第五のMOSトランジスタは、該第一の型であり、該第五のMOSトランジスタは、ゲート、ドレインおよびソースを含み、該ゲートは、該第二の供給電圧のフィルタリングされたバージョンを受け取るように構成されており、該ドレインは、該第四のMOSトランジスタのソースに電気的に接続されており、該ソースは、該第一の供給電圧に電気的に接続されていることと20

を含み、該第二のMOSトランジスタの本体は、該第三のMOSトランジスタのソースに電気的に接続されていることにより、一時的な信号イベントが該第一のパッド上で受け取られた場合に、該第二のMOSトランジスタのドレインから該第二の供給電圧まで該第二のMOSトランジスタの本体を通り流れる電流を妨げる、方法。

#### 【請求項11】

抵抗器およびコンデンサーを含むフィルタを提供することをさらに含み、該抵抗器は、前記第二の供給電圧に電気的に接続されている第一の端、および該コンデンサーの第一の端と前記第五のMOSトランジスタのゲートとに前記フィルタリングされた出力において電気的に接続されている第二の端を含み、該コンデンサーは、前記第一の供給電圧に電気的に接続されている第二の端をさらに含み、該抵抗器およびコンデンサーは、前記一時的な信号イベントが前記第一のパッド上で受け取られた場合に、前記第四のMOSトランジスタが該一時的な信号イベント中に前記第一のMOSトランジスタのゲートを帯電または放電することを妨げるように、該第二の供給電圧をフィルタリングするように構成されている、請求項10に記載の方法。30

#### 【請求項12】

前記抵抗器は、150 k ~ 300 k の範囲の抵抗を有しており、前記コンデンサーは、1.5 pF ~ 2.5 pF の範囲の静電容量を有している、請求項11に記載の方法。

#### 【請求項13】

前記第一のMOSトランジスタは、高電圧二重拡散MOS(DMOS)トランジスタである、請求項10に記載の方法。40

#### 【請求項14】

前記バイアス信号は、前記第三のMOSトランジスタのゲートとソースとの間の電圧の大きさが該第三のMOSトランジスタの最大定格ゲート-ソース電圧の1.0 ~ 1.5倍になるように選択された電圧レベルを有している、請求項10に記載の方法。

#### 【請求項15】

前記第一の型は、p型であり、前記第二の型は、n型である、請求項10に記載の方法。45

#### 【請求項16】

前記第一の型は、n型であり、前記第二の型は、p型である、請求項10に記載の方法50

。

### 【請求項 17】

前記第一の参照電圧は、前記第一の供給電圧である、請求項10に記載の方法。

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

(発明の詳細な説明)

(背景)

(発明の分野)

発明の実施形態は、電子システムに関する。より具体的には、発明の実施形態は、電子 10

システムのための金属酸化物半導体（MOS）出力回路に関する。

#### 【背景技術】

#### 【0002】

(発明の背景)

(関連技術の説明)

ある電子システムは、一時的な信号イベント、または急速に変化する電圧および高電力を有している比較的短い持続期間の電気信号に晒され得る。一時的な信号イベントは、例えば、物または人から電子システムへの電荷の急な解放により生じる静電気放電（ESD）イベントを含み得る。

#### 【0003】

一時的な信号イベントは、集積回路（IC）の比較的小さい範囲にわたる過電圧条件および／または高レベルな電力散逸に起因して、出力ドライバー回路のような電子システム中のICの一部に損傷を与え得る。高電力散逸は、IC温度を増加させ得、ゲート酸化物突抜け現象、接合損傷、金属損傷、および／または表面電荷蓄積のような数多くの信頼性問題につながり得る。さらに、一時的な信号イベントは、ラッチャップ（換言すると、低インピーダンスパスの偶然の生成）を誘導し得ることによって、ICの機能を中断させ、ICへの永続的な損傷を潜在的に引き起こす。したがって、ICのピンまたはパッドへ接続された出力ドライバーを含み、ICの機能性および／または信頼性に影響せずに、安全に高電力で一時的な信号イベントを放電する能力を有しているICを提供する必要性がある。

20

### 【発明の概要】

### 【課題を解決するための手段】

#### 【0004】

(概要)

金属酸化物半導体（MOS）出力回路およびそれを形成する方法が提供される。一実施形態において、集積回路が提供される。集積回路は、基板の表面の上に配置された第一のパッド、第一のMOSトランジスタを含む。第一のMOSトランジスタは、基板であり、第一の型である。第一のMOSトランジスタは、ゲート、ソースおよびドレインを含む。ドレインは、第一のパッドに電気的に接続されている。ソースは、第一の供給電圧に電気的に接続されている。集積回路は、第二のMOSトランジスタをさらに含む。第二のMOSトランジスタは、基板であり、第一の型とは反対の第二の型である。第二のMOSトランジスタは、ゲート、ソース、ドレンおよび本体を含む。ゲートは、制御信号を受信するように構成されている。ドレンは、第一のMOSトランジスタのゲートに電気的に接続されている。集積回路は、第三のMOSトランジスタをさらに含む。第三のMOSトランジスタは、基板であり、第一の型である。第三のMOSトランジスタは、ゲート、ドレン、ソースおよび本体を含む。ゲートは、バイアス信号を受信するように構成されている。ドレンは、第二の供給電圧に電気的に接続されている。ソースは、第二のMOSトランジスタのソースに電気的に接続されている。本体は、第一の参照電圧に電気的に接続されている。第二のMOSトランジスタの本体は、一時的な信号イベントが第一のパッド上で受け取られた場合に、第二のMOSトランジスタのドレンから第二の供給電圧まで

30

40

50

第二のMOSトランジスタの本体を通り流れる電流を妨げるよう、第三のMOSトランジスタのソースに電気的に接続されている。

#### 【0005】

別の実施形態において、一時的な信号イベントからの保護を提供する方法が提供される。方法は、第一のパッドを基板の表面の上に形成することと、第一のMOSトランジスタを基板上に形成することとを含む。第一のMOSトランジスタは、第一の型であり、ゲート、ソースおよびドレインを含む。ドレインは、第一のパッドに電気的に接続されている。ソースは、第一の供給電圧に電気的に接続されている。方法は、第二のMOSトランジスタを基板上に形成することをさらに含む。第二のMOSトランジスタは、第一の型とは反対の第二の型である。第二のMOSトランジスタは、ゲート、ソース、ドレインおよび本体を含む。ゲートは、制御信号を受信するように構成されている。ドレインは、第一のMOSトランジスタのゲートに電気的に接続されている。方法は、第三のMOSトランジスタを基板上に形成することをさらに含む。第三のMOSトランジスタは、第一の型である。第三のMOSトランジスタは、ゲート、ドレイン、ソースおよび本体を含む。ゲートは、バイアス信号を受信するように構成されている。ドレインは、第二の供給電圧に電気的に接続されている。ソースは、第二のMOSトランジスタのソースに電気的に接続されている。本体は、第一の参照電圧に電気的に接続されている。第二のMOSトランジスタの本体は、一時的な信号イベントが第一のパッド上で受け取られた場合に、第二のMOSトランジスタのドレインから第二の供給電圧まで第二のMOSトランジスタの本体を通り流れる電流を妨げるよう、第三のMOSトランジスタのソースに電気的に接続されている。10

#### 【0006】

例えば、本発明は以下の項目を提供する。

##### (項目1)

基板の表面上に配置されている第一のパッド(61)と、

第一の金属酸化物半導体(MOS)トランジスタ(62)であって、該第一のMOSトランジスタは、該基板および第一の型であり、該第一のMOSトランジスタは、ゲート、ソースおよびドレインを含み、該ドレインは、該第一のパッドに電気的に接続されており、該ソースは、第一の供給電圧に電気的に接続されている、第一のMOSトランジスタと、30

第二のMOSトランジスタ(65)であって、該第二のMOSトランジスタは、該基板および該第一の型とは反対の第二の型であり、該第二のMOSトランジスタは、ゲート、ソース、ドレインおよび本体を含み、該ゲートは、制御信号を受信するように構成されており、該ドレインは、該第一のMOSトランジスタのゲートに電気的に接続されている、第二のMOSトランジスタと、

第三のMOSトランジスタ(66)であって、該第三のMOSトランジスタは、該基板および該第一の型であり、該第三のMOSトランジスタは、ゲート、ドレイン、ソースおよび本体を含み、該ゲートは、バイアス信号を受信するように構成されており、該ドレインは、第二の供給電圧に電気的に接続されており、該ソースは、該第二のMOSトランジスタのソースに電気的に接続されており、該本体は、第一の参照電圧に電気的に接続されている、第三のMOSトランジスタと40

を含み、該第二のMOSトランジスタの本体は、該第三のMOSトランジスタのソースに電気的に接続されていることにより、一時的な信号イベントが該第一のパッド上で受け取られた場合に、該第二のMOSトランジスタのドレインから該第二の供給電圧まで該第二のMOSトランジスタの本体を通り流れる電流を妨げる、集積回路。

##### (項目2)

前記基板および前記第一の型である第四のMOSトランジスタ(64)をさらに含み、該第四のMOSトランジスタは、ゲート、ドレインおよびソースを含み、該ゲートは、前記制御信号に電気的に接続されており、該ドレインは、前記第一のMOSトランジスタのゲートに電気的に接続されている、上記項目のうちのいずれかに記載の集積回路。50

## (項目3)

第五のMOSトランジスタ(81)およびフィルタ回路(85)をさらに含み、該フィルタ回路は、前記第二の供給電圧をフィルタリングして、フィルタリングされた出力を生成するように構成されており、該第五のMOSトランジスタは、前記基板および前記第一の型であり、該第五のMOSトランジスタは、ゲート、ドレインおよびソースを含み、該ゲートは、該フィルタリングされた出力に電気的に接続されており、該ドレインは、前記第四のMOSトランジスタのソースに電気的に接続されており、該ソースは、前記第一の供給電圧に電気的に接続されている、上記項目のうちのいずれか一項目に記載の集積回路。

## (項目4)

10

前記フィルタ回路は、抵抗器(86)およびコンデンサー(87)を含み、該抵抗器は、前記第二の供給電圧に電気的に接続されている第一の端、および該コンデンサーの第一の端と前記第五のMOSトランジスタのゲートとに前記フィルタリングされた出力において電気的に接続されている第二の端を含み、該コンデンサーは、前記第一の供給電圧に電気的に接続されている第二の端をさらに含み、該抵抗器およびコンデンサーは、前記一時的な信号イベントが前記第一のパッド上で受け取られた場合に、該第二の供給電圧をフィルタリングするように構成されている、上記項目のうちのいずれか一項目に記載の集積回路。

## (項目5)

20

前記抵抗器は、約150k~約300kの範囲の抵抗を有しており、前記コンデンサーは、約1.5pF~約2.5pFの範囲の静電容量を有している、上記項目のうちのいずれか一項目に記載の集積回路。

## (項目6)

前記第一のMOSトランジスタは、高電圧二重拡散MOS(DMOS)トランジスタである、上記項目のうちのいずれか一項目に記載の集積回路。

## (項目7)

30

前記バイアス信号は、前記第三のMOSトランジスタのゲートとソースとの間の電圧の大きさが該第三のMOSトランジスタの最大定格ゲート-ソース電圧の約1.0~約1.5倍となるように選択された電圧レベルを有している、上記項目のうちのいずれか一項目に記載の集積回路。

## (項目8)

前記第一の型は、p型であり、前記第二の型は、n型である、上記項目のうちのいずれか一項目に記載の集積回路。

## (項目9)

前記第一の型は、n型であり、前記第二の型は、p型である、上記項目のうちのいずれか一項目に記載の集積回路。

## (項目10)

前記第一の供給電圧は、接地供給であり、前記第二の供給電圧は、正の供給電圧である、上記項目のうちのいずれか一項目に記載の集積回路。

## (項目11)

40

前記第一の参照電圧は、前記第一の供給電圧である、上記項目のうちのいずれか一項目に記載の集積回路。

## (項目12)

一時的な信号イベントからの保護を提供する方法であって、

該方法は、

第一のパッド(61)を基板(71)の表面の上方に形成することと、

第一の金属酸化物半導体(MOS)トランジスタ(62)を該基板上に形成することであって、該第一のMOSトランジスタは、第一の型であり、該第一のMOSトランジスタは、ゲート、ソースおよびドレインを含み、該ドレインは、該第一のパッドに電気的に接続されており、該ソースは、第一の供給電圧に電気的に接続されている、ことと、

50

第二のMOSトランジスタ(65)を該基板上に形成することであつて、該第二のMOSトランジスタは、該第一の型の反対の第二の型であり、該第二のMOSトランジスタは、ゲート、ソース、ドレインおよび本体を含み、該ゲートは、制御信号を受信するように構成されており、該ドレインは、該第一のMOSトランジスタのゲートに電気的に接続されている、ことと、

第三のMOSトランジスタ(66)を該基板上に形成することであつて、該第三のMOSトランジスタは、該第一の型であり、該第三のMOSトランジスタは、ゲート、ドレイン、ソースおよび本体を含み、該ゲートは、バイアス信号を受信するように構成されており、該ドレインは、第二の供給電圧に電気的に接続されており、該ソースは、該第二のMOSトランジスタのソースに電気的に接続されており、該本体は、第一の参照電圧に電気的に接続されている、ことと

10

を含み、該第二のMOSトランジスタの本体は、該第三のMOSトランジスタのソースに電気的に接続されていることにより、一時的な信号イベントが該第一のパッド上で受け取られた場合に、該第二のMOSトランジスタのドレインから第二の供給電圧まで該第二のMOSトランジスタの本体を通り流れる電流を妨げる、方法。

(項目13)

第四のMOSトランジスタ(64)を前記基板上に形成することをさらに含み、該第四のMOSトランジスタは、前記第一の型であり、該第四のMOSトランジスタは、ゲート、ドレインおよびソースを含み、該ゲートは、前記制御信号に電気的に接続されており、該ドレインは、前記第一のMOSトランジスタのゲートに電気的に接続されている、上記項目のうちのいずれかに記載の方法。

20

(項目14)

第五のMOSトランジスタ(81)を前記基板上に形成することをさらに含み、該第五のMOSトランジスタは、前記第一の型であり、該第五のMOSトランジスタは、ゲート、ドレインおよびソースを含み、該ゲートは、前記第二の供給電圧のフィルタリングされたバージョンを受け取るように構成されており、該ドレインは、前記第四のMOSトランジスタのソースに電気的に接続されており、該ソースは、前記第一の供給電圧に電気的に接続されている、上記項目のうちのいずれか一項目に記載の方法。

(項目15)

抵抗器(86)およびコンデンサー(87)を含むフィルタ(85)を提供することをさらに含み、該抵抗器は、前記第二の供給電圧に電気的に接続されている第一の端、および該コンデンサーの第一の端と前記第五のMOSトランジスタのゲートとに前記フィルタリングされた出力において電気的に接続されている第二の端を含み、該コンデンサーは、前記第一の供給電圧に電気的に接続されている第二の端をさらに含み、該抵抗器およびコンデンサーは、前記一時的な信号イベントが前記第一のパッド上で受け取られた場合に、前記第四のMOSトランジスタが該一時的な信号イベント中に前記第一のMOSトランジスタのゲートを帯電または放電することを妨げるよう、該第二の供給電圧をフィルタリングするように構成されている、上記項目のうちのいずれか一項目に記載の方法。

30

(項目16)

前記抵抗器は、約150k~約300kの範囲の抵抗を有しており、前記コンデンサーは、約1.5pF~約2.5pFの範囲の静電容量を有している、上記項目のうちのいずれか一項目に記載の方法。

40

(項目17)

前記第一のMOSトランジスタは、高電圧二重拡散MOS(DMOS)トランジスタである、上記項目のうちのいずれか一項目に記載の方法。

(項目18)

前記バイアス信号は、前記第三のMOSトランジスタのゲートとソースとの間の電圧の大きさが該第三のMOSトランジスタの最大定格ゲート-ソース電圧の約1.0~約1.5倍になるように選択された電圧レベルを有している、上記項目のうちのいずれか一項目に記載の方法。

50

## (項目 19)

前記第一の型は、p型であり、前記第二の型は、n型である、上記項目のうちのいずれか一項目に記載の方法。

## (項目 20)

前記第一の型は、n型であり、前記第二の型は、p型である、上記項目のうちのいずれか一項目に記載の方法。

## (項目 21)

前記第一の参照電圧は、前記第一の供給電圧である、上記項目のうちのいずれか一項目に記載の方法。

## 【0007】

10

## (開示の要約)

金属酸化物半導体(MOS)保護回路およびそれを形成する方法が開示される。一実施形態において、集積回路は、パッド(61)、p型MOS(PMOS)トランジスタ(65)、第一のn型MOS(NMOS)トランジスタ(62)および第二のNMOSトランジスタ(66)を含む。第一のNMOSトランジスタは、PMOSトランジスタのパッド、第一の供給電圧およびドレインに、それぞれ電気的に接続されているドレイン、ソースおよびゲートを含む。第二のNMOSトランジスタは、PMOSトランジスタのバイアスノード、第二の供給電圧およびソースに、それぞれ電気的に接続されているゲート、ドレインおよびソースを含む。第二のNMOSトランジスタのソースは、一時的な信号イベントがパッド上で受け取られた場合に、PMOSトランジスタのドレインから第二の供給電圧までPMOSトランジスタの本体を通り流れる電流を妨げるように、PMOSトランジスタの本体にさらに電気的に接続されている。

20

## 【図面の簡単な説明】

## 【0008】

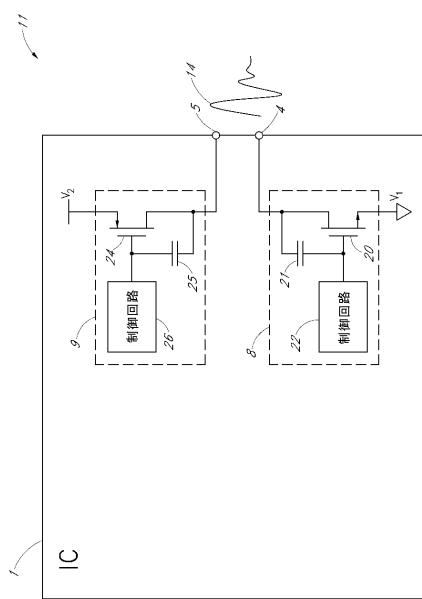

【図1A】図1Aは、電子システムの一例の概略ブロック図である。

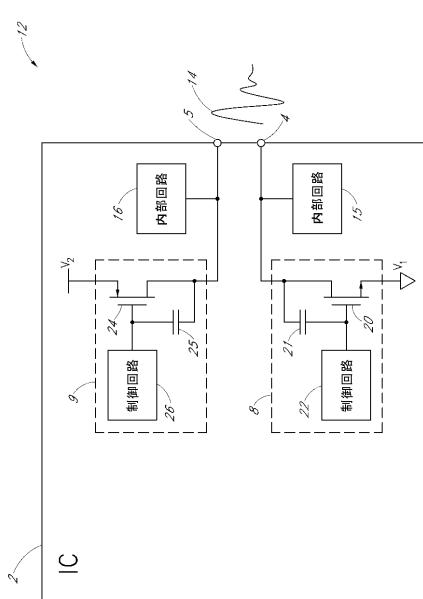

【図1B】図1Bは、電子システムの別の例の概略ブロック図である。

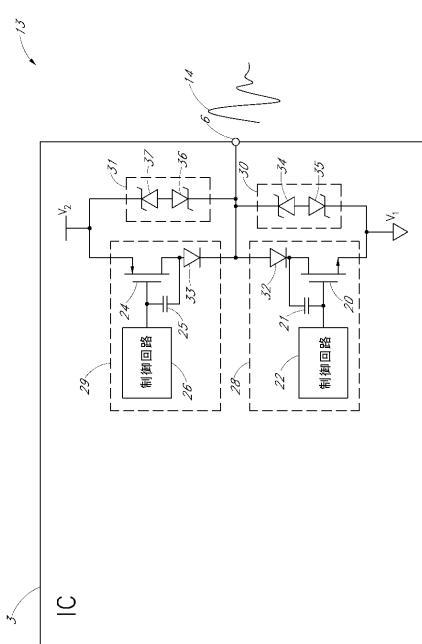

【図1C】図1Cは、電子システムのさらに別の例の概略ブロック図である。

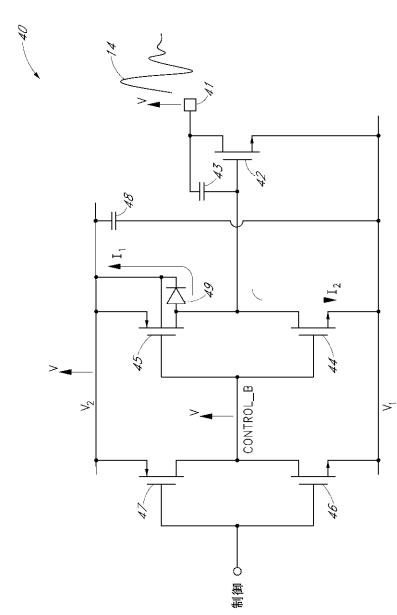

【図2】図2は、パッドおよびn型金属酸化物半導体(NMOS)トランジスタを含む集積回路の一部の例の注釈をつけられている回路図である。

【図3A】図3Aは、一実施形態に従うNMOS保護回路の概略ブロック図である。

30

【図3B】図3Bは、図3AのNMOS保護回路の一部の一実装の断面図である。

【図4】図4は、別の実施形態に従うNMOS保護回路の概略ブロック図である。

【図5】図5は、さらに別の実施形態に従うNMOS保護回路の概略ブロック図である。

【図6】図6は、一実施形態に従うp型金属酸化物半導体(PMOS)保護回路の概略ブロック図である。

【図7A】図7Aは、NMOSトランジスタに対するドレイン-ソース電流対ドレイン-ソース電圧の一例のグラフである。

【図7B】図7Bは、ドレイン-ソース電流、ドレイン-ソース電圧、およびゲート電圧対時間の一例のグラフである。

【図7C】図7Cは、ドレイン-ソース電流、ドレイン-ソース電圧、およびゲート電圧対時間の別の例のグラフである。

40

## 【発明を実施するための形態】

## 【0009】

## (実施形態の詳細な説明)

以下のある実施形態の詳細な説明は、発明の特定の実施形態の様々な説明を示す。しかし、発明は、特許請求の範囲によって規定され、含まれる複数の異なる方法によって具現化され得る。この説明において、図面が参照される。図面において、類似の参照数字は、同一または機能的に類似する素子を示す。

## 【0010】

電子システムは、典型的には、回路または回路における構成要素を一時的な信号イベン

50

トから保護するように構成されている。さらに、電子システムが信頼性を有していることを保証するのを助けるために、製造業者は、規定されたストレス条件下で、電子システムをテストし得る。ストレス条件は、the Joint Electronic Device Engineering Council (JEDEC)、the International Electrotechnical Commission (IEC)、およびthe Automotive Engineering Council (AEC)のような様々な組織によって設定された規格によって記述され得る。規格は、ESDイベントを含む幅広い範囲の一時的な信号イベントを含み得る。

#### 【0011】

電子回路信頼性は、自己保護的であるか、または一時的な信号保護を提供する別個の構造を必要としないデバイスを用いて提供され得る。例えば、NMOSまたはPMOSトランジスタのような電界効果トランジスタは、ICの通常動作中に電気回路において機能することと、一時的な信号保護を一時的な信号イベント中に単独または他の構成要素と組合わせて提供することを行なうように構成され得る。ICに自己保護的なデバイスを含むことによって、電子システムは、信頼性と、製造コストが低く、回路範囲が比較的小さいという性能要件とを満たし得る。

#### 【0012】

(電子システムの様々な例の概観)

図1Aは、様々な実施形態に従う1つ以上の保護回路を含み得る電子システム11の一例の概略ブロック図である。例示された電子システム11は、第一および第二のピンまたはパッド4、5と、第一および第二の出力ドライバー回路8、9とを含む集積回路(IC)1を含む。

#### 【0013】

第一の出力ドライバー回路8は、第一のパッド4に電気的に接続されており、NMOSトランジスタ20、第一のコンデンサー21、および第一の制御回路22を含む。ある実装において、NMOSトランジスタは、例えば、二重拡散MOS(DMOS)トランジスタのようなドレイン拡張MOSトランジスタを含む高電圧MOS(HV-MOS)デバイスであり得る。NMOSトランジスタ20は、例えば、接地または負の供給電圧であり得る第一の供給電圧V<sub>1</sub>に電気的に接続されているソースを含む。NMOSトランジスタ20は、第一の制御回路22と第一のコンデンサー21の第一の端とに電気的に接続されているゲート、および第一のコンデンサー21の第二の端と第一のパッド4とに電気的に接続されているドレインをさらに含む。第一のコンデンサー21は、例えば、NMOSトランジスタ20のドレインの金属相互接続および/または拡散領域と、NMOSトランジスタ20のゲートの金属および/またはポリシリコン構造との間の寄生コンデンサーを表し得る。しかし、ある実装において、第一のコンデンサー21は、他の構造から形成され得る。

#### 【0014】

第二の出力ドライバー回路9は、第二のパッド5に電気的に接続されており、PMOSトランジスタ24、第二のコンデンサー25および第二の制御回路26を含む。PMOSトランジスタ24は、例えば、正の供給電圧であり得る第二の供給電圧V<sub>2</sub>に電気的に接続されているソースを含む。PMOSトランジスタ24は、第二の制御回路26と第二のコンデンサー25の第一の端とに電気的に接続されているゲート、および第二のコンデンサー25の第二の端と第二のパッド5とに電気的に接続されているドレインをさらに含む。第二のコンデンサー25は、例えば、PMOSトランジスタ24のドレインの金属相互接続および/または拡散領域と、PMOSトランジスタ24のゲートの金属および/またはポリシリコン構造との間の寄生コンデンサーを表し得る。しかし、ある実装において、第二のコンデンサー25は、他の構造から形成され得る。

#### 【0015】

第一および第二の出力ドライバー回路8、9は、信号をIC1から、それぞれ第一および第二のパッド4、5を用いて通信するために用いられ得る。例えば、制御回路22、2

10

20

30

40

50

6は、それぞれ、N MOSおよびPMOSトランジスタ20、24の状態を制御するため用いられ得、それによって第一および第二のパッド4、5の電位を制御する。加えて、第一および第二の制御回路22、26は、第一および/または第二の供給電圧V<sub>1</sub>、V<sub>2</sub>の初期化のようなパワーアップ条件中にN MOSおよびPMOSトランジスタ20、24の状態を制御するためにも用いられ得る。

#### 【0016】

IC1の第一および第二のピン4、5は、ESDイベントのような一時的な信号イベントに晒され得る。一時的な信号イベントは、一時的な信号イベントに対して保護されていない場合に、IC損傷を引き起こし得、ラッチアップを誘導し得る。例えば、第一および/または第二のパッド4、5は、一時的な信号イベント14を受け取り得る。N MOSおよびPMOSトランジスタ20、24は、以下に説明されるように、一時的な信号イベント中に保護を第一および第二の出力ドライバー回路8、9に提供し得る。したがって、N MOSおよびPMOSトランジスタ20、24は、通常動作中に信号通知機能性を提供し得るだけでなく、N MOSおよびPMOSトランジスタ20、24は、一時的な信号イベント中に自己保護的なデバイスとしても動作し得る。自己保護的なN MOSおよびPMOSトランジスタ20、24をIC1上に含むことは、別個の保護デバイスを採用するスキームに対して、比較的小さい範囲を有している出力ドライバーおよび/または他の回路を提供するのを助け得る。

#### 【0017】

一時的な信号イベント中に、第一および第二のコンデンサー21、25は、一時的な信号イベント保護をN MOSおよびPMOSトランジスタ20、24を用いて提供することを助け得る変位または結合電流を提供し得る。例えば、第一のコンデンサー21は、一時的な信号イベントに関連する電圧変化のような第一のパッド4上における電圧の突然の変化に応答して、N MOSトランジスタ20のゲートを結合し得る。例えば、一時的な信号イベント中に、第一のコンデンサー21は、N MOSトランジスタ20のドレインからゲートに電流Iを注入し得る。電流Iは、約C<sub>21</sub>\*dV<sub>4</sub>/dtに等しく、ここで、C<sub>21</sub>は、第一のコンデンサー21の静電容量であり、dV<sub>4</sub>/dtは、第一のパッド4における電圧変化の速度である。ある速度および持続時間で第一のパッド4の電圧を変化させる一時的な信号イベントに応答して、第一のコンデンサー21は、N MOSトランジスタ20のゲートの電圧を、N MOSトランジスタ20のゲート-ソース電圧がN MOSトランジスタ20の閾値電圧を超えるのに十分なレベルまで、有効ゲート-ソース静電容量を帯電させることによって、増加させ得る。したがって、電圧変化の十分な速度および持続時間の一時的な信号イベントの間、第一のコンデンサー21は、N MOSトランジスタ20のゲート電圧を、N MOSトランジスタ20を低インピーダンスオン状態まで遷移させるのに十分なレベルまで結合するために用いられ得る。N MOSトランジスタ20が立ち上げられると、N MOSトランジスタ20は、ドレイン-ソース電流を低インピーダンスチャネルを通して伝導し得ることによって、第一のパッド4の電圧の大きさを減少させ、一時的な信号イベント14に対して、N MOSトランジスタ20のドレインとソースとの間に低インピーダンス放電バスを生成する。同様に、第二のコンデンサー25は、一時的な信号イベント保護をPMOSトランジスタ24を用いて提供することを助け得る変位電流を提供し得る。

#### 【0018】

図1Aの保護回路は、第一および第二の出力ドライバー回路8、9が、それぞれ第一および第二のパッド4、5に電気的に接続される構成を例示する。この構成において、IC1は、例えば、コントローラーエリアネットワーク(CAN)インターフェースを含む電子システムを含む幅広い様々な電子システムおよび用途において用いられ得る。しかし、当業者は、IC1が他のシステムにおける使用に適合され得ることを認識する。例えば、IC1が、ローカル相互接続ネットワーク(LIN)インターフェースにわたり動作するよう構成されているシステムにおいて用いられた場合は、第一および第二の出力ドライバー回路8、9は、同じパッドに電気的に接続されるように改変され得る。

10

20

30

40

50

## 【0019】

図1Bは、電子システム12の別の例の概略ブロック図である。例示された電子システム12は、第一および第二のピンまたはパッド4、5と、第一および第二の出力ドライバー回路8、9と、第一および第二の内部回路15、16とを含むIC2を含む。図1Bの電子システム12は、図1BのIC2が第一および第二の内部回路15、16をさらに含むことを除いて、図1Aの電子システム11に類似する。第一および第二の内部回路15、16は、それぞれ、第一および第二のパッド4、5に電気的に接続されている。図1Bにおいて例示されるように、NMOSトランジスタ20は、保護をIC2の第一の出力ドライバー回路8と第一の内部回路15との両方に提供し得る。同じように、PMOSトランジスタ24は、保護をIC2の第二の出力ドライバー回路9と第二の内部回路16との両方に提供し得る。したがって、ある実装において、NMOSおよびPMOSトランジスタ20、24は、自己保護だけでなく、保護を他の回路および/または構造にも提供するために用いられ得る。10

## 【0020】

図1Cは、電子システム13のさらに別の例の概略ブロック図である。例示された電子システム13は、パッド6と、第一および第二の出力ドライバー回路28および29と、第一および第二の補助保護回路30、31とを含むIC3を含む。

## 【0021】

第一の出力ドライバー回路28は、パッド6に電気的に接続されており、NMOSトランジスタ20、第一のコンデンサー21、第一の制御回路22および第一のブロッキングダイオード32を含む。NMOSトランジスタ20は、第一の供給電圧V<sub>1</sub>に電気的に接続されているソース、第一の制御回路22と第一のコンデンサー21の第一の端とに電気的に接続されているゲート、および第一のコンデンサー21の第二の端と第一のブロッキングダイオード32のカソードとに電気的に接続されているドレインを含む。第一のブロッキングダイオード32は、パッド6に電気的に接続されているアノードをさらに含む。第一の出力ドライバー回路28は、第一の出力ドライバー回路28がNMOSトランジスタ20のパッド6とドレインとの間に挿入された第一のブロッキングダイオード32をさらに含むことを除いて、図1A～図1Bの第一の出力ドライバー回路8に類似する。第一のブロッキングダイオード32は、システムに対して、NMOSトランジスタ20の本体を通した伝導を妨げることを助け得る。システムにおいて、ピン6は、通常動作中に参照電圧V<sub>1</sub>よりも低くあり得る電圧レベルを有している。第一のブロッキングダイオード32を第一の出力ドライバー回路28に含むことは、一時的な信号イベントがNMOSトランジスタ20のゲート上に結合することを妨げることを助け得（そうでない場合は、一時的な信号イベントは、パッド6の電圧を減らす）、保護スキームを、大きい正/負の電圧レベルを有して動作するピンに対して、以下に詳細に説明されるように、MOSトランジスタと補助保護回路との両方を用いて実装する場合に、有用であり得る。2030

## 【0022】

第二の出力ドライバー回路29は、パッド6に電気的に接続されており、PMOSトランジスタ24、第二のコンデンサー25、第二の制御回路26、および第二のブロッキングダイオード33を含む。PMOSトランジスタ24は、第二の供給電圧V<sub>2</sub>に電気的に接続されているソース、第二の制御回路26と第二のコンデンサー25の第一の端とに電気的に接続されているゲート、および第二のコンデンサー25の第二の端と第二のブロッキングダイオード33のアノードとに電気的に接続されているドレインを含む。第二のブロッキングダイオード33は、パッド6に電気的に接続されているカソードをさらに含む。第二の出力ドライバー回路29は、第二の出力ドライバー回路29がPMOSトランジスタ24のパッド6とドレインとの間に挿入された第二のブロッキングダイオード33をさらに含むことを除いて、図1A～図1Bの第二の出力ドライバー回路9に類似する。第二のブロッキングダイオード33は、システムに対して、PMOSトランジスタ24の本体を通る伝導を妨げることを助け得る。システムにおいて、ピン6は、通常動作中に参照電圧V<sub>2</sub>より上であり得る電圧レベルを有している。第二のブロッキングダイオード334050

を第二の出力ドライバー回路 29 に含むことは、一時的な信号イベントが PMOS トランジスタ 24 のゲート上に結合することを妨げることを助け得（そうでない場合は、一時的な信号イベントは、パッド 6 の電圧を増加させる）、保護スキームを、大きい正／負の電圧レベルを有して動作するピンに対して、下記に詳細に説明されるように、MOS トランジスタと補助保護回路との両方を用いて実装する場合に、有用であり得る。

#### 【0023】

第一の補助保護回路 30 は、第三のブロッキングダイオード 34 および第四のブロッキングダイオード 35 を含む。第三のブロッキングダイオード 34 は、パッド 6 に電気的に接続されているカソードおよび第四のブロッキングダイオード 35 のアノードに電気的に接続されているアノードを含む。第四のブロッキングダイオード 35 は、第一の供給電圧  $V_1$  に電気的に接続されているカソードをさらに含む。第一の補助保護回路 30 は、パッド 6 の電圧を第三のブロッキングダイオード 34 の所定のブロッキング電圧より上まで増加させる正の一時的な信号イベントと、パッド 6 の電圧を第四のブロッキングダイオード 35 の所定のブロッキング電圧より下に減らす負の一時的な信号イベントとの両方に対する保護を提供し得る。例えば、一時的な信号イベントがパッド 6 の電圧を増加させた場合は、第一の補助保護回路 30 は、第四のブロッキングダイオード 35 が順方向バイアスをかけられる降伏の条件に到達し得、第三のブロッキングダイオード 34 は、例えば、動作電圧レベルに応じて、電子なだれおよび／またはツェナー型降伏のような降伏の条件に到達する。同様に、一時的な信号イベントがパッド 6 の電圧を減らせた場合は、第一の補助保護回路 30 は、第三のブロッキングダイオード 34 が順方向バイアスをかけられる降伏の条件に到達し得、第四のブロッキングダイオード 35 も降伏の条件に到達する。10

#### 【0024】

第二の補助保護回路 31 は、第五のブロッキングダイオード 36 および第六のブロッキングダイオード 37 を含む。第五のブロッキングダイオード 36 は、パッド 6 に電気的に接続されているカソードおよび第六のブロッキングダイオード 37 のアノードに電気的に接続されているアノードを含む。第六のブロッキングダイオード 37 は、第二の供給電圧  $V_2$  に電気的に接続されているカソードをさらに含む。第二の補助保護回路 31 は、第一の補助保護回路 30 を参照して上記で説明したものと類似した態様で、一時的な信号イベントに対する双方向保護を提供し得る。20

#### 【0025】

第一および第二の出力ドライバー回路 28、29、ならびに第一および第二の補助保護回路 30、31 は、NMOS および PMOS トランジスタ 20、24 と、第一および第二の補助保護回路 30、31 との両方が一時的な信号イベント保護を提供するために用いられる構成において用いられ得る。例えば、先に示したように、NMOS および PMOS トランジスタ 20、24 は、それぞれ、二重拡散 MOS (DMOS) および／または高電圧 MOS (HV-MOS) トランジスタであり得る。二重拡散 MOS (DMOS) および／または高電圧 MOS (HV-MOS) トランジスタは、一時的な信号イベント保護を単独で提供するようなサイズにされた場合に、IC3 の比較的多くの面積を占め得る。したがって、ある実装において、MOS デバイスは、目標保護性能特性に到達するようなサイズにされるか、および／または、そうでない場合は、到達するように最適化される他の補助保護デバイスと組合せて用いられ得、それにより、独立してストレスを受ける構造を用いて、スキームに対する回路面積を最小化する。30

#### 【0026】

図 1C は、第一および第二の出力ドライバー回路 28、29 が同じパッド 6 に電気的に接続される構成を示し、したがって、例示された IC3 は、例えば、パッド 6 がローカル相互接続ネットワーク (LIN) インターフェースに電気的に接続される構成を含む様々な用途に適切であり得る。しかし、第一および第二の出力ドライバー回路 28、29 は、IC3 がコントローラーエリアネットワーク (CAN) インターフェースを用いた電子システムに採用された場合などでは、異なるパッドに電気的に接続され得る。例えば、第一の出力ドライバー回路 28 および第一の補助保護回路 30 は、第一のパッドに電気的に接40

続され得、第二の出力ドライバー回路 29 および第二の補助保護回路 31 は、第二のパッドに電気的に接続され得る。

#### 【 0 0 2 7 】

図 2 は、集積回路 40 の一部の例の注釈付き回路図である。集積回路 40 は、パッド 41、第一の NMOS トランジスタ 42、第二の NMOS トランジスタ 44、第一の PMOS トランジスタ 45、第三の NMOS トランジスタ 46、および第二の PMOS トランジスタ 47 を含む。回路 40 は、パッド 41 上に受け取られた一時的な信号イベント 14 と、第一のコンデンサー 43、第二のコンデンサー 48 および p - n 接合ダイオード 49 のような回路内にあり得る様々な寄生デバイスとを示すために注釈が付けられている。

#### 【 0 0 2 8 】

第一の NMOS トランジスタ 42 は、パッド 41 に電気的に接続されているドレイン、第一の供給電圧  $V_1$  に電気的に接続されているソース、および第二の NMOS トランジスタ 44 のドレインと第一の PMOS トランジスタ 45 のドレインとに電気的に接続されているゲートを含む。第二の NMOS トランジスタ 44 は、第一の供給電圧  $V_1$  に電気的に接続されているソース、および第一の PMOS トランジスタ 45 のゲートと第三の NMOS トランジスタ 46 のドレインと第二の PMOS トランジスタ 47 のドレインとに C O N T R O L\_B ヒラギンガラベルが付けられているノードにおいて電気的に接続されているゲートをさらに含む。第一の PMOS トランジスタ 45 は、第二の供給電圧  $V_2$  に電気的に接続されているソースをさらに含む。第三の NMOS トランジスタ 46 は、第一の供給電圧  $V_1$  に電気的に接続されているソース、および第二の PMOS トランジスタ 47 のゲートに電気的に接続されており、制御信号 C O N T R O L を受信するように構成されているゲートをさらに含む。第二の PMOS トランジスタ 47 は、第二の供給電圧  $V_2$  に電気的に接続されているソースをさらに含む。

#### 【 0 0 2 9 】

第一のコンデンサー 43、第二のコンデンサー 48、および p - n 接合ダイオード 49 は、例示された回路の寄生デバイスを表し得る。例えば、第一のコンデンサー 43 は、第一の NMOS トランジスタ 42 のドレインに電気的に接続されている第一の端および第一の NMOS トランジスタ 42 のゲートに電気的に接続されている第二の端を含み、第一の NMOS トランジスタ 42 のドレインの金属相互接続および / または拡散領域と第一の NMOS トランジスタ 42 のゲートの金属および / またはポリシリコン構造との間の寄生静電容量を表し得る。加えて、第二のコンデンサー 48 は、第一の電力供給電圧  $V_1$  に電気的に接続されている第一の端および第二の電力供給電圧  $V_2$  に電気的に接続されている第二の端を含み、第一の電力供給電圧  $V_1$  と第二の電力供給電圧  $V_2$  との間の寄生静電容量（例えば、電力供給相互接続および / または第一および第二の電力供給電圧  $V_1$ 、 $V_2$  に電気的に接続されている基板から生じるか、および / またはウェルの一部の間の寄生静電容量）を表し得る。p - n 接合ダイオード 49 は、第一の PMOS トランジスタ 45 のドレインと本体との間に形成された接合から生じる寄生ダイオード構成を表し得る。

#### 【 0 0 3 0 】

一時的な信号イベント 14 がパッド 41 上に受け取られ、パッド 41 の電圧を増加させた場合、電圧の変化は、第一のコンデンサー 43 に第一の NMOS トランジスタ 42 のゲート電圧を上方へ結合するようにさせる。十分な電圧変化の速度および持続時間に有している一時的な信号イベントの間、第一の NMOS トランジスタ 42 が伝導性となり、一時的な信号イベント 14 に関連する電荷を分路し、パッド 41 の電圧を減少させるソース - ドレイン電流を伝導するレベルまで第一の NMOS トランジスタ 41 のゲートは、増加され得る。したがって、第一の NMOS トランジスタ 42 は、パッド 41 の電圧を動作の安全な範囲内に維持し、破壊的な降伏を引き起こし得る第一の NMOS トランジスタ 42 のドレインとソースとの間の比較的大きい電圧のビルトアップを避けるために用いられ得る。

#### 【 0 0 3 1 】

しかし、回路 40 は、一時的な信号イベント中に、第一の NMOS トランジスタ 42 の

10

20

30

40

50

ゲートをプルダウンさせ得る寄生放電パスを含み得る。例えば、第一のN MOSトランジスタ42のゲート電圧が一時的な信号イベント中に上昇した場合は、第一のPMOSトランジスタ45のドレインの電圧は、第一のPMOSトランジスタ45の本体の電圧よりも上まで上昇し得、それによってp-n接合ダイオード49に順方向バイアスをかける。p-n接合ダイオード49が順方向バイアスをかけられた場合、電流I<sub>1</sub>は、p-n接合ダイオード49を通り第二の供給電圧V<sub>2</sub>上に流れることによって、第二のコンデンサー48を帯電させる。電流I<sub>1</sub>は、第一のN MOSトランジスタ42のゲートを放電させ得る。第一のN MOSトランジスタ42は、第一のN MOSトランジスタ42のゲート電圧およびチャネル伝導を減らせ得るか、および／またはN MOSトランジスタ42を一時的な信号イベント中にディセーブル（非伝導性になるように）させ得、したがって、低インピーダンス放電パスをV<sub>1</sub>に提供しない。

#### 【0032】

回路40は、第一のPMOSトランジスタ45の寄生p-n接合ダイオードを通るバスに加えて、追加の寄生放電パスを含み得る。例えば、一時的な信号イベント14がパッド41上において受け取られた場合、第二の電力供給V<sub>2</sub>の電圧は、容量結合を含む様々な理由によって上方へ結合され得るか、および／または上記で説明したI<sub>1</sub>に関連する放電バスのような放電バスを通して上方へ結合され得る。第二の供給電圧V<sub>2</sub>の増加は、第二のN MOSトランジスタ44にバイアスをかけるために用いられる電圧の増加につながり得る。例えば、制御信号CONTROLが低い状態にある場合は、CONTROL\_Bノードの電圧レベルは、第二の供給電圧V<sub>2</sub>の電圧によよそ等しくあり得る。したがって、第二の供給電圧V<sub>2</sub>の増加は、第二のN MOSトランジスタ44のチャネル伝導性の増加につながり得る。第二のN MOSトランジスタ44は、第一のN MOSトランジスタ42のゲートから第一の電力供給電圧V<sub>1</sub>まで第二のN MOSトランジスタ44を通って流れる電流I<sub>2</sub>を増加させ得る。加えて、制御信号CONTROLが最初に高い状態でバイアスをかけられる構成においてさえ、通常の条件を超える第二の供給電圧V<sub>2</sub>の増加は、集積回路（図2においては例示されていない）の制御ループを作動させ得る。集積回路の制御ループは、制御信号CONTROLの状態を始動条件に設定し得る。始動条件は、第二のN MOSトランジスタ44の作動に関連した状態であり得る。したがって、ある実装において、一時的な信号イベントは、第二の電力供給電圧V<sub>2</sub>に結合し得、供給電圧を増加させることによって、第二のN MOSトランジスタ44の作動と、第一のN MOSトランジスタ42のゲートの放電とにつながる。

#### 【0033】

ICのパッドに電気的に接続されているN MOSトランジスタのゲート上の寄生放電パスは、一時的な信号イベント中に作動しないか、または一時的な信号イベント中のある点において、作動停止するN MOSトランジスタにつながり得る。N MOSトランジスタを立ち上げることと、保護を提供するチャネルを形成することとを失敗することは、N MOSトランジスタおよび／またはパッドに電気的に接続されている他の回路および構成要素への損傷につながり得るので、改善されたMOS出力回路に対する必要性がある。さらに、プリドライバー回路によって提供されるゲート制御を維持しつつ、改善された信頼性を有している出力MOS回路アーキテクチャに対する必要性がある。

#### 【0034】

##### （MOSトランジスタ保護回路の概観）

MOS保護回路およびそれを形成する方法が提供される。ある実装において、保護回路は、パッドに電気的に接続されているMOSトランジスタと、MOSトランジスタのゲートを制御するように構成されている制御回路とを含む。制御回路は、MOSトランジスタのゲートが寄生漏れパスに起因して一時的な信号イベント中に放電することを妨げるように構成されている1つ以上のトランジスタを含む。寄生漏れパスを取り除くことは、一時的な信号イベント中のMOSトランジスタのゲート上に結合された電荷がイベントの持続時間中にMOSトランジスタのゲート上に存在したままであることを可能にし、それによって、トランジスタをエヌーブルし、一時的な信号保護を提供することに十分なレベルに

10

20

30

40

50

MOSトランジスタのゲートの電位を維持することを助ける。

#### 【0035】

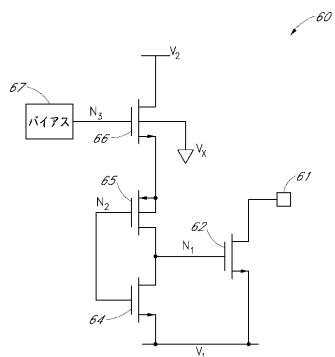

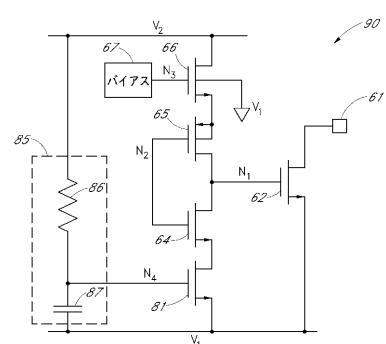

図3Aは、一実施形態に従うNMOS保護回路60の概略ブロック図である。NMOS保護回路60は、パッド61、第一のNMOSトランジスタ62、第二のNMOSトランジスタ64、PMOSトランジスタ65、第三のNMOSトランジスタ66およびバイアス回路67を含む。パッド61は、例えば、図1A～図1Bの第一のパッド4およびノまたは図1Cのパッド6を含む任意の適切なパッドであり得る。

#### 【0036】

第一のNMOSトランジスタ62は、パッド61に電気的に接続されているドレイン、第一の電力供給電圧 $V_1$ に電気的に接続されているソース、および第二のNMOSトランジスタ64のドレインとPMOSトランジスタ65のドレインとに $N_1$ とラベルが付けられているノードにおいて電気的に接続されているゲートを含む。第二のNMOSトランジスタ64は、第一の電力供給電圧 $V_1$ に電気的に接続されているソースおよびノード $N_2$ に電気的に接続されているゲートをさらに含む。PMOSトランジスタ65は、ノード $N_2$ に電気的に接続されているゲートおよび第三のNMOSトランジスタ66のソースに電気的に接続されているソースおよび本体をさらに含む。第三のNMOSトランジスタ66は、バイアス回路67の出力にノード $N_3$ において電気的に接続されているゲート、第二の電力供給電圧 $V_2$ に電気的に接続されているドレイン、および参照電圧 $V_x$ に電気的に接続されている本体をさらに含む。参照電圧 $V_x$ は、例えば、第一の電力供給電圧 $V_1$ を含む $V_2$ よりも低い任意の適切な電圧であり得る。

10

20

#### 【0037】

第一および第二の電力供給電圧 $V_1$ 、 $V_2$ は、任意の適切なノードであり得る。例えば、第一の電力供給電圧 $V_1$ は、一時的な信号イベントがパッド61上において受け取られた場合に、一時的な信号イベントに関連する電荷を分路するように構成されている低インピーダンス接地または電力供給ノードであり得る。第二の電力供給電圧 $V_2$ は、例えば、低インピーダンス電力供給ノードであり得る。しかし、ある実装において、第二の電力供給電圧 $V_2$ は、低インピーダンスである必要はない。なぜなら、第二の電力供給電圧 $V_2$ は、一時的な信号イベントに関連する電荷を分路するように構成される必要がないからである。

#### 【0038】

30

ノード $N_1$ は、第一のNMOSトランジスタ62のゲートを制御することによって、パッド61の電位を制御するために用いられ得る。ノード $N_1$ の電位を制御することを助けるために、ノード $N_1$ は、第一のNMOSトランジスタ62に対する制御回路として動作するように構成されている1つ以上のトランジスタまたは他のデバイスに電気的に接続され得る。例えば、図3Aにおいて例示されるように、第二のNMOSトランジスタ64およびPMOSトランジスタ65は、ノード $N_2$ 上において受信された信号を論理的に反転させるように構成されている。ノード $N_2$ は、図2において示されたノードCONTROL\_Bのような制御ノードであり得る。

#### 【0039】

第三のNMOSトランジスタ66は、PMOSトランジスタ65のソースおよび本体と、第二の電力供給電圧 $V_2$ との間に配置されている。一時的な信号イベントが存在しない回路の通常動作中に、バイアス回路67は、第三のNMOSトランジスタ66が低インピーダンスパスを第二の電力供給電圧 $V_2$ とPMOSトランジスタ65のソースとの間に提供するように、ブースト電圧をノード $N_3$ 上に提供するように構成され得る。したがって、第三のNMOSトランジスタ66を含むことは、回路の通常動作中に、第二のNMOSトランジスタ64とPMOSトランジスタ65との動作を妨害する必要はない。ある実装において、バイアス回路67は、電圧を第三のNMOSトランジスタ66のゲートに提供するように構成されており、この電圧は、第二の電力供給電圧 $V_2$ よりも約1.3～約1.8倍大きい。例えば、バイアス回路67は、電荷ポンプ回路を使用し得る。

40

#### 【0040】

50

バイアス回路 6 7 は、任意の適切な態様で実装され得る。例えば、バイアス回路は、予め規定された値の電流源、ならびにそれぞれ、N MOSトランジスタ 6 6 およびP MOSトランジスタ 6 5 に類似するダミーのN MOSトランジスタとダミーのP MOSトランジスタとの直列の組合わせを含み得る。電流源は、ダミーのN MOSトランジスタのドレインに電気的に接続され得る。電流がダミーのN MOS およびダミーのP MOSトランジスタを通過するのに十分なゲート電圧でダミーのN MOSトランジスタがバイアスをかけられるまで、バイアス回路 6 7 は、ダミーのN MOSトランジスタのゲート電圧を制御するよう構成され得る。しかし、バイアス回路 6 7 は、制御ループを含む必要はなく、他の方法によって実装され得る。例えば、適切な回路条件を有している構成において、バイアス回路 6 7 は、約  $V_2$  に等しい電圧をN MOSトランジスタ 6 6 のゲートに提供するように構成され得る。

#### 【 0 0 4 1 】

一実装において、バイアス回路 6 7 は、N MOSトランジスタ 6 6 の処理定格 (process - rated) ゲート電圧を超えてN MOSトランジスタ 6 6 のゲートにバイアスをかける。例えば、N MOSトランジスタ 6 6 は、オン状態であり得、ゲート酸化物にわたる電圧への本体 - ゲート電圧の影響を減少させ得る反転層を含み得る。したがって、N MOSトランジスタ 6 6 は、オフ状態にバイアスをかけられる類似のジオメトリおよびゲート酸化物の厚さのN MOSトランジスタのゲート電圧よりも大きいゲート電圧までバイアスをかけられ得る。ある実装において、バイアス回路 6 7 は、N MOSトランジスタ 6 6 のゲートに、処理定格ゲート電圧の約 1.5 倍までバイアスをかけ得る。例えば、バイアス回路 6 7 は、N MOSトランジスタ 6 6 のゲートに、N MOSトランジスタ 6 6 とおよそ同じゲート酸化物の厚さを有しているトランジスタに対して、最大定格ゲートソース電圧の約 1 倍 ~ 約 1.5 倍の電圧までバイアスをかけるように構成され得る。

#### 【 0 0 4 2 】

第三のN MOSトランジスタ 6 6 を含むことは、寄生漏れパスを減少させることを助け得る（そうでない場合は、一時的な信号イベント中に寄生漏れパスは、第一のN MOSトランジスタ 6 2 のゲートを放電させ得る）。例えば、P MOSトランジスタ 6 5 は、P MOSトランジスタ 6 5 のドレインと本体との間に配置された寄生 p - n 接合ダイオードを含み得る。一時的な信号イベント中に、第一のN MOSトランジスタ 6 2 のゲート - ドレイン静電容量は、ノード N<sub>1</sub> に上方へ結合し得ることによって、P MOSトランジスタ 6 5 のドレイン電圧をP MOSトランジスタ 6 5 の本体の電圧より上までブーストする。次に、これは、図 2 を参照して先に説明したように、順方向バイアスをかけられ、電流をドレインから本体まで提供する p - n 接合ダイオードにつながり得る。

#### 【 0 0 4 3 】

第三のN MOSトランジスタ 6 6 をP MOSトランジスタ 6 5 の本体と第二の電力供給電圧  $V_2$  との間に直列に配置することによって、第三のN MOSトランジスタ 6 6 は、P MOSトランジスタ 6 5 の本体から第二の電力供給電圧  $V_2$  までの電流の流れを遮断し得る。例えば、P MOSトランジスタ 6 5 の本体電圧が一時的な信号イベント中に上昇した場合、第三のN MOSトランジスタ 6 6 のソース電圧も上昇し得る。第三のN MOSトランジスタ 6 6 が高インピーダンスカットオフモードの動作に入るよう、第三のN MOSトランジスタ 6 6 のゲート - ソースが第三のN MOSトランジスタ 6 6 の閾値電圧の下まで下がる点まで、第三のN MOSトランジスタ 6 6 のソースは上昇し得る。したがって、第三のN MOSトランジスタ 6 6 は、一時的な信号イベント中に、パッド 6 1 上において受け取られた寄生放電パスを取り除くために用いられ得、それによって、第一のN MOSトランジスタ 6 2 によって提供された保護の堅牢性を、一時的な信号イベント中に、MOS伝導に対して十分大きい結合されたゲート電圧を維持することによって改善する。

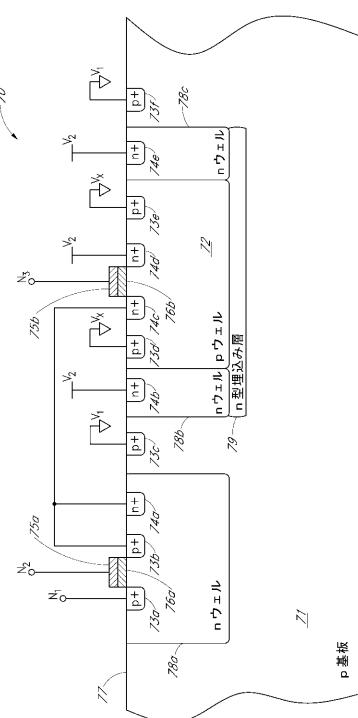

#### 【 0 0 4 4 】

図 3 B は、図 3 A のN MOS保護回路 6 0 の一部の一実装の断面図 7 0 である。例示された断面図 7 0 は、図 3 A のP MOSトランジスタ 6 5 と第三のN MOSトランジスタ 6 6 との一実装を例示する。断面図 7 0 は、p型基板 7 1 、n型作用範囲 7 4 a ~ 7 4 e 、

10

20

30

40

50

p型作用範囲73a～73f、nウェル78a～78c、pウェル72、n型埋込み層79、ゲート75a、75bおよびゲート酸化物76a、76bを含む。断面図は、ゲート75a、75bと、n型作用範囲74a～74eと、p型作用範囲73a～73fとの電気接続を例示するために注釈が付けられている。例えば、第一の電力供給電圧V<sub>1</sub>が参考電圧V<sub>x</sub>として用いられる実装を含むいくつかの実装において、n型埋込み層79は省略され得る。

#### 【0045】

図3Bにおいて例示されるように、pウェル72は、基板71の表面77上に配置される。nウェル78b、78cは、基板71の表面77上にpウェル72に隣接して、pウェル72の反対側に配置される。ある実装において、pウェル72を基板71の上から観察した場合に、nウェル78b、78cは、pウェル72を囲む輪の一部を形成する。例示された実装において、n型埋込み層79は、nウェル78b、78cおよびpウェル72の下に配置される。nウェル78aは、基板71の表面77上にnウェル78bに隣接して配置される。ゲート酸化物76aは、基板71の表面77を覆って、nウェル78aの上に配置され、ゲート75aは、ゲート酸化物76aを覆って配置される。p型作用範囲73a、73bは、nウェル78aの中に、ゲート75aの反対側に配置される。n型作用範囲74aは、nウェル78aの中に、p型作用範囲73bに隣接して配置される。p型作用範囲73cは、基板71の表面77上に、nウェル78bに隣接して配置され、p型作用範囲73fは、基板71の表面77上に、nウェル78cに隣接して配置される。

10

20

#### 【0046】

ゲート酸化物76bは、基板71の表面77を覆って、pウェル72の上に配置され、ゲート75bは、ゲート酸化物76bを覆って配置される。n型作用範囲74c、74dは、pウェル72の中に、ゲート75bの反対側に配置される。p型作用範囲73d、73eは、pウェル72の中に、それぞれ、n型作用領域74c、74dに隣接して配置される。n型作用領域74b、74eは、それぞれ、nウェル78b、78cの中に配置される。

#### 【0047】

p型作用範囲73aは、ノードN<sub>1</sub>に電気的に接続されている。ゲート75aは、ノードN<sub>2</sub>に電気的に接続されている。ゲート75bは、ノードN<sub>3</sub>に電気的に接続されている。p型作用範囲73c～73fは、第一の電力供給電圧V<sub>1</sub>に電気的に接続されている。n型作用範囲74b、74d、74eは、第二の電力供給電圧V<sub>2</sub>に電気的に接続されている。p型作用範囲73dは、n型作用範囲74a、74cに電気的に接続されている。

30

#### 【0048】

nウェル78a、78bおよびn型埋込み層79は、pウェル72をp型基板71から電気的に隔離することを助け得、それによって、p型基板71およびpウェル72が異なる電位において動作することを可能にする。例えば、n型埋込み層79を含むことは、pウェル72から形成されたNMOSデバイスの本体が異なる電位に電気的に接続されることを可能にする。本明細書において用いられる場合は、当業者によって理解されるよう、用語「n型埋込み層」は、例えば、シリコンオンインシュレーター(SOI)技術またはディープnウェル技術において用いられるものを含む任意の適切なn型埋込み層を指す。

40

#### 【0049】

例示された断面図70は、図3AのPMOSトランジスタ65と第三のNMOSトランジスタ66との一実装を例示する。例えば、ゲート75a、p型作用範囲73a、p型作用範囲73bおよびnウェル78aは、図3AのPMOSトランジスタ65のゲート、ドレイン、ソースおよび本体として動作し得る。ゲート75b、n型作用範囲74d、n型作用範囲74cおよびpウェル72は、図3Aの第三のNMOSトランジスタ66のゲート、ドレイン、ソースおよび本体として動作し得る。図3AのPMOSトランジスタ65

50

と第三のN M O Sトランジスタ6 6との一実装は、図3 Bにおいて示されるが、他の実装も可能である。加えて、ある詳細は、明確さのために図3 Bから省略されている。例えば、断面図7 0は、接点および金属被覆を形成するためにバックエンド処理を受け得る。接点および金属被覆は、例示された接続を形成するために用いられ得る。加えて、断面図7 0は、領域を分離、領域を隔離および／または異なる電気ノードに接続されている作用範囲間の静的な電流漏れを減少させるための浅いトレンチ領域、深いトレンチ領域またはシリコンの局所酸化（L O C O S）領域のような隔離領域を含み得る。隔離領域の形成は、基板7 1におけるトレンチを食刻することと、トレンチを二酸化ケイ素のような誘電体で満たすことと、化学機械平坦化のような任意の適切な方法を用いて過剰な誘電体を取り除くことを含み得る。

10

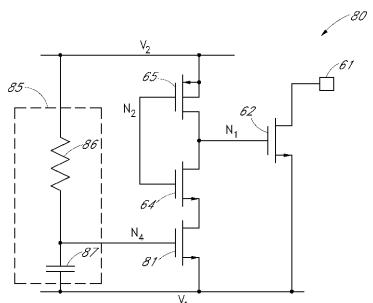

## 【0 0 5 0】

図4は、別の実施形態に従うN M O S保護回路8 0の概略ブロック図である。N M O S保護回路8 0は、パッド6 1、第一のN M O Sトランジスタ6 2、第二のN M O Sトランジスタ6 4、P M O Sトランジスタ6 5、第四のN M O Sトランジスタ8 1およびフィルタ回路8 5を含む。図3 Aの第三のN M O Sトランジスタ6 6およびバイアス回路6 7は、この実施形態には含まれていない。

## 【0 0 5 1】

第一のN M O Sトランジスタ6 2は、パッド6 1に電気的に接続されているドレイン、第一の電力供給電圧V<sub>1</sub>に電気的に接続されているソース、および第二のN M O Sトランジスタ6 4のドレインとP M O Sトランジスタ6 5のドレインとにN<sub>1</sub>とラベルを付けられているノードにおいて電気的に接続されているゲートを含む。第二のN M O Sトランジスタ6 4は、第四のN M O Sトランジスタ8 1のドレインに電気的に接続されているソースおよびノードN<sub>2</sub>に電気的に接続されているゲートをさらに含む。第四のN M O Sトランジスタ8 1は、第一の電力供給電圧V<sub>1</sub>に電気的に接続されているソースおよびフィルタ回路8 5の出力にノードN<sub>4</sub>において電気的に接続されているゲートをさらに含む。P M O Sトランジスタ6 5は、ノードN<sub>2</sub>に電気的に接続されているゲート、ならびに第二の電力供給電圧V<sub>2</sub>に電気的に接続されているソースおよび本体をさらに含む。第一および第二のノードN<sub>1</sub>、N<sub>2</sub>と第一および第二の電力供給電圧V<sub>1</sub>、V<sub>2</sub>との追加の詳細は、図3 Aを参照して、上記で説明した通りであり得る。

20

## 【0 0 5 2】

例示されたフィルタ回路8 5は、抵抗器8 6およびコンデンサー8 7を含む。抵抗器8 6は、第二の電力供給電圧V<sub>2</sub>に電気的に接続されている第一の端、およびコンデンサー8 7の第一の端と第四のN M O Sトランジスタ8 1のゲートとにノードN<sub>4</sub>において電気的に接続されている第二の端を含む。コンデンサー8 7は、第一の電力供給電圧V<sub>1</sub>に電気的に接続されている第二の端をさらに含む。例示されたフィルタ回路8 5は、第二の電力供給電圧V<sub>2</sub>をフィルタリングし得、フィルタリングされた供給電圧をノードN<sub>4</sub>上に生成する。フィルタ回路8 5の一特定の実装が図5において例示されるが、フィルタ回路8 5は、例えば、任意の適切な低域通過フィルタを含む任意の適切なフィルタであり得る。

30

## 【0 0 5 3】

第四のN M O Sトランジスタ8 1は、第二のN M O Sトランジスタ6 4のソースと第一の電力供給電圧V<sub>1</sub>との間に配置されている。回路の通常動作中に、一時的な信号イベントが不在の場合は、フィルタ回路8 5は、第二の電力供給電圧V<sub>2</sub>によよそ等しい電圧をノードN<sub>4</sub>に提供し得る。したがって、通常動作中は、第四のN M O Sトランジスタ8 1はイネーブルされ得、通常動作中のインバーターとしての第二のN M O Sトランジスタ6 4とP M O Sトランジスタ6 5との動作を妨害する必要はない。ある実装において、抵抗器は、約1 5 0 k ~ 約3 0 0 k の範囲の抵抗（例えば、約2 5 0 k ）を有しており、コンデンサーは、約1 . 5 p F ~ 約2 . 5 p F（例えば、約2 . 0 p F）の範囲の静電容量を有している。

40

## 【0 0 5 4】

50

第四のN MOSトランジスタ81およびフィルタ回路85を含むことは、寄生漏れバスを減少させることを助け得る（そうでない場合は、一時的な信号イベント中に寄生漏れバスは、第一のN MOSトランジスタ62のゲートを放電させ得る）。例えば、一時的な信号イベントがパッド61において受け取られた場合は、第二の電力供給V<sub>2</sub>の電圧は、先に説明したように、上方へ結合され得る。第二の供給電圧V<sub>2</sub>の増加は、第二のN MOSトランジスタ64にバイアスをかけるために用いられる電圧の増加につながり得る。なぜなら、ノードN-2は、第二の供給電圧V<sub>2</sub>の出力によそ等しい出力を有している制御回路によって制御され得るからである。加えて、ある実装において、第二の供給電圧V<sub>2</sub>の増加は、ノードN<sub>2</sub>の状態を始動条件に設定し得る始動中に用いられる集積回路の制御ループを作動させ得る。始動条件は、第二のN MOSトランジスタ64の作動に関連した状態であり得る。したがって、ある実装において、一時的な信号イベントは、第二の電力供給電圧V<sub>2</sub>に結合し得、供給電圧を増加させ得、それによって、一時的な信号イベント中に、第二のN MOSトランジスタ64の作動と、第一のN MOSトランジスタ62のゲートの放電とにつながる。

#### 【0055】

第四のN MOSトランジスタ81を第二のN MOSトランジスタ64のソースと、第四のN MOSトランジスタ81のゲートがフィルタ回路85の出力に接続されている第一の電力供給電圧V<sub>1</sub>との間に直列に配置することによって、ノードN<sub>4</sub>の電位は、一時的な信号イベント中に比較的低いままであり得、それによって、第四のトランジスタ81のゲート電圧を一時的な信号イベントの持続時間の間、比較的低いレベルに維持する。第二および第四のN MOSトランジスタ64、81は、第四のN MOSトランジスタ81に直列に電気的に接続されているので、第四のN MOSトランジスタ81のゲートに提供された電圧をフィルタリングすることは、一時的な信号イベントがノードN<sub>2</sub>の電圧および／または第二の電力供給電圧V<sub>2</sub>を増加させたとしても、一時的な信号イベント中に第一のN MOSトランジスタ62のゲートからの電流の放電を制限し得る。したがって、第四のN MOSトランジスタ81は、パッド61において受け取られた一時的な信号イベント中に、寄生放電バスを取り除くために用いられ得、それによって、第一のN MOSトランジスタ62によって提供された保護のロバスト性を改善する。

#### 【0056】

図5は、さらに別の実施形態に従うN MOS保護回路90の概略ブロック図である。N MOS保護回路90は、パッド61、第一のN MOSトランジスタ62、第二のN MOSトランジスタ64、第三のN MOSトランジスタ66、第四のN MOSトランジスタ81、PMOSトランジスタ65、バイアス回路67、およびフィルタ回路85を含む。

#### 【0057】

第一のN MOSトランジスタ62は、パッド61に電気的に接続されているドレイン、第一の電力供給電圧V<sub>1</sub>に電気的に接続されているソース、および第二のN MOSトランジスタ64のドレインとPMOSトランジスタ65のドレインとにN<sub>1</sub>とラベルを付けられているノードにおいて電気的に接続されているゲートを含む。第二のN MOSトランジスタ64は、第四のN MOSトランジスタ81のドレインに電気的に接続されているソースおよびノードN<sub>2</sub>に電気的に接続されているゲートをさらに含む。第四のN MOSトランジスタ81は、第一の電力供給電圧V<sub>1</sub>に電気的に接続されているソース、および抵抗器86の第一の端とコンデンサー87の第一の端とにノードN<sub>4</sub>において電気的に接続されているゲートをさらに含む。コンデンサー87は、第一の電力供給電圧V<sub>1</sub>に電気的に接続されている第二の端をさらに含む。抵抗器86は、第二の電力供給電圧V<sub>2</sub>に電気的に接続されている第二の端をさらに含む。PMOSトランジスタ65は、ノードN<sub>2</sub>に電気的に接続されているゲート、ならびに第三のN MOSトランジスタ66のソースに電気的に接続されているソースおよび本体をさらに含む。第三のN MOSトランジスタ66は、バイアス回路67の出力にノードN<sub>3</sub>において電気的に接続されているゲート、第二の電力供給電圧V<sub>2</sub>に電気的に接続されているドレイン、および第一の電力供給電圧V<sub>1</sub>に電気的に接続されている本体をさらに含む。

10

20

30

40

50

## 【0058】

例示されたN MOS保護回路90は、寄生漏れパスを減少させるか、または取り除くように構成されている（そうでない場合は、一時的な信号イベント中に寄生漏れパスは、第一のN MOSトランジスタ62のゲートを放電させ得る）。例えば、例示されたN MOS保護回路90は、第三のN MOSトランジスタ66およびバイアス回路67を含む。第三のN MOSトランジスタ66およびバイアス回路67は、第一のN MOSトランジスタ62のゲートから第二の電力供給電圧V<sub>2</sub>までPMOSトランジスタ65の本体を通る寄生漏れパスを減少させるために用いられ得る。加えて、例示されたN MOS保護回路90は、第四のN MOSトランジスタ81およびフィルタ回路85を含む。第四のN MOSトランジスタ81およびフィルタ回路85は、第一のN MOSトランジスタ62のゲートから第一の電力供給電圧V<sub>1</sub>まで第二のN MOSトランジスタ64を通る寄生漏れパス減少させるために用いられ得る。N MOS保護回路90の追加の詳細は、上の図3A～図4について、上記で説明したものに類似し得る。図5は、第三のN MOSトランジスタ66の本体が第一の電力供給電圧V<sub>1</sub>に電気的に接続されている構成に対して例示されるが、第三のN MOSトランジスタ66の本体は、先に説明したように、他のノードにも電気的に接続され得る。

## 【0059】

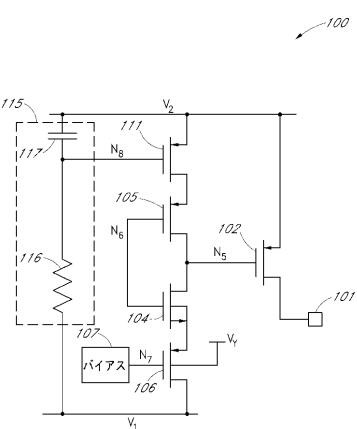

図3A～図5は、パッドに電気的に接続されているN MOSトランジスタの観点から漏れ減少スキームを説明しているが、漏れ減少スキームは、PMOSトランジスタ構成および、図1Cにおいて示された構成のような、共通の出力パッドに接続されている出力ドライバーネットとPMOSとの組合せにも適用され得る。

## 【0060】

図6は、一実施形態に従うp型金属酸化物半導体(PMOS)保護回路100の概略ブロック図である。PMOS保護回路100は、パッド101、第一のPMOSトランジスタ102、第二のPMOSトランジスタ105、第三のPMOSトランジスタ106、第四のPMOSトランジスタ111、N MOSトランジスタ104、バイアス回路107、およびフィルタ回路115を含む。フィルタ回路115は、抵抗器116およびコンデンサー117を含む。

## 【0061】

第一のPMOSトランジスタ102は、パッド101に電気的に接続されているドレイン、第二の電力供給電圧V<sub>2</sub>に電気的に接続されているソース、および第二のPMOSトランジスタ105のドレインとN MOSトランジスタ104のドレインとにN<sub>5</sub>とラベルを付けられているノードにおいて電気的に接続されているゲートを含む。第二のPMOSトランジスタ105は、第四のPMOSトランジスタ111のドレインに電気的に接続されているソースおよびノードN<sub>6</sub>に電気的に接続されているゲートをさらに含む。第四のPMOSトランジスタ111は、第二の電力供給電圧V<sub>2</sub>に電気的に接続されているソース、および抵抗器116の第一の端とコンデンサー117の第一の端とにノードN<sub>8</sub>において電気的に接続されているゲートをさらに含む。コンデンサー117は、第二の電力供給電圧V<sub>2</sub>に電気的に接続されている第二の端をさらに含み、抵抗器116は、第一の電力供給電圧V<sub>1</sub>に電気的に接続されている第二の端をさらに含む。N MOSトランジスタ104は、ノードN<sub>6</sub>に電気的に接続されているゲート、ならびに第三のPMOSトランジスタ106のソースに電気的に接続されているソースおよび本体をさらに含む。第三のPMOSトランジスタ106は、バイアス回路107の出力にノードN<sub>7</sub>において電気的に接続されているゲート、第一の電力供給電圧V<sub>1</sub>に電気的に接続されているドレイン、および参照電圧V<sub>Y</sub>に電気的に接続されている本体をさらに含む。参照電圧V<sub>Y</sub>は、例えば、第二の電力供給電圧V<sub>2</sub>を含むV<sub>1</sub>よりも大きい任意の適切な電圧であり得る。

## 【0062】

例示されたPMOS保護回路100は、寄生漏れパスを減少させるか、または取り除くように構成されている（そうでない場合は、一時的な信号イベント中に寄生漏れパスは、第一のPMOSトランジスタ102のゲートを帯電させ得る）。例えば、例示されたP

MOS保護回路100は、第三のPMOSトランジスタ106およびバイアス回路107を含む。第三のPMOSトランジスタ106およびバイアス回路107は、第一のPMOSトランジスタ102のゲートから第一の電力供給電圧V<sub>1</sub>までNMOSトランジスタ104の本体を通る寄生漏れバスを減少させるために用いられ得る。加えて、例示されたPMOS保護回路100は、第四のPMOSトランジスタ111およびフィルタ回路115を含む。第四のPMOSトランジスタ111およびフィルタ回路115は、第一のPMOSトランジスタ102のゲートから第二の電力供給電圧V<sub>2</sub>まで第二のPMOSトランジスタ105を通る寄生漏れバスを減少させるために用いられ得る。PMOS保護回路100の追加の詳細は、上の図3A～図4に関して、上記で説明したものに類似し得る。

## 【0063】

10

ある実装において、PMOS保護回路およびNMOS保護回路は、IC上に含まれ得る。例えば、図1A～図1Cにおいて示される構成において、ICは、PMOS出力ドライバーとNMOS出力ドライバーとの両方を含み得、これらの出力ドライバーは、それぞれ、本明細書において説明される保護スキームを組み込み得る。PMOS保護回路とNMOS保護回路との両方を提供することは、ICの供給電圧を一時的な信号イベントから保護することを助け得る。例えば、一時的な信号イベントが供給電圧V<sub>2</sub>を増加させ、供給電圧V<sub>1</sub>を減らす場合、PMOSとNMOSとの両方が作動させられ得、低インピーダンス放電バスは、第一の供給電圧V<sub>1</sub>と第二の供給電圧V<sub>2</sub>との間に提供され得る。

## 【0064】

20

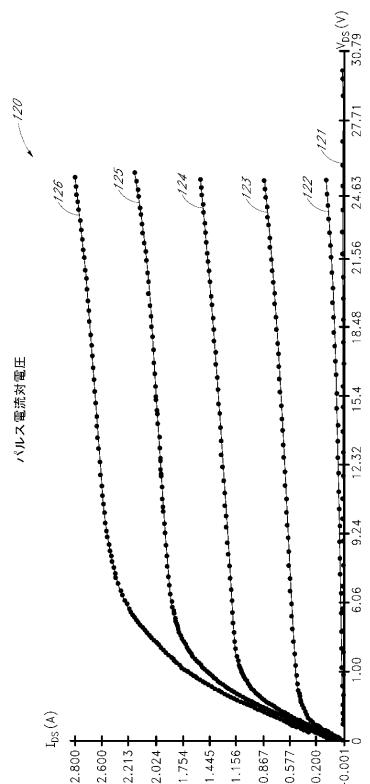

図7Aは、NMOSトランジスタに対するドレイン-ソース電流対ドレイン-ソース電圧の一例のグラフ120である。グラフ120は、約2nsの立ち上がり時間および約100nsのパルス幅を有している伝送ラインパルス(TLP)測定値を例示する。NMOSトランジスタは、異なるゲート電圧結合条件に対して特性付けられ、約10,000μmの幅を有している。NMOSトランジスタは、約20Vまでの電圧において動作するよう構成されており、2kVの人体モデル(HBM)ESDイベントのようなある一時的な信号イベントに耐え得る。例示されたプロット121～126は、それぞれ、約0V、約1V、約2V、約3V、約4Vおよび約5Vのゲート-ソース結合電圧に対するドレイン-ソース電流を例示する。図7Aは、NMOSトランジスタが約20Vまでの電圧において動作するように構成されている構成を例示するが、NMOSトランジスタは、例えば、約200Vまでの電圧を含む任意の適切な電圧において動作するように構成され得る。加えて、NMOSトランジスタは、例えば、8kVのHBMよりも大きいESDイベントを含む、より大きさが大きい一時的な信号イベントに耐えるように構成され得る。プロット121は、非常に低い電流を維持しつつ、非常に低いゲート電圧に対して、デバイスが降伏の条件に到達することを示す。加えて、デバイスがより大きいゲート電圧を受け取るプロット122～126に対しては、デバイスは、ある一時的な信号イベントに対する保護を提供することに適切な比較的多い電流量を伝導する能力を有しており、それによって、デバイスが自己保護することを可能にする。

30

## 【0065】

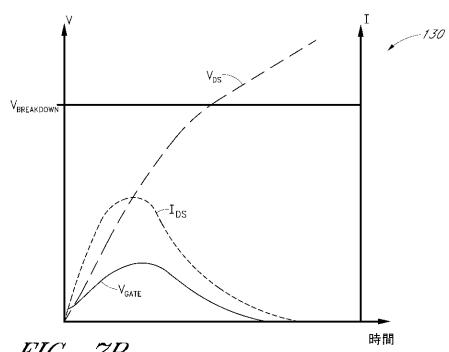

図7Bは、ドレイン-ソース電流、ドレイン-ソース電圧、およびゲート電圧対時間の一例のグラフ130である。グラフ130は、時間0で始まる一時的な信号イベント中のNMOSトランジスタの動作を例示する。図7Bにおいて例示されるように、一時的な信号イベントは、継続的にトランジスタのドレイン-ソース電圧V<sub>DS</sub>を増加させ得る。ドレイン-ソース電圧V<sub>DS</sub>の増加は、上方へ結合されているゲートV<sub>GATE</sub>の電圧に至り得る。ゲートV<sub>GATE</sub>の電圧は、ドレイン-ソースチャネル電流I<sub>DS</sub>を増加させ得る。しかし、先に説明したように、NMOSトランジスタのゲート上の寄生漏れバスは、一時的な信号イベント中にゲート電圧を減少させ得る。ゲート電圧を減少させることは、ドレイン-ソースチャネル電流I<sub>DS</sub>を減らし得、ドレイン-ソース電圧V<sub>DS</sub>の、デバイス損傷に関連する降伏電圧V<sub>BREAKDOWN</sub>を超えた増加につながり得る。

40

## 【0066】

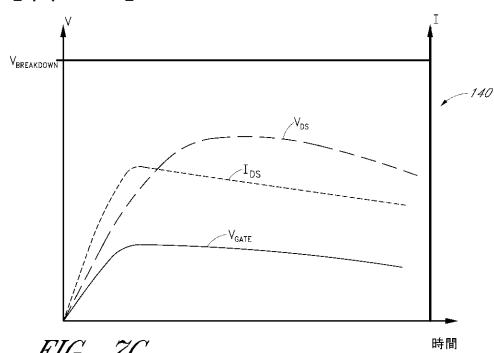

図7Cは、ドレイン-ソース電流、ドレイン-ソース電圧、およびゲート電圧対時間の

50

別の例のグラフ 140 である。グラフ 140 は、時間 0 で始まる一時的な信号イベント中の N MOS トランジスタの動作を例示する。図 7C において示されるように、一時的な信号イベントは、継続的にトランジスタのドレイン - ソース電圧  $V_{DS}$  を増加させ得る。ドレイン - ソース電圧  $V_{DS}$  の増加は、上方へ結合されているゲート  $V_{GATE}$  の電圧に至り得、ドレイン - ソースチャネル電流  $I_{DS}$  を増加させ得る。図 7C において例示される構成において、一時的な信号イベント中の N MOS トランジスタのゲートからの寄生漏れパスは、図 7B において示されたものに対して減少されている。したがって、N MOS トランジスタのゲートの電圧  $V_{GATE}$  は、図 7B において示されたゲート電圧に対して、継続的に、より遅い速度で減る。したがって、ドレイン - ソースチャネル電流  $I_{DS}$  は、継続的に比較的高いままであり得、ドレイン - ソース電圧  $V_{DS}$  が減り、デバイス損傷に 10 関連する電圧  $V_{BREAKDOWN}$  に到達しないことにつながり得る。

#### 【0067】

前述の説明および特許請求の範囲は、一緒に「接続」または「結合」されている素子または機能を指し得る。本明細書において用いられる場合は、そうではないと明確に述べられない限り、「接続されている」は、1つの素子 / 機能が、別の素子 / 機能に直接的または間接的に接続されていることを意味しており、必ずしも機械的に接続されているわけではない。同じように、そうではないと明確に述べられない限り、「結合されている」は、1つの素子 / 機能が、別の素子 / 機能に直接的または間接的に結合されていることを意味しており、必ずしも機械的に結合されているわけではない。したがって、図において示された様々な概略図は、素子および構成要素の例示的配列を描写するが、追加の仲介素子、デバイス、機能、または構成要素が実際の実施形態（描写された回路の機能性は、不都合に影響されないと想定する）に存在し得る。 20

#### 【0068】

##### （用途）

上記のスキームを採用するデバイスは、様々な電子システムに実装され得る。電子デバイスの例は、大衆消費電子製品、大衆消費電子製品のparts、電子試験装置などを含み得るが、それらに限定されない。電子デバイスの例は、メモリチップ、メモリモジュール、光学ネットワークまたは他の通信ネットワークの回路、およびディスクドライバー回路も含み得る。大衆消費電子製品は、モバイル電話、電話、テレビ、コンピュータモニター、コンピュータ、ハンドヘルドコンピュータ、携帯情報端末（PDA）、電子レンジ、冷蔵庫、自動車、ステレオシステム、カセットレコーダーまたはプレーヤー、DVDプレーヤー、CDプレーヤー、VCR、MP3プレーヤー、ラジオ、カムコーダー、カメラ、デジタルカメラ、ポータブルメモリチップ、洗濯機、乾燥機、洗濯乾燥機、複写機、ファクシミリ装置、スキャナー、多機能周辺装置、腕時計、時計などを含み得るが、それらに限定されない。さらに、電子デバイスは、未完成の製品を含み得る。 30

#### 【0069】

本発明は、ある実施形態の観点から説明されたが、本明細書に記載された機能および利点の全ては提供しない実施形態を含む、当業者に明らかな他の実施形態も本発明の範囲内である。さらに、上で説明された様々な実施形態は、さらなる実施形態を提供するために組合せられ得る。加えて、一実施形態との関連で示されたある機能は、他の実施形態にも組み込まれ得る。そのため、本発明の範囲は、添付の特許請求の範囲への参照のみによつて規定される。 40

【図1A】

FIG. IA

【 図 1 B 】

FIG. 1B

【図1C】

FIG. 1C

【図2】

FIG. 2

【図3A】

FIG. 3A

【図3B】

FIG. 3B

【図4】

FIG. 4

【図6】

FIG. 6

【図5】

FIG. 5

【図 7 A】

FIG. 7A

【図 7 B】

FIG. 7B

【図 7 C】

FIG. 7C

---

フロントページの続き

(72)発明者 ハビエル アー . サルセド

アメリカ合衆国 マサチューセッツ 01862 , ノース ビレリカ , レンジウェイ ロード

216 ナンバー 134

審査官 宇多川 勉

(56)参考文献 特開平06-216735(JP,A)

実開平02-004318(JP,U)

特開平06-085648(JP,A)

特開平02-137269(JP,A)

特開平05-326853(JP,A)

特開2003-133938(JP,A)

特開2009-081307(JP,A)

特開2006-165947(JP,A)

特開2007-214158(JP,A)

特開2001-014853(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/822

H01L 27/04

H01L 27/06

H03K 19/003