## (12) 发明专利

(10) 授权公告号 CN 107112952 B

(45) 授权公告日 2021.07.23

(21) 申请号 201580058036.8

(22) 申请日 2015.11.02

(65) 同一申请的已公布的文献号

申请公布号 CN 107112952 A

(43) 申请公布日 2017.08.29

(30) 优先权数据

14/533,988 2014.11.05 US

(85) PCT国际申请进入国家阶段日

2017.04.25

(86) PCT国际申请的申请数据

PCT/US2015/058663 2015.11.02

(87) PCT国际申请的公布数据

W02016/073371 EN 2016.05.12

(73) 专利权人 高通股份有限公司

地址 美国加利福尼亚州

(72) 发明人 许俊海 P·J·德拉克斯勒

(51) Int.CI.

H03F 1/02 (2006.01)

H03H 7/48 (2006.01)

H01Q 1/50 (2006.01)

H03F 1/56 (2006.01)

H03F 3/24 (2006.01)

H03F 3/68 (2006.01)

H01P 5/16 (2006.01)

H03H 11/36 (2006.01)

(56) 对比文件

CN 202721250 U, 2013.02.06

CN 103490131 A, 2014.01.01

US 2006/0055458 A1, 2006.03.16

WO 2008/111172 A1, 2008.09.18

JP 特开2008-125044 A, 2008.05.29

JP 平1-202007 A, 1989.08.15

CN 1750388 A, 2006.03.22

审查员 鲍威尔

(74) 专利代理机构 北京市金杜律师事务所

11256

代理人 王茂华 张曦

权利要求书3页 说明书6页 附图5页

(54) 发明名称

动态功分器电路及方法

(57) 摘要

本公开包括动态功分器电路及方法。在一个实施例中，动态功分器包括第一和第二四分之一波长线，它们接收输入信号并且在线路的第二端子上产生第一和第二信号。输入信号的动态功率划分使用第一四分之一波长线的第二端子与第二四分之一波长线的第二端子之间的可变阻抗电路。可变阻抗可以随着输入信号功率增大而减小两个输出路径之间的阻抗，或者随着输入信号功率减小而增大输出路径之间的阻抗。

**100**

B

1.一种功分器电路,包括:

第一四分之一波长线,具有第一端子和第二端子,其中所述第一四分之一波长线的所述第一端子接收输入信号;

第二四分之一波长线,具有第一端子和第二端子,其中所述第二四分之一波长线的所述第一端子接收所述输入信号;

可变阻抗电路,耦合在所述第一四分之一波长线的所述第二端子与所述第二四分之一波长线的所述第二端子之间,所述可变阻抗电路具有控制输入以调节所述可变阻抗电路的阻抗;以及

功率控制电路,被配置为接收表示所述输入信号的功率特性的第一信号,并且所述功率控制电路的输出耦合至所述可变阻抗电路的所述控制输入以响应于所述第一信号来调节所述可变阻抗电路的阻抗,

其中所述可变阻抗电路的阻抗在所述输入信号的功率增大时被减小以增大所述第二四分之一波长线的所述第二端子处的功率,并且所述可变阻抗电路的阻抗在所述输入信号的功率减小时被增大以减小所述第二四分之一波长线的所述第二端子处的功率,

其中所述可变阻抗电路包括可编程的电阻器网络和至少一个半导体器件,

其中所述功率控制电路包括:

包络检测器,其中所述功率控制电路的所述输出包括第一输出,所述第一输出耦合至所述至少一个半导体器件以用于按所述输入信号的包络的速率来改变所述阻抗;以及

平均功率发生器,其中所述功率控制电路的所述输出进一步包括第二输出,所述第二输出耦合至所述可编程的电阻器网络以根据所述输入信号的平均功率来改变经编程的电阻。

2.根据权利要求1所述的功分器电路,其中所述第一四分之一波长线的所述第二端子耦合至第一功率放大器级,并且所述第二四分之一波长线的所述第二端子耦合至第二功率放大器级,并且其中所述第一功率放大器级和所述第二功率放大器级驱动天线。

3.根据权利要求2所述的功分器电路,其中所述第一功率放大器级和所述第二功率放大器级包括Doherty功率放大器。

4.根据权利要求1所述的功分器电路,进一步包括可调节LC电路,其中在第一配置中所述可调节LC电路在所述第二四分之一波长线的所述第二端子处产生第一阻抗并且在所述第二四分之一波长线的所述第一端子处产生对应的第二阻抗,其中所述第一阻抗小于所述第二阻抗,并且其中在第二配置中所述可调节LC电路在所述第二四分之一波长线的所述第二端子处产生第三阻抗并且在所述第二四分之一波长线的所述第一端子处产生对应的第四阻抗,其中所述第三阻抗大于所述第四阻抗。

5.根据权利要求4所述的功分器电路,其中所述可调节LC电路被配置为在所述输入信号的功率减小时产生所述第一阻抗,以减小从所述第二四分之一波长线的所述第一端子被传送至所述第二四分之一波长线的所述第二端子的所述输入信号的功率,并且其中所述可调节LC电路被配置为在所述输入信号的功率增大时产生所述第三阻抗,以增大从所述第二四分之一波长线的所述第一端子被传送至所述第二四分之一波长线的所述第二端子的所述输入信号的功率。

6.根据权利要求1所述的功分器电路,其中所述半导体器件包括PIN二极管,并且其中

所述控制输入调节通过所述PIN二极管的电流。

7. 根据权利要求1所述的功分器电路,其中所述半导体器件包括晶体管,所述晶体管具有:第一端子,其耦合到所述第一四分之一波长线的所述第二端子;第二端子,其耦合到所述第二四分之一波长线的所述第二端子;以及控制端子,其包括所述控制输入。

8. 根据权利要求1所述的功分器电路,其中所述第一四分之一波长线包括至少一个电感器,并且所述第二四分之一波长线包括至少一个电感器。

9. 根据权利要求1所述的功分器电路,其中由所述功率控制电路接收的所述第一信号是来自调制解调器的功率控制信号。

10. 一种划分输入信号功率的方法,包括:

在第一四分之一波长线的第一端子上接收输入信号以在所述第一四分之一波长线的第二端子上产生第二信号,所述第二信号具有所述输入信号的功率的第一部分;

在第二四分之一波长线的第一端子上接收所述输入信号以在所述第二四分之一波长线的第二端子上产生第三信号,所述第三信号具有所述输入信号的功率的第二部分;以及

响应于表示所述输入信号的功率特性的第一信号,调节耦合在所述第一四分之一波长线的所述第二端子与所述第二四分之一波长线的所述第二端子之间的可变阻抗电路的阻抗,

其中所述可变阻抗电路的阻抗在所述输入信号的功率增大时被减小,以增大所述第二四分之一波长线的所述第二端子处的所述第三信号的功率,并且所述可变阻抗电路的阻抗在所述输入信号的功率减小时被增大,以减小所述第二四分之一波长线的所述第二端子处的所述第三信号的功率,

其中所述可变阻抗电路包括可编程的电阻器网络和至少一个半导体器件,

其中通过以下方式调节所述可变阻抗电路的阻抗:

检测所述输入信号的包络并控制所述至少一个半导体器件以用于按所述输入信号的包络的速率来改变所述阻抗;以及

确定所述输入信号的平均功率并根据所述输入信号的平均功率来改变所述可编程的电阻器网络的经编程的电阻。

11. 根据权利要求10所述的方法,进一步包括:使用可调节LC电路来调节所述第二四分之一波长线的所述第二端子处的阻抗,其中在第一配置中所述可调节LC电路在所述第二四分之一波长线的所述第二端子处产生第一阻抗并且在所述第二四分之一波长线的所述第一端子处产生对应的第二阻抗,其中所述第一阻抗小于所述第二阻抗,并且其中在第二配置中所述可调节LC电路在所述第二四分之一波长线的所述第二端子处产生第三阻抗并且在所述第二四分之一波长线的所述第一端子处产生对应的第四阻抗,其中所述第三阻抗大于所述第四阻抗。

12. 一种功分器电路,包括:

用于在第一四分之一波长线的第一端子上接收输入信号以在所述第一四分之一波长线的第二端子上产生第二信号的装置,所述第二信号具有所述输入信号的功率的第一部分;

用于在第二四分之一波长线的第一端子上接收所述输入信号以在所述第二四分之一波长线的第二端子上产生第三信号的装置,所述第三信号具有所述输入信号的功率的第二

部分;以及

用于响应于表示所述输入信号的功率特性的第一信号来调节耦合在所述第一四分之一波长线的所述第二端子与所述第二四分之一波长线的所述第二端子之间的可变阻抗电路的阻抗的装置，

其中所述可变阻抗电路的阻抗在所述输入信号的功率增大时被减小,以增大所述第二四分之一波长线的所述第二端子处的所述第三信号的功率,并且所述可变阻抗电路的阻抗在所述输入信号的功率减小时被增大,以减小所述第二四分之一波长线的所述第二端子处的所述第三信号的功率,

其中所述可变阻抗电路包括可编程的电阻器网络和至少一个半导体器件，

其中用于调节所述可变阻抗电路的阻抗的装置包括:

包络检测器,其中用于调节所述可变阻抗电路的阻抗的装置的第一输出耦合至所述至少一个半导体器件以用于按所述输入信号的包络的速率来改变所述阻抗;以及

平均功率发生器,其中用于调节所述可变阻抗电路的阻抗的装置的第二输出耦合至所述可编程的电阻器网络以根据所述输入信号的平均功率来改变经编程的电阻。

13. 根据权利要求12所述的功分器电路,进一步包括:用于使用可调节LC电路来调节所述第二四分之一波长线的所述第二端子处的阻抗的装置,其中在第一配置中所述可调节LC电路在所述第二四分之一波长线的所述第二端子处产生第一阻抗并且在所述第二四分之一波长线的所述第一端子处产生对应的第二阻抗,其中所述第一阻抗小于所述第二阻抗,并且其中在第二配置中所述可调节LC电路在所述第二四分之一波长线的所述第二端子处产生第三阻抗并且在所述第二四分之一波长线的所述第一端子处产生对应的第四阻抗,其中所述第三阻抗大于所述第四阻抗。

## 动态功分器电路及方法

[0001] 相关申请的交叉引用

[0002] 本申请要求2014年11月5日提交的美国专利申请号14/533,988的优先权，其内容以它的整体通过引用并入本文用于所有目的。

### 技术领域

[0003] 本公开涉及电子电路及方法，并且特别地，涉及动态功分器电路及方法。

### 背景技术

[0004] 电子电路中的功耗是正得到增加关注的主题。随着电子电路的使用变得无所不在，由这些设备消耗的功率逐步上升，而对基础设施和环境提出了增加的需求。例如，无线设备是当代对能量和功率的增长的需求及消耗的“罪魁祸首”。RF收发器内部的电路系统经常消耗大量的功率以发射、接收和处理RF通信信号。

[0005] 经常低效且功率渴求的一个示例电路组件是功率放大器。在无线应用中，功率放大器接收无线通信信号并且增大信号的功率以用于在天线上的发射。处理用于在天线上的发射的信号可以包括沿着多个信号路径来划分信号、放大信号以增大电压和/或电流、以及对信号进行组合以用于在天线上的发射。在信号沿着多个路径被耦合的情况下，信号功率也典型地在这些路径之间被划分。随着对操作条件进行改变，有时的情况是特定路径在一些操作条件期间可能较不活动或完全不活动，并且提供给这种路径的信号功率被浪费。

### 发明内容

[0006] 本公开包括动态功分器电路及方法。在一个实施例中，动态功分器包括第一和第二四分之一波长线，它们接收输入信号并且在线路的第二端子上产生第一和第二信号。输入信号的动态功率划分使用第一四分之一波长线的第二端子与第二四分之一波长线的第二端子之间的可变阻抗电路。可变阻抗可以随着输入信号功率增大而减小两个输出路径之间的阻抗、或者随着输入信号功率减小而增大输出路径之间的阻抗。

[0007] 以下详细描述及附图提供对本公开的性质和优点的更好的理解。

### 附图说明

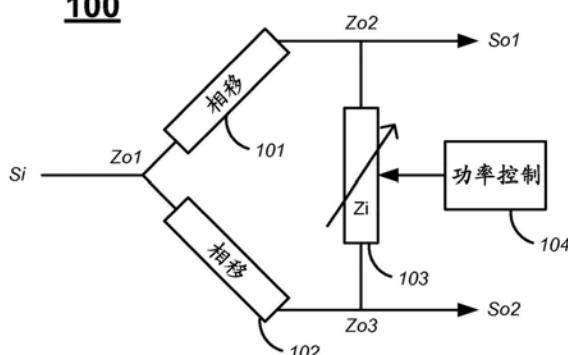

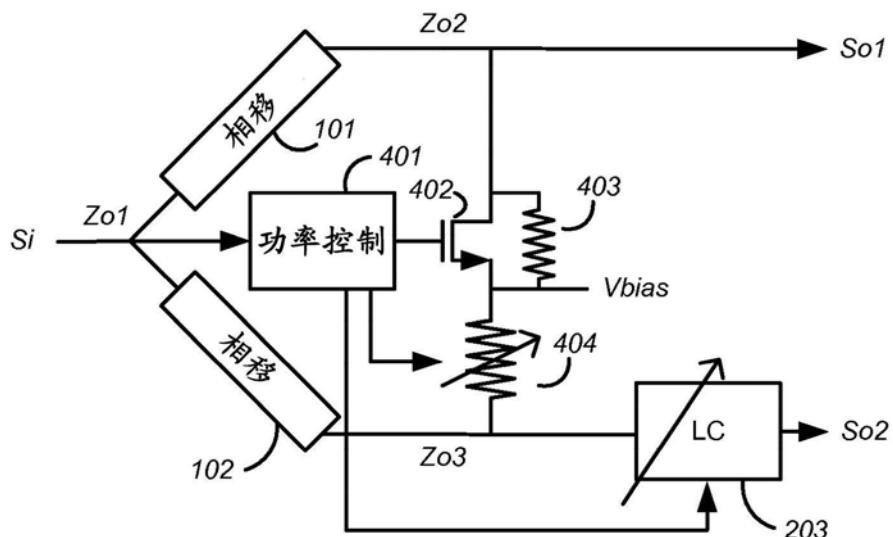

[0008] 图1图示了根据一个实施例的动态功分器。

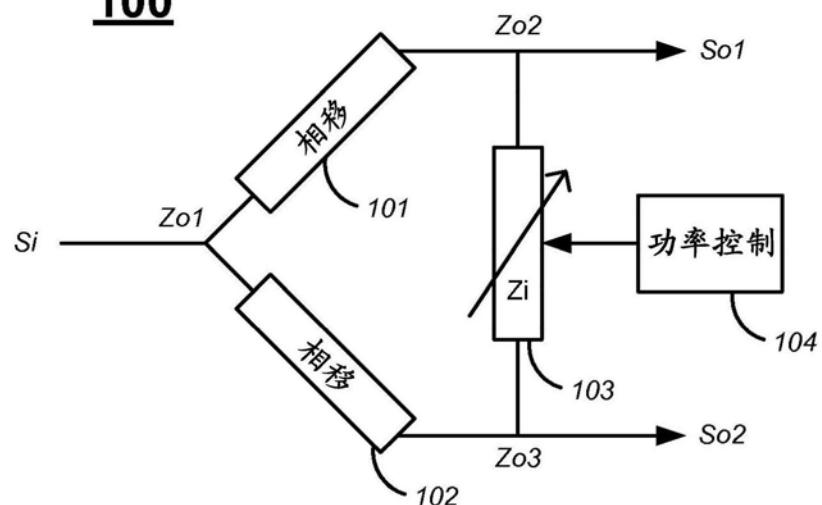

[0009] 图2图示了根据另一实施例的动态功分器。

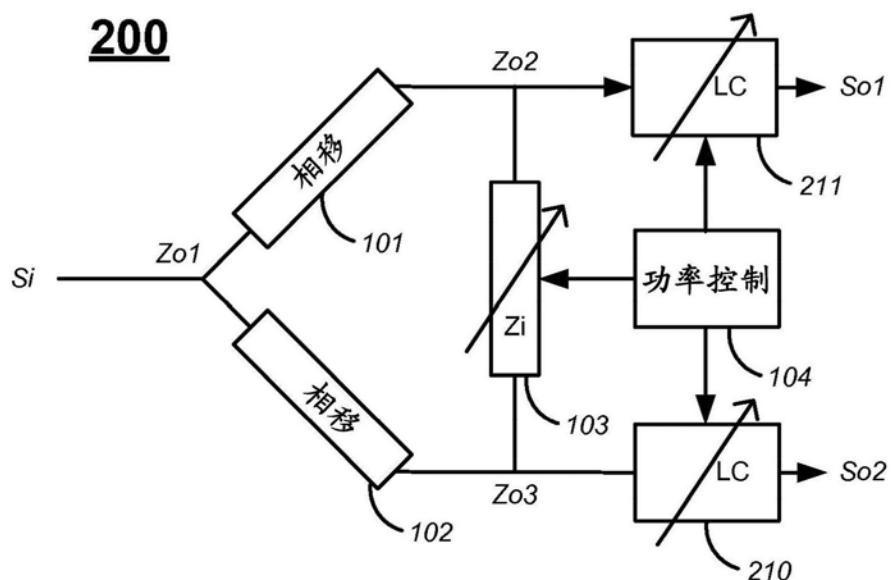

[0010] 图3图示了根据另一实施例的包括可调节电阻的示例功分器。

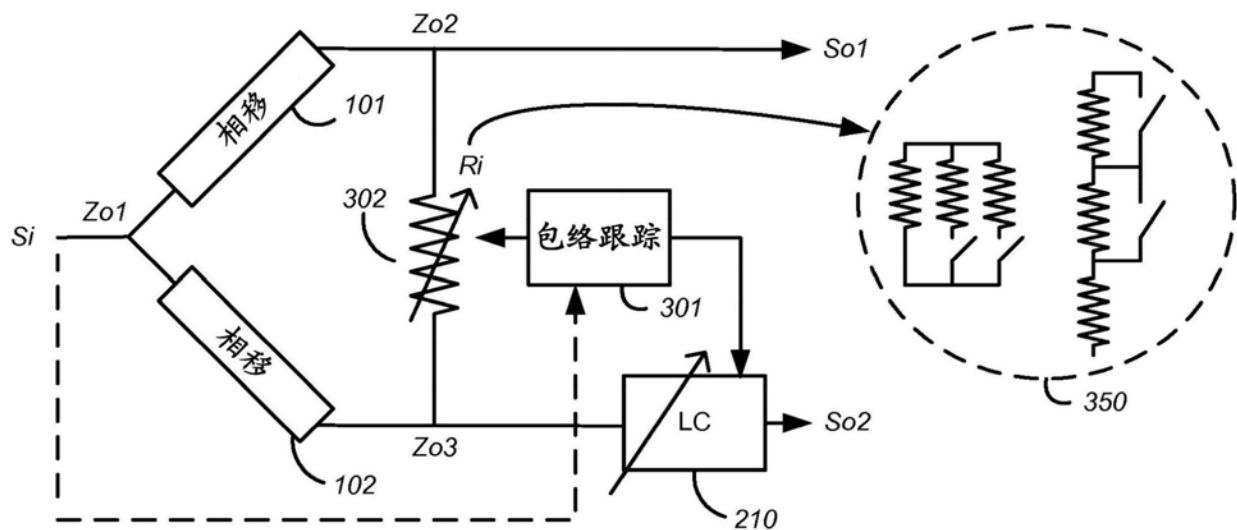

[0011] 图4图示了根据另一实施例的包括半导体器件的示例功分器。

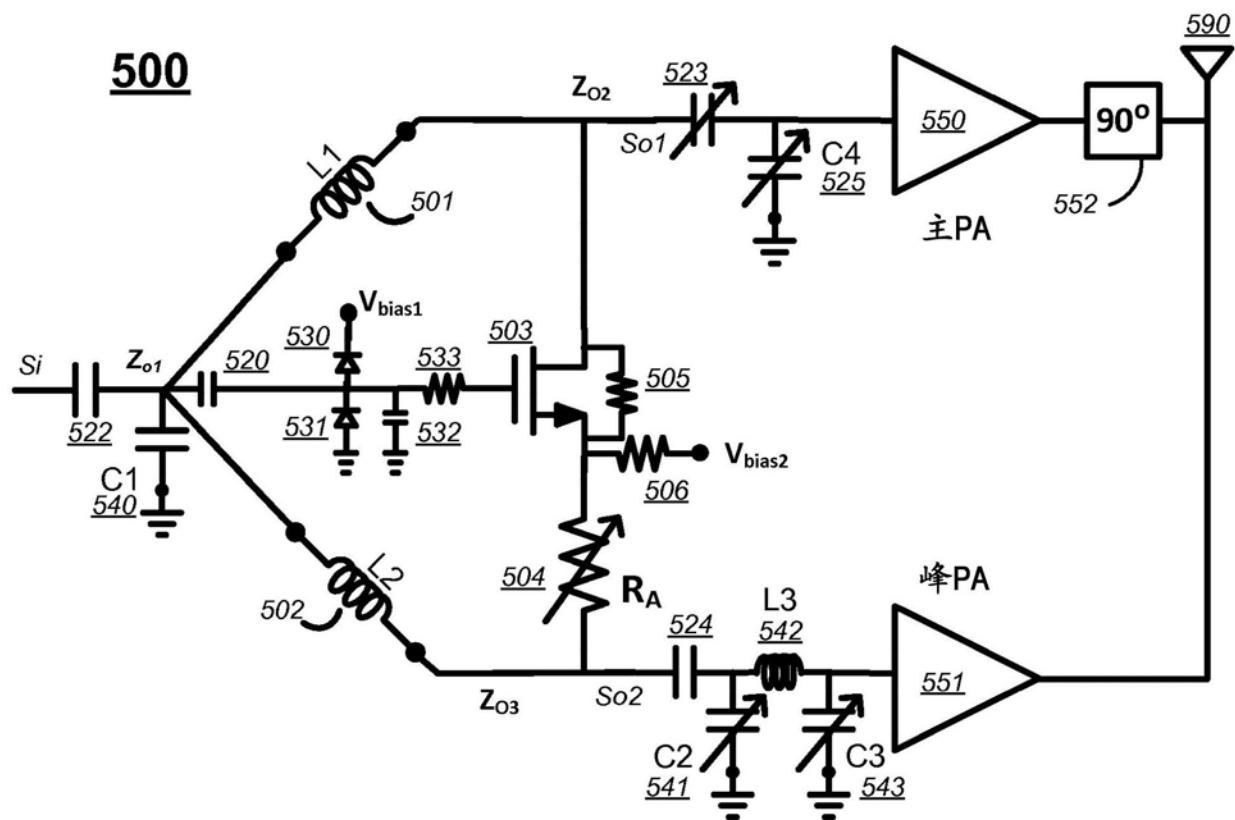

[0012] 图5图示了根据一个实施例的在功率放大器的输入处的示例功分器。

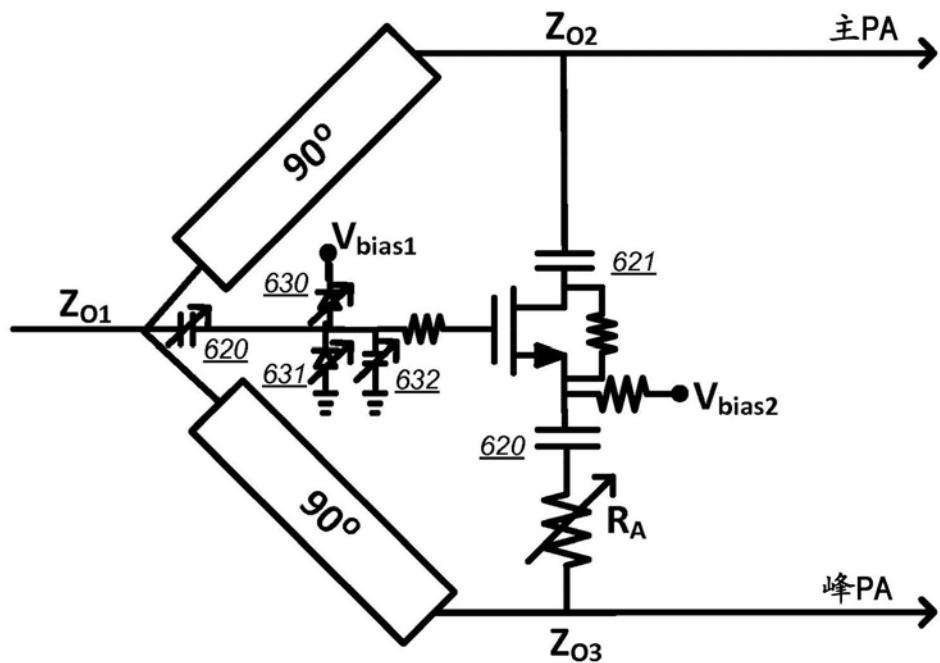

[0013] 图6图示了根据另一实施例的在功率放大器的输入处的示例功分器。

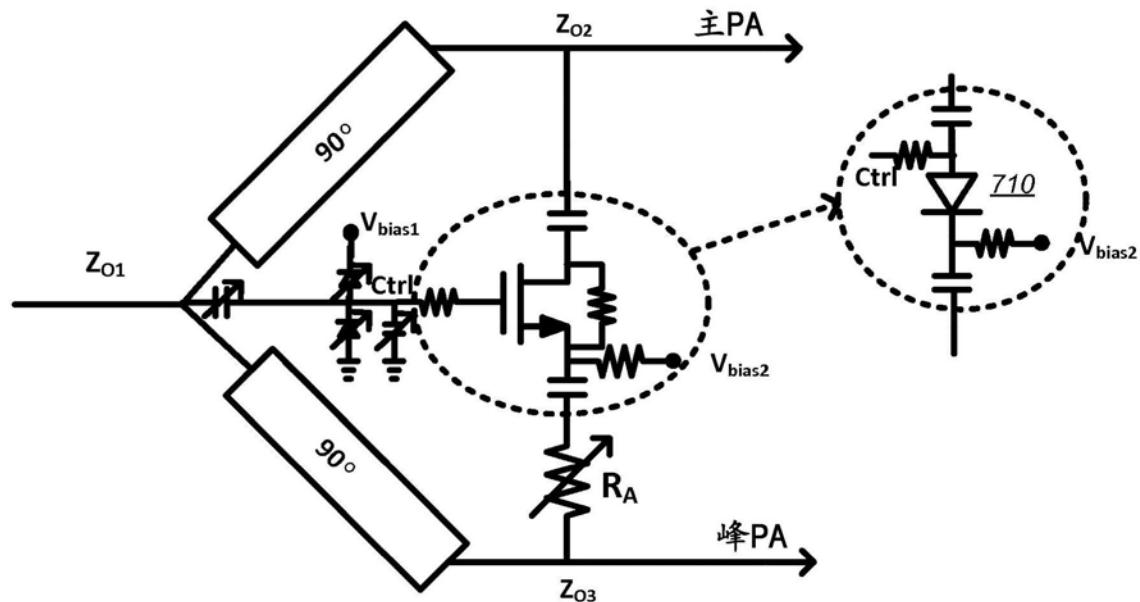

[0014] 图7图示了根据另一实施例的在功率放大器的输入处的示例功分器。

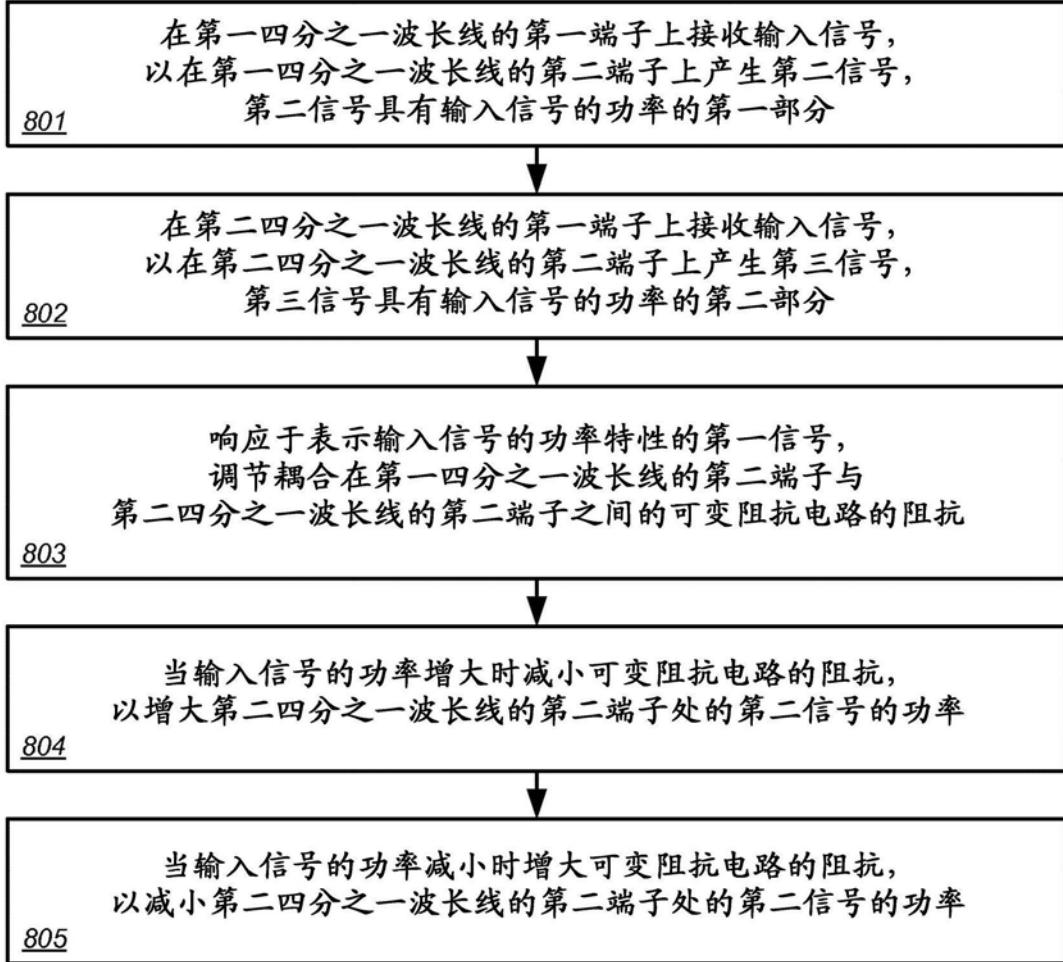

[0015] 图8图示了根据一个实施例的划分输入信号功率的方法。

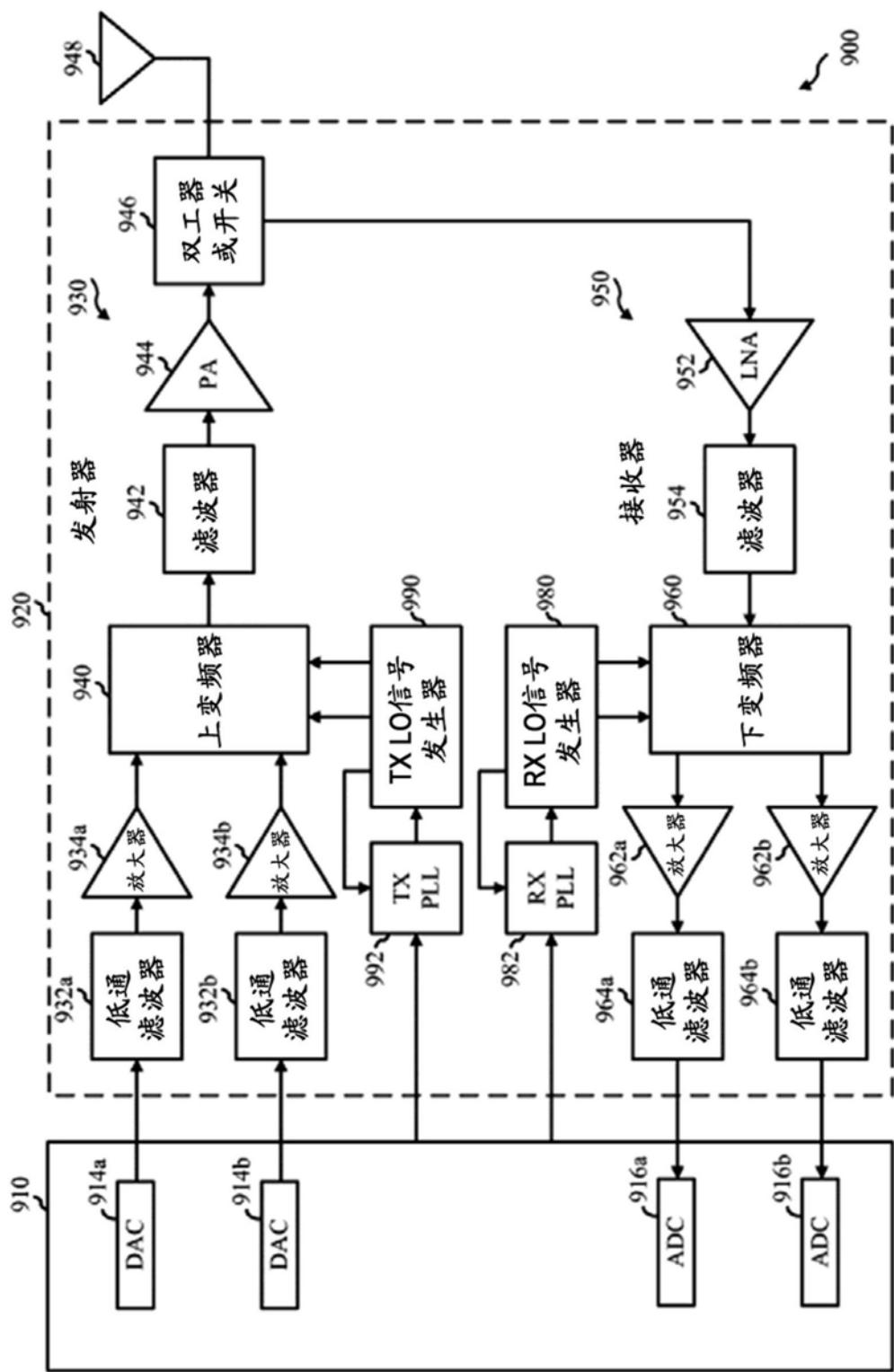

[0016] 图9图示了根据一个实施例的包括动态功率划分的无线系统。

### 具体实施方式

[0017] 本公开与动态功分器电路及方法有关。在以下描述中,为了解释的目的,阐述了许多示例和具体细节以便提供对本公开的透彻理解。然而,对本领域的技术人员将明显的是,本公开可以单独地或与下面描述的其他特征相组合地包括这些示例中的一些或所有特征,并且可以进一步包括本文中描述的特征和概念的修改和等价物。

[0018] 图1图示了根据一个实施例的动态功分器。本公开的实施例包括功分器电路,其可以在多个信号路径之间动态地路由信号功率。例如,功分器电路100在第一四分之一波长线101的第一端子上和在第二四分之一波长线102的第一端子上接收输入信号Si。在这一示例中,四分之一波长线101和102在信号Si中产生90度相移( $\pi/4$ )。四分之一波长线有时被称为四分之一波长阻抗变换器或 $\pi/4$ 阻抗变换器,并且可以包括预定长度的传输线(导体),其中终接端被设计为产生期望的阻抗。如下面的特定示例中说明的,阻抗变换可以被用来改进功分器的效率。

[0019] 本公开的特征和优点包括通过可变阻抗电路103将功分器输出信号路径耦合在一起。例如,在一些应用中,可能合意的是在某些条件下增大去往路径So1的信号功率并减小去往路径So2的信号功率,并且可能合意的是在其他条件下减小去往路径So1的信号功率并增大去往路径So2的信号功率。因此,可变阻抗电路103包括控制输入以调节可变阻抗电路的阻抗Zi。功率控制电路104可以向可变阻抗电路103的控制输入提供一个或多个信号,以例如增大或减小路径So1与路径So2之间的阻抗。

[0020] 在一个实施例中,可变阻抗电路103的阻抗Zi基于输入信号的功率条件而被调节。随着可变阻抗电路103的阻抗Zi被改变,在不同路径之间流动的信号功率的量可以基于输入信号功率而改变。例如,可变阻抗电路103的阻抗Zi可以在输入信号Si的功率增大时减小,以增大四分之一波长线102的第二端子处(路径So2)的信号功率并且减小四分之一波长线101的第二端子处(路径So1)的信号功率。类似地,可变阻抗电路103的阻抗Zi可以在输入信号Si的功率减小时增大,以减小四分之一波长线102的第二端子处的信号功率并且增大四分之一波长线101的第二端子处的信号功率。因此,信号功率可以通过调节Zi而在路径So1与路径So2之间被划分和传送。在一些应用中,路径之间的功率划分可以是不对称的,其中当Zi为高时一个路径(例如,路径So1)可以接收比另一路径(例如,路径So2)更多的信号功率。因此,在一些实施例中,来自高功率路径的信号功率可以基于输入信号条件例如通过减小Zi而可变地耦合至较低功率路径。在各种实施例中,可变阻抗电路103可以包括开关电阻器网络、一个或多个半导体器件(例如,晶体管或PIN二极管)、或它们的组合。进一步地,功率控制电路104可以例如基于包络跟踪、平均功率跟踪、或(例如,来自调制解调器的)功率控制信号来调节阻抗。下面提供了特定实施例的进一步示例。

[0021] 图2图示了根据另一实施例的动态功分器。如上面所提到的,阻抗变换可以被用来改进功分器电路的效率。在这一示例中,四分之一波长线102的第二端子处的阻抗Zo3被选择性地调节以改变由输入信号Si看向四分之一波长线102的输入阻抗。在这一示例中,功分器电路200包括可调节LC电路210,其可以包括电感器和电容器以设置阻抗Zo3。可调节LC电路210中的例如电容可以是(例如,使用开关电容器)可编程的,以修改可调节LC电路210的

输入阻抗并且改变 $Z_{o3}$ 。在第一配置中,可调节LC电路210可以在四分之一波长线102的第二端子处( $Z_{o3}$ 处)产生第一阻抗。由特定LC配置所设置的第一阻抗通过四分之一波长线102被转化,以在四分之一波长线102的第一端子处( $Z_{o1}$ 处)产生对应的第二阻抗。在第一配置中, $Z_{o3}$ 处的第一阻抗小于 $Z_{o1}$ 处的第二阻抗。在第二配置中,可调节LC电路210可以在四分之一波长线102的第二端子处( $Z_{o3}$ 处)产生第三阻抗,其被转化为四分之一波长线102的第一端子处( $Z_{o1}$ 处)对应的第四阻抗。在这一配置中, $Z_{o3}$ 处的第三阻抗大于 $Z_{o1}$ 处的第四阻抗。

[0022] 基于可调节LC电路210的上述操作,一些应用可以动态地重新配置可调节LC电路210以在多个路径之间产生不同的信号功率划分。例如,可调节LC电路210可以被配置为在输入信号的功率减小时产生第一阻抗(例如, $Z_{o3}$ 处的低阻抗)。 $Z_{o3}$ 处的第一低阻抗被转化为 $Z_{o1}$ 处的第二高阻抗,其使得更多信号功率通过四分之一波长线101行进到路径So1并且减小通过四分之一波长线102到路径So2的信号功率。因此,从四分之一波长线102的第一端子传送到四分之一波长线102的第二端子的输入信号 $S_i$ 的功率减小。

[0023] 类似地,可调节LC电路210可以被配置为在输入信号的功率增大时产生第三阻抗(例如, $Z_{o3}$ 处的高阻抗)。在这种情况下,可能有利的是,例如将更多信号功率路由至第二路径So2。 $Z_{o3}$ 处的第三高阻抗被转化为 $Z_{o1}$ 处的第四低阻抗,其例如使得更多信号功率通过四分之一波长线102行进到路径So2并且较少信号功率通过四分之一波长线101行进到路径S01。因此,从四分之一波长线102的第一端子传送至四分之一波长线102的第二端子的输入信号 $S_i$ 的功率增大。

[0024] 一起进行操作,可调节LC电路210和可变阻抗电路103可以被用来控制被递送至路径So1和路径So2的信号功率的量。由于信号功率以受控方式(例如,通过调节阻抗 $Z_i$ 和线路102的输入阻抗)被传递,所以功率的使用有利地是更高效的。

[0025] 在替换性实施例中,电路200可以包括第二可调节LC电路211,第二可调节LC电路211可以如上文所描述的改变 $Z_{o2}$ 和 $Z_{o1}$ 处的阻抗以进一步控制两个路径之间的功率划分。

[0026] 图3图示了根据另一实施例的包括可调节电阻的示例功分器。这一示例示出了使用可调节(可变)电阻 $R_i$  302(例如,诸如开关电阻器网络)实施的可变阻抗电路。标注350示出了例如开关电阻器的两个示例实施方式。这一特定示例还示出了功率控制电路可以是包络跟踪电路301。包络跟踪功率控制电路301可以接收与输入信号 $S_i$ 的包络相对应的上游包络信号。随着 $S_i$ 的包络增大,可能有利的是增大去往So2路径的信号功率。例如,下面说明的一个功率放大器架构可以包括主级和峰级(peaking stage)。例如,当信号功率为低时,可能有利的是向主级输送(channel)更多信号功率,并且当信号功率增大时,可能有利的是增大去往峰级的功率。包络跟踪功率控制电路301可以接收包络信号,并且如果包络为低则增大 $R_i$ 的值。因此,在低信号功率水平处,更多信号功率被输送至So1路径并且较少信号功率被输送至So2路径。替换地,包络跟踪功率控制电路301可以接收包络信号,并且如果包络为高则减小 $R_i$ 的值。因此,在高信号功率水平处,更多信号功率从So1路径通过 $R_i$ 被输送至So2路径。相应地, $R_i$ 可以按包络速率而被改变以高效地在路径之间移动信号功率。再次参考标注350,在一些示例实施方式中,一个电阻器可以串联地被安装在路径之间以设置路径之间的最大或最小电阻。可选地,如上文所描述的,在低信号功率水平处,LC电路210可以被配置为在 $Z_{o3}$ 处产生低阻抗,其被转化为用于输入信号 $S_i$ 的高阻抗,并且由此将输入信号功率输送至线路101和路径So1。替换地,在高信号功率水平处,LC电路210可以被配置为在 $Z_{o3}$ 处产

生较高阻抗，其被转化为用于输入信号Si的较低阻抗，并且由此将输入信号功率输送至线路102和路径So2。

[0027] 图4图示了根据另一实施例的包括半导体器件的示例功分器。这一示例图示了一种类型的半导体器件，其可以被用来使路径So1与路径So2之间的阻抗变化。在这一示例中，晶体管402耦合在四分之一波长线101的第二端子与四分之一波长线102的第二端子之间。尽管这里示出了NMOS晶体管，但是将理解可以使用其他晶体管类型。在这一示例中，电阻器403耦合在晶体管402的漏极与源极之间，并且可调节电阻404也可选地耦合在晶体管402的源极与四分之一波长线102的第二端子处的路径So2之间。最后，可调节LC 203可以耦合至四分之一波长线102的第二端子。

[0028] 在一个实施例中，功率控制电路401可以包括包络检测器。在这一示例中，功率控制电路401可以接收输入信号Si，并且基于信号包络来改变晶体管402的栅极处的电压以增大或减小线路101的第二端子与线路102的第二端子之间的阻抗。在一个实施例中，功率控制电路401可以包括平均功率发生器以确定平均信号功率并且调节电阻404。例如，功率控制电路401可以包括均方根(RMS)滤波器以确定平均信号功率。因此，在示例实施例中，例如，组合晶体管402和可调节电阻404，晶体管402的阻抗可以按信号包络速率而改变，并且可调节电阻404的阻抗可以按较慢的平均功率速率而改变。在一些情况下，可调节电阻404可以在制造期间(例如，在工厂中)被设置，并且在操作期间保持固定以设置线路101和线路102的第二端子之间的最小电阻。因此，在该情况下，晶体管402设置路径之间的阻抗的变化范围。

[0029] 图5图示了根据一个实施例的在功率放大器的输入处的示例功分器。在这一示例中，动态功分器包括第一四分之一波长线电感器501、第二四分之一波长线电感器502、包络跟踪功率控制电路(组件530-533)、可调节阻抗电路(组件503-506)、以及可调节LC电路(组件541-543)。动态功分器被配置为产生两个信号So1和So2，以用于主功率放大器级550和峰功率放大器级551。归因于主级与峰级之间的不同偏置条件，阻抗Zo2可以不同于阻抗Zo3(例如，Zo2>Zo3>Zo1)，这导致两个路径之间的信号功率的自然地不对称分布。主级550的输出通过另一四分之一波长电路552耦合至峰级551的输出，并且耦合至天线590以用于将RF通信信号驱动至空中波。在这一示例中，主级550和峰级551被配置作为Doherty功率放大器级。

[0030] 在这一示例中，输入信号Si耦合至包络跟踪功率控制电路，其包括作为包络检测器操作的二极管530和531、电容器532、以及电阻器533。Si耦合至串联连接的二极管530和531之间的节点，二极管530和531被布置在偏置电压Vbias1与接地之间。这些二极管对输入信号整流，并且电容器532、电阻器533和晶体管503的寄生栅极电容对经整流的信号进行低通滤波以产生包络。该包络被用作对晶体管503的栅极的控制输入以如上文所阐述的调节Zo2与Zo1之间的阻抗。在这一示例配置中，主PA路径与峰PA路径之间的电阻可以为如下：

$$[0031] V_{GS} = F(P_{IN})$$

$$[0032] RIsolateAC = RA + RON = RA + \frac{1}{\frac{unCoxW}{L}(VGS - VTH)}$$

[0033] 其中Pin是与提供给晶体管503的栅极的输入信号的输入功率相对应的包络信号，

RA是电阻504，并且RON是晶体管503的导通(ON)电阻，其是晶体管的栅源电压VGS、阈值电压VTH和物理参数的函数。

[0034] 晶体管506耦合至另一偏置电压Vbias2以设置晶体管503上的偏置点。电容器520提供与包络跟踪组件和由晶体管503设置的可变阻抗的AC耦合。在这一示例中，可变电阻器504可以被设置在固定值以设置路径之间的最小电阻，其中晶体管503的范围设置路径之间的阻抗范围。

[0035] 在这一示例中，输入信号Si的功率划分使用包括电感器L1和L2的两个四分之一波长线而被实现。Si通过AC耦合电容器522耦合至每个电感器的第一端子。第一四分之一波长变换由电容器C1、电感器L1和电容器C4 525的组合来实现。类似地，第二四分之一波长变换由电容器C1、电感器L2和电容器C2 521的组合来实现。信号So1和So2分别通过AC耦合电容器523和524耦合至主级和峰级。So2通过可调节LC电路被耦合，其包括可编程电容C2 541和C3 543以及电感器L3 542。Zo3处的阻抗可以例如通过重新配置C2和/或C3而被调节。L3、C2和C3还可以在峰放大器551的输入处提供四分之一波长偏移。在一个实施例中，电容器523和525可以是可调节的(例如，可编程的)，以例如改变Zo2处的阻抗并且修改So1与So2之间的功率划分。

[0036] 图6图示了根据另一实施例的在功率放大器的输入处的示例功分器。在这一示例中，电容器621-622在包络跟踪组件和由晶体管设置的可变阻抗周围提供DC隔离。这一示例还说明了另一方面。在这一示例中，电容器620、二极管630-631和电容器632是可变的(例如，可编程的)。因此，本公开的实施例可以在制造期间或动态地在操作期间被微调，以针对特定应用或操作条件的集合来优化性能。

[0037] 图7图示了根据另一实施例的在功率放大器的输入处的示例功分器。在这一示例中，半导体器件是PIN二极管710。PIN二极管是在p型半导体与n型半导体区域之间具有本征半导体区域的二极管。本征区域可以是宽的且轻微掺杂的“几乎”本征材料。在这一示例中，功分器在Zo2和Zo3处的输出端子之间的RF电阻可以通过改变通过PIN二极管的偏置电流而快速地被改变。在高频处，PIN二极管表现为电阻器，该电阻器的电阻是它的正向电流的反函数。结果，PIN二极管710提供可变衰减。随着(例如，来自功率控制电路的)控制信号Ctrl被改变，通过PIN二极管710的电流改变，并且电阻改变。

[0038] 图8图示了根据一个实施例的划分输入信号功率的方法。在801处，输入信号在第一四分之一波长线的第一端子上被接收以在第一四分之一波长线的第二端子上产生第二信号，第二信号具有输入信号的功率的第一部分。在802处，输入信号在第二四分之一波长线的第一端子上被接收以在第二四分之一波长线的第二端子上产生第三信号，第三信号具有输入信号的功率的第二部分。在803处，响应于表示输入信号的功率特性的第一信号，耦合在第一四分之一波长线的第二端子与第二四分之一波长线的第二端子之间的可变阻抗电路的阻抗被调节。在804处，可变阻抗电路的阻抗当输入信号的功率增大时被减小，以增大第二四分之一波长线的第二端子处的第二信号的功率。在805处，可变阻抗电路的阻抗当输入信号的功率减小时被增大，以减小第二四分之一波长线的第二端子处的第二信号的功率。

[0039] 图9图示了根据一种实施例的包括功分器的无线系统。无线系统900可以包括基带电路910用于发送、接收和处理去往和来自收发器920的基带数字信号。收发器920向天线

948发送RF通信信号并且从天线948接收RF通信信号。数字通信信号在DAC 914a-b中被转换为模拟信号并且耦合至发射通道930,其中“a”通道和“b”通道可以对应于信号的“I”分量和“Q”分量。模拟信号被低通滤波(框932a-b)、被放大(框934a-b)、并且使用来自发射(TX)锁相环(PLL)992和TX L0信号发生器990的本地振荡器(L0)信号而被上变频(框940)。经上变频的信号被滤波(框942)并且被耦合至功率放大器944。功率放大器(PA)944可以包括用于从输入信号包络生成包络跟踪信号的电路,并且可以包括本文描述的例如用于划分输入信号的功率和将多个输出信号耦合至功率放大器的不同级的电路系统。PA 944可以例如进一步包括如上文所描述的Doherty功率放大器。PA 944的输出通过双工器或开关946耦合至天线以用于广播RF信号。

[0040] 收发器920进一步包括用于从天线948接收信号的接收通道(或接收器)950,其包括低噪放大器(LNA)952。LNA 952的输出被滤波(框954)并且使用例如来自接收器(RX)锁相环(PLL)982和RX L0信号发生器980的L0信号而被下变频(框960)。经下变频的信号被放大(框962a-b)、被滤波(框964a-b)、并且被耦合至基带电路910中的ADC 916a-b以便转换至数字域以用于进一步的信号处理。

[0041] 上面的描述说明了本公开的各种实施例以及特定实施例的多个方面可以如何被实施的示例。上面的示例不应当被认为是仅有的实施例,并且被提出以说明特定实施例的灵活性和优点。基于上面的公开,其他布置、实施例、实施方式和等价物可以被采用,而不偏离本公开的范围。

**100**

图1

**200**

图2

图3

图4

图5

图6

图7

图8

图9