(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-103653

(P2008-103653A)

(43) 公開日 平成20年5月1日(2008.5.1)

| (51) Int.Cl.                 | F 1             | テーマコード (参考) |

|------------------------------|-----------------|-------------|

| <b>H01L 21/336 (2006.01)</b> | H01L 29/78 627A | 4M1O4       |

| <b>H01L 29/786 (2006.01)</b> | H01L 29/78 626C | 5F11O       |

| <b>H01L 29/417 (2006.01)</b> | H01L 29/78 617U |             |

|                              | H01L 29/78 617L |             |

|                              | H01L 29/50 M    |             |

審査請求 未請求 請求項の数 40 O L (全 22 頁)

|              |                              |          |                                            |

|--------------|------------------------------|----------|--------------------------------------------|

| (21) 出願番号    | 特願2006-313492 (P2006-313492) | (71) 出願人 | 504157024<br>国立大学法人東北大学                    |

| (22) 出願日     | 平成18年11月20日 (2006.11.20)     |          | 宮城県仙台市青葉区片平二丁目1番1号                         |

| (31) 優先権主張番号 | 特願2006-257848 (P2006-257848) | (71) 出願人 | 000229117<br>日本ゼオン株式会社                     |

| (32) 優先日     | 平成18年9月22日 (2006.9.22)       | (74) 代理人 | 東京都千代田区丸の内一丁目6番2号<br>弁理士 池田 篤保             |

| (33) 優先権主張国  | 日本国 (JP)                     | (72) 発明者 | 大見 忠弘<br>宮城県仙台市青葉区片平二丁目1番1号<br>国立大学法人東北大学内 |

|              |                              | (72) 発明者 | 杉谷 耕一<br>東京都千代田区丸の内一丁目6番2号 日本ゼオン株式会社内      |

最終頁に続く

(54) 【発明の名称】半導体装置及び半導体装置の製造方法

## (57) 【要約】

【課題】 ゲート絶縁膜の平坦性が優れた薄膜トランジスタ(TFT)及びその製造方法を提供する。

【解決手段】 基板10上の絶縁体層に溝を設け、この溝中にその表面が前記絶縁体層の表面とほぼ平坦になるようゲート電極12を形成し、該ゲート電極12上にゲート絶縁膜13を介して半導体層14を配置し、該半導体層にソース電極15およびドレイン電極の少なくとも一方を電気的に接続した半導体装置において、前記ゲート絶縁膜13を前記ゲート電極12上に設けた絶縁体塗布膜131とその上に形成された絶縁体CVD膜132とを含んで構成した。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

基板と、該基板上に設けられかつ溝を有する絶縁体層と、該溝中にその表面が前記絶縁体層の表面とほぼ平坦になるように設けられた導電体層と、該導電体層上に設けられた絶縁膜と、該導電体層の少なくとも一部の上方において該絶縁膜上に設けられた半導体層とを有する半導体装置において、前記絶縁膜が絶縁体塗布膜を含むことを特徴とする半導体装置。

**【請求項 2】**

前記絶縁膜が前記絶縁体塗布膜のみからなることを特徴とする請求項 1 に記載の半導体装置。 10

**【請求項 3】**

前記絶縁膜が他の絶縁体膜をさらに含むことを特徴とする請求項 1 に記載の半導体装置。 10

**【請求項 4】**

前記他の絶縁体膜が絶縁体 CVD 膜であることを特徴とする請求項 3 に記載の半導体装置。 10

**【請求項 5】**

前記他の絶縁体膜が前記絶縁体塗布膜と前記半導体層との間に設けられたことを特徴とする請求項 3 又は 4 に記載の半導体装置。 10

**【請求項 6】**

前記他の絶縁体膜が前記絶縁体塗布膜と前記導電体層との間に設けられたことを特徴とする請求項 3 又は 4 に記載の半導体装置。 20

**【請求項 7】**

前記導電体層の一部がゲート電極であり、該ゲート電極上の前記絶縁膜がゲート絶縁膜であり、前記半導体層は前記ゲート絶縁膜上に設けられたことを特徴とする請求項 1 ~ 6 の一つに記載の半導体装置。 20

**【請求項 8】**

前記半導体層にソース電極およびドレイン電極の少なくとも一方が電気的に接続されていることを特徴とする請求項 7 に記載の半導体装置。 20

**【請求項 9】**

基板上の絶縁体層に溝を設け、該溝中にその表面が前記絶縁体層の表面とほぼ平坦になるようにゲート電極を形成し、該ゲート電極上にゲート絶縁膜を介して半導体層を配置し、該半導体層にソース電極およびドレイン電極の少なくとも一方を電気的に接続した半導体装置において、前記ゲート絶縁膜を前記ゲート電極上に設けた絶縁体塗布膜とその上に形成された絶縁体 CVD 膜とを含んで構成したことを特徴とする半導体装置。 30

**【請求項 10】**

前記絶縁体塗布膜は、その表面の平坦度が Ra で 1 nm 以下、ピーク・トウ・バレイ値で 20 nm 以下であることを特徴とする請求項 1 ~ 9 の一つに記載の半導体装置。 30

**【請求項 11】**

前記ゲート電極は、その表面の平坦度が Ra で 3 nm 以上、ピーク・トウ・バレイ値で 30 nm 以上であることを特徴とする請求項 7 ~ 9 の一つに記載の半導体装置。 40

**【請求項 12】**

前記基板は実質的に透明な絶縁体基板であって、前記絶縁体層は実質的に透明な樹脂層であることを特徴とする請求項 1 ~ 11 の一つに記載の半導体装置。 40

**【請求項 13】**

前記樹脂層が、アルカリ可溶性脂環式オレフィン系樹脂と感放射線成分とを含有する感光性樹脂組成物で形成されたものである請求項 12 に記載の半導体装置。 40

**【請求項 14】**

前記樹脂層がアクリル系樹脂、シリコーン系樹脂、フッ素系樹脂、ポリイミド系樹脂、ポリオレフィン系樹脂、脂環式オレフィン系樹脂、およびエポキシ系樹脂からなる群から 50

選ばれた一種以上の樹脂を含む請求項 1 2 に記載の半導体装置。

**【請求項 1 5】**

前記ゲート電極が、下地密着層と導電金属層と導電金属拡散抑止層とを少なくとも含んで構成されていることを特徴とする請求項 7 ~ 9 および 1 1 の一つに記載の半導体装置。

**【請求項 1 6】**

前記絶縁体塗布膜が前記導電体層と前記絶縁体層との間の隙間を埋め、かつ前記絶縁体層の表面上に延在していることを特徴とする請求項 1 ~ 6 、 1 0 、および 1 2 ~ 1 4 の一つに記載の半導体装置。

**【請求項 1 7】**

前記絶縁体塗布膜は実質的に透明であり、前記ゲート電極と前記絶縁体層との間の隙間を埋め、かつ前記絶縁体層の表面上に延在していることを特徴とする請求項 7 ~ 9 および 1 1 の一つに記載の半導体装置。 10

**【請求項 1 8】**

前記絶縁体 C V D 膜は実質的に透明であり、前記絶縁体層の表面上に延在している前記絶縁体塗布膜上に延在していることを特徴とする請求項 1 7 に記載の半導体装置。

**【請求項 1 9】**

前記絶縁体塗布膜は、金属有機化合物および金属無機化合物の少なくとも一方と溶媒とを含む液体状の塗布膜を乾燥、焼成して得た膜であることを特徴とする請求項 1 ~ 1 8 の一つに記載の半導体装置。 20

**【請求項 2 0】**

前記絶縁体層は実質的に透明な樹脂層であり、前記絶縁体塗布膜は、金属有機化合物および金属無機化合物の少なくとも一方と溶媒とを含む液体状の塗布膜を乾燥し 3 0 0 以下で焼成して得た膜であることを特徴とする請求項 1 ~ 1 8 の一つに記載の半導体装置。

**【請求項 2 1】**

前記絶縁体塗布膜の誘電率は 2 . 6 以上であることを特徴とする請求項 1 ~ 2 0 の一つに記載の半導体装置。

**【請求項 2 2】**

前記絶縁体 C V D 膜の誘電率は 4 以上であることを特徴とする請求項 4 または 9 に記載の半導体装置。 30

**【請求項 2 3】**

前記ゲート絶縁膜の厚さが E O T (二酸化珪素換算) で 9 5 n m 乃至 2 0 0 n m であることを特徴とする請求項 7 ~ 2 2 の一つに記載の半導体装置。

**【請求項 2 4】**

前記絶縁体 C V D 膜の厚さが E O T (二酸化珪素換算) で 8 0 n m 乃至 1 8 5 n m であることを特徴とする請求項 2 2 に記載の半導体装置。

**【請求項 2 5】**

前記絶縁体塗布膜の厚さが E O T (二酸化珪素換算) で 1 5 n m 乃至 1 2 0 n m であることを特徴とする請求項 1 ~ 2 4 の一つに記載の半導体装置。

**【請求項 2 6】**

請求項 1 ~ 2 5 のいずれかに記載の半導体装置を用いて製造された表示装置。 40

**【請求項 2 7】**

前記表示装置は液晶表示装置または有機 E L 表示装置であることを特徴とする請求項 2 6 に記載の表示装置。

**【請求項 2 8】**

溝を有する絶縁体層を基板上に設ける工程と、該溝中にその表面が前記絶縁体層の表面とほぼ平坦になるように導電体層を形成する工程と、該導電体層上に絶縁体塗布膜を形成する工程と、前記絶縁体塗布膜の少なくとも一部の上に半導体層を形成する工程とを有することを特徴とする半導体装置の製造方法。

**【請求項 2 9】**

前記絶縁体塗布膜を形成する工程の前または後に他の絶縁体膜を形成する工程を含むこ 50

とを特徴とする請求項 2 8 に記載の半導体装置の製造方法。

**【請求項 3 0】**

前記他の絶縁体膜を C V D で形成することを特徴とする請求項 2 9 に記載の半導体装置の製造方法。

**【請求項 3 1】**

前記導電体層の一部をゲート電極とし、該ゲート電極上の前記絶縁体塗布膜をゲート絶縁膜の少なくとも一部とし、前記半導体層を前記ゲート絶縁膜上に設けることを特徴とする請求項 2 8 ~ 3 0 の一つに記載の半導体装置の製造方法。

**【請求項 3 2】**

前記半導体層にソース電極およびドレイン電極の少なくとも一方を形成する工程をさらに含むことを特徴とする請求項 3 1 に記載の半導体装置の製造方法。 10

**【請求項 3 3】**

基板上に溝を有する絶縁体層を設ける工程と、該溝中にその表面が前記絶縁体層の表面とほぼ平坦になるようにゲート電極を形成する工程と、該ゲート電極上に絶縁体塗布膜を形成する工程と、前記絶縁体塗布膜上に C V D で誘電体膜を形成する工程と、前記誘電体膜上に半導体層を形成する工程と、該半導体層にソース電極およびドレイン電極の少なくとも一方を電気的に接続する工程とを有することを特徴とする半導体装置の製造方法。

**【請求項 3 4】**

前記絶縁体塗布膜を形成する工程は、金属有機化合物および金属無機化合物の少なくとも一方と溶媒とを含む液体状の材料を前記ゲート電極上に塗布する工程と、塗布した膜を乾燥する工程と、乾燥した膜を焼成する工程とを含むことを特徴とする請求項 2 8 ~ 3 3 の一つに記載の半導体装置の製造方法。 20

**【請求項 3 5】**

前記ゲート電極を形成する工程が、導電金属層をめっき法、印刷法またはインクジェットによる塗布法により形成する工程と、その上に導電金属拡散抑止層をめっき法、印刷法またはインクジェットによる塗布法により形成する工程と含むことを特徴とする請求項 3 1 ~ 3 4 に記載の半導体装置の製造方法。

**【請求項 3 6】**

前記絶縁体塗布膜を形成する工程が、前記液体状の材料を前記ゲート電極と前記絶縁体層との間の隙間を埋め、かつ前記絶縁体層の表面上に延在するように塗布する工程を含むことを特徴とする請求項 3 1 ~ 3 5 の一つに記載の半導体装置の製造方法。 30

**【請求項 3 7】**

前記基板上に溝を有する絶縁体層を設ける工程が、前記基板上に樹脂膜を形成する工程と、該樹脂膜をパターニングすることで前記ゲート電極を収容すべき溝を形成する工程とを含むことを特徴とする請求項 2 8 ~ 3 6 の一つに記載の半導体装置の製造方法。

**【請求項 3 8】**

前記焼成を不活性ガス雰囲気中または大気雰囲気中で行うことを特徴とする請求項 3 4 に記載の半導体装置の製造方法。

**【請求項 3 9】**

請求項 2 8 ~ 3 8 のいずれかに記載の方法を用いて半導体装置を形成する工程を有することを特徴とする液晶表示装置または有機 E L 表示装置の製造方法。 40

**【請求項 4 0】**

前記導電金属層は C u および A g の少なくとも一つを含み、前記導電金属拡散抑止層は N i 、 W 、 T a 、 N b 、及び T i のいずれかから選択される金属を含んでなることを特徴とする請求項 1 5 に記載の半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本発明は半導体装置特に薄膜トランジスタ ( T F T ) に関し、またその製造方法に関する。 50

**【背景技術】****【0002】**

一般に、液晶表示装置、有機EL装置、無機EL装置等の表示装置は、平坦な一主面を有する基板上に、配線パターン、電極パターン等の導電パターンを順次、成膜、パターニングすることによって形成されている。そして、電極膜、表示装置を構成する素子に必要な各種の膜等を順次成膜、パターニングすることによって、表示装置が製作されている。

**【0003】**

近年、この種の表示装置に対しては大型化の要望が強くなっている。大型の表示装置を形成するには、より多くの表示素子を高精度で基板上に形成し、これらの素子を配線パターンと電気的に接続する必要がある。この場合、基板上には配線パターンの他に、絶縁膜、TFT(薄膜トランジスタ)素子、発光素子等が多層化された状態で形成されている。その結果、基板上には、階段状に段差ができるのが普通であり、配線パターンはこれらの段差を越えて配線されている。更に、表示装置を大型化する際、配線パターン自体が長くなるため、当該配線パターンの抵抗を低くすることが必要になってくる。配線パターンの段差を解消し、かつ低抵抗化する手法として、特許文献1、特許文献2および特許文献3では液晶ディスプレイのような平面ディスプレイ用配線を形成するために、透明な基板表面上に配線と、これと同等の高さの透明な絶縁材料を配線パターンに接するように形成することが開示されている。また特許文献3においては、さらに加熱プレスやCMPにより配線をより平坦化する方法が開示されている。

10

**【0004】**

20

**【特許文献1】WO 2004 / 110117号****【特許文献2】特願2005 - 173050号公報****【特許文献3】特開2005 - 210081号公報****【発明の開示】****【発明が解決しようとする課題】****【0005】**

特許文献1においては、樹脂パターンにより形成された溝の中に配線を埋設し厚膜配線化することにより表示装置の特性の向上が可能であることが開示されており、配線形成方法としてインクジェット法やスクリーン印刷法等の手法が開示されている。

30

**【0006】**

しかしながら、開示された方法では基板への密着性に問題があることが判明した。

**【0007】**

更に、特許文献1に記載されているように、配線を導電性インクやスクリーン印刷等で形成すると、配線の表面が粗く、配線上に形成される絶縁層等の平坦性が悪くなることも分かった。導電性インクやスクリーン印刷によって形成された配線をゲート電極として使用した場合、配線表面の粗さのため、チャンネルを通るキャリアの伝播率が悪化し、高速動作の障害になると言う現象が観測された。更に、導電性インクやスクリーン印刷等では、配線が微細になると、所望の形状を得ることが困難になることも判明した。たとえば、幅20μm、長さ50μmのゲート電極をこれらの方針で形成しようとしても、電極材料が全面に行き渡らず、所望のパターンの形成が実用上不可能であることが判明した。

40

**【0008】**

特許文献2では、これらの問題を解決するために、密着性を高めるように、絶縁基板上を表面修飾する工程と、該絶縁基板上に樹脂膜を形成する工程と、該樹脂膜をパターニングすることで電極もしくは配線が収容される凹部を形成する工程と、該凹部に触媒付与する工程と、該樹脂膜を加熱硬化する工程と、該凹部にめっき法により導電性材料を形成する工程と、を少なくとも含む製造方法を提案している。ゲート電極等の導電金属層、たとえばCu層は無電解めっき法により形成され、その上にCu拡散抑制層として選択的CVD法によりW層を形成するか、無電解めっき法によりNi層を形成してゲート電極としている。この方法によれば、ゲート電極の基板への密着性は改善され、さらに幅20μm、長さ50μmのゲート電極であっても、寸法の大小にかかわりなく、所望のパターンの形

50

成が可能である。しかしながら、この方法でもゲート電極の表面が粗く、ゲート電極上に形成されるゲート絶縁層の平坦性が悪いことが分かった。例えば、無電解めっきで形成されたCu層表面の平坦度はRaで17.74nm、ピーク・トウ・バレイ値で193.92nmにも達し、その上に形成されたNi層表面も平坦度はRaで8.58nm、ピーク・トウ・バレイ値で68.7nmとなり、この表面の粗さのためにゲート絶縁膜としてCVD形成された窒化シリコンの表面、すなわち半導体層のチャンネル領域との界面も粗く、表面散乱の結果キャリアの移動度が悪化することが判明した。ゲート電極表面の平坦度はRaで1nm以下、ピーク・トウ・バレイ値で20nm以下であることがゲート絶縁膜とチャンネル領域との界面における平坦性を維持しキャリアの界面散乱を防ぐために必要である。

10

## 【0009】

特許文献3では、これらの配線表面の粗さの問題を解決する方法として、プレス部材によって絶縁膜および埋め込み配線を押圧する加熱プレス処理、またはCMP処理する工程を提案している。しかしながら、近年のマザーガラスの基板サイズの大型化に伴い、特に第5世代の1100mm×1300mm以上の大きさのガラス基板においては、これらの配線の平坦化の方法は現実的ではなくなっている。加熱プレス処理はわずかなガラスのひずみが破損につながり、またCMPによる大型ガラス基板の全面均一研磨は非常に困難であり、コストの増大につながる。

20

## 【0010】

また、めっき層と周囲の樹脂膜との間に隙間が生じる現象も観測された。原因はめっき処理時の高温で樹脂が膨張し、めっき形成後に収縮するためと見られる。このような隙間があると、ゲート絶縁膜に電界集中が起きて絶縁破壊が生じ、ゲート電極とチャンネル領域とがショートしてしまう。

## 【0011】

本発明の目的は、ゲート絶縁膜の平坦性が優れた薄膜トランジスタ(TFT)及びその製造方法を提供することである。

## 【0012】

本発明の他の目的は、ゲート電極表面の粗さおよび周囲の絶縁層との隙間の問題を解決した半導体装置及びその製造方法を提供することである。

30

## 【0013】

本発明の更に他の目的は、界面平坦性の優れた薄膜トランジスタを含む表示装置及びその製造方法を提供することである。

## 【課題を解決するための手段】

## 【0014】

本発明によれば、基板と、該基板上に設けられかつ溝を有する絶縁体層と、該溝中にその表面が前記絶縁体層の表面とほぼ平坦になるように設けられた導電体層と、該導電体層上に設けられた絶縁膜と、該導電体層の少なくとも一部の上方において該絶縁膜上に設けられた半導体層とを有する半導体装置において、前記絶縁膜が絶縁体塗布膜を含むことを特徴とする半導体装置が得られる。

40

## 【0015】

本発明によれば、前記絶縁膜が前記絶縁体塗布膜のみからなることを特徴とする半導体装置が得られる。

## 【0016】

本発明によれば、前記絶縁膜が他の絶縁体膜をさらに含むことを特徴とする半導体装置が得られる。

## 【0017】

本発明によれば、前記他の絶縁体膜が絶縁体CVD膜であることを特徴とする半導体装置が得られる。

## 【0018】

本発明によれば、前記他の絶縁体膜が前記絶縁体塗布膜と前記半導体層との間に設けら

50

れることを特徴とする半導体装置が得られる。

【0019】

本発明によれば、前記他の絶縁体膜が前記絶縁体塗布膜と前記導電体層との間に設けられたことを特徴とする半導体装置が得られる。

【0020】

本発明によれば、前記導電体層の一部がゲート電極であり、該ゲート電極上の前記絶縁膜がゲート絶縁膜であり、前記半導体層は前記ゲート絶縁膜上に設けられたことを特徴とする半導体装置が得られる。

【0021】

本発明によれば、前記半導体層にソース電極およびドレイン電極の少なくとも一方が電気的に接続されていることを特徴とする半導体装置が得られる。 10

【0022】

本発明によれば、基板上の絶縁体層に溝を設け、該溝中にその表面が前記絶縁体層の表面とほぼ平坦になるようにゲート電極を形成し、該ゲート電極上にゲート絶縁膜を介して半導体層を配置し、該半導体層にソース電極およびドレイン電極の少なくとも一方を電気的に接続した半導体装置において、前記ゲート絶縁膜を前記ゲート電極上に設けた絶縁体塗布膜とその上に形成された絶縁体CVD膜とを含んで構成したことを特徴とする半導体装置が得られる。

【0023】

本発明によれば、前記絶縁体塗布膜は、その表面の平坦度がRaで1nm以下、ピーク・トゥ・バレイ値で20nm以下であることを特徴とする半導体装置が得られる。 20

【0024】

本発明によれば、前記ゲート電極は、その表面の平坦度がRaで3nm以上、ピーク・トゥ・バレイ値で30nm以上であることを特徴とする半導体装置が得られる。

【0025】

本発明によれば、前記基板は実質的に透明な絶縁体基板であって、前記絶縁体層は実質的に透明な樹脂層であることを特徴とする半導体装置が得られる。

【0026】

本発明によれば、前記樹脂層が、アルカリ可溶性脂環式オレフィン系樹脂と感放射線成分とを含有する感光性樹脂組成物で形成されたものであることを特徴とする半導体装置が得られる。 30

【0027】

本発明によれば、前記樹脂層がアクリル系樹脂、シリコーン系樹脂、フッ素系樹脂、ポリイミド系樹脂、ポリオレフィン系樹脂、脂環式オレフィン系樹脂、およびエポキシ系樹脂からなる群から選ばれた一種以上の樹脂を含むことを特徴とする半導体装置が得られる。

【0028】

本発明によれば、前記ゲート電極が、下地密着層と導電金属層と導電金属拡散抑止層とを少なくとも含んで構成されていることを特徴とする半導体装置が得られる。

【0029】

本発明によれば、前記絶縁体塗布膜が前記導電体層と前記絶縁体層との間の隙間を埋め、かつ前記絶縁体層の表面上に延在していることを特徴とする半導体装置が得られる。 40

【0030】

本発明によれば、前記絶縁体塗布膜は実質的に透明であり、前記ゲート電極と前記絶縁体層との間の隙間を埋め、かつ前記絶縁体層の表面上に延在していることを特徴とする半導体装置が得られる。

【0031】

本発明によれば、前記絶縁体CVD膜は実質的に透明であり、前記絶縁体層の表面上に延在している前記絶縁体塗布膜上に延在していることを特徴とする半導体装置が得られる。 50

**【 0 0 3 2 】**

本発明によれば、前記絶縁体塗布膜は、金属有機化合物および金属無機化合物の少なくとも一方と溶媒とを含む液体状の塗布膜を乾燥、焼成して得た膜であることを特徴とする半導体装置が得られる。

**【 0 0 3 3 】**

本発明によれば、前記絶縁体層は実質的に透明な樹脂層であり、前記絶縁体塗布膜は、金属有機化合物および金属無機化合物の少なくとも一方と溶媒とを含む液体状の塗布膜を乾燥し300℃以下で焼成して得た膜であることを特徴とする半導体装置が得られる。

**【 0 0 3 4 】**

本発明によれば、前記絶縁体塗布膜の誘電率は2.6以上であることを特徴とする半導体装置が得られる。 10

**【 0 0 3 5 】**

本発明によれば、前記絶縁体CVD膜の誘電率は4以上であることを特徴とする半導体装置が得られる。

**【 0 0 3 6 】**

本発明によれば、前記ゲート絶縁膜の厚さがEOT(二酸化珪素換算)で95nm乃至200nmであることを特徴とする半導体装置が得られる。

**【 0 0 3 7 】**

本発明によれば、前記絶縁体CVD膜の厚さがEOT(二酸化珪素換算)で80nm乃至185nmであることを特徴とする半導体装置が得られる。 20

**【 0 0 3 8 】**

本発明によれば、前記絶縁体塗布膜の厚さがEOT(二酸化珪素換算)で15nm乃至120nmであることを特徴とする半導体装置が得られる。

**【 0 0 3 9 】**

本発明によれば、上記した半導体装置を用いて製造された表示装置が得られる。

**【 0 0 4 0 】**

本発明によれば、前記表示装置は液晶表示装置または有機EL表示装置であることを特徴とする表示装置が得られる。

**【 0 0 4 1 】**

本発明によれば、溝を有する絶縁体層を基板上に設ける工程と、該溝中にその表面が前記絶縁体層の表面とほぼ平坦になるように導電体層を形成する工程と、該導電体層上に絶縁体塗布膜を形成する工程と、前記絶縁体塗布膜の少なくとも一部の上に半導体層を形成する工程とを有することを特徴とする半導体装置の製造方法が得られる。 30

**【 0 0 4 2 】**

本発明によれば、前記絶縁体塗布膜を形成する工程の前または後に他の絶縁体膜を形成する工程を含むことを特徴とする半導体装置の製造方法が得られる。

**【 0 0 4 3 】**

本発明によれば、前記他の絶縁体膜をCVDで形成することを特徴とする半導体装置の製造方法が得られる。

**【 0 0 4 4 】**

本発明によれば、前記導電体層の一部をゲート電極とし、該ゲート電極上の前記絶縁体塗布膜をゲート絶縁膜の少なくとも一部とし、前記半導体層を前記ゲート絶縁膜上に設けることを特徴とする半導体装置の製造方法が得られる。 40

**【 0 0 4 5 】**

本発明によれば、前記半導体層にソース電極およびドレイン電極の少なくとも一方を形成する工程をさらに含むことを特徴とする半導体装置の製造方法が得られる。

**【 0 0 4 6 】**

本発明によれば、基板上に溝を有する絶縁体層を設ける工程と、該溝中にその表面が前記絶縁体層の表面とほぼ平坦になるようにゲート電極を形成する工程と、該ゲート電極上に絶縁体塗布膜を形成する工程と、前記絶縁体塗布膜上にCVDで誘電体膜を形成する工 50

程と、前記誘電体膜上に半導体層を形成する工程と、該半導体層にソース電極およびドレイン電極の少なくとも一方を電気的に接続する工程とを有することを特徴とする半導体装置の製造方法が得られる。

#### 【0047】

本発明によれば、前記絶縁体塗布膜を形成する工程は、金属有機化合物および金属無機化合物の少なくとも一方と溶媒とを含む液体状の材料を前記ゲート電極上に塗布する工程と、塗布した膜を乾燥する工程と、乾燥した膜を焼成する工程とを含むことを特徴とする半導体装置の製造方法が得られる。

#### 【0048】

本発明によれば、前記ゲート電極を形成する工程が、導電金属層をめっき法、印刷法またはインクジェットによる塗布法により形成する工程と、その上に導電金属拡散抑止層をめっき法、印刷法またはインクジェットによる塗布法により形成する工程と含むことを特徴とする半導体装置の製造方法が得られる。 10

#### 【0049】

本発明によれば、前記絶縁体塗布膜を形成する工程が、前記液体状の材料を前記ゲート電極と前記絶縁体層との間の隙間を埋め、かつ前記絶縁体層の表面上に延在するように塗布する工程を含むことを特徴とする半導体装置の製造方法が得られる。

#### 【0050】

本発明によれば、前記基板上に溝を有する絶縁体層を設ける工程が、前記基板上に樹脂膜を形成する工程と、該樹脂膜をパターニングすることで前記ゲート電極を収容すべき溝を形成する工程とを含むことを特徴とする半導体装置の製造方法が得られる。 20

#### 【0051】

本発明によれば、前記焼成を不活性ガス雰囲気中または大気雰囲気中で行うことを特徴とする半導体装置の製造方法が得られる。

#### 【0052】

本発明によれば、上記した方法を用いて半導体装置を形成する工程を有することを特徴とする液晶表示装置または有機EL表示装置の製造方法が得られる。

#### 【0053】

本発明によれば、前記導電金属層はCuおよびAgの少なくとも一つを含み、前記導電金属拡散抑止層はNi、W、Ta、Nb、及びTiのいずれかから選択される金属を含んでなることを特徴とする半導体装置が得られる。 30

#### 【発明の効果】

#### 【0054】

本発明によれば、表面の粗いゲート電極上に絶縁体塗布膜を設けることによってその表面の平坦度をRaで1nm以下、ピーク・トゥ・バレイ値で20nm以下にすることができ、その結果、ゲート絶縁膜の表面を平坦化し、チャンネル領域との界面が平坦となってキャリアの界面散乱を防ぎ、高いキャリア移動度を達成することができる。また、ゲート電極とその周囲の絶縁層との間の隙間を埋めゲート電極上から絶縁層表面上にわたって平坦な表面を提供し、ゲート絶縁膜の破壊を防止することができる。

#### 【発明を実施するための最良の形態】

#### 【0055】

本発明の実施例1について図を用いて説明する。

#### 【実施例1】

#### 【0056】

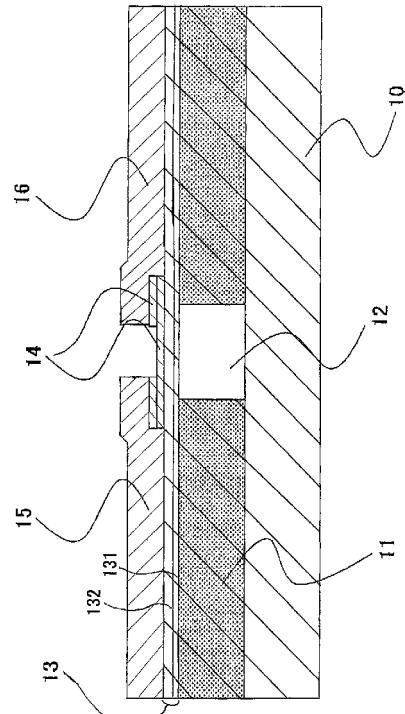

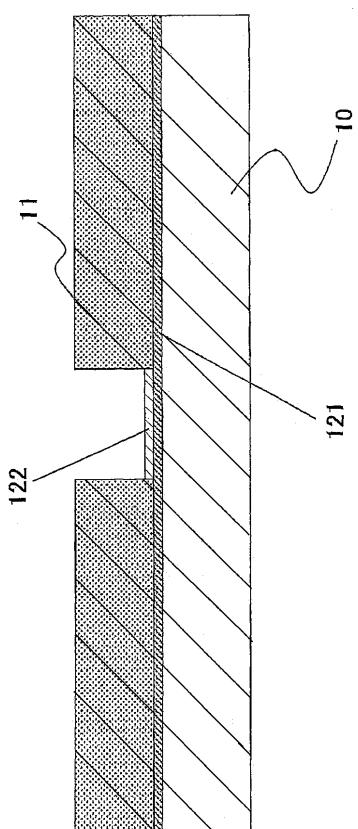

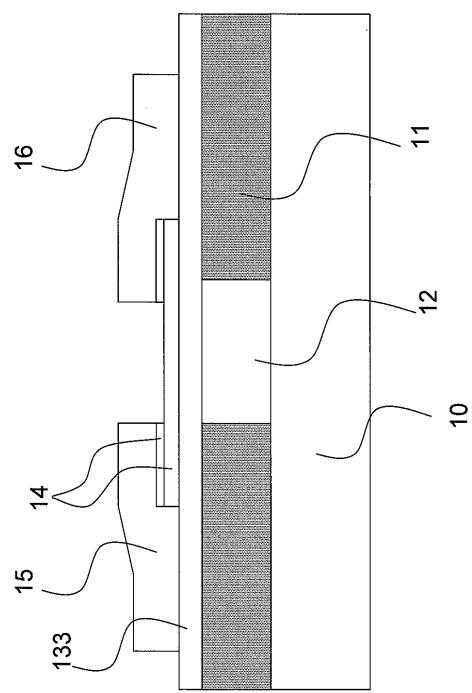

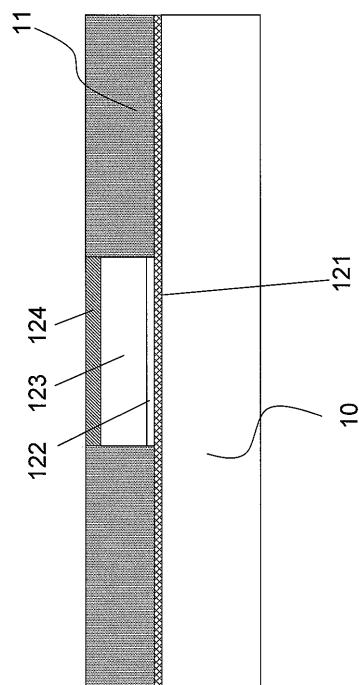

図1は本発明の薄膜トランジスタ(TFT)の構造の一例を示す断面図である。図1を参照すると、ガラス基板(絶縁基板)10上に形成された透明感光性樹脂からなる透明樹脂膜11と、該透明樹脂膜11にガラス基板10に達するように形成され、該透明樹脂膜11と略同一の高さまで形成されたゲート電極12と、該透明樹脂膜11と該ゲート電極12上にわたって形成された絶縁体塗布膜131およびその上のCVD誘電体膜132とかなるゲート絶縁膜13と、該ゲート電極12上に該ゲート絶縁膜13を介して形成され 40

10

20

30

40

50

てなる半導体層 14 と、該半導体層 14 に接続されたソース電極 15 とドレイン電極 16 とを有している。

#### 【0057】

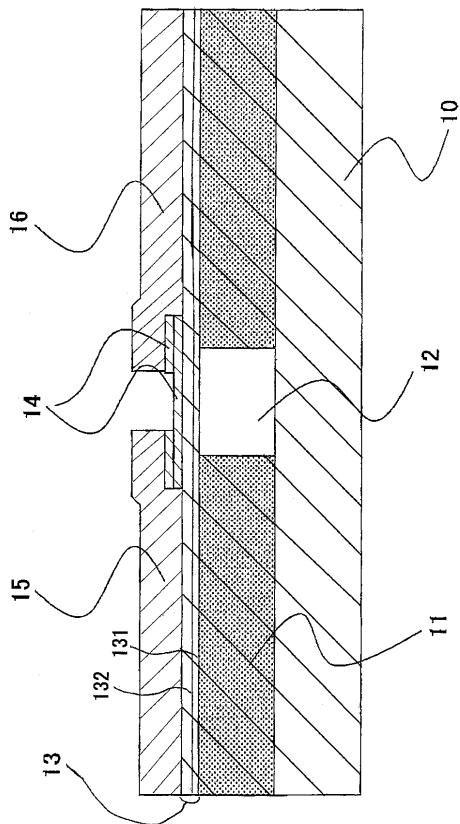

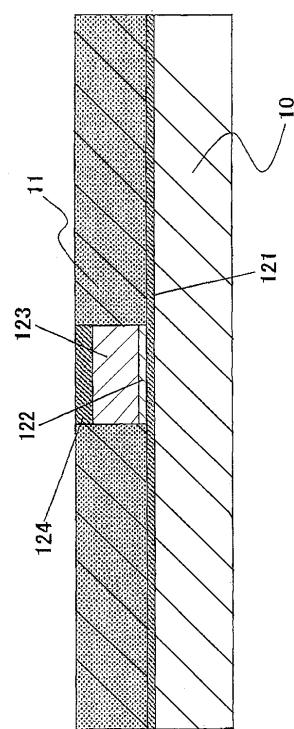

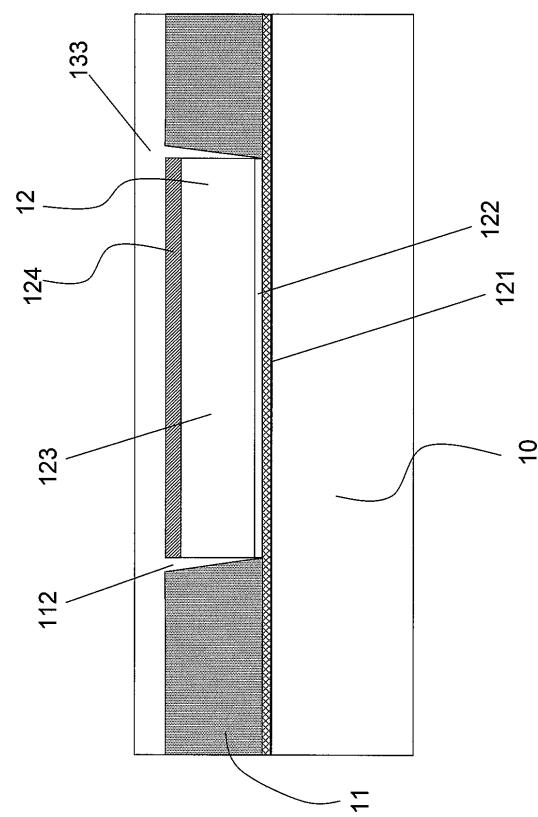

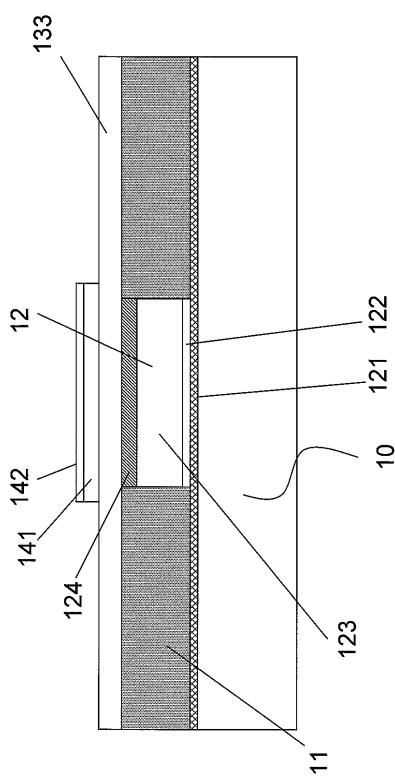

図2は本実施例1に係る薄膜トランジスタのゲート電極部の構造を拡大して示した断面図である。図示されたゲート電極12は、ガラス基板10側から半導体層側に向かって(即ち、図の下から順に)下地密着層121、触媒層122、導電金属層123、導電金属拡散抑止層124によって構成され、当該ゲート電極12は平坦な透明樹脂膜11に形成された溝中に埋設されている。図示されているように、ゲート電極12の表面と透明樹脂膜11とは略同一平面を形成するように、透明樹脂膜の溝に埋設されている。このため、ゲート電極12の上部構造の平坦性は確保されるが、ミクロに見た場合の平坦性に問題がある。すなわち、無電解めっきによる導電金属層123(Cu層)表面の平坦度はRaで17.74nm、ピーク・トウ・バレイ値で193.92nmにも達し、その上に形成された導電金属拡散抑止層124(無電解めっきNi層)表面も平坦度はRaで8.58nm、ピーク・トウ・バレイ値で68.7nmである。

10

#### 【0058】

本発明では、その上に厚さ40nmの絶縁体塗布膜131が形成され、この膜がゲート電極12と樹脂膜11との間の隙間112を埋めるとともに、ゲート電極表面の凹凸を反映しない、Raで0.24nm、ピーク・トウ・バレイ値で2.16nmという平坦な表面を提供する。

20

#### 【0059】

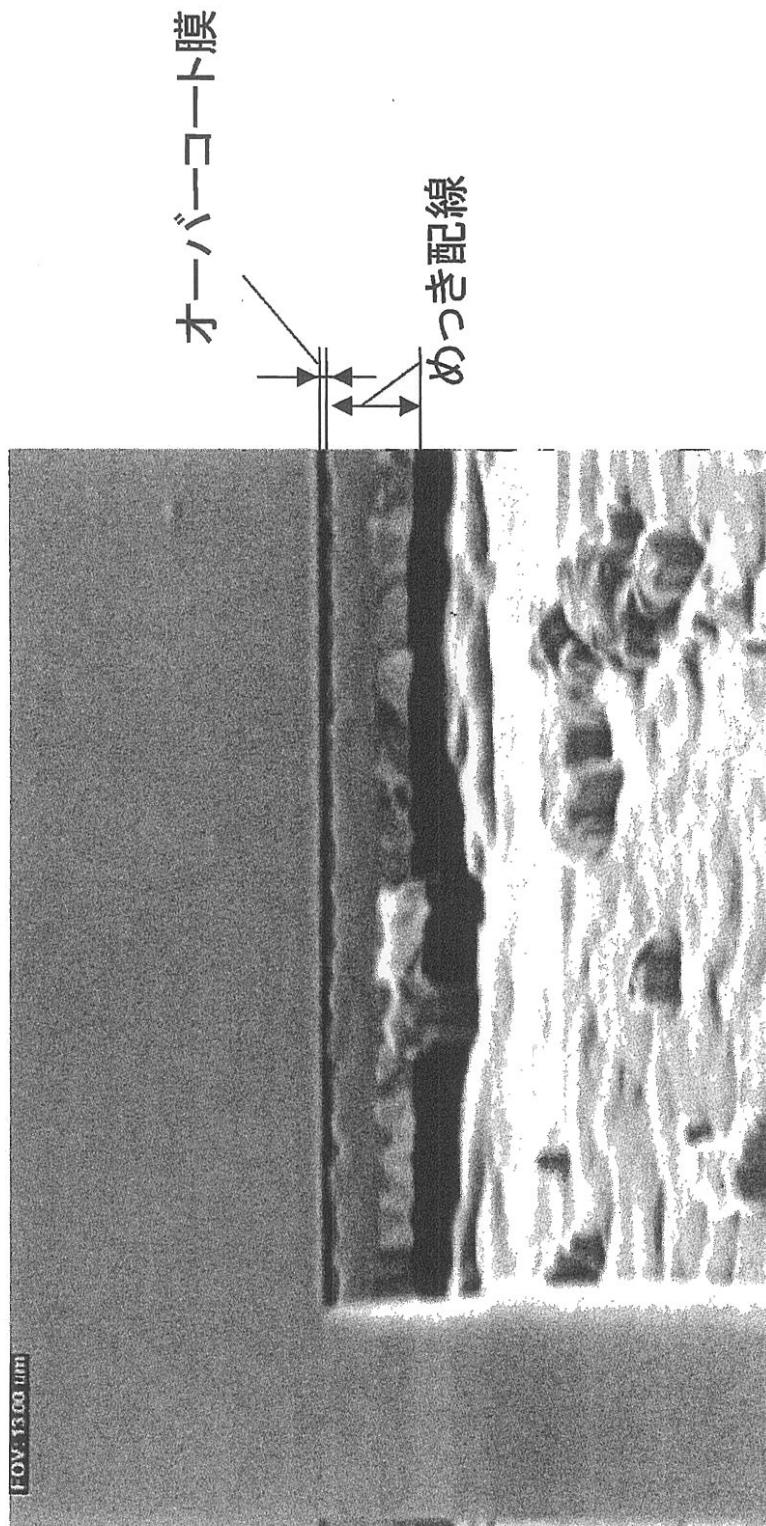

図8は、めっき配線によるゲート電極上に絶縁体塗布膜(オーバーコート膜)を形成した構成をFIB加工により断面を観察した状況を示す電子顕微鏡写真である。図8に示すように、下地のラフネスに依存せず平坦な表面を形成していることがわかる。

20

#### 【0060】

この結果、絶縁体塗布膜(オーバーコート膜)131上にCVDにより形成された厚さ150~160nmの窒化シリコン誘電体膜132の表面は、Raで0.70nm、ピーク・トウ・バレイ値で7.54nmという平坦性を得ることが出来た(図2)。この結果、ゲート絶縁膜13上に形成される半導体層にゲート電極に起因する凹凸を生じることなく薄膜トランジスタ(TFT)を形成できるため、移動度の大幅な向上が可能となった。

30

#### 【0061】

なお、絶縁体塗布膜(オーバーコート膜)131としては、SOG(スピンドルガラス)を用いることが出来る。SOG膜は膜となるシロキサン成分と溶媒としてのアルコール成分などから調整される。この溶液をスピンドル法によって基板上に塗布し、熱処理で溶媒などを蒸発させ膜を硬化させるとSOG絶縁膜が形成される。SOGとは、これら溶液と形成される膜の総称である。SOGは、シロキサンの構造により、シリカガラス、アルキルシロキサンポリマー、アルキルシリセスキオキサンポリマー(MSQ)、水素化シリセスキオキサンポリマー(HSQ)、水素化アルキルシリセスキオキサンポリマー(HOSQ)に分類される。塗布材で分類すると、シリカガラスは第1世代無機SOG、アルキルシロキサンポリマーは第1世代有機SOG、HSQは第2世代の無機SOG、MSQとHOSQは第2世代有機SOGになる。また、塗布膜について説明すると、これらは500以上で焼成することが多いが、いずれにしても透明樹脂層を使うときは高温にすることができないので、焼成温度が300以下のものを用いる。また、以上のようなSiの有機化合物、Siの無機化合物の代わりに他の有機金属化合物又は金属無機化合物を有機溶媒に溶解したもの(特に、焼成温度が300以下のもの)を用いることができる。他の金属としては、Ti、Ta、Al、Sn、Zr等を例示することができる。

40

#### 【0062】

ここで、絶縁体塗布膜131およびその上のCVD誘電体膜132とからなるゲート絶縁膜13の厚さとしては、厚すぎるとトランジスタの駆動能力が悪化し、またゲート容量が増加して信号遅延を招くことから、窒化シリコン膜であれば350~360nm程度以下、EOT(膜の平均誘電率で二酸化シリコンの誘電率を割った商に膜厚を掛けて得られ

50

た二酸化シリコン換算膜厚)で200 nm以下が好ましい。また、その厚さが薄すぎるとリーク電流が増すこと、通常のLCDであれば最大15Vの電圧が TFT のゲート・ソース間にかかるので耐圧15V以上であることが好ましいことから、EOTで95 nm以上あることが好ましい。

#### 【0063】

絶縁体塗布膜131の厚さは、下地のラフネスに依存せず平坦な表面を得るために(下地の表面粗さがP-Vで30 nm程度であれば)その物理膜厚が最低40 nmは必要である。この膜の誘電率はさまざまありうるが、誘電率が最大10程度であることを考えるとEOTで15 nm以上とすることが好ましい。また、最高膜厚は120 nm程度以下が好ましい。

10

#### 【0064】

CVD誘電体膜132の厚さは、耐圧をこの膜で主に引き受けることを考慮すると、EOTで80 nm以上が好ましい。その上限は、200 nm - 15 nm = 185 nmとするのが好ましい。

#### 【0065】

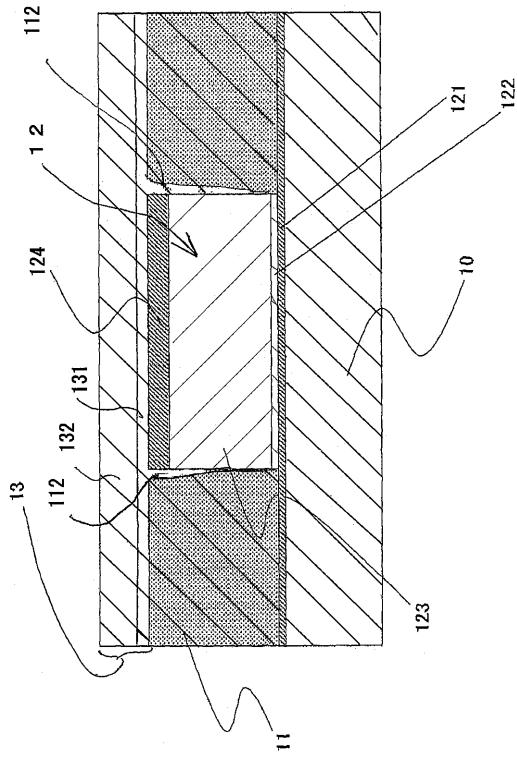

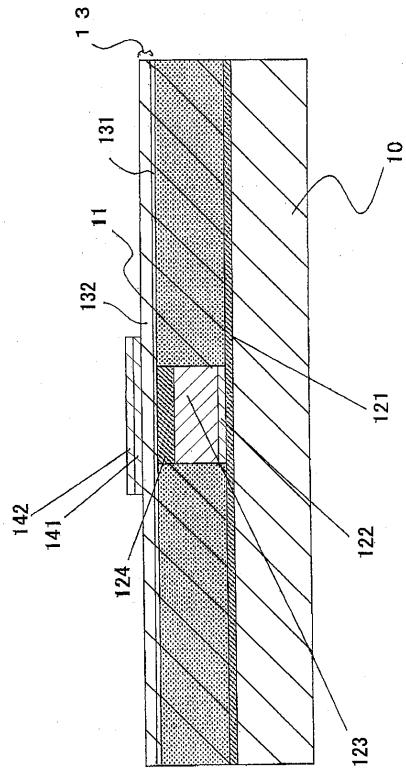

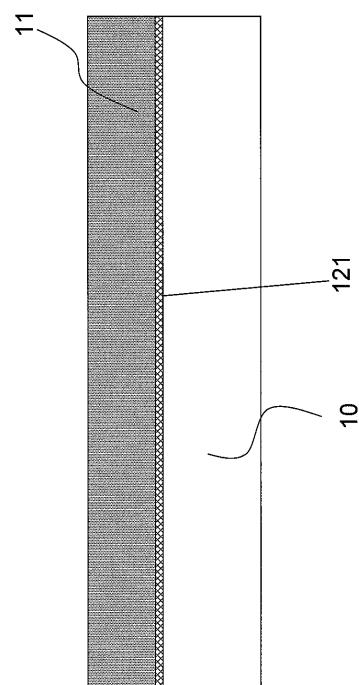

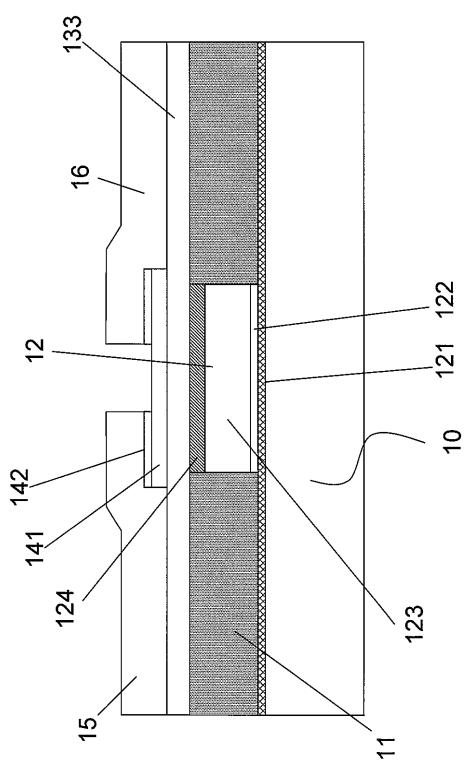

次に、上記のような本実施例1の薄膜トランジスタの形成方法について図を用いて説明する。図3～図7は本実施例1に係る薄膜トランジスタの製造方法を工程順に示す模式図である。まず、図3を参照すると、基板としてガラス基板10を用意する。このガラス基板としては30インチ以上の大型画面を形成できるような大型の基板でも良い。このガラス基板を0.5体積%のフッ酸水溶液で10秒間処理し、純水で水洗して表面の汚染をリフトオフ除去する。次に、ガラス基板10を、水酸化ナトリウムを純水に添加することによりpHを10に制御した水溶液に0.1体積%の濃度でシランカップリング剤であるアミノプロピルエトキシシランを溶解したシランカップリング剤溶液で処理、即ち、該シランカップリング剤溶液に室温で30分間浸漬し、ガラス基板表面にシランカップリング剤を吸着させた。その後、ホットプレート上で、110、60分処理し、ガラス基板表面にシランカップリング剤を化学結合させ、下地密着層(厚さ10 nm)121とした。このように、下地密着層を形成することにより、基板表面に実質的にアミノ基が配置され、金属錯体が配位しやすい構造を作ることができる。シランカップリング剤は、通常、透明であるため、ガラス基板全面に渡って形成しても、本発明の効果を得ることが可能であり、更に、ガラス基板と後の工程で用いる透明感光性樹脂の密着性を得る観点から好ましい。

20

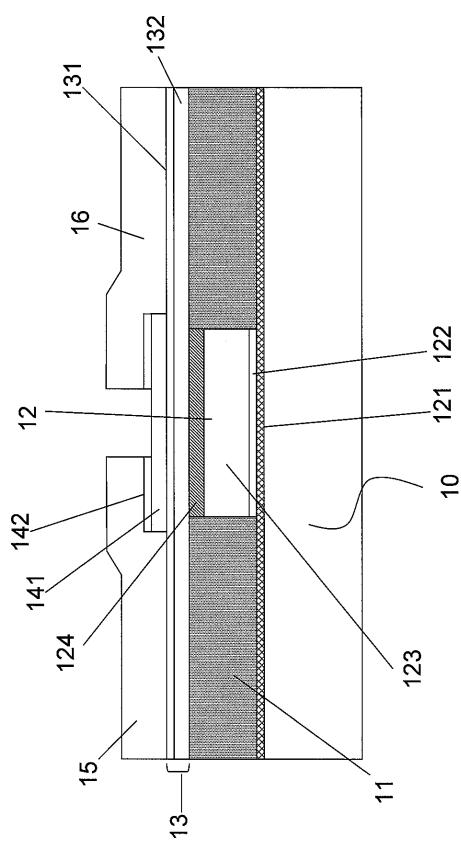

#### 【0066】

下地密着層121形成後、下地密着層の表面にポジ型フォトレジスト液を、スピナーを用いて塗布し、ホットプレート上で、100で120秒間加熱ブリベーカー処理することにより、2 μmの厚さを有する感光性透明樹脂膜11を形成した。尚、上記したポジ型フォトレジストは、特開2002-296780号公報に記載されたアルカリ可溶性脂環式オレフィン系樹脂を含有したものを使用した。透明膜を形成する有機材料としては、アクリル系樹脂、シリコーン系樹脂、フッ素系樹脂、ポリイミド系樹脂、ポリオレフィン系樹脂、脂環式オレフィン樹脂、およびエポキシ系樹脂からなる群から選ばれた透明樹脂が使用可能である。しかし、以降の工程を容易にする観点で、透明膜としては、感光性透明樹脂膜は好都合であり、特に、特開2001-188343号公報あるいは特開2002-296780号公報に詳述されたような感光性透明樹脂組成物を使用するのが好ましい。

30

#### 【0067】

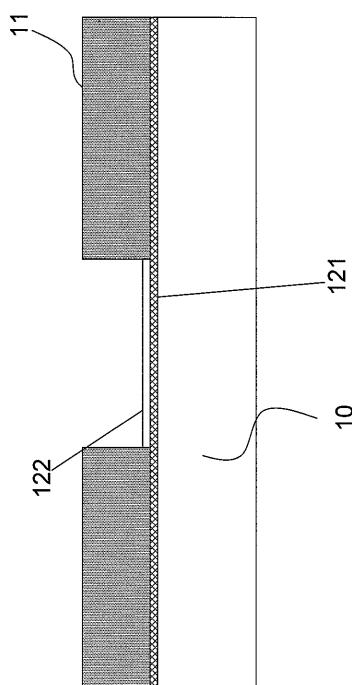

図4を参照すると、感光性透明樹脂膜11の形成後、マスクアライナーにより、マスクパターンを介して、g、h、i線の混合光を感光性透明樹脂膜に選択的に照射した。その後、0.3重量%テトラメチルアンモニウムヒドロキシド水溶液で90秒間現像した後、純水で60秒間リノス処理を行い、ガラス基板上に所定のパターンを有する溝を形成した。その後、窒素雰囲気中で230、60分の熱処理をし、感光性透明樹脂膜11を硬化した。次に、これを塩化パラジウム-塩酸水溶液(塩化パラジウム0.005体積%、塩酸0.01体積%)に室温で3分間、浸漬し、還元剤(上村工業(株)製レデューサーM

40

50

A B - 2 ) で処理し水洗することで、形成された溝内に選択的にパラジウム触媒（厚さ 10 ~ 50 nm）122 を付与した。

#### 【0068】

図 5 を参照すると、パラジウム触媒 122 を付与した基板を、銅無電解めっき液（上村工業（株）製 P G T ）に浸漬し、前述の溝内に選択的に銅層 124（厚さ 1.9 μm ）を形成した。銅層は、続く拡散抑止膜 124 の膜厚の分だけ、透明感光性樹脂 11 の表面高さより低い位置で処理を終了することが好ましい。次に、ニッケル無電解めっき液に浸漬し、銅層 124 上にニッケルの拡散抑止膜 124（厚さ 0.1 μm ）を形成した。

#### 【0069】

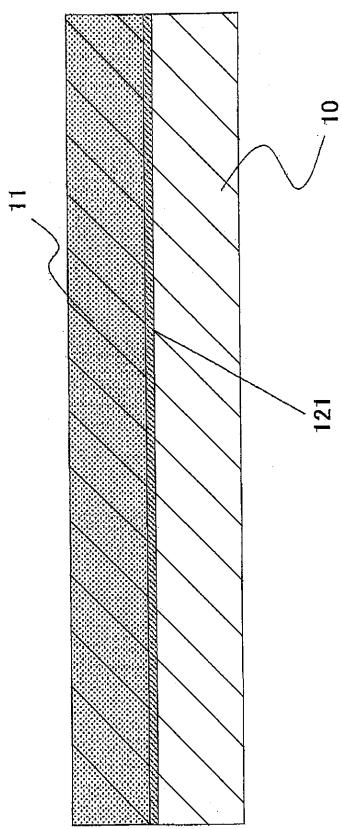

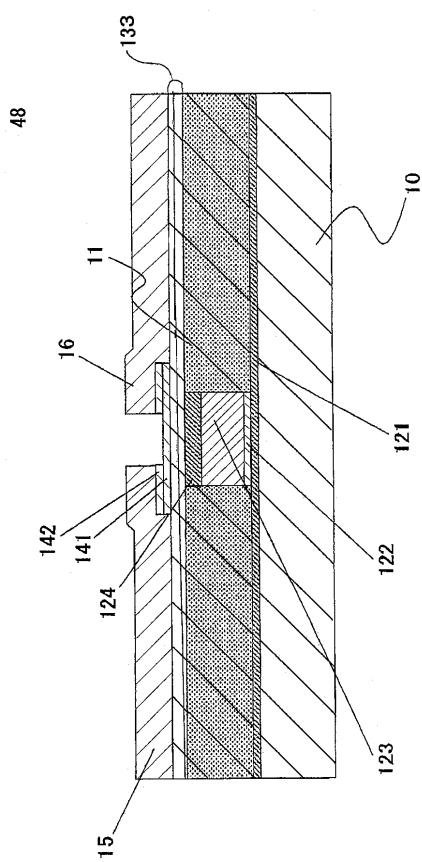

図 6 を参照すると、次にゲート電極 12 の表面から透明樹脂膜 11 の表面にわたって延在するように、絶縁体塗布膜 131 を形成した。この膜は、Si 有機化合物であるオルガノシロキサンを有機溶媒（プロピレングリコールモノメチルエーテル）に溶かした液体を塗布し、120 にて大気中で 90 秒間保って乾燥させ、次いで大気中（窒素ガス中でもよい）180 で 1 時間焼成して得たものである。次に、マイクロ波励起 R L S A プラズマ処理装置にて Si<sub>3</sub>N<sub>4</sub> 膜 132 を C V D 成長させ、ゲート絶縁膜 13 を作成した。次に公知の P E C V D 法によりアモルファスシリコン膜 141、n+ 型アモルファスシリコン膜 142 を連続堆積し、フォトリソグラフィー法および公知の RIE 法によりゲート電極 12 上およびその周辺部を除いてアモルファスシリコン膜を一部除去した。

#### 【0070】

図 7 を参照すると、引き続き、公知のスパッタ法などにより、ソース電極およびドレイン電極とすべく、Ti、Al、Ti の順で成膜を行い、フォトリソグラフィー法でパターニングを行うことによって、ソース電極 15 およびドレイン電極 16 を形成した。次に、形成されたソース電極 15 およびドレイン電極 16 をマスクとして、公知の手法により n+ 型アモルファスシリコン膜 142 をエッチングすることで、ソース領域とドレイン領域の分離を行った。次に、公知の P E C V D 法により、保護膜としてシリコン窒化膜（図示せず）を形成して、本発明の薄膜トランジスタを完成した。

#### 【実施例 2】

#### 【0071】

本発明の実施例 2 について図を用いて説明する。図 9 は本発明の実施例 2 による薄膜トランジスタ（TFT）の構造を示す断面図であり、ガラス基板（絶縁基板）10 上に形成された透明感光性樹脂からなる透明樹脂膜 11 と、該透明樹脂膜 11 にガラス基板 10 に達するように形成され、該透明樹脂膜と略同一の高さまで形成されたゲート電極 12 と、該透明樹脂 11 と該ゲート電極 12 上にわたって形成された絶縁体塗布膜からなるゲート絶縁膜 133 と、該ゲート電極 12 上に該ゲート絶縁膜 133 を介して形成されてなる半導体層 14 と、該半導体層 14 に接続されたソース電極 15 とドレイン電極 16 とを有している。

#### 【0072】

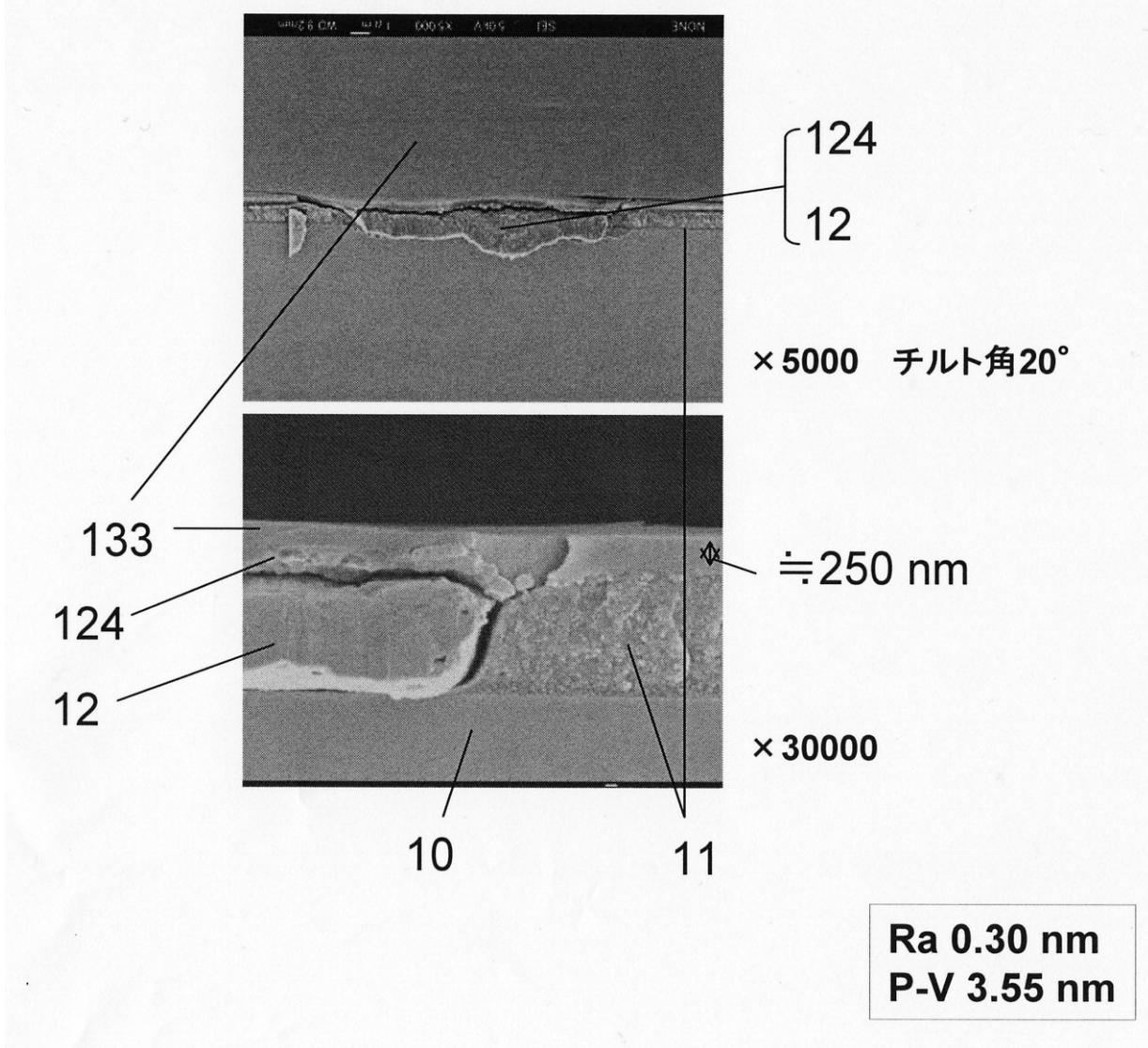

図 10 は本実施例 2 に係る薄膜トランジスタのゲート電極部の構造を拡大して示した断面図である。図示されたゲート電極 12 は、ガラス基板 10 側から半導体層側に向かって（即ち、図の下から順に）下地密着層 121、触媒層 122、導電金属層 123、導電金属拡散抑止層 124 によって構成され、当該ゲート電極 12 は平坦な透明樹脂膜 11 に形成された溝中に埋設されている。図示されているように、ゲート電極 12 の表面と透明樹脂膜 11 とは略同一平面を形成するように、透明樹脂膜の溝に埋設されている。このため、ゲート電極 12 の上部構造の平坦性は確保されるが、ミクロに見た場合の平坦性に問題がある。すなわち、無電解めっきによる導電金属層 123（Cu 層）表面の平坦度は Ra で 17.74 nm、ピーク・トウ・バレイ値で 193.92 nm にも達し、その上に形成された導電金属拡散抑止層 124（無電解めっき Ni 層）表面も平坦度は Ra で 8.58 nm、ピーク・トウ・バレイ値で 68.7 nm である。

#### 【0073】

本発明では、導電金属拡散抑止層 124 上に厚さ 250 nm の絶縁体塗布膜 133 を形

10

20

30

40

50

成し、この膜 133 によってゲート電極 12 と樹脂膜 11 との間の隙間 112 を埋めるとともに、ゲート電極表面の凹凸を反映しない、Ra で 0.30 nm、ピーク・トウ・パレイ値で 3.55 nm という平坦な表面を有するゲート絶縁膜を提供することができた。図 13 は、このようなゲート電極上に絶縁体塗布膜によるゲート絶縁膜を形成した構成の断面を観察した状況を示す電子顕微鏡写真である。図 13 に示すように、下地のラフネスに依存せず平坦な表面を形成していることがわかる。

#### 【0074】

この結果、ゲート絶縁膜上に形成される半導体層にゲート電極に起因する凹凸を生じることなく薄膜トランジスタ ( TFT ) を形成できるため、移動度の大幅な向上が可能となり、更に、ゲート絶縁膜の成膜工程において CVD 工程を省略し、簡易な塗布型で成膜することで工程の簡略化が実現できた。10

#### 【0075】

次に、上記のような本実施例 2 の薄膜トランジスタの形成方法について図を用いて説明する。図 11 (a) ~ (e) は本実施例 1 に係る薄膜トランジスタの製造方法を工程順に示す模式図である。まず、図 11 (a) を参照すると、基板としてガラス基板 10 を用意する。このガラス基板としては 30 インチ以上の大型画面を形成できるような大型の基板でも良い。このガラス基板を 0.5 体積 % のフッ酸水溶液で 10 秒間処理し、純水で水洗して表面の汚染をリフトオフ除去する。次に、ガラス基板 10 を、水酸化ナトリウムを純水に添加することにより pH を 10 に制御した水溶液に 0.1 体積 % の濃度でシランカップリング剤であるアミノプロピルエトキシシランを溶解したシランカップリング剤溶液で処理、即ち、該シランカップリング剤溶液に室温で 30 分間浸漬し、ガラス基板表面にシランカップリング剤を吸着させた。その後、ホットプレート上で、110 ~ 60 分処理し、ガラス基板表面にシランカップリング剤を化学結合させ、下地密着層 ( 厚さ 10 nm ) 121 とした。このように、下地密着層を形成することにより、基板表面に実質的にアミノ基が配置され、金属錯体が配位しやすい構造を作ることができる。シランカップリング剤は、通常、透明であるため、ガラス基板全面に渡って形成しても、本発明の効果を得ることが可能であり、更に、ガラス基板と後の工程で用いる透明感光性樹脂の密着性を得る観点から好ましい。20

#### 【0076】

下地密着層 121 形成後、下地密着層の表面にポジ型フォトレジスト液を、スピナーを用いて塗布し、ホットプレート上で、100 ~ 120 秒間加熱ブリベーク処理することにより、2 μm の厚さを有する感光性透明樹脂膜 11 を形成した。尚、上記したポジ型フォトレジストは特開 2002-296780 号公報に記載されたアルカリ可溶性脂環式オレフィン系樹脂を含有したものを使用した。透明膜を形成する有機材料としては、アクリル系樹脂、シリコーン系樹脂、フッ素系樹脂、ポリイミド系樹脂、ポリオレフィン系樹脂、脂環式オレフィン樹脂、およびエポキシ系樹脂からなる群から選ばれた透明樹脂が使用可能である。しかし、以降の工程を容易にする観点で、透明膜としては、感光性透明樹脂膜は好都合であり、特に、特開 2001-188343 号公報あるいは特開 2002-296780 号公報に詳述されたような感光性透明樹脂組成物を使用するのが好ましい。30

#### 【0077】

図 11 (b) を参照すると、感光性透明樹脂膜 11 の形成後、マスクアライナーにより、マスクパターンを介して、g、h、i 線の混合光を感光性透明樹脂膜に選択的に照射した。その後、0.3 重量 % テトラメチルアンモニウムヒドロキシド水溶液で 90 秒間現像した後、純水で 60 秒間リヌス処理を行い、ガラス基板上に所定のパターンを有する溝を形成した。その後、窒素雰囲気中で 230 ~ 60 分の熱処理をし、感光性透明樹脂膜 11 を硬化した。次に、これを塩化パラジウム - 塩酸水溶液 ( 塩化パラジウム 0.005 体積 % 、塩酸 0.01 体積 % ) に室温で 3 分間、浸漬し、還元剤 ( 上村工業 ( 株 ) 製レデューサー MAB-2 ) で処理し水洗することで、形成された溝内に選択的にパラジウム触媒 ( 厚さ 10 ~ 50 nm ) 122 を付与した。40

#### 【0078】

10

20

30

40

50

図11(c)を参照すると、パラジウム触媒122を付与した基板を、銅無電解めっき液(上村工業(株)製PGT)に浸漬し、前述の溝内に選択的に銅層123(厚さ1.9μm)を導電金属層として形成した。銅層123は、続く拡散抑止膜124の膜厚の分だけ、透明感光性樹脂11の表面高さより低い位置で処理を終了することが好ましい。次に、ニッケル無電解めっき液に浸漬し、銅層123上にニッケルの拡散抑止膜124(厚さ0.1μm)を形成した。

#### 【0079】

図11(d)を参照すると、次にゲート電極12の表面から透明樹脂膜11の表面にわたって延在するように、絶縁体膜を塗布し、ゲート絶縁膜133を形成した。この膜は、Si有機化合物であるオルガノシロキサンを有機溶媒(プロピレングリコールモノメチルエーテル)に溶かした液体を塗布し、120にて大気中で90秒間保って乾燥させ、次いで大気中(窒素ガス中でもよい)180で1時間焼成して得たものである。次に公知のPECVD法によりアモルファスシリコン膜141、n+型アモルファスシリコン膜142を連続堆積し、フォトリソグラフィー法および公知のRIE法によりゲート電極12上およびその周辺部を除いてアモルファスシリコン膜を一部除去した。

10

#### 【0080】

図11(e)を参照すると、引き続き、公知のスパッタ法などにより、ソース電極およびドレイン電極とすべく、Ti、Al、Tiの順で成膜を行い、フォトリソグラフィー法でパターニングを行うことによって、ソース電極15およびドレイン電極16を形成した。次に、形成されたソース電極15およびドレイン電極16をマスクとして、公知の手法によりn+型アモルファスシリコン膜142をエッチングすることで、ソース領域とドレイン領域の分離を行った。次に、公知のPECVD法により、保護膜としてシリコン窒化膜(図示せず)を形成して、本発明の薄膜トランジスタを完成した。

20

#### 【実施例3】

#### 【0081】

実施例2で説明した薄膜トランジスタの製造方法において、銅層123上にニッケルの拡散抑止膜124(厚さ0.1μm)を形成し、ゲート電極12を形成した後、ゲート電極12の表面から透明樹脂膜11の表面の全領域に渡って、マイクロ波励起RLSAプラズマ処理装置にてSi<sub>3</sub>N<sub>4</sub>膜132をCVD成長させ、絶縁膜を形成した。次に絶縁体塗布膜131を該Si<sub>3</sub>N<sub>4</sub>膜上全体にわたって塗布し、ゲート絶縁膜13を形成した。この膜は、Si有機化合物であるオルガノシロキサンを有機溶媒(プロピレングリコールモノメチルエーテル)に溶かした液体を塗布し、120にて大気中で90秒間保って乾燥させ、次いで大気中(窒素ガス中でもよい)180で1時間焼成して得たものである。該塗布型絶縁膜により、表面粗さの大きいゲート電極12上へCVDしたことにより生じた絶縁膜表面の表面粗さを低減することができ、チャンネル層であるゲート絶縁膜と半導体層との界面のラフネスを低減することができた。このときの薄膜トランジスタの断面図を図12に示す。

30

#### 【0082】

尚、上記した実施形態では、液晶表示装置についてのみ説明したが、本発明は平面ディスプレイパネルを構成する各種基板、その他配線基板に適用できる。

40

#### 【0083】

また、配線を構成する材料として、銅、銀だけでなく、例えば、インジウムースズオキサイド(ITO)等の金属酸化物のような導電性膜を形成しても良い。

#### 【産業上の利用可能性】

#### 【0084】

本発明は液晶表示装置、有機EL装置、無機EL装置等の表示装置に適用して、これら表示装置を大型化することができると共に、表示装置以外の配線にも適用できる。

#### 【図面の簡単な説明】

#### 【0085】

【図1】本発明に係る薄膜トランジスタの構造の一例を示す断面図である。

50

【図2】本発明に係る薄膜トランジスタのゲート電極部の構造の一例を拡大して示す断面図である。

【図3】本発明に係る薄膜トランジスタの製造方法の一例を工程順に説明する断面図である。

【図4】本発明に係る薄膜トランジスタの製造方法の一例を工程順に説明する断面図である。

【図5】本発明に係る薄膜トランジスタの製造方法の一例を工程順に説明する断面図である。

【図6】本発明に係る薄膜トランジスタの製造方法の一例を工程順に説明する断面図である。

【図7】本発明に係る薄膜トランジスタの製造方法の一例を工程順に説明する断面図である。

【図8】本発明に係るオーバーコート膜のFIB断面を示す写真である。

【図9】本発明の実施例2の薄膜トランジスタの構造の一例を示す断面図である。

【図10】本発明の実施例2の薄膜トランジスタのゲート電極部の構造の一例を拡大して示す断面図である。

【図11(a)】本発明の実施例2の薄膜トランジスタの製造方法の一例を工程順に説明する断面図である。

【図11(b)】本発明の実施例2の薄膜トランジスタの製造方法の一例を工程順に説明する断面図である。

【図11(c)】本発明の実施例2の薄膜トランジスタの製造方法の一例を工程順に説明する断面図である。

【図11(d)】本発明の実施例2の薄膜トランジスタの製造方法の一例を工程順に説明する断面図である。

【図11(e)】本発明の実施例2の薄膜トランジスタの製造方法の一例を工程順に説明する断面図である。

【図12】本発明の実施例3の薄膜トランジスタの構造の一例を示す断面図である。

【図13】本発明の実施例2に係るオーバーコート膜の断面を示す写真である。

#### 【符号の説明】

##### 【0086】

10 : ガラス基板(透明基体)

11 : 透明樹脂膜

121 : 下地密着層

122 : 触媒層

123 : 導電金属層

124 : 導電金属拡散抑止膜

13 : ゲート絶縁膜

131 : 絶縁体塗布膜

132 : CVD誘電体膜

14 : 半導体層

141 : アモルファスシリコン膜

142 : n+型アモルファスシリコン膜

15 : ソース電極

16 : ドレイン電極

11 : 感光性透明樹脂膜

121 : 下地密着層

122 : パラジウム触媒

123 : 銅層

124 : 拡散抑止膜

133 : 塗布型ゲート絶縁膜

10

20

30

40

50

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図9】

【図 10】

【図 11(a)】

【図 11(b)】

【図 11(c)】

【図11(d)】

【図11(e)】

【図12】

【図 8】

## オーバーコート膜 FIB断面図

【図13】

## SEM断面図

---

フロントページの続き

F ターム(参考) 4M104 AA09 BB04 BB14 CC01 CC05 DD09 DD15 DD37 DD53 EE03

EE06 FF13 GG09 GG10 GG14 HH05 HH08 HH12

5F110 AA01 AA12 AA18 AA28 BB01 CC07 DD02 DD12 DD21 DD25

EE02 EE15 EE42 FF01 FF02 FF03 FF05 FF09 FF27 FF30

GG02 GG15 GG45 HK03 HK04 HK09 HK16 HK22 HK33 HK35

NN24 NN35 QQ09 QQ14