(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4170996号

(P4170996)

(45) 発行日 平成20年10月22日(2008.10.22)

(24) 登録日 平成20年8月15日(2008.8.15)

(51) Int.Cl.

F 1

|             |              |                  |             |              |

|-------------|--------------|------------------|-------------|--------------|

| <b>H03F</b> | <b>3/30</b>  | <b>(2006.01)</b> | <b>H03F</b> | <b>3/30</b>  |

| <b>H03F</b> | <b>1/56</b>  | <b>(2006.01)</b> | <b>H03F</b> | <b>1/56</b>  |

| <b>H03F</b> | <b>3/34</b>  | <b>(2006.01)</b> | <b>H03F</b> | <b>3/34</b>  |

| <b>GO1R</b> | <b>31/28</b> | <b>(2006.01)</b> | <b>GO1R</b> | <b>31/28</b> |

Z

H

請求項の数 8 (全 16 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2005-34686 (P2005-34686)    |

| (22) 出願日  | 平成17年2月10日 (2005.2.10)        |

| (65) 公開番号 | 特開2006-222770 (P2006-222770A) |

| (43) 公開日  | 平成18年8月24日 (2006.8.24)        |

| 審査請求日     | 平成20年1月22日 (2008.1.22)        |

|           |                                              |

|-----------|----------------------------------------------|

| (73) 特許権者 | 390005175<br>株式会社アドバンテスト<br>東京都練馬区旭町1丁目32番1号 |

| (74) 代理人  | 100104156<br>弁理士 龍華 明裕                       |

| (72) 発明者  | 小寺 悟司<br>東京都練馬区旭町1丁目32番1号 株式会社アドバンテスト内       |

審査官 野元 久道

最終頁に続く

(54) 【発明の名称】電力增幅回路、及び試験装置

## (57) 【特許請求の範囲】

## 【請求項 1】

与えられる入力電圧に応じた出力電圧を出力する電力增幅回路であって、直列に接続され、接続点における電圧を前記出力電圧として出力する正側出力抵抗及び負側出力抵抗と、

ソース端子が前記正側出力抵抗に接続され、ゲート端子に与えられる電圧に応じた電流を前記正側出力抵抗に流す正側トランジスタと、

ソース端子が前記負側出力抵抗に接続され、ゲート端子に与えられる電圧に応じた電流を前記負側出力抵抗に流す負側トランジスタと、

前記入力電圧に所定の電圧を加えて正側バイアス電圧を生成する正側バイアス生成部と 10

、 前記入力電圧から前記所定の電圧を減じて負側バイアス電圧を生成する負側バイアス生成部と、

前記正側バイアス電圧と、前記正側トランジスタのソース電圧とが略同一となるように、前記正側トランジスタの前記ゲート端子に印加する電圧を制御する正側制御部と、

前記負側バイアス電圧と、前記負側トランジスタのソース電圧とが略同一となるように、前記負側トランジスタの前記ゲート端子に印加する電圧を制御する負側制御部とを備え、

前記正側バイアス生成部は、

前記入力電圧に所定の電圧を加える昇圧部と、

10

20

前記昇圧部の出力端と、前記正側出力抵抗及び前記負側出力抵抗間の前記接続点との間に直列に設けられ、前記昇圧部が出力する電圧を分圧した電圧を、前記正側バイアス電圧として前記正側制御部に供給する2つの正側分圧抵抗と

を有し、

前記負側バイアス生成部は、

前記入力電圧から前記所定の電圧を減じる降圧部と、

前記降圧部の出力端と、前記正側出力抵抗及び前記負側出力抵抗間の前記接続点との間に直列に設けられ、前記降圧部が出力する電圧を分圧した電圧を、前記負側バイアス電圧として前記負側制御部に供給する2つの負側分圧抵抗と

を有し、

前記2つの正側分圧抵抗の抵抗比、及び前記2つの負側分圧抵抗の抵抗比を制御することにより、前記電力增幅回路の出力インピーダンスを制御する抵抗制御部を更に備える電力增幅回路。

#### 【請求項2】

前記正側制御部は、非反転入力端子に前記正側バイアス電圧を受け取り、反転入力端子に前記正側トランジスタの前記ソース電圧を受け取る増幅器を有し、

前記負側制御部は、非反転入力端子に前記負側バイアス電圧を受け取り、反転入力端子に前記負側トランジスタの前記ソース電圧を受け取る増幅器を有する

請求項1に記載の電力增幅回路。

#### 【請求項3】

前記正側出力抵抗の抵抗値は、前記2つの正側分圧抵抗のそれぞれの抵抗値より小さく、

前記負側出力抵抗の抵抗値は、前記2つの負側分圧抵抗のそれぞれの抵抗値より小さい

請求項1に記載の電力增幅回路。

#### 【請求項4】

前記正側バイアス生成部は、

前記入力電圧に所定の電圧を加える昇圧部と、

コレクタ端子が第1の正側分圧抵抗を介して所定の正電位に接続され、エミッタ端子が第2の正側分圧抵抗を介して前記接続点に接続され、ゲート端子に前記昇圧部が出力する電圧を受け取り、コレクタ電圧を前記正側バイアス電圧として前記正側制御部に供給する正側バイアストランジスタと

を有し、

前記負側バイアス生成部は、

前記入力電圧から前記所定の電圧を減じる降圧部と、

コレクタ端子が第1の負側分圧抵抗を介して所定の負電位に接続され、エミッタ端子が第2の負側分圧抵抗を介して前記接続点に接続され、ゲート端子に前記降圧部が出力する電圧を受け取り、コレクタ電圧を前記負側バイアス電圧として前記負側制御部に供給する負側バイアストランジスタと

を有する

請求項1に記載の電力增幅回路。

#### 【請求項5】

被試験デバイスを試験する試験装置であつて、

前記被試験デバイスに印加すべき入力電圧が与えられ、前記入力電圧に基づいて、前記被試験デバイスに電源電力を供給する電力增幅回路と、

前記電源電力が供給された前記被試験デバイスの動作を検出し、前記被試験デバイスの良否を判定する判定部と

を備え、

前記電力增幅回路は、

直列に接続され、接続点における電圧を電源電圧として前記被試験デバイスに出力する正側出力抵抗及び負側出力抵抗と、

10

20

30

40

50

ソース端子が前記正側出力抵抗に接続され、ゲート端子に与えられる電圧に応じた電流を前記正側出力抵抗に流す正側トランジスタと、

ソース端子が前記負側出力抵抗に接続され、ゲート端子に与えられる電圧に応じた電流を前記負側出力抵抗に流す負側トランジスタと、

前記入力電圧に所定の電圧を加えて正側バイアス電圧を生成する正側バイアス生成部と

前記入力電圧から前記所定の電圧を減じて負側バイアス電圧を生成する負側バイアス生成部と、

前記正側バイアス電圧と、前記正側トランジスタのソース電圧とが略同一となるように、前記正側トランジスタの前記ゲート端子に印加する電圧を制御する正側制御部と、

前記負側バイアス電圧と、前記負側トランジスタのソース電圧とが略同一となるように、前記負側トランジスタの前記ゲート端子に印加する電圧を制御する負側制御部と

を有し、

前記正側バイアス生成部は、

前記入力電圧に所定の電圧を加える昇圧部と、

前記昇圧部の出力端と、前記正側出力抵抗及び前記負側出力抵抗間の前記接続点との間に直列に設けられ、前記昇圧部が出力する電圧を分圧した電圧を、前記正側バイアス電圧として前記正側制御部に供給する2つの正側分圧抵抗と

を有し、

前記負側バイアス生成部は、

前記入力電圧から前記所定の電圧を減じる降圧部と、

前記降圧部の出力端と、前記正側出力抵抗及び前記負側出力抵抗間の前記接続点との間に直列に設けられ、前記降圧部が出力する電圧を分圧した電圧を、前記負側バイアス電圧として前記負側制御部に供給する2つの負側分圧抵抗と

を有し、

前記2つの正側分圧抵抗の抵抗比、及び前記2つの負側分圧抵抗の抵抗比を制御することにより、前記電力增幅回路の出力インピーダンスを制御する抵抗制御部を更に備える試験装置。

#### 【請求項6】

前記試験装置は、複数の前記被試験デバイスを並行して試験し、前記電力增幅回路を、

前記被試験デバイス毎に備える

請求項5に記載の試験装置。

#### 【請求項7】

与えられる入力電圧に応じた出力電圧を出力する電力增幅回路であって、

ゲート端子に与えられる電圧に応じた電流を流す正側トランジスタと、

ドレイン端子が前記正側トランジスタのドレイン端子に接続され、ゲート端子に与えられる電圧に応じた電流を流す負側トランジスタと、

前記正側トランジスタのソース端子と、所定の正電位との間に設けられた正側出力抵抗と、

前記負側トランジスタのソース端子と、所定の負電位との間に設けられた負側出力抵抗と、

前記入力電圧に所定の電圧を加えて正側バイアス電圧を生成する正側バイアス生成部と

前記入力電圧から前記所定の電圧を減じて負側バイアス電圧を生成する負側バイアス生成部と、

前記正側バイアス電圧と、前記正側トランジスタのソース電圧とが略同一となるように、前記正側トランジスタの前記ゲート端子に印加する電圧を制御する正側制御部と、

前記負側バイアス電圧と、前記負側トランジスタのソース電圧とが略同一となるように、前記負側トランジスタの前記ゲート端子に印加する電圧を制御する負側制御部と

を備え、

10

20

40

50

前記正側トランジスタのドレイン端子と、前記負側トランジスタのドレイン端子との接続点における電圧を前記出力電圧として出力し、

前記正側バイアス生成部は、

前記入力電圧に所定の電圧を加える昇圧部と、

ベース端子が前記昇圧部の出力端に接続された正側バッファトランジスタと、

前記正側バッファトランジスタのコレクタ端子と、前記所定の正電位との間に設けられた第1の正側分圧抵抗と、

前記正側バッファトランジスタのエミッタ端子に一端が接続された第2の正側分圧抵抗と

を有し、

10

前記負側バイアス生成部は、

前記入力電圧から前記所定の電圧を減じる降圧部と、

ベース端子が前記降圧部の出力端に接続された負側バッファトランジスタと、

前記負側バッファトランジスタのコレクタ端子と、前記所定の負電位との間に設けられた第1の負側分圧抵抗と、

前記負側バッファトランジスタのエミッタ端子に一端が接続された第2の負側分圧抵抗と

を有し、

20

前記第1並びに第2の正側分圧抵抗の抵抗比、及び前記第1並びに第2の負側分圧抵抗の抵抗比を制御することにより、前記電力增幅回路の出力インピーダンスを制御する抵抗制御部を更に備える電力增幅回路。

#### 【請求項8】

被試験デバイスを試験する試験装置であって、

前記被試験デバイスに印加すべき入力電圧が与えられ、前記入力電圧に基づいて、前記被試験デバイスに電源電力を供給する電力增幅回路と、

前記電源電力が供給された前記被試験デバイスの動作を検出し、前記被試験デバイスの良否を判定する判定部と

を備え、

前記電力増幅回路は、

ゲート端子に与えられる電圧に応じた電流を流す正側トランジスタと、

30

ドレイン端子が前記正側トランジスタのドレイン端子に接続され、ゲート端子に与えられる電圧に応じた電流を流す負側トランジスタと、

前記正側トランジスタのソース端子と、所定の正電位との間に設けられた正側出力抵抗と、

前記負側トランジスタのソース端子と、所定の負電位との間に設けられた負側出力抵抗と、

前記入力電圧に所定の電圧を加えて正側バイアス電圧を生成する正側バイアス生成部と、

前記入力電圧から前記所定の電圧を減じて負側バイアス電圧を生成する負側バイアス生成部と、

40

前記正側バイアス電圧と、前記正側トランジスタのソース電圧とが略同一となるように、前記正側トランジスタの前記ゲート端子に印加する電圧を制御する正側制御部と、

前記負側バイアス電圧と、前記負側トランジスタのソース電圧とが略同一となるように、前記負側トランジスタの前記ゲート端子に印加する電圧を制御する負側制御部と

を有し、

前記正側トランジスタのドレイン端子と、前記負側トランジスタのドレイン端子との接続点における電圧を電源電圧として前記被試験デバイスに出力し、

前記正側バイアス生成部は、

前記入力電圧に所定の電圧を加える昇圧部と、

ベース端子が前記昇圧部の出力端に接続された正側バッファトランジスタと、

50

前記正側バッファトランジスタのコレクタ端子と、前記所定の正電位との間に設けられた第1の正側分圧抵抗と、

前記正側バッファトランジスタのエミッタ端子に一端が接続された第2の正側分圧抵抗と

を有し、

前記負側バイアス生成部は、

前記入力電圧から前記所定の電圧を減じる降圧部と、

ベース端子が前記降圧部の出力端に接続された負側バッファトランジスタと、

前記負側バッファトランジスタのコレクタ端子と、前記所定の負電位との間に設けられた第1の負側分圧抵抗と、

前記負側バッファトランジスタのエミッタ端子に一端が接続された第2の負側分圧抵抗と

を有し、

前記第1並びに第2の正側分圧抵抗の抵抗比、及び前記第1並びに第2の負側分圧抵抗の抵抗比を制御することにより、前記電力增幅回路の出力インピーダンスを制御する抵抗制御部を更に備える試験装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、与えられる入力電圧に応じた出力電圧を出力する電力增幅回路、及び被試験デバイスを試験する試験装置に関する。 20

【背景技術】

【0002】

従来、例えば半導体回路等の被試験デバイスを試験する場合、被試験デバイスを駆動するための電源電力を被試験デバイスに供給している。当該電源電力は、電力增幅回路によって生成される。

【0003】

電力增幅回路は、与えられる入力電圧に応じた電源電圧を出力し、また被試験デバイスの消費電流に応じて電源電流を出力する。従来、電力增幅回路として、パワーデバイスとして機能する2つのトランジスタを備えるプッシュプル回路が用いられている。プッシュプル回路は、電源電流を出力しない状態で、パワーデバイスにアイドリング電流を流すことにより、パワーデバイスの動作点を所望の領域に調整する回路である。 30

【0004】

関連する特許文献等は、現在認識していないため、その記載を省略する。

【発明の開示】

【発明が解決しようとする課題】

【0005】

電力增幅回路のアイドリング電流は、パワーデバイスの特性によって変化する。例えば、同一の構成を有する電力增幅回路であっても、パワーデバイスの特性のばらつきにより、流れるアイドリング電流は一定にならない。このため、電力增幅回路の特性が設計値と一致しない場合がある。また、複数の電力增幅回路を並列に使用する場合、それぞれの電力增幅回路の特性にばらつきが生じてしまう。 40

【0006】

また、パワーデバイスは、温度変動と共に、流れる電流量が変化する。このため、電力增幅回路の電源投入時から定常状態になるまで、アイドリング電流が変動し、電力増幅回路の特性も変動してしまう。

【0007】

また、このような電力増幅回路を用いて被試験デバイスの試験を行うと、被試験デバイスに所望の電源電力を供給することができない場合があり、試験を精度よく行なうことができない。 50

**【0008】**

また、このようなパワーデバイスの特性のばらつき等の影響を低減するために、電力増幅回路の出力段に抵抗値の高い抵抗を挿入することも考えられるが、出力インピーダンスの悪化を招くと共に、パワーデバイスを駆動するために高電圧を印加する必要があり、電力増幅回路の消費電力の増大を招いてしまう。

**【0009】**

このため本発明は、上述した課題を解決することのできる電力増幅回路及び試験装置を提供することを目的とする。この目的は、請求の範囲における独立項に記載の特徴の組み合わせにより達成される。また従属項は本発明の更なる有利な具体例を規定する。

**【課題を解決するための手段】**

10

**【0010】**

上記課題を解決するために、本発明の第1の形態においては、与えられる入力電圧に応じた出力電圧を出力する電力増幅回路であって、直列に接続され、接続点における電圧を出力電圧として出力する正側出力抵抗及び負側出力抵抗と、ソース端子が正側出力抵抗に接続され、ゲート端子に与えられる電圧に応じた電流を正側出力抵抗に流す正側トランジスタと、ソース端子が負側出力抵抗に接続され、ゲート端子に与えられる電圧に応じた電流を負側出力抵抗に流す負側トランジスタと、入力電圧に応じた正側バイアス電圧を生成する正側バイアス生成部と、入力電圧に応じた負側バイアス電圧を生成する負側バイアス生成部と、正側バイアス電圧と、正側トランジスタのソース電圧とが略同一となるように、正側トランジスタのゲート端子に印加する電圧を制御する正側制御部と、負側バイアス電圧と、負側トランジスタのソース電圧とが略同一となるように、負側トランジスタのゲート端子に印加する電圧を制御する負側制御部とを備える電力増幅回路を提供する。

20

**【0011】**

正側バイアス生成部は、入力電圧に所定の電圧を加えて正側バイアス電圧を生成し、負側バイアス生成部は、入力電圧から所定の電圧を減じて負側バイアス電圧を生成してよい。正側制御部は、非反転入力端子に正側バイアス電圧を受け取り、反転入力端子に正側トランジスタのソース電圧を受け取る増幅器を有し、負側制御部は、非反転入力端子に負側バイアス電圧を受け取り、反転入力端子に負側トランジスタの前記ソース電圧を受け取る増幅器を有してよい。

**【0012】**

30

正側バイアス生成部は、入力電圧に所定の電圧を加える昇圧部と、昇圧部の出力端と、正側出力抵抗及び負側出力抵抗間の接続点との間に直列に設けられ、昇圧部が出力する電圧を分圧した電圧を、正側バイアス電圧として正側制御部に供給する2つの正側分圧抵抗とを有し、負側バイアス生成部は、入力電圧から所定の電圧を減じる降圧部と、降圧部の出力端と、正側出力抵抗及び負側出力抵抗間の接続点との間に直列に設けられ、降圧部が出力する電圧を分圧した電圧を、負側バイアス電圧として負側制御部に供給する2つの負側分圧抵抗とを有してよい。

**【0013】**

正側出力抵抗の抵抗値は、2つの正側分圧抵抗のそれぞれの抵抗値より小さく、負側出力抵抗の抵抗値は、2つの負側分圧抵抗のそれぞれの抵抗値より小さいことが好ましい。電力増幅回路は、2つの正側分圧抵抗の抵抗比、及び2つの負側分圧抵抗の抵抗比を制御することにより、電力増幅回路の出力インピーダンスを制御する抵抗制御部を更に備えてよい。

40

**【0014】**

正側バイアス生成部は、入力電圧に所定の電圧を加える昇圧部と、コレクタ端子が第1の正側分圧抵抗を介して所定の正電位に接続され、エミッタ端子が第2の正側分圧抵抗を介して接続点に接続され、ゲート端子に昇圧部が出力する電圧を受け取り、コレクタ電圧を正側バイアス電圧として正側制御部に供給する正側バイアストランジスタとを有し、負側バイアス生成部は、入力電圧から所定の電圧を減じる降圧部と、コレクタ端子が第1の負側分圧抵抗を介して所定の負電位に接続され、エミッタ端子が第2の負側分圧抵抗を介

50

して接続点に接続され、ゲート端子に降圧部が出力する電圧を受け取り、コレクタ電圧を負側バイアス電圧として負側制御部に供給する負側バイアストランジスタとを有してよい。

### 【0015】

本発明の第2の形態においては、被試験デバイスを試験する試験装置であって、被試験デバイスに印加するべき入力電圧が与えられ、入力電圧に基づいて、被試験デバイスに電源電力を供給する電力增幅回路と、電源電力が供給された被試験デバイスの動作を検出し、被試験デバイスの良否を判定する判定部とを備え、電力增幅回路は、直列に接続され、接続点における電圧を電源電圧として被試験デバイスに出力する正側出力抵抗及び負側出力抵抗と、ソース端子が正側出力抵抗に接続され、ゲート端子に与えられる電圧に応じた電流を正側出力抵抗に流す正側トランジスタと、ソース端子が負側出力抵抗に接続され、ゲート端子に与えられる電圧に応じた電流を負側出力抵抗に流す負側トランジスタと、入力電圧に応じた正側バイアス電圧を生成する正側バイアス生成部と、入力電圧に応じた負側バイアス電圧を生成する負側バイアス生成部と、正側バイアス電圧と、正側トランジスタのソース電圧とが略同一となるように、正側トランジスタのゲート端子に印加する電圧を制御する正側制御部と、負側バイアス電圧と、負側トランジスタのソース電圧とが略同一となるように、負側トランジスタのゲート端子に印加する電圧を制御する負側制御部とを有する試験装置を提供する。10

### 【0016】

試験装置は、複数の被試験デバイスを並行して試験し、電力增幅回路を、被試験デバイス毎に備えてよい。本発明の第3の形態においては、与えられる入力電圧に応じた出力電圧を出力する電力增幅回路であって、ゲート端子に与えられる電圧に応じた電流を流す正側トランジスタと、ドレイン端子が正側トランジスタのドレイン端子に接続され、ゲート端子に与えられる電圧に応じた電流を流す負側トランジスタと、正側トランジスタのソース端子と、所定の正電位との間に設けられた正側出力抵抗と、負側トランジスタのソース端子と、所定の負電位との間に設けられた負側出力抵抗と、入力電圧に応じた正側バイアス電圧を生成する正側バイアス生成部と、入力電圧に応じた負側バイアス電圧を生成する負側バイアス生成部と、正側バイアス電圧と、正側トランジスタのソース電圧とが略同一となるように、正側トランジスタのゲート端子に印加する電圧を制御する正側制御部と、負側バイアス電圧と、負側トランジスタのソース電圧とが略同一となるように、負側トランジスタのゲート端子に印加する電圧を制御する負側制御部とを備え、正側トランジスタのドレイン端子と、負側トランジスタのドレイン端子との接続点における電圧を出力電圧として出力する電力增幅回路を提供する。本発明の第4の形態においては、被試験デバイスを試験する試験装置であって、被試験デバイスに印加するべき入力電圧が与えられ、入力電圧に基づいて、被試験デバイスに電源電力を供給する電力增幅回路と、電源電力が供給された被試験デバイスの動作を検出し、被試験デバイスの良否を判定する判定部とを備え、電力增幅回路は、ゲート端子に与えられる電圧に応じた電流を流す正側トランジスタと、ドレイン端子が正側トランジスタのドレイン端子に接続され、ゲート端子に与えられる電圧に応じた電流を流す負側トランジスタと、正側トランジスタのソース端子と、所定の正電位との間に設けられた正側出力抵抗と、負側トランジスタのソース端子と、所定の負電位との間に設けられた負側出力抵抗と、入力電圧に応じた正側バイアス電圧を生成する正側バイアス生成部と、入力電圧に応じた負側バイアス電圧を生成する負側バイアス生成部と、正側バイアス電圧と、正側トランジスタのソース電圧とが略同一となるように、正側トランジスタのゲート端子に印加する電圧を制御する正側制御部と、負側バイアス電圧と、負側トランジスタのソース電圧とが略同一となるように、負側トランジスタのゲート端子に印加する電圧を制御する負側制御部とを有し、正側トランジスタのドレイン端子と、負側トランジスタのドレイン端子との接続点における電圧を電源電圧として被試験デバイスに出力する試験装置を提供する。3040

### 【0017】

なお、上記の発明の概要は、本発明の必要な特徴の全てを列挙したものではなく、これ

50

20

30

40

50

らの特徴群のサブコンビネーションもまた、発明となりうる。

**【発明を実施するための最良の形態】**

**【0018】**

以下、発明の実施の形態を通じて本発明を説明するが、以下の実施形態は特許請求の範囲にかかる発明を限定するものではなく、また実施形態の中で説明されている特徴の組み合わせの全てが発明の解決手段に必須であるとは限らない。

**【0019】**

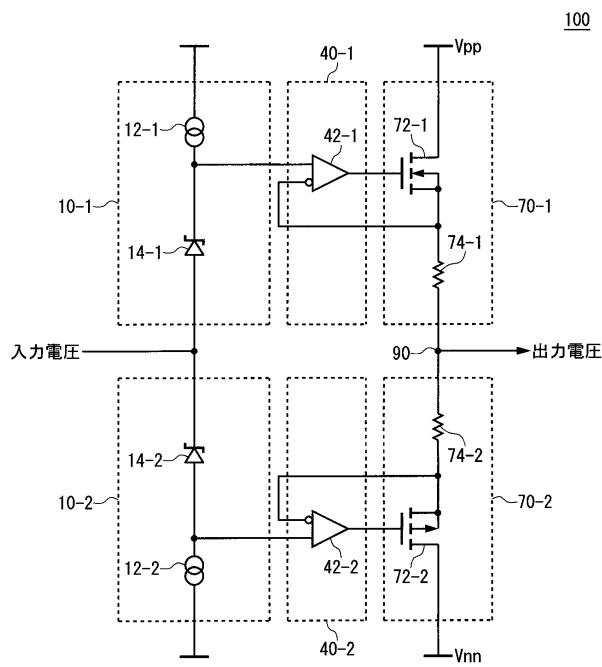

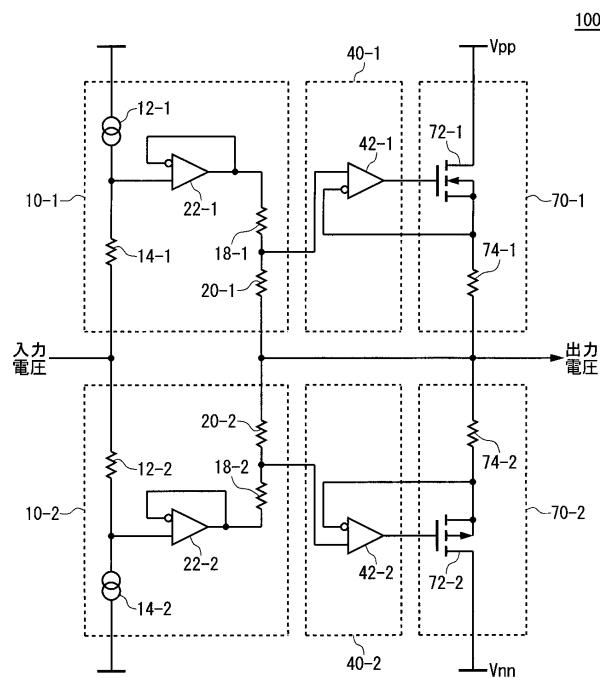

図1は、本発明の実施形態に係る電力增幅回路100の構成の第1例を示す図である。電力增幅回路100は、与えられる入力電圧に応じた出力電圧を出力する回路である。本例においては、正側制御部40-1及び負側制御部40-2が、出力段の正側トランジスタ72-1及び負側トランジスタ72-2のソース電圧を一定値に制御することにより、出力段に流れるアイドリング電流を一定に制御し、これらのトランジスタを所望の動作領域で駆動させる。

**【0020】**

電力增幅回路100は、正側バイアス生成部10-1、負側バイアス生成部10-2、正側制御部40-1、負側制御部40-2、正側出力部70-1、及び負側出力部70-2を備える。

**【0021】**

正側バイアス生成部10-1及び負側バイアス生成部10-2は、与えられる入力電圧に基づいて、正側バイアス電圧及び負側バイアス電圧を生成する。本例において、正側バイアス生成部10-1は、入力電圧に所定の電圧を加えて正側バイアス電圧を生成し、負側バイアス生成部10-2は、入力電圧から所定の電圧を減じて負側バイアス電圧を生成する。

**【0022】**

正側バイアス生成部10-1は、昇圧部14-1及びノレータ12-1を有する。昇圧部14-1は、一端に入力電圧を受け取り、他端がノレータ12-1を介して正電位V<sub>p</sub>に接続される。昇圧部14-1は、受け取った入力電圧に所定の電圧を加えて出力する。本例において昇圧部14-1は、ツエナーダイオードを有する。昇圧部14-1は、入力電圧を、ツエナーダイオードによって定まる昇圧値だけ昇圧して、正側バイアス電圧を生成する。

**【0023】**

負側バイアス生成部10-2は、降圧部14-2及びノレータ12-2を有する。降圧部14-2は、一端に入力電圧を受け取り、他端がノレータ12-2を介して負電位V<sub>n</sub>に接続される。降圧部14-2は、受け取った入力電圧から所定の電圧を減じて出力する。ここで、昇圧部14-1において昇圧される電圧量と、降圧部14-2において降圧される電圧量とは、略等しい。本例において降圧部14-2は、昇圧部14-1におけるツエナーダイオードと略同一の特性のツエナーダイオードを有する。降圧部14-2は、入力電圧を、ツエナーダイオードによって定まる降圧値だけ降圧して、負側バイアス電圧を生成する。

**【0024】**

正側出力部70-1は、正側トランジスタ72-1及び正側出力抵抗74-1を有する。また、負側出力部70-2は、負側トランジスタ72-2及び負側出力抵抗74-2を有する。ここで、正側出力抵抗74-1の抵抗値と、負側出力抵抗74-2の抵抗値とは略等しい。また、本例において正側トランジスタ72-1は、n型MOSFETであり、負側トランジスタ72-2は、p型MOSFETである。

**【0025】**

正側トランジスタ72-1は、ドレイン端子が所定の正電位V<sub>p</sub>に接続され、ソース端子が正側出力抵抗74-1に接続され、ゲート端子に与えられる電圧に応じた電流を正側出力抵抗74-1に流す。また、負側トランジスタ72-2は、ドレイン端子が所定の負電位V<sub>n</sub>に接続され、ソース端子が負側出力抵抗74-2に接続され、ゲート端子に

10

20

30

40

50

与えられる電圧に応じた電流を負側出力抵抗 74-2 に流す。

**【0026】**

正側出力抵抗 74-1 及び負側出力抵抗 74-2 は、正側トランジスタ 72-1 のソース端子と、負側トランジスタ 72-2 のソース端子との間に直列に接続される。また、正側出力抵抗 74-1 と負側出力抵抗 74-2 との接続点における電圧が、出力電圧として外部に出力される。

**【0027】**

正側制御部 40-1 は、正側バイアス生成部 10-1 が出力する正側バイアス電圧と、正側トランジスタ 72-1 のソース電圧が略同一となるように、正側トランジスタのゲート端子に印加する電圧を制御する。つまり、正側制御部 40-1 は、正側バイアス電圧と、当該ソース電圧とが略同一となるように正側トランジスタ 72-1 が正側出力抵抗 74-1 に流す電流を制御する。正側制御部 40-1 は、非反転入力端子に正側バイアス電圧を受け取り、反転入力端子に正側トランジスタ 72-1 のソース電圧を受け取る差動増幅器 42-1 を有してよい。10

**【0028】**

負側制御部 40-2 は、負側バイアス生成部 10-2 が出力する負側バイアス電圧と、負側トランジスタ 72-2 のソース電圧が略同一となるように、負側トランジスタのゲート端子に印加する電圧を制御する。つまり、負側制御部 40-2 は、負側バイアス電圧と、当該ソース電圧とが略同一となるように負側トランジスタ 72-2 が負側出力抵抗 74-2 に流す電流を制御する。負側制御部 40-2 は、非反転入力端子に負側バイアス電圧を受け取り、反転入力端子に負側トランジスタ 72-2 のソース電圧を受け取る差動増幅器 42-2 を有してよい。20

**【0029】**

このような構成により、電力增幅回路 100 のアイドリング時に正側出力抵抗 74-1 及び負側出力抵抗 74-2 に流れるアイドリング電流は一定となる。すなわち、アイドリング電流  $I_d$  は、昇圧部 14-1 が昇圧する電圧を  $V_B_p$ 、降圧部 14-2 が降圧する電圧を  $V_B_n$ 、正側出力抵抗 74-1 の抵抗値を  $R_o_p$ 、負側出力抵抗 74-2 の抵抗値を  $R_o_n$  とすると、下式であたえられる。

$$I_d = (V_B_p - V_B_n) / (R_o_p + R_o_n) \quad \cdots \text{式(1)}$$

**【0030】**

また、正側制御部 40-1 及び負側制御部 40-2 は、アイドリング電流が式(1)に示した値となるように、正側トランジスタ 72-1 及び負側トランジスタ 72-2 を制御する。このように、本例における電力增幅回路 100 は、正側トランジスタ 72-1 及び負側トランジスタ 72-2 の特性に関わらず、アイドリング電流を所定の値に制御することができる。このため、これらのトランジスタを所定の動作領域で動作させることができる。また、複数の電力增幅回路 100 を並列に使用する場合、トランジスタの特性のはらつきに関わらず、それぞれの電力增幅回路 100 におけるアイドリング電流を一定値に制御することができる。

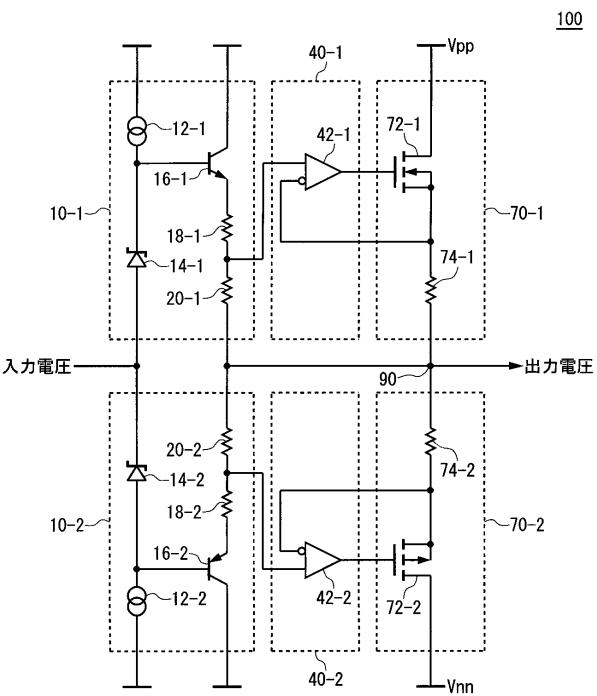

**【0031】**

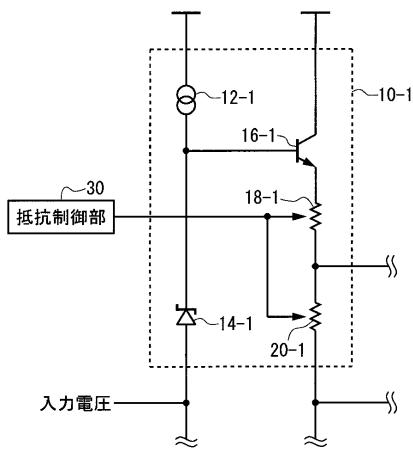

図 2 は、電力增幅回路 100 の構成の第 2 例を示す図である。本例における電力增幅回路 100 は、アイドリング電流を一定に制御し、且つ出力段における消費電力を抑えながら出力インピーダンスを調整可能な回路である。本例における電力增幅回路 100 は、図 1 に示した電力增幅回路 100 の構成に対し、正側バイアス生成部 10-1 及び負側バイアス生成部 10-2 の構成が異なる。他の構成要素については、図 1 において説明した電力增幅回路 100 の構成要素と同一である。40

**【0032】**

正側バイアス生成部 10-1 は、図 1 において説明した正側バイアス生成部 10-1 の構成に加え、正側バッファトランジスタ 16-1、第 1 の正側分圧抵抗 18-1、及び第 2 の正側分圧抵抗 20-1 を更に有する。また、負側バイアス生成部 10-2 は、図 1 において説明した負側バイアス生成部 10-2 の構成に加え、負側バッファトランジスタ 150

6 - 2、第1の負側分圧抵抗18 - 2、及び第2の負側分圧抵抗20 - 2を更に有する。

【0033】

正側バッファトランジスタ16 - 1は、コレクタ端子が所定の正電位V<sub>p p</sub>に接続され、エミッタ端子が第1の正側分圧抵抗18 - 1に接続され、ベース端子が昇圧部14 - 1の出力端に接続される。また負側バッファトランジスタ16 - 1は、コレクタ端子が所定の負電位V<sub>n n</sub>に接続され、エミッタ端子が第1の負側分圧抵抗18 - 2に接続され、ベース端子が降圧部14 - 2の出力端に接続される。本例において正側バッファトランジスタ16 - 1は、n p n型バイポーラトランジスタであり、負側バッファトランジスタ16 - 2は、p n p型バイポーラトランジスタである。

【0034】

10

第1の正側分圧抵抗18 - 1、第2の正側分圧抵抗20 - 1、第2の負側分圧抵抗20 - 2、及び第1の負側分圧抵抗18 - 2は、正側バッファトランジスタ16 - 1のエミッタ端子から、負側バッファトランジスタ16 - 2のエミッタ端子にかけて、順に直列に接続される。

【0035】

第1の正側分圧抵抗18 - 1及び第2の正側分圧抵抗20 - 1は、昇圧部14 - 1により昇圧された電圧を、正側バッファトランジスタ16 - 1を介して受け取り、受け取った電圧をそれぞれの抵抗値の比で分圧し、正側バイアス電圧として正側制御部40 - 1に供給する。つまり、第1の正側分圧抵抗18 - 1と、第2の正側分圧抵抗20 - 1との接続点における電圧が、正側バイアス電圧として正側制御部40 - 1に供給される。

20

【0036】

第1の負側分圧抵抗18 - 2及び第2の負側分圧抵抗20 - 2は、降圧部14 - 2により昇圧された電圧を、負側バッファトランジスタ16 - 2を介して受け取り、受け取った電圧をそれぞれの抵抗値の比で分圧し、負側バイアス電圧として負側制御部40 - 2に供給する。つまり、第1の負側分圧抵抗18 - 2と、第2の負側分圧抵抗20 - 2との接続点における電圧が、負側バイアス電圧として負側制御部40 - 2に供給される。ここで、第1の正側分圧抵抗18 - 1の抵抗値と、第1の負側分圧抵抗18 - 2の抵抗値とは略等しく、第2の正側分圧抵抗20 - 1の抵抗値と、第2の負側分圧抵抗20 - 2の抵抗値とは略等しい。

【0037】

30

また、第2の正側分圧抵抗20 - 1と第2の負側分圧抵抗20 - 2との接続点は、正側出力抵抗74 - 1と負側出力抵抗74 - 2との接続点に接続される。このような構成により、アイドリング電流I<sub>d</sub>は、正側バッファトランジスタ16 - 1のベース - エミッタ間電圧をV<sub>b e p</sub>、負側バッファトランジスタ16 - 2のベース - エミッタ間電圧をV<sub>b e n</sub>、第1の正側分圧抵抗18 - 1の抵抗値をR<sub>c 1 p</sub>、第2の正側分圧抵抗20 - 1の抵抗値をR<sub>c 2 p</sub>、第1の負側分圧抵抗18 - 2の抵抗値をR<sub>c 1 n</sub>、第2の負側分圧抵抗20 - 2の抵抗値をR<sub>c 2 n</sub>とすると、下式で与えられる。

$$\begin{aligned} I_d &= ((V_B_p - V_{b e p}) \times R_{c 2 p}) / (R_{c 1 p} + R_{c 2 p}) \\ &\quad - (V_B_n - V_{b e n}) \times R_{c 2 n} / (R_{c 1 n} + R_{c 2 n}) \\ &/ (R_o p + R_o n) \end{aligned} \quad \cdots \text{式(2)}$$

40

【0038】

式(2)より明らかなように、アイドリング電流I<sub>d</sub>は、出力段のトランジスタの特性によらず、一定値となる。また、電力增幅回路100の出力インピーダンスZ<sub>o</sub>は、下式で与えられる。

$$\begin{aligned} Z_o &= R_o p \times (R_{c 1 p} + R_{c 2 p}) / R_{c 2 p} \\ &= R_o n \times (R_{c 1 n} + R_{c 2 n}) / R_{c 2 n} \\ &\cdots \text{式(3)} \end{aligned}$$

【0039】

式(3)から明らかなように、出力インピーダンスZ<sub>o</sub>は、正側及び負側における第1の分圧抵抗18と第2の分圧抵抗20の比を調整することにより、制御することができる

50

。つまり、出力インピーダンス  $Z_o$  を大きくする場合であっても、抵抗値の小さい正側及び負側における出力抵抗 74 を用いることができ、電力增幅回路 100 の電源として与えられる正電位  $V_{pp}$  及び負電位  $V_{nn}$  を低く抑えることができる。このため、電力增幅回路 100 における消費電力を抑えつつ、出力インピーダンス  $Z_o$  を制御することができる。

#### 【0040】

本例においては、正側出力抵抗 74-1 の抵抗値は、2つの正側分圧抵抗 (18-1、20-1) のそれぞれの抵抗値より小さく、負側出力抵抗 74-2 の抵抗値は、2つの負側分圧抵抗 (18-2、20-2) のそれぞれの抵抗値より小さいことが好ましい。例えば、それぞれの出力抵抗の抵抗値は 1 以下であって、それぞれの分圧抵抗の抵抗値は、数  $k$  あってよい。10

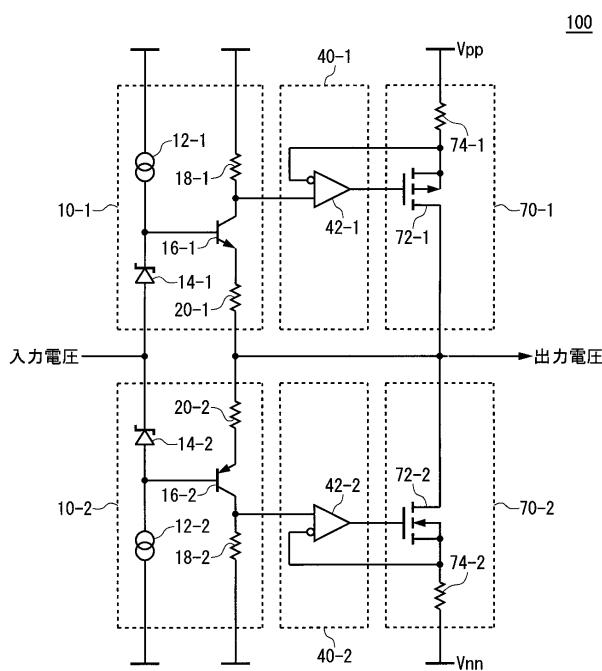

#### 【0041】

図 3 は、電力增幅回路 100 の構成の第 3 例を示す図である。本例における電力增幅回路 100 は、図 2 において説明した電力增幅回路 100 において、正側トランジスタ 72-1 及び負側トランジスタ 72-2 の極性を逆転した構成を有する。つまり、本例における電力增幅回路 100 の正側トランジスタ 72-1 は、p 型 MOSFET であり、負側トランジスタ 72-2 は、n 型 MOSFET である。

#### 【0042】

この場合、正側出力抵抗 74-1 は、正側トランジスタ 72-1 のソース端子と、所定の正電位  $V_{pp}$ との間に設けられ、負側出力抵抗 74-2 は、負側トランジスタ 72-2 のソース端子と、所定の負電位  $V_{nn}$ との間に設けられる。また、正側トランジスタ 72-1 のドレイン端子と、負側トランジスタ 72-2 のドレイン端子とは接続され、当該接続点における電圧が、出力電圧として外部に出力される。このような構成によっても、図 1 又は図 2 において説明した電力增幅回路 100 と同様に、出力段のトランジスタの特性に関わらず、アイドリング電流を所定値にすることができます。20

#### 【0043】

また、図 3 に示すように、正側及び負側のバイアス生成部 10 において、バッファトランジスタ 16 のコレクタ端子と所定の正電位  $V_{pp}$ との間に、第 1 の分圧抵抗 18 が設けられ、バッファトランジスタ 16 のソース端子に、第 2 の分圧抵抗 20 が接続されていてもよい。この場合、バッファトランジスタ 16 のコレクタ端子と、第 1 の分圧抵抗 18 の接続点における電圧が、バイアス電圧として正側又は負側の制御部 40 に供給される。このような構成によっても、図 2 において説明した電力增幅回路 100 と同様に、出力インピーダンス  $Z_o$  を調整することができる。30

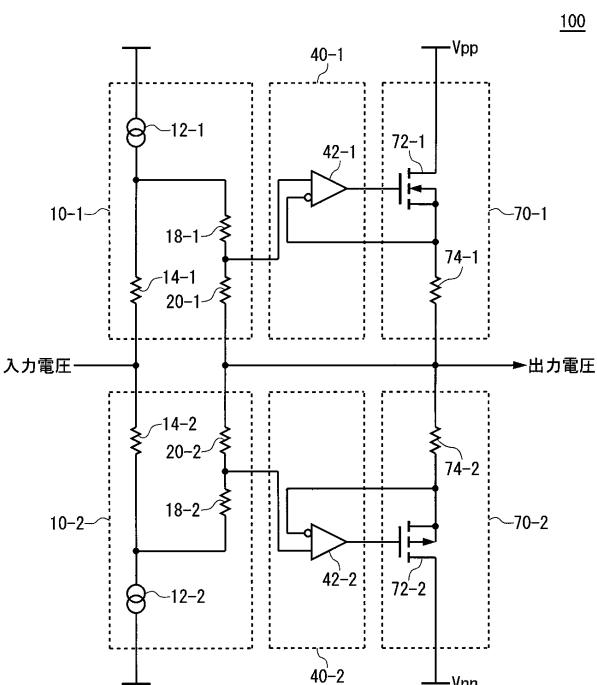

#### 【0044】

図 4 は、電力增幅回路 100 の構成の第 4 例を示す図である。本例における電力增幅回路 100 は、正側及び負側のバイアス生成部 10 において、抵抗によりバイアス電圧を生成する。ウェナーダイオードの順方向電圧、及びトランジスタのベース - エミッタ間電圧にはばらつきが生じやすいため、これらを用いてバイアス電圧を生成すると、所望のバイアス電圧を生成できない場合がある。これに対し、抵抗は抵抗値を精度よく調整して形成することができるため、本例における電力增幅回路 100 は、所望のバイアス電圧を精度よく生成することができる。40

#### 【0045】

正側バイアス生成部 10-1 は、昇圧部 14-1 として抵抗を用いる。また、本例における正側バイアス生成部 10-1 は、図 2 において説明した正側バイアス生成部 10-1 の構成に対し、正側バッファトランジスタ 16-1 を有さない。第 1 の正側分圧抵抗 18-1 及び第 2 の正側分圧抵抗 20-1 は、昇圧部 14-1 の出力端と、正側出力抵抗 74-1 及び負側出力抵抗 74-2 の接続点との間に直列に設けられる。

#### 【0046】

また、負側バイアス生成部 10-2 は、図 4 に示すように、正側バイアス生成部 10-1 と同様の構成を有する。このような構成により、上述したように、所望のバイアス電圧50

を精度よく生成することができる。

#### 【0047】

ここで、昇圧部14-1として機能する抵抗の抵抗値は、第1の正側分圧抵抗18-1及び第2の正側分圧抵抗20-1の抵抗値より十分小さいことが好ましい。例えば、ノレータ12-1に流れる電流の略全てが、昇圧部14-1に流れるような抵抗値を有することが好ましい。また同様に、降圧部14-2として機能する抵抗の抵抗値は、第1の負側分圧抵抗18-2及び第2の負側分圧抵抗20-2の抵抗値より十分小さいことが好ましい。

#### 【0048】

図5は、電力增幅回路100の構成の第5例を示す図である。本例における電力增幅回路100は、図4において説明した電力增幅回路100の構成に対し、正側及び負側のバイアス生成部10において、ボルテージフォロワ回路22を更に有する。

10

#### 【0049】

正側バイアス生成部10-1は、昇圧部14-1の出力端と、第1の正側分圧抵抗18-1との間に、ボルテージフォロワ回路22-1を有する。また、負側バイアス生成部10-2は、降圧部14-2の出力端と、第1の負側分圧抵抗18-2との間に、ボルテージフォロワ回路22-2を有する。このような構成により、昇圧部14-1又は降圧部14-2が生成した電圧を、精度よく第1の正側分圧抵抗18-1又は第1の負側分圧抵抗18-2に伝送することができる。

#### 【0050】

また、電力增幅回路100は、第1の分圧抵抗18及び第2の分圧抵抗20の抵抗値を制御する抵抗制御部を更に有していてもよい。これにより、電力增幅回路100の出力インピーダンスを所望の値に制御することができる。

20

#### 【0051】

図6は、電力增幅回路100が備える抵抗制御部30を説明する図である。抵抗制御部30は、正側及び負側のバイアス生成部10における第1の分圧抵抗18及び第2の分圧抵抗20の抵抗値を制御する。図6においては、正側バイアス生成部10-1における第1の正側分圧抵抗18-1及び第2の正側分圧抵抗20-1の抵抗値を制御する場合について説明する。

#### 【0052】

30

式(3)に関連して説明したように、抵抗制御部30は、第1の正側分圧抵抗18-1及び第2の正側分圧抵抗20-1の抵抗比を制御することにより、出力インピーダンスの値を容易に制御することができる。第1の正側分圧抵抗18-1及び第2の正側分圧抵抗20-1は、例えば可変抵抗であってよい。また、正側バイアス生成部10における分圧抵抗の抵抗値を制御した場合、抵抗制御部30は、負側バイアス生成部10における分割抵抗の抵抗値も、同様に制御する。

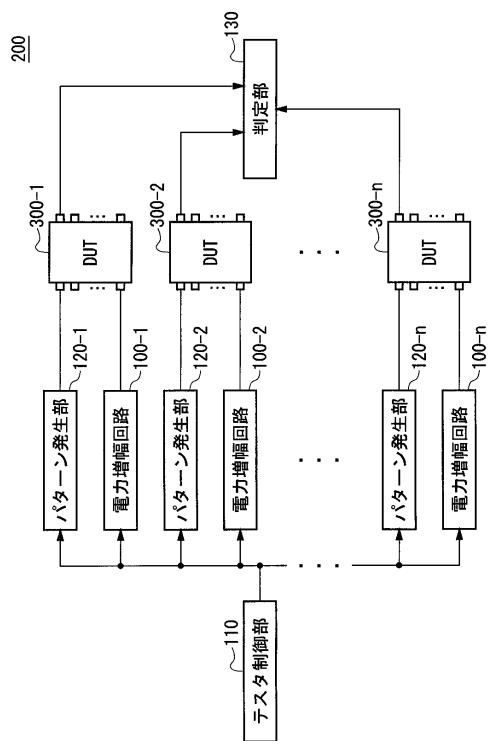

#### 【0053】

図7は、本発明の実施形態に係る試験装置200の構成の一例を示す図である。試験装置200は、複数の被試験デバイス300を並行して試験する装置であって、複数のパターン発生部(120-1～120-n、但し n は任意の整数)、複数の電力增幅回路(100-1～100-n)、テスト制御部110、及び判定部130を備える。被試験デバイス300は、例えば半導体回路等の電子デバイスである。

40

#### 【0054】

複数の電力增幅回路100は、複数の被試験デバイス300に対応して設けられる。複数の電力增幅回路100は、それぞれ図1から図6において説明した電力增幅回路100と同一の構成を有し、対応する被試験デバイス300に電源電力を供給する。

#### 【0055】

複数のパターン発生部120-1は、複数の被試験デバイス300に対応して設けられる。それぞれのパターン発生部120-1は、被試験デバイス300の試験を行うための試験パターンを、対応する被試験デバイス300に供給する。

50

**【0056】**

テスタ制御部110は、複数のパターン発生部120、及び複数の電力增幅回路100を制御し、それぞれの被試験デバイス300に所定の試験パターン及び電源電圧を供給させる。また判定部130は、電源電力が供給された被試験デバイス300の動作を検出し、それぞれの被試験デバイス300の良否を判定する。例えば、判定部130は、被試験デバイス300が出力する出力信号に基づいて良否を判定してよく、また被試験デバイス300に供給される電源電流を検出し、当該電源電流に基づいて被試験デバイス300の良否を判定してもよい。

**【0057】**

本例におけるそれぞれの電力增幅回路100における昇圧部14-1及び降圧部14-2は、同一の昇圧電圧及び降圧電圧を生成することが好ましい。例えば、それぞれの昇圧部14-1及び降圧部14-2は、同一の特性を有するツエナーダイオードによって構成されてよい。これにより、それぞれの電力增幅回路100におけるアイドリング電流を同一にすることができる。このため、それぞれの被試験デバイス300の試験を精度よく行なうことができる。

10

**【0058】**

以上、本発明を実施の形態を用いて説明したが、本発明の技術的範囲は上記実施の形態に記載の範囲には限定されない。上記実施の形態に、多様な変更または改良を加えることが可能であることが当業者に明らかである。その様な変更または改良を加えた形態も本発明の技術的範囲に含まれ得ることが、特許請求の範囲の記載から明らかである。

20

**【産業上の利用可能性】****【0059】**

以上から明らかなように、本発明によれば、出力段のトランジスタの特性に関わらず、アイドリング電流が所定の値となる電力增幅回路を提供することができる。

**【図面の簡単な説明】****【0060】**

【図1】本発明の実施形態に係る電力增幅回路100の構成の第1例を示す図である。

【図2】電力増幅回路100の構成の第2例を示す図である。

【図3】電力増幅回路100の構成の第3例を示す図である。

【図4】電力増幅回路100の構成の第4例を示す図である。

30

【図5】電力増幅回路100の構成の第5例を示す図である。

【図6】抵抗制御部30を説明する図である。

【図7】本発明の実施形態に係る試験装置200の構成の一例を示す図である。

**【符号の説明】****【0061】**

100…バイアス生成部、120…ノレータ、14-1…昇圧部、14-2…降圧部、160…バッファトランジスタ、180…分圧抵抗、200…分圧抵抗、220…ボルテージフォロワ回路、300…抵抗制御部、400…制御部、420…差動増幅器、700…出力部、720…トランジスタ、740…出力抵抗、1000…電力増幅回路、1100…テスタ制御部、1200…パターン発生部、1300…判定部、2000…試験装置、3000…被試験デバイス

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(56)参考文献 特開2003-046347(JP,A)

特開平05-067932(JP,A)

実開平01-169810(JP,U)

特開昭52-010753(JP,A)

特開平06-331700(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 03 F 3 / 30

G 01 R 31 / 28

H 03 F 1 / 56

H 03 F 3 / 34