(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6407992号

(P6407992)

(45) 発行日 平成30年10月17日(2018.10.17)

(24) 登録日 平成30年9月28日(2018.9.28)

|                          |                       |

|--------------------------|-----------------------|

| (51) Int.Cl.             | F 1                   |

| HO 1 L 27/10 (2006.01)   | HO 1 L 27/10 4 8 1    |

| HO 1 L 21/8242 (2006.01) | HO 1 L 27/108 6 8 1 F |

| HO 1 L 27/108 (2006.01)  | HO 1 L 27/108 6 8 1 E |

| HO 1 L 21/8244 (2006.01) | HO 1 L 27/11          |

| HO 1 L 27/11 (2006.01)   |                       |

請求項の数 14 (全 15 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2016-525483 (P2016-525483)  |

| (86) (22) 出願日 | 平成26年7月10日 (2014.7.10)        |

| (65) 公表番号     | 特表2016-528727 (P2016-528727A) |

| (43) 公表日      | 平成28年9月15日 (2016.9.15)        |

| (86) 国際出願番号   | PCT/US2014/046152             |

| (87) 国際公開番号   | W02015/006563                 |

| (87) 国際公開日    | 平成27年1月15日 (2015.1.15)        |

| 審査請求日         | 平成29年6月13日 (2017.6.13)        |

| (31) 優先権主張番号  | 61/845,044                    |

| (32) 優先日      | 平成25年7月11日 (2013.7.11)        |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 14/012,478                    |

| (32) 優先日      | 平成25年8月28日 (2013.8.28)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                               |

|-----------|---------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 595020643<br>クアルコム・インコーポレイテッド<br>QUALCOMM INCORPORATED<br>アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775 |

| (74) 代理人  | 100108855<br>弁理士 蔵田 昌俊                                                                                        |

| (74) 代理人  | 100109830<br>弁理士 福原 淑弘                                                                                        |

| (74) 代理人  | 100158805<br>弁理士 井関 守三                                                                                        |

| (74) 代理人  | 100194814<br>弁理士 奥村 元宏                                                                                        |

最終頁に続く

(54) 【発明の名称】 ビットセルおよび論理区画を有するモノリシック3次元(3D)ランダムアクセスメモリ(RAM)アレイアーキテクチャ

## (57) 【特許請求の範囲】

## 【請求項1】

第1の3次元(3D)集積回路(ASIC)(3DIC)ティア内に配設された第1のランダムアクセスメモリ(RAM)データバンクと、

前記第1の3DICティア内に配設された第2のRAMデータバンクと、

前記第1の3DICティア内に配設された前記第1のRAMデータバンクと前記第1の3DICティア内に配設された前記第2のRAMデータバンクとの間に配設された、少なくとも1つの第1のローデコーダと、少なくとも1つの第1のワード線ドライバと、第1のグローバルロック制御論理とを備える第1のRAMアクセス論理と、前記第1のRAMアクセス論理は、前記少なくとも1つの第1のローデコーダと前記少なくとも1つの第1のワード線ドライバとを介して前記第1の3DICティア内に配設された前記第1のRAMデータバンクおよび前記第1の3DICティア内に配設された前記第2のRAMデータバンクへのデータアクセスを制御するように構成され、

を備える第1の3DICティアと、

第2の3DICティア内に配設された第1のRAMデータバンクと、

前記第2の3DICティア内に配設された第2のRAMデータバンクと、

前記第2の3DICティア内に配設された前記第1のRAMデータバンクと前記第2の3DICティア内に配設された前記第2のRAMデータバンクとの間に配設された、少なくとも1つの第2のローデコーダと、少なくとも1つの第2のワード線ドライバと、第2のグローバルロック制御論理とを備える第2のRAMアクセス論理と、前記第2のR

10

20

A M アクセス論理は、前記少なくとも 1 つの第 2 のローデコーダと前記少なくとも 1 つの第 2 のワード線ドライバとを介して前記第 2 の 3 D I C ティア内に配設された前記第 1 の R A M データバンクおよび前記第 2 の 3 D I C ティア内に配設された前記第 2 の R A M データバンクへのデータアクセスを制御するように構成され、

を備える第 2 の 3 D I C ティアと、

を備える、3 D R A M であって、

前記第 1 および第 2 のグローバルブロック制御論理は、前記メモリの入力および出力のための特定の読み取り / 書き込みマルチプレクサを選択するための処理論理を備え、

前記 3 D R A M は、モノリシック 3 D I C 内に配設され、

前記第 1 の 3 D I C ティアおよび前記第 2 の 3 D I C ティアのうちの一方のティア内の前記第 1 の R A M データバンクおよび前記第 2 の R A M データバンクは、他方のティアへフォールドされ、

前記一方のティア内の前記第 1 の R A M データバンクおよび前記第 2 の R A M データバンクのうちの少なくとも一方、または前記他方のティア内の前記第 1 の R A M データバンクおよび前記第 2 の R A M データバンクのうちの少なくとも一方は、前記 3 D R A M のための入力および出力を提供するように構成されたグローバルデータパスを備える、3 D R A M。

#### 【請求項 2】

前記第 1 のティア内の前記第 1 の R A M データバンクは、少なくとも 1 つの静的 R A M ( S R A M ) データバンクで構成される、請求項 1 に記載の 3 D R A M。

#### 【請求項 3】

前記第 1 のティア内の前記第 1 の R A M データバンクは、少なくとも 1 つの動的 R A M ( D R A M ) データバンクで構成される、請求項 1 に記載の 3 D R A M。

#### 【請求項 4】

R A M データバンクが配設される少なくとも 1 つの追加の 3 D I C ティアをさらに備える、請求項 1 に記載の 3 D R A M。

#### 【請求項 5】

前記グローバルデータパスは、前記第 1 および第 2 の 3 D I C ティアのうちの一番上の 3 D I C ティア上に配置される、または、

前記グローバルデータパスは、前記第 1 および第 2 のティアのうちの一番下の 3 D I C ティア上に配置される、請求項 1 に記載の 3 D R A M。

#### 【請求項 6】

前記第 1 のティアを前記第 2 のティアへ結合している複数のモノリシックインターティアバイアス ( M I V ) をさらに備える、請求項 1 に記載の 3 D R A M。

#### 【請求項 7】

セットトップボックス、娛樂ユニット、ナビゲーションデバイス、通信デバイス、固定ロケーションデータユニット、モバイルロケーションデータユニット、モバイル電話、セルラ電話、コンピュータ、携帯用コンピュータ、デスクトップコンピュータ、携帯情報端末 ( P D A ) 、モニタ、コンピュータモニタ、テレビ、チューナー、ラジオ、衛星ラジオ、音楽プレイヤ、デジタル音楽プレイヤ、携帯用音楽プレイヤ、デジタルビデオプレイヤ、ビデオプレイヤ、デジタルビデオディスク ( D V D ) プレイヤ、および携帯用デジタルビデオプレイヤから成るグループから選択されるデバイスへ統合される、請求項 1 に記載の 3 D R A M。

#### 【請求項 8】

第 1 の 3 次元 ( 3 D ) 集積回路 ( I C ) ( 3 D I C ) ティア内に配設された第 1 のメモリ手段と、

前記第 1 の 3 D I C ティア内に配設された第 2 のメモリ手段と、

前記第 1 の 3 D I C ティア内に配設された前記第 1 のメモリ手段と前記第 1 の 3 D I C ティア内に配設された前記第 2 のメモリ手段との間に配設された、少なくとも 1 つの第 1 のローデコーダと、少なくとも 1 つの第 1 のワード線ドライバと、第 1 のグローバルブ

10

20

30

40

50

ロック制御論理とを備える第1のRAMアクセス論理と、前記第1のRAMアクセス論理は、前記少なくとも1つの第1のローデコーダと前記少なくとも1つの第1のワード線ドライバとを介して前記第1の3DICティア内に配設された前記第1のメモリ手段および前記第1の3DICティア内に配設された前記第2のメモリ手段へのデータアクセスを制御するように構成され、

を備える第1の3DICティアと、

第2の3DICティア内に配設された第1のメモリ手段と、

前記第2の3DICティア内に配設された第2のメモリ手段と、

前記第2の3DICティア内に配設された前記第1のメモリ手段と前記第2の3DICティア内に配設された前記第2のメモリ手段との間に配設された、少なくとも1つの第2のローデコーダと、少なくとも1つの第2のワード線ドライバと、第2のグローバルブロック制御論理とを備える第2のRAMアクセス論理と、前記第2のRAMアクセス論理は、前記少なくとも1つの第2のローデコーダと前記少なくとも1つの第2のワード線ドライバとを介して前記第2の3DICティア内に配設された前記第1のメモリ手段および前記第2の3DICティア内に配設された前記第2のメモリ手段へのデータアクセスを制御するように構成され、

を備える第2の3DICティアと、

を備える、3D RAMであって、

前記第1および第2のグローバルブロック制御論理は、前記メモリの入力および出力のための特定の読み取り／書き込みマルチブレクサを選択するための処理論理を備え、

前記3D RAMは、モノリシック3DIC内に配設され、

前記第1の3DICティアおよび前記第2の3DICティアのうちの一方のティア内の前記第1のメモリ手段および前記第2のメモリ手段は、他方のティアへフォールドされ、

前記一方のティア内の前記第1のメモリ手段および前記第2のメモリ手段のうちの少なくとも一方、または前記他方のティア内の前記第1のメモリ手段および前記第2のメモリ手段のうちの少なくとも一方は、前記3D RAMのための入力および出力を提供するように構成されたグローバルデータパスを備える、3D RAM。

#### 【請求項9】

前記第1の3DICティア内に配設された前記第1のメモリ手段は、RAMデータバンクを備える、請求項8に記載の3D RAM。

#### 【請求項10】

前記第1のティアを前記第2のティアへ結合している複数のモノリシックインターティアバイアス(MIV)をさらに備える、請求項8に記載の3D RAM。

#### 【請求項11】

前記RAMデータバンクは、少なくとも1つの静的RAM(SRAM)データバンクを備える、請求項9に記載の3D RAM。

#### 【請求項12】

前記RAMデータバンクは、少なくとも1つの動的RAM(DRAM)データバンクを備える、請求項9に記載の3D RAM。

#### 【請求項13】

RAMデータバンクが配設される少なくとも1つの追加の3DICティアをさらに備える、請求項8に記載の3D RAM。

#### 【請求項14】

前記グローバルデータパスは、前記第1および第2の3DICティアのうちの一番上の3DICティア上に配置される、請求項8に記載の3D RAM。

#### 【発明の詳細な説明】

#### 【優先権主張出願】

#### 【0001】

[0001] 本願は、2013年7月11日に出願され、「ビットセルおよび論理区画を有するモノリシック3次元(3D)静的ランダムアクセスメモリ(SRAM)アレイアーキ

10

20

30

40

50

テクチャ (A MONOLITHIC THREE DIMENSIONAL (3D) STATIC RANDOM ACCESS MEMORY (SRAM) ARRAY ARCHITECTURE WITH BITCELL AND LOGIC PARTITIONING) 」と題された、米国仮特許出願第61/845,044号に対する優先権を主張し、ここに参照によってその全体が組み込まれる。

【0002】

[0002] 本願はまた、2013年8月28日に出願され、「ビットセルおよび論理区画を有するモノリシック3次元(3D)ランダムアクセスメモリ(RAM)アレイアーキテクチャ(A MONOLITHIC THREE DIMENSIONAL (3D) RANDOM ACCESS MEMORY (RAM) ARRAY ARCHITECTURE WITH BITCELL AND LOGIC PARTITIONING)」と題された、米国特許出願第14/012,478号に対する優先権を主張し、ここに参照によってその全体が組み込まれる。 10

【背景技術】

【0003】

I. 技術分野

[0003] 本開示の技術は、一般に計算デバイスに使用するためのメモリセルに関する。

【0004】

II. 背景技術

[0004] モバイル通信デバイスは、現在の社会において一般的になっている。これらのモバイルデバイスの普及は、部分的に、そのようなデバイス上で今や可能にされる多くの機能によって促進される。そのような機能の需要は、処理能力要件を増加させ、よりパワフルなバッテリの必要性を生む。モバイル通信デバイスのハウジングの制限されたスペース内で、バッテリは処理回路と競争する(competes)。ハウジング内のスペースに関する競争(competition)および他の要因は、続いている回路内の電力消費およびコンポーネントの縮小化に貢献する。 20

【0005】

[0005] 縮小化の圧力(pressures)と同時に、モバイル通信デバイス内の電圧レベルを低減させるための圧力がある。低減された電圧レベルは、バッテリ寿命を延長し、モバイルデバイス内の発熱を低減させる。電圧レベルを低減させるための圧力がある一方で、対応するより大きな電圧レベルの必要性を有する増加している大きなメモリブロックの存在が対立する(opposing)圧力を提供する。多くの場合において、これらのメモリブロックは、ランダムアクセスメモリ(RAM)から作られ、より具体的には、メモリビットセルから、およびメモリビットセルへコマンドを読み取るおよび書き込むためのロー(row)およびコラム(column)のアクセスを実行するためのワード線およびビット線上の動作電圧(operating voltages)を有する静的RAM(SRAM)から作られる。ビット線およびワード線の長さが、メモリセルアレイ内で要求される電圧レベルに悪影響を与える。すなわち、大きなアレイにおいて、ビット線またはワード線の長さは、所望の低い動作電圧が遠隔の(distant)ビットセルにおいてトランジスタを動作させるために不十分であるようなレベルまで、遠隔のビットセルにおいて電圧を低減するために十分な容量性の(capacitive)または抵抗の(resistive)品質を導入させ得る。 30

【発明の概要】

【0006】

[0006] 詳細な説明において開示される実施形態は、ビットセルおよび論理区画を有するモノリシック3次元(3D)メモリセルアレイアーキテクチャを含む。3D集積回路(ASIC)(3DIC)内で異なるティアヘメモリセルのエレメントをフォールドする(folds)、さもなければスタックする(stacks)3DICが提案される。典型的な実施形態において、3DICは、異なるティア内のエレメントを結合するモノリシックインターティアバイアス(MIV:monolithic intertier vias)を有するモノリシック3DICである。典型的な実施形態において、ビットセルは、ビットセルが制御論理「胸部(thorax)」のいずれかの側(either side)にある「羽」であるため、いわゆる「バタフライ(butterfly)」配列(arrangement)で配列される。3DICの各ティアはメモリセル、ならびにグローバルブロック制御論理を含むアクセス論理を有する。メモリセルを有する各テ 50

イア内のグローバルブロック制御論理とアクセス論理を配置することによって、各メモリセルについてのワード線およびビット線の長さが短くされ、低減された供給電圧ならびに一般にメモリデバイスの全体のフットプリントを低減させることを可能にする。

#### 【0007】

[0007] これに関する実施形態において、3Dランダムアクセスメモリ( RAM )が提供される。3D RAMは、第1の3DICティアを備える。第1の3DICティアは、第1の3DICティア内に配設された第1のRAMデータバンクを備える。第1の3DICティアはまた、第1の3DICティア内に配設された第2のRAMデータバンクを備える。第1の3DICティアはまた、第1の3DICティア内に配設された第1のRAMデータバンクと第1の3DICティア内に配設された第2のRAMデータバンクとの間に配設された第1のグローバルブロック制御論理を備える第1のRAMアクセス論理と、第1の3DICティア内に配設された第1のRAMデータバンクおよび第1の3DICティア内に配設された第2のRAMデータバンクへのデータアクセスを制御するように構成されたRAMアクセス論理を備える。3D RAMはまた、第2の3DICティアを備える。第2の3DICティアは、第2の3DICティア内に配設された第1のRAMデータバンクを備える。第2の3DICティアはまた、第2の3DICティア内に配設された第2のRAMデータバンクを備える。第2の3DICティアはまた、第2の3DICティア内に配設された第1のRAMデータバンクと第2の3DICティア内に配設された第2のRAMデータバンクとの間に配設された第2のグローバルブロック制御論理を備える第2のRAMアクセス論理を備え、第2のRAMアクセス論理は、第2の3DICティア内に配設された第1のRAMデータバンクおよび第2の3DICティア内に配設された第2のRAMデータバンクへのデータアクセスを制御するように構成される。

10

20

30

40

#### 【0008】

[0008] 別の実施形態において、3D RAMが開示される。3D RAMは、第1の3DICティアを備える。第1の3DICティアは、第1の3DICティア内に配設された第1のメモリ手段を備える。第1の3DICティアはまた、第1の3DICティア内に配設された第2のメモリ手段を備える。第1の3DICティアはまた、第1の3DICティア内に配設された第1のメモリ手段と第1の3DICティア内に配設された第2のメモリ手段との間に配設された第1のグローバルブロック制御論理を備える第1のRAMアクセス論理を備え、RAMアクセス論理は、第1の3DICティア内に配設された第1のメモリ手段および第1の3DICティア内に配設された第2のメモリ手段へのデータアクセスを制御するように構成される。3D RAMはまた、第2の3DICティアを備える。第2の3DICティアは、第2の3DICティア内に配設された第1のメモリ手段を備える。第2の3DICティアはまた、第2の3DICティア内に配設された第2のメモリ手段を備える。第2の3DICティアはまた、第2の3DICティア内に配設された第1のメモリ手段と第2の3DICティア内に配設された第2のメモリ手段との間に配設された第2のグローバルブロック制御論理を備える第2のRAMアクセス論理を備え、第2のRAMアクセス論理は、第2の3DICティア内に配設された第1のメモリ手段および第2の3DICティア内に配設された第2のメモリ手段へのデータアクセスを制御するように構成される。

#### 【図面の簡単な説明】

#### 【0009】

【図1】図1は、従来のメモリセルの概略図である。

【図2】図2は、図1のもののようなメモリセルを含む従来のメモリセルアレイの概略図である。

【図3】図3は、関係づけられた制御論理を有する従来のメモリセルアレイの概略図である。

【図4】図4は、2次元バタフライ実施形態に従う典型的なメモリセルアレイのブロック図である。

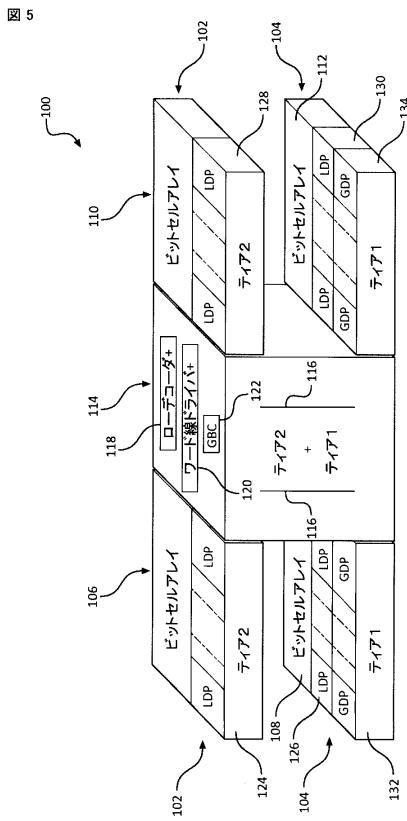

【図5】図5は、3次元バタフライ実施形態に従う典型的なメモリセルアレイの簡略化さ

50

れた観点の図である。

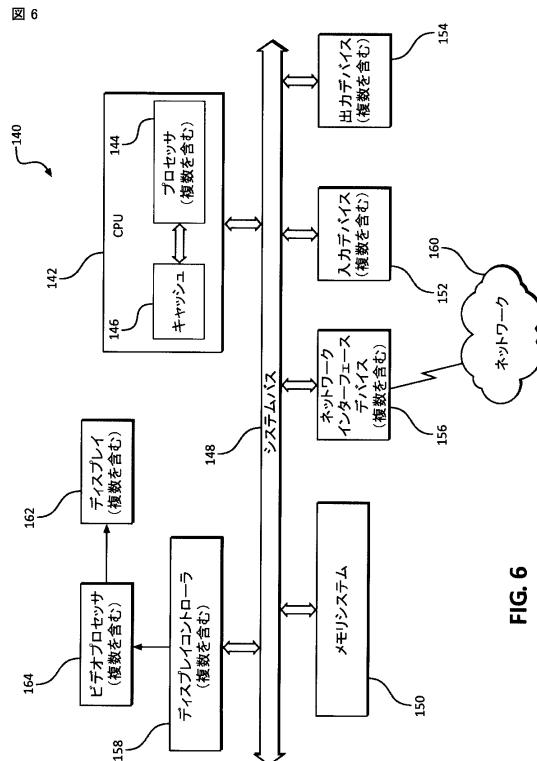

【図6】図6は、図4または図5のメモリセルアレイを含むことができる典型的なプロセッサベースのシステムのブロック図である。

【詳細な説明】

【0010】

[0015] 次に図面を参照すると、本開示のいくつかの典型的な実施形態が説明されている。「典型的(exemplary)」という用語は、ここでは、「例、事例、または実例としての役割を果たす」という意味で用いられる。「典型的」としてここに記述されている任意の実施形態は、必ずしも、他の実施形態より有利または優先されると解釈されるべきではない。

10

【0011】

[0016] 詳細な説明において開示される実施形態は、ピットセルおよび論理区画を有するモノリシック3次元(3D)メモリセルアレイアーキテクチャを含む。3D集積回路(3DIC)(3DIC)内で異なるティアヘメモリセルのエレメントをフォールドする、さもなければスタッカする3DICが提案される。典型的な実施形態において、3DICは、異なるティア内のエレメントを結合するモノリシックインターティアバイアス(MIV:monolithic intertier vias)を有するモノリシック3DICである。典型的な実施形態において、ピットセルは、ピットセルが制御論理「胸部」のいずれかの側にある「羽」であるため、いわゆる「バタフライ」配列で配列される。3DICの各ティアはメモリセル、ならびにグローバルブロック制御論理を含むアクセス論理を有する。メモリセルを有する各ティア内のグローバルブロック制御論理とアクセス論理を配置することによって、各メモリセルについてのワード線およびピット線の長さが短くされ、低減された供給電圧を可能にし、ならびに一般にメモリデバイスの全体のフットプリントを低減させる。

20

【0012】

[0017] 本開示の実施形態に取り組む前に、従来のメモリセルアレイの簡単な概説が、図1-図3を参照して提供される。本開示の実施形態の議論は、図4を参照して以下に開始する。

【0013】

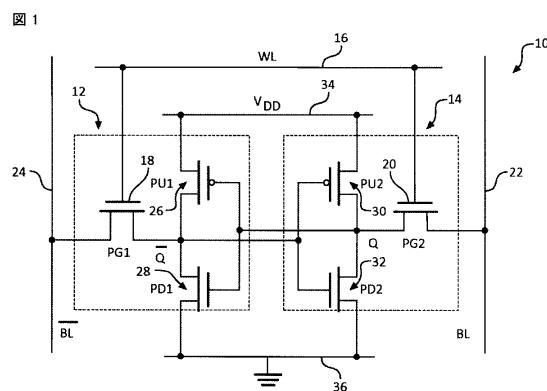

[0018] これに関して、図1はメモリセル10、特に6トランジスタ(6T)静的ランダムアクセスメモリ(RAM)(SRAM)ピットセルを例示する。メモリセル10は、第1のインバータ12および第2のインバータ14を有する。ワード線(WL)16は、インバータ12、14の両方に結合する。特に、ワード線16は、第1のパスゲート(PG)トランジスタ18(PG1)のゲートを通して第1のインバータ12に結合し、第2のPGトランジスタ20(PG2)のゲートを通して第2のインバータ14に結合する。ピット線(BL)22は、第2のPGトランジスタ20のドレインに結合する。ピット線バー

30

【数1】

$(\overline{BL})$

40

24は、第1のPGトランジスタ18のソースに結合する。

【0014】

[0019] つづけて図1を参照すると、第1のインバータ12は、第1のプルアップ(PU)トランジスタ26(PU1)および第1のプルダウン(PD)トランジスタ28(PD1)を含む。第2のインバータ14は、第2のPUトランジスタ30(PU2)および第2のPDトランジスタ32(PD2)を含む。電圧ソース( $V_{DD}$ )34は、第1および第2のPUトランジスタ26、30に結合する。PDトランジスタ28、32は、接地36に結合される。

【0015】

[0020] メモリセル10は、産業においてよく理解されており、図2において例示され

50

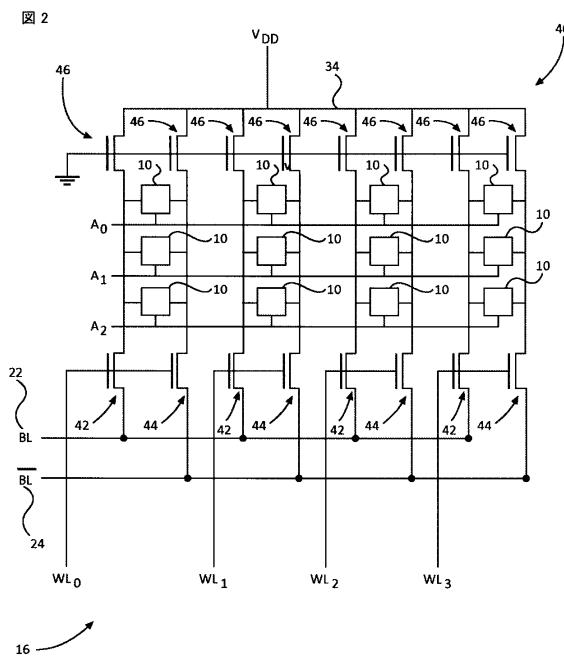

ているメモリセルアレイ 4 0 のようなセルのアレイ内へしばしば集められる (assembled)。特に、メモリセルアレイ 4 0 は、 $3 \times 4$  メモリセルアレイであるが、他のアレイもまた知られている (たとえば、 $8 \times 128$ 、 $64 \times 64$  等)。ビット線 2 2 およびビット線バー 2 4 は、センストランジスタ (sense transistor) 4 2、4 4 をそれぞれ通して、メモリセル 1 0 に結合される。電圧ソース 3 4 は、同様に、トランジスタ 4 6 を通してメモリセルに結合され得る。同様に、ワード線 1 6 は、トランジスタ 4 2、4 4 を通してメモリセル 1 0 に結合され得る。

## 【0016】

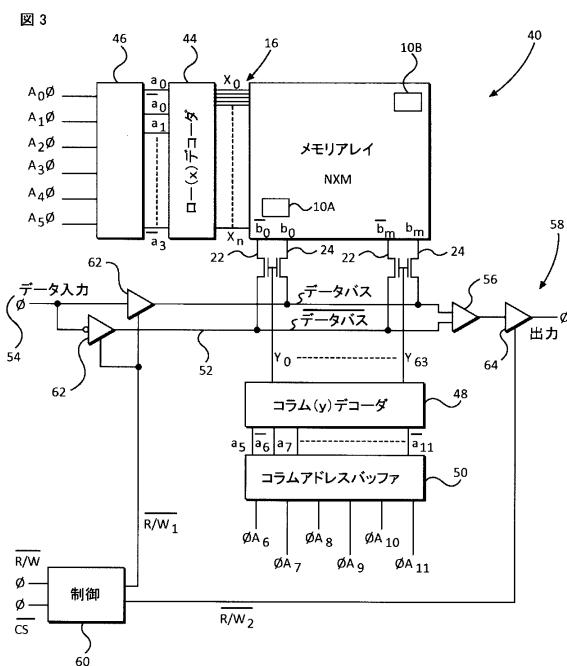

[0021] メモリセルアレイ 4 0 もまた、従来そのようなメモリセルアレイと関連付けられる制御論理工レメントであるものとして、産業においてよく理解されている。そのような制御論理工レメントは、図 3 におけるメモリセルアレイ 4 0 と関連付けられて例示される。特に、メモリセルアレイ 4 0 は、ワード線 1 6 によってローデコーダ 4 4 に結合される。ローデコーダ 4 4 は、ロードレスバッファ 4 6 に結合され得る。メモリセル 4 0 はさらに、ビット線 2 2 およびビット線バー 2 4 によってコラムデコーダ 4 8 に結合される。コラムデコーダ 4 8 は、コラムアドレスバッファ 5 0 に結合され得る。データバス線およびデータバスバー線 (bar line)

## 【数 2】

(*data bus*)

を有するデータバス 5 2 は、ビット線 2 2、2 4 にデータ入力 5 4 を結合する。データバス 5 2 はさらに、信号を出力 5 8 へ供給するセンス増幅器 5 6 へ結合し得る。制御論理 6 0 は、入力バッファ 6 2 および出力バッファ 6 4 を制御し得る。

## 【0017】

[0022] ビット線 2 2、ビット線バー 2 4、およびワード線 1 6 は、メモリセルアレイ 4 0 内の遠隔のメモリセル 1 0 へ到達するためにより長くなっているため (たとえば、下方左のコーナーにおけるメモリセル 1 0 A は、上方右のコーナーにおけるメモリセル 1 0 B と比較して相対的に短い線 1 6、2 2、2 4 を有する)、線 1 6、2 2、2 4 の物理的な特徴は、容量性のおよび抵抗のロスをもたらし、それは、それらの線に適用された電圧が要求される仮説の最低電圧より上に上げられる (elevated) ことを要求する。そのような上げられた電圧はバッテリ寿命を低減し、廃熱 (waste heat) を生成し、さもなければ望ましくないと考慮される。

## 【0018】

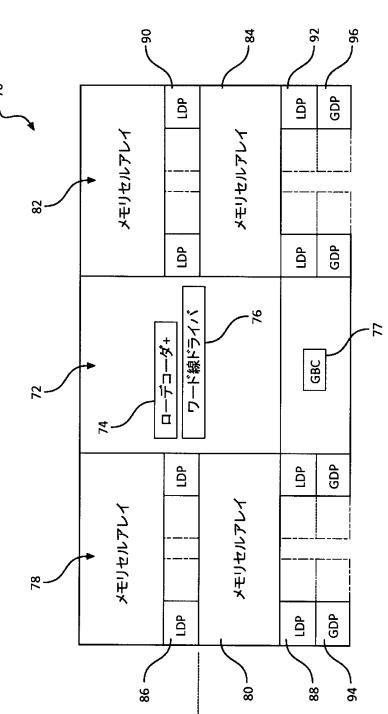

[0023] ビット線 2 2 の長さを短くするための 1 つの解決策は、ビット線バー 2 4 およびワード線 1 6 がいわゆる「バタフライ」構成でメモリセルアレイを配列する (arrange) ことである。すなわち、メモリセルアレイは制御論理工レメントのどちらかの側上に配置される。比喩を続けると、制御論理は、バタフライの「胸部」となり、メモリセルアレイは「羽」である。2 次元 (2 D) バタフライ RAM 7 0 の典型的な実施形態の簡略化されたブロック図が図 4 において例示される。バタフライ RAM 7 0 は、ローデコーダ 7 4 およびワード線ドライバ 7 6 ならびにグローバルブロック制御 (GBC) ユニット 7 7 を有するコア 7 2 を有する。GBC は、メモリの入力および出力のための特定の読み取り / 書き込みマルチプレクサを選択するためにすべての処理論理を有する。コア 7 2 は、複数のメモリセルアレイ 7 8、8 0、8 2、8 4 に隣接していることがあり得る。各メモリセルアレイ 7 8、8 0、8 2、8 4 は、それぞれローカルデータバス (LDP) 8 6、8 8、9 0、9 2 を有する。LDP 8 6、8 8、9 0、9 2 は、任意のセンス増幅器 (たとえば、センス増幅器 5 6) および任意のマルチプレクサ (mux) ならびにメモリセルを制御するための実際のドライバを含み得る。コア 7 2 の各側は、グローバルデータバス (GDP) 9 4、9 6 を有することがあり得、それはバタフライ RAM 7 0 のための入力および出力を含む。しかしながら、1 つの GDP 9 4、9 6 のみが側ごとに必要とされる。

10

20

30

40

50

## 【0019】

[0024] このように LDP 86、88、90、92 を位置づけること (placing) によって、ビット線 22、ビット線バー 24、およびワード線 16 (図 4 に図示せず) の長さが短くされる。これらの線 22、24、16 を短くすることは、従来のメモリセルアレイ 40 と比較して、RAM 70 を動作するために必要とされる電圧レベルを低減する。加えて、より短い線を有することによって、クロックスキュー (clock skew) が最小化され得る。

## 【0020】

[0025] 2D バタフライ RAM 70 の利点が目覚ましい一方で、3DIC 技術の到来は、線の長さを低減することにおけるさらに優れた改善を可能にし、メモリのフットプリントを低減し、回路設計者 (circuit designer) の必要に従ってメモリデバイスをカスタマイズすることによって縮小化を改善する。3DIC 技術の使用は、バタフライ RAM 70 の「羽」を、同一のメモリ記憶容量が維持されている間、全体的なフットプリントが半分にされる (またはより多く) ように、一方の上にもう一方が折り重ねられること (to be folded one atop the other) を可能にする。加えて、異なる製造技法は、メモリの異なるフレーバーが異なるティア上で提供されることを可能にするために 3DIC の異なるティア間で使用され得る。

10

## 【0021】

[0026] この点に関して、図 5 は第 1 のティア 102 および第 2 のティア 104 を有する 3D バタフライ RAM 100 を例示する。より多くのティアが提供され得ることが理解されるべきである (図示せず)。ティア 102、104 間の間隔は、RAM データバンク (ビットセルアレイとも称される) 106、108、110、112、がどのようにコア 114 のいずれかの側へ拡張するかを表すためにいくらか誇張されている。また、例示されているものは、第 1 のティア 102 からコア 114 内の第 2 のティア 104 へ拡張している MIV 116 の定型化された (stylized) 表現である。図示されてはいないが、追加の MIV がコア 114 の外側のティア 102、104 間に存在することがあり得る。2D バタフライ RAM 70 について、ローデコーダ 118、ワード線ドライバ 120 および GBC 122 がコア 114 内に配置される。各 RAM データバンク 106、108、110、112 は、それぞれの LDP 124、126、128、130 を有する。加えて、GDP 132、134 は第 2 のティア 104 内に配置され、それは、図示されるように、3D バタフライ RAM 100 の底面 (bottom) 上にある。代替の実施形態において、GDP 132、134 は第 1 のティア 102 にあり得、したがって 3D バタフライ RAM 100 の最上部 (top) 上にあり得る。

20

## 【0022】

[0027] 実施において、ローデコーダ 118 およびワード線ドライバ 120 ならびにコア 114 内の GBC 122 のアクセス論理を、RAM データバンクの折り重ねられる特性とともに置くことによって、ワード線 16、ビット線 22、およびビット線バー 24 (図 5 に図示せず) のためにより短いワイヤの長さが達成される。より短いワイヤの長さは、メモリの読み取る / 書き込むアクセス回数 (memory read/write access times) を増加させ、低減された線の後部の容量 (back-end-of-line capacitance) を通して動的電力を節約する。RAM データバンクの折り重ねること (folding) はまた、増加された濃度およびより小さいダイおよび包装経費をもたらす、より小さいダイエリアをもたらすことができる。包括的な (generic) RAM として説明されたが、動的 RAM (DRAM) と SRAM の両方が本開示の利益を享受し得る。

30

## 【0023】

[0028] ここで開示されている実施形態に従う論理区画およびビットセルを有するモノリシック 3D RAM アレイアーキテクチャは、任意のプロセッサベースのデバイス内に提供され得る、あるいは任意のプロセッサベースのデバイスに統合され得る。例は、限定なく、セットトップボックス、娛樂ユニット、ナビゲーションデバイス、通信デバイス、固定ロケーションデータユニット、モバイルロケーションデータユニット、モバイル電話

40

50

、セルラ電話、コンピュータ、携帯用コンピュータ、デスクトップコンピュータ、携帯情報端末（PDA）、モニタ、コンピュータモニタ、テレビ、チューナー、ラジオ、衛星ラジオ、音楽プレイヤ、デジタル音楽プレイヤ、携帯用音楽プレイヤ、デジタルビデオプレイヤ、ビデオプレイヤ、デジタルビデオディスク（DVD）プレイヤ、および携帯用デジタルビデオプレイヤを含む。

#### 【0024】

[0029] この点に関して、図6は、図5において例示されている3DバタフライRAM100を用いることができるプロセッサベースシステム140の例を例示している。この例では、プロセッサベースシステム140は、それぞれが1つまたは複数のプロセッサ144を含む1つまたは複数の中央処理ユニット（CPU）142を含む。CPU（複数を含む）142は、マスタデバイスであり得る。CPU（複数を含む）142は、一時的に記憶されたデータへの迅速なアクセスのためにプロセッサ（複数を含む）144に結合された1つまたは複数の3DバタフライRAM100を含むキャッシュメモリ146を有し得る。CPU（複数を含む）142は、システムバス148に結合され、プロセッサベースシステム140に含まれるスレーブデバイスとマスタデバイスを相互結合することができる。周知であるように、CPU（複数を含む）142は、システムバス148を介して、アドレス、制御情報、およびデータ情報を交換することによってこれらの他のデバイスと通信する。たとえば、CPU（複数を含む）142は、1つまたは複数の3DバタフライRAM100を含み得るメモリシステム150へバストランザクション要求を通信することができる。図6では例示されていないが、複数のシステムバス148が提供されることができ、ここにおいて各システムバス148が異なる骨組（fabric）の構成要素となる（constitutes）。

#### 【0025】

[0030] 他のマスタおよびスレーブデバイスが、システムバス148に接続されることができる。図6で例示されているように、これらのデバイスは、例として、メモリシステム150、1つまたは複数の入力デバイス152、1つまたは複数の出力デバイス154、1つまたは複数のネットワークインターフェースデバイス156、および1つまたは複数のディスプレイコントローラ158を含むことができる。入力デバイス（複数を含む）152は、それに限定されるものではないが、入力キー、スイッチ、音声プロセッサ、等を含む、任意のタイプの入力デバイスを含むことができる。出力デバイス（複数を含む）154は、それに限定されるものではないが、オーディオ、ビデオ、他の視覚インジケータ、等を含む、任意のタイプの出力デバイスを含むことができる。ネットワークインターフェースデバイス（複数を含む）156は、ネットワーク160へ、またはネットワーク160からデータの交換を可能にさせるように構成される任意のデバイスであることができる。ネットワーク160は、それに限定されるものではないが、ワイヤード（wired）またはワイヤレスネットワーク、私的または公的ネットワーク、ローカルエリアネットワーク（LAN）、ワイドローカルエリアネットワーク（WLAN）、およびインターネットを含む、あらゆるタイプのネットワークであり得る。ネットワークインターフェースデバイス（複数を含む）156は、あらゆるタイプの所望の通信プロトコルをサポートするように構成されることができる。

#### 【0026】

[0031] CPU（複数を含む）142はまた、1つまたは複数のディスプレイ162に送られる情報を制御するために、システムバス148を介してディスプレイコントローラ（複数を含む）158にアクセスするように構成され得る。ディスプレイコントローラ（複数を含む）158は、1つまたは複数のビデオプロセッサ164を介して表示されるように、ディスプレイ（複数を含む）162に情報を送り、それはディスプレイ（複数を含む）162に適したフォーマットに表示されるべきその情報を処理する。ディスプレイ（複数を含む）162は、それに限定されるものではないが、ブラウン管（CRT）、液晶ディスプレイ（LCD）、プラズマディスプレイ等を含む、あらゆるタイプのディスプレイを含むことができる。

10

20

30

40

50

## 【0027】

[0032] 当業者は、ここで開示された実施形態と関連して記述される様々な例示的な論理ブロック、モジュール、回路、およびアルゴリズムが、電子ハードウェア、メモリまたは別のコンピュータ可読媒体に記憶され、かつプロセッサまたは他の処理デバイスによって実行される命令、あるいはその両方の組み合わせとしてインプリメントされ得ることをさらに認識するだろう。ここで記述されるアービター(arbiter)、マスタデバイス、およびスレーブデバイスは、例として、あらゆる回路、ハードウェアコンポーネント、I C、またはI Cチップで用いられ得る。ここで開示されたメモリは、あらゆるタイプおよびサイズのメモリであることができ、あらゆるタイプの望まれる情報を記憶するように構成され得る。この互換性を明確に例示するために、様々な例示的なコンポーネント、ブロック、モジュール、回路、およびステップが、一般的にそれらの機能の観点から上述されている。そのような機能がどのようにインプリメントされるかは、特定のアプリケーション、設計選択、および／または全体のシステムに課された設計制限に依存する。当業者は、各々の特定のアプリケーションに関して、多様な方法で説明された機能をインプリメントすることができるが、このようなインプリメンテーションの決定は、本開示の範囲からの逸脱を引き起こしていると解釈されるべきでない。

## 【0028】

[0033] ここに開示された実施形態に関連して説明されたさまざまな例示的な論理ブロック、モジュール、および回路は、プロセッサ、デジタルシグナルプロセッサ(DSP)、特定用途向け集積回路(ASIC)、フィールド・プログラマブル・ゲート・アレイ(FPGA)または他のプログラマブル論理デバイス、ディスクリート・ゲートまたはトランジスタ論理、ディスクリート・ハードウェア・コンポーネント、あるいはここに説明された機能を実行するように設計されたこれらの任意の組み合わせで、インプリメントまたは実行され得る。プロセッサはマイクロプロセッサであり得るが、代わりとして、プロセッサは任意の従来のプロセッサ、コントローラ、マイクロコントローラ、またはステートマシンでもあり得る。プロセッサはまた、例えば、DSPおよびマイクロプロセッサとの組み合わせ、複数のマイクロプロセッサ、DSPコアと連結した1つまたは複数のマイクロプロセッサ、または任意の他のそのような構成の、コンピューティングデバイスの組み合わせとしてもまたインプリメントされ得る。

## 【0029】

[0034] ここで開示されている実施形態は、ハードウェアに記憶され、かつ、例えば、RAM、フラッシュメモリ、読み取り専用メモリ(ROM)、電気的プログラマブルROM(EPROM)、電気的消去可能プログラマブルROM(EEPROM(登録商標))、レジスタ、ハードディスク、リムーバルディスク、CD-ROM、あるいは当該技術分野において知られているコンピュータ可読媒体のあらゆる他の形態、に存在し得る命令およびハードウェアで実現され得る。典型的な記憶媒体は、プロセッサが情報を記憶媒体から読み取り、情報を記憶媒体に書き込むことができるようプロセッサに結合される。代替において、記憶媒体は、プロセッサに組み込まれ得る。プロセッサおよび記憶媒体はASIC内に存在し得る。ASICは、遠隔局内に存在し得る。代替において、プロセッサおよび記憶媒体は、遠隔局、基地局、またはサーバ内にディスクリートコンポーネントとして存在し得る。

## 【0030】

[0035] ここにおける典型的な実施形態のいずれかで記述されている動作ステップは、例および議論を提供するために記述されていることにも留意されたい。記述されている動作は、例示されているシーケンス以外の多くの異なるシーケンスで実行され得る。さらに、単一の動作ステップで記述されている動作は実際、多くの異なるステップで実行されることができる。加えて、典型的な実施形態で論じられている1つまたは複数の動作ステップが組み合され得る。フローチャート図で例示されている動作ステップは、当業者に容易に明らかになるように、多くの異なる変更に影響を受け得ることは理解されるべきである。当業者は、さまざまな異なる技術および技法のうちのいずれかを使用して、情報ならび

10

20

30

40

50

に信号が表現され得ることを理解するだろう。例えば、上の記述全体を通して参照され得るデータ、命令、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁場または磁性粒子、光場または光粒子、またはこれらの任意の組み合わせによって表され得る。

【0031】

[0036] 本開示の先の説明は、いずれの当業者でも本開示を作り出し、使用することを可能にさせるために提供されている。本開示に対するさまざまな変更は、当業者に容易に明らかになり、ここで定義される一般的な原理は、本開示の趣旨または範囲から逸脱することなく、他の変化に適用されることができる。従って、本開示は、ここに記載された例および設計に制限されることを意図せず、ここに開示された原理および新規な特徴に合致する最も広い範囲が与えられるべきである。 10

以下に、本願出願の当初の特許請求の範囲に記載された発明を付記する。

[C1] 第1の3次元(3D)集積回路(3DIC)(3DIC)ティア内に配設された第1のランダムアクセスメモリ(RAM)データバンクと、

前記第1の3DICティア内に配設された第2のRAMデータバンクと、

前記第1の3DICティア内に配設された前記第1のRAMデータバンクと前記第1の3DICティア内に配設された前記第2のRAMデータバンクとの間に配設された第1のグローバルブロック制御論理を備える第1のRAMアクセス論理と、前記RAMアクセス論理は、前記第1の3DICティア内に配設された前記第1のRAMデータバンクおよび前記第1の3DICティア内に配設された前記第2のRAMデータバンクへのデータアクセスを制御するように構成され、 20

を備える第1の3DICティアと、

第2の3DICティア内に配設された第1のRAMデータバンクと、

前記第2の3DICティア内に配設された第2のRAMデータバンクと、

前記第2の3DICティア内に配設された前記第1のRAMデータバンクと前記第2の3DICティア内に配設された前記第2のRAMデータバンクとの間に配設された第2のグローバルブロック制御論理を備える第2のRAMアクセス論理と、前記第2のRAMアクセス論理は、前記第2の3DICティア内に配設された前記第1のRAMデータバンクおよび前記第2の3DICティア内に配設された前記第2のRAMデータバンクへのデータアクセスを制御するように構成され、 30

を備える第2の3DICティアと

を備える、3D RAM。

[C2] 前記第1のティア内の前記第1のRAMデータバンクは、少なくとも1つの静的RAM(SRAM)データバンクで構成される、C1に記載の3D RAM。

[C3] 前記第1のティア内の前記第1のRAMデータバンクは、少なくとも1つの動的RAM(DRAM)データバンクで構成される、C1に記載の3D RAM。

[C4] モノリシック3DIC内に配設される、C1に記載の3D RAM。

[C5] 対応するRAMデータバンクが配設される少なくとも1つの追加の3DICティアをさらに備える、C1に記載の3D RAM。

[C6] 前記3D RAMのための入力および出力を提供するように構成されたグローバルデータパスをさらに備える、C1に記載の3D RAM。 40

[C7] 前記グローバルデータパスは、前記第1および第2の3DICティアのうちの一一番上の3DICティア上に配置される、C6に記載の3D RAM。

[C8] 前記グローバルデータパスは、前記第1および第2のティアのうちの一一番下の3DICティア上に配置される、C6に記載の3D RAM。

[C9] 前記第1のティアを前記第2のティアへ結合している複数のモノリシックインターティアバイアス(MIV)をさらに備える、C1に記載の3D RAM。

[C10] ICへ統合される、C1に記載の3D RAM。

[C11] セットトップボックス、娛樂ユニット、ナビゲーションデバイス、通信デバイス、固定ロケーションデータユニット、モバイルロケーションデータユニット、モバ

イル電話、セルラ電話、コンピュータ、携帯用コンピュータ、デスクトップコンピュータ、携帯情報端末（PDA）、モニタ、コンピュータモニタ、テレビ、チューナー、ラジオ、衛星ラジオ、音楽プレイヤ、デジタル音楽プレイヤ、携帯用音楽プレイヤ、デジタルビデオプレイヤ、ビデオプレイヤ、デジタルビデオディスク（DVD）プレイヤ、および携帯用デジタルビデオプレイヤから成るグループから選択されるデバイスへ統合される、C1に記載の3D RAM。

[C12] 第1の3次元（3D）集積回路（IC）（3DIC）ティア内に配設された第1のメモリ手段と、

前記第1の3DICティア内に配設された第2のメモリ手段と、

前記第1の3DICティア内に配設された前記第1のメモリ手段と前記第1の3DICティア内に配設された前記第2のメモリ手段との間に配設された第1のグローバルbrook制御論理を備える第1のRAMアクセス論理と、前記RAMアクセス論理は、前記第1の3DICティア内に配設された前記第1のメモリ手段および前記第1の3DICティア内に配設された前記第2のメモリ手段へのデータアクセスを制御するように構成され、

を備える第1の3DICティアと、

第2の3DICティア内に配設された第1のメモリ手段と、

前記第2の3DICティア内に配設された第2のメモリ手段と、

前記第2の3DICティア内に配設された前記第1のメモリ手段と前記第2の3DICティア内に配設された前記第2のメモリ手段との間に配設された第2のグローバルbrook制御論理を備える第2のRAMアクセス論理と、前記第2のRAMアクセス論理は、前記第2の3DICティア内に配設された前記第1のメモリ手段および前記第2の3DICティア内に配設された前記第2のメモリ手段へのデータアクセスを制御するように構成され、

を備える第2の3DICティアと、

を備える、3D RAM。

[C13] 前記第1の3DICティア内に配設された前記第1のメモリ手段は、RAMデータバンクを備える、C12に記載の3D RAM。

[C14] モノリシックICに内に配設される、C12に記載の3D RAM。

[C15] 前記第1のティアを前記第2のティアへ結合している複数のモノリシックインターティアバイアス（MIV）をさらに備える、C14に記載の3D RAM。

[C16] 前記RAMデータバンクは、少なくとも1つの静的RAM（SRAM）データバンクを備える、C13に記載の3D RAM。

[C17] 前記RAMデータバンクは、少なくとも1つの動的RAM（DRAM）データバンクを備える、C13に記載の3D RAM。

[C18] 対応するRAMデータバンクが配設される少なくとも1つの追加の3DICティアをさらに備える、C12に記載の3D RAM。

[C19] 前記3D RAMのための入力および出力を提供するように構成されたグローバルデータパスをさらに備える、C12に記載の3D RAM。

[C20] 前記グローバルデータパスは、前記第1および第2の3DICティアのうちの一番上の3DICティア上に配置される、C19に記載の3D RAM。

10

20

30

40

【図1】

FIG. 1

従来技術

【図2】

FIG. 2

従来技術

【図3】

FIG. 3

従来技術

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

---

フロントページの続き

(72)発明者 カマル、プラトウシュ

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72)発明者 ドウ、ヤン

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

審査官 上田 智志

(56)参考文献 特開平09-270191(JP, A)

特開2006-013337(JP, A)

国際公開第00/051184(WO, A1)

特開平03-205682(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8229, 21/8244,

27/10, 27/102,

27/108, 27/11

G11C 7/18, 8/14,

11/4096, 11/4097,

11/419