#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

## (19) World Intellectual Property Organization International Bureau

###

## (43) International Publication Date 30 June 2011 (30.06.2011)

# (10) International Publication Number WO 2011/079240 A1

- (51) International Patent Classification: *G09G 3/36* (2006.01)

- (21) International Application Number:

PCT/US2010/061954

(22) International Filing Date:

23 December 2010 (23.12.2010)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

61/289,622 23 December 2009 (23.12.2009) US 12/975,757 22 December 2010 (22.12.2010) US

(71) Applicant (for all designated States except US): SYNDI-ANT, INC. [US/US]; 18325 Waterview Parkway, Suite A

- 101, Dallas, Texas 75252 (US).

- (72) Inventors; and

(75) Inventors/Applicants (for US only): GUTTAG, Karl M. [US/US]; 6425 Rockbluff Circle, Plano, Texas 75024 (US). WALLER, Craig M. [US/US]; 10225 Bridgegate Way, Dallas, Texas 75243 (US). LUND, Joshua A. [US/US]; 6320 Belmont Ave., Dallas, Texas 75214 (US). RUSSELL, Andrew I. [JM/US]; 300 Legacy Drive, Apt. 823, Plano, Texas 75023 (US).

- (74) Agent: GUTTAG, Mark J.; VEDDER PRICE, PC, 875 15th Street NW Suite 725, Washington, District of Columbia 20005 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

— with international search report (Art. 21(3))

#### (54) Title: SPATIAL LIGHT MODULATOR WITH MASKING-COMPARATORS

(57) Abstract: Described is a device comprising a spatial light modulator comprising a plurality of comparators for computing a respective drive for each pixel of a plurality of pixels.

#### SPATIAL LIGHT MODULATOR WITH MASKING-COMPARATORS

#### CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application claims benefit of priority to U.S. Provisional Patent Application No. 61/289,522 to Guttag et al., entitled "SPATIAL LIGHT MODULATOR WITH CONDITIONAL PARALLEL PROCESSING," filed December 23, 2009, which is incorporated herein by reference in its entirety.

#### **BACKGROUND**

#### 10 Field of the Invention

[0002] The present invention relates to digital backplanes and various methods, systems and devices for controlling a digital backplane, light modulating elements and spatial light modulators.

#### Related Art

25

30

15 [0003] Display systems using microdisplay spatial light modulators (SLM) with solidstate illumination such as LEDs and lasers are used in many products today, but they have limitations in brightness and power efficiency. The brightness of the projectors with a given light source is also limited by the total amount of light-on time (time that the light sources can be turned on) that the SLMs allow.

20 SUMMARY

[0004] According to a first broad aspect of the present invention, there is provided a device comprising: a spatial light modulator comprising a plurality of masking-processors for computing a respective drive for each pixel of a plurality of pixels on the spatial light modulator, wherein each masking-processor comprises logic circuitry for logically and/or arithmetically comparing one or more multiple-bit pixel control values to one or more multiple-bit match values.

[0005] According to a second broad aspect of the present invention, there is provided a device comprising: a spatial light modulator comprising a plurality of processing elements for computing a respective drive waveform for each respective pixel of a plurality of pixels on the spatial light modulator, and a command sequencer for generating a sequence of one or more programmable match values, wherein each processing element of the plurality of processing elements comprises logic circuitry for logically and/or arithmetically comparing

one or more multiple-bit pixel control values for a respective pixel of the plurality of pixels to the one or more programmable match values for the respective pixel.

[0006] According to a third broad aspect of the present invention, there is provided a device comprising: a spatial light modulator comprising: a plurality of processing elements, a pixel control value storage, and an MRRAM array, wherein the plurality of processing elements, the pixel control value storage and the MRRAM array are arranged in an ERAM-aligned architecture.

5

10

15

20

25

30

**[0007]** According to a fourth broad aspect of the present invention, there is provided a method comprising the following steps: (a) controlling a leading edge of a drive pulse based on a first subset of bits of a pixel control value, and (b) controlling a trailing edge of that drive pulse based on a second subset of bits of the pixel control value to thereby generate a pixel drive waveform on a spatial light modulator that controls a pixel on a spatial light modulator for one multi-primary color, wherein the second subset of bits is different than the first subset of bits.

[0008] According to a fifth broad aspect of the present invention, there is provided a method comprising the following steps: (a) controlling a pixel of a spatial light modulator based on a first multiple-bit pixel control value, (b) ignoring one or more first bits of the first multiple-bit pixel control value to thereby form one or more ignored bits, and (c) storing one or more second bits for a second multiple-bit pixel control value in respective storage locations of the one or more ignored bits, wherein the pixel of the spatial light modulator is controlled based on the second multiple-bit control bit control value.

**[0009]** According to a sixth broad aspect of the present invention, there is provided a device comprising: a spatial light modulator, a multiple-bit-wide storage for multiple-bit pixel control values, and a masking-loader for writing a subset of bits within the multiple-bit pixel control values, wherein the multiple-bit pixel control values are used to control pixels on the spatial light modulator.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

[0010] For a more complete understanding of the present invention, and the advantages thereof, reference is now made to the following descriptions taken in conjunction with the accompanying drawings, in which:

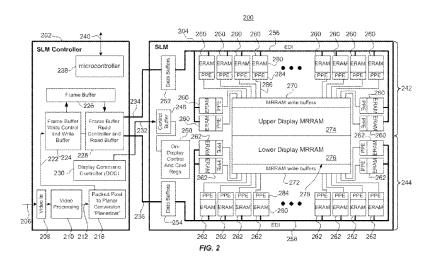

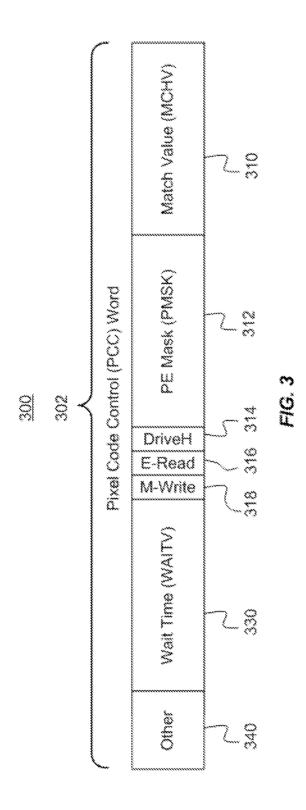

[0011] FIG. 1 is schematic diagram of part of an MRRAM;

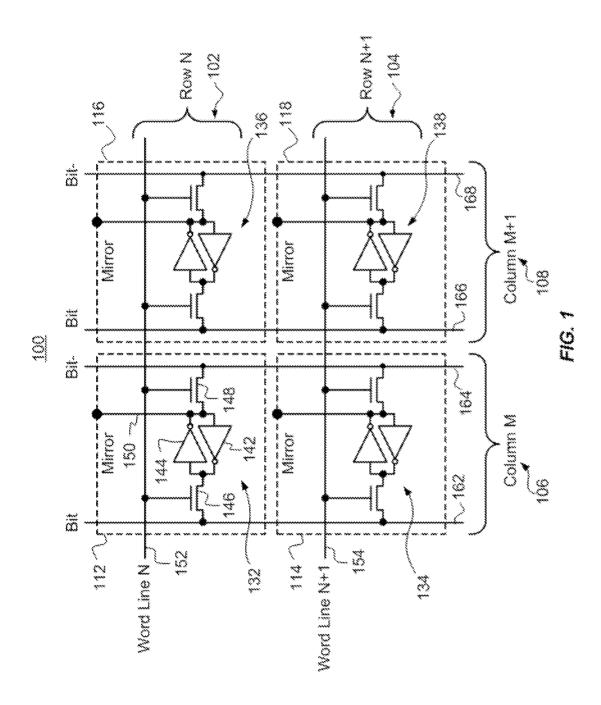

[0012] FIG. 2 is a block diagram showing an implementation of a display subsystem that includes a spatial light modulator (SLM) and a controller for the SLM in accordance with one embodiment of the present invention;

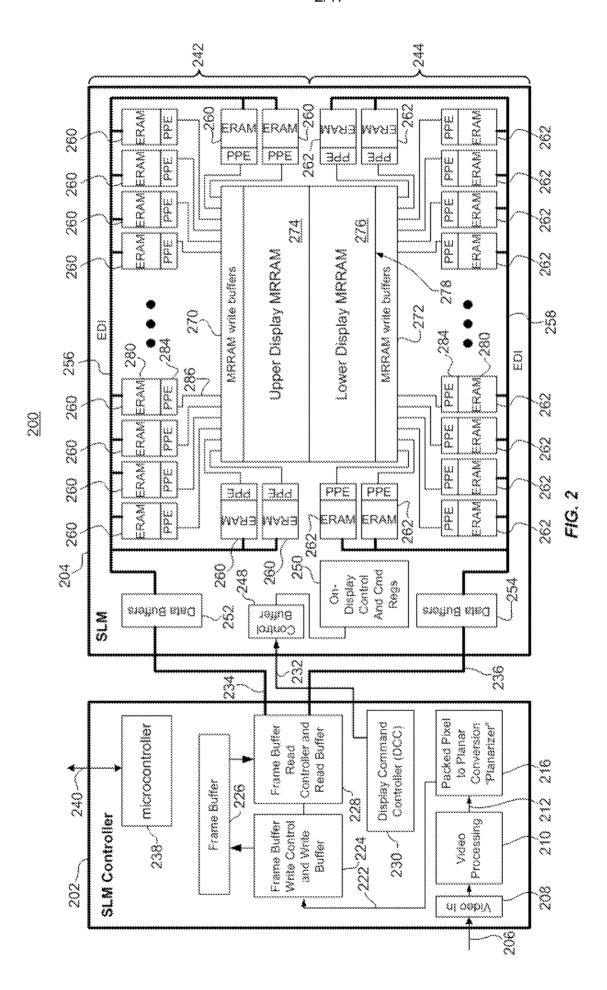

[0013] FIG. 3 is a diagram showing a pixel control code word held by a command register in accordance with one embodiment of the present invention;

5

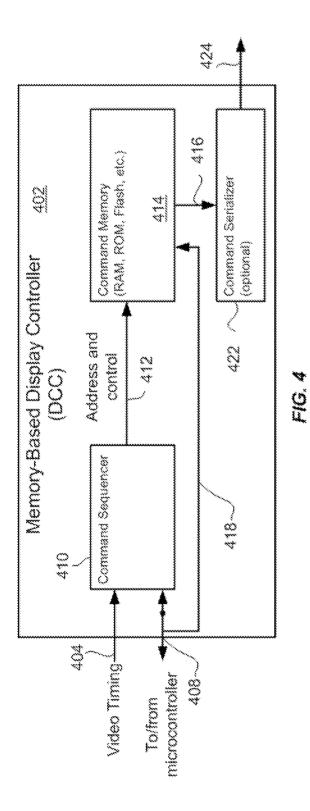

- [0014] FIG. 4 is a diagram showing the operation of a memory-based display controller in accordance with one embodiment of the present invention;

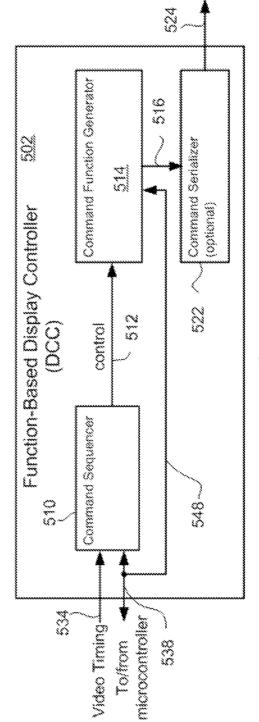

- [0015] FIG. 5 is a diagram showing the operation of a function-based display controller in accordance with one embodiment of the present invention;

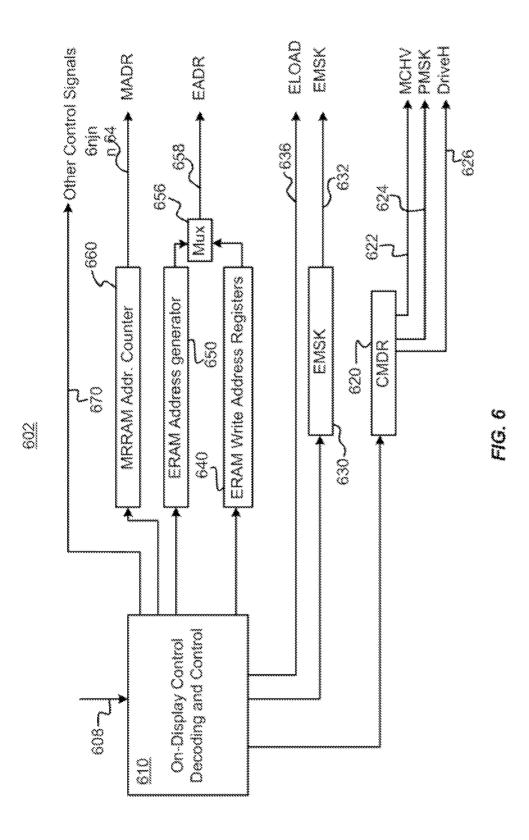

- 10 **[0016]** FIG. 6 is a diagram showing an on-display controller in accordance with one embodiment of the present invention;

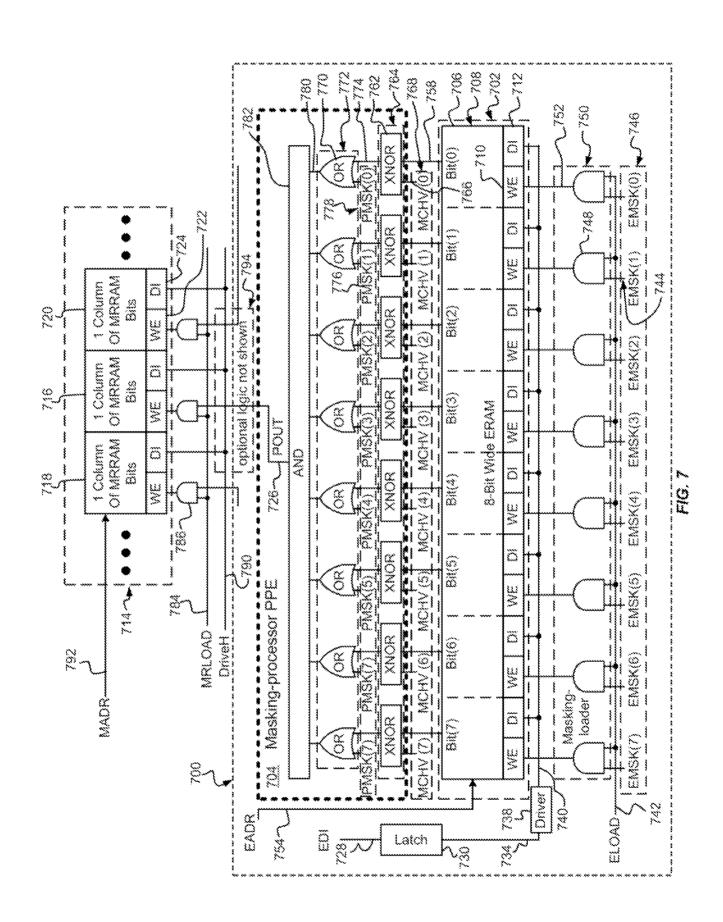

- [0017] FIG. 7 is a masking-comparator PPE in accordance with one embodiment of the present invention;

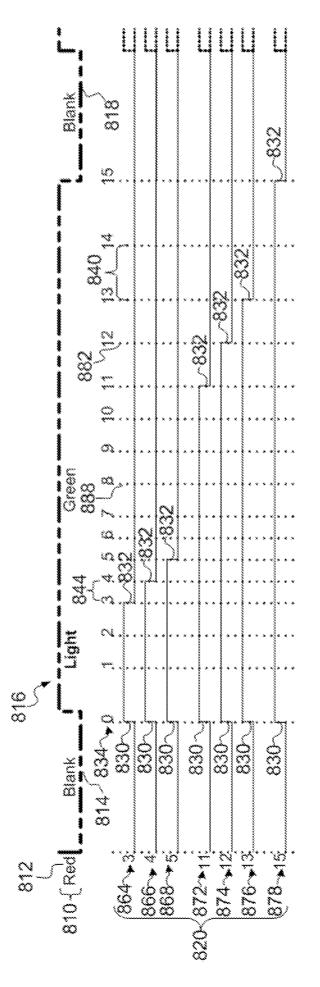

- [0018] FIG. 8 shows a pixel drive waveform for a drive method in accordance with one embodiment of the present invention;

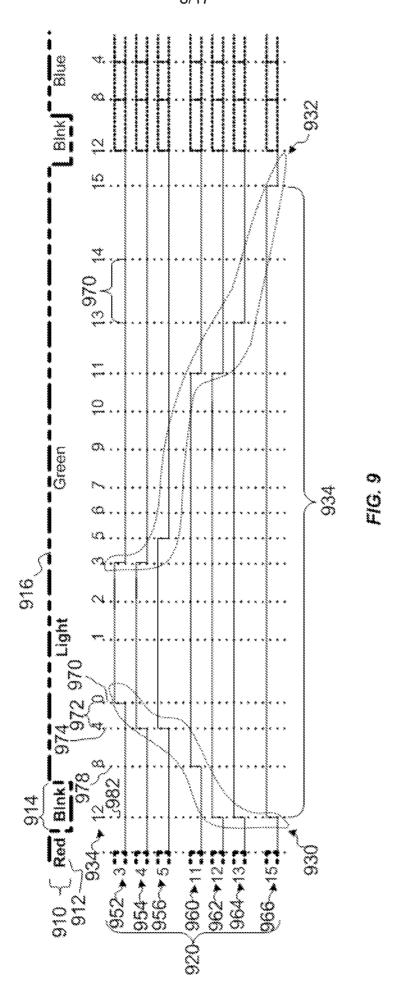

- [0019] FIG. 9 shows a pixel drive waveform for a drive method in accordance with one embodiment of the present invention;

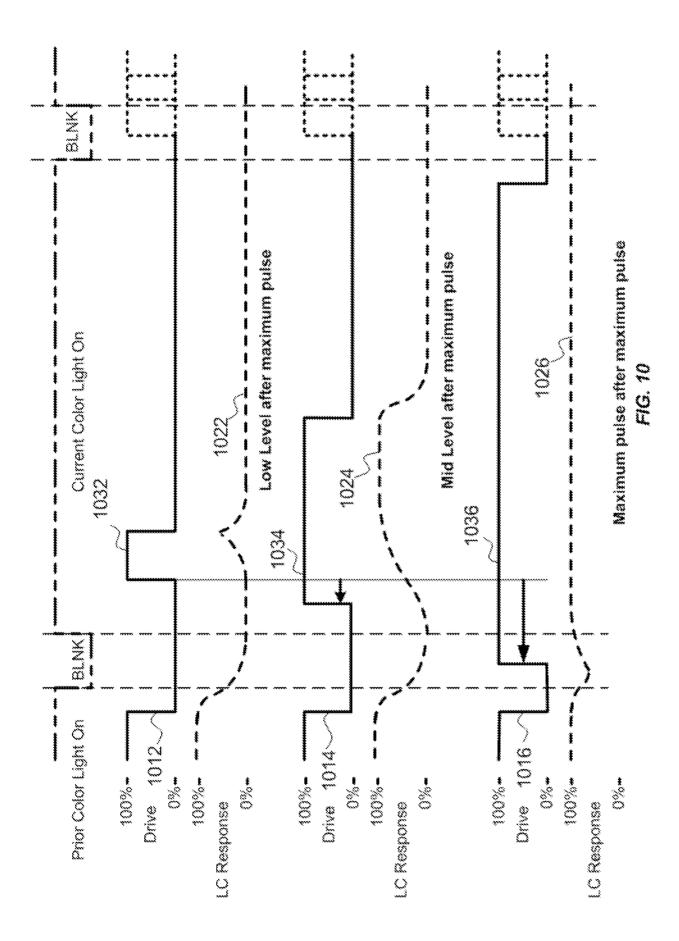

- [0020] FIG. 10 shows how a drive method in accordance with one embodiment of the present invention operates when the prior color field has a pulse width at or near the 20 maximum pulse width.

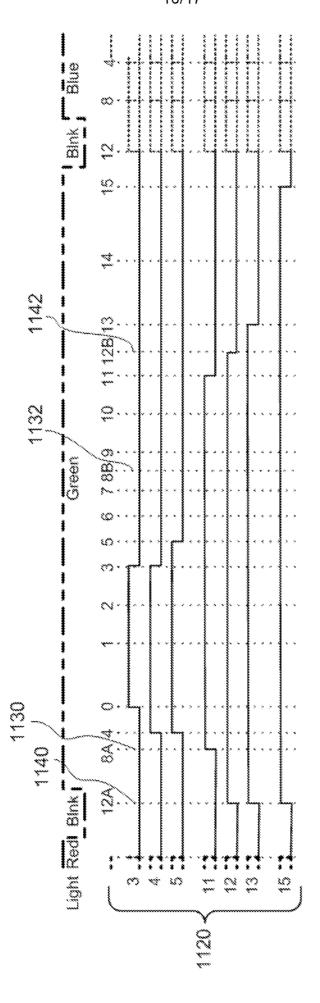

- [0021] FIG. 11 shows a pixel drive waveform for a drive method in accordance with one embodiment of the present invention;

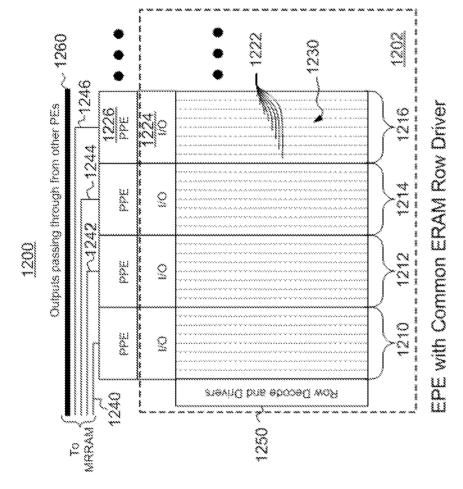

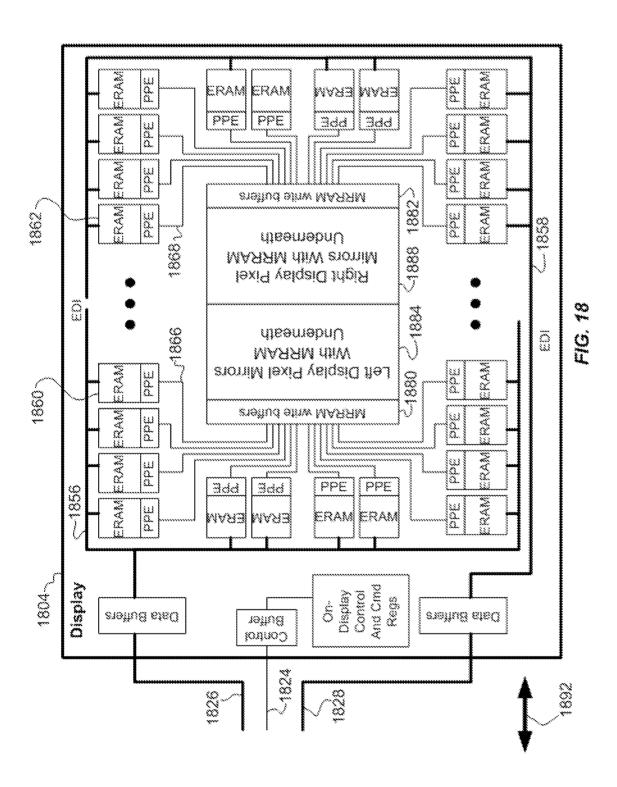

- [0022] FIG. 12 is a diagram showing how multiple parallel processing elements and ERAM may be configured with a common ERAM row driver wherein the PPEs are aligned to the ERAM (ERAM-aligned architecture);

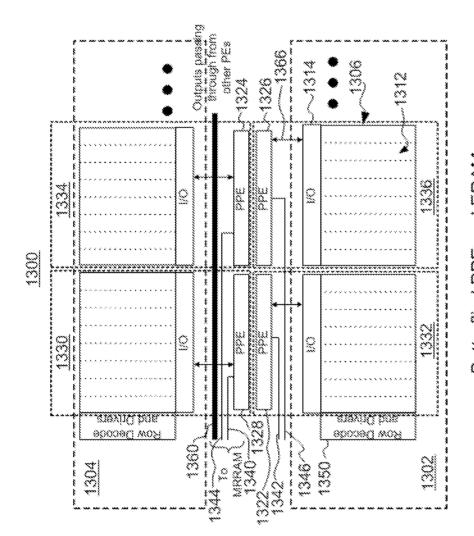

- [0023] FIG. 13 is a diagram showing a "butterflied-ERAM-and-processors architecture" in accordance with one embodiment of the present invention;

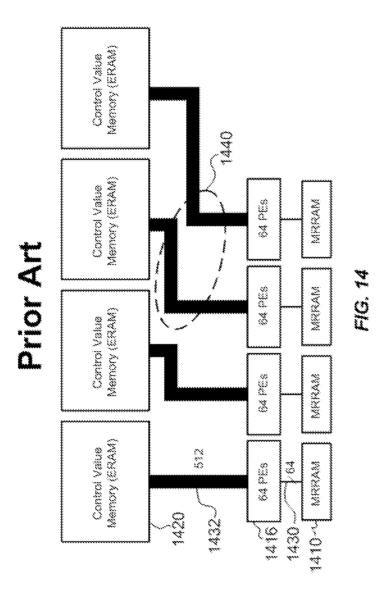

- [0024] FIG. 14 is a diagram showing the prior art connection of ERAM and processing elements;

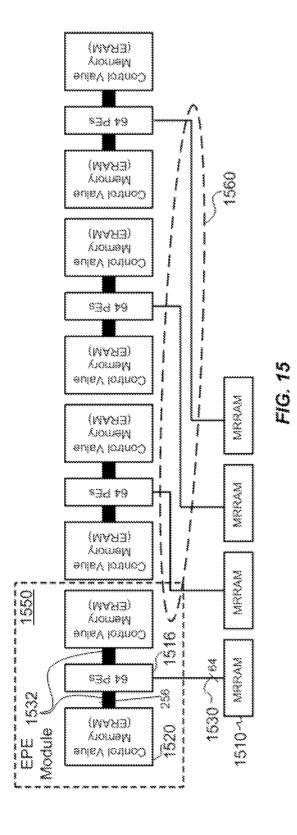

[0025] FIG. 15 is a diagram showing the connection of ERAM and processing modules in accordance with one embodiment of the present invention;

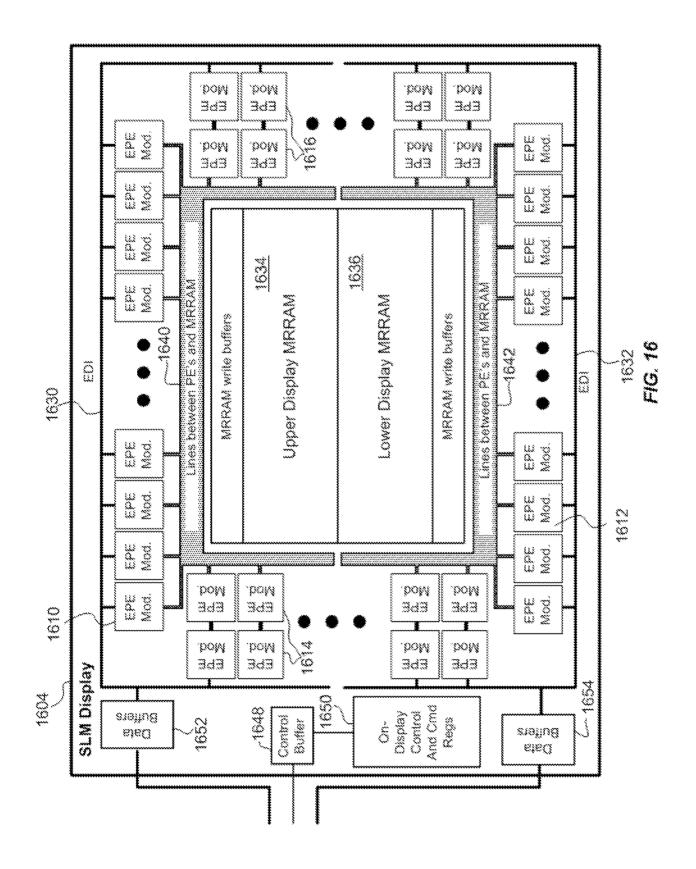

- [0026] FIG. 16 is a diagram showing an SLM with EPE processing modules in accordance with one embodiment of the present invention; and

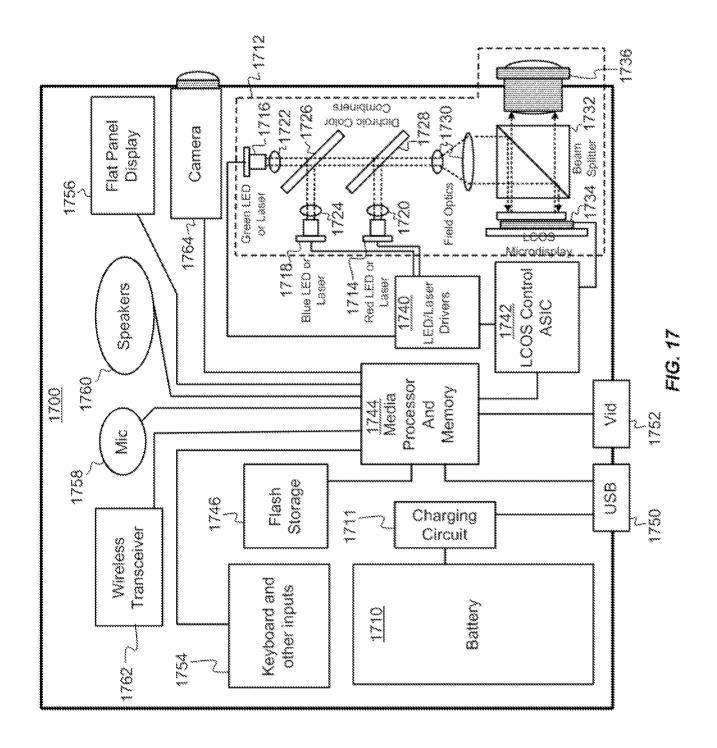

- 5 **[0027]** FIG. 17 is a system diagram showing the application of the SLM in accordance with some embodiments of the present invention.

- [0028] In the drawings nothing is meant to infer the size or scale of the various features, such as data blocks, relative to each other. Also, it should be noted that in some cases, various systems, processes, circuits, apparatuses, etc. have been shown in simplified form in the drawings to more clearly show particular features in the drawings.

#### **DETAILED DESCRIPTION**

[0029] It is advantageous to define several terms before describing the invention. It should be appreciated that the following definitions are used throughout this application.

#### **Definitions**

10

- 15 **[0030]** Where the definition of terms departs from the commonly used meaning of the term, applicant intends to utilize the definitions provided below, unless specifically indicated.

- [0031] For purposes of the present invention, it should be noted that the singular forms, "a", "an", and "the" include reference to the plural unless the context as herein presented clearly indicates otherwise.

- 20 [0032] For purposes of the present invention, directional terms such as "top", "bottom", "upper", "lower", "above", "below", "left", "right", "horizontal", "vertical", "up", "down", etc. are merely used for convenience in describing the various embodiments of the present invention. The embodiments of the present invention may be oriented in various ways. For example, the diagrams, apparatuses, etc. shown in the drawing figures may be flipped over, rotated in any direction, reversed, etc.

- [0033] For purposes of the present invention, a value or property is "based" on a particular value, property, the satisfaction of a condition, or other factor, if that value is derived by performing a mathematical calculation or logical decision using that value, property or other factor.

[0034] For purposes of the present invention, the term "1-of-N decoder" refers to the conventional meaning of the term 1-of-N decoder, i.e., a device/chip that takes an encoded bit pattern as input and activates one out of N possible outputs.

[0035] For purposes of the present invention, the term "array" refers to a 1-dimensional or 2-dimensional set of elements where each element has one or more bits of data. The array elements or even the bits within elements may or may not be stored physically next to each other. While a 2-dimensional array may imply some physical relationship in a 2-dimensional image or the like, it does not imply that the elements/bits are stored in a 2-dimensional array or, if they are stored in a 2-dimensional array, the physical array and the conceptual array have the same dimensions. For example an 2-dimensional (conceptual) image may be stored in a 1-dimensional physical memory array. Similarly a 1-dimensional conceptual array may be stored in a 2-dimensional physical memory array.

5

10

15

20

25

30

[0036] For purposes of the present invention, the term "available memory" refers to memory on a device that is not currently needed by some other process performed by the device.

[0037] For purposes of the present invention, the term "backplane" refers to a substrate that is used to build logic and control functions for an SLM. A backplane may be made of a semiconductor material, such as silicon, GaAs, etc. and it would include transistors that are deposited or grown on a substrate, such as the formation of transistors on a glass or other insulating substrate.

[0038] For purposes of the present invention, the term "bit plane buffer" refers to storing all or part of a bit plane in a physical memory location. A bit plane buffer may or may not store the bit plane in the same array order as it is seen in a visual display. In some embodiments of the present invention, the ERAM will store one or more bit plane buffers. In some embodiments a series of bit plane buffers may be stored as a series of circular buffers of varying sizes.

[0039] For purposes of the present invention, the term "bit plane format" or "planar format" refers to storing pixel data in such a way that one bit from each consecutive pixel of one color are stored or sent together. For example in a planer format, a 32-bit word of pixels would contain 1-bit position from 32 consecutive pixels whereas in packed pixel format, 24 bits would have all the bits for 8 bits per color of red, green, and blue. So in planar format, bits from consecutive bits of, say, bit 3 of red would be stored together for easy retrieval.

[0040] For purposes of the present invention, the term "bit selective compare" or "BSC" refers to a compare that could have some bits masked from comparison.

[0041] For purposes of the present invention, the term "bit-plane" refers to taking one bit position from an array of values to form a bit array that is of the same dimensions as the original array but with only one bit per element of the array. A "bit-plane" may be either physically separated in the case of "bit-plane organized" data, or it may be used to refer to the concept of a bit position within an array of values. A "bit plane" may also be an array of bits that correspond to an array of values, and the bit value may be based on some computation of the original value. A common use of a "bit plane" in graphics is to refer to any array containing one bit position from an array of multiple-bit pixel values, but the array does not have to comprise only pixel values. A "bit plane" refers to all the bits associated with one bit of one color for all the pixels. For the case of 24 bits per pixel, there would be 24 bit planes.

5

10

15

20

25

30

[0042] For purposes of the present invention, the term "bit-serial processing" refers to a method where a multi-bit computation is performed as a series of one-bit-wide operations where the result(s) from previous operations may be used as inputs to the next operation. Bit-serial processing may store each bit of precision at a different memory address.

[0043] For purposes of the present invention, the term "bit-serial processor" refers to a device that carries out bit-serial processing.

[0044] For purposes of the present invention, the term "color channel" will mean the information that defines a single color in an image. For example, the "red color channel" would have bits that define the bits associated with red color. While it is common to have color channels associated with the primary colors of red, green, and blue, a color field or color channel may also refer to a multi-primary color such as cyan, magenta, yellow or white.

[0045] For purposes of the present invention, the term "color crosstalk" will refer the case where in a field sequential color system, the drive of a prior color in a sequence has an effect on the next color in a sequence.

[0046] For purposes of the present invention, the term "color field" or "field" for short generally refers to the time period in which a single multi-primary color is displayed. For example, in field sequential color, the red field would be the time in and around the red field being displayed. The drive for a given color field may start before a given color illumination starts, but that drive would be associated with that color. There will generally be multiple fields (of different colors and/or the same color) per frame (see frame definition below).

When it will not be ambiguous, the term "color field" will also be used to generally refer to information associate with displaying a single color.

[0047] For purposes of the present invention, the term "color space" refers to space in the sense of multidimensional vector space formed by taking each color component as one dimension of the space.

5

15

20

25

30

[0048] For purposes of the present invention, the term "column" is used with respect to a memory array segment organized on bit lines. Often there are two bit lines per "column" of memory. Often there is a column decoder which functions to multiplex a plurality of columns to form a single output.

10 **[0049]** For purposes of the present invention, the term "command sequencer" refers a set of hardware or a processor that generates a series of control codes, including but not limited to match values for controlling a spatial light modulator.

[0050] For purposes of the present invention, the term "comparator" refers to a set of logic or processing that compares two or more numbers either arithmetically or logically to each other. A logical compare is a bit-wise compare of two or more inputs wherein there is no ordering or weighting of the inputs; for example, an equals compare is a logical compare that can be perform by logically ANDing series of XORs. With an arithmetic compare, the bit positions of each input are "weighted" (often given binary weighting) so that the order of the corresponding input bits of each input affects the result of the comparison. Examples of "arithmetic compares" would be "greater than," "less-than," "greater than or equal to," "less than or equal to," "positive," and "negative" among many others. For purposes of the present invention, a "comparator" may be hardware that directly produces a specific comparison, or it could involve, say, an arithmetic or Boolean operation followed by some logic that looks at the result. For example, a comparator may perform a subtraction and then use the sign bit to determine "greater than."

[0051] For purposes of the present invention, the term "comparing arithmetically" refers to a comparison that involves a carry ripple or simple carry operation. Greater-than, less-than, and greater-than-or-equal-to are some examples of "arithmetic comparisons."

[0052] For purposes of the present invention, the term "comparing logically" refers to an operation that takes two N bit values and inputs and generates one or more bits based on those bits a result of Boolean operations without a carry ripple path. An equal compare

commonly comprises an XNOR function between each pair of bits in the input and then an AND of the results of all the XNOR outputs and this is an example of "logical compare."

[0053] For purposes of the present invention, the term "current color field" will mean the color that is currently being displayed by a field sequential color display device.

5 **[0054]** For purposes of the present invention, the term "display" refers to either to the array of light modulating elements of the SLM that generates an image or, depending on the context, the image itself.

[0055] For purposes of the present invention, the term "display panel" or "panel" refers to a device that is a spatial light modulator or SLM. A display panel is a spatial light modulator and may be used synonymously with "spatial light modular" or "SLM" for purposes of the present invention.

10

15

20

25

[0056] For purposes of the present invention, the term "don't care" refers to one or more bits of input for a logic function that do not affect the output of the logic function.

[0057] For purposes of the present invention, the term "double frame buffer" will mean that at least part of two different frames/images are stored in a memory or region of memory at the same time. The data stored may be compressed/subsampled or uncompressed versions of the original image.

[0058] For purposes of the present invention, the term "drive waveform" or "pixel drive waveform" refers a digital or analog signal that changes with time and controls the light output of a pixel within a displayed image. In some embodiments, the drive waveform may consist of a single pulse or multiple pulses. Each pulse having a "leading edge" or "pulse start" and a "trailing edge" or "pulse end." The leading edge of a single pulse occurs first and the trailing edge occurs second. Pulses can be "positive" or "negative" so that the leading edge could be rising or falling and the corresponding trailing edge could be falling or rising. The time between the "leading edge" and "falling edge" of a pulse is its "pulse width." The terms "on" and "off" with respect to a "drive waveform" are purely relative but we will generally refer to "on" meaning that the drive will cause the light output to increase and "off" causes the light output to decrease. Drive waveforms can also be "subtractive" that the drive waveform causes a reduction in light.

30 **[0059]** For purposes of the present invention, the term "driving an electrode" refers to driving an electrode either directly or through other circuitry. The circuitry used in driving an electrode may include logic functions.

[0060] For purposes of the present invention, the term "ERAM" or "execution RAM" or "execution memory" refers to an array of memory bits that are on the spatial light modulator backplane that are at least in part used to compute the output of the backplane. The bits may also be used for other purposes as well. ERAM supports read and write operations like a normal RAM but may have special features to facility display control. Depending on the context, the word "ERAM" can refer to the entire ERAM or to some subset of ERAM bits in the same way the work RAM can be used.

5

10

20

25

30

[0061] For purposes of the present invention, the term "ERAM group" refers to a group of ERAM bits that share common addressing hardware which may include address decoding, word lines, and other control signals. An ERAM group may include multiple ERAM subarrays.

[0062] For purposes of the present invention, the term "ERAM sub-array" refers to a group of ERAM bits associated with a given processing element or group of processing elements.

15 **[0063]** For purposes of the present invention, the term "ERAM with processing element" or "EPE" refers to a module that has an ERAM sub-array and the bit-processing capabilities of a PE or PPE.

[0064] For purposes of the present invention, the term "ERAM-aligned architecture" or "ERAM alignment" refers to an SLM architecture where the processing logic is optimized to fit the ERAM structure. One or more processors are designed to closely fit the width of one or more ERAM arrays and their associated logic. This is in contrast to the prior art "MRRAM-aligned" architectures, where the processors are designed to fit the width of one or more MRRAM columns.

[0065] For purposes of the present invention, the term "field sequential color" refers to the situation where a spatial light modulator is illuminated using a sequence of colored light. This would be the case, for example, if the spatial light modulator is illuminated by a series of flashes from LEDs, lasers, or other colored light sources. Generally, at a minimum there are the color light primaries of red, green, and blue light, but there can additionally be light sources that are a combination of two or more colors by either turning more than one of the light sources on at a time, or by having a different light source, or by using spectral filtering or other means.

[0066] For purposes of the present invention, the term "frame" refers to one image in a sequence of images. In the context of field sequential color there will typically be at least one each of the red, green, and blue fields per frame and there may be more fields either repeating some of the primary colors and/or in the case of a multi-primary color system, with other colors such as yellow, cyan, magenta, and/or white.

5

10

15

20

25

[0067] For purposes of the present invention, the term "frame buffer" will mean a memory or region of memory where at least part of the representation of an image/frame is stored. This representation may be compressed/subsampled or uncompressed. The frame buffer may or may not have the entire image at any one time. The frame buffer may store different aspects of the image for different lengths of time. The frame buffer may be implemented as one or more circular buffers.

[0068] For purposes of the present invention, the term "frame rate" in the context of field sequential color refers to the rate at which the entire image may change. Commonly in U.S. standard television progressive scanned video, the frame rate will be about 60Hz. The "frame time" is one (1) divided by the frame rate (or about 1/60th of a second for U.S. standard television). In the context of field sequential color there will be multiple color fields in one "frame time."

[0069] For purposes of the present invention, the term "function generator" refers to a set of hardwired logic or a processor that generates a data output based on a set of control parameters. For example, it could take in binary number and output the log-base-2 output.

[0070] For purposes of the present invention, the term "gamma correction" refers to mapping input pixel values to output pixel values. In display devices, it is common to not want a linear change in the input value to have a linear response on the display.

[0071] For purposes of the present invention, the term "group of EPEs" is more than one EPE and its associated memory that may share some common logic or driver circuitry. For example, a group of EPEs might share row decode and drivers for the ERAM sub-arrays.

[0072] For purposes of the present invention, the term "hardware and/or software" refers to functions that may be performed by digital software, digital hardware, or a combination of both digital hardware and digital software.

30 **[0073]** For purposes of the present invention, the term "input pixel value" refers the numerical value associated with a pixel before the value is corrected or adjusted to compensate for the various system and device response characteristics.

[0074] For purposes of the present invention, the term "light modulating element" refers to an element/device for controlling the properties of a light source. For example, a light modulating element may control a light emitting source such as a phosphor dot, LED, etc., may control the way light is reflected by a mirror device, may control the polarization of light such as in an LCD or LCOS device, etc.

5

25

30

[0075] For purposes of the present invention, the term "line" refers to a horizontal or vertical display line of the mirror RAM array. This typically represents an array of pixels in which one dimensions of the array is 1, and the other is the full horizontal or vertical dimension of the mirror RAM array.

10 **[0076]** For purposes of the present invention, the term "liquid crystal display" or "LCD" refers to the conventional meaning of the term LCD device, such as a large direct view LCD television, as well as to related devices such as liquid crystal on silicon (LCOS) devices.

[0077] For purposes of the present invention, the term "logic circuitry" refers to circuitry that performs logical operations or is used to perform logical operations.

15 **[0078]** For purposes of the present invention, the term "machine-readable medium" refers to any mechanism that stores information in a form accessible by a machine such as a computer, network device, personal digital assistant, manufacturing tool, any device with a set of one or more processors, etc. For example, a machine-readable medium may be a recordable/non-recordable media (*e.g.*, read only memory (ROM), random access memory (RAM), magnetic disk storage media, optical storage media, flash memory devices, etc.), a bar code, an RFID tag, etc.

[0079] For purposes of the present invention, the term "masked-write" refers to a write operation in which some bit or group of bits is enabled or disabled from writing based on a separate mask value. In one embodiment of the present invention, the masking is supported on a bit-by-bit basis, but in other embodiments of the present invention a limited combination of bits may be masked. In one embodiment of the present invention, the data written is common broadcasted in some operations and the control of the outputs is based on whether various bits are enabled to be written. This in effect treats the storage bits as a "Set Reset" (SR) flip flop, that may be set, reset, or left unmodified. A masked-write is one way to implement a conditional update. An example of a RAM with masked-write capability in shown in FIG. 9 of U.S. Pat. No. 7,071,908 to Guttag et al., entitled "Digital backplane,"

issued July 4, 2006, and the entire contents and disclosure of this patent is incorporated herein by reference.

[0080] For purposes of the present invention, the term "masking-comparator" refers to arithmetic and/or logical comparison hardware, software or a combination thereof, that compares two or more multiple-bit numbers together and can selectively mask-off/ignore one or more bits of the inputs from affecting the comparison result.

5

10

15

[0081] For purposes of the present invention, the term "masking-loader" refers to a set of hardware that supports writing to selected bits within a multiple value in memory. In at least one embodiment of the present invention, the masking-loader combined with the masking-processor facilitates reusing/reallocating bits within a word of memory; for example it can be used for loading bits for the next color field while other bits within the word are being used for the current color field.

**[0082]** For purposes of the present invention, the term "masking-processor" refers to arithmetic and/or logical hardware, software or a combination thereof, that processes two or more multiple-bit numbers together and can selectively mask-off/ignore one or bits of the inputs from affecting the processing result. An example of a "masking-processor" is one that comprises a "masking-comparator." A "parallel processor" can be "masking-processor."

[0083] For purposes of the present invention, the term "masking-writer" refers to a writer that is able to perform masked-writes.

20 [0084] For purposes of the present invention, the term "match stage" or "stage" refers to a write or masked-write to some or all active lines in the MRRAM plus any delay/wait that is specified before the next match stage can start. The number of cycles a match stage takes is a function of the number of bits written to the MRRAM in a cycle, the number of active pixel segments in the display, plus any programmed wait time. In some embodiments, a match stage will write to all the pixel segments of the display, but it is possible that a match stage could write to only a subset of the pixel segments in a given match stage.

[0085] For purposes of the present invention, the term "match sub-stage" includes an ERAM read, compare and unconditional or conditional MRRAM write for all or part of a segment of pixels.

30 **[0086]** For purposes of the present invention, the term "match value" or "MCHV" refers to a multiple-bit quantity that is compared against the pixel control value. The result of this comparison is then used as part of the control for turning a pixel's output on or off, or to

leave the pixel's output in its current state. A match value can come from a counter, or it could come from a list of match values, or it may be computed in some other way. A series of match values that are not a simple count may be used to save memory and/or to generate pulses that are not simply a width based on a count. Match values can be arbitrarily programmable, such as would occur from storing in a memory table, or can be computed by one or more function generators. The term "multiple-bit-match value" refers to a match value that is a multiple-bit value/quantity or number.

5

10

15

20

[0087] For purposes of the present invention, the term "memory reallocation" or "reallocation" refers to storing a new value in a given memory location based on no longer needing that memory location for a previous value that was stored at that location. Some embodiments of the present invention support the reallocation of memory in order to require less total memory. In some embodiments of the present invention bits are reallocated within the storage for a multiple-bit value.

[0088] For purposes of the present invention, the term "microdisplays" refers to any of a class of display devices that are sufficiently small to require some form of magnification for human viewing for their intended use in a product. Microdisplays are one type of spatial light modulator.

[0089] For purposes of the present invention, the term "mirror RAM" or "MRRAM" refers generically to a memory that includes electrodes or other elements that drive a spatial light modulator. An MRRAM is a RAM that comprises "MRRAM bits." Depending on the context, the word "MRRAM" can refer to the entire MRRAM or to some subset of MRRAM bits in the same way the work RAM can be used.

[0090] For purposes of the present invention, the term "mirror RAM array" or "MRRAM array" is a collection of MRRAM bits organized into a memory array.

25 [0091] For purposes of the present invention, the term "mirror RAM bit" or "MRRAM bit" refers a storage bit that is used to drive an electrode that controls the output of a spatial light modulator. The MRRAM bit may drive an electrode through additional circuitry, including logic circuitry for inverting the output of the storage bit and/or voltage level shifting so that the electrode is based on the drive output bit.

30 **[0092]** For purposes of the present invention, the term "mirror RAM-aligned architecture" or "MRRAM-aligned" refers to an SLM architecture where the processing logic and its associated memory are organized to roughly match the columns of the display Mirror RAM.

Examples of this column structure display can be seen in U.S. Pat. No. 7,283,105 to Dallas et al., entitled "Microdisplay and interface on single chip," issued October 16, 2007; U.S. Pat. No. 7,113,195 to Willis et al, entitled "Generating pulse width modulated waveforms to digitally drive pixels," issued September 26, 2006; U.S. Pat. No. 7,071,908 to Guttag et al., entitled "Digital backplane," issued July 4, 2006; and U.S. Patent Application No. 2004/0179155 to Willis et al., entitled "LCOS imaging device," published September 16, 2004; the entire contents and disclosures of all of which are incorporated herein by reference.

5

10

15

20

25

30

[0093] For purposes of the present invention, the term "multi-primary color" refers to a single color component of a color image or color system. It is a generalization/superset of the term "primary color" that traditionally refers only to red, green or blue. A "multi-primary color" includes the traditional "primary colors" of red, green or blue, and it could also include some other color that is used to make up a color image, such as white, yellow, cyan, magenta, amber, etc. By this definition, the set of possible multi-primary colors is a superset of the traditional primary colors of red, green, and blue. There may also be cases where non-visible colors such as infrared or ultraviolet are treated as multi-primary colors. For purposes of the present invention, the term "primary color" will be synonymous with "multi-primary color," unless specified otherwise.

[0094] For purposes of the present invention, the term "pack sequential format" refers to storing or sending pixel data in such a way that all the bits for a series of bits for a single color are available at one time. In color plane format, 32 consecutive bits of memory could contain, say, four (4), 8-bit red values.

[0095] For purposes of the present invention, the term "pack sequential format" refers to storing or sending pixel data in such a way that a all the bits for a series of bits for a single color is available at one time. In color plane format 32 consecutive bits of memory could contain say four (4), 8-bit red values.

**[0096]** For purposes of the present invention, the term "packed pixel" or "packed format" refers to a way of storing or sending an "ordered group of bits" wherein all the bits are grouped together. For example, it is common to use 24 bits of data to specify a pixel with 8 bits of data for each of the primary colors of red, green and blue. In a packed pixel representation, all the bits of the entire pixel are sent together or can be read from memory in one or a very few operations.

[0097] For purposes of the present invention, the term "parallel processing element" or "PPE" refers to a "processing element" or "PE" that has some hardware that processes multiple-bit values in parallel ("bit parallel processing" as opposed to "bit serial processing") in what is considered a single clock period. Multiple cycle operations may be performed by a "parallel processing element" by doing one or more parallel operations over multiple cycles. In the case of an SLM, each parallel processing element may control a single pixel or more than one pixel with results being produce in one processor clock cycle or multiple processor clock cycles. A "processing element" or "PE" is a superset of the term PPE in that a PE may be either a bit-parallel or a bit-serial processor. For the purposes of the present invention, the terms "PE" and "PPE" will be used synonymously except in cases where it is necessary to specifically discuss bit-serial processing elements.

5

10

15

20

25

30

[0098] For purposes of the present invention, the term "parallel processing elements with selective masking" refers to a set of parallel processing elements where each of the processing elements acts as a mask input that causes the processing element to selectively mask (ignore) one or more inputs in computing a result.

[0099] For purposes of the present invention, the term "pixel" or "picture element" refers to a single element of a multidimensional display or a multidimensional image. When referring to part of a spatial light modulator, a "pixel" is a physical structure including but not limited to a small mirror in the case of LCOS or a DLP<sup>TM</sup> device, or it may be a single Light Emitting Diode (LED), or one or more transmissive element that controls light, or even an element of a printout from a printer. The term "pixel" also generally to refers to both a single element of the physical display and as a single element of a conceptual image.

[0100] For purposes of the present invention, the term "pixel control value" refers to any value or number which is used to control the output of one or more pixels. A "multiple-bit pixel control value" is a pixel control value that is a multiple-bit value or number.

[0101] For purposes of the present invention, the term "pixel control value storage" refers to the storage where one or more pixel control values are stored.

**[0102]** For purposes of the present invention, the term "pixel segment" or "segment" refers to a series of pixels that are either horizontally or vertically adjacent on the display that can be written simultaneously. In some embodiments, the segment may be exactly equal to the number of pixels in a horizontal or vertical line, but it could also be either part of a line or more than the number of pixels in one line.

[0103] For purposes of the present invention, the term "pixel value" refers to the numerical value associated with a pixel. When used without a pre-qualifier as "input or output." a pixel value refers to the current value of the pixel. A "pixel value" is a multiple-bit number that controls the light output and/or reflectance and/or polarization change of a pixel. Although generally 3 or more "pixel color values" are contained within a "pixel value," the term "pixel value" may also be used to refer to a "pixel color value" when it will not be ambiguous. In some embodiments, the "pixel value" will be modified to form a "modified pixel value."

5

10

15

20

25

30

[0104] For purposes of the present invention, the term "planarization" will refer to the process whereby pixels in "packed pixel format" are converted into "bit plane format." "Planarization hardware" takes in data in packed pixel format and output data in bit plane format.

[0105] For purposes of the present invention, the term "plane splitting" or "planarization" refers to the process of taking a series of multi-bit pack data (such as a packed pixel) quantities and splitting off the bits of one or more bit positions and repacking the split-off bits into multi-bit data quantities that only have the bits of one bit position for the series of data quantities. Plane splitting is a way to take "packed pixel" arrays and convert them into "bit plane organized" arrays. Plane splitting may be done on the whole array or on only some subset of the array. Plane splitting is one of many ways in which incoming pixel data may be reformatted (reorganized) for more efficient data processing or display manipulation.

[0106] For purposes of the present invention, the term "primary color" or "color" may refer to the usual notion of primary color, that is, one of red, green or blue. However, in systems that treat other colors as independent, such colors may be treated as primary colors for purposes of processing and display. For example, a system may for some reason have two green channels, both of which we would refer to as primary colors. A system may also treat a white, cyan, magenta or yellow channel as a primary color. Taken together, the primary colors plus any other colors processed like primary colors will be referred to as "multi-primary colors". For the purpose of the present invention, there is no difference between the terms "primary colors" and "multi-primary colors." There may also be cases in which non-visible colors such as infrared or ultraviolet are treated as primary colors.

[0107] For purposes of the present invention, the term "processing element" or "PE" refers to one of a number processing data paths that can operate at the same time on different

data. The term "element" when referring to a processing data path implies that there are multiple and often large numbers of the processors in some way sharing some amount of common control but working on different data. The processing data path can include logical and/or arithmetic processing that produces either a single bit or multiple-bits of results or outputs. Processing may take multiple cycles to produce an output and may produce intermediate results in the process of producing an output(s). In the case of an SLM in which the PEs are used to control the drive waveforms for pixels, i.e., an "SLM parallel processor," the output of each processing element may control a single pixel or more than one pixel with results being produced in one processor clock cycle or multiple processor clock cycles. A PE can take the form of a bit-serial PE that takes multiple cycles to process multiple-bits or a parallel processing element or "PPE" that can compute a result based on multiple-bits in what is considered a "single" cycle. For the purposes of the present invention, the terms "PE" and "PPE" will be used synonymously except in cases in which it is necessary to specifically discuss bit-serial processing elements.

5

10

20

25

30

15 **[0108]** For purposes of the present invention, the term "processing mask," abbreviated "PMSK," is one or more bits that make one or more bit positions from being processed. In the case of an arithmetic or logical comparison, it causes the corresponding bits to be ignored by the comparison.

[0109] For purposes of the present invention, the term "programmable match value" is a match value that can be matched to some value other than a simple up or down count. A programmable match value may be from a table or set of addresses in memory, or it may be from one or more function generators, or it may be generated by a computer.

**[0110]** For purposes of the present invention, the term "programmable match value sequencer" refers to is a unit that provides match values as needed, and it may be programmed with a predetermined sequence of values or it may compute these values. A programmable match value sequencer may be capable of providing non-sequential match values or sequential match values as needed.

**[0111]** For purposes of the present invention, the term "raster process" refers to the conventional meaning of the term "raster process," i.e., a process involving a series of steps in which a first line of pixels are processed and then subsequent lines of pixels are processed. Sometimes a raster process will process more than one line in parallel. Sometimes, but not always, a raster process processes lines or rows sequentially from say either top down,

bottom up, middle to the outside (in the case of a dual rasters starting in the middle), left to right, right to left or in some other order.

[0112] For purposes of the present invention, the term "row" is used with respect to a memory array segment organized on word-lines (WLs). When the term "row" is used with respect to an image, it will mean a line of pixel as would be part of a raster process.

5

10

15

20

25

30

[0113] For purposes of the present invention, the term "segment match" refers to one or more ERAM reads of pixel values for one vertical or horizontal segment of pixels and comparing each pixel value to a match value. A segment match may occur in a single cycle or may take multiple cycles. All or part of the bits of the pixel value may be used in the match. A mask may be used to choose which bits in the pixel and mask value are ignored.

[0114] For purposes of the present invention, the term "selectively masking one or more bits" means that there is processing hardware that supports masking one or more bits of input and, in doing so, only a subset of the input bits affect the result. For example, if there is an 8 bit-wide equal comparison and 3 of the bits are "masked," then only the 5 bits that are not masked will affect the equals compare. In effect, the masked bits of input become "don't cares" in terms of the result and are ignored.

[0115] For purposes of the present invention, the term "series of match stages" refers to a sequence in which multiple match stages are applied one after another. The end result of a series of match stages cause the individual MRRAM bits to apply or not apply a charge to a mirror or electrode that drives a pixel. The result of the changing charge on the mirror/electrodes causes an optical pixel drive waveform that modulates the light for each of the pixels.

[0116] For purposes of the present invention, the term "single pulse" refers not only to a single pulse, but to two or more pulses that are sufficiently close together to behave substantially as a signal pulse.

[0117] For purposes of the present invention, the term "SLM device" refers to any device that includes an SLM or is an SLM. Examples of SLM devices include visual display devices, SLMs, etc.

[0118] For purposes of the present invention, the term "spatial light modulator" or "SLM" refers to a one-, two- or multi-dimensional array of light modulating elements that control or modify incoming or emitted light and the circuitry included to control those elements on a device and all the control circuitry and memory on the device that is performing the spatial

light modulation. For example, each element of a spatial light modulator may change the direction of the incoming or emitted light, the intensity of the incoming or emitted light, the polarity of the incoming or emitted light, the wavelength of the incoming or emitted light, the focus of incoming or emitted light, etc. A spatial light modulator is a component in a display system that has an array of light modulating elements.

5

10

20

25

30

- **[0119]** For purposes of the present invention, the term "storage" or "storage medium" refers to any form of storage that may be used to store bits of information. Examples of storage include both volatile and non-volatile memories such as MRRAM, MRRAM, ERAM, flash memory, floppy disks, Zip<sup>TM</sup> disks, CD-ROM, CD-R, CD-RW, DVD, DVD-R, hard disks, optical disks, etc.

- [0120] For purposes of the present invention, the term "subset" refers to the conventional meaning of the term subset including an improper subset which would include all members of the set. For example, a subset of an array of circuits may include some or all of the circuits of the array of circuits.

- 15 **[0121]** For purposes of the present invention, the term "time base remapping" refers to using non-binary weighting of the timing control to weight the time of pulse width(s) based on incoming pixel values either instead of or in conjunction with remapping the pixel values from an input pixel values to an output pixel value such as is done with a "gamma table."

- [0122] For purposes of the present invention, the term "value" refers to a numerical quantity. The quantity may either be a conceptual infinite-precision number, or a member of a finite set of numbers. For example, the pixel value may be an integer in the range 0 to 255 and can be represented in a circuit as 8 bits, but in a mathematical description, the pixel value may be thought of as having arbitrary precision.

- [0123] For purposes of the present invention, the term "visual display device" or "visual display apparatus" includes any type of visual display device or apparatus such as a CRT monitor, LCD screen, LEDs, a projected display, a printer for printing out an image such as a picture and/or text, etc. A visual display device may be a part of another device such as a computer monitor, television, projector, cell phone, smartphone, laptop computer, tablet computer, handheld music and/or video player, personal data assistant (PDA), handheld game player, head mounted display, heads-up display (HUD), water screen upon which an image is projected, greeting card upon which an image is projected, cake upon which an image is

projected, global positioning system (GPS) receiver, automotive navigation system, dashboard, watch, microwave oven, electronic organ, automated teller machine (ATM), etc.

#### Description

5

10

15

20

25

[0124] Incorporated into some spatial light modulator (SLM) display devices is a controller including memory and processing for controlling pulse widths on pixels. Associated with the controller are: (1) a frame buffer that holds pixel data, (2) hardware that converts incoming video data into a form that can be readily processed by the SLM display device, and (3) control logic for the SLM display device. The controller may be physically built on one or more substrates. For example, it may be more cost effective to use a separate DRAM device for the frame buffer. Also, some or all of the control logic may be located on the controller device, the display device or some combination of the controller and the display device. Therefore, the splitting of functional blocks between the controller and the display device may be somewhat arbitrary.

[0125]Typical display panel architectures that have on-chip processing capability of multiple bit planes of data have a commonality in that various bit-planes of a specified pixel are loaded into a processing element that may include a comparator or other logic unit to produce displayable actions that are generated on the display pixels. It is further common that the processing elements are vertically aligned in columns above/below the pixels they are intended to influence, as would be their natural location, what for purposes of the present application is defined as a "mirror RAM-aligned architecture". It is also usual that the supporting memory bits that supply data to the processing elements are generally aligned (if not strictly aligned) to the pixel column or columns that they are intended to influence. This can be seen in U.S. Pat. No. 7,283,105 to Dallas et al., entitled "Microdisplay and interface on single chip," issued October 16, 2007; U.S. Pat. No. 7,317,464 to Willis et al., entitled "Pulse width modulated spatial light modulators with offset pulses," issued January 8, 2008; U.S. Pat. No. 7,071,908 to Guttag et al., entitled "Digital backplane," issued July 4, 2006; and U.S. Patent Application No. 2004/0179155 to Willis et al., entitled "LCOS imaging device" published September 16, 2004; the entire contents and disclosures of all of which are incorporated herein by reference.

30 **[0126]** A counter may be used with a comparator to control pulse widths, and this approach is used in U.S. Pat. No. 7,283,105 to Dallas et al., entitled "Microdisplay and interface on single chip," issued October 16, 2007; U.S. Pat. No. 7,317,464 to Willis et al.,

entitled "Pulse width modulated spatial light modulators with offset pulses," issued January 8, 2008; and U.S. Patent Application No. 2004/0179155 to Willis et al., entitled "LCOS imaging device" published September 16, 2004; the entire contents and disclosures of all of which are incorporated herein by reference. In contrast, the present invention provides a method that does not perform an unconditional compare to a counter, but rather uses masking-processors that can mask various bits of a pixel control value that compared to a programmable (not sequential) mask value in order to reduce the need for storage on an SLM.

5

10

15

20

25

30

previously described is to compare the pulse width value to a counter. The pulse is initialized to 1 if the pulse width is none/zero (or, alternatively, the pulse is initialed to 1 unconditionally and then quickly set to zero if the value is zero). At some time interval the counter increments by one each time and the comparison is remade. When the value of the pulse width equals the value of the counter, then the pulse is driven low. This method for use in driving pulse widths on pixels is described in U.S. Pat. No. 7,113,195 to Willis et al., entitled "Generating pulse width modulated waveforms to digitally drive pixels," issued September 26, 2006 (Willis et al. '195); and U.S. Pat. No. 7,283,105 to Dallas et al., entitled "Microdisplay and interface on single chip," issued October 16, 2007 (Dallas et al. '105), the entire contents and disclosures of both of which are incorporated herein by reference. It should be noted that both Willis et al. '195 and Dallas et al. '105 perform a full unconditional compare between all bits of the pixel/pulse value and a counter.

[0128] U.S. Pat. No. 7,071,908 to Guttag et al., entitled "Digital backplane," issued July 4, 2006 (Guttag et al. '908), shows how pulse widths on a spatial light modulator can be controlled with a series of partial comparisons. Guttag et al. '908 also shows how to do these comparisons with bit-serial processing. In one embodiment, the present invention uses parallel data processing hardware with conditional per-bit masking support to accomplish a similar function.

[0129] The present invention relates to a digital backplane and various methods, systems and devices for controlling a digital backplane, light modulating elements and spatial light modulators. Furthermore, the present invention has features that are particularly useful for supporting field sequential color where a single microdisplay controls the pixel intensity for more than one color that illuminates the panel in sequence.

[0130] In some embodiments of the present invention, an SLM device has incorporated into it memory and processing for controlling pulse widths for pixel drive waveforms. The controller has associated with it a frame buffer that holds the pixel data, hardware to convert incoming video data into a form that can be readily processed by the SLM device, and a controller for the SLM device. In some embodiments, the controller of the present invention may be physically built on one or more substrates. For example, it may be more cost effective to use a separate DRAM device for the frame buffer. In some embodiments of the present invention, some or all of the control logic may be on either the controller device, the SLM device or some split between them so the splitting of the functional blocks between the controller and the SLM is somewhat arbitrary.

5

10

15

20

25

30

[0131] In the prior art, field sequential color systems generally require at least a "double buffer" of the data to be displayed because most common display formats send RGB values of pixels at the same time, and field sequential color systems display only one color at a time and often repeat the same color more than one time per frame of data. While the prior frame is being displayed one color at a time, the next frame is being saved in the frame buffer. Because for higher resolutions it is generally cost and/or size prohibitive to place a double frame-buffer on the display backplane, it is desirable to send to the panel only bits associated with a single field/color at a time.

[0132] In some embodiments of the present invention, the buffering/double buffering of data of the incoming images will be held in memory that is separate from the SLM. This allows the large amount of data to be stored in a device technology that is better suited for making large memory arrays. Separating the main/large data buffer from the SLM also supports making a physically small panel device, which is advantageous in supporting small embedded projectors in devices such as mobile/cell phones. Having the main buffer separated from the panel then requires that the data be sent from the main frame buffer to the SLM. Some embodiments of the present invention reduce the bandwidth required to send data from the main frame buffer to the SLM.

[0133] With the main frame buffer storing all the pixel information at a location other than on the panel and with field sequential color, the panel will need data associated with the currently being displayed color to be stored on it to control the currently displaying color. Additionally, at some point the panel will need to receive some or all of the data associated with the next color to be displayed before it can start displaying the next color.

[0134] One way to support field sequential color with a separate main frame buffer would be to load all the data associated with one color/field during the blanking time. This may require the use of very high speed I/O's and/or may require an increase in the total amount of blanking time and reduce the percentage of light-on time and thus reduce brightness.

- 5 [0135] An alternate method that may be used to help overcome the possibility that not all bits can be sent during the blanking time is to bring in data before the blanking time begins. Without the concepts of the current invention, this may require additional storage on the SLM device. A brute force approach would be to have a full double buffer for a given color field or a total of 16 bits per pixel to double buffer 8 bits per color field. In this method, the next color to be displayed is loaded into a second buffer while the current color is being displayed using a first buffer. Once the next color starts working out of the second buffer, the first buffer is used to load the data for the following color.

- [0136] In one embodiment of the present invention, a panel may have one field buffer of memory on the SLM panel. This is equivalent to 8 bits per pixel (8 bits of red, 8 bits of green, 8 bits of blue, or 8 bits of gray/white). In this embodiment, there is just enough storage for a single field buffer of 8 bits per pixel. This single buffer is shared as the color being displayed changes.

15

20

- [0137] In a sequential color display system, the panel is responsible for displaying individual color fields one after the other. The sequential colors at a minimum are the primary colors of red, green and blue or RGB. A white field may be calculated that is a combination of the input RGB so that all three light sources can be turned on at the same time. In this case the sequential colors can be red, green, blue and white (RGBW), but many variations are possible including RGBW with or without subtractive primaries such a yellow, cyan, and magenta or other combinations of the primary colors.

- 25 [0138] It is often desirable for each color to have a variable amount of "on" time relative to the field sequential time slots. Between each of the field sequential time slots, it is typical to have blanking time. During this time, one form of light is turned off (R, G, B or W), and the panel will reconfigure for the next light source (R, G, B or W).

- [0139] In one embodiment, the present invention reduces the need for storage on the panel, reduces the amount of bandwidth to the panel, and provides a large percentage of light-on time while at the same time supporting very fine control of pulse width(s) used to control the light output.

[0140] In one embodiment, the present invention achieves most/all of the benefits of a full double buffer system, including lower bandwidth and shorter blanking time, while requiring less than a double buffer of a color field's data.

[0141] In one embodiment, the present invention provides a method that selective uses some bit and ignores other when comparing a match value to a pixel value to control pulse edges in order to reduce the need for storage on an SLM.

5

20

25

30

- [0142] In one embodiment, the present invention provides parallel data processing hardware with conditional per-bit masking support to support controlling edges of pulse widths using different sets of bits within a pixel's value.

- 10 [0143] In at least one embodiment of the present invention, the electrode may be a mirror that both reflects light and creates an electric field that causes liquid crystal to modify the polarization of polarized light. Using a semiconductor CMOS substrate, such as silicon, GaAs, etc. to control the Liquid Crystal in this way is known as liquid crystal on silicon (LCOS). In other embodiments, this electric field may be used to control a micro-mirror, as in the case of a Texas Instruments DLP<sup>TM</sup> device.

- [0144] FIG. 1 shows part of an MRRAM 100 having two (2) rows, i.e., rows 102 and 104, and two (2) columns, i.e., columns 106 and 108. In this example there are four (4) mirror/electrodes, i.e., mirror/electrodes 112, 114, 116, 118 that are driven by four (4) SRAM bits, i.e., SRAM bits 132, 134, 136, and 138, respectively. Each SRAM bit is composed of two (2) inverters, i.e., inverters 142 and 144, and two bit input pass-transistors, input pass-transistors 146 and 148. Each SRAM bit 132, 134, 136, or 138 combined with its respective mirror/electrode 112, 114, 116 or 118 constitutes an MRRAM bit. An output of each inverter 144 for each SRAM bit 132, 134, 136 or 138 of MRRAM 100 connects via a line 150 to a respective mirror/electrode 112, 114, 116 or 118. Each part of MRRAM 100 includes two (2) word lines, i.e., word lines 152 and 154, and four (4) true and false bit lines, i.e., true and false bit lines 162, 164, 166, and 168, just like a common 6-T SRAM.

- [0145] In addition to normal SRAM operation, the MRRAM in some embodiments can include "masked-writes" as described in U.S. Pat. No. 7,071,908 to Guttag et al., entitled "Digital backplane," issued July 4, 2006 (Guttag et al. '908), and the entire contents and disclosure of this patent is incorporated herein by reference.

- [0146] There may be additional transistors for voltage "level shifting" hardware to get a different voltage other than the SRAM bit's voltage on the mirror as described in Guttag et al.

'908. But, this is only one of many ways to implement a memory bit that may be used as part of an MRRAM bit. Additionally, different display technologies might require both the true and false electrodes.

[0147] FIG. 2 shows one implementation of a display subsystem 200 according to one embodiment of the present invention that includes an SLM controller 202 and an SLM 204. For the embodiment shown in FIG. 2, there is an upper and lower set of data buffers. With the upper/lower split shown, the upper and lower halves of the device can be nearly identical.

5

10

15

20

25

30

[0148] Incoming video data 206 may be in any of a number of formats, including but not limited to: digital red, green, and blue (RGB); component video in Y, Cr, Cb format; composite video such as NTSC; cell phone oriented MIPI DSI; television video HDMI; or any other analog or digital video format. Incoming video data 206 may be compressed or uncompressed data. Incoming video data 206 enters SLM controller 202 through video input buffers 208.

[0149] Video processing 210 may perform any of a number of video processing and/or enhancement operations. Video processing 210 may include transforming the data in one format or color space into a format for displaying. Video processing 210 may include the decoding of compressed data. Video processing 210 may also include taking, say, red, green, and blue data and generating values for other color fields such as yellow, magenta, cyan, and/or white. Video processing 210 may also include any of a number of adjustments of the incoming video data, such as gamma correction and color adjustment and correction, as well as adjustments related to characteristics of the liquid crystal and/or light sources.

[0150] Output 212 of video processing system 210 may be converted from a "packed pixel" representation by bit field planarizer 216 into a "planar" representation where bits are grouped such that there are strings of bits corresponding to one bit-plane of one color packed together. The result of planarizer 216 is sent out on planarizer output data lines 222. It should be noted that while some embodiments of SLM 204 may require this "planarization," it is also possible to provide an SLM, i.e., SLM 204, that can process pixel data and thus obviate the need for bit field planarizer 216. This planarization step on SLM controller 202 supports sending SLM 204 data an order that saves memory on SLM 204 in some embodiments of the present invention.

[0151] In the case of field sequential color or in the case where the display rate is different than the incoming video rate, there is a need to store most if not all of the data for an image, a

"frame," so the data can be sent to the display at the color field rate. In the case of field sequential color, some or all of the color fields may be displayed more than one per frame. A frame buffer write controller 224 intakes planarizer output data 222 and stores incoming planarizer output data 222 in frame buffer 226. In one embodiment of the present invention, frame buffer 226 has at least enough memory to store two or more complete or partial frames. This type of buffering for frame rate conversion is well understood in the art.

5

10

15

20

25

[0152] In at least one embodiment of the present invention, a more conventional full double frame buffer is not needed. The frame buffer instead comprises a collection of circular buffers. One circular buffer is used for each bit-plane, or sometimes for subsets of bit-planes. The size of each of these circular buffers may be different depending on how long that particular bit-plane needs to be stored. The size of a particular buffer can be set so that as it is being filled with data from the next frame, the data for the current frame is freed up in time to allow the buffer to not overflow. The data for the current frame can be freed up once that particular bit-plane is transmitted for the last time because the current frame does not need to be stored anymore.

[0153] Frame buffer read controller 228 takes data out of the frame buffer 226 and buffers the data to be sent to SLM 204. Frame buffer read controller 228 keeps track of data that is needed from the frame buffer 226 and generates the necessary addresses. Frame buffer read controller 228 may in some embodiments also generate the address of where the data is to be stored on SLM 204, or in other embodiments, the address generation may be done on SLM 204.

[0154] Display command controller (DCC) 230 generates display control information that will be used by SLM 204, as will be discussed below. The control information from the DCC 230 may be sent on a separate signal line 232 or may be alternatively sent over data lines/buses 234 and/or 236. Although the signal line 232 in FIG. 2 is shown as a single line for simplicity of illustrations, there may be multiple signal lines 232 from the DCC 230. Frame buffer read controller 228, and/or DCC 230 may in some embodiments generate the address of where the data is to be stored on SLM 204, or in other embodiments, the address generation may be done on SLM 204.

30 **[0155]** Microcontroller 238 is a programmable microcontroller. It is capable of running programs stored in ROM, Flash, RAM or other memory either inside the microcontroller itself or external to it (not shown). Microcontroller 238 may have various inputs and outputs

both from functions within SLM controller 202 and external inputs and outputs via I/O lines 240, as well as analog-to-digital and/or digital-to-analog converters and other functionalities. For example, video processing 210 may collect statistical data on the video data coming in and send that information to microcontroller 238, which in turn may process it to control an external I/O that would affect the drive of an LED. External light sensors could send a signal via I/O lines 240 to the microcontroller 238 and, after processing the signal, in turn could change some parameters that control SLM 204.

5

10

15

20

25

30

[0156] In some embodiments of the present invention, depending on the technology available, part or all of various functions of the SLM controller 202 may be implemented on SLM 204. Although SLM controller 202 of FIG. 2 shows only the basic functionality, in some embodiments of the present invention, other functionality may be incorporated onto the controller, including but not limited to digital-to-analog converters, analog-to-digital converters, and voltage-level-changing hardware.

[0157]Data lines/buses 234 and 236 are used to send the data that has been read from frame buffer 226 by frame buffer read controller 228 to SLM 204. The display process in display subsystem 200 is split in half into upper half 242 and lower half 244 of SLM 204. A control buffer 248 acts as the interface to bring control information into SLM 204. The control information is sent to the part of on-display controller 250. The type of control information sent is discussed in more detail below. Data lines/buses 234 and 236 connect to data buffers 252 and 254, respectively, in SLM 204. SLM 204 also includes upper and lower ERAM Data In (EDI) lines/buses 256 and 258, respectively; upper and lower ERAM and PPE processing (EPE) modules 260 and 262, respectively; upper and lower MRRAM write buffers 270 and 272, respectively; and upper and lower display pixel mirrors 274 and 276, respectively, of an active display 278. Each EPE module 260 or 262 comprises an ERAM 280 which acts as scratch memory for parallel processing elements (PPE) 284. Signal/control lines 286 connect each EPE module 260 to upper MRRAM write buffer 270 and each EPE module 262 to lower MRRAM write buffer 272. Results from EPE modules 260 are sent to the upper MRRAM write buffers 270, which in turn drive upper display pixel mirror 274. Results from EPE modules 262 are sent to the lower MRRAM write buffers 272, which in turn drive lower MRRAM array 276.

[0158] Although in the embodiment of the present invention shown in FIG. 2 various features of the SLM such as the data lines/buses, display pixel mirrors, MRRAM write buffers, etc. are shown as being oriented as upper and lower, other orientations of these

features are also possible. For example, these features of the SLM may be oriented as being left and right.

[0159] Shown in FIG. 2 is a signal line between each PPE and the upper or lower MRRAM buffers, but this is only for simplicity of illustration. For example, in some embodiments, there may be fewer signal lines that are time multiplexed. As will be explained later, while the drawing shows a single PPE 284 and ERAM 280 group together, in various physical embodiments, multiple PPEs 284 and/or ERAMs 280 can be grouped together. Additionally, while FIG. 2 shows each PPE 284 as having an output signal on signal/control line 286 that goes to MRRAM write buffers 270 and/or 272, in some embodiments as will be described later the results of two or more PPEs 284 may be combined together to form one or more output signals on signal/control line 286.

5

10

15

20

25

30

[0160] An example operation of display system 200 will now be explained. Video data 206 enters SLM controller 202, and various types of processing of the data may be optionally performed by video processing 210. This processing may include but is not limited to conversion from one display format to another, decompression if the video data is in a compressed format, color correction, image scaling, generating "white" fields and other multi-primary color fields, and image enhancement.

**[0161]** In the embodiment of the present invention shown in FIG. 2, the output of video processing 210 is in a "packed pixel" format. Bit field planarizer 216 converts packed pixel data into a series of bit-planes wherein multiple-bits for a single bit of a single color are put into groups of bits. It should be noted that in some embodiments, the SLM may be capable of using "pack-pixel" (without being planarized) data, and so the packed pixel to bit field planarizer 216 may not be necessary.

[0162] For a field sequential color system, video data 206 is generally received by video processing 210 in a pack-pixel format at the frame rate. Generally this frame of data is coming in at a rate that is slower than the "field rate" in a color sequential display system, and the data is formatted differently than SLM 204 can process to generate a display image. Therefore, frame buffer write control 224 stores the output of bit field planarizer 216 in frame buffer 226. While frame buffer 226 is called a "frame buffer," it may buffer up more or less data than is required for an entire frame.

[0163] Frame buffer read controller 228 reads data from frame buffer 226 for sending to SLM 204. In some embodiments it can be advantageous to read the data out of frame buffer 226 in an order that helps reduce the total storage required for ERAMs 280.

[0164] DCC 230 generates and sends pixel control codes (PCC) to the on-display controller 250. While a dedicated DCC may be used, the PCCs may be computed by a processor or other device.

5

10

15

20

25

30

[0165] DCC 230 also controls the overall coordination and control of the frame buffer write control 224 and frame buffer read control 228. It also can exchange data and control information with other controllers within the SLM controller 202, including but not limited to microcontroller 238, frame buffer write controller 224, and frame buffer read controller 228.

[0166] Frame buffer read controller 228 has associated with it data buffers that store data from frame buffer 226. Data is sent via data line/bus 234 and data buffers 252 on ERAM on EDI line/bus 256 to EPE modules 260. Data is also sent via data line/bus 236 and buffers 254 on ERAM on EDI line/bus 258 to EPE modules 262. Pixel data information is loaded into ERAM 280 and an associated PPE 284 conducts a series of operations on the data to control the pulse width(s). Each EPE module 260 or 262 or a group of EPE modules 260 or 262 computes results that can be used to turn one or more pixels in one line of active display 278 on or off either conditionally or unconditionally. These results are sent via signal/control lines 286 that connect EPE modules 260 to upper MRRAM write buffers 270 or connect EPE modules 262 to lower MRRAM write buffers 272.

[0167] It should be noted that in some embodiments of the present invention, there may be at least one EPE column of pixels for each of the upper half and lower half of the display. In other embodiments there may be more or less EPEs per column of pixels in each half of the display. In some embodiments, the pixels may be processed in blocks, and, therefore, the EPE may be processing multiple pixels within a block. Additionally, in some embodiments the results of multiple PPEs 284 may be combined to produce one or more signal/control lines 286.

[0168] In the configuration shown in FIG. 2, MRRAM is split upper and lower, but this is only one of several options, including splitting left and right or not splitting at all. With an upper-lower split, essentially the top and bottom work in parallel but have essentially the same functionality. Similarly, with a left-right split, essentially the left and right work in parallel but have essentially the same functionality. With either type of split, the two halves