(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2018-0004135

(43) 공개일자 2018년01월10일

- (51) 국제특허분류(Int. Cl.)

**H03F 1/02** (2006.01) **H03F 3/189** (2006.01)

**H03F 3/19** (2006.01) **H03F 3/21** (2006.01)

**H03F 3/24** (2006.01) **H03F 3/62** (2006.01)

**H03F 3/68** (2006.01) **H03F 3/72** (2006.01)

**H04B 17/21** (2014.01) **H04W 24/02** (2009.01)

- (52) CPC특허분류

**H03F 1/0205** (2013.01)

**H03F 1/0277** (2013.01)

- (21) 출원번호 10-2017-7032016

(22) 출원일자(국제) 2016년04월08일

심사청구일자 없음

- (85) 번역문제출일자 2017년11월03일

(86) 국제출원번호 PCT/US2016/026679

(87) 국제공개번호 WO 2016/178794

국제공개일자 2016년11월10일

- (30) 우선권주장

14/706,917 2015년05월07일 미국(US)

- (71) 출원인

**퀄컴 인코포레이티드**

미국 92121-1714 캘리포니아주 샌 디에고 모어하

우스 드라이브 5775

- (72) 발명자

**령, 라이 칸**

미국 92121-1714 캘리포니아주 샌 디에고 모어하

우스 드라이브 5775

**왕, 케빈 시이 화이**

미국 92121-1714 캘리포니아주 샌 디에고 모어하

우스 드라이브 5775

(뒷면에 계속)

- (74) 대리인

**특허법인 남앤드남**

전체 청구항 수 : 총 20 항

(54) 발명의 명칭 **출력 커플러를 가지는 저잡음 증폭기 모듈**

**(57) 요 약**

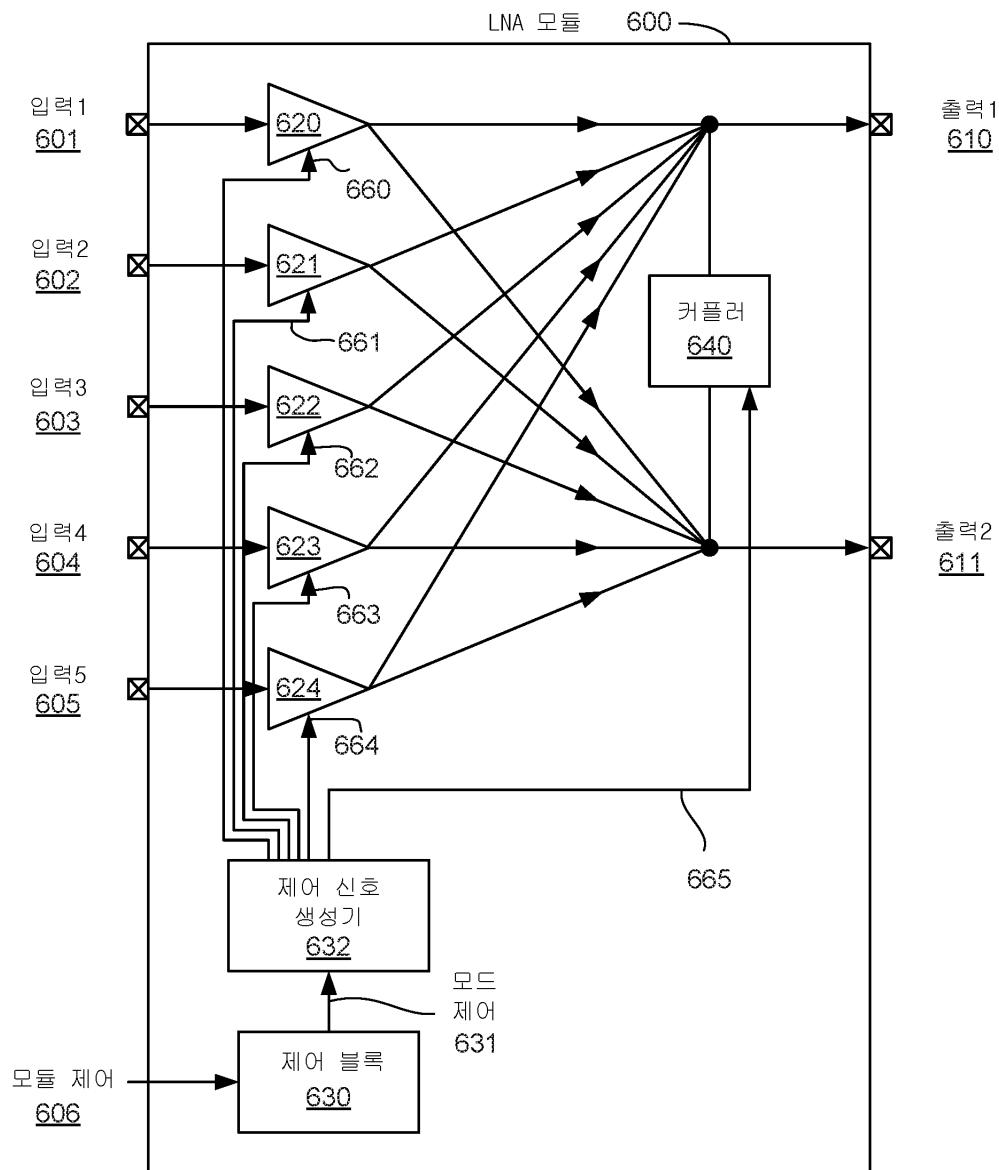

출력 커플러(640)를 가지는 증폭기 모듈(600)이 개시된다. 증폭기 모듈(600)은 복수의 입력 단자들(601-605) 및 2 또는 그 초과의 출력 단자들(610, 611)을 포함할 수 있다. 각각의 입력 단자는 독립적인 증폭기(620-624)의 입력에 커플링될 수 있다. 독립적인 증폭기들(620-624)로부터의 출력들은 2 또는 그 초과의 출력 단자들(610, 611)에 커플링될 수 있다. 증폭기 모듈(600)은 2 또는 그 초과의 출력 단자들(610, 611)을 함께 커플링하기 위하여 출력 커플러(640)를 포함할 수 있다. 신호는 제1 출력 단자(610)에 의해 수신되고 출력 커플러(640)에 의해 제2 출력 단자(611)에 커플링될 수 있다. 일부 실시예들에서, 2 또는 그 초과의 출력 단자들(610, 611)이 함께 커플링될 때, 독립적인 증폭기들(620-624)은 비활성화되거나 최소 이득 구성으로 동작될 수 있다.

**대 표 도** - 도6a

(52) CPC특허분류

*H03F 3/189* (2013.01)

*H03F 3/19* (2013.01)

*H03F 3/211* (2013.01)

*H03F 3/24* (2013.01)

*H03F 3/62* (2013.01)

*H03F 3/68* (2013.01)

*H03F 3/72* (2013.01)

*H04B 17/21* (2015.01)

*H04W 24/02* (2013.01)

(72) 발명자

판, 동령

미국 92121-1714 캘리포니아주 샌 디에고 모어하우

스 드라이브 5775

나라통, 츄챈

미국 92121-1714 캘리포니아주 샌 디에고 모어하우

스 드라이브 5775

## 명세서

### 청구범위

#### 청구항 1

장치로서,

복수의 증폭기들 – 각각의 증폭기는 입력 단자를 가짐 –;

복수의 출력 단자들 – 각각의 출력 단자는 2 또는 그 초과의 증폭기 출력들에 커플링됨 –; 및

상기 복수의 출력 단자들 중 적어도 2개의 출력 단자들을 함께 선택적으로 커플링시키도록 구성된 커플러를 포함하는,

장치.

#### 청구항 2

제1 항에 있어서,

상기 커플러는 상기 복수의 출력 단자들 중 제1 출력 단자에서 수신된 신호를 증폭하고 증폭된 신호를 상기 복수의 출력 단자들 중 제2 출력 단자에 제공하도록 구성되는,

장치.

#### 청구항 3

제1 항에 있어서,

상기 커플러는 모드 제어 신호의 제1 상태에 기반하여 상기 복수의 출력 단자들 중 적어도 2개의 출력 단자들을 함께 커플링하도록 구성되고, 그리고 상기 커플러는 상기 모드 제어 신호의 제2 상태에 기반하여 상기 복수의 출력 단자들 중 적어도 2개의 출력 단자들을 격리시키도록 구성되는,

장치.

#### 청구항 4

제1 항에 있어서,

상기 커플러에 의해 제공된 이득은 제어 신호에 기반하는,

장치.

#### 청구항 5

제1 항에 있어서,

제1 출력 단자는 제1 신호를 수신하도록 구성되고 제2 출력 단자는 상기 제1 신호를 출력하도록 구성되는,

장치.

#### 청구항 6

제5 항에 있어서,

상기 제1 신호는 교정 신호인,

장치.

#### 청구항 7

제1 항에 있어서,

상기 커플러는 양방향 증폭기를 포함하는,

장치.

#### 청구항 8

제7 항에 있어서,

상기 양방향 증폭기는 상기 장치의 동작 모드에 기반하여 구성되는,

장치.

#### 청구항 9

제7 항에 있어서,

상기 양방향 증폭기는 제어 신호의 제1 상태에 기반하여 상기 복수의 출력 단자들 중 제1 출력 단자로부터 입력 신호를 수신하고 상기 복수의 출력 단자들 중 제2 출력 단자를 통하여 증폭된 출력 신호를 생성하도록 구성되고, 그리고 상기 양방향 증폭기는 상기 제어 신호의 제2 상태에 기반하여 상기 복수의 출력 단자들 중 제2 출력 단자로부터 상기 입력 신호를 수신하고 상기 복수의 출력 단자들 중 제1 출력 단자를 통하여 증폭된 출력 신호를 생성하도록 구성되는,

장치.

#### 청구항 10

제1 항에 있어서,

상기 커플러는 상기 복수의 출력 단자들 중 제1 출력 단자와 상기 복수의 출력 단자들 중 제2 출력 단자를 함께 커플링하도록 구성된 트랜지스터 또는 스위치 또는 이들의 조합 중 적어도 하나를 포함하는,

장치.

#### 청구항 11

제1 항에 있어서,

입력 단자들의 수는 출력 단자들의 수보다 더 큰,

장치.

#### 청구항 12

제1 항에 있어서,

상기 복수의 증폭기들은 상기 장치의 동작 모드에 기반하여 비활성화되도록 구성되는,

장치.

#### 청구항 13

제1 항에 있어서,

상기 복수의 증폭기들은 상기 장치의 동작 모드에 기반하여 최소 이득 구성으로 구성되는,

장치.

#### 청구항 14

제1 항에 있어서,

상기 장치의 동작 모드에 기반하여 모드 제어 신호를 생성하기 위한 제어 블록을 더 포함하는,

장치.

**청구항 15**

제14 항에 있어서,

상기 제어 블록은:

상기 장치가 상기 복수의 증폭기들을 통하여 제1 신호를 증폭할 때 상기 모드 제어 신호를 제1 상태로 구동하고; 그리고

제2 신호가 상기 복수의 출력 단자들 중 제1 출력 단자로부터 상기 복수의 출력 단자들 중 제2 출력 단자로 커플링될 때 상기 모드 제어 신호들을 제2 상태로 구동하기 위한 것인,

장치.

**청구항 16**

장치로서,

복수의 증폭기들을 통하여 신호들을 증폭하기 위한 수단;

복수의 출력 단자들을 통하여 복수의 출력 신호들을 생성하기 위한 수단; 및

상기 복수의 출력 단자들 중 적어도 2개의 출력 단자들을 함께 선택적으로 커플링시키기 위한 수단을 포함하는,

장치.

**청구항 17**

제16 항에 있어서,

상기 복수의 출력 신호들을 생성하기 위한 수단은 2 또는 그 초과의 증폭기 출력들을 상기 복수의 출력 단자들 중 적어도 하나에 커플링하기 위한 것인,

장치.

**청구항 18**

제16 항에 있어서,

상기 복수의 출력 단자들 중 적어도 2개의 출력 단자들을 함께 선택적으로 커플링시키기 위한 수단은 상기 복수의 출력 단자들 중 제1 출력 단자에서 수신된 신호를 증폭하고 증폭된 신호를 상기 복수의 출력 단자들 중 제2 출력 단자에 제공하기 위한 것인,

장치.

**청구항 19**

제16 항에 있어서,

상기 장치의 동작 모드에 기반하여 모드 제어 신호를 생성하기 위한 수단을 더 포함하는,

장치.

**청구항 20**

방법으로서,

장치의 동작 모드를 결정하는 단계; 및

결정된 동작 모드에 기반하여 상기 장치의 제1 출력 단자를 상기 장치의 제2 출력 단자에 커플링하기 위한 커플러를 구성하는 단계

를 포함하는,

방법.

### 발명의 설명

#### 기술 분야

[0001] 예시적인 실시예들은 일반적으로 증폭기들, 및 구체적으로 출력 커플러를 가지는 구성가능 저잡음 증폭기 모듈에 관한 것이다.

#### 배경 기술

[0002] 무선 통신 시스템의 무선 디바이스(예컨대, 셀룰러 폰 또는 스마트폰)는 양방향 통신을 위해 데이터를 송신 및 수신할 수 있다. 무선 디바이스는 데이터 송신을 위한 송신기 및 데이터 수신을 위한 수신기를 포함할 수 있다. 데이터 송신을 위하여, 송신기는 라디오 주파수(RF) 캐리어 신호를 데이터로 변조하여 변조된 RF 신호를 생성하고, 변조된 RF 신호를 증폭하여 적절한 출력 전력 레벨을 가지는 송신 RF 신호를 생성하고, 그리고 송신 RF 신호를 안테나를 통하여 다른 디바이스, 이를테면 예컨대 기지국으로 송신할 수 있다. 데이터 수신을 위하여, 수신기는 안테나를 통하여 수신된 RF 신호를 획득하고 수신된 RF 신호를 증폭 및 프로세싱하여 다른 디바이스에 의해 전송된 데이터를 복원할 수 있다.

[0003] 무선 디바이스는 다수의 주파수 대역들 내에서 동작할 수 있다. 예컨대, 무선 디바이스는 제1 주파수 대역 및/또는 제2 주파수 대역 내의 RF 신호를 송신 및/또는 수신할 수 있다. 다수의 주파수 대역들 및/또는 다이버시티(diversity) 동작을 지원하기 위하여, 무선 디바이스는 복수의 트랜스시버들을 포함할 수 있다. 각각의 트랜스시버는 독립적인 로컬 발진기들을 통하여 상이한 주파수 대역들 내에서 동작하도록 투닝(tune)될 수 있는 독립적인 송신기 및 수신기를 포함할 수 있다.

[0004] 수신기들의 교정은 하나 또는 그 초과의 인근 수신기들의 로컬 발진기 주파수들과 유사한 특징들(예컨대, 주파수들)을 가지는 하나 또는 그 초과의 교정 신호들을 요구할 수 있다. 교정 신호들을 생성하기 위한 신호 생성기들을 구현하는 것은 연관된 집적 회로의 다이(die) 사이즈(및 그러므로 비용)를 증가시키고 수신기 설계에 복잡한 교정 신호 회로 라우팅을 도입할 수 있다.

#### 발명의 내용

[0005] 따라서, 무선 디바이스의 수신기들을 교정하기 위한 교정 신호들을 제공하기 위하여 저비용의 다이 효율적 접근법이 필요하다.

#### 도면의 간단한 설명

[0006] 본 실시예들은 예로써 예시되고 첨부 도면들의 도면들에 의해 제한되도록 의도되지 않는다. 동일한 번호들은 도면들 및 명세서 전반에 걸쳐 동일한 엘리먼트들을 지칭한다.

[0007] 도 1은 일부 예시적인 실시예들에 따른, 무선 통신 시스템과 통신하는 무선 디바이스를 도시한다.

[0008] 도 2는 도 1의 무선 디바이스의 예시적인 설계의 블록 다이어그램을 도시한다.

[0009] 도 3은 도 1의 무선 디바이스에 의해 지원될 수 있는 3개의 예시적인 대역 그룹들을 묘사하는 대역 다이어그램이다.

[0010] 도 4는 도 2의 무선 디바이스의 다른 실시예인 무선 디바이스를 도시한다.

[0011] 도 5는 예시적인 실시예들에 따른, 도 1의 무선 디바이스의 LNA 모듈 및 트랜스시버 모듈을 도시하는 블록 다이어그램이다.

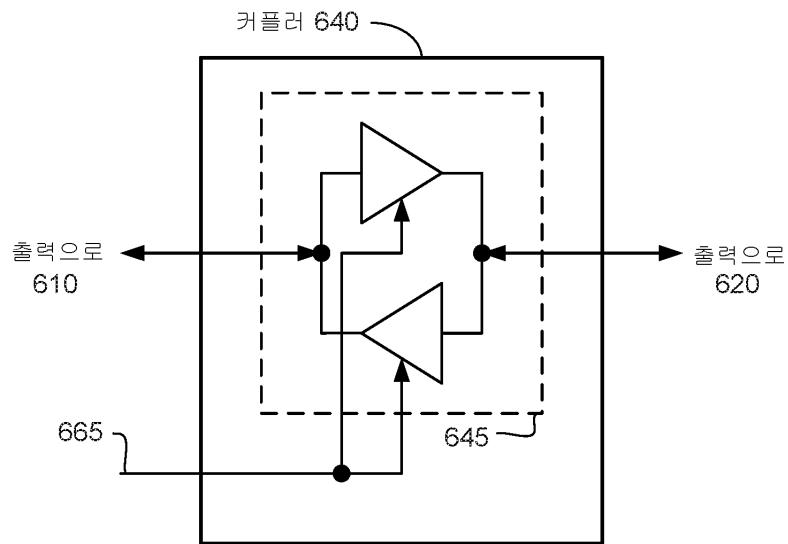

[0012] 도 6a는 예시적인 실시예들에 따른, LNA 모듈의 블록 다이어그램이다.

[0013] 도 6b는 예시적인 실시예들에 따른, 도 6a의 커플러의 블록 다이어그램이다.

[0014] 도 7은 예시적인 실시예들에 따른, LNA 모듈을 동작시키기 위한 예시적인 동작을 묘사하는 예시적인 흐름도를 도시한다.

#### 발명을 실시하기 위한 구체적인 내용

[0007]

[0015] 다음 설명에서, 다수의 특정 세부사항들은 본 개시내용의 완전한 이해를 제공하기 위하여 특정 컴포넌트들, 회로들 및 프로세스들의 예들처럼 설명된다. 본원에 사용되는 "커플링된"이라는 용어는 직접 커플링되거나 또는 하나 또는 그 초과의 개체 컴포넌트들 또는 회로들을 통하여 커플링되는 것을 의미한다. 또한, 다음 설명에서 설명의 목적들을 위하여, 특정 명명법 및/또는 세부사항들은 본 실시예들의 완전한 이해를 제공하기 위하여 설명된다. 그러나, 이들 특정 세부사항들이 본 실시예들을 실시하기 위하여 요구되지 않을 수 있다는 것이 당업자에게 자명할 것이다. 다른 경우들에서, 잘-알려진 회로들 및 디바이스들은 본 개시내용을 모호하게 하는 것을 회피하기 위하여 블록 다이어그램 형태로 도시된다. 본원에 설명된 다양한 버스들을 통하여 제공된 신호들 중 임의의 신호는 다른 신호들과 시간 멀티플렉싱되고 하나 또는 그 초과의 공통 버스들을 통해 제공될 수 있다. 부가적으로, 회로 엘리먼트들 또는 소프트웨어 블록들 간의 상호연결은 버스들 또는 단일 신호 라인들로서 도시될 수 있다. 버스들 각각은 대안적으로 단일 신호 라인일 수 있고, 그리고 단일 신호 라인들 각각은 대안적으로 버스들일 수 있고, 그리고 신호 라인 또는 버스는 컴포넌트들 간의 통신을 위한 무수한 물리적 또는 로지컬 메커니즘들 중 임의의 하나 또는 그 초과를 나타낼 수 있다. 본 실시예들은 본원에 설명된 특정 예들로 제한되는 것으로 이해되는 것이 아니라 오히려 첨부된 청구항들에 의해 정의된 모든 실시예들을 자신의 범위 내에 포함하는 것으로 이해된다.

[0008]

[0016] 게다가, 첨부된 도면들과 관련하여 아래에 설명된 상세한 설명은 본 개시내용의 예시적인 실시예들의 설명으로서 의도되고 그리고 본 개시내용이 실시될 수 있는 유일한 실시예들을 나타내는 것으로 의도되지 않는다. 본 명세서 전반에 걸쳐 사용된 "예시적인"이라는 용어는 "예, 경우, 또는 예시로서 역할을 하는 것"을 의미하고, 그리고 반드시 다른 실시예들에 비해 바람직하거나 유리한 것으로 이해되지 않아야 한다.

[0009]

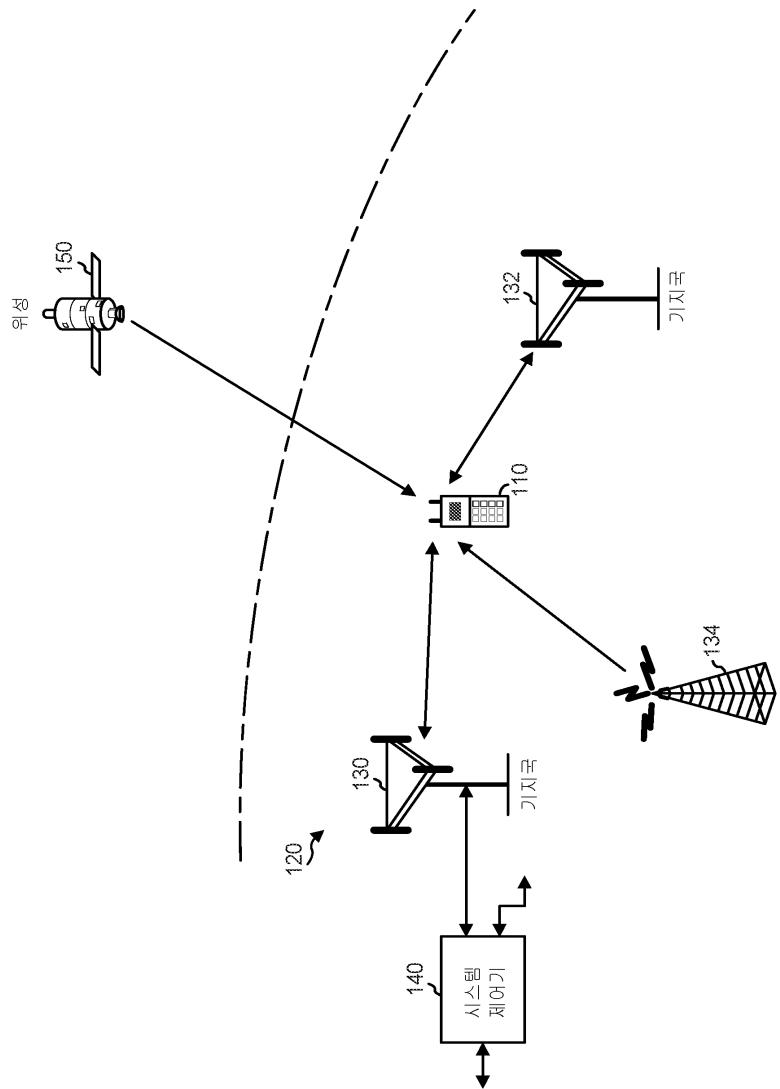

[0017] 도 1은 일부 예시적인 실시예들에 따른, 무선 통신 시스템(120)과 통신하는 무선 디바이스(110)를 도시한다. 무선 통신 시스템(120)은 LTE(Long Term Evolution) 시스템, LTE-A(LTE Advanced) 시스템, CDMA(Code Division Multiple Access) 시스템, GSM(Global System for Mobile Communications) 시스템, WLAN(wireless local area network) 시스템, 또는 일부 다른 무선 시스템일 수 있다. CDMA 시스템은 WCDMA(Wideband CDMA), CDMA 1X, EVDO(Evolution-Data Optimized), TD-SCDMA(Time Division Synchronous CDMA), 또는 일부 다른 버전의 CDMA를 구현할 수 있다. 간략화를 위하여, 도 1은 2개의 기지국들(130 및 132) 및 하나의 시스템 제어기(140)를 포함하는 무선 통신 시스템(120)을 도시한다. 일반적으로, 무선 시스템은 임의의 수의 기지국들 및 임의의 세트의 네트워크 엔티티들을 포함할 수 있다.

[0010]

[0018] 무선 디바이스(110)는 또한 사용자 장비(UE), 이동국, 단말, 액세스 단말, 가입자 유닛, 스테이션 등으로 지칭될 수 있다. 무선 디바이스(110)는 셀룰러 폰, 스마트폰, 태블릿, 무선 모뎀, PDA(personal digital assistant), 핸드헬드 디바이스, 랩톱 컴퓨터, 스마트북, 넷북, 코드리스 폰, WLL(wireless local loop) 국, 블루투스 디바이스 등일 수 있다. 무선 디바이스(110)는 무선 통신 시스템(120)과 통신할 수 있다. 무선 디바이스(110)는 또한 브로드캐스트 스테이션들(예컨대, 브로드캐스트 스테이션(134))로부터 신호들을 수신하고, 하나 또는 그 초과의 GNSS(global navigation satellite systems)의 위성들(예컨대, 위성(150))로부터 신호들을 수신할 수 있는 식이다. 무선 디바이스(110)는 무선 통신을 위한 하나 또는 그 초과의 라디오 기술들, 이를테면 LTE, LTE-A, WCDMA, CDMA 1X, EVDO, TD-SCDMA, GSM, 802.11 등을 지원할 수 있다.

[0011]

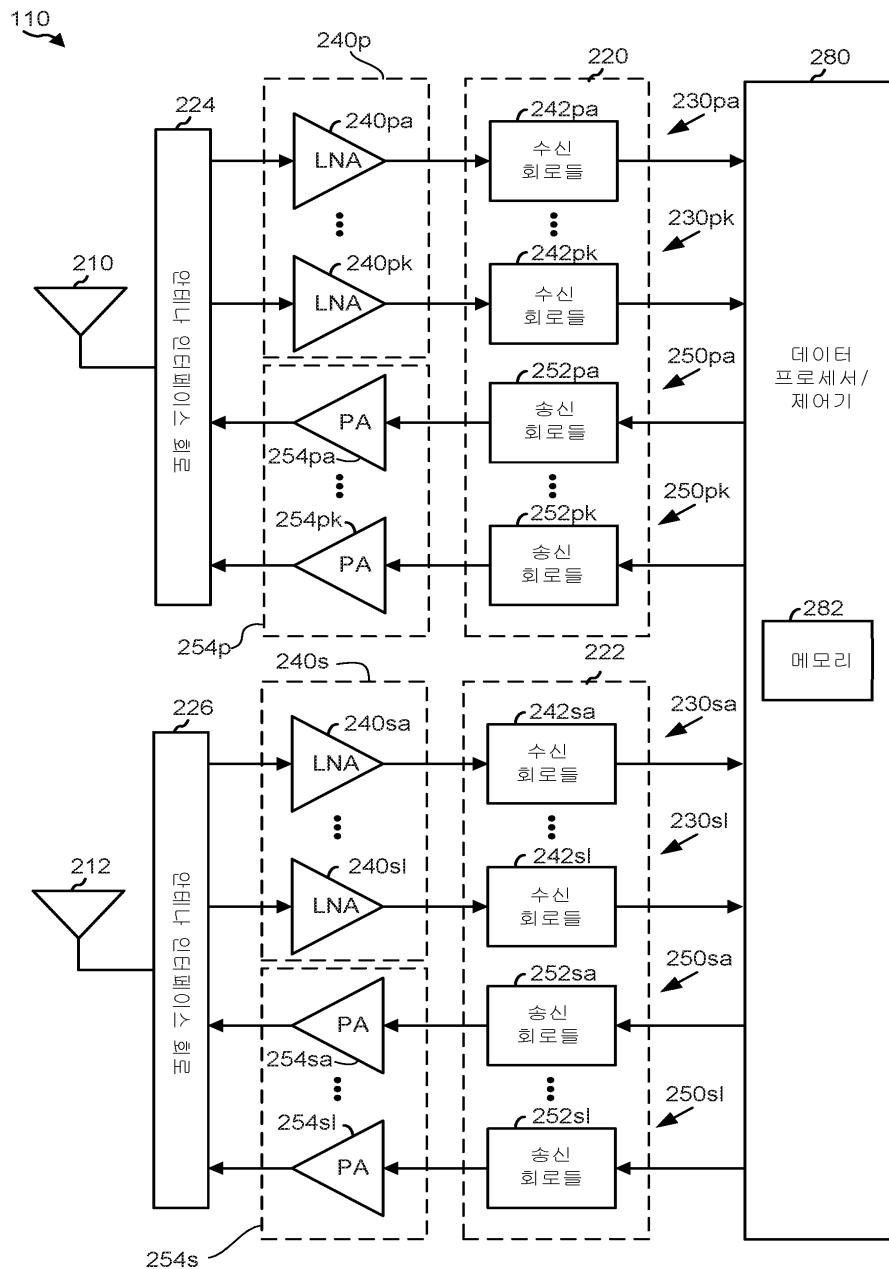

[0019] 도 2는 도 1의 무선 디바이스(110)의 예시적인 설계의 블록 다이어그램을 도시한다. 이 예시적인 설계에서, 무선 디바이스(110)는 1차 안테나(210)에 커플링된 1차 트랜스시버(220), 2차 안테나(212)에 커플링된 2차 트랜스시버(222), 및 데이터 프로세서/제어기(280)를 포함한다. 1차 트랜스시버(220)는 다수의 주파수 대역들, 다수의 라디오 기술들, 캐리어 어그리게이션(aggregation) 등을 지원하기 위하여 K개의 1차 수신기들(230pa 내지 230pk) 및 K개의 1차 송신기들(250pa 내지 250pk)을 포함한다. 2차 트랜스시버(222)는 다수의 주파수 대역들, 다수의 라디오 기술들, 캐리어 어그리게이션, 수신 다이버서티, 다수의 송신 안테나들로부터 다수의 수신 안테나들로의 MIMO(multiple-input multiple-output) 송신 등을 지원하기 위하여 L개의 2차 수신기들(230sa 내지 230s1) 및 L개의 2차 송신기들(250sa 내지 250s1)을 포함한다.

[0012]

[0020] 도 2에 도시된 예시적인 설계에서, 1차 수신기들(230pa 내지 230pk)은 1차 저잡음 증폭기(LNA) 모듈(240p) 및 1차 수신 회로들(242pa 내지 242pk)에 커플링될 수 있다. 1차 LNA 모듈(240p)은 LNA들(240pa 내지 240pk)을 포함할 수 있고 2차 LNA 모듈(240s)은 LNA들(240sa 내지 240s1)을 포함할 수 있다. 데이터 수신을 위해, 1차 안테나(210)는 기지국들 및/또는 다른 송신기 스테이션들로부터 신호들을 수신하고 수신된 라디오 주파수(RF) 신호를 제공하고, 수신된 라디오 주파수(RF) 신호는 1차 안테나 인터페이스 회로(224)를 통하여 라우팅되고 입력 RF 신호로서 선택된 수신기에 제시된다. 1차 안테나 인터페이스 회로(224)는 스위치들, 듀플렉서들, 송신 필터들, 수신 필터들, 매칭 회로들 등을 포함할 수 있다. 아래의 설명은, 1차 수신기(230pa)가 선택

된 수신기인 것을 가정한다. 1차 수신기(230pa) 내에서, LNA(240pa)는 입력 RF 신호를 증폭하고 출력 RF 신호를 제공한다. 1차 수신 회로들(242pa)은 출력 RF 신호를 RF로부터 기저대역으로 하향변환하고, 하향변환된 신호를 증폭 및 필터링하고, 그리고 아날로그 입력 신호를 데이터 프로세서/제어기(280)에 제공한다. 1차 수신 회로들(242pa)은 혼합기들, 필터들, 증폭기들, 매칭 회로들, 발진기, LO(local oscillator) 생성기, PLL(phase locked loop) 등을 포함할 수 있다. 1차 트랜스시버(220) 및 2차 트랜스시버(222) 내의 각각의 나머지 1차 수신기(230pa 내지 230pk) 및 2차 수신기들(230sa 내지 230s1)은 1차 수신기(230pa)와 유사한 방식으로 동작할 수 있다.

[0013]

[0021] 도 2에 도시된 예시적인 설계에서, 각각의 1차 송신기(250pa 내지 250pk)는 1차 송신 회로들(252pa 내지 252pk)을 포함하고 1차 전력 증폭기 모듈(PA)(254p)에 커플링된다. 1차 PA 모듈(254p)은 1차 전력 증폭기들(254pa 내지 254pk)을 포함할 수 있고 2차 PA 모듈(254s)은 2차 전력 증폭기들(254sa 내지 254s1)을 포함할 수 있다. 데이터 송신을 위하여, 데이터 프로세서/제어기(280)는 송신될 데이터를 프로세싱하고(예컨대, 인코딩 및 변조하고) 아날로그 출력 신호를 선택된 송신기에 제공한다. 아래의 설명은, 1차 송신기(250pa)가 선택된 송신기인 것을 가정한다. 1차 송신기(250pa) 내에서, 1차 송신 회로들(252pa)은 아날로그 출력 신호를 증폭, 필터링 및 기저대역으로부터 RF로 상향 변환하고 변조된 RF 신호를 제공한다. 1차 송신 회로들(252pa)은 증폭기들, 필터들, 혼합기들, 매칭 회로들, 발진기, LO 생성기, PLL 등을 포함할 수 있다. 1차 PA(254pa)는 변조된 RF 신호를 수신 및 증폭하고 적절한 출력 전력 레벨을 가지는 송신 RF 신호를 제공한다. 송신 RF 신호는 1차 안테나 인터페이스 회로(224)를 통하여 라우팅되고 1차 안테나(210)를 통하여 송신된다. 1차 트랜스시버(220) 내의 각각의 나머지 1차 송신기(250pa 내지 250pk) 및 2차 트랜스시버(222) 내의 2차 송신기들(250sa 내지 250s1)은 송신기(250pa)와 유사한 방식으로 동작할 수 있다. 유사한 방식으로, 2차 안테나 인터페이스 회로(226)는 2차 안테나(212)와, 2차 LNA 모듈(240s) 및/또는 2차 전력 증폭기 모듈(254s) 간에 RF 신호들을 라우팅할 수 있다.

[0014]

[0022] 각각의 1차 및 2차 수신기(230)(예컨대, 230pa-230pk 및 230sa-230s1) 및 1차 및 2차 송신기(250)(예컨대, 250pa-250pk 및 250sa-250s1)는 또한 도 2에 도시되지 않은 다른 회로들, 이를테면 필터들, 매칭 회로들 등을 포함할 수 있다. 1차 트랜스시버(220) 및 2차 트랜스시버(222) 모두 또는 일부는 하나 또는 그 초과의 아날로그 집적 회로(IC)들, RF IC(RFIC)들, 혼합된-신호 IC들 등 상에 구현될 수 있다. 예컨대, 트랜스시버들(220 및 222) 내의 LNA들(240) 및 수신 회로들(242)은 아래에 설명되는 바와 같이, 다수의 IC 칩들 상에 구현될 수 있다. 트랜스시버들(220 및 222)의 회로들은 또한 다른 방식들로 구현될 수 있다. 일부 실시예들에서, 1차 및 2차 수신기(230)는 캐리어 어그리게이션을 지원할 수 있고 상이한 캐리어 주파수들을 가지는 2 또는 그 초과의 동시에 신호들을 수신할 수 있다.

[0015]

[0023] 데이터 프로세서/제어기(280)는 무선 디바이스(110)에 대한 다양한 기능들을 수행할 수 있다. 예컨대, 데이터 프로세서/제어기(280)는 수신기들(230)을 통하여 수신되는 데이터 및 송신기들(250)을 통하여 송신되는 데이터에 대한 프로세싱을 수행할 수 있다. 데이터 프로세서/제어기(280)는 트랜스시버들(220 및 222) 내의 다양한 회로들의 동작을 제어할 수 있다. 메모리(282)는 데이터 프로세서/제어기(280)에 대한 프로그램 코드들 및 데이터를 저장할 수 있다. 데이터 프로세서/제어기(280)는 하나 또는 그 초과의 ASIC(application specific integrated circuit)들 및/또는 다른 IC들 상에 구현될 수 있다.

[0016]

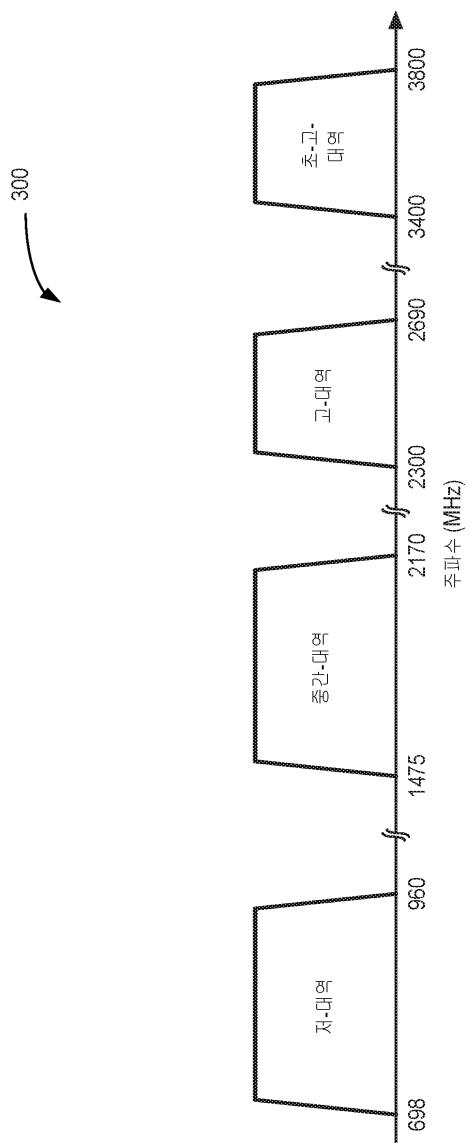

[0024] 도 3은 무선 디바이스(110)에 의해 지원될 수 있는 3개의 예시적인 대역 그룹들을 묘사하는 대역 다이어그램(300)이다. 일부 실시예들에서, 무선 디바이스(110)는 1000 메가헤르츠(MHz)보다 더 낮은 주파수들을 가지는 RF 신호들을 포함하는 저-대역(LB), 1475 MHz 내지 2170 MHz의 주파수들을 가지는 RF 신호들을 포함하는 중간-대역(MB), 2300 MHz 내지 2690 MHz의 주파수들을 가지는 RF 신호들을 포함하는 고-대역(HB), 및/또는 3400 MHz보다 더 높은 주파수들을 가지는 RF 신호들을 포함하는 초-고-대역(UHB)에서 동작할 수 있다. 예컨대, 도 3에 도시된 바와 같이, 저-대역 RF 신호들은 698 MHz 내지 960 MHz를 커버할 수 있고, 중간-대역 RF 신호들은 1475 MHz 내지 2170 MHz를 커버할 수 있고, 그리고 고-대역 RF 신호들은 2300 MHz 내지 2690 MHz를 커버할 수 있고 그리고 초-고-대역 RF 신호들은 3400 MHz 내지 3800 MHz 및 5000MHz 내지 5800MHz를 커버할 수 있다. 저-대역, 중간-대역, 및 고-대역, 및 초-고 대역은 대역들의 4개의 그룹들(또는 대역 그룹들)을 지칭하고, 각각의 대역 그룹은 다수의 주파수 대역들(또는 간단히, "대역들")을 포함한다. LTE 릴리스(11)는 LTE/UMTS 대역들로 지칭되는 35개의 대역들을 지원하고 3GPP TS 36.101에 리스트된다.

[0017]

[0025] 일반적으로, 임의의 수의 대역 그룹들이 정의될 수 있다. 각각의 대역 그룹은 도 3에 도시된 주파수 범위들 중 임의의 주파수 범위에 매칭하거나 매칭하지 않을 수 있는 임의의 범위의 주파수들을 커버할 수 있다.

각각의 대역 그룹은 또한 임의의 수의 대역들을 포함할 수 있다.

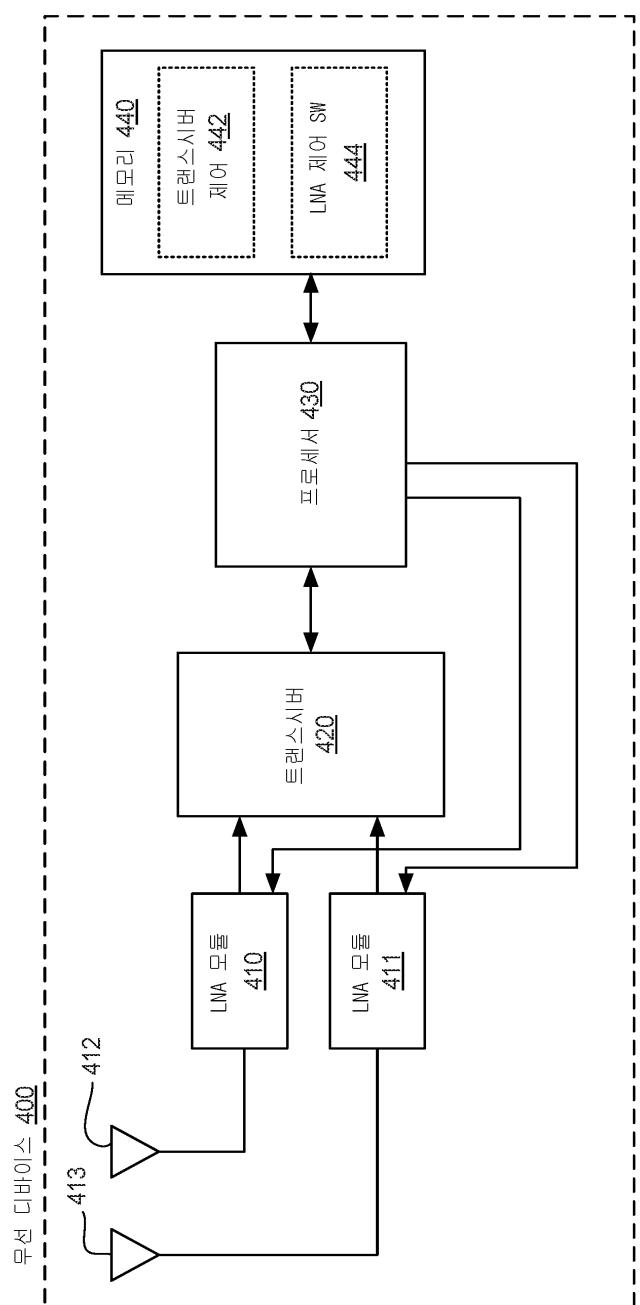

[0018] 도 4는 도 2의 무선 디바이스(110)의 다른 실시예인 무선 디바이스(400)를 도시한다. 무선 디바이스(400)는 제1 안테나(412), 제2 안테나(413), 제1 LNA 모듈(410), 제2 LNA 모듈(411), 트랜스시버(420), 프로세서(430), 및 메모리(440)를 포함한다. 제1 LNA 모듈(410)은 LNA 모듈(240p) 또는 LNA 모듈(500)의 다른 실시 예일 수 있다. 유사한 방식으로, 제2 LNA 모듈(411)은 LNA 모듈(240s) 또는 LNA 모듈(500)의 다른 실시예일 수 있다. 제1 안테나(412)는 1차 안테나(210)의 다른 실시예일 수 있고, 제2 안테나(413)는 2차 안테나(212)의 다른 실시예일 수 있다. 일부 실시예들에서, 트랜스시버(420)는 통신 신호들을 송신하기 위한 송신기들 및 다른 무선 디바이스들로부터 통신 신호들을 수신하기 위한 수신기들을 포함할 수 있다. 부가적으로, 제1 LNA 모듈(410) 및 제2 LNA 모듈(411)은 각각 제1 안테나(412) 및 제2 안테나(413)를 통하여 통신 신호들을 수신할 수 있다. 비록 단지 2개의 안테나들 및 2개의 LNA 모듈들이 도 4에 도시되지만, 다른 실시예들은 다른 수들의 안테나들 및/또는 LNA 모듈들을 포함할 수 있다.

[0019] 메모리(440)는 다음의 소프트웨어 모듈들을 저장할 수 있는 비-일시적 컴퓨터-판독가능 저장 매체(예컨대, 하나 또는 그 초과의 비휘발성 메모리 엘리먼트들, 이를테면 EPROM, EEPROM, 플래시 메모리, 하드 드라이브 등)를 포함할 수 있다:

- 하나 또는 그 초과의 통신 프로토콜들에 따라 통신 신호들을 송신 및 수신하기 위하여 트랜스시버(420)를 제어하기 위한 트랜스시버 제어 모듈(442); 및

- 제1 LNA 모듈(410) 및/또는 제2 LNA 모듈(411)을 제어하기 위한 LNA 제어 소프트웨어 모듈(444).

[0022] 각각의 소프트웨어 모듈은, 프로세서(430)에 의해 실행될 때, 무선 디바이스(400)로 하여금 대응하는 기능(들)을 수행하게 할 수 있는 프로그램 명령들을 포함한다. 따라서, 메모리(440)의 비-일시적 컴퓨터-판독가능 저장 매체는 도 7의 동작들 모두 또는 일부를 수행하기 위한 명령들을 포함할 수 있다.

[0023] [0028] 트랜스시버(420), 제1 LNA 모듈(410), 제2 LNA 모듈(411), 및 메모리(440)에 커플링된 프로세서(430)는 무선 디바이스(400)에(예컨대, 메모리(440) 내에) 저장된 하나 또는 그 초과의 소프트웨어 프로그램들의 스크립트(script)들 또는 명령들을 실행할 수 있는 임의의 하나 또는 그 초과의 적절한 프로세서들일 수 있다.

[0024] [0029] 프로세서(430)는 통신 프로토콜에 따라 통신 신호들을 수신 및/또는 송신하도록 트랜스시버(420)를 구성하기 위해 트랜스시버 제어 모듈(442)을 실행할 수 있다. 일부 실시예들에서, 트랜스시버 제어 모듈(442)은 트랜스시버(420)에 대한 동작 주파수(예컨대, 캐리어 주파수 및/또는 로컬 발진기 주파수)를 결정할 수 있다. 트랜스시버 제어 모듈(442)은 교정 신호를 생성하기 위하여 사용될 수 있는 트랜스시버(420) 내의 하나 또는 그 초과의 로컬 발진기들을 제어할 수 있다. 트랜스시버 제어 모듈(442)은 또한 수신된 교정 신호에 기반하여, 수신기의 출력 신호를 분석하고 수신기와 연관된 하나 또는 그 초과의 세팅들을 수정함으로써 트랜스시버(420) 내의 하나 또는 그 초과의 수신기들을 교정할 수 있다.

[0025] [0030] 프로세서(430)는 제1 LNA 모듈(410) 및/또는 제2 LNA 모듈(411)을 제어하기 위해 LNA 제어 소프트웨어 모듈(444)을 실행할 수 있다. 일부 실시예들에서, LNA 제어 소프트웨어 모듈(444)은 제1 LNA 모듈(410) 및/또는 제2 LNA 모듈(411)에 대한 정상 동작 모드 또는 출력 커플링 동작 모드를 선택할 수 있다. 예컨대, LNA 제어 소프트웨어 모듈(444)은 교정 신호를 트랜스시버(420) 내의 수신기에 제공하기 위하여 출력 커플링 동작 모드에서 제1 LNA 모듈(410) 및/또는 제2 LNA 모듈(411)을 동작시킬 수 있다.

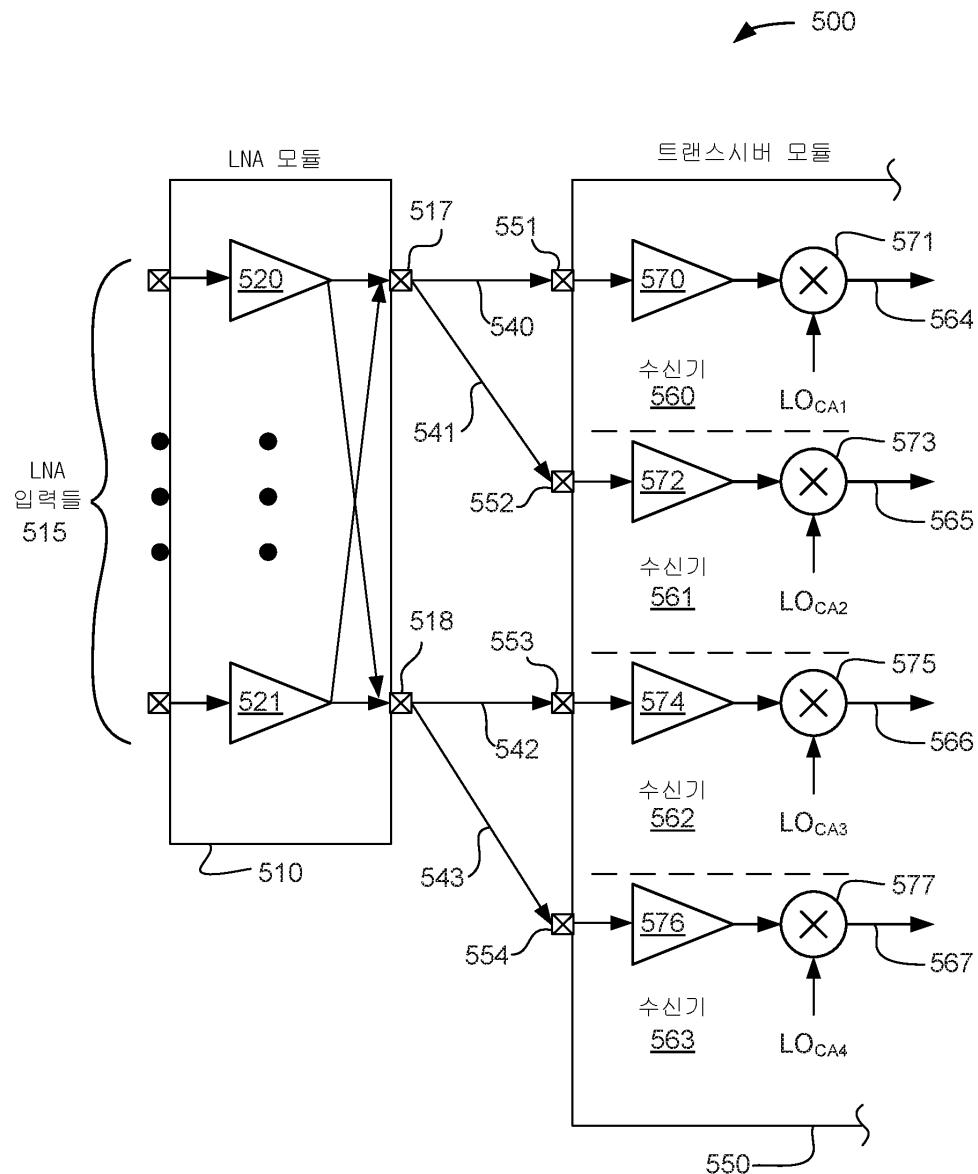

[0026] [0031] 도 5는 예시적인 실시예들에 따른, 무선 디바이스(110)의 LNA 모듈(510) 및 트랜스시버 모듈(550)을 도시하는 블록 다이어그램(500)이다. LNA 모듈(510)은 도 2의 1차 LNA 모듈(240p) 및/또는 2차 LNA 모듈(240s)의 다른 실시예일 수 있다. 일부 실시예들에서, LNA 모듈(510)은 LB, MB, HB 및/또는 UHB를 비롯하여, 상이한 주파수 대역들의 RF 신호들을 수신할 수 있다. 유사한 방식으로, 트랜스시버 모듈(550)은 도 2의 1차 트랜스시버(220) 및/또는 2차 트랜스시버(222)의 다른 실시예일 수 있다.

[0027] [0032] 일부 실시예들에서, LNA 모듈(510)은 복수의 LNA 모듈 입력 단자들(515), 제1 LNA 모듈 출력 단자(517), 제2 LNA 모듈 출력 단자(518), 및 복수의 LNA들을 포함할 수 있다. 도시된 바와 같이, LNA 모듈(510)은 제1 LNA(520) 및 제2 LNA(521)를 포함할 수 있다. 다른 실시예들에서, LNA 모듈(510)은 2개보다 많은 LNA들을 포함할 수 있다. 비록 LNA들로서 도시되지만, 다른 실시예들에서, 제1 LNA(520) 및 제2 LNA(521)는 임의의 기술적으로 실현가능 증폭기일 수 있다. 일부 실시예들에서, LNA 모듈(510) 내의 각각의 LNA는 대응하는 LNA 모듈 입력 단자(예컨대, LNA 모듈 입력 단자들(515) 내의 전용 입력 단자)에 커플링될 수 있다.

- [0028] [0033] 비록 단지 제1 LNA 모듈 출력 단자(517) 및 제2 LNA 모듈 출력 단자(518)만이 도시되지만, 다른 실시예들에서, LNA 모듈(510)은 다른 수들의 LNA 모듈 출력 단자들을 포함할 수 있다. 일부 실시예들에서, 각각의 LNA 모듈 출력 단자는 2 또는 그 초과의 LNA 출력들에 커플링될 수 있다. 예컨대, 제1 LNA 모듈 출력 단자(517)는 제1 LNA(520)로부터의 출력 및 제2 LNA(521)로부터의 출력에 커플링될 수 있다. 유사한 방식으로, 제2 LNA 모듈 출력 단자(518)는 또한 제1 LNA(520)로부터의 출력 및 제2 LNA(521)로부터의 출력에 커플링될 수 있다. 다른 실시예들에서, 각각의 LNA로부터의 출력들은 모든 LNA 모듈 출력 단자들의 서브세트로 라우팅될 수 있다. 일부 실시예들에서, LNA 모듈 출력 단자들의 수는 LNA 모듈 입력 단자들의 수 미만일 수 있다. 예컨대, LNA 모듈은 M개의 LNA 모듈 입력 단자들 및 N개의 LNA 모듈 출력 단자들을 포함하고, 여기서  $M > N$ 이다.

- [0029] [0034] 트랜스시버 모듈(550)은 복수의 수신기들 및 송신기들을 포함할 수 있다. 도 5에 도시된 바와 같이, 트랜스시버 모듈(550)은 제1 수신기(560), 제2 수신기(561), 제3 수신기(562), 및 제4 수신기(563)를 포함할 수 있다. 다른 실시예들에서, 트랜스시버 모듈(550)은 다른 수들의 수신기들을 포함할 수 있다. 트랜스시버 모듈(550)은 하나 또는 그 초과의 송신기들(간략화를 위하여 도시되지 않음)을 포함할 수 있다. 예컨대, 트랜스시버 모듈(550) 내의 각각의 수신기는 대응하는 송신기와 연관될 수 있다. 각각의 수신기는 베퍼 및 혼합기를 포함할 수 있다. 예컨대, 제1 수신기(560)는 제1 베퍼(570) 및 제1 혼합기(571)를 포함할 수 있고, 제2 수신기(561)는 제2 베퍼(572) 및 제2 혼합기(573)를 포함할 수 있고, 제3 수신기(562)는 제3 베퍼(574) 및 제3 혼합기(575)를 포함할 수 있고, 그리고 제4 수신기(563)는 제4 베퍼(576) 및 제4 혼합기(577)를 포함할 수 있다. 다른 실시예들에서, 각각의 수신기는 상이한 수들의 베퍼들, 상이한 수들의 혼합기들, 부가적인 컴포넌트들, 및 /또는 더 적은 수의 컴포넌트들을 포함할 수 있다.

- [0030] [0035] 일부 실시예들에서, 각각의 수신기는 입력 신호를 수신하기 위해 입력 단자와 연관될 수 있다. 예컨대, 제1 수신기(560)는 제1 베퍼(570)에 커플링된 제1 수신기 입력 단자(551)를 포함할 수 있다. 유사한 방식으로, 제2 수신기(561)는 제2 베퍼(572)에 커플링된 제2 수신기 입력 단자(552)를 포함할 수 있고, 제3 수신기(562)는 제3 베퍼(574)에 커플링된 제3 수신기 입력 단자(553)를 포함할 수 있고, 그리고 제4 수신기(563)는 제4 베퍼(576)에 커플링된 제4 수신기 입력 단자(554)를 포함할 수 있다.

- [0031] [0036] 일부 실시예들에서, 각각의 수신기는 상이한 LO(local oscillator) 신호(예컨대, 상이한 LO 주파수)로 동작할 수 있다. 예컨대, 제1 수신기(560)는 LO<sub>CA1</sub> 신호로 동작할 수 있고, 제2 수신기(561)는 LO<sub>CA2</sub> 신호로 동작할 수 있고, 제3 수신기(562)는 LO<sub>CA3</sub> 신호로 동작할 수 있고, 그리고 제4 수신기(563)는 LO<sub>CA4</sub> 신호로 동작할 수 있다.

- [0032] [0037] 일부 실시예들에서, 제1 혼합기(571)는 제1 베퍼(570)로부터의 출력 신호와 LO<sub>CA1</sub>에 기반하여 제1 혼합기 출력 신호(564)를 생성할 수 있다. 유사한 방식으로, 제2 혼합기(573)는 제2 베퍼(572)로부터의 출력 신호와 LO<sub>CA2</sub>에 기반하여 제2 혼합기 출력 신호(565)를 생성할 수 있고, 제3 혼합기(575)는 제3 베퍼(574)로부터의 출력 신호와 LO<sub>CA3</sub>에 기반하여 제3 혼합기 출력 신호(566)를 생성할 수 있고, 그리고 제4 혼합기(577)는 제4 베퍼(576)로부터의 출력 신호와 LO<sub>CA4</sub>에 기반하여 제4 혼합기 출력 신호(567)를 생성할 수 있다. 각각의 혼합기 출력 신호는 다른 무선 디바이스들로부터 송신된 데이터를 디코딩 및 복원하도록 각각의 개별 수신기(간략화를 위하여 도시되지 않음) 내의 부가적인 컴포넌트들에 커플링될 수 있다.

- [0033] [0038] LNA 모듈(510)은 LNA 모듈 출력 단자들(517 및 518)을 수신기 입력 단자들(551-554)에 커플링하기 위하여 복수의 회로들을 통하여 트랜스시버 모듈(550)에 커플링될 수 있다. 회로들은 회로 기판상에 배치된 전도성 트레이스(trace)들, LNA 모듈(510)과 트랜스시버 모듈(550) 간의 와이어들, 또는 임의의 다른 기술적으로 실현 가능 전도성 커플링일 수 있다. 일부 실시예들에서, LNA 모듈(510) 및 트랜스시버 모듈(550)은 공통 접적 회로 상에서 같은 위치에 배치될 수 있다. 따라서, 일부 실시예들에서, 회로들은 전도성 루트들(예컨대, 금속 층들, 도핑된 실리콘 등), 본드 와이어들, 또는 다른 온-칩 전도성 연결일 수 있다. 일부 실시예들에서, LNA 모듈 출력 단자는 트랜스시버 모듈(550)의 2 또는 그 초과의 입력 단자들에 커플링될 수 있다. 예컨대, 제1 LNA 모듈 출력 단자(517)는 제1 회로(540)를 통하여 제1 수신기 입력 단자(551)에 그리고 제2 회로(541)를 통하여 제2 수신기 입력 단자(552)에 커플링될 수 있다. 유사한 방식으로, 제2 LNA 모듈 출력 단자(518)는 제3 회로(542)를 통하여 제3 수신기 입력 단자(553)에 그리고 제4 회로(543)를 통하여 제4 수신기 입력 단자(554)에 커플링될 수 있다. 다른 실시예들에서, LNA 모듈(510)과 트랜스시버 모듈(550) 간의 다른 회로 연결들은 구현될 수 있다.

- [0034] [0039] 일부 실시예들에서, 수신기는 수신기 성능을 개선하기 위하여 교정될 수 있다. 예컨대, 제1 수신기(560)는 제1 수신기 입력 단자(551)를 통하여 동위상(I) 입력 신호 및 직교(Q) 입력 신호를 수신하는 직교 수신

기일 수 있다. 제1 수신기(560)는 2개의 신호 프로세싱 경로들을 포함할 수 있다: 동위상 입력 신호를 프로세싱하기 위한 제1 프로세싱 경로 및 직교 입력 신호를 프로세싱하기 위한 제2 프로세싱 경로(프로세싱 경로들은 간략화를 위해 도시되지 않음). 신호 프로세싱이 2개의 신호 프로세싱 경로들 내에서 벨런싱(즉, 실질적으로 유사)되지 않으면, I/Q 미스매치가 발생할 수 있다. I/Q 미스매치는 연관된 신호 대 잡음 비율 측정치를 감소시킬 수 있고 또한 수신된 신호와 연관된 디코딩 에러들을 유발할 수 있다. 일부 실시예들에서, 수신기는 알려진(예컨대, 교정) 신호를 수신 및 프로세싱함으로써 교정될 수 있다. 그 다음 수신기의 출력은 시험될 수 있고 임의의 신호 프로세싱 임밸런스(imbalance)를 수정하기 위하여 2개의 신호 프로세싱 경로들 내에서 조정들이 이루어질 수 있다.

[0035] [0040] 일부 실시예들에서, 트랜스시버 모듈(550) 내의 하나의 수신기에 의해 제공된 신호는 트랜스시버 모듈(550) 내의 다른 수신기에 대한 교정 신호로서 사용될 수 있다. 수신기 입력 단자들(551-554)은 통상적으로 입력 신호들을 수신할 수 있다. 일부 실시예들에서, 수신기 입력 단자는 또한 출력 신호를 생성할 수 있다. 예컨대, 위에서 설명된 바와 같이, 제1 수신기(560)는 LO<sub>CA1</sub>을 입력 신호와 혼합하여 제1 혼합기 출력 신호(564)를 생성할 수 있다. 동작 동안, LO<sub>CA1</sub>은 제1 혼합기(571) 및 버퍼(570)를 통하여 제1 수신기 입력 단자(551)로 누설될 수 있다. 다른 말로, LO<sub>CA1</sub>은 제1 수신기 입력 단자(551)에 커플링될 수 있다. 일부 실시예들에서, LO<sub>CA1</sub>은 제1 수신기(560) 이외의 수신기들에 대한 교정 신호로서 사용될 수 있다. 예컨대, 도 5에 도시된 바와 같이, 제2 수신기(561)는 제1 수신기(560)로부터 제1 회로(540) 및 제2 회로(541)를 통하여(예컨대, LNA 모듈 출력 단자(517)를 통하여) LO<sub>CA1</sub>을 수신할 수 있다.

[0036] [0041] 트랜스시버 모듈(550) 내의 다른 수신기들은 회로들을 통하여 제1 수신기 입력 단자(551)에 커플링되지 않을 수 있다. 예컨대, 제3 수신기 입력 단자(553) 및 제4 수신기 입력 단자(554)는 서로 커플링되는 동안, 제1 수신기 입력 단자(551)에 커플링되지 않을 수 있다. 따라서, 제3 수신기(562) 및 제4 수신기(563)는 LO<sub>CA1</sub>을 수신하지 못할 수 있다. 일부 실시예들에서, LNA 모듈(510)은 선택적으로 2 또는 그 초과의 LNA 모듈 출력 단자들을 함께 커플링하도록 구성가능한 커플러를 포함할 수 있다. 따라서, LNA 모듈(510)의 제1 모듈 출력 단자에서 수신된 신호(예컨대, 수신기로부터의 누설 신호)는 LNA 모듈(510)의 제2 모듈 출력 단자에 커플링될 수 있다. 예컨대, 이것은 제3 수신기(562) 및 제4 수신기(563)가 LO<sub>CA1</sub> 및/또는 LO<sub>CA2</sub>를 수신하는 것을 허용한다. 구성가능 커플러는 도 6a 및 6b과 함께 아래에 더 상세히 설명된다.

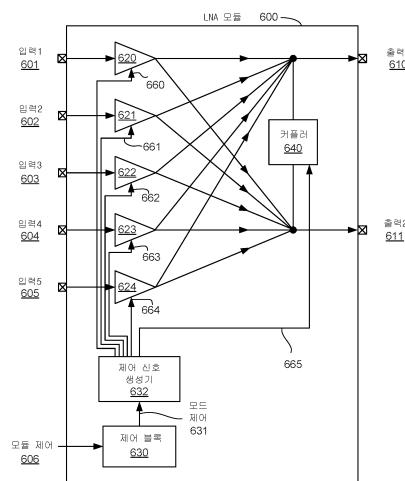

[0037] [0042] 도 6a는 예시적인 실시예들에 따른, LNA 모듈(600)의 블록 다이어그램이다. LNA 모듈(600)은 도 5의 LNA 모듈(510)의 다른 실시예일 수 있다. LNA 모듈(600)은 LNA 모듈 입력 단자들(601-605), LNA 모듈 출력 단자들(610 및 611), LNA들(620-624), 제어 신호 생성기(632), 제어 블록(630), 및 커플러(640)를 포함할 수 있다. 다른 실시예들에서, 다른 수들의 LNA 모듈 입력 단자들, LNA 모듈 출력 단자들, 및 LNA들이 사용될 수 있다.

[0038] [0043] 각각의 LNA(620-624)는 LNA 모듈 입력 단자들(601-605) 중 하나와 연관될 수 있다. 예컨대, 제1 LNA 모듈 입력 단자(601)는 제1 LNA(620)의 입력에 커플링될 수 있다. 유사한 방식으로, LNA 모듈 입력 단자들(602-605)은 각각 LNA들(621-624)에 커플링될 수 있다. LNA들(620-624)로부터의 출력들(예컨대, 증폭기 출력 단자들)은 함께 커플링될 수 있고 또한 LNA 모듈 출력 단자들(610 및 611)에 커플링될 수 있다. 예컨대, 도 6에 도시된 바와 같이, LNA들(620-624) 각각으로부터의 출력은 제1 LNA 모듈 출력 단자(610) 및 제2 LNA 모듈 출력 단자(611)에 커플링될 수 있다. 일부 실시예들에서, LNA 모듈 출력 단자들의 수는 LNA 모듈 입력 단자들의 수 미만일 수 있다.

[0039] [0044] 일부 실시예들에서, LNA들(620-624)은 각각 독립적인 LNA 제어 신호들(660-664)을 통하여 제어될 수 있다. 예컨대, 각각의 LNA(620-624)는 LNA 제어 신호들(660-664)을 통하여 독립적인 이득 제어 및/또는 독립적인 모드 제어(예컨대, 동작 모드 또는 비활성 모드)를 가질 수 있다.

[0040] [0045] 커플러(640)는 2개의 LNA 모듈 출력 단자들을 함께 커플링할 수 있다. 비록 단지 하나의 커플러(640)가 LNA 모듈(600) 내에 도시되지만, 다른 실시예들에서, 다른 수들의 커플러(640)가 사용될 수 있다. 일부 실시예들에서, 커플러(640)는 제1 모듈 출력 단자에서 수신된 신호가 제2 모듈 출력 단자에 의해 출력되는 것을 가능하게 할 수 있다. 예컨대, 커플러(640)는 제1 LNA 모듈 출력 단자(610)에서 수신된 신호가 제2 LNA 모듈 출력 단자(611)에 제공되는 것을 가능하게 할 수 있다. 다른 예에서, 커플러(640)는 제2 LNA 모듈 출력 단자(611)에서 수신된 신호가 제1 LNA 모듈 출력 단자(610)에 제공되는 것을 가능하게 할 수 있다. 일부 실시예들에서, 커플러(640)가 활성일 때(예컨대, 제1 모듈 출력 단자를 제2 모듈 출력 단자에 커플링함), LNA들(620-624)은 비활

성이거나 최소 이득 구성으로 동작할 수 있다. 또 다른 실시예들에서, 커플러(640)는 제1 모듈 출력 단자를 제2 모듈 출력 단자로부터 격리할 수 있다.

[0041] 일부 실시예들에서, 커플러(640)는 제1 LNA 모듈 출력 단자(610)를 제2 LNA 모듈 출력 단자(611)에 커플링하기 위한 기계적 및/또는 전기적 스위치를 포함할 수 있는 스위치 유닛으로 구현될 수 있다. 예시적인 전기적 스위치들은 릴레이, 및/또는 트랜지스터(예컨대, 양극 트랜지스터 또는 MOSFET)일 수 있다. 다른 실시예들에서, 커플러(640)는 선택적인 증폭기, 이를테면 양방향 증폭기를 포함할 수 있다. 양방향 증폭기는 제1 LNA 출력 단자로부터 신호들을 수신하여 증폭할 수 있고 이들을 제2 LNA 출력 단자에 제공할 수 있다. 커플러(640)는 커플러 제어 신호(665)에 의해 제어될 수 있다. 커플러(640)는 도 6b와 함께 아래에 더 상세히 설명된다.

[0042] 제어 블록(630)은 모듈 제어 신호(606)를 수신하고, 이에 대한 응답으로, 모드 제어 신호(631)를, LNA 모듈(600)로 하여금 정상 동작 모드 또는 출력 커플링 동작 모드로 동작하게 할 수 있는 상태로 구동할 수 있다. 모듈 제어 신호(606)는 데이터 프로세서/제어기(280), 무선 디바이스(110) 내의 다른 디바이스, 별개의 프로세서, 또는 임의의 다른 기술적으로 실현가능 디바이스에 의해 제공될 수 있다. LNA 모듈(600)이 정상 동작 모드에서 동작할 때, 커플러(640)는 디스에이블될 수 있고, 그리고 LNA들(620-624)로부터의 적어도 하나의 LNA는 LNA 출력 신호를 제1 LNA 모듈 출력 단자(610) 및/또는 제2 LNA 모듈 출력 단자(611)에 제공하기 위하여 인에이블될 수 있다. LNA 모듈(600)이 출력 커플링 동작 모드에서 동작할 때, LNA들(620-624)은 비활성일 수 있거나 최소 이득 구성으로 동작할 수 있다. 게다가, 커플러(640)는 제1 LNA 모듈 출력 단자로부터의 신호를 제2 LNA 모듈 출력 단자에 커플링하고 및/또는 증폭할 수 있다.

[0043] 제어 신호 생성기(632)는 모드 제어 신호(631)를 수신할 수 있고 이에 대한 응답으로, 하나 또는 그 초과의 LNA 제어 신호들(660-664) 및 커플러 제어 신호(665)를 생성할 수 있다. 일부 실시예들에서, 5개의 정상 동작 모드들 및 2개의 출력 커플링 동작 모드들이 있을 수 있다. 예컨대, LNA 모듈(600)이 정상 동작 모드들 중 하나에서 동작할 때, 제어 신호 생성기(632)는 정상 동작 모드에서, 모드 제어 신호(631)를 수신하고 각각, LNA들(620-624) 중 하나를 동작시키기 위하여 하나 또는 그 초과의 LNA 제어 신호들(660-664)을 어서트(assert)할 수 있다. 부가적으로, 제어 신호 생성기(632)는 커플러 제어 신호(665)를 어서트하여 커플러(640)를 디스에이블할 수 있다. LNA 모듈(600)이 출력 커플링 동작 모드들 중 하나에서 동작할 때, 제어 신호 생성기(632)는 LNA 제어 신호들(660-664)을 어서트하여, 개별 LNA들(620-624)이 비활성화되게 하거나 이들을 최소 이득 구성으로 동작하게 할 수 있다. 부가적으로, 제어 신호 생성기(632)는 커플러 제어 신호(665)를 어서트하여, 커플러(640)를 인에이블하고, 커플러(640)에 대한 신호 흐름 방향을 결정하고, 및/또는 커플러(640)에 의해 제공될 수 있는 이득 양을 결정할 수 있다. 예시적인 모드들 및 제어 신호들은 아래에서 표 1에 도시된다. 간략화를 위하여, 커플러(640)에 대한 가변 이득 제어와 연관된 표 엔트리들은 생략되었다.

## 표 1

| 모드      | LNA 제어 (660 – 664) | 커플러 제어 (665)                |

|---------|--------------------|-----------------------------|

| 정상 1    | 인에이블 LNA 620       | 디스에이블                       |

| 정상 2    | 인에이블 LNA 621       | 디스에이블                       |

| 정상 3    | 인에이블 LNA 622       | 디스에이블                       |

| 정상 4    | 인에이블 LNA 623       | 디스에이블                       |

| 정상 5    | 인에이블 LNA 624       | 디스에이블                       |

| 출력 커플 1 | 비활성/최소 이득 구성       | LNA 출력 610을 LNA 출력 611에 커플링 |

| 출력 커플 2 | 비활성/최소 이득 구성       | LNA 출력 611을 LNA 출력 610에 커플링 |

[0044]

- [0045] [0049] 따라서, LNA 모듈(600)이 출력 커플링 동작 모드에서 동작할 때, 제1 수신기에 의해 제공된 신호는 교정 및/또는 테스팅을 수행하기 위하여 제2 수신기에 의해 사용될 수 있다. 전용 테스트 신호 생성기들은 수신기 설계로부터 제거될 수 있고, 다른 수신기들로부터의 LO 신호 생성기들은 교정 및/또는 테스트 신호를 제공하기 위하여 사용될 수 있다.

- [0046] [0050] 도 6b는 예시적인 실시예들에 따른, 도 6a의 커플러(640)의 블록 다이어그램이다. 커플러(640)는 선택적인 양방향 증폭기(645)(파선들 내에 도시됨)를 포함할 수 있다. 양방향 증폭기(645)는 LNA 모듈 출력 단자(610)를 LNA 모듈 출력 단자(620)에 커플링할 수 있다.

- [0047] [0051] 예컨대, 양방향 증폭기(645)는 LNA 모듈 출력 단자(610)를 통하여 LO(누설) 신호를 증폭기 입력 신호로서 수신할 수 있다. 양방향 증폭기(645)는 LO 신호를 증폭할 수 있고, 그리고 증폭된 LO 신호를 LNA 모듈 출력 단자(620)에 커플링할 수 있다. 일부 실시예들에서, 양방향 증폭기(645)는 또한 수신된 신호에 대해, 선택 가능한 양의 이득, 이를테면 10 내지 20 dB의 이득을 제공할 수 있다.

- [0048] [0052] 일부 실시예들에서, 커플러 제어 신호(665)는 커플러(640)를 인에이블(활성화되게)하고, 커플러(640)를 디스에이블(비활성 및/또는 격리되게)하고, 양방향 증폭기(645)의 이득 양들을 결정하고, 및/또는 양방향 증폭기(645) 신호 흐름 방향(예컨대, 제1 LNA 모듈 출력 단자(610)로부터 제2 LNA 모듈 출력 단자(611)로 또는 제2 LNA 모듈 출력 단자(611)로부터 제1 LNA 모듈 출력 단자(610)로)을 결정할 수 있다. 도 6a에 대해 위에서 설명된 바와 같이, 커플러 제어 신호(665)는 제어 신호 생성기(632)에 의해 구동될 수 있다.

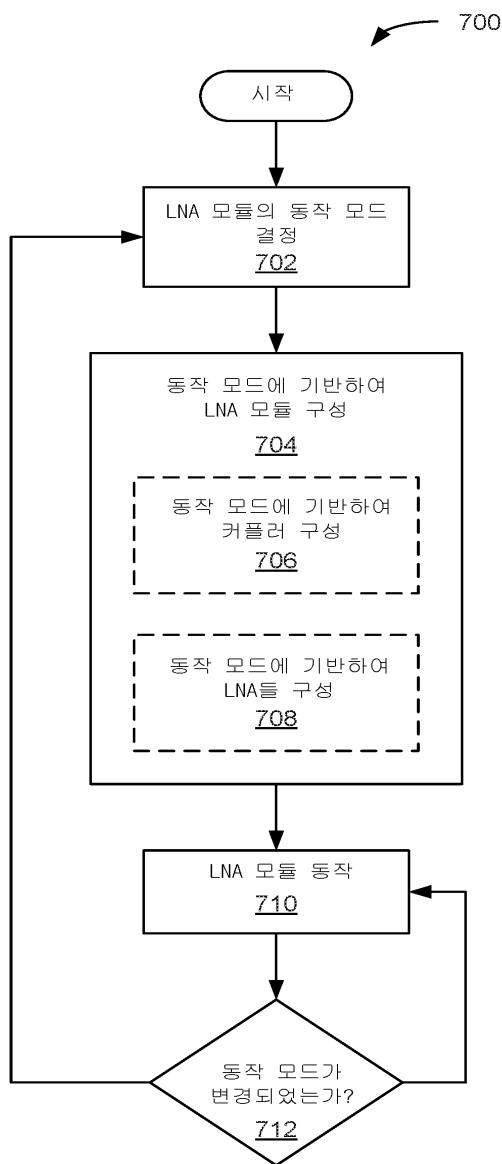

- [0049] [0053] 도 7은 예시적인 실시예들에 따른, LNA 모듈(600)을 동작시키기 위한 예시적인 동작(700)을 묘사하는 예시적인 흐름도를 도시한다. 또한 도 2-도 6b를 참조하면, LNA 모듈(600)의 동작 모드가 결정된다(702). 예컨대, LNA 모듈(600)은 무선 디바이스(110) 내의 하나 또는 그 초과의 수신기들(예컨대, 수신기들(560-563))을 교정하기 위하여 출력 커플링 동작 모드에서 동작될 수 있다. 다른 예에서, LNA 모듈(600)은 무선 디바이스(110) 내의 하나 또는 그 초과의 수신기들을 통하여 통신 신호들을 수신하도록 정상 동작 모드에서 동작될 수 있다. 일부 실시예들에서, LNA 모듈(600)의 동작 모드는 LNA 모듈(600)에 의해 수신된 모듈 제어 신호(606)에 의해 결정될 수 있다.

- [0050] [0054] 다음으로, LNA 모듈(600)은 결정된 동작 모드에 기반하여 구성될 수 있다(704). 일부 실시예들에서, LNA 모듈(600)의 구성은 LNA 모듈(600)의 결정된 동작 모드에 기반하여 커플러(640)를 구성하는 것을 포함할 수 있다(706). 예컨대, 커플러(640)는 표 1에 대해 위에서 설명된 바와 같이 LNA 모듈(600)의 동작 모드에 기반하여 구성될 수 있다. 일부 실시예들에서, LNA 모듈(600)의 구성은 LNA 모듈(600)의 결정된 동작 모드에 기반하여 LNA 모듈(600) 내에 포함된 하나 또는 그 초과의 LNA들을 구성하는 것을 포함할 수 있다(708). 예컨대, LNA 들(620-624)의 구성은 표 1에 대해 위에서 설명된 바와 같이 LNA 모듈(600)의 동작 모드에 기반할 수 있다.

- [0051] [0055] 다음으로, LNA 모듈(600)이 동작된다(710). LNA 모듈(600)은 LNA 모듈(600) 구성(704에서 결정됨)에 기반하여 동작될 수 있다. 따라서, 통신 신호들은 LNA 모듈(600)의 결정된 동작 모드에 기반하여 LNA 출력 단자들 사이에서 증폭되고 및/또는 라우팅될 수 있다. 일부 경우들에서, 교정 신호는 제1 LNA 모듈 출력 단자로부터 제2 LNA 모듈 출력 단자로 라우팅될 수 있다.

- [0052] [0056] 다음으로, 동작 모드의 변경이 결정된다(712). 동작 모드가 변경되면, 동작들은 702로 진행한다. 동작 모드가 동일하게 유지되면, 동작들은 710으로 진행한다.

- [0053] [0057] 본원에 개시된 실시예들에 관련하여 설명된 다양한 예시적인 로지컬 블록들, 모듈들 및 회로들은 범용 프로세서, DSP(digital signal processor), ASIC(application specific integrated circuit), FPGA(field programmable gate array) 또는 다른 프로그램가능 로직 디바이스, 이산 게이트 또는 트랜지스터 로직, 이산 하드웨어 컴포넌트들, 또는 본원에 설명된 기능들을 수행하도록 설계된 이들의 임의의 조합으로 구현되거나 수행될 수 있다. 범용 프로세서는 마이크로프로세서일 수 있지만, 대안적으로, 프로세서는 임의의 종래의 프로세서, 제어기, 마이크로제어기, 또는 상태 머신일 수 있다. 프로세서는 또한 컴퓨팅 디바이스들의 조합, 예컨대 DSP와 마이크로프로세서의 조합, 복수의 마이크로프로세서들, DSP 코어와 함께 하나 또는 그 초과의 마이크로프로세서들, 또는 임의의 다른 그런 구성으로서 구현될 수 있다.

- [0054] [0058] 하나 또는 그 초과의 예시적인 실시예들에서, 설명된 기능들은 하드웨어, 소프트웨어, 펌웨어 또는 이들의 임의의 조합으로 구현될 수 있다. 소프트웨어로 구현되면, 기능들은 컴퓨터-판독가능 매체상에 하나 또는 그 초과의 명령들 또는 코드로서 저장되거나 이를 통해 송신될 수 있다. 컴퓨터-판독가능 매체들은 컴퓨터 저장 매체들 및 하나의 장소에서 다른 장소로 컴퓨터 프로그램의 전달을 가능하게 하는 임의의 매체를 포함하는

통신 매체들 둘 모두를 포함한다. 저장 매체들은 컴퓨터에 의해 액세스될 수 있는 임의의 이용 가능한 매체들일 수 있다. 제한이 아닌 예로서, 그런 컴퓨터-판독가능 매체들은 RAM, ROM, EEPROM, CD-ROM 또는 다른 광학 디스크 저장부, 자기 디스크 저장부 또는 다른 자기 저장 디바이스들, 또는 명령들 또는 데이터 구조들의 형태의 원하는 프로그램 코드를 반송하거나 저장하기 위하여 사용될 수 있고 컴퓨터에 의해 액세스될 수 있는 임의의 다른 매체를 포함할 수 있다. 또한, 임의의 연결은 적절히 컴퓨터-판독가능 매체라 지칭된다. 예컨대, 소프트웨어가 웹 사이트, 서버, 또는 다른 원격 소스로부터 동축 케이블, 광섬유 케이블, 트위스트 페어(twisted pair), DSL(digital subscriber line), 또는 무선 기술들, 이를테면 적외선, 라디오 및 마이크로파를 사용하여 송신되면, 동축 케이블, 광섬유 케이블, 트위스트 페어, DSL 또는 무선 기술들, 이를테면 적외선, 라디오, 및 마이크로파는 매체의 정의 내에 포함된다. 본원에 사용된 디스크(disk) 및 디스크(disc)는 CD(compact disc), 레이저 디스크(disc), 광학 디스크(disc), DVD(digital versatile disc), 플로피 디스크(disk) 및 블루레이 디스크(disc)를 포함하고, 디스크(disk)들은 보통 데이터를 자기적으로 재생하는 반면, 디스크(disc)들은 레이저들을 사용하여 광학적으로 데이터를 재생한다. 위의 조합들은 또한 컴퓨터-판독가능 매체들의 범위 내에 포함되어야 한다.

[0055] [0059] 전술한 명세서에서, 본 실시예들은 본 발명의 특정 예시적인 실시예들을 참조하여 설명되었다. 그러나, 다양한 수정들 및 변화들이 첨부된 청구항들에 설명된 바와 같은 본 개시내용의 더 넓은 범위에서 벗어나지 않고 이루어질 수 있다는 것이 명백할 것이다. 따라서, 명세서 및 도면들은 제한적 의미보다 오히려 예시로 고려되어야 한다.

도면

도면1

## 도면2

도면3

도면4

## 도면5

## 도면6a

도면6b

## 도면7