(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5374546号

(P5374546)

(45) 発行日 平成25年12月25日(2013.12.25)

(24) 登録日 平成25年9月27日(2013.9.27)

(51) Int.Cl.

F 1

**H01L 21/336 (2006.01)**

**H01L 29/788 (2006.01)**

**H01L 29/792 (2006.01)**

**H01L 21/8247 (2006.01)**

**H01L 27/115 (2006.01)**

**H01L 29/78 371**

**H01L 27/10 434**

**G11C 17/00 623Z**

請求項の数 14 (全 54 頁) 最終頁に続く

(21) 出願番号 特願2011-136165 (P2011-136165)

(22) 出願日 平成23年6月20日 (2011.6.20)

(62) 分割の表示 特願2006-139823 (P2006-139823)

の分割

原出願日 平成18年5月19日 (2006.5.19)

(65) 公開番号 特開2011-228729 (P2011-228729A)

(43) 公開日 平成23年11月10日 (2011.11.10)

審査請求日 平成23年6月20日 (2011.6.20)

(31) 優先権主張番号 特願2005-265548 (P2005-265548)

(32) 優先日 平成17年9月13日 (2005.9.13)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 岡 保志

東京都千代田区丸の内二丁目4番1号 株

式会社ルネサステクノロジ内

(72) 発明者 志波 和佳

東京都千代田区丸の内二丁目4番1号 株

式会社ルネサステクノロジ内

審査官 小山 満

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1主面およびその裏側の第2主面を有する半導体基板と、

前記半導体基板の第1主面に配置された主回路形成領域と、

前記半導体基板の第1主面に配置された不揮発性メモリ領域とを備え、

前記不揮発性メモリ領域には、

前記半導体基板の主面に形成された第1導電型の第1ウエルと、

前記第1導電型とは反対の導電型を有する第2導電型のウエルであって、前記第1ウエルに内包されるように配置された第2ウエルと、

前記第2導電型のウエルであって、前記第2ウエルとは電気的に分離された状態で、前記第2ウエルに対して沿うように、前記第1ウエルに内包されるように配置された第3ウエルと、

前記第2導電型のウエルであって、前記第2ウエルおよび前記第3ウエルとは電気的に分離された状態で、前記第2ウエルに対して沿うように、前記第1ウエルに内包されるように配置された第4ウエルと、

前記第2ウエル、前記第3ウエルおよび前記第4ウエルに平面的に重なるように配置された不揮発性メモリセルとを備え、

前記不揮発性メモリセルは、

前記第2ウエル、前記第3ウエルおよび前記第4ウエルに平面的に重なるように第1方向に延在して配置された浮遊ゲート電極と、

10

20

前記浮遊ゲート電極が前記第2ウエルに平面的に重なる第1位置に形成されたデータ書き込みおよび消去用の素子と、

前記浮遊ゲート電極が前記第3ウエルに平面的に重なる第2位置に形成されたデータ読み出し用の電界効果トランジスタと、

前記浮遊ゲート電極が前記第4ウエルに平面的に重なる第3位置に形成された容量素子とを有し、

前記データ書き込みおよび消去用の素子は、

前記浮遊ゲート電極の前記第1位置に形成される第1電極と、前記第1電極および前記半導体基板の間に形成される第1絶縁膜と、前記第2ウエル内において前記第1電極を挟み込む位置に形成される一対の半導体領域と、前記第2ウエルとを有し、

10

前記データ読み出し用の電界効果トランジスタは、

前記浮遊ゲート電極の前記第2位置に形成される第2電極と、前記第2電極および前記半導体基板の間に形成される第2絶縁膜と、前記第3ウエル内において前記第2電極を挟み込む位置に形成された第1導電型の一対の半導体領域とを有し、

前記容量素子は、

前記浮遊ゲート電極の前記第3位置に形成される第3電極と、前記第3電極および前記半導体基板の間に形成される第3絶縁膜と、前記第4ウエル内において前記第3電極を挟み込む位置に形成される一対の半導体領域と、前記第4ウエルとを有し、

前記データ書き込みおよび消去用の素子の前記一対の半導体領域は、互いに逆の導電型とされており、

20

前記容量素子の前記一対の半導体領域は、いずれも前記第2導電型とされていることを特徴とする半導体装置。

#### 【請求項2】

請求項1記載の半導体装置において、

前記データ書き込みおよび消去用の素子の配置領域の前記浮遊ゲート電極には、前記第1導電型の半導体領域と前記第2導電型の半導体領域との両方が形成されていることを特徴とする半導体装置。

#### 【請求項3】

請求項2記載の半導体装置において、

前記データ書き込みおよび消去用の素子の配置領域の前記浮遊ゲート電極の前記第1導電型の半導体領域と前記第2導電型の半導体領域とは、

30

前記浮遊ゲート電極の導電型が、前記第1方向に交差する第2方向に沿って前記第1導電型と前記第2導電型とに分かれ、

前記浮遊ゲート電極の導電型が、前記第1方向に沿って前記第1導電型と前記第2導電型とに分かれないように配置されていることを特徴とする半導体装置。

#### 【請求項4】

請求項3記載の半導体装置において、

前記データ書き込みおよび消去用の素子の配置領域の前記浮遊ゲート電極の前記第1導電型の半導体領域と前記第2導電型の半導体領域との境界は、前記第2方向における前記浮遊ゲート電極の中央に配置されていることを特徴とする半導体装置。

40

#### 【請求項5】

請求項2記載の半導体装置において、

前記データ書き込みおよび消去用の素子の前記一対の半導体領域と、前記容量素子の前記一対の半導体領域の上面にはシリサイド層が形成されており、

前記浮遊ゲート電極の上面には絶縁膜が形成されシリサイド層が形成されていないことを特徴とする半導体装置。

#### 【請求項6】

第1主面およびその裏側の第2主面を有する半導体基板と、

前記半導体基板の第1主面に配置された主回路形成領域と、

前記半導体基板の第1主面に配置された不揮発性メモリ領域とを備え、

50

前記不揮発性メモリ領域には、

前記半導体基板の正面に形成された第1導電型の第1ウエルと、

前記第1導電型とは反対の導電型を有する第2導電型のウエルであって、前記第1ウエルに内包されるように配置された第2ウエルと、

前記第2導電型のウエルであって、前記第2ウエルとは電気的に分離された状態で、前記第2ウエルに対して沿うように、前記第1ウエルに内包されるように配置された第3ウエルと、

前記第2導電型のウエルであって、前記第2ウエルおよび前記第3ウエルとは電気的に分離された状態で、前記第2ウエルに対して沿うように、前記第1ウエルに内包されるように配置された第4ウエルと、

前記第2ウエル、前記第3ウエルおよび前記第4ウエルに平面的に重なるように配置された不揮発性メモリセルとを備え、

前記不揮発性メモリセルは、

前記第2ウエル、前記第3ウエルおよび前記第4ウエルに平面的に重なるように第1方向に延在して配置された浮遊ゲート電極と、

前記浮遊ゲート電極が前記第2ウエルに平面的に重なる第1位置に形成されたデータ書き込みおよび消去用の素子と、

前記浮遊ゲート電極が前記第3ウエルに平面的に重なる第2位置に形成されたデータ読み出し用の電界効果トランジスタと、

前記浮遊ゲート電極が前記第4ウエルに平面的に重なる第3位置に形成された容量素子とを有し、

前記データ書き込みおよび消去用の素子は、

前記浮遊ゲート電極の前記第1位置に形成される第1電極と、前記第1電極および前記半導体基板の間に形成される第1絶縁膜と、前記第2ウエル内において前記第1電極を挟み込む位置に形成される一対の半導体領域と、前記第2ウエルとを有し、

前記データ読み出し用の電界効果トランジスタは、

前記浮遊ゲート電極の前記第2位置に形成される第2電極と、前記第2電極および前記半導体基板の間に形成される第2絶縁膜と、前記第3ウエル内において前記第2電極を挟み込む位置に形成された第1導電型の一対の半導体領域とを有し、

前記容量素子は、

前記浮遊ゲート電極の前記第3位置に形成される第3電極と、前記第3電極および前記半導体基板の間に形成される第3絶縁膜と、前記第4ウエル内において前記第3電極を挟み込む位置に形成される一対の半導体領域と、前記第4ウエルとを有し、

前記容量素子の前記一対の半導体領域は、互いに逆の導電型とされており、

前記データ書き込みおよび消去用の素子の前記一対の半導体領域は、いずれも前記第2導電型とされていることを特徴とする半導体装置。

#### 【請求項7】

請求項6記載の半導体装置において、

前記容量素子の配置領域の前記浮遊ゲート電極には、前記第1導電型の半導体領域と前記第2導電型の半導体領域との両方が形成されていることを特徴とする半導体装置。

#### 【請求項8】

請求項7記載の半導体装置において、

前記容量素子の配置領域の前記浮遊ゲート電極の前記第1導電型の半導体領域と前記第2導電型の半導体領域とは、

前記浮遊ゲート電極の導電型が、前記第1方向に交差する第2方向に沿って前記第1導電型と前記第2導電型とに分かれ、

前記浮遊ゲート電極の導電型が、前記第1方向に沿って前記第1導電型と前記第2導電型とに分かれないように配置されていることを特徴とする半導体装置。

#### 【請求項9】

請求項8記載の半導体装置において、

10

20

30

40

50

前記容量素子の配置領域の前記浮遊ゲート電極の前記第1導電型の半導体領域と前記第2導電型の半導体領域との境界は、前記第2方向における前記浮遊ゲート電極の中央に配置されていることを特徴とする半導体装置。

**【請求項10】**

請求項7記載の半導体装置において、

前記データ書き込みおよび消去用の素子の前記一対の半導体領域と、前記容量素子の前記一対の半導体領域の上面にはシリサイド層が形成されており、

前記浮遊ゲート電極の上面には絶縁膜が形成されシリサイド層が形成されていないことを特徴とする半導体装置。

**【請求項11】**

10

第1主面およびその裏側の第2主面を有する半導体基板と、

前記半導体基板の第1主面に配置された主回路形成領域と、

前記半導体基板の第1主面に配置された不揮発性メモリ領域とを備え、

前記不揮発性メモリ領域には、

前記半導体基板の主面に形成された第1導電型の第1ウエルと、

前記第1導電型とは反対の導電型を有する第2導電型のウエルであって、前記第1ウエルに内包されるように配置された第2ウエルと、

前記第2導電型のウエルであって、前記第2ウエルとは電気的に分離された状態で、前記第2ウエルに対して沿うように、前記第1ウエルに内包されるように配置された第3ウエルと、

20

前記第2導電型のウエルであって、前記第2ウエルおよび前記第3ウエルとは電気的に分離された状態で、前記第2ウエルに対して沿うように、前記第1ウエルに内包されるように配置された第4ウエルと、

前記第2ウエル、前記第3ウエルおよび前記第4ウエルに平面的に重なるように配置された不揮発性メモリセルとを備え、

前記不揮発性メモリセルは、

前記第2ウエル、前記第3ウエルおよび前記第4ウエルに平面的に重なるように第1方向に延在して配置された浮遊ゲート電極と、

前記浮遊ゲート電極が前記第2ウエルに平面的に重なる第1位置に形成されたデータ書き込みおよび消去用の素子と、

30

前記浮遊ゲート電極が前記第3ウエルに平面的に重なる第2位置に形成されたデータ読み出し用の電界効果トランジスタと、

前記浮遊ゲート電極が前記第4ウエルに平面的に重なる第3位置に形成された容量素子とを有し、

前記データ書き込みおよび消去用の素子は、

前記浮遊ゲート電極の前記第1位置に形成される第1電極と、前記第1電極および前記半導体基板の間に形成される第1絶縁膜と、前記第2ウエル内において前記第1電極を挟み込む位置に形成される一対の半導体領域と、前記第2ウエルとを有し、

前記データ読み出し用の電界効果トランジスタは、

前記浮遊ゲート電極の前記第2位置に形成される第2電極と、前記第2電極および前記半導体基板の間に形成される第2絶縁膜と、前記第3ウエル内において前記第2電極を挟み込む位置に形成された第1導電型の一対の半導体領域とを有し、

40

前記容量素子は、

前記浮遊ゲート電極の前記第3位置に形成される第3電極と、前記第3電極および前記半導体基板の間に形成される第3絶縁膜と、前記第4ウエル内において前記第3電極を挟み込む位置に形成される一対の半導体領域と、前記第4ウエルとを有し、

前記容量素子の前記一対の半導体領域は、互いに逆の導電型とされており、

前記データ書き込みおよび消去用の素子の前記一対の半導体領域は、互いに逆の導電型とされており、

前記データ書き込みおよび消去用の素子と前記容量素子との配置領域の前記浮遊ゲート

50

電極には、前記第1導電型の半導体領域と前記第2導電型の半導体領域との両方が形成されていることを特徴とする半導体装置。

【請求項12】

請求項11記載の半導体装置において、

前記データ書き込みおよび消去用の素子と前記容量素子との配置領域の前記浮遊ゲート電極の前記第1導電型の半導体領域と前記第2導電型の半導体領域とは、

前記浮遊ゲート電極の導電型が、前記第1方向に交差する第2方向に沿って前記第1導電型と前記第2導電型とに分かれ、

前記浮遊ゲート電極の導電型が、前記第1方向に沿って前記第1導電型と前記第2導電型とに分かれないように配置されていることを特徴とする半導体装置。 10

【請求項13】

請求項12記載の半導体装置において、

前記データ書き込みおよび消去用の素子と前記容量素子との配置領域の前記浮遊ゲート電極の前記第1導電型の半導体領域と前記第2導電型の半導体領域との境界は、前記第2方向における前記浮遊ゲート電極の中央に配置されていることを特徴とする半導体装置。

【請求項14】

請求項11記載の半導体装置において、

前記データ書き込みおよび消去用の素子の前記一対の半導体領域と、前記容量素子の前記一対の半導体領域の上面にはシリサイド層が形成されており、

前記浮遊ゲート電極の上面には絶縁膜が形成されシリサイド層が形成されていないことを特徴とする半導体装置。 20

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置技術に関し、特に、不揮発性メモリを有する半導体装置に適用して有効な技術に関するものである。

【背景技術】

【0002】

半導体装置の中には、その内部に、例えばトリミング時、救済時およびLCD(Liquid Crystal Device)の画像調整時に使用する情報や半導体装置の製造番号等のように比較的小容量の情報を記憶するための不揮発性メモリ回路部を有するものがある。 30

【0003】

この種の不揮発性メモリ回路部を有する半導体装置については、例えば特開2001-185633号公報(特許文献1)に記載がある。この文献には、半導体基板上に絶縁層によって絶縁して配置された单一導電層上に構成されるEEPROM(Electric Erasable Programmable Read Only Memory)デバイスにおいて、ピット当たりの面積を小さくできる単一レベル・ポリEEPROMデバイスが開示されている。

【0004】

また、例えば特開2001-257324号公報(特許文献2)には、単層ポリフラッシュ技術で形成された不揮発性記憶素子において、長期の情報保持性能を向上させることのできる技術が開示されている。 40

【0005】

さらに、例えばUSP6788574(特許文献3)のFig.7には、容量部、書き込みトランジスタ、読み出しトランジスタが、それぞれnウェルで分離されている構成が開示されている。また、特許文献3のFig.4A-4C、column 6-7には、書き込み/消去はFNトンネル電流で行う構成が開示されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2001-185633号公報 50

【特許文献2】特開2001-257324号公報

【特許文献3】U.S.P. 6,788,574のFig.7, Fig.4A-4C

【発明の概要】

【発明が解決しようとする課題】

【0007】

ところで、本発明者は上記不揮発性メモリにおいて、書き込み用電界効果トランジスタにチャネル全面のFNトンネル電流によりデータを書き込むことについて検討した。その結果、上記FNトンネル電流によりデータ書き込みを行うと、書き込み用電界効果トランジスタのソース・ドレイン用の半導体領域とウエルとの接合耐圧が持たずブレークダウンし書き込み用電界効果トランジスタが劣化する問題、データ書き換えが不安定になる問題およびデータを上手く書き込むことができない問題等が生じることを見出した。

10

【0008】

そこで、本発明の目的は、不揮発性メモリセルのデータ書き込みおよび消去用の素子において、チャネル全面のFNトンネル電流によりデータを書き換えることのできる技術を提供することにある。

【0009】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0010】

20

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0011】

すなわち、本発明は、共通の浮遊ゲート電極をゲート電極とするデータ書き込みおよび消去用の素子とデータ読み出し用のトランジスタとを有する不揮発性メモリセルにおいて、上記データ書き込みおよび消去用の素子とデータ読み出し用のトランジスタとを互いに電気的に分離された同一導電型のウエル内に設け、データ書き込みおよび消去用の素子の一対の半導体領域をウエルと同一導電型の半導体領域により形成したものである。

【発明の効果】

【0012】

30

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0013】

すなわち、共通の浮遊ゲート電極をゲート電極とするデータ書き込みおよび消去用の素子とデータ読み出し用のトランジスタとを有する不揮発性メモリセルにおいて、上記データ書き込みおよび消去用の素子とデータ読み出し用のトランジスタとを互いに電気的に分離された同一導電型のウエル内に設け、データ書き込みおよび消去用の素子の一対の半導体領域をウエルと同一導電型の半導体領域により形成する。これにより、不揮発性メモリセルのデータ書き込みおよび消去用の素子において、チャネル全面のFNトンネル電流によりデータを書き換えることができる。

40

【図面の簡単な説明】

【0014】

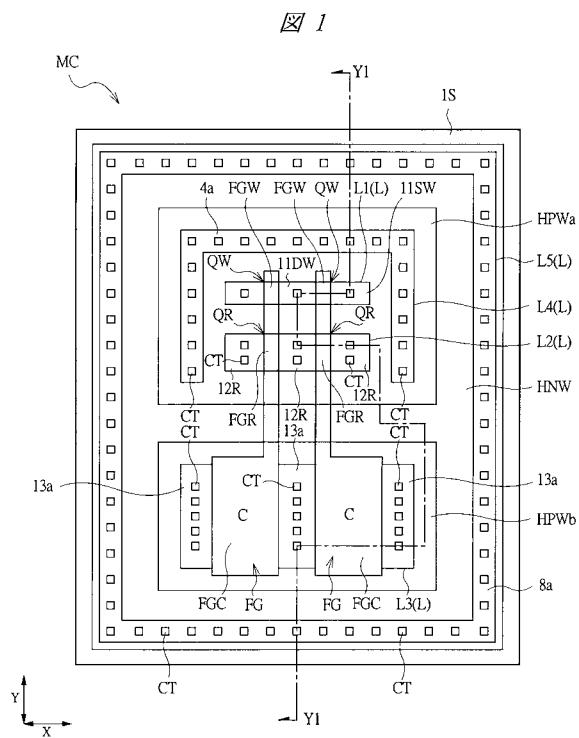

【図1】本発明者が検討した不揮発性メモリのメモリセルの平面図である。

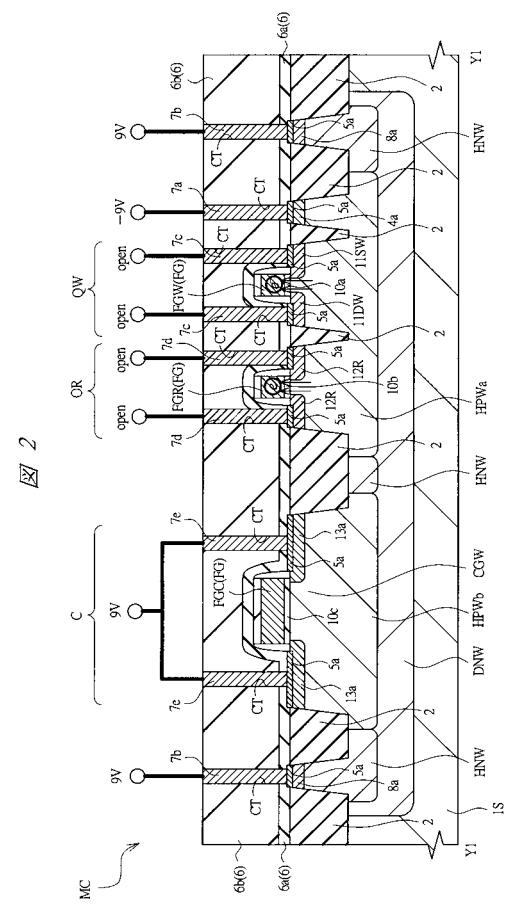

【図2】図1のY1-Y1線の断面図である。

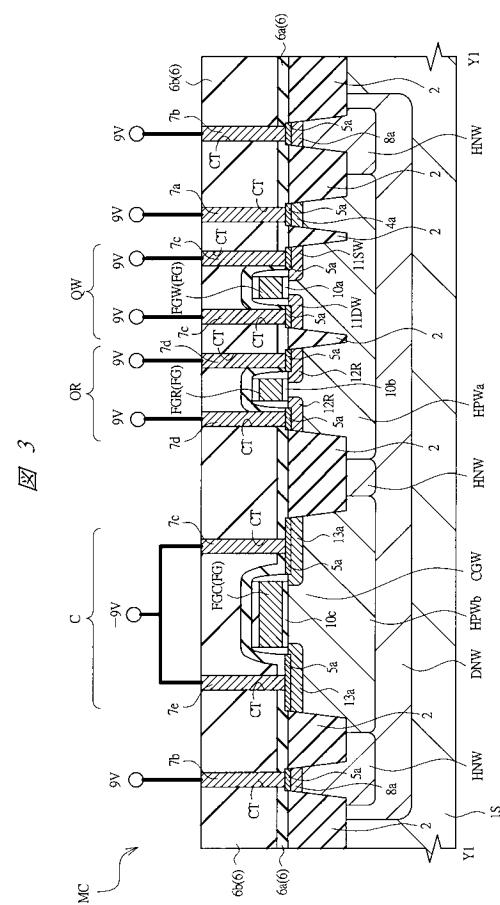

【図3】図1のY1-Y1線の断面図である。

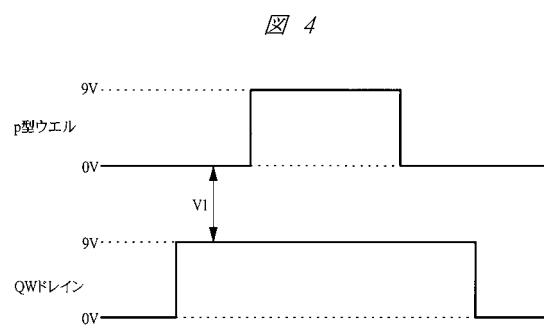

【図4】本発明者が検討した不揮発性メモリのデータ消去動作時における電圧印加のタイミングを示す説明図である。

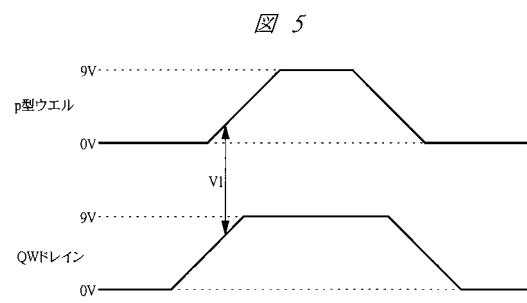

【図5】本発明者が検討した不揮発性メモリのデータ消去動作時における電圧印加のタイミングを示す説明図である。

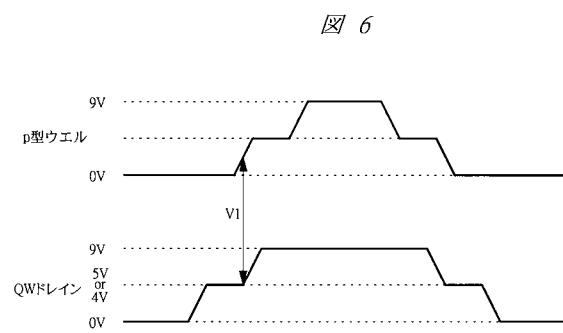

【図6】本発明者が検討した不揮発性メモリのデータ消去動作時における電圧印加のタイ

50

ミングを示す説明図である。

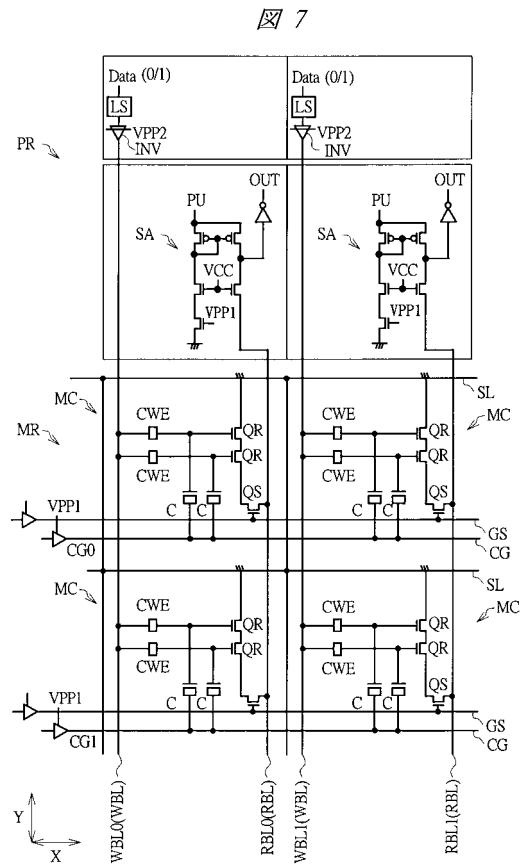

【図 7】本発明の一実施の形態である半導体装置における不揮発性メモリの要部回路図である。

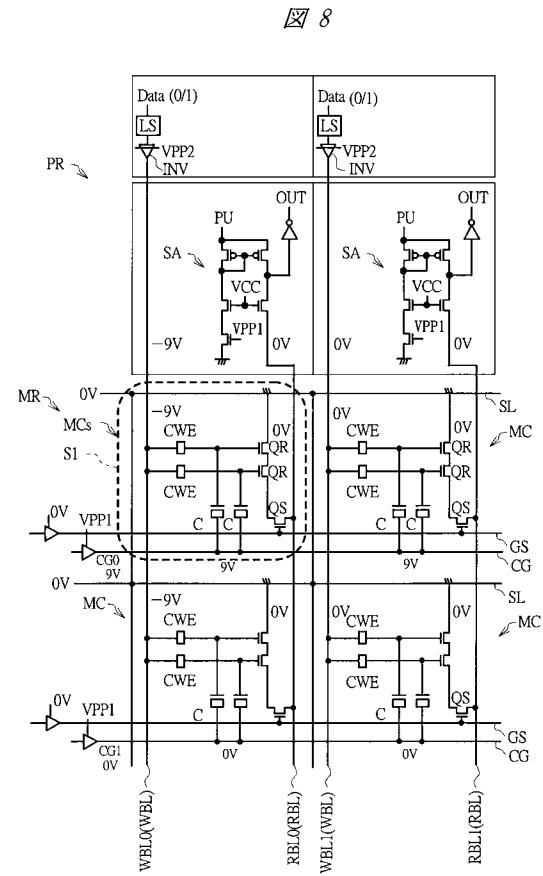

【図 8】図 7 の不揮発性メモリのデータ書き込み動作時における各部への印加電圧を示す回路図である。

【図 9】図 7 の不揮発性メモリのデータ消去動作時における各部への印加電圧を示す回路図である。

【図 10】図 7 の不揮発性メモリのデータ・ビット単位消去動作時における各部への印加電圧を示す回路図である。

【図 11】図 7 の不揮発性メモリのデータ読み出し動作時における各部への印加電圧を示す回路図である。 10

【図 12】本発明の一実施の形態である半導体装置における不揮発性メモリの 1 ビット分のメモリセルの平面図である。

【図 13】図 12 の Y 2 - Y 2 線の断面図である。

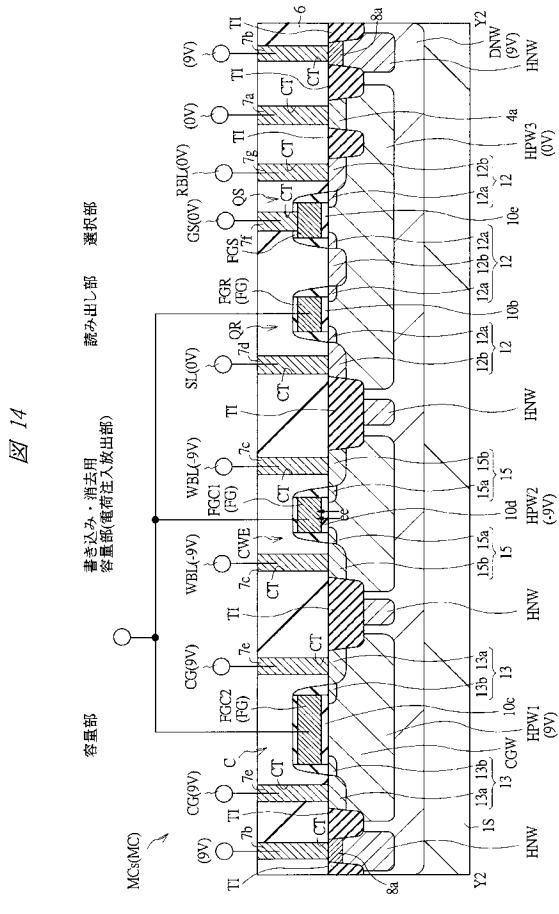

【図 14】本発明の一実施の形態である半導体装置における不揮発性メモリのデータ書き込み動作時のメモリセルでの各部への印加電圧の一例を示す図 12 の Y 2 - Y 2 線の断面図である。

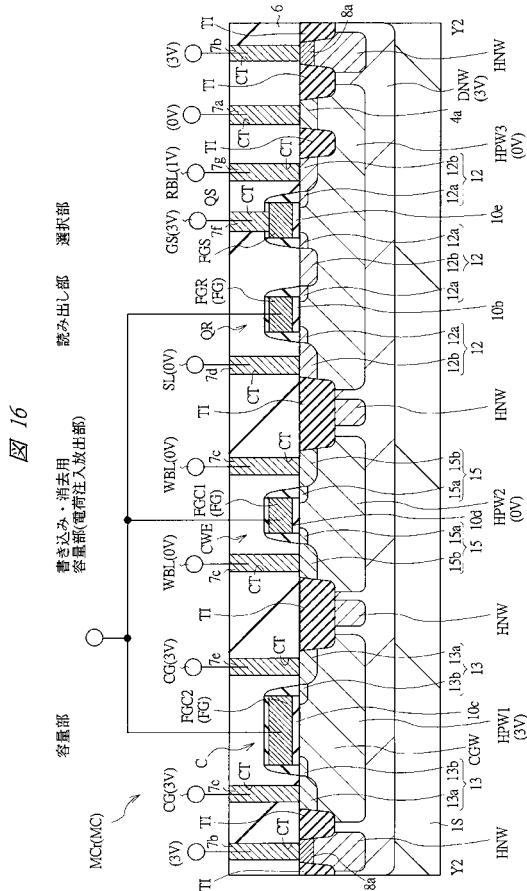

【図 15】本発明の一実施の形態である半導体装置の不揮発性メモリのデータ消去動作時における各部への印加電圧を示す図 12 の Y 2 - Y 2 線の断面図である。

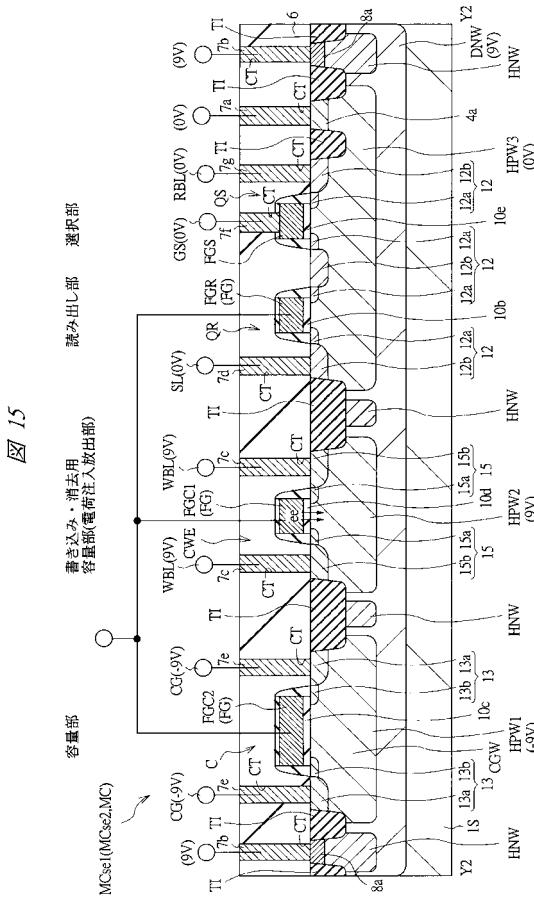

【図 16】本発明の一実施の形態である半導体装置の不揮発性メモリのデータ読み出し動作時における各部への印加電圧を示す図 12 の Y 2 - Y 2 線の断面図である。 20

【図 17】本発明の他の実施の形態である半導体装置の製造工程中の主回路形成領域の半導体基板の要部断面図である。

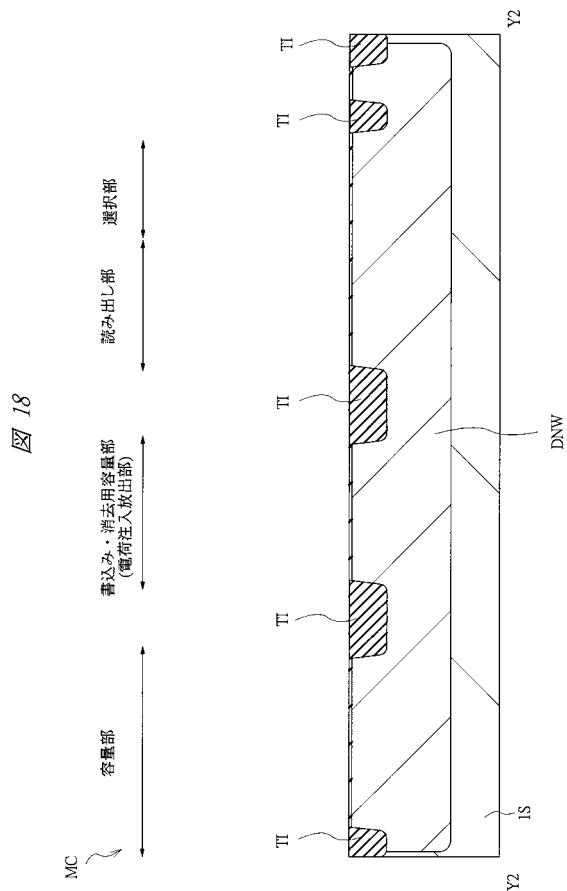

【図 18】図 17 と同一工程時の不揮発性メモリ領域の半導体基板の要部断面図である。

【図 19】図 17 および図 18 に続く半導体装置の製造工程中の主回路形成領域の半導体基板の要部断面図である。

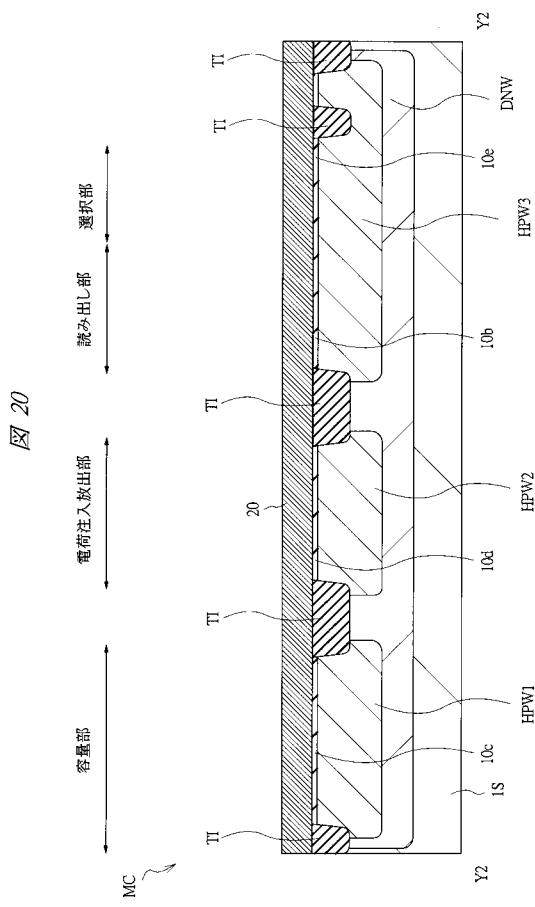

【図 20】図 19 と同一工程時の不揮発性メモリ領域の半導体基板の要部断面図である。

【図 21】図 19 および図 20 に続く半導体装置の製造工程中の主回路形成領域の半導体基板の要部断面図である。 30

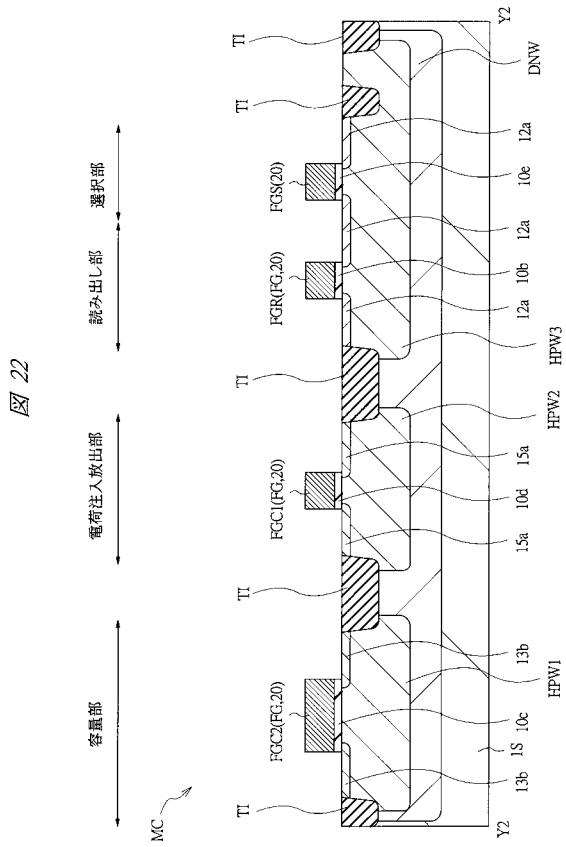

【図 22】図 21 と同一工程時の不揮発性メモリ領域の半導体基板の要部断面図である。

【図 23】図 21 および図 22 に続く半導体装置の製造工程中の主回路形成領域の半導体基板の要部断面図である。

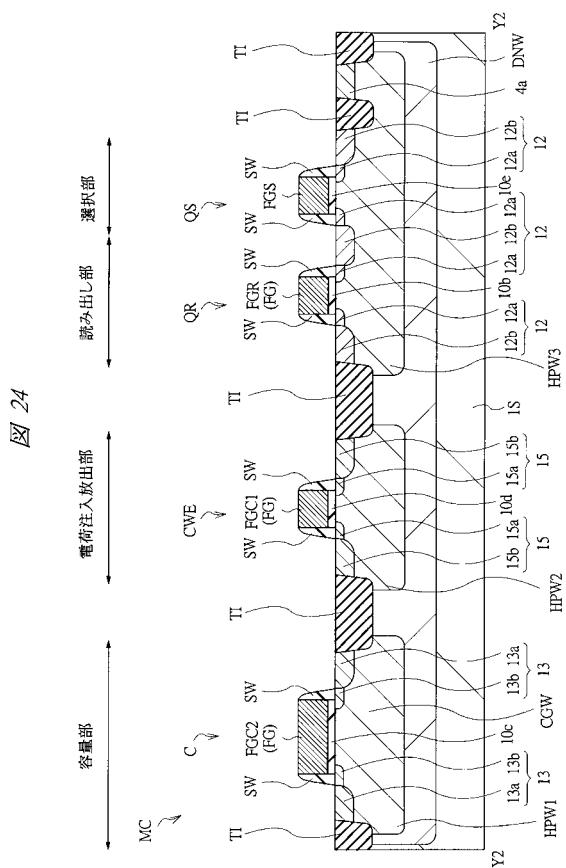

【図 24】図 23 と同一工程時の不揮発性メモリ領域の半導体基板の要部断面図である。

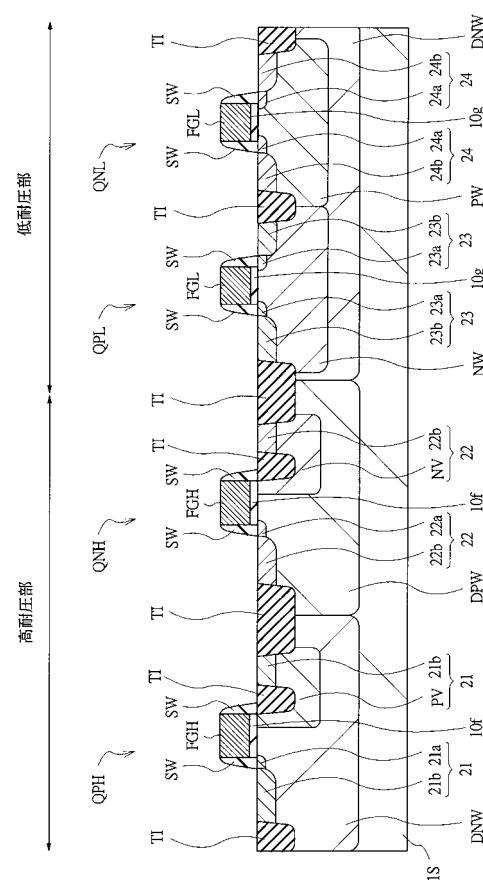

【図 25】図 23 および図 24 に続く半導体装置の製造工程中の主回路形成領域の半導体基板の要部断面図である。 40

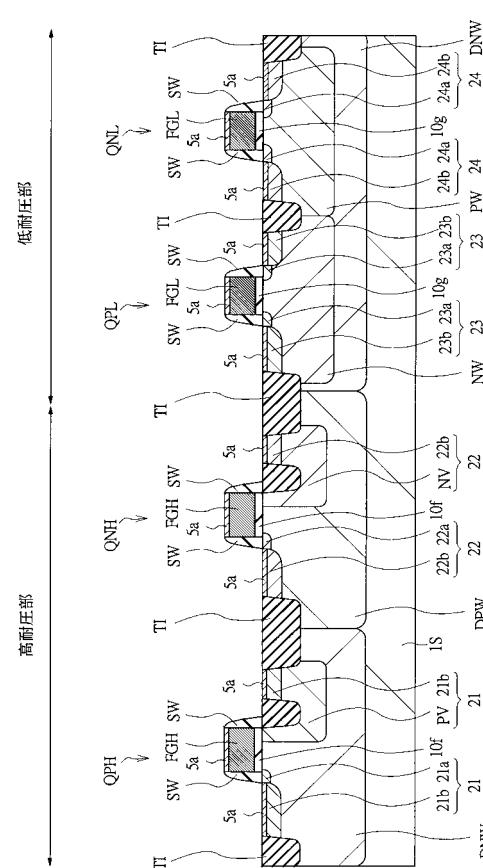

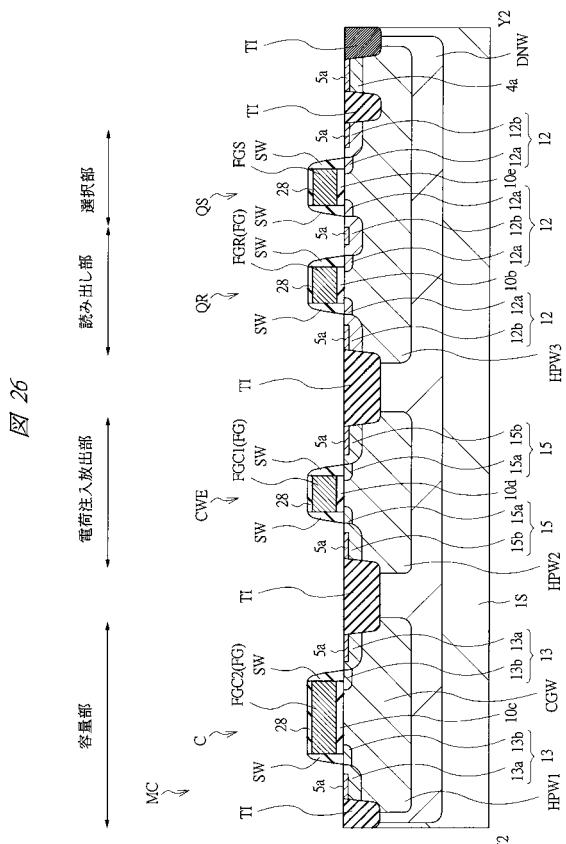

【図 26】図 25 と同一工程時の不揮発性メモリ領域の半導体基板の要部断面図である。

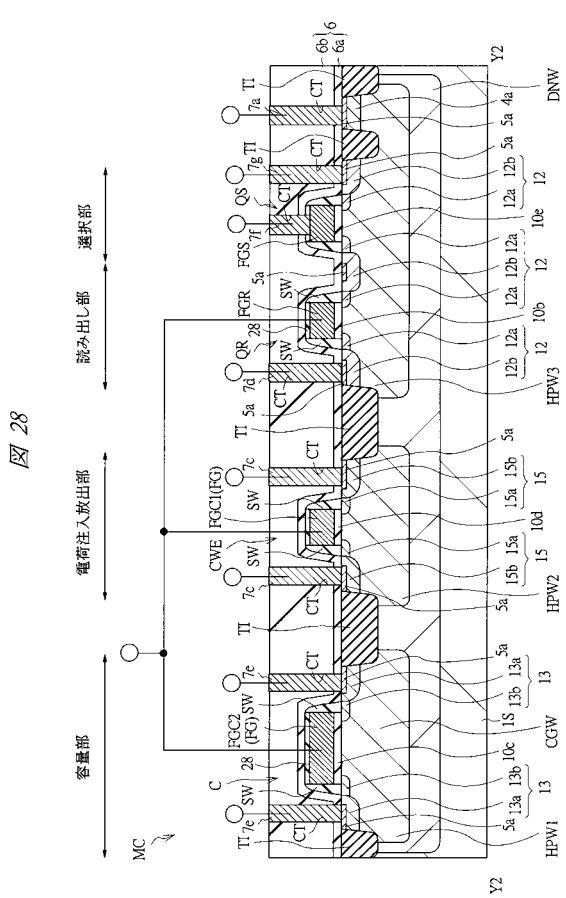

【図 27】図 25 および図 26 に続く半導体装置の製造工程中の主回路形成領域の半導体基板の要部断面図である。

【図 28】図 27 と同一工程時の不揮発性メモリ領域の半導体基板の要部断面図である。

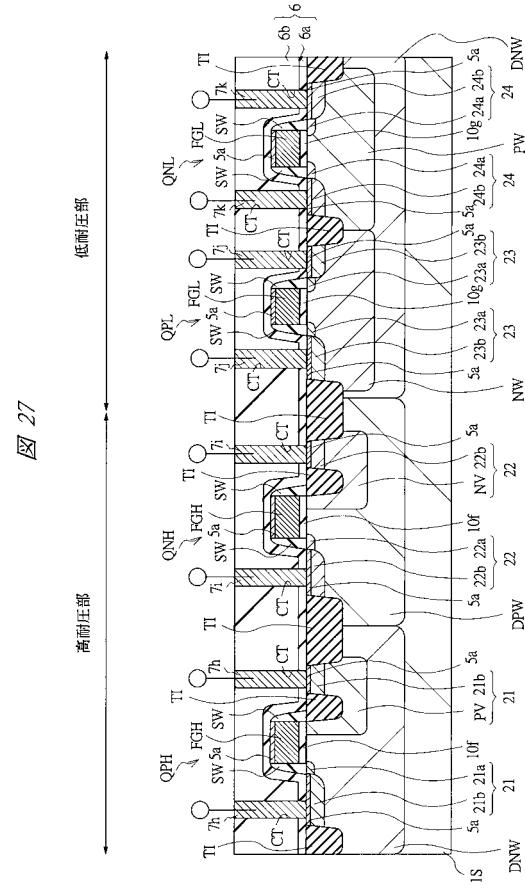

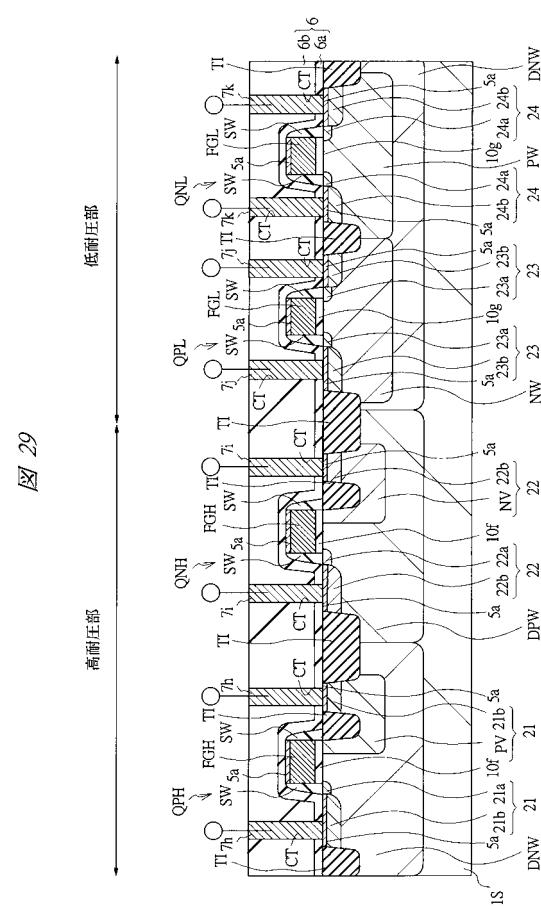

【図 29】本発明の他の実施の形態である半導体装置の主回路形成領域の半導体基板の断面図である。

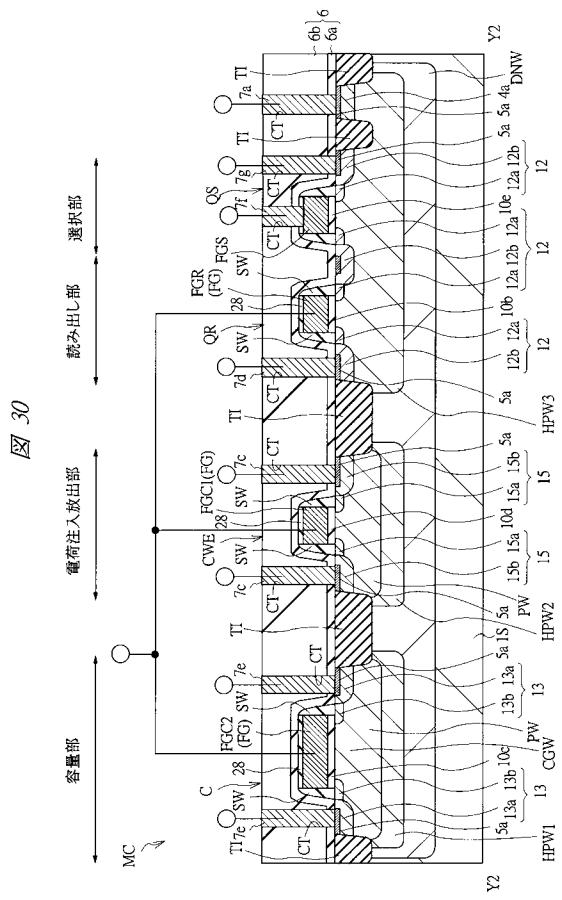

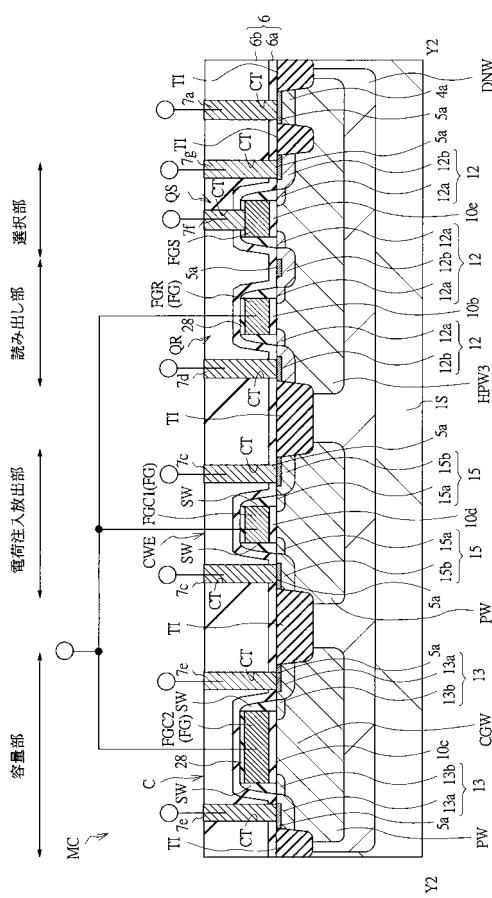

【図 30】図 29 と同じ半導体装置の不揮発性メモリ領域の半導体基板の断面図である。

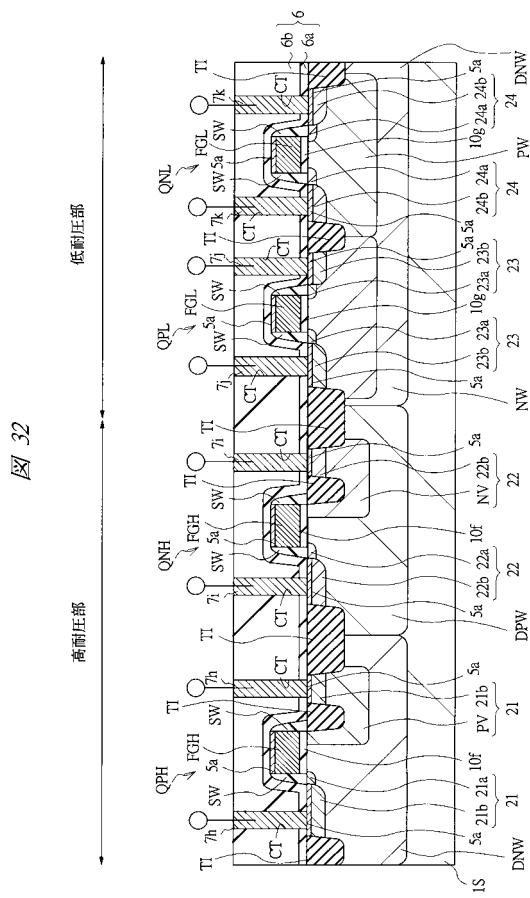

【図 31】図 29 および図 30 の半導体装置のデータ書き込み特性および消去特性の説明図である。

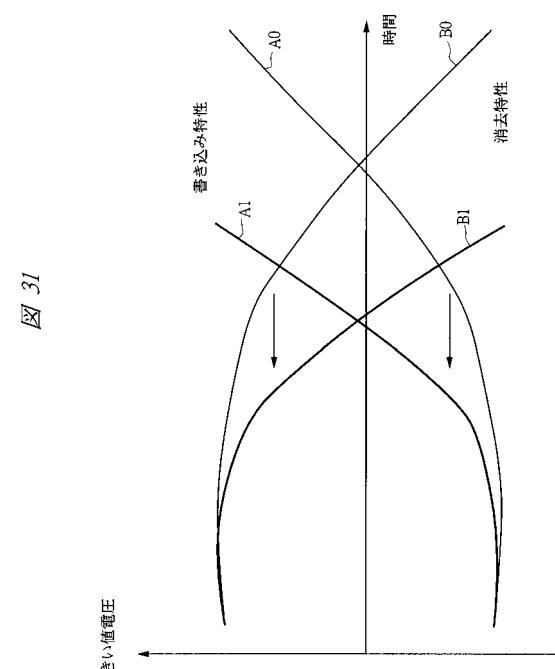

【図 32】本発明の他の実施の形態である半導体装置の主回路形成領域の半導体基板の断面図である。

【図 33】図 32 と同じ半導体装置の不揮発性メモリ領域の半導体基板の断面図である。

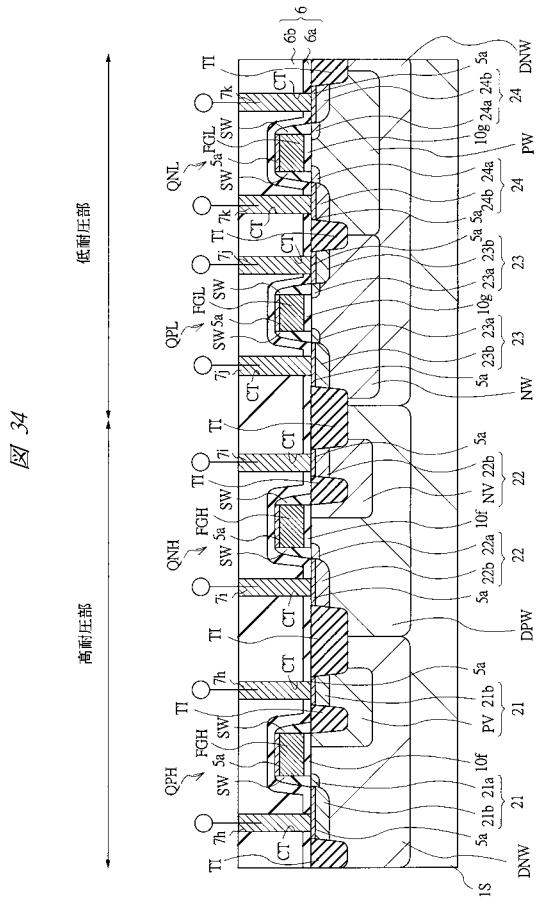

【図 34】本発明の他の実施の形態である半導体装置の主回路形成領域の半導体基板の断面図である。

【図 35】図 34 と同じ半導体装置の不揮発性メモリ領域の半導体基板の断面図である。 50

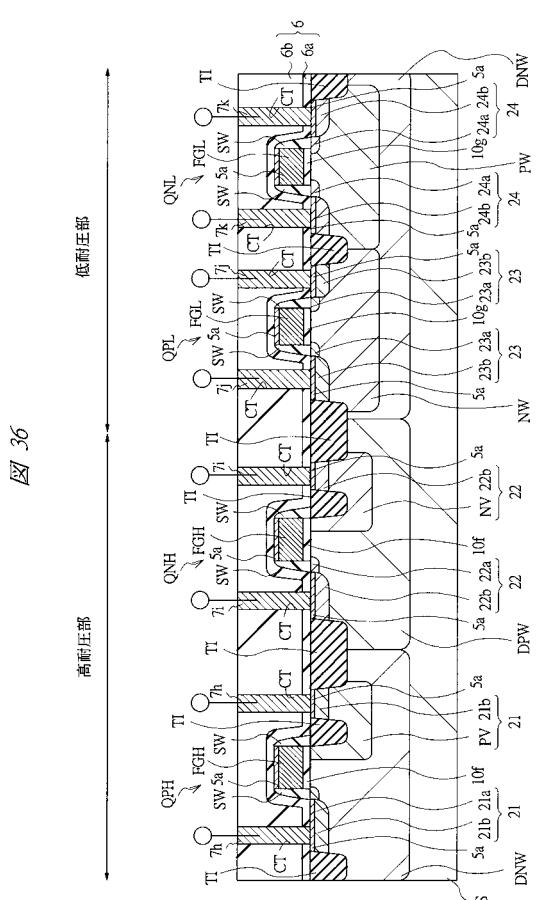

【図36】本発明の他の実施の形態である半導体装置の主回路形成領域の半導体基板の断面図である。

【図37】図36と同じ半導体装置の不揮発性メモリ領域の半導体基板の断面図である。

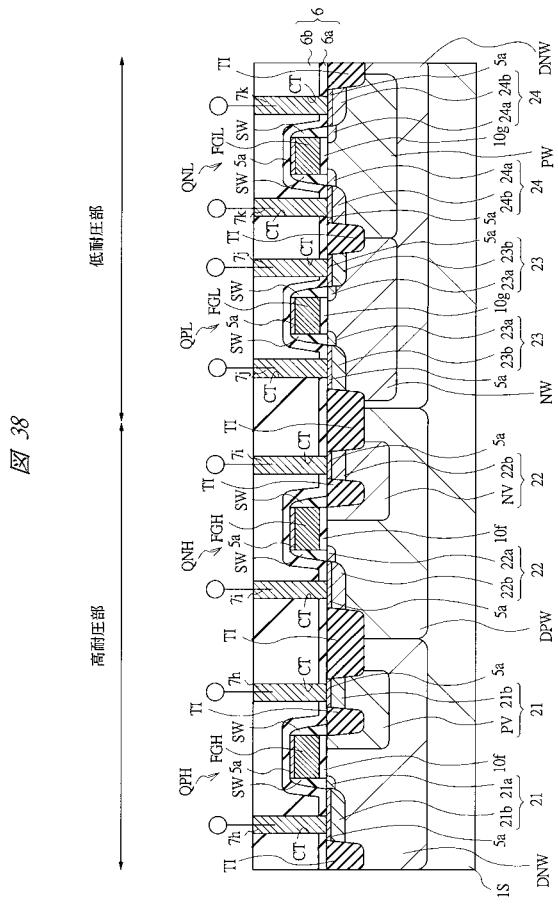

【図38】本発明の他の実施の形態である半導体装置の主回路形成領域の半導体基板の断面図である。

【図39】図38と同じ半導体装置の不揮発性メモリ領域の半導体基板の断面図である。

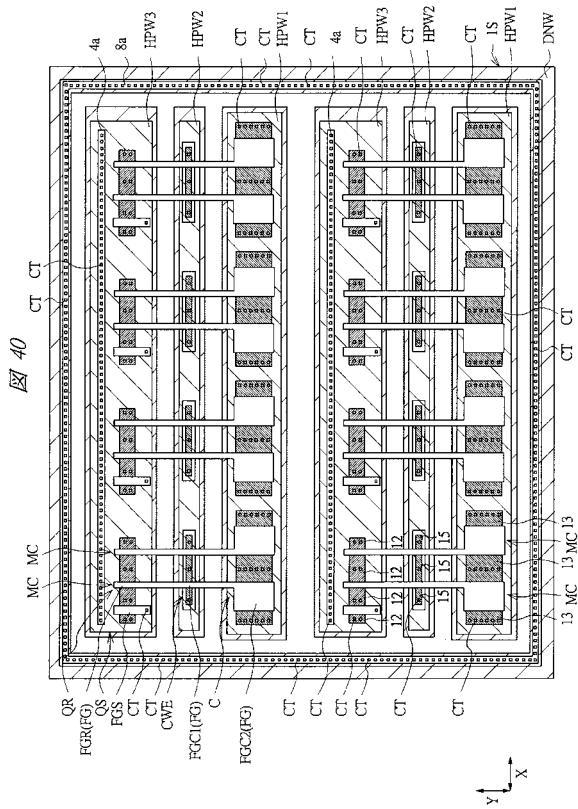

【図40】本発明のさらに他の実施の形態である半導体装置の不揮発性メモリ領域の平面図である。

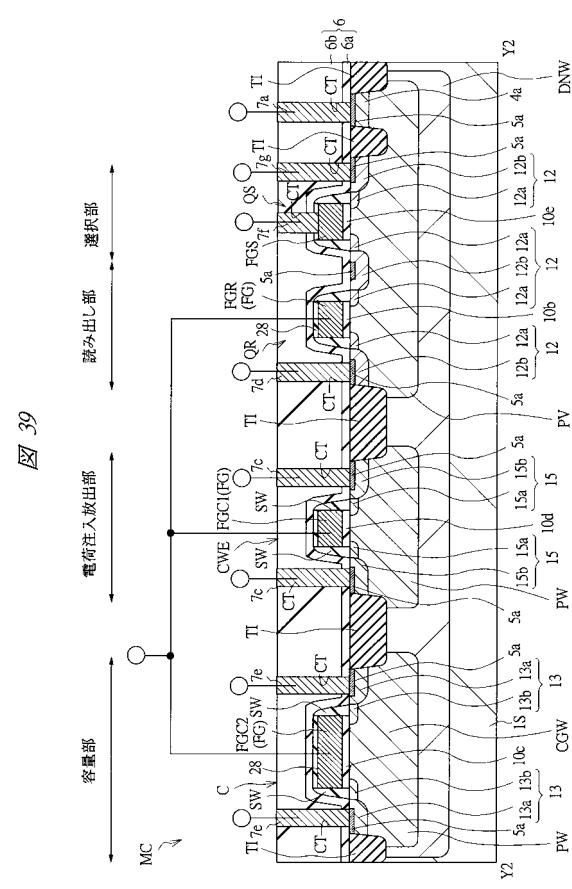

【図41】本発明の他の実施の形態である半導体装置におけるフラッシュメモリのメモリセルの一例の平面図である。 10

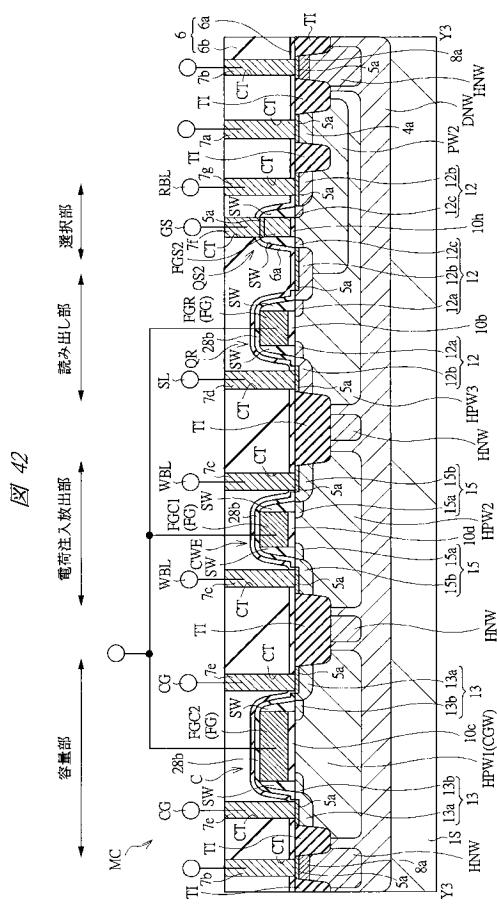

【図42】図41のY3-Y3線の断面図である。

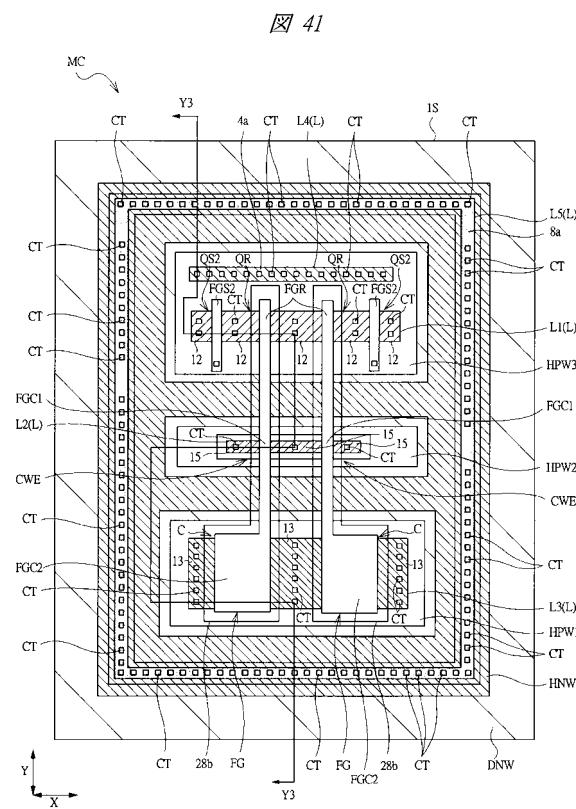

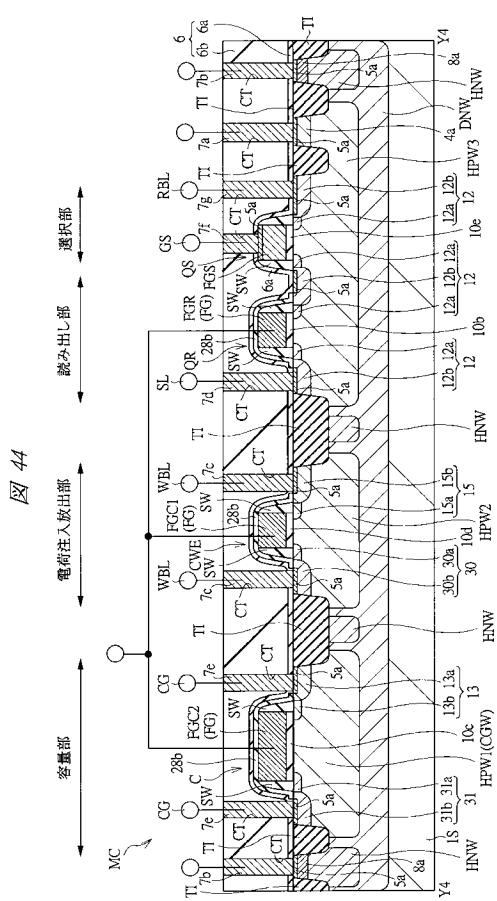

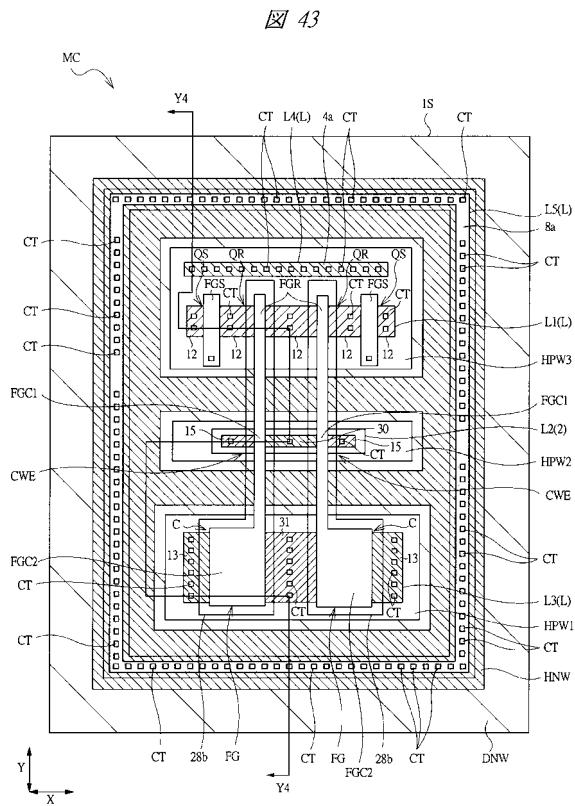

【図43】本発明の他の実施の形態である半導体装置におけるフラッシュメモリのメモリセルの一例の平面図である。

【図44】図43のY4-Y4線の断面図である。

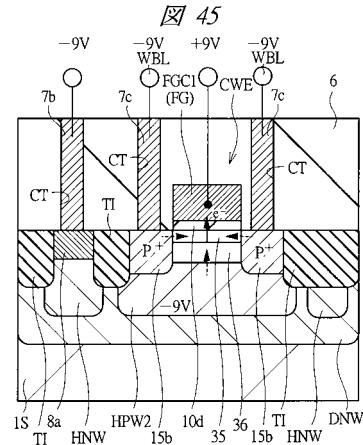

【図45】本発明の実施の形態である半導体装置のメモリセルの電荷注入放出部の半導体基板の断面図である。

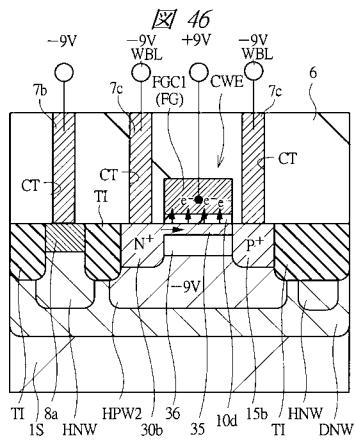

【図46】本発明の他の実施の形態である半導体装置のメモリセルの電荷注入放出部の半導体基板の断面図である。

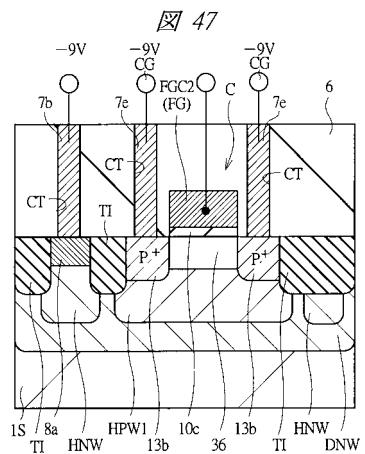

【図47】本発明の実施の形態である半導体装置のメモリセルの容量部の半導体基板の断面図である。 20

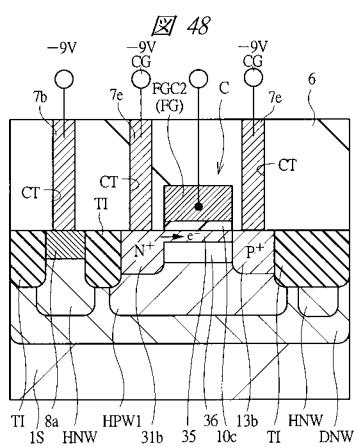

【図48】本発明の他の実施の形態である半導体装置のメモリセルの容量部の半導体基板の断面図である。

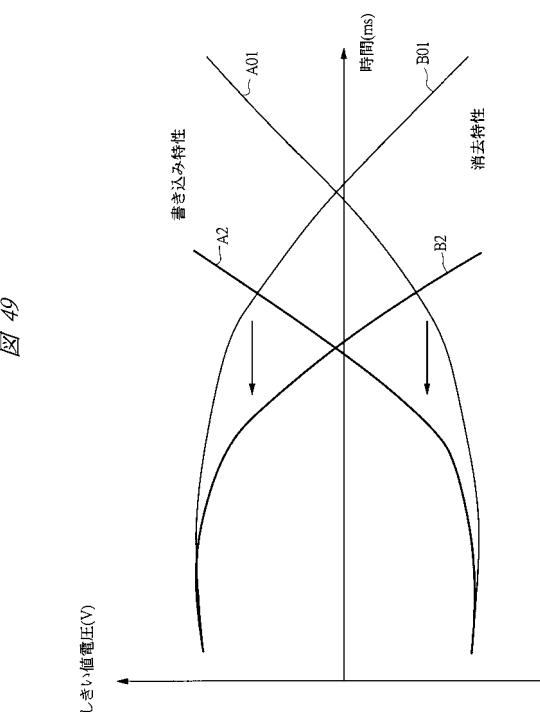

【図49】本発明の他の実施の形態である半導体装置のデータの書き込み・消去特性を比較して示したグラフ図である。

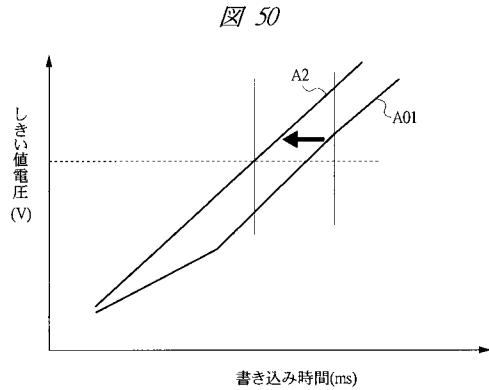

【図50】本発明の他の実施の形態である半導体装置のデータ書き込み特性を示すグラフ図である。

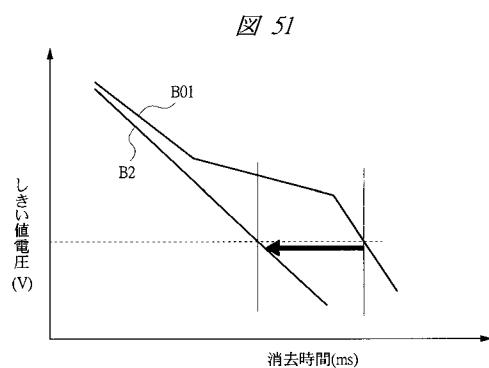

【図51】本発明の他の実施の形態である半導体装置のデータ消去特性を示すグラフ図である。

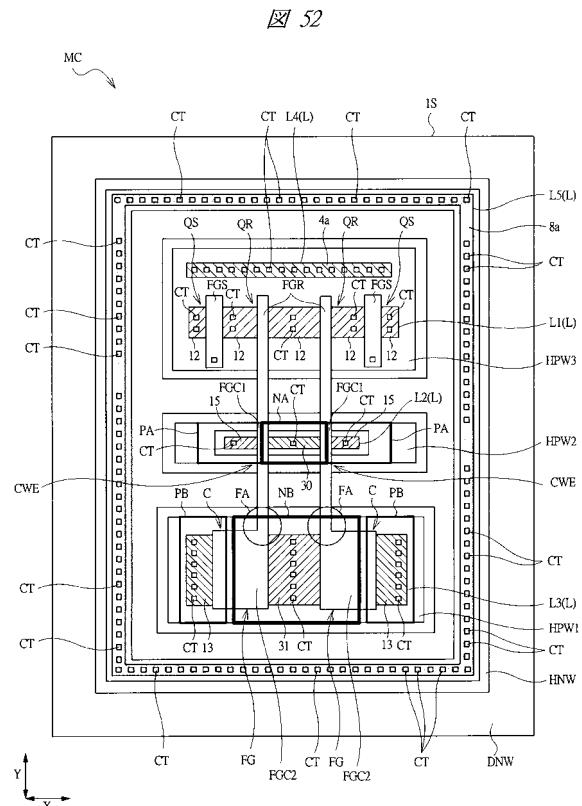

【図52】本発明の他の実施の形態である半導体装置の製造工程中の半導体基板の正面のメモリセル形成領域の平面図である。 30

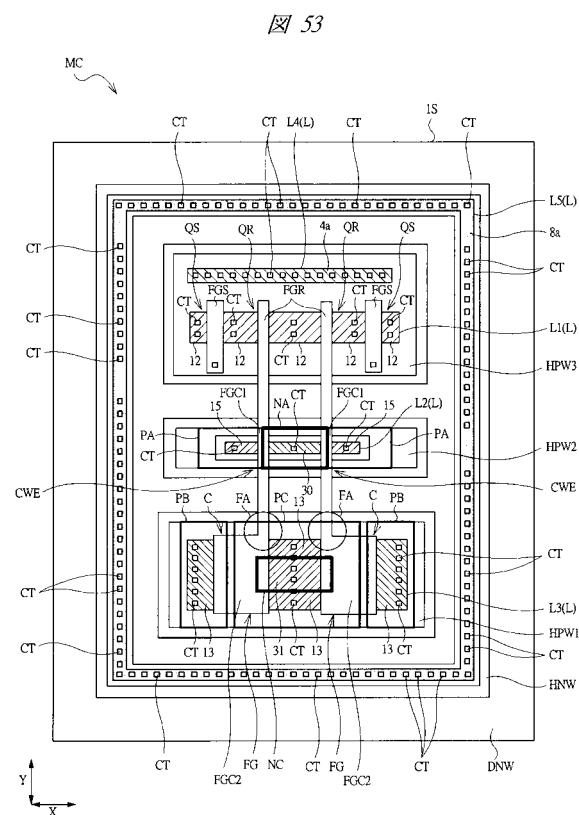

【図53】半導体装置の製造工程中の半導体基板の正面のメモリセル形成領域の平面図である。

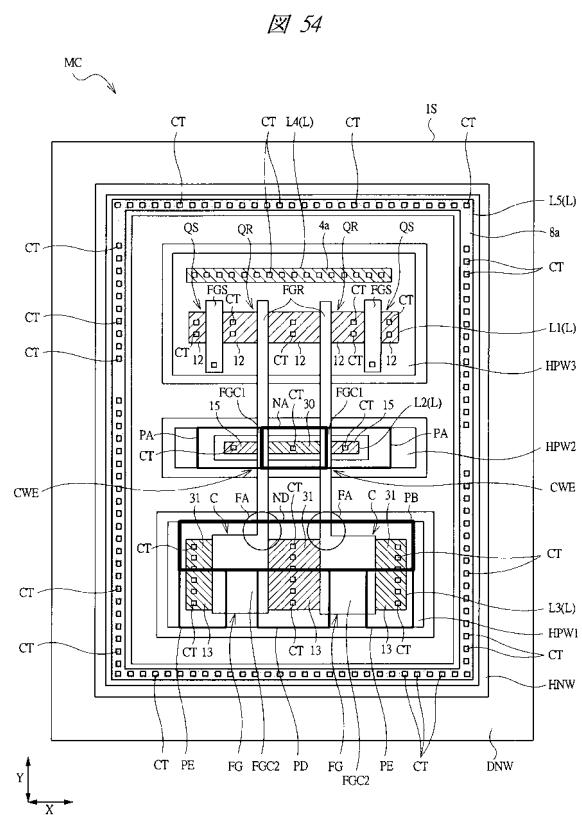

【図54】本発明の他の実施の形態である半導体装置の製造工程中の半導体基板の正面のメモリセル形成領域の平面図である。

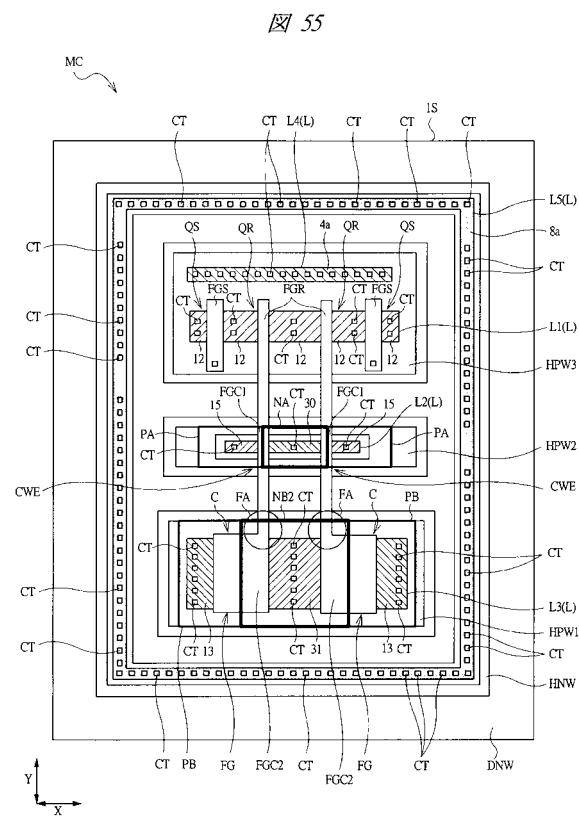

【図55】本発明の他の実施の形態である半導体装置のフラッシュメモリにおけるメモリセルにn型の半導体領域およびp型の半導体領域を形成する際のマスクを示したメモリセルの平面図である。

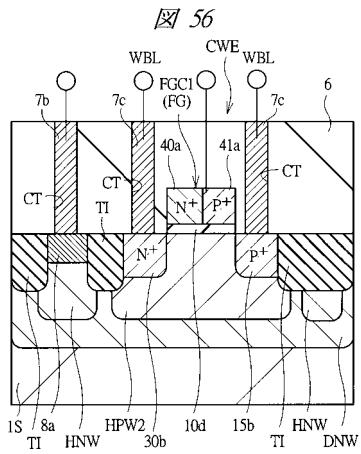

【図56】本発明の他の実施の形態である半導体装置のフラッシュメモリにおけるメモリセルの電荷注入放出部の半導体基板の第2方向Xに沿った要部断面図である。

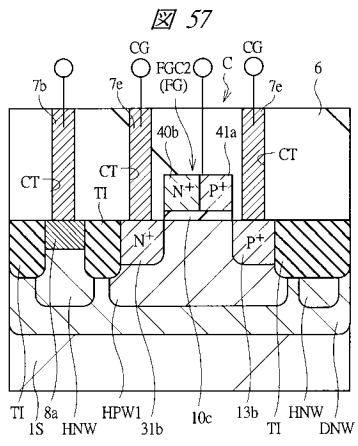

【図57】本発明の他の実施の形態である半導体装置のフラッシュメモリにおけるメモリセルの容量部の半導体基板の第2方向Xに沿った要部断面図である。 40

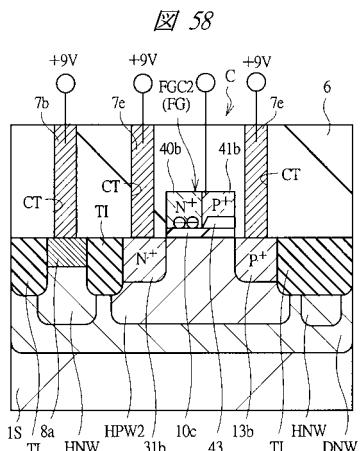

【図58】本発明の他の実施の形態である半導体装置のフラッシュメモリにおけるメモリセルのデータ書き込み時の容量部の半導体基板の第2方向Xに沿った要部断面図である。

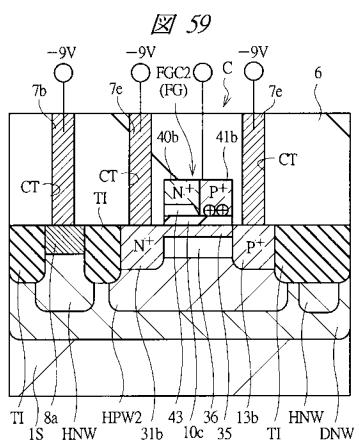

【図59】本発明の他の実施の形態である半導体装置のフラッシュメモリにおけるメモリセルのデータ消去時の容量部の半導体基板の第2方向Xに沿った要部断面図である。

【発明を実施するための形態】

【0015】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。ま 50

た、以下の実施の形態において、要素の数等（個数、数値、量、範囲等を含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。さらに、以下の実施の形態において、その構成要素（要素ステップ等も含む）は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。また、本実施の形態を説明するための全図において同一機能を有するものは同一の符号を付すようにし、その繰り返しの説明は可能な限り省略するようにしている。以下、本発明の実施の形態を図面に基づいて詳細に説明する。

#### 【0016】

##### （実施の形態1）

まず、本発明者が検討したフラッシュメモリの構成およびそのフラッシュメモリにおけるデータ書き込み時の問題について説明する。図1は本発明者が検討したフラッシュメモリのメモリセルMCの平面図、図2および図3は図1のY1-Y1線の断面図であってチャネル全面のFNトンネル電流によりデータ書き込みを行う場合のそれぞれ異なる例を示したものである。なお、符号のYは第1方向でローカルデータ線の延在方向、符号のXは第1方向に直交する第2方向でワード線の延在方向を示している。

#### 【0017】

半導体チップを構成する半導体基板（以下、単に基板という）1Sは、例えばp型（第2導電型）のシリコン（Si）単結晶により形成されている。この基板1Sの主面には分離部TIが配置されている。この分離部TIは、活性領域L（L1, L2, L3, L4, L5）を規定する部分である。ここでは分離部TIが、例えば基板1Sの主面に掘られた浅溝内に酸化シリコン等からなる絶縁膜を埋め込むことで形成された、いわゆるSGI（Shallow Groove Isolation）またはSTI（Shallow Trench Isolation）と称する溝形の分離部とされている。

#### 【0018】

上記基板1Sには、その主面から所望の深さに渡ってn型（第1導電型）の埋込ウエルDNWが形成されている。この埋込ウエルDNWには、p型のウエルHPWa, HPWbおよびn型のウエルHNWが形成されている。p型のウエルHPWa, HPWbは、n型のウエルHNWにより互いに電気的に分離された状態で埋込ウエルDNWに内包されている。

#### 【0019】

このp型のウエルHPWa, HPWbには、例えばホウ素等のようなp型を示す不純物が含有されている。このp型のウエルHPWaの上層一部には、p<sup>+</sup>型の半導体領域4aが形成されている。p<sup>+</sup>型の半導体領域4aには、p型のウエルHPWaと同じ不純物が含有されているが、p<sup>+</sup>型の半導体領域4aの不純物濃度の方が、p型のウエルHPWaの不純物濃度よりも高くなるように設定されている。このp<sup>+</sup>型の半導体領域4aの表層一部には、例えばコバルトシリサイド（CoSi<sub>x</sub>）等のようなシリサイド層5aが形成されている。このp<sup>+</sup>型の半導体領域4aは、シリサイド層5aを介して、基板1Sの主面上の絶縁層6に形成されたコンタクトホールCT内の導体部7aに電気的に接続されている。絶縁層6は、絶縁層6aとその上に堆積された絶縁層6bとを有している。下層の絶縁層6aは、例えば窒化シリコン（Si<sub>3</sub>N<sub>4</sub>）からなり、上層の絶縁層6bは、例えば酸化シリコン（SiO<sub>2</sub>）からなる。

#### 【0020】

また、上記n型のウエルHNWには、例えばリン（P）またはヒ素（As）等のようなn型を示す不純物が含有されており、その不純物濃度は、上記の埋込ウエルDNWよりも高い濃度で形成されている。このn型のウエルHNWの上層一部には、n<sup>+</sup>型の半導体領

10

20

30

40

50

域 8 a が形成されている。n<sup>+</sup>型の半導体領域 8 a には、n 型のウエル H N W と同じ不純物が含有されているが、n<sup>+</sup>型の半導体領域 8 a の不純物濃度の方が、n 型のウエル H N W の不純物濃度よりも高くなるように設定されている。この n<sup>+</sup>型の半導体領域 8 a は、その表層一部に形成されたシリサイド層 5 a を介して、上記絶縁層 6 に形成されたコンタクトホール C T 内の導体部 7 b に電気的に接続されている。

#### 【 0 0 2 1 】

上記フラッシュメモリのメモリセル M C は、浮遊ゲート電極 F G と、データ書き込み・消去用の M I S · F E T (Metal Insulator Semiconductor Field Effect Transistor) Q W と、データ読み出し用の M I S · F E T Q R と、容量部 C とを有している。

#### 【 0 0 2 2 】

浮遊ゲート電極 F G は、情報の記憶に寄与する電荷を蓄積する部分である。この浮遊ゲート電極 F G は、例えば低抵抗な多結晶シリコン等のような導電体膜からなり、電気的に浮遊状態（他の導体と絶縁された状態）で形成されている。また、この浮遊ゲート電極 F G は、図 1 に示すように、互いに隣接する上記 p 型のウエル H P W a , H P W b の両方に平面的に重なるように第 1 方向 Y に沿って延在した状態で形成されている。

#### 【 0 0 2 3 】

この浮遊ゲート電極 F G が p 型のウエル H P W a の活性領域 L 1 に平面的に重なる位置には、上記データ書き込み・消去用の M I S · F E T Q W が配置されている。データ書き込み・消去用の M I S · F E T Q W は、ゲート電極 F G W と、ゲート絶縁膜 1 0 a と、一对のソース用の n 型の半導体領域 1 1 S W およびドレイン用の n 型の半導体領域 1 1 D W とを有している。データ書き込み・消去用の M I S · F E T Q W のチャネルは、上記ゲート電極 F G W と活性領域 L 1 とが平面的に重なる上記 p 型のウエル H P W a の上層に形成される。

#### 【 0 0 2 4 】

ゲート電極 F G W は、上記浮遊ゲート電極 F G の一部により形成されている。上記ゲート絶縁膜 1 0 a は、例えば酸化シリコンからなり、ゲート電極 F G W と基板 1 S (p 型のウエル H P W a )との間に形成されている。ゲート絶縁膜 1 0 a の厚さは、例えば 1 3 . 5 nm 程度である。上記ソース用の半導体領域 1 1 S W およびドレイン用の半導体領域 1 1 D W は、p 型のウエル H P W a 内においてゲート電極 F G W を挟み込む位置にゲート電極 F G W に対して自己整合的に形成されている。この半導体領域 1 1 S W , 1 1 D W は、それぞれチャネル側の n<sup>-</sup>型の半導体領域と、その各々に接続された n<sup>+</sup>型の半導体領域とを有している。この n<sup>-</sup>型の半導体領域および n<sup>+</sup>型の半導体領域には、例えばリンまたはヒ素 (A s) 等のような同一導電型の不純物が含有されているが、n<sup>+</sup>型の半導体領域の不純物濃度の方が、n<sup>-</sup>型の半導体領域の不純物濃度よりも高くなるように設定されている。このような半導体領域 1 1 S W , 1 1 D W は、その表層一部に形成されたシリサイド層 5 a を介して、上記絶縁層 6 に形成されたコンタクトホール C T 内の導体部 7 c に電気的に接続されている。

#### 【 0 0 2 5 】

また、上記浮遊ゲート電極 F G が p 型のウエル H P W a の活性領域 L 2 に平面的に重なる位置には、上記データ読み出し用の M I S · F E T Q R が配置されている。データ読み出し用の M I S · F E T Q R は、ゲート電極 F G R と、ゲート絶縁膜 1 0 b と、一对の n 型の半導体領域 1 2 R , 1 2 R とを有している。データ読み出し用の M I S · F E T Q R のチャネルは、上記ゲート電極 F G R と活性領域 L 2 とが平面的に重なる上記 p 型のウエル H P W a の上層に形成される。

#### 【 0 0 2 6 】

ゲート電極 F G R は、上記浮遊ゲート電極 F G の一部により形成されている。上記ゲート絶縁膜 1 0 b は、例えば酸化シリコンからなり、ゲート電極 F G R と基板 1 S (p 型のウエル H P W )との間に形成されている。ゲート絶縁膜 1 0 b の厚さは、例えば 1 3 . 5 nm 程度である。上記一对の n 型の半導体領域 1 2 R , 1 2 R は、p 型のウエル H P W a 内においてゲート電極 F G R を挟み込む位置にゲート電極 F G R に対して自己整合的に形

10

20

30

40

50

成されている。一対の n 型の半導体領域 1 2 R , 1 2 R は、それぞれチャネル側の n - 型の半導体領域と、その各々に接続された n + 型の半導体領域とを有している。この n - 型の半導体領域および n + 型の半導体領域には、例えばリン ( P ) またはヒ素 ( As ) 等のような同一導電型の不純物が含有されているが、 n + 型の半導体領域の不純物濃度の方が、 n - 型の半導体領域の不純物濃度よりも高くなるように設定されている。このような半導体領域 1 2 R , 1 2 R は、その表層一部に形成されたシリサイド層 5 a を介して、上記絶縁層 6 に形成されたコンタクトホール C T 内の導体部 7 d に電気的に接続されている。

#### 【 0 0 2 7 】

また、上記浮遊ゲート電極 F G が上記 p 型のウエル H P W b に平面的に重なる位置には、上記容量部 C が形成されている。この容量部 C は、制御ゲート電極 C G W と、容量電極 F G C と、容量絶縁膜 1 0 c と、 p + 型の半導体領域 1 3 a とを有している。10

#### 【 0 0 2 8 】

制御ゲート電極 C G W は、浮遊ゲート電極 F G が対向する p 型のウエル H P W b 部分により形成されている。一方、容量電極 F G C は、上記制御ゲート電極 C G W に対向する浮遊ゲート電極 F G 部分により形成されている。このようにメモリセル M C のゲート構成を単層構成とすることにより、フラッシュメモリのメモリセル M C と主回路の素子との製造上の整合を容易にすることができるので、半導体装置の製造時間の短縮や製造コストの低減を図ることができる。

#### 【 0 0 2 9 】

また、容量電極 F G C の第 2 方向 X の長さは、上記データ書き込み・消去用の M I S · F E T Q W や上記データ読み出し用の M I S · F E T Q R のゲート電極 F G W , F G R の第 2 方向 X の長さよりも長くなるように形成されている。これにより、容量電極 F G C の平面積を大きく確保できるので、カップリング比を高めることができ、制御ゲート配線 C G W からの電圧供給効率を向上させることができることが可能となっている。20

#### 【 0 0 3 0 】

上記容量絶縁膜 1 0 c は、例えば酸化シリコンからなり、上記制御ゲート電極 C G W と容量電極 F G C との間に形成されている。この容量絶縁膜 1 0 c は、上記ゲート絶縁膜 1 0 a , 1 0 b を形成するための熱酸化工程により同時に形成されており、その厚さは、例えば 1 3 . 5 nm 程度である。また、上記ゲート絶縁膜 1 0 a , 1 0 b および容量絶縁膜 1 0 c は、主回路における相対的に厚いゲート絶縁膜を持つ高耐圧 M I S F E T と相対的に薄いゲート絶縁膜を持つ低耐圧 M I S F E T のうち、高耐圧 M I S F E T のゲート絶縁膜と同工程により形成されている。これにより、フラッシュメモリの信頼性を向上させることができる。30

#### 【 0 0 3 1 】

上記 p + 型の半導体領域 1 3 a は、 p 型のウエル H P W b 内において容量電極 F G C を挟み込む位置に容量電極 F G C に対して自己整合的に形成されている。この半導体領域 1 3 a には、例えばホウ素 ( B ) 等のような上記 p 型のウエル H P W b と同一導電型の不純物が含有されているが、 p + 型の半導体領域 1 3 a の不純物濃度の方が、 p 型のウエル H P W b の不純物濃度よりも高くなるように設定されている。この半導体領域 1 3 a は、その表層一部に形成されたシリサイド層 5 a を介して、上記絶縁層 6 に形成されたコンタクトホール C T 内の導体部 7 e に電気的に接続されている。40

#### 【 0 0 3 2 】

ところで、このような構成のフラッシュメモリの書き込み・消去用の M I S · F E T Q W において、チャネル全面の F N トンネル電流により、データを書き込む際には、図 2 および図 3 に示すように、書き込み・消去用の M I S · F E T Q W のソースおよびドレイン用の n 型の半導体領域 1 1 S W , 1 1 D W を、例えばオープン ( O P E N ) に設定するか、または 9 V に設定する。しかし、オープンにする場合 ( 図 2 ) は、ソースおよびドレイン用の n 型の半導体領域 1 1 S W , 1 1 D W の両側にカットオフするためのトランジスタが必要となり半導体装置の小型化を阻害する問題があることを見出した。一方、 n 型の半導体領域 1 1 S W , 1 1 D W に 9 V を印加する場合は ( 図 3 ) 、ソースおよびドレイン用50

の n 型の半導体領域 11 SW, 11 DW の接合耐圧が 9 V より低いと、接合耐圧が持たずブレークダウンし書き込み・消去用の MIS · FET QW が劣化する問題が生じる。また、データ書き換え領域とデータ読み出し領域とが同一のウエル内に形成されていること等により、データ書き換えが不安定になりデータを上手く書き込むことができない問題が生じることを見出した。

#### 【0033】

そこで、上記構成のフラッシュメモリでは、ソースおよびドレイン用の n 型の半導体領域 11 SW, 11 DW に耐圧以上の電圧がかからないようにタイミング設計が必要となる。図 4 ~ 図 6 はフラッシュメモリのデータ消去動作時における電圧印加のタイミングを示す説明図を示している。まず、図 4 に示すように、p 型のウエル HP Wa に 9 V の電圧が印加されるのに先立ってデータ書き込み・消去用の MIS · FET QW のドレインに 9 V の電圧を印加する。また、データ書き込み・消去用の MIS · FET QW のドレイン電圧を 0 V に戻すのに先立って p 型のウエル HP Wa の電圧を 0 V に戻すと、双方の電位差 V<sub>1</sub> が上記接合耐圧を超えてしまい接合破壊を引き起こしてしまう。そこで、データ消去動作時においては、図 5 および図 6 に示すようなタイミングで p 型のウエル HP Wa およびデータ書き込み・消去用の MIS · FET QW のドレイン (n 型半導体領域 11 DW) に電圧を印加し、双方の電位差 V<sub>1</sub> が約 7 V 以上とならないようにする。

10

#### 【0034】

例えは図 5 に示すように、p 型のウエル HP Wa の電圧を立ち上げるのに先立って MIS · FET QW のドレインの電圧を立ち上げる。この時、双方の電圧は、急峻に立ち上げずに緩やかに上昇させ、双方の電位差 V<sub>1</sub> が上記接合耐圧を超えないようにする。また、MIS · FET QW のドレイン電圧を 0 V に戻すのに先立って p 型のウエル HP Wa の電圧を 0 V に戻し、この時の双方の電圧変化も急峻とならないようにすることにより、双方の電位差 V<sub>1</sub> が上記接合耐圧を超えないようにする。

20

#### 【0035】

また、例えは図 6 に示すように、p 型のウエル HP Wa の電圧を立ち上げるのに先立って MIS · FET QW のドレインの電圧を立ち上げ、9 V まで上昇させる前に 4 V もしくは 5 V とし、その間に p 型のウエル HP Wa の電圧を立ち上げても良い。この時、p 型のウエル HP Wa の電圧は、タイミングが異なるだけで MIS · FET QW のドレインの電圧と同様に変化させる。それにより、双方の電位差 V<sub>1</sub> が上記接合耐圧を超えないようにすることができます。また、MIS · FET QW のドレイン電圧および p 型のウエル HP Wa の電圧を 0 V に戻す際には、MIS · FET QW のドレイン電圧を低下させるのに先立って p 型のウエル HP Wa の電圧を低下させ、その際の電圧変化は、電圧を上昇させる際の変化過程を逆に経るようにすれば良い。

30

#### 【0036】

このように上記構成のフラッシュメモリの書き込み・消去用の MIS · FET QW においてチャネル全面の FN トンネル電流によりデータの書き換えを行うべく、そのソースおよびドレイン用の n 型の半導体領域 11 SW, 11 DW に 9 V を印加する場合、上記のようなタイミング設計が必要となる。しかし、上記のようなタイミング設計を実現するためには、同一の基板 1 S 上に形成する周辺回路の規模が大きくなり、半導体装置の小型化を阻害する問題があることを見出した。

40

#### 【0037】

次に、本実施の形態 1 の半導体装置について説明する。

#### 【0038】

本実施の形態 1 の半導体装置は、同一の半導体チップに、主回路と、その主回路に関する比較的小容量の所望の情報を記憶するフラッシュメモリ (不揮発性メモリ) とが形成されているものである。上記主回路には、例えは DRAM (Dynamic Random Access Memory) 、や SRAM (Static RAM) 等のようなメモリ回路、CPU (Central Processing Unit) や MPU (Micro Processing Unit) 等のような論理回路、これらメモリ回路および論理回路の混在回路あるいは LCD (Liquid Crystal Device) ドライバ回路等がある。

50

また、上記所望の情報には、例えば半導体チップ内のトリミングの際に使用する有効（使用）素子の配置アドレス情報、メモリやLCDの救済の際に使用する有効メモリセル（不良のないメモリセル）や有効LCD素子の配置アドレス情報、LCD画像調整時に使用する調整電圧のトリミングタップ情報あるいは半導体装置の製造番号等がある。この半導体装置（半導体チップ、半導体基板）の外部から供給される外部電源は、単一電源とされている。単一電源の電源電圧は、例えば3.3V程度である。

#### 【0039】

図7は本実施の形態1の半導体装置におけるフラッシュメモリの要部回路図を示している。このフラッシュメモリは、メモリセルアレイMRと周辺回路領域PRとを有している。メモリセルアレイMRには、第1方向Yに延在する複数のデータ書き込み・消去用のビット線WBL（WBL0, WBL1…）と、データ読み出し用のビット線RBL（RBL0, RBL2…）とが第2方向Xに沿って配置されている。また、メモリセルアレイMRには、上記ビット線WBL, RBLに対して直交する第2方向Xに沿って延在する複数の制御ゲート配線（ワード線）CG（CG0, CG1…）と、複数のソース線SLと、複数の選択線GSとが第1方向Yに沿って配置されている。

10

#### 【0040】

各データ書き込み・消去用のビット線WBLは、上記周辺回路領域PRに配置されたデータ（0/1）入力用のインバータ回路INVに電気的に接続されている。また、各データ読み出し用のビット線RBLは、上記周辺回路領域PRに配置されたセンスアンプ回路SAに電気的に接続されている。センスアンプ回路SAは、例えばカレントミラー形とされている。そして、このようなビット線WBL, RBLと、制御ゲート配線CG、ソース線SLおよび選択線GSとの格子状交点の近傍に、1ビット分のメモリセルMCが電気的に接続されている。ここでは、1ビットが2つのメモリセルMCで構成されている場合が例示されている。

20

#### 【0041】

各メモリセルMCは、データ書き込み・消去用の容量部（電荷注入放出部）CWEと、データ読み出し用のMIS·FETQRと、容量部Cと、選択MIS·FETQSとを有している。各ビットの2つのメモリセルMCの各々のデータ書き込み・消去用の容量部CWE, CWEは、互いに並列になるように電気的に接続されている。その各々のデータ書き込み・消去用の容量部CWEの一方の電極は、データ書き込み・消去用のビット線WBLに電気的に接続されている。また、その各々のデータ書き込み・消去用の容量部CWEの他方の電極（浮遊ゲート電極FG）は、それぞれ別々のデータ読み出し用のMIS·FETQR, QRのゲート電極（浮遊ゲート電極FG）に電気的に接続されるとともに、容量部C, Cの一方の電極（浮遊ゲート電極FG）に電気的に接続されている。そして、その容量部C, Cは他方の電極（制御ゲート電極CGW）は制御ゲート配線CGに電気的に接続されている。一方、各ビットの2つのメモリセルMCのデータ読み出し用のMIS·FETQR, QRは、互いに直列に電気的に接続されており、そのドレインは、選択MIS·FETQSを介してデータ読み出し用のビット線RBLに電気的に接続され、ソースはソース線SLに電気的に接続されている。選択MIS·FETQSのゲート電極は、選択線GSに電気的に接続されている。

30

#### 【0042】

次に、このようなフラッシュメモリにおけるデータ書き込み動作例を図8～図11により説明する。図8は図7のフラッシュメモリのデータ書き込み動作時における各部への印加電圧を示している。破線S1はデータ書き込み対象のメモリセルMC（以下、選択メモリセルMCsという）を示している。なお、ここでは、電子を浮遊ゲート電極に注入することをデータ書き込みと定義するが、その逆に浮遊ゲート電極の電子を抜き取ることをデータ書き込みと定義することもできる。

40

#### 【0043】

データの書き込み時には、上記選択メモリセルMCsの上記容量部Cの他方の電極が接続されている制御ゲート配線CG0（CG）に、例えば9V程度の正の制御電圧を印加す

50

る。それ以外の制御ゲート配線 C G 1 ( C G ) には、例えば 0 V の電圧を印加する。また、選択メモリセル M C s の上記データ書き込み・消去用の容量部 C W E の一方の電極が電気的に接続されているデータ書き込み・消去用のビット線 W B L 0 ( W B L ) に、例えば - 9 V 程度の負の電圧を印加する。それ以外のデータ書き込み・消去用のビット線 W B L 1 ( W B L ) には、例えば 0 V の電圧を印加する。また、選択線 G S 、ソース線 S L およびデータ書き込み用のビット線 R B L に、例えば 0 V を印加する。これにより、選択メモリセル M C s のデータ書き込み・消去用の容量部 C W E , C W E の浮遊ゲート電極にチャネル全面の F N トンネル電流により電子を注入し、データを書き込む。

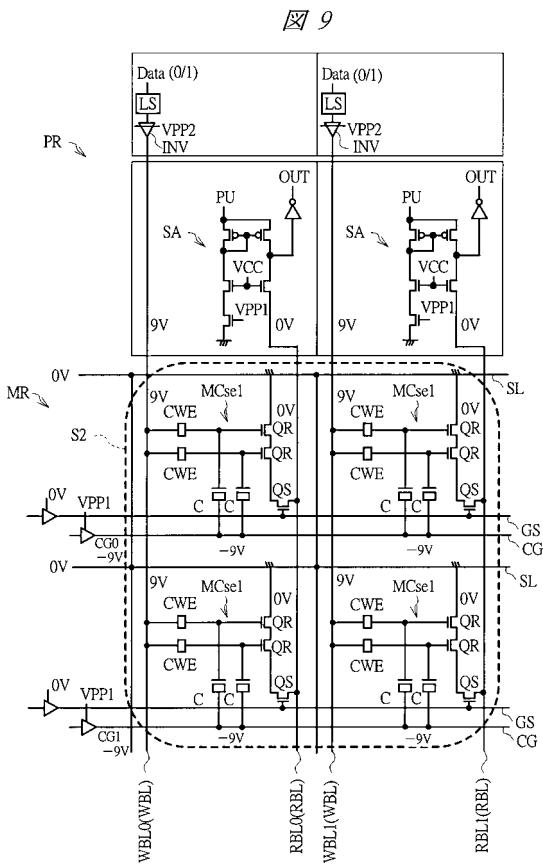

#### 【 0 0 4 4 】

次に、図 9 は図 7 のフラッシュメモリのデータ一括消去動作時における各部への印加電圧を示している。破線 S 2 はデータ一括消去対象の複数のメモリセル M C ( 以下、選択メモリセル M C s e 1 という ) を示している。なお、ここでは、浮遊ゲート電極の電子を引き抜くことをデータ消去と定義するが、その逆に浮遊ゲート電極に電子を注入することをデータ消去と定義することもできる。

#### 【 0 0 4 5 】

データ一括消去時には、上記複数の選択メモリセル M C s e 1 の上記容量部 C の他方の電極が接続されている制御ゲート配線 C G 0 , C G 1 ( C G ) に、例えば - 9 V 程度の負の制御電圧を印加する。また、選択メモリセル M C s e 1 の上記データ書き込み・消去用の容量部 C W E の一方の電極が電気的に接続されているデータ書き込み・消去用のビット線 W B L 0 , W B L 1 ( W B L ) に、例えば 9 V 程度の負の電圧を印加する。また、選択線 G S 、ソース線 S L およびデータ書き込み用のビット線 R B L に、例えば 0 V を印加する。これにより、データ一括消去を行う複数の選択メモリセル M C s e 1 のデータ書き込み・消去用の容量部 C W E , C W E の浮遊ゲート電極に蓄積された電子をチャネル全面の F N トンネル電流により放出し、複数の選択メモリセル M C s e 1 のデータを一括消去する。

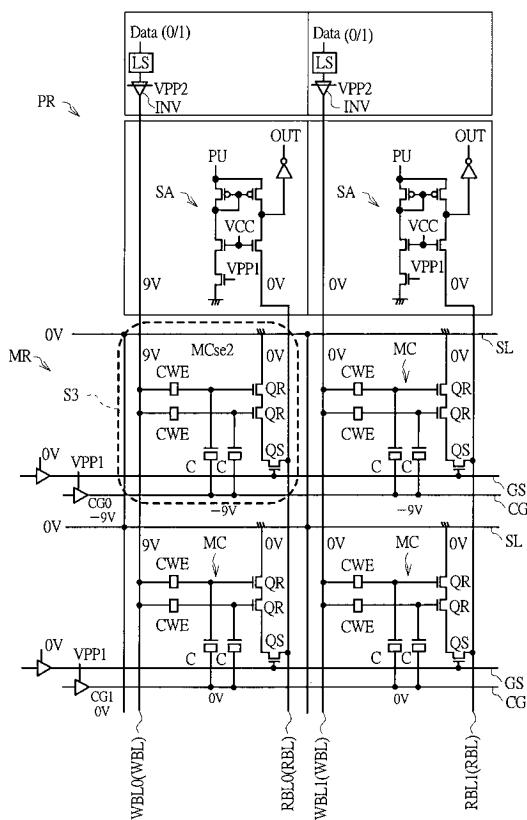

#### 【 0 0 4 6 】

次に、図 10 は図 7 のフラッシュメモリのデータ・ビット単位消去動作時における各部への印加電圧を示している。破線 S 3 はデータ一括消去対象のメモリセル M C ( 以下、選択メモリセル M C s e 2 という ) を示している。

#### 【 0 0 4 7 】

データ・ビット単位消去時には、上記選択メモリセル M C s e 2 の上記容量部 C の他方の電極が接続されている制御ゲート配線 C G 0 ( C G ) に、例えば - 9 V 程度の負の制御電圧を印加する。それ以外の制御ゲート配線 C G 1 ( C G ) には、例えば 0 V の電圧を印加する。また、選択メモリセル M C s e 2 の上記データ書き込み・消去用の容量部 C W E の一方の電極が電気的に接続されているデータ書き込み・消去用のビット線 W B L 0 ( W B L ) に、例えば 9 V 程度の正の電圧を印加する。それ以外のデータ書き込み・消去用のビット線 W B L 1 ( W B L ) には、例えば 0 V の電圧を印加する。また、選択線 G S 、ソース線 S L およびデータ書き込み用のビット線 R B L に、例えば 0 V を印加する。これにより、データ消去対象の選択メモリセル M C s e 2 のデータ書き込み・消去用の容量部 C W E , C W E の浮遊ゲート電極に蓄積された電子をチャネル全面の F N トンネル電流により放出し、データ消去対象の選択メモリセル M C s e 2 のデータを消去する。

#### 【 0 0 4 8 】

次に、図 11 は図 7 のフラッシュメモリのデータ読み出し動作時における各部への印加電圧を示している。破線 S 4 はデータ読み出し対象のメモリセル M C ( 以下、選択メモリセル M C r という ) を示している。

#### 【 0 0 4 9 】

データ読み出し時には、上記選択メモリセル M C r の上記容量部 C の他方の電極が接続されている制御ゲート配線 C G 0 ( C G ) に、例えば 3 V 程度の制御電圧を印加する。それ以外の制御ゲート配線 C G 1 ( C G ) には、例えば 0 V の電圧を印加する。また、選択メモリセル M C r の上記データ書き込み・消去用の容量部 C W E の一方の電極が電気的に

10

20

30

40

50

接続されているデータ書き込み・消去用のビット線W B L 0 , W B L 0 ( W B L )に、例えば0 V程度の電圧を印加する。また、上記選択メモリセルM C rの上記選択M I S · F E T Q Sのゲート電極が電気的に接続されている選択線G Sに、例えば3 V程度の電圧を印加する。そして、データ書き込み用のビット線R B Lに、例えば1 V程度の電圧を印加する。さらに、ソース線S Lに、例えば0 Vを印加する。これにより、データ読み出し対象の選択メモリセルM C rのデータ読み出し用のM I S · F E T Q Rをオン条件とし、そのデータ読み出し用のM I S · F E T Q Rのチャネルにドレイン電流が流れるか否かにより、選択メモリセルM C rに記憶されているデータが0 / 1のいずれなのかを読み出す。

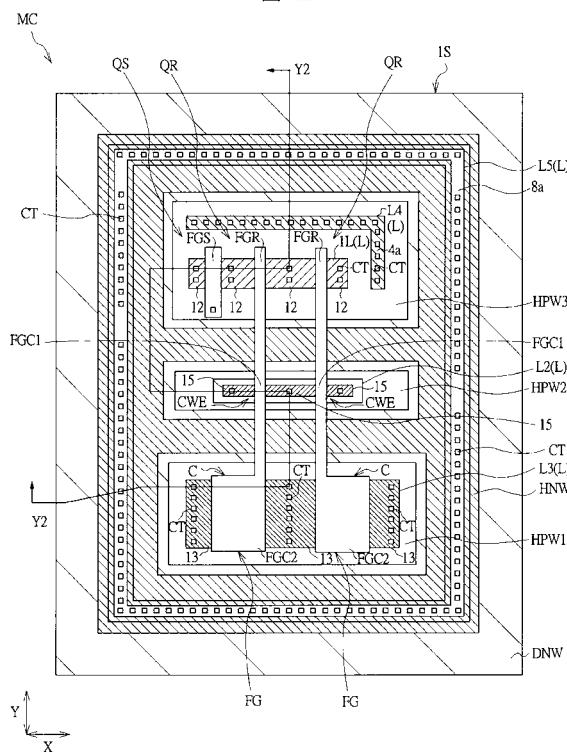

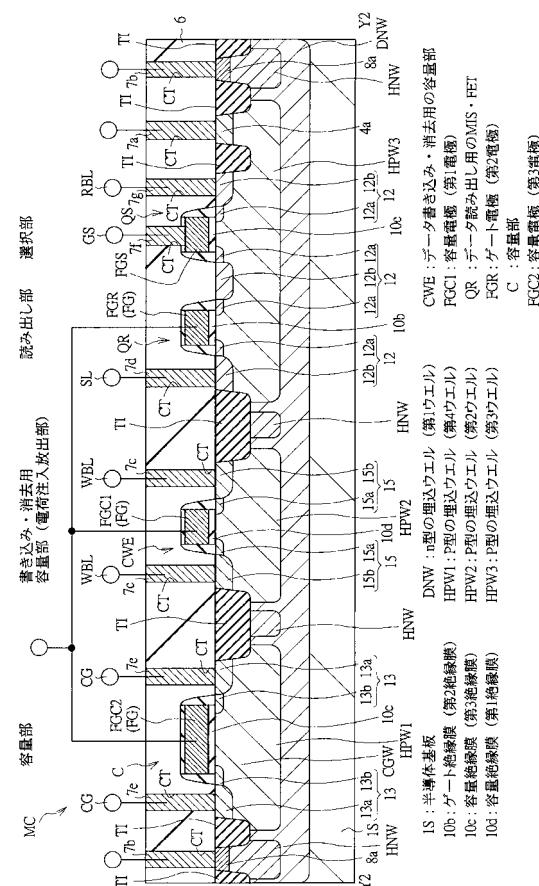

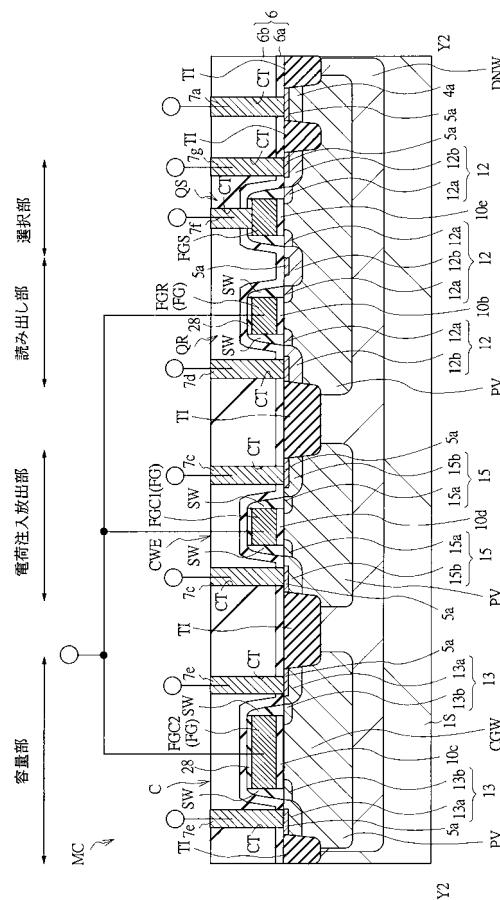

#### 【0050】

次に、図12は本実施の形態1の半導体装置におけるフラッシュメモリの1ビット分のメモリセルM Cの平面図、図13は図12のY 2 - Y 2線の断面図である。なお、図12では図面を見易くするために一部にハッチングを付した。 10

#### 【0051】

p型の基板1 Sの主面には、活性領域L ( L 1 , L 2 , L 3 , L 4 , L 5 )を規定する上記溝形の分離部T Iが形成されている。この基板1 Sに形成されたn型(第1導電型)の埋込ウエル(第1ウエル)D N Wには、p型(第2導電型)のウエルH P W 1 , H P W 2 , H P W 3およびn型のウエルH N Wが形成されている。p型のウエルH P W 1 , H P W 2 , H P W 3は、埋込ウエルD N Wおよびn型のウエルH N Wにより互いに電気的に分離された状態で埋込ウエルD N Wに内包されている。

#### 【0052】

このp型のウエルH P W 1 ~ H P W 3には、例えばホウ素(B)等のようなp型を示す不純物が含有されている。p型のウエルH P W 3の上層一部には、p<sup>+</sup>型の半導体領域4 aが形成されている。p<sup>+</sup>型の半導体領域4 aには、p型のウエルH P W 3と同じ不純物が含有されているが、p<sup>+</sup>型の半導体領域4 aの不純物濃度の方が、p型のウエルH P W 3の不純物濃度よりも高くなるように設定されている。このp<sup>+</sup>型の半導体領域4 aは、基板1 Sの主面上の絶縁層6に形成されたコンタクトホールC T内の導体部7 aに電気的に接続されている。この導体部7 aが接するp<sup>+</sup>型の半導体領域4 aの表層一部に上記シリサイド層5 aを形成しても良い。

#### 【0053】

また、上記n型のウエルH N Wには、例えばリン(P)またはヒ素(A s)等のようなn型を示す不純物が含有されている。このn型のウエルH N Wの上層一部には、n<sup>+</sup>型の半導体領域8 aが形成されている。n<sup>+</sup>型の半導体領域8 aには、n型のウエルH N Wと同じ不純物が含有されているが、n<sup>+</sup>型の半導体領域8 aの不純物濃度の方が、n型のウエルH N Wの不純物濃度よりも高くなるように設定されている。n<sup>+</sup>型の半導体領域8 aは、上記p型のウエルH P W 1 ~ H P W 3に接触しないように、p型のウエルH P W 1 ~ H P W 3から離れている。すなわち、n<sup>+</sup>型の半導体領域8 aとp型のウエルH P W 1 ~ H P W 3との間にはn型の埋込ウエルD N Wの一部が介在されている。このようなn<sup>+</sup>型の半導体領域8 aは、上記絶縁層6に形成されたコンタクトホールC T内の導体部7 bに電気的に接続されている。この導体部7 bが接するn<sup>+</sup>型の半導体領域8 aの表層一部にシリサイド層5 aを形成しても良い。 30

#### 【0054】

本実施の形態1のフラッシュメモリのメモリセルM Cは、浮遊ゲート電極F Gと、データ書き込み・消去用の容量部C W Eと、データ読み出し用のM I S · F E T Q Rと、容量部Cとを有している。

#### 【0055】

浮遊ゲート電極F Gは、情報の記憶に寄与する電荷を蓄積する部分である。この浮遊ゲート電極F Gは、例えば低抵抗な多結晶シリコン等のような導電体膜からなり、電気的に浮遊状態(他の導体と絶縁された状態)で形成されている。また、この浮遊ゲート電極F Gは、図12に示すように、互いに隣接する上記p型のウエルH P W 1 , H P W 2 , H P W 3に平面的に重なるように第1方向Yに沿って延在した状態で形成されている。 40 50

## 【0056】

この浮遊ゲート電極 F G が p 型のウエル（第 2 ウエル）H PW 2 の活性領域 L 2 に平面的に重なる第 1 位置には、上記データ書き込み・消去用の容量部 C WE が配置されている。データ書き込み・消去用の容量部 C WE は、容量電極（第 1 電極）F GC 1 と、容量絶縁膜（第 1 絶縁膜）10d と、p 型の半導体領域 15, 15 と、p 型のウエル H PW 2 を有している。

## 【0057】

容量電極 F GC 1 は、上記浮遊ゲート電極 F G の一部により形成されており、容量部 C WE の上記他方の電極を形成する部分である。上記容量絶縁膜 10d は、例えば酸化シリコンからなり、容量電極 F GC 1 と基板 1S（p 型のウエル H PW 2）との間に形成されている。容量絶縁膜 10d の厚さは、例えば 10nm 以上、20nm 以下とされている。ただし、本実施の形態 1 の容量部 C WE では、データの書き換えにおいて、電子を p 型のウエル H PW 2 から容量絶縁膜 10d を介して容量電極 F GC 1 に注入したり、容量電極 F GC 1 の電子を容量絶縁膜 10d を介して p 型のウエル H PW 2 に放出したりするので、容量絶縁膜 10d の厚さは薄く、具体的には、例えば 13.5nm 程度の厚さに設定されている。容量絶縁膜 10d の厚さを 10nm 以上とする理由は、それより薄いと容量絶縁膜 10d の信頼性を確保できないからである。また、容量絶縁膜 10d の厚さを 20nm 以下とする理由は、それより厚いと電子を通過させることが難しくなり、データの書き換えが上手くできないからである。

## 【0058】

容量部 C WE の p 型の半導体領域 15 は、p 型のウエル H PW 2 内において容量電極 F GC 1 を挟み込む位置に容量電極 F GC 1 に対して自己整合的に形成されている。この半導体領域 15 は、それぞれチャネル側の p<sup>-</sup> 型の半導体領域 15a と、その各々に接続された p<sup>+</sup> 型の半導体領域 15b とを有している。この p<sup>-</sup> 型の半導体領域 15a および p<sup>+</sup> 型の半導体領域 15b には、例えばホウ素（B）等のような同一導電型の不純物が含有されているが、p<sup>+</sup> 型の半導体領域 15b の不純物濃度の方が、p<sup>-</sup> 型の半導体領域 15a の不純物濃度よりも高くなるように設定されている。この p 型の半導体領域 15 は、p 型のウエル H PW 2 と電気的に接続されている。p 型の半導体領域 15 および p 型のウエル H PW 2 は、容量部 C WE の上記一方の電極を形成する部分である。この p 型の半導体領域 15 は、上記絶縁層 6 に形成されたコンタクトホール C T 内の導体部 7c に電気的に接続されている。この導体部 7c は、上記データ書き込み・消去用のピット線 W BL に電気的に接続されている。この導体部 7c が接する p<sup>+</sup> 型の半導体領域 15b の表層一部にシリサイド層 5a を形成しても良い。

## 【0059】

また、上記浮遊ゲート電極 F G が p 型のウエル（第 3 ウエル）H PW 3 の活性領域 L 1 に平面的に重なる第 2 位置には、上記データ読み出し用の M IS · F ET QR が配置されている。データ読み出し用の M IS · F ET QR の構成は図 1 ~ 図 3 で説明したものと同じである。すなわち、データ読み出し用の M IS · F ET QR は、ゲート電極（第 2 電極）F GR と、ゲート絶縁膜（第 2 絶縁膜）10b と、一対の n 型の半導体領域 12, 12 とを有している。データ読み出し用の M IS · F ET QR のチャネルは、上記ゲート電極 F GR と活性領域 L 1 とが平面的に重なる上記 p 型のウエル H PW 3 の上層に形成される。

## 【0060】

ゲート電極 F GR は、上記浮遊ゲート電極 F G の一部により形成されている。上記ゲート絶縁膜 10b は、例えば酸化シリコンからなり、ゲート電極 F GR と基板 1S（p 型のウエル H PW 3）との間に形成されている。ゲート絶縁膜 10b の厚さは、例えば 13.5nm 程度である。上記データ読み出し用の M IS · F ET QR の一対の n 型の半導体領域 12, 12 は、p 型のウエル H PW 3 内においてゲート電極 F GR を挟み込む位置にゲート電極 F GR に対して自己整合的に形成されている。データ読み出し用の M IS · F ET QR の一対の n 型の半導体領域 12, 12 は、それぞれチャネル側の n<sup>-</sup> 型の半導体領

10

20

30

40

50

域 12 a と、その各々に接続された n<sup>+</sup> 型の半導体領域 12 b を有している。この n<sup>-</sup> 型の半導体領域 12 a および n<sup>+</sup> 型の半導体領域 12 b には、例えばリン (P) またはヒ素 (As) 等のような同一導電型の不純物が含有されているが、n<sup>+</sup> 型の半導体領域 12 b の不純物濃度の方が、n<sup>-</sup> 型の半導体領域 12 a の不純物濃度よりも高くなるように設定されている。このようなデータ読み出し用の MIS · FETQR の半導体領域 12, 12 の一方は、上記絶縁層 6 に形成されたコンタクトホール CT 内の導体部 7d に電気的に接続されている。この導体部 7d は、上記ソース線 SL に電気的に接続されている。この導体部 7d が接する n<sup>+</sup> 型の半導体領域 12 b の表層一部にシリサイド層 5a を形成しても良い。一方、データ読み出し用の MIS · FETQS のソースおよびドレイン用の n 型の半導体領域 12 の一方と共有とされている。

## 【0061】

選択 MIS · FETQS は、ゲート電極 FGS と、ゲート絶縁膜 10e と、ソース・ドレイン用の一対の n 型の半導体領域 12, 12 とを有している。選択 MIS · FETQS のチャネルは、上記ゲート電極 FGS と活性領域 L1 とが平面的に重なる上記 p 型のウエル HPW3 の上層に形成される。

## 【0062】

上記ゲート電極 FGS は、例えば低抵抗な多結晶シリコンにより形成されている。このゲート電極 FGS は、上記絶縁層 6 に形成されたコンタクトホール CT 内の導体部 7f に電気的に接続されている。この導体部 7f は、上記選択線 GS に電気的に接続されている。上記ゲート絶縁膜 10e は、例えば酸化シリコンからなり、ゲート電極 FGS と基板 1S (p 型のウエル HPW3) との間に形成されている。このゲート絶縁膜 10e の厚さは、例えば 13.5 nm 程度である。選択 MIS · FETQS の一対の n 型の半導体領域 12, 12 の構成は、上記データ読み出し用の MIS · FETQR の n 型の半導体領域 12 と同じである。選択 MIS · FETQS の他方の n 型の半導体領域 12 は、上記絶縁層 6 に形成されたコンタクトホール CT 内の導体部 7g に電気的に接続されている。この導体部 7g には、上記データ読み出し用のビット線 RBL に電気的に接続されている。この導体部 7g が接する n<sup>+</sup> 型の半導体領域 12 b の表層一部にシリサイド層 5a を形成しても良い。

## 【0063】

また、上記浮遊ゲート電極 FG が上記 p 型のウエル (第 4 ウエル) HPW1 に平面的に重なる位置には、上記容量部 C が形成されている。この容量部 C の構成は図 1 ~ 図 3 で説明したものと同じである。すなわち、この容量部 C は、制御ゲート電極 CGW と、容量電極 (第 3 電極) FGC2 と、容量絶縁膜 (第 3 絶縁膜) 10c と、p 型の半導体領域 13 と、p 型のウエル HPW1 とを有している。

## 【0064】

容量電極 FGC2 は、上記制御ゲート電極 CGW に対向する浮遊ゲート電極 FG 部分により形成されており、上記容量部 C の一方の電極を形成する部分である。このようにメモリセル MC のゲート構成を単層構成とすることにより、フラッシュメモリのメモリセル MC と主回路の素子との製造上の整合を容易にすることができるので、半導体装置の製造時間の短縮や製造コストの低減を図ることができる。

## 【0065】

また、容量電極 FGC2 の第 2 方向 X の長さは、上記データ書き込み・消去用の容量部 CWE の容量電極 FGC1 や上記データ読み出し用の MIS · FETQR のゲート電極 FGR の第 2 方向 X の長さよりも長くなるように形成されている。これにより、容量電極 FGC2 の平面積を大きく確保できるので、カップリング比を高めることができ、制御ゲート配線 CGW からの電圧供給効率を向上させることができることが可能となっている。

## 【0066】

上記容量絶縁膜 10c は、例えば酸化シリコンからなり、容量電極 FGC2 と基板 1S (p 型のウエル HPW1) との間に形成されている。容量絶縁膜 10c は、上記ゲート絶縁層 6 に形成されたコンタクトホール CT 内の導体部 7g に電気的に接続されている。

10

20

30

40

50

縁膜 10 b, 10 e、容量絶縁膜 10 d を形成するための熱酸化工程により同時に形成されており、その厚さは、例えば 13.5 nm 程度である。

#### 【0067】

容量部 C の p 型の半導体領域 13 は、p 型のウエル H PW 1 内において容量電極 F GC 2 を挟み込む位置に容量電極 F GC 2 に対して自己整合的に形成されている。この半導体領域 13 は、それぞれチャネル側の p<sup>-</sup> 型の半導体領域 13 b と、その各々に接続された p<sup>+</sup> 型の半導体領域 13 a とを有している。この p<sup>-</sup> 型の半導体領域 13 b および p<sup>+</sup> 型の半導体領域 13 a には、例えばホウ素 (B) 等のような同一導電型の不純物が含有されているが、p<sup>+</sup> 型の半導体領域 13 a の不純物濃度の方が、p<sup>-</sup> 型の半導体領域 13 b の不純物濃度よりも高くなるように設定されている。この p 型の半導体領域 13 は、p 型のウエル H PW 1 と電気的に接続されている。p 型の半導体領域 13 および p 型のウエル H PW 1 は、容量部 C の制御ゲート電極 CGW (上記他方の電極) を形成する部分である。この p 型の半導体領域 13 は、上記絶縁層 6 に形成されたコンタクトホール CT 内の導体部 7 e に電気的に接続されている。この導体部 7 e は、上記制御ゲート配線 CG に電気的に接続されている。この導体部 7 c が接する p<sup>+</sup> 型の半導体領域 15 b の表層一部にシリサイド層 5 a を形成しても良い。10

#### 【0068】

次に、図 14 は本実施の形態 1 のフラッシュメモリのデータ書き込み動作時の上記選択メモリセル MCS での各部への印加電圧の一例を示す図 12 の Y2 - Y2 線の断面図である。20

#### 【0069】

ここでは導体部 7 b を通じて n 型のウエル H NW および n 型の埋込ウエル D NW に、例えば 9 V 程度の電圧を印加して基板 1 S と p 型のウエル H PW 1 ~ H PW 3 との電気的な分離を行う。また、上記制御ゲート配線 CG から導体部 7 e を通じて容量部 C の制御ゲート電極 CGW に、例えば 9 V 程度の正の制御電圧を印加する。また、上記データ書き込み・消去用のビット線 WBL から導体部 7 c を通じて容量部 CWE の一方の電極 (p 型の半導体領域 15 および p 型のウエル H PW 2) に、例えば -9 V 程度の負の電圧を印加する。また、導体部 7 a を通じて、p 型のウエル H PW 3 に、例えば 0 V を印加する。また、上記選択線 GS から導体部 7 f を通じて選択 MIS · FETQS のゲート電極 FGS に、例えば 0 V を印加する。また、上記ソース線 SL から導体部 7 d を通じてデータ読み出し用の MIS · FETQR の一方の n 型の半導体領域 12 に、例えば 0 V を印加する。また、データ書き込み用のビット線 RBL から導体部 7 g を通じて、選択 MIS · FETQS の一方の n 型の半導体領域 12 に、例えば 0 V を印加する。これにより、選択メモリセル MCS のデータ書き込み・消去用の容量部 CWE の p 型のウエル H PW 2 の電子 e を、チャネル全面の FN トンネル電流により容量絶縁膜 10 d を通じて容量電極 FGC1 (浮遊ゲート電極 FG) に注入し、データを書き込む。30

#### 【0070】

次に、図 15 は本実施の形態 1 のフラッシュメモリのデータ消去動作時における各部への印加電圧を示す図 12 の Y2 - Y2 線の断面図である。

#### 【0071】

ここでは導体部 7 b を通じて n 型のウエル H NW および n 型の埋込ウエル D NW に、例えば 9 V 程度の電圧を印加して基板 1 S と p 型のウエル H PW 1 ~ H PW 3 との電気的な分離を行う。また、上記制御ゲート配線 CG から導体部 7 e を通じて容量部 C の制御ゲート電極 CGW に、例えば -9 V 程度の負の制御電圧を印加する。また、上記データ書き込み・消去用のビット線 WBL から導体部 7 c を通じて容量部 CWE の一方の電極 (p 型の半導体領域 15 および p 型のウエル H PW 2) に、例えば 9 V 程度の正の電圧を印加する。また、導体部 7 a を通じて、p 型のウエル H PW 3 に、例えば 0 V を印加する。また、上記選択線 GS から導体部 7 f を通じて選択 MIS · FETQS のゲート電極 FGS に、例えば 0 V を印加する。また、上記ソース線 SL から導体部 7 d を通じてデータ読み出し用の MIS · FETQR の一方の n 型の半導体領域 12 に、例えば 0 V を印加する。また40

50

、データ書き込み用のビット線 RBL から導体部 7g を通じて、選択 MIS · FETQS の一方の n 型の半導体領域 12 に、例えば 0V を印加する。これにより、選択メモリセル MCse1 (MCse2) のデータ書き込み・消去用の容量部 CWE の容量電極 FGC1 (浮遊ゲート電極 FG) に蓄積された電子 e を、チャネル全面の FN トンネル電流により容量絶縁膜 10d を通じて p 型のウエル HPW2 に放出し、データを消去する。

#### 【0072】

次に、図 16 は本実施の形態 1 のフラッシュメモリのデータ読み出し動作時における各部への印加電圧を示す図 12 の Y2 - Y2 線の断面図である。

#### 【0073】

ここでは導体部 7b を通じて n 型のウエル HNW および n 型の埋込ウエル DNW に、例えば 3V 程度の電圧を印加して基板 1S と p 型のウエル HPW1 ~ HPW3 との電気的な分離を行う。また、上記制御ゲート配線 CG から導体部 7e を通じて容量部 C の制御ゲート電極 CGW に、例えば 3V 程度の正の制御電圧を印加する。これにより、データ読み出し用の MIS · FETQR のゲート電極 FGR に正の電圧を印加する。また、導体部 7a を通じて、p 型のウエル HPW3 に、例えば 0V を印加する。また、上記選択線 GS から導体部 7f を通じて選択 MIS · FETQS のゲート電極 FGS に、例えば 3V を印加する。また、上記ソース線 SL から導体部 7d を通じてデータ読み出し用の MIS · FETQR の一方の n 型の半導体領域 12 に、例えば 0V を印加する。また、データ書き込み用のビット線 RBL から導体部 7g を通じて、選択 MIS · FETQS の一方の n 型の半導体領域 12 に、例えば 1V を印加する。また、上記データ書き込み・消去用のビット線 WB から導体部 7c を通じて容量部 CWE の一方の電極 (p 型の半導体領域 15 および p 型のウエル HPW2) に、例えば 0V の電圧を印加する。これにより、選択メモリセル MCr のデータ読み出し用の MIS · FETQR をオン条件とし、そのデータ読み出し用の MIS · FETQR のチャネルにドレイン電流が流れるか否かにより、選択メモリセル MCr に記憶されているデータが 0 / 1 のいずれなのかを読み出す。

#### 【0074】

このような本実施の形態 1 によれば、データ書き換え領域 (容量部 CWE) 、データ読み出し領域 (データ読み出し用の MIS · FETQR) および容量結合領域 (容量部 C) をそれぞれ別々の p 型のウエル HPW1 ~ HPW3 内に形成し、それぞれを n 型のウエル HNW および n 型の埋込ウエル DNW により分離する。データ書き換えは、容量素子で行う。

#### 【0075】

これにより、フラッシュメモリのデータ書き換え領域において、上記カットオフ用のトランジスタを設ける必要がなくなるので、半導体装置の小型化を推進できる。

#### 【0076】

また、データ書き換え用の素子を容量素子で形成し、チャネル全面の FN トンネル電流によるデータ書き換えにおいて、p 型の半導体領域 15 と p 型のウエル HPW2 とは同電位になるので、上記接合耐圧の問題が生じることもない。このため、フラッシュメモリのメモリセル MC の劣化を抑制または防止でき、フラッシュメモリの動作信頼性を向上させることができる。また、上記のようなタイミング設計が不要となるので、フラッシュメモリの周辺回路の規模を小さく抑えることができるので、半導体装置の小型化を推進できる。また、データ書き換えを、最も消費電流が小さく、低電圧における単一電源書き換えに適したチャネル全面の FN トンネル電流により行えるので、内部昇圧回路による、単一電源化が容易である。さらに、データ書き込みおよび消去において、ホール発生のないチャネル FN トンネル電流を使用するため、データの書き換え回数を向上させることができる。

#### 【0077】

また、データ書き換え領域 (容量部 CWE) と、データ読み出し領域 (データ読み出し用の MIS · FETQR) とをそれぞれ別々の p 型のウエル HPW2 , HPW3 内に形成したことにより、データ書き換えを安定化させることができる。このため、フラッシュメ

10

20

30

40

50

モリの動作信頼性を向上させることができる。

**【0078】**

(実施の形態2)

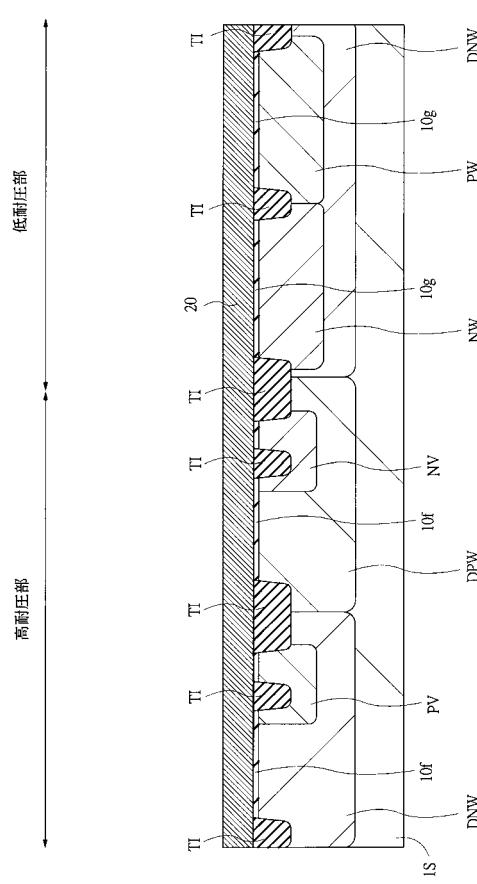

本実施の形態2では、例えばLCDドライバ回路(主回路)が形成された半導体チップに、その主回路に関する比較的小容量の所望の情報を記憶するフラッシュメモリが形成されている半導体装置の製造方法の一例を図17～図28により説明する。

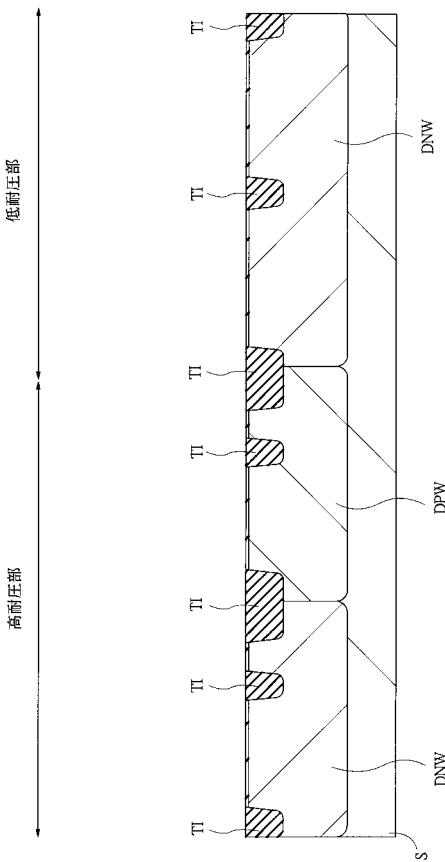

**【0079】**

図17～図28は、本実施の形態2の半導体装置の製造工程における同一の基板1S(ここでは、半導体ウエハと証する平面円形状の半導体薄板)の要部断面図である。高耐圧部および低耐圧部は、LCDドライバ回路を構成するMIS・FETの形成領域である。高耐圧部のMIS・FETの動作電圧は、例えば25V程度である。また、低耐圧部のMIS・FETには、上記の動作電圧が6.0Vのもののに他に、動作電圧が1.5VのMIS・FETがある。この動作電圧が1.5VのMIS・FETは、動作電圧が6.0VのMIS・FETよりも高速に動作する目的で設けられ、他のMIS・FETと共に上記のLCDドライバ回路を構成する。また、動作電圧が1.5VのMIS・FETは、そのゲート絶縁膜が動作電圧が6.0VのMIS・FETのゲート絶縁膜よりも薄く、その膜厚が1～3nm程度で構成されている。以降の図面および明細書文中では、説明の簡略化のため、主として動作電圧が25Vの高耐圧部のMIS・FETと、動作電圧が6.0Vの低耐圧部のMIS・FETとを図示し、動作電圧が1.5VのMIS・FETは図示しない。なお、本実施の形態2の半導体装置(半導体チップ、基板1S)においても外部から供給される電源は、単一電源とされている。

10

20

**【0080】**

まず、図17および図18に示すように、p型の基板1S(半導体ウエハ)を用意し、その高耐圧部に、p型の埋込ウエルDPWをフォトリソグラフィ(以下、単にリソグラフィという)工程およびイオン注入工程等により形成する。リソグラフィ工程は、フォトレジスト(以下、単にレジストという)膜の塗布、露光および現像等により所望のレジストパターンを形成する一連の工程である。イオン注入工程では、リソグラフィ工程を経て基板1Sの主面上に形成されたレジストパターンをマスクとして、基板1Sの所望の部分に所望の不純物を選択的に導入する。ここでレジストパターンは、不純物の導入領域が露出され、それ以外の領域が覆われるようなパターンとされている。

30

**【0081】**

続いて、高耐圧部、低耐圧部およびフラッシュメモリのメモリセル形成領域に、n型の埋込ウエルDNWをリソグラフィ工程およびイオン注入工程等により同時に形成する。その後、基板1Sの主面の分離領域に分離溝を形成した後、その分離溝内に絶縁膜を埋め込むことにより、溝形の分離部TIを形成する。これにより、活性領域を規定する。

**【0082】**

次いで、図19および図20に示すように、高耐圧部のnチャネル型のMIS・FET形成領域に、n型の半導体領域NVをリソグラフィ工程およびイオン注入工程等により形成する。このn型の半導体領域NVはn型の埋込ウエルDNWよりも高い不純物濃度を有する領域である。続いて、高耐圧部のpチャネル型のMIS・FET形成領域に、p型の半導体領域PVをリソグラフィ工程およびイオン注入工程等により形成する。このp型の半導体領域PVはp型の埋込ウエルDPWよりも高い不純物濃度を有する領域である。

40

**【0083】**

続いて、低耐圧部のnチャネル型のMIS・FET形成領域に、p型のウエルPWをリソグラフィ工程およびイオン注入工程等により形成する。このp型のウエルPWはp型の埋込ウエルDPWよりも高い不純物濃度を有する領域であり、p型の半導体領域PVよりも高い不純物濃度を有する領域である。続いて、低耐圧部のpチャネル型のMIS・FET形成領域に、n型のウエルNWをリソグラフィ工程およびイオン注入工程等により形成する。このn型のウエルNWはn型の埋込ウエルDNWよりも高い不純物濃度を有する領

50

域であり、n型の半導体領域N Vよりも高い不純物濃度を有する領域である。

#### 【0084】

続いて、フラッシュメモリのメモリセル形成領域に、p型のウエルH P W 1 ~ H P W 3 をリソグラフィ工程およびイオン注入工程等により同時に形成する。このp型のウェルH P W 1 ~ H P W 3はp型の埋込ウエルD P Wよりも高い不純物濃度を有する領域であり、p型の半導体領域P Vと同程度の不純物濃度を有する領域である。

#### 【0085】

また、これらn型の埋込ウエルD N W、p型の埋込ウエルD P W、n型の半導体領域N V、p型の半導体領域P V、n型のウェルN W、p型のウェルP W、p型のウェルH P W 1 ~ H P W 3の不純物濃度の大小関係は、後述の実施の形態においても同様である。

10

#### 【0086】

その後、ゲート絶縁膜10b, 10e, 10f, 10gおよび容量絶縁膜10c, 10dを熱酸化法等により形成した後、基板1S(半導体ウエハ)の主面上に、例えば低抵抗な多結晶シリコンからなる導体膜20をCVD(Chemical Vapor Deposition)法等により形成する。このとき、高耐圧部のMIS·FETのゲート絶縁膜10fは、25Vの耐圧に耐えられるように、低耐圧部のMIS·FETのゲート絶縁膜10gよりも厚い膜厚のゲート絶縁膜で形成する。高耐圧のMIS·FETのゲート絶縁膜10fの厚さは、例えば50~100nmである。上記の熱酸化法による酸化膜の他に、CVD法などによって堆積した絶縁膜を積層させることも出来る。

#### 【0087】

20

また、本実施の形態においては、不揮発性メモリのゲート絶縁膜10b, 10eおよび容量絶縁膜10c, 10dは、低耐圧部のMIS·FET(ここでは動作電圧が、例えば6.0VのMIS·FET)のゲート絶縁膜10gと同じ工程によって形成されており、不揮発性メモリのゲート絶縁膜10b, 10eおよび容量絶縁膜10c, 10dの厚さは、上記低耐圧部のMIS·FETのゲート絶縁膜10gと同じ厚さで形成されている。前述の実施の形態1の絶縁膜10a等と同様の理由から、ゲート絶縁膜10b, 10e, 10gおよび容量絶縁膜10c, 10dの膜厚は10nm以上であって20nm以下が好ましく、例えば13.5nmで形成されている。

#### 【0088】

30

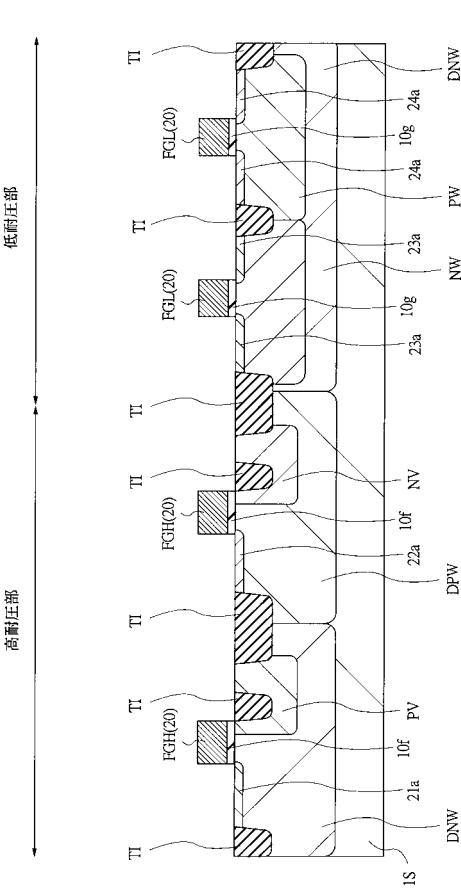

次いで、上記した導体膜20を図21および図22に示すように、リソグラフィ工程およびエッチング工程によりパターニングすることにより、ゲート電極FGH, FGL, FGSおよび浮遊ゲートFG(ゲート電極FGRおよび容量電極FGC1, FGC2)を同時に形成する。続いて、高耐圧部のpチャネル型のMIS·FET形成領域、容量部Cの形成領域およびデータ書き込み・消去用の容量部CWEの形成領域に、p<sup>-</sup>型の半導体領域21a, 13b, 15aをリソグラフィ工程およびイオン注入法等により同時に形成する。続いて、高耐圧部のnチャネル型のMIS·FET形成領域、データ読み出し用のMIS·FETQRの形成領域および選択MIS·FETQSの形成領域に、n<sup>-</sup>型の半導体領域22a, 12aをリソグラフィ工程およびイオン注入法等により同時に形成する。続いて、低耐圧部のpチャネル型のMIS·FET形成領域に、p<sup>-</sup>型の半導体領域23aをリソグラフィ工程およびイオン注入法等により形成する。続いて、低耐圧部のnチャネル型のMIS·FET形成領域に、n<sup>-</sup>型の半導体領域24aをリソグラフィ工程およびイオン注入法等により形成する。

40

#### 【0089】

次いで、図23および図24に示すように、基板1S(半導体ウエハ)の主面上に、例えば酸化シリコンからなる絶縁膜をCVD法等により堆積した後、それを異方性のドライエッティングによりエッチバックすることにより、ゲート電極FGH, FGL, FGR, FGSおよび容量電極FGC1, FGC2の側面にサイドウォールSWを形成する。

#### 【0090】

続いて、高耐圧部および低耐圧部のpチャネル型のMIS·FET形成領域と、容量部および書き込み・消去用容量部形成領域と、p型のウエルH P W 3の引き出し領域とに、

50

$p^+$ 型の半導体領域21b, 23b, 13a, 15b, 4aをリソグラフィ工程およびイオン注入法等により同時に形成する。これにより、高耐圧部に、ソースおよびドレイン用のp型の半導体領域21を形成し、pチャネル型のMIS·FETQPHを形成する。また、低耐圧部に、ソースおよびドレイン用のp型の半導体領域23を形成し、pチャネル型のMIS·FETQPLを形成する。また、容量部形成領域に、p型の半導体領域13を形成し、容量部Cを形成する。また、書き込み・消去用容量部形成領域に、p型の半導体領域15を形成し、データ書き込み・消去用の容量部CWEを形成する。

#### 【0091】

続いて、高耐圧部、低耐圧部、読み出し部および選択部のnチャネル型のMIS·FET形成領域に、 $n^+$ 型の半導体領域22b, 24b, 12bをリソグラフィ工程およびイオン注入法等により同時に形成する。これにより、高耐圧部に、ソースおよびドレイン用のn型の半導体領域22を形成し、nチャネル型のMIS·FETQNHを形成する。また、低耐圧部に、ソースおよびドレイン用のn型の半導体領域24を形成し、nチャネル型のMIS·FETQNLを形成する。また、読み出し部および選択部に、n型の半導体領域12を形成し、データ読み出し用のMIS·FETQRFおよび選択MIS·FETQSを形成する。

#### 【0092】

次いで、図25および図26に示すように、シリサイド層5aを選択的に形成する。このシリサイド層5aの形成工程に先立って、メモリセルMCの領域においては、浮遊ゲート電極FG (容量電極FGC1, FGC2、ゲート電極FGR) およびゲート電極FGSの上面にキャップ絶縁膜28を形成するとともに、基板1Sの一部上に絶縁膜を形成することで、その部分にシリサイド層5aが形成されないようにする。続いて、図27および図28に示すように、基板1S (半導体ウエハ) の主面上に、例えば窒化シリコンからなる絶縁層6aをCVD法等により堆積した後、その上に、例えば酸化シリコンからなる絶縁層6bを絶縁層6aよりも厚くCVD法等により堆積し、さらに絶縁層6bに化学的機械的研磨 (Chemical Mechanical Polishing: CMP) 処理を施し絶縁層6bの上面を平坦化する。その後、絶縁層6にコンタクトホールCTをリソグラフィ工程およびエッチング工程により形成する。その後、基板1S (半導体ウエハ) の主面上に、例えばタンゲステン(W)等からなる導体膜をCVD法等により堆積した後、それをCMP法等により研磨することでコンタクトホールCT内に導体部7a, 7c~7kを形成する。これ以降は通常の配線形成工程、検査工程および組立工程を経て半導体装置を製造する。

#### 【0093】

本実施の形態2によれば、LCDドライバ回路用のMIS·FETQPH, QNH, QPL, QNLの構成部と、メモリセルMCの容量部C, CWEおよびMIS·FETQRF, QSの構成部とを同時に形成することができるので、半導体装置の製造工程を簡略化することができる。これにより、半導体装置の製造時間を短縮できる。また、半導体装置のコストを低減できる。

#### 【0094】

また、半導体装置の外部単一電源電圧 (例えば3.3V) をLCDドライバ回路用の負電圧昇圧回路 (内部昇圧回路) により、メモリセルMCのデータ書き込み時に使用する電圧 (例えば-9V) に変換できる。また、外部単一電源電圧 (例えば3.3V) をLCDドライバ回路用の正電圧昇圧回路 (内部昇圧回路) により、メモリセルMCのデータ消去時に使用する電圧 (例えば9V) に変換できる。すなわち、フラッシュメモリ用に新たに内部昇圧回路を設ける必要がない。このため、半導体装置の内部の回路規模を小さく抑えることができるので、半導体装置の小型化を推進できる。

#### 【0095】

##### (実施の形態3)

図29は本実施の形態3の半導体装置のLCDドライバ回路 (主回路) 領域の要部断面図、図30は図29と同じ基板1Sに形成されたフラッシュメモリ領域の要部断面図を示している。

10

20

30

40

50

**【 0 0 9 6 】**

本実施の形態 3 では、図 29 および図 30 に示すように、容量部 C , CWE の p 型のウエル HPW1 , HPW2 内に p 型のウエル PW が形成されている。これにより、容量電極 FGC1 , FGC2 の直下の基板 1S 部分の p 型不純物の濃度が高くなるので、データ書き換え（書き込み・消去）時において、容量電極 FGC1 , FGC2 の直下の基板 1S 部分の空乏化を抑制または防止することができる。このため、容量絶縁膜 10c , 10d に印加される電圧を高くすることができるので、データの書き換え速度を速くすることができる。図 31 は、データの書き込み・消去特性を示している。実線 A1 , B1 はそれぞれ本実施の形態 3 の書き込み特性および消去を、実線 A0 , B0 はそれぞれ p 型のウエル HPW1 , HPW2 内に p 型のウエル PW を形成しない場合の書き込み特性および消去特 10 示している。本実施の形態 3 の場合、データの書き込み・消去時間を短縮できることが分かる。

**【 0 0 9 7 】**

このようなフラッシュメモリ領域における p 型のウエル HPW1 , HPW2 内の p 型のウエル PW は、LCD ドライバ回路領域の低耐圧部の n チャネル型の MIS · FETQNL の形成領域の p 型のウエル PW を形成する際に同時に形成されている。すなわち、フラッシュメモリ領域および低耐圧部の p 型のウエル PW の形成領域が露出され、それ以外の領域が覆われるようなレジストパターンを形成後、そのレジストパターンをマスクとして、p 型の不純物を基板 1S に導入することで形成されている。これにより、p 型のウエル HPW1 , HPW2 内に p 型のウエル PW を形成するからといって製造工程が増えること 20 もない。これ以外の製造工程は前記実施の形態 2 と同じである。また、上記以外の効果は、前記実施の形態 1 , 2 と同じなので説明を省略する。

**【 0 0 9 8 】****( 実施の形態 4 )**

図 32 は本実施の形態 4 の半導体装置の LCD ドライバ回路（主回路）領域の要部断面図、図 33 は図 32 と同じ基板 1S に形成されたフラッシュメモリ領域の要部断面図を示している。

**【 0 0 9 9 】**

本実施の形態 4 では、図 32 および図 33 に示すように、容量部 C , CWE のウエルが、LCD ドライバ回路領域の低耐圧部の n チャネル型の MIS · FETQNL の形成領域のウエルである p 型のウエル PW により形成されている。この p 型のウエル PW の p 型の不純物濃度の方が、p 型のウエル HPW3 の p 型の不純物濃度よりも高く設定されている。これにより、容量部 C , CWE の容量電極 FGC1 , FGC2 の直下の基板 1S 部分の p 型不純物の濃度が高くなるので、データ書き換え（書き込み・消去）時において、容量電極 FGC1 , FGC2 の直下の基板 1S 部分の空乏化を抑制または防止することができる。このため、容量絶縁膜 10c , 10d に印加される電圧を高くすることができるので、データの書き換え速度を速くすることができる。 30

**【 0 1 0 0 】**

このようなフラッシュメモリ領域における p 型のウエル PW は、前記実施の形態 3 と同様に、LCD ドライバ回路領域の低耐圧部の n チャネル型の MIS · FETQNL の形成領域の p 型のウエル PW を形成する際に同時に形成されている。これにより、メモリセル MC に p 型のウエル PW を形成するからといって製造工程が増えることもない。これ以外の製造工程は前記実施の形態 2 と同じである。また、上記以外の効果は、前記実施の形態 1 , 2 と同じなので説明を省略する。 40

**【 0 1 0 1 】****( 実施の形態 5 )**

図 34 は本実施の形態 5 の半導体装置の LCD ドライバ回路（主回路）領域の要部断面図、図 35 は図 34 と同じ基板 1S に形成されたフラッシュメモリ領域の要部断面図を示している。

**【 0 1 0 2 】**

10

20

30

40

50

本実施の形態 5 では、図 3 4 および図 3 5 に示すように、容量部 C , CWE 、データ読み出し用の MIS · FETQR および選択 MIS · FETQS のウエルが、LCD ドライバ回路領域の高耐圧部の p チャネル型の MIS · FETQPH の p 型の半導体領域 PV により形成されている。この容量部 C , CWE 、データ読み出し用の MIS · FETQR および選択 MIS · FETQS のウエルを形成する p 型の半導体領域 PV は、LCD ドライバ回路領域の高耐圧部の p チャネル型の MIS · FETQPH の p 型の半導体領域 PV を形成する際に同時に形成されている。すなわち、フラッシュメモリ領域および高耐圧部の p 型の半導体領域 PV の形成領域が露出され、それ以外の領域が覆われるようなレジストパターンを形成後、そのレジストパターンをマスクとして、 p 型の不純物を基板 1S に導入することで形成されている。これにより、フラッシュメモリの上記 p 型のウエル HPW 1 ~ HPW 3 の形成のためのリソグラフィ工程（レジスト塗布、露光および現像等のような一連の処理および露光時に使用するフォトマスクの製造工程）を削減できるので、半導体装置の製造時間を短縮できる。また、半導体装置の製造コストを低減できる。

10

#### 【 0103 】

これ以外の製造工程は前記実施の形態 2 と同じである。また、上記以外の効果は、前記実施の形態 1 , 2 と同じなので説明を省略する。

#### 【 0104 】

##### （実施の形態 6 ）

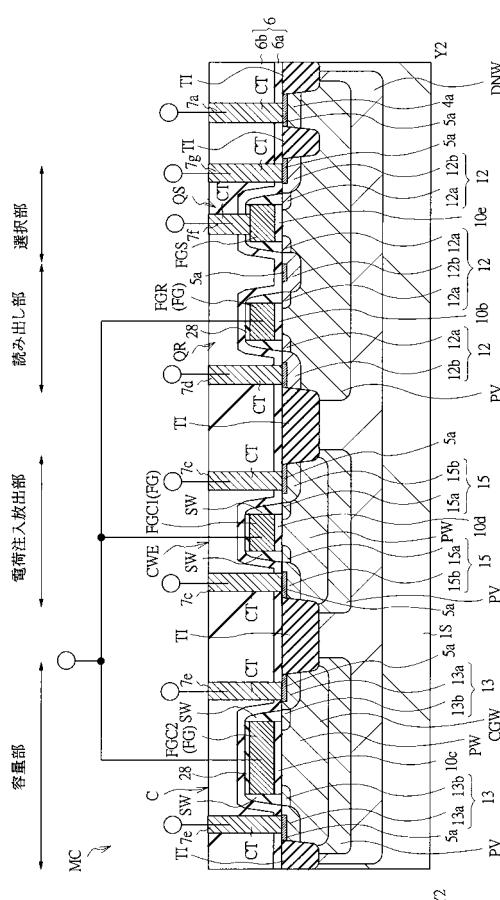

図 3 6 は本実施の形態 6 の半導体装置の LCD ドライバ回路（主回路）領域の要部断面図、図 3 7 は図 3 6 と同じ基板 1S に形成されたフラッシュメモリ領域の要部断面図を示している。

20

#### 【 0105 】

本実施の形態 6 では、図 3 6 および図 3 7 に示すように、容量部 C , CWE 、データ読み出し用の MIS · FETQR および選択 MIS · FETQS のウエルが、LCD ドライバ回路領域の高耐圧部の p チャネル型の MIS · FETQPH の p 型の半導体領域 PV により形成されている。この容量部 C , CWE 、データ読み出し用の MIS · FETQR および選択 MIS · FETQS のウエルを形成する p 型の半導体領域 PV は、前記実施の形態 5 と同様に、LCD ドライバ回路領域の高耐圧部の p チャネル型の MIS · FETQPH の p 型の半導体領域 PV を形成する際に同時に形成されている。これにより、前記実施の形態 5 と同様に、フラッシュメモリの上記 p 型のウエル HPW 1 ~ HPW 3 の形成のためのリソグラフィ工程を削減できるので、半導体装置の製造時間を短縮できる。また、半導体装置の製造コストを低減できる。

30

#### 【 0106 】

また、容量部 C , CWE のウエルを形成する p 型の半導体領域 PV 内に、 p 型のウエル PW が形成されている。これにより、容量部 C , CWE の容量電極 FGC1 , FGC2 の直下の基板 1S 部分の p 型不純物の濃度が高くなるので、データ書き換え（書き込み・消去）時ににおける、容量電極 FGC1 , FGC2 の直下の基板 1S 部分の空乏化を抑制または防止することができる。このため、容量絶縁膜 10c , 10d に印加される電圧を高くすることができるので、データの書き換え速度を速くすることができる。

40

#### 【 0107 】

また、メモリ領域の容量部 C , CWE の p 型の半導体領域 PV 内の p 型のウエル PW は、前記実施の形態 3 と同様に、LCD ドライバ回路領域の低耐圧部の n チャネル型の MIS · FETQNL の形成領域の p 型のウエル PW を形成する際に同時に形成されている。これにより、容量部 C , CWE のウエルを形成する p 型の半導体領域 PV 内に p 型のウエル PW を形成するからといって製造工程が増えることもない。これ以外の製造工程は前記実施の形態 2 と同じである。また、上記以外の効果は、前記実施の形態 1 , 2 と同じなので説明を省略する。

50

#### 【 0108 】

##### （実施の形態 7 ）

図 3 8 は本実施の形態 7 の半導体装置の LCD ドライバ回路（主回路）領域の要部断面

図、図39は図38と同じ基板1Sに形成されたフラッシュメモリ領域の要部断面図を示している。

#### 【0109】

本実施の形態7では、図38および図39に示すように、容量部C、CWEのウエルが、LCDドライバ回路領域の低耐圧部のnチャネル型のMIS・FETQNLの形成領域のウエルであるp型のウエルPWにより形成されている。このp型のウエルPWのp型の不純物濃度の方が、上記p型のウエルHPW1～HPW3のp型の不純物濃度よりも高く設定されている。これにより、容量部C、CWEの容量電極FGC1、FGC2の直下の基板1S部分のp型不純物の濃度が高くなるので、データ書き換え（書き込み・消去）時において、容量電極FGC1、FGC2の直下の基板1S部分の空乏化を抑制または防止することができる。このため、容量絶縁膜10c、10dに印加される電圧を高くすることができる。データの書き換え速度を速くすることができる。10

#### 【0110】

このようなフラッシュメモリ領域におけるp型のウエルPWは、前記実施の形態3と同様に、LCDドライバ回路領域の低耐圧部のnチャネル型のMIS・FETQNLの形成領域のp型のウエルPWを形成する際に同時に形成されている。これにより、メモリセルMCにp型のウエルPWを形成するからといって製造工程が増えることもない。

#### 【0111】

また、本実施の形態7では、データ読み出し用のMIS・FETQRおよび選択MIS・FETQSのウエルが、LCDドライバ回路領域の高耐圧部のpチャネル型のMIS・FETQPHのp型の半導体領域PVにより形成されている。このデータ読み出し用のMIS・FETQRおよび選択MIS・FETQSのウエルを形成するp型の半導体領域PVは、前記実施の形態5と同様に、LCDドライバ回路領域の高耐圧部のpチャネル型のMIS・FETQPHのp型の半導体領域PVを形成する際に同時に形成されている。すなわち、本実施の形態7では、前記実施の形態5と同様に、フラッシュメモリの上記p型のウエルHPW1～HPW3の形成のためのリソグラフィ工程を削減できるので、半導体装置の製造時間を短縮できる。また、半導体装置の製造コストを低減できる。20

#### 【0112】

これ以外の製造工程は前記実施の形態2と同じである。また、上記以外の効果は、前記実施の形態1、2と同じなので説明を省略する。30

#### 【0113】

##### （実施の形態8）

図40は本実施の形態8の半導体装置のフラッシュメモリ形成領域の要部平面図を示している。本実施の形態8の半導体装置の断面構成は前記実施の形態1～7で示したものと同じなので図示および説明を省略する。

#### 【0114】

本実施の形態8においては、半導体チップを構成する基板1Sの正面（第1正面）のフラッシュメモリ領域には、例えば8×2ビット構成の複数の上記メモリセルMCがアレイ状（行列状）に規則的に並んで配置されている。

#### 【0115】

p型のウエルHPW1～HPW2は、第2方向Xに延びて形成されている。p型のウエルHPW1には、複数のビット分の容量部Cが配置されている。また、p型のウエルHPW2には、複数のビット分のデータ書き込み・消去用の容量部CWEが配置されている。また、p型のウエルHPW3には、複数のビット分のデータ読み出し用のMIS・FETQRおよび選択MIS・FETQSが配置されている。40

#### 【0116】

このようなアレイ構成にすることにより、フラッシュメモリの占有領域を縮小することができるので、主回路が形成された半導体チップのサイズ増大を招くことなく、半導体装置の付加価値を向上させることができる。

#### 【0117】

10

30

40

50

(実施の形態 9)

本実施の形態 9においては、前記フラッシュメモリのメモリセルの選択MIS·FETを、例えばLCDドライバ回路(主回路)の動作電圧が1.2V(または1.5V)の相対的に低耐圧なMIS·FET(以下、1.2V系のMIS·FETともいう)により形成した場合について説明する。

【0118】

前記実施の形態においては、前記フラッシュメモリのメモリセルMCの選択MIS·FETQSが、作り易さを優先して、データ読み出し用のMIS·FETQRFと同じく、動作電圧が6VのMIS·FET(以下、6V系のMIS·FETともいう)により形成されている。

10

【0119】

しかし、本実施の形態のフラッシュメモリの構成においては、メモリセルMCのデータ読み出し用のMIS·FETQRFに印加されるドレイン電圧が、例えば~1.0V程度である。すなわち、データ読み出し用のMIS·FETQRFの選択MIS·FETQSのドレインには、例えば1.0V程度しか印加されない。また、選択MIS·FETQSのゲート電極はメモリセルMCの浮遊ゲート電極FGとも接続されておらず電荷保持能力に対する影響が無い。

【0120】

そこで、本実施の形態9においては、図41および図42に示すように、データ読み出し用のMIS·FETQRFの選択MIS·FETQS2を、例えばLCDドライバ回路の上記1.2V系のMIS·FETにより形成した。

20

【0121】

図41は本実施の形態9の半導体装置におけるフラッシュメモリのメモリセルMCの一例の平面図、図42は図41のY3-Y3線の断面図である。なお、図41では図面を見易くするために一部にハッチングを付した。

【0122】

基板1Sの選択部には、p型のウエルPW2が形成されている。この選択部のp型のウエルPW2は、上記メモリセルMCの上記p型のウエルHPW3に取り囲まれている。すなわち、p型のウエルPW2は、p型のウエルHPW3に内包されている。

【0123】

この選択部のp型のウエルPW2は、上記LCDドライバ回路の上記1.2V系のMIS·FETの配置領域のp型のウエルと同じものである。すなわち、選択部のp型のウエルPW2は、LCDドライバ回路の1.2V系のMIS·FET用のp型のウエルと同工程時にp型の不純物のホウ素が導入されることで形成されており、p型のウエルPW2の不純物濃度は、LCDドライバ回路の1.2V系のMIS·FET用のp型のウエルの不純物濃度と同じである。

30

【0124】

このp型のウエルPW2には、上記選択MIS·FETQS2のソース・ドレイン用の一対のn型の半導体領域12,12を構成するn-型の半導体領域12cが形成されている。このn-型の半導体領域12cは、選択MIS·FETQS2のチャネル形成領域を挟んでチャネル形成領域の両側に配置されており、n+型の半導体領域12bに電気的に接続されている。このn-型の半導体領域12cおよびn+型の半導体領域12bには、例えばリン(P)またはヒ素(A s)等のような同一導電型の不純物が含有されているが、n+型の半導体領域12bの不純物濃度の方が、n-型の半導体領域12cよりも不純物濃度が高くなっている。

40

【0125】

本実施の形態9において選択MIS·FETQS2のn-型の半導体領域12cの構成は、上記LCDドライバ回路の上記1.2V系のMIS·FETのソース・ドレイン用の一対の半導体領域を構成するn-型の半導体領域の構成と同じである。すなわち、選択MIS·FETQS2のn-型の半導体領域12cは、LCDドライバ回路の上記1.2V

50

系のMIS・FETのn<sup>-</sup>型の半導体領域と同工程時にn型の不純物が導入されることで形成されており、n<sup>-</sup>型の半導体領域12cの不純物濃度は、LCDドライバ回路の1.2V系のMIS・FET用のn<sup>-</sup>型の半導体領域の不純物濃度と同じである。

#### 【0126】

上記p型のウエルPW2が形成された基板1Sの正面(チャネル形成領域)上には、選択MIS・FETQS2のゲート絶縁膜10hが形成されている。この選択MIS・FETQS2のゲート絶縁膜10hの構成は、上記LCDドライバ回路の上記1.2V系のMIS・FETのゲート絶縁膜の構成と同じである。すなわち、選択MIS・FETQS2のゲート絶縁膜10hは、例えば酸化シリコンにより形成されている。また、選択MIS・FETQS2のゲート絶縁膜10hは、LCDドライバ回路の1.2V系のMIS・FETのゲート絶縁膜と同工程時に形成されている。このため、選択MIS・FETQS2のゲート絶縁膜10hの厚さは、上記LCDドライバ回路の上記1.2V系のMIS・FETのゲート絶縁膜の厚さと等しい。ただし、選択MIS・FETQS2のゲート絶縁膜10hの厚さは、2種ゲートプロセスによって、上記選択MIS・FETQSのゲート絶縁膜10eや上記データ読み出し用のMIS・FETQRのゲート絶縁膜10bよりも薄く形成されている。10

#### 【0127】

2種ゲートプロセスは、例えば以下の工程を有している。まず、基板1Sに対して第1回目の熱酸化処理を施すことにより、基板1Sの厚膜部および薄膜部の両方の正面に所定の厚さの第1ゲート絶縁膜を同時に形成する。続いて、薄膜部の第1ゲート絶縁膜のみを選択的に除去する。その後、厚膜部に第1ゲート絶縁膜を残したまま、基板1Sに対して第2回目の熱酸化処理等を施す。この第2回目の熱酸化処理では、薄膜部に形成するゲート絶縁膜の厚さが所望の厚さになるように酸化処理を施す。これにより、薄膜部に相対的に薄いゲート絶縁膜を形成すると同時に、厚膜部に相対的に厚いゲート絶縁膜を形成する。20

#### 【0128】

このようなゲート絶縁膜10h上には、選択MIS・FETQS2のゲート電極FGS2が形成されている。この選択MIS・FETQS2のゲート電極FGS2の構成は、上記LCDドライバ回路の上記1.2V系のMIS・FETのゲート電極の構成と同じである。すなわち、選択MIS・FETQS2のゲート電極FGS2は、例えば低抵抗なn<sup>+</sup>型の多結晶シリコンにより形成されている。また、選択MIS・FETQS2のゲート電極FGS2は、LCDドライバ回路の1.2V系のMIS・FETのゲート電極と同工程時に形成されている。この選択MIS・FETQS2のゲート電極FGS2のゲート長(ゲート電極FGS2の短方向の長さであって、ドレン電流が流れる方向の長さ)Lgは、上記LCDドライバ回路の上記1.2V系のMIS・FETのゲート長さLg(ミニマム寸法)と等しく、上記選択MIS・FETQSのゲート長や上記データ読み出し用のMIS・FETQRのゲート長よりも小さい。30

#### 【0129】

また、本実施の形態9においては、浮遊ゲート電極FG(すなわち、容量電極FGC、ゲート電極FGW, FGR)の上面、サイドウォールSWの表面全体およびその外周の基板1Sの正面一部を覆うように、キャップ絶縁膜28bが形成されている。40

#### 【0130】

このキャップ絶縁膜28bは、例えば酸化シリコンからなり、窒化シリコンからなる絶縁層6aが浮遊ゲート電極FGの上面に直接接しないように、浮遊ゲート電極FGの上面と絶縁層6bとの間に形成されている。これは、以下の理由からである。すなわち、窒化シリコンからなる絶縁層6aをプラズマ化学気相成長(Chemical Vapor Deposition: CVD)法等により堆積する場合、絶縁層6aは、その堆積の初期段階においてシリコンリッチな膜になり易い。このため、絶縁層6aが浮遊ゲート電極FGの上面に直接接した状態で形成されると、浮遊ゲート電極FG中の電荷が絶縁層6aのシリコンリッチな部分を通じて基板1S側に流れ、プラグを通じて放出されてしまう場合がある。その結果、フ50

ラッシュメモリのデータ保持特性が低下するので、そのような不具合を抑制または防止するためである。

#### 【0131】

また、このキャップ絶縁膜28bは、半導体基板1Sの他の領域に設けられた抵抗素子(図示せず)の上にも形成されている。この抵抗素子は、例えば、前述の容量電極FGCおよびゲート電極FGW, FGR, FGS, FGS2等と同工程で形成することができ、多結晶シリコン膜から成る。このような抵抗素子上にキャップ絶縁膜28bを設けることで、抵抗素子上にシリサイド層5aが形成される領域と形成されない領域とを選択的に作り分けることができ、これにより所望の抵抗値を有する抵抗素子を形成することができる。

10

#### 【0132】

すなわち、本実施の形態では、キャップ絶縁膜28bを用いることで、抵抗素子上にシリサイド層5aを作り分けるための絶縁膜と、浮遊ゲート電極FG上の絶縁層6aとの間に設ける絶縁膜を同工程で形成している。これにより、各々の絶縁膜を別工程で形成する必要がなく、製造工程の簡略化を図れる。

#### 【0133】

本実施の形態9では、浮遊ゲート電極FGの上面と絶縁層6bとの間にキャップ絶縁膜28bを形成したことにより、上記のような電荷の放出を抑制または防止することができるので、フラッシュメモリのデータ保持特性を向上させることができる。

#### 【0134】

また、上記シリサイド層5aは、キャップ絶縁膜28bをパターン形成した後に形成されている。このため、シリサイド層5aは、基板1Sの正面( $p^+$ 型の半導体領域13a, 15b、 $n^+$ 型の半導体領域12b)上には形成されているが、浮遊ゲート電極FGの上面には形成されていない。

20

#### 【0135】

このように本実施の形態9においては、前記実施の形態で得られた効果の他に、以下の効果を得ることができる。

#### 【0136】

すなわち、選択MIS・FETQS2のゲート長が、上記選択MIS・FETQSのゲート長より小さく、また、ゲート絶縁膜10hの膜厚が、上記選択MIS・FETQSのゲート絶縁膜10eよりも薄いことにより、同じ電圧で駆動させた場合、より大きな電流(ドレイン電流IdS)を得ることができる。このため、データの読み出し電流を増大させることができるので、回路的なマージンを拡大することができる。

30

#### 【0137】

また、選択MIS・FETQS2の占有面積を小さくすることができるので、フラッシュメモリの占有面積を小さくできる。特に、複数のメモリセルMCをアレイ状に配置する場合に、フラッシュメモリの占有面積を縮小することができる。

#### 【0138】

##### (実施の形態10)

本実施の形態10においては、フラッシュメモリでのデータの消去時や書き込み時に基板1Sに空乏層が形成されるのを抑制または防止するための構成について説明する。

40

#### 【0139】

図43は本実施の形態10の半導体装置におけるフラッシュメモリのメモリセルMCの一例の平面図、図44は図43のY4-Y4線の断面図である。なお、図43では図面を見易くするために一部にハッチングを付した。

#### 【0140】

本実施の形態10においては、データ書き込み・消去用の容量部CWEに、 $p$ 型の半導体領域15と $n$ 型の半導体領域30との異なる導電型の半導体領域が形成されている。すなわち、データ書き込み・消去用の容量部CWEにおいては、容量電極FGC1の左右の半導体領域の導電型が非対称になっている。

50

**【0141】**

$n^-$ 型の半導体領域30は、互いに電気的に接続された $n^-$ 型の半導体領域30aと $n^+$ 型の半導体領域30bとを有している。 $n^-$ 型の半導体領域30aは、容量電極FGC1の一方の端部辺りから基板1Sの正面に沿ってサイドウォールSWの幅分程度延びて終端している。 $n^+$ 型の半導体領域30bは、上記 $n^-$ 型の半導体領域30aの終端で一部重なり、その重なり位置から基板1Sの正面に沿って所望の長さ分だけ延びて分離部TIで終端している。

**【0142】**

この $n^-$ 型の半導体領域30aおよび $n^+$ 型の半導体領域30bには、例えはリン(P)またはヒ素(As)等のような同一導電型の不純物が含有されているが、 $n^+$ 型の半導体領域30bの不純物濃度の方が、 $n^-$ 型の半導体領域30aよりも不純物濃度が高くなっている。 10

**【0143】**

本実施の形態10では、上記 $n$ 型の半導体領域30が、図43に示すように、互いに隣接する2つの浮遊ゲート電極FGの隣接間に形成されている。すなわち、 $n$ 型の半導体領域30は、2つのデータ書き込み・消去用の容量部CWEの共有領域になっている。

**【0144】**

また、本実施の形態10においては、容量部Cに、 $p$ 型の半導体領域13と $n$ 型の半導体領域31との異なる導電型の半導体領域が形成されている。すなわち、容量部Cにおいては、容量電極FGC2の左右の半導体領域の導電型が非対称になっている。 20

**【0145】**

$n^-$ 型の半導体領域31は、互いに電気的に接続された $n^-$ 型の半導体領域31aと $n^+$ 型の半導体領域31bとを有している。 $n^-$ 型の半導体領域31aは、容量電極FGC2の一方の端部辺りから基板1Sの正面に沿ってサイドウォールSWの幅分程度延びて終端している。 $n^+$ 型の半導体領域31bは、上記 $n^-$ 型の半導体領域31aの終端で一部重なり、その重なり位置から基板1Sの正面に沿って所望の長さ分だけ延びて分離部TIで終端している。

**【0146】**

この $n^-$ 型の半導体領域31aおよび $n^+$ 型の半導体領域31bには、例えはリン(P)またはヒ素(As)等のような同一導電型の不純物が含有されているが、 $n^+$ 型の半導体領域31bの不純物濃度の方が、 $n^-$ 型の半導体領域31aよりも不純物濃度が高くなっている。 30

**【0147】**

本実施の形態10では、上記 $n$ 型の半導体領域31が、図43に示すように、互いに隣接する2つの浮遊ゲート電極FGの隣接間に形成されている。すなわち、 $n$ 型の半導体領域31は、2つの容量部Cの共有領域になっている。

**【0148】**

上記した $n^-$ 型の半導体領域30a, 31aは、上記データ読み出し用のMIS·FETQRおよび選択MIS·FETQSの $n^-$ 型の半導体領域12aの形成工程時に同時に形成されている。また、上記した $n^+$ 型の半導体領域30b, 31bは、上記データ読み出し用のMIS·FETQRおよび選択MIS·FETQSの $n^+$ 型の半導体領域12bの形成工程時に同時に形成されている。 40

**【0149】**

次に、このような構成にした理由を図45～図48により説明する。なお、図45～図48において、符号35は反転層、符号36は空乏層、e⁻は電子を示している。

**【0150】**

まず、電荷注入放出部について説明する。図45は前記実施の形態のメモリセルMCの電荷注入放出部の基板1Sの第2方向Xに沿った断面図を示している。データ書き込みに際して、電荷注入放出部の $p$ 型のウエルHPW2には、例えは-9V程度の負電圧が印加される。このため、容量絶縁膜10dの直下に空乏層36が形成される。その結果、カッ 50

プリング容量が低下する。また、注入される電子も枯渇しており、注入効率が低下すると考えられる。したがって、データの書き込み速度が低下する。また、データの書き込み速度にバラツキが生じる。

#### 【0151】

一方、図46は本実施の形態10のメモリセルMCの電荷注入放出部の基板1Sの第2方向Xに沿った断面図を示している。上記のようにn<sup>+</sup>型の半導体領域30bを追加したことにより、反転層35の形成が促進される。また、電子はp型半導体では少数キャリアであるのに対してn型半導体では多数キャリアである。このため、n<sup>+</sup>型の半導体領域30bを設けたことにより、注入電子を容量電極FGC1の直下の反転層35に容易に供給することができる。その結果、実効的なカップリング容量を増大させることができるので、容量電極FGC1(浮遊ゲート電極FG)の電位を効率的にコントロールすることができる。したがって、データの書き込み速度を向上させることができる。また、データ書き込み速度のバラツキも低減できる。

#### 【0152】

次に、容量部について説明する。図47は前記実施の形態のメモリセルMCの容量部の基板1Sの第2方向Xに沿った断面図を示している。データ消去に際して、容量部のp型のウエルHPW1には、例えば-9V程度の負電圧が印加されるため、容量絶縁膜10cの直下に空乏層36が形成される。その結果、実質的なカップリング容量が低下し、データの消去が遅くなる。また、データの消去速度にバラツキが生じる。

#### 【0153】

一方、図48は本実施の形態10のメモリセルMCの容量部の基板1Sの第2方向Xに沿った断面図を示している。上記のようにn<sup>+</sup>型の半導体領域31bを追加したことにより、電子を容量絶縁膜10cの直下にスムーズに供給することができる。このため、反転層35を素早く形成することができるので、p型のウエルHPW1を素早く-9Vに固定することができる。その結果、実効的なカップリング容量を増大させることができるので、容量電極FGC2(浮遊ゲート電極FG)の電位を効率的にコントロールすることができる。したがって、データ消去速度を向上させることができる。また、データ消去速度のバラツキも低減できる。

#### 【0154】

このように本実施の形態10によれば、電荷注入放出部および容量部に、p<sup>+</sup>型の半導体領域15b, 13bおよびn<sup>+</sup>型の半導体領域30b, 31bの両方を設けたことにより、電荷注入放出部ではn<sup>+</sup>型の半導体領域30bが電荷注入時の電子の供給源として作用し、容量部ではn<sup>+</sup>型の半導体領域31bが反転層への電子の供給源として作用するので、データの書き込み速度および消去速度を向上させることができる。

#### 【0155】

ここで、図49は、本実施の形態10の場合と前記実施の形態の場合とでデータの書き込み・消去特性を比較して示している。また、図50はデータ書き込み特性を抜き出して示し、図51はデータ消去特性を抜き出して示している。

#### 【0156】

実線A2, B2はそれぞれ本実施の形態10のデータ書き込み特性およびデータ消去特性を示し、実線A01, B01はn<sup>+</sup>型の半導体領域30b, 31bを形成せず、p<sup>+</sup>型の半導体領域15b, 13bのみの場合のデータ書き込み特性およびデータ消去特性を示している。

#### 【0157】

本実施の形態10の場合、データの書き込み時間を1.5桁ほど短くすることができた。また、データの消去時間を2桁ほど短くすることができた。

#### 【0158】

以上の説明では、電荷注入放出部および容量部の両方において、p<sup>+</sup>型の半導体領域15b, 13bおよびn<sup>+</sup>型の半導体領域30b, 31bの両方を設けた場合について説明したが、これに限定されるものではない。

10

20

30

40

50

## 【0159】

例えばデータの消去のみを高速化する場合、容量部には p 型の半導体領域 13 ( p<sup>+</sup> 型の半導体領域 13 b ) および n 型の半導体領域 31 ( n<sup>+</sup> 型の半導体領域 31 b ) の両方を設け、電荷注入放出部には p 型の半導体領域 15 ( p<sup>+</sup> 型の半導体領域 15 b ) のみを設けるようにしても良い。

## 【0160】

また、データの書き込みのみ高速化する場合、電荷注入放出部には p 型の半導体領域 15 ( p<sup>+</sup> 型の半導体領域 15 b ) および n 型の半導体領域 30 ( n<sup>+</sup> 型の半導体領域 30 b ) の両方を設け、容量部には p 型の半導体領域 13 ( p<sup>+</sup> 型の半導体領域 13 b ) のみを設けるようにしても良い。

10

## 【0161】

また、基板 1S の空乏化を抑制または防止する観点について、本実施の形態 10 で説明した構成と前記実施の形態 3 で説明した構成とを組み合わせても良い。すなわち、本実施の形態 10 においても、容量部 C, CWE の p 型のウエル HPW1, HPW2 内に p 型のウエル PW を設けても良い。

## 【0162】

次に、上記 n 型の半導体領域 30, 31 の形成方法の一例を図 52 ~ 図 54 により説明する。

## 【0163】

図 52 は本実施の形態 10 の半導体装置のフラッシュメモリにおけるメモリセル MC に n 型の半導体領域 30, 31 および p 型の半導体領域 13, 15 を形成する際のマスクを示したメモリセル MC の平面図を示している。

20

## 【0164】

図 52 に示す開口部 NA, NB は、本実施の形態 10 の半導体装置の製造工程において基板 1S (この段階ではウエハと称する平面円形状の半導体薄板) の主面上に堆積された第 1 レジスト膜 (マスク) に形成された平面四角形状の開口部である。この開口部 NA, NB は、それぞれ上記 n 型の半導体領域 30, 31 を形成するための n 型不純物の導入領域になる。

## 【0165】

また、2つの開口部 PA および 2つの開口部 PB は、本実施の形態 10 の半導体装置の製造工程において基板 1S (この段階では上記ウエハ) の主面上に堆積された第 2 レジスト膜 (マスク) に形成された平面四角形状の開口部である。この開口部 PA, PB は、それぞれ上記 p 型の半導体領域 15, 13 を形成するための p 型不純物の導入領域になる。

30

## 【0166】

なお、上記第 1 レジスト膜および上記第 2 レジスト膜はそれぞれ別々に塗布された別々のレジスト膜であるが、ここでは開口部 NA, NB, PA, PB の相対的な平面位置関係を示すため同一の図に示した。

## 【0167】

上記電荷注入放出部に配置される上記開口部 NA は、その第 2 方向 X の両端部が、互いに隣接する 2 つの容量電極 FGC1 (浮遊ゲート電極 FG) の一部に重なった状態で、互いに隣接する 2 つの容量電極 FGC1 (浮遊ゲート電極 FG) の間に配置されている。

40

## 【0168】

この開口部 NA は、互いに隣接する 2 つの容量電極 FGC1 の間の活性領域 L2 部分を内包するように配置されている。開口部 NA の第 2 方向 X の長さは、互いに隣接する 2 つの容量電極 FGC1 のうち、一方の容量電極 FGC1 の第 2 方向 X (短方向) の中央から他方の容量電極 FGC1 の第 2 方向 X (短方向) の中央まで延在している。また、開口部 NA の第 2 方向 Y の長さは、p 型のウエル HPW2 の第 2 方向 Y の長さとほぼ一致する程度となっている。

## 【0169】

50

このため、開口部 N A からは、互いに隣接する容量電極 F G C 1 の間の活性領域 L 2 部分の全体と、2つの容量電極 F G C 1 の各々の第2方向 X (短方向) の半分の部分とが露出される。

#### 【 0 1 7 0 】

一方、上記電荷注入放出部に配置される上記2つの開口部 P A の各々は、その第2方向 X の一端部が、互いに隣接する2つの容量電極 F G C 1 (浮遊ゲート電極 F G ) の各々の一部に重なるように配置されている。この2つの開口部 P A の各々の第2方向 X の一端は、互いに隣接する2つの容量電極 F G C 1 の各々の第2方向 X (短方向) の中央で終端している。このため、2つの開口部 P A の各々からは、p型の半導体領域 1 5 の形成領域 (活性領域 L 2 ) の他、2つの容量電極 F G C 1 の各々の第2方向 X (短方向) の半分の部分が露出される。10

#### 【 0 1 7 1 】

このため、互いに隣接する2つの容量電極 F G C 1 の各々には、開口部 N A からの n 型不純物の導入により形成される n 型の半導体領域と、開口部 P A からの p 型不純物の導入により形成される p 型の半導体領域とが第2方向 X (短方向) に沿って半分ずつ並んで形成されている。

#### 【 0 1 7 2 】

ただし、この容量電極 F G C 1 の n 型の半導体領域と、p 型の半導体領域との接合面 (境界面) が、浮遊ゲート電極 F G の長手方向 (第2方向 Y ) に対して交差することないように形成されている。すなわち、この容量電極 F G C 1 の n 型の半導体領域と、p 型の半導体領域との接合面は、浮遊ゲート電極 F G の長手方向 (第2方向 Y ) に対して沿うように配置される。20

#### 【 0 1 7 3 】

これは、仮に容量電極 F G C 1 の n 型の半導体領域と、p 型の半導体領域との接合面が、浮遊ゲート電極 F G の長手方向 (第2方向 Y ) に対して交差するように形成されると、その p n 接合面が電位の供給方向に対して交差するので、電位の伝達が劣化し、データの書き込み・消去特性あるいは読み出し特性が劣化してしまうからである。

#### 【 0 1 7 4 】

ここで、浮遊ゲート電極 F G の上面にシリサイド層が形成されている場合は、容量電極 F G C 1 の長手方向に対して交差するように上記 p n 接合面が形成されていたとしてもシリサイド層を通じて電位の供給ができる。これに対して、本実施の形態 1 0 の場合、上記のように浮遊ゲート電極 F G の上面にシリサイド層が形成されていないので、上記 p n 接合面が容量電極 F G C 1 の長手方向に対して交差するように形成されていると、上記電位の伝達の劣化が生じ易い。したがって、本実施の形態 1 0 の場合は、特に容量電極 F G C 1 に形成される上記 p n 接合面が容量電極 F G C 1 の長手方向に交差しないように配置することが好ましい。30

#### 【 0 1 7 5 】

なお、浮遊ゲート電極 F G は、上記開口部 N A , P A からの不純物導入工程前は、前記したように n<sup>+</sup> 型の多結晶シリコンにより形成されている。

#### 【 0 1 7 6 】

上記容量部に配置される上記開口部 N B は、その第2方向 X の両端部が、互いに隣接する2つの容量電極 F G C 2 (浮遊ゲート電極 F G ) の一部に重なった状態で、互いに隣接する2つの容量電極 F G C 2 (浮遊ゲート電極 F G ) の間に配置されている。40

#### 【 0 1 7 7 】

この開口部 N B は、互いに隣接する2つの容量電極 F G C 2 の間の活性領域 L 3 部分を内包するように配置されている。開口部 N B の第2方向 X の長さは、互いに隣接する2つの容量電極 F G C 2 のうち、一方の容量電極 F G C 2 の第2方向 X (短方向) の所望位置から他方の容量電極 F G C 2 の第2方向 X (短方向) の所望位置まで延在している。また、開口部 N B の第2方向 Y の長さは、p 型のウエル H P W 1 の第2方向 Y の長さとほぼ一致する程度となっている。50

**【 0 1 7 8 】**

このため、開口部 N B からは、互いに隣接する容量電極 F G C 2 の間の活性領域 L 3 部分の全体と、2つの容量電極 F G C 2 の各々の大半部分とが露出される。ここでは、浮遊ゲート電極 F G のネック部分 F A (くびれ部分、浮遊ゲート電極 F G の幅広の部分 (容量電極 F G C 2 ) と、幅の狭い部分との境界部分) も開口部 N B から露出される。

**【 0 1 7 9 】**

一方、上記容量部に配置される上記2つの開口部 P B の各々は、その第2方向 X の一端部が、互いに隣接する2つの容量電極 F G C 2 (浮遊ゲート電極 F G ) の各々の一部に重なるように配置されている。2つの開口部 P B の各々からは、p型の半導体領域 1 3 の形成領域 (活性領域 L 3 ) の他、2つの容量電極 F G C 2 の各々の第2方向 X (短方向) の一部分が露出される。

10

**【 0 1 8 0 】**

このため、互いに隣接する2つの容量電極 F G C 2 の各々には、開口部 N B からの n 型不純物の導入により形成される n 型の半導体領域と、開口部 P B からの p 型不純物の導入により形成される p 型の半導体領域とが第2方向 X (短方向) に沿って隣接した状態で並んで形成されている。なお、この容量電極 F G C 2 の n 型の半導体領域と p 型の半導体領域との接合面は、浮遊ゲート電極 F G の長手方向 (第2方向 Y ) に対して沿うように容量電極 F G C 2 に形成される。

**【 0 1 8 1 】**

ただし、本実施の形態 1 0においては、浮遊ゲート電極 F G の上記ネック部分 F A に n 型の半導体領域と p 型の半導体領域との接合面 (境界面) が形成されないようにしている。このため、開口部 N B は、その長辺 (浮遊ゲート電極 F G の長手方向に交差する第2方向 X に沿う辺) が浮遊ゲート電極 F G の幅の細いところで横切るように形成される。

20

**【 0 1 8 2 】**

これは、仮に浮遊ゲート電極 F G のネック部分 F A において、n 型の半導体領域と p 型の半導体領域との接合面が、浮遊ゲート電極 F G の長手方向 (第2方向 Y ) に対して交差するように形成されてしまうと、その p n 接合面が電位の供給方向に対して交差するので、電位の伝達が劣化し、データの書き込み・消去特性あるいは読み出し特性が劣化してしまうからである。

**【 0 1 8 3 】**

30

図 5 3 は、上記ネック部分 F A に上記 p n 接合面が形成される場合の一例を示している。なお、この場合も n 型不純物導入時のマスクとなるレジスト膜と、p 型不純物導入時のマスクとなるレジスト膜とはそれぞれ別々に塗布された別々のレジスト膜である。

**【 0 1 8 4 】**

開口部 N C は n 型不純物導入用の開口部を示している。この開口部 N C は、その第2方向 X の両端部が、互いに隣接する2つの容量電極 F G C 2 (浮遊ゲート電極 F G ) の一部に重なった状態で、互いに隣接する2つの容量電極 F G C 2 (浮遊ゲート電極 F G ) の間に配置されている。ただし、開口部 N C の第2方向 Y の長さは、活性領域 L 3 の第2方向 Y の長さよりも小さく、この開口部 N C からはネック部分 F A が露出されない。

**【 0 1 8 5 】**

40

一方、開口部 P C は p 型不純物導入用の開口部を示している。この開口部 P C は、その第2方向 X の両端部が、互いに隣接する2つの容量電極 F G C 2 (浮遊ゲート電極 F G ) の一部に重なった状態で、互いに隣接する2つの容量電極 F G C 2 (浮遊ゲート電極 F G ) の間に配置されている。開口部 P C からは、互いに隣接する2つの容量電極 F G C 2 間の活性領域 L 3 の全体と、2つの容量電極 F G C 2 の各々の第2方向 X (短方向) の大半部分とが露出される他、上記ネック部分 F A も露出される。

**【 0 1 8 6 】**

この例では、2つの容量電極 F G C 2 の間の1つの活性領域 L 3 内に、n 型の半導体領域 3 1 と p 型の半導体領域 1 3 とが形成されるようになる。このため、上記基板 1 S の空乏層の問題については効果的である。

50

## 【0187】

しかし、上記のように浮遊ゲート電極 F G は  $n^+$  型の多結晶シリコンにより形成されているので、図 5 3 の例の場合、ネック部分 F A に、 p n 接合面が浮遊ゲート電極 F G の長手方向に対して交差するように形成されてしまう。このため、その p n 接合面が電位の供給方向に対して交差するように形成されるので、電位の伝達が劣化し、データの書き込み・消去特性あるいは読み出し特性が劣化してしまう。

## 【0188】

ここで、浮遊ゲート電極 F G の上面にシリサイド層が形成されている場合は、浮遊ゲート電極 F G の長手方向に交差するように上記 p n 接合面が存在していてもシリサイド層を通じて電位の供給ができるので問題が生じない。これに対して、本実施の形態 10 の場合、上記のように浮遊ゲート電極 F G の上面にシリサイド層が形成されていないので、上記 p n 接合面が浮遊ゲート電極 F G の長手方向に対して交差して形成されると、上記電位の伝達の劣化が生じ易い。したがって、本実施の形態 10 の場合は、特にネック部分 F A に上記 p n 接合面が形成されないようにすることが好ましい。

10

## 【0189】

また、図 5 4 は、上記ネック部分 F A に上記 p n 接合面が形成されないようにする他の一例を示している。なお、この場合も  $n$  型不純物導入時のマスクとなるレジスト膜と、  $p$  型不純物導入時のマスクとなるレジスト膜とはそれぞれ別々に塗布された別々のレジスト膜である。

20

## 【0190】

開口部 N D は  $n$  型不純物導入用の開口部を示している。この開口部 N D は、互いに隣接する 2 つの容量電極 F G C 2 ( 浮遊ゲート電極 F G ) および活性領域 L 3 の上側部分に重なるように配置されている。この開口部 N D の第 2 方向 Y の長さは、活性領域 L 3 の第 2 方向 Y の長さよりも小さいが、この開口部 N D からは上記ネック部分 F A が露出されている。一方、開口部 P D , P E は  $p$  型不純物導入用の開口部を示している。

## 【0191】

この例では、2 つの容量電極 F G C 2 の間の 1 つの活性領域 L 3 内に、  $n$  型の半導体領域 3 1 と  $p$  型の半導体領域 1 3 とが形成されるので、上記基板 1 S の空乏層の問題については効果的である。また、上記ネック部分 F A には p n 接合面が形成されないので、上記電位の伝達の劣化に起因するデータの書き込み・消去特性あるいは読み出し特性の劣化の問題についても効果的である。

30

## 【0192】

しかし、この場合のように、一つの活性領域 L 3 内に、  $n$  型の半導体領域 3 1 と  $p$  型の半導体領域 1 3 とが形成される。この場合、以下の問題がある。すなわち、ウエットエッティング時や洗浄時に、  $n$  型の半導体領域 3 1 と  $p$  型の半導体領域 1 3 とで形成される p n 接合部に光が当たると光起電力が生じ、  $p$  型の半導体領域 3 1 と  $n$  型の半導体領域 1 3 とでエッティングレートが変わってしまう不具合が生じる。このため、このような場合には、ウエットエッティング時や洗浄時に基板 1 S の  $n$  型の半導体領域 3 1 と  $p$  型の半導体領域 1 3 とで形成される p n 接合部に光が当たらないようにする。このように図 5 4 に示したようにすることも可能ではあるが、一つの活性領域 L 3 内に p n 接合部が形成されないようにする方が好ましい。

40

## 【0193】

## ( 実施の形態 11 )

本実施の形態 11 においては、フラッシュメモリの浮遊ゲート電極に、導電型の異なる半導体領域を形成する他の構成例について説明する。

## 【0194】

図 5 5 は本実施の形態 11 の半導体装置のフラッシュメモリにおけるメモリセル M C に  $n$  型の半導体領域 3 0 , 3 1 および  $p$  型の半導体領域 1 3 , 1 5 を形成する際のマスクを示したメモリセル M C の平面図を示している。なお、この場合も  $n$  型不純物導入時のマスクとなるレジスト膜と、  $p$  型不純物導入時のマスクとなるレジスト膜とはそれぞれ別々に

50

塗布された別々のレジスト膜である。

**【0195】**

図55に示す本実施の形態11のフラッシュメモリのメモリセルMCにおいて、上記図52のメモリセルMCの構成と異なるのは、容量部の開口部NB2の構成である。この開口部NB2は、本実施の形態11の半導体装置の製造工程中において基板1S（この段階では上記ウエハ）の主面上の上記第1レジスト膜（マスク）に形成された平面四角形状の開口部であって、上記n型の半導体領域31を形成するためのn型不純物の導入領域になる。

**【0196】**

この開口部NB2の第2方向Yの寸法や配置は、上記図52で説明した構成と同じである。異なるのは、開口部NB2の第2方向Xの長さが、互いに隣接する2つの容量電極FGC2のうち、一方の容量電極FGC2の第2方向X（短方向）の中央から他方の容量電極FGC2の第2方向X（短方向）の中央まで延在していることである。このため、開口部NB2からは、互いに隣接する容量電極FGC2の間の活性領域L3部分の全体と、2つの容量電極FGC2の各々の第2方向X（短方向）の半分の部分とが露出される。

**【0197】**

次に、図56は本実施の形態11の半導体装置のフラッシュメモリにおけるメモリセルMCの電荷注入放出部の基板1Sの第2方向Xに沿った要部断面図、図57は本実施の形態11の半導体装置のフラッシュメモリにおけるメモリセルMCの容量部の基板1Sの第2方向Xに沿った要部断面図である。

**【0198】**

図56および図57に示すように、電荷注入放出部および容量部の容量電極FGC1, FGC2の各々には、n<sup>+</sup>型の半導体領域40a, 40bとp<sup>+</sup>型の半導体領域41a, 41bとが第2方向Xに沿って半分ずつ並んで形成されている。なお、浮遊ゲート電極FGにおいて、容量部CWE, C以外の部分はn<sup>+</sup>型となっている。これ以外の構成は前記実施の形態10と同じである。

**【0199】**

このような構成にした理由は、容量電極FGC1, FGC2の導電型が単一であると、p型のウエルHPW1, HPW2に印加される電圧によって、容量電極FGC1, FGC2の下部全面が空乏化してしまう場合が生じるからである。例えば容量電極FGC1, FGC2の全体がn<sup>+</sup>型の場合、p型のウエルHPW1, HPW2に正の電圧が印加される場合は良いが、p型のウエルHPW1, HPW2に負の電圧が印加されると、容量電極FGC1, FGC2の下部（ゲート絶縁膜10c, 10dに接する部分側）全体に空乏層が形成されてしまう。この結果、実効的なカップリング容量が低下するので、容量電極FGC1, FGC2（浮遊ゲート電極FG）の電位の制御効率が低下する。したがって、データの書き込み速度および消去速度が遅くなる。また、データ書き込み速度および消去速度にバラツキが生じる。

**【0200】**

これに対して、本実施の形態11によれば、容量電極FGC1, FGC2にp型とn型との両方の導電型の半導体領域を形成したことにより、p型のウエルHPW1, HPW2に正負いずれの電圧が印加されても、容量電極FGC1, FGC2の下部の半分のいずれか一方は空乏化されずに済む。これにより、実効的なカップリング容量を増大させることができるので、容量電極FGC1, FGC2（浮遊ゲート電極FG）の電位を効率的にコントロールすることができる。したがって、データの書き込み速度および消去速度向上させることができる。また、データ書き込み速度および消去速度のバラツキも低減できる。

**【0201】**

このメモリセルMCのデータ書き込み・消去時の容量部の様子の一例を図58および図59により説明する。なお、ここではメモリセルMCの容量部Cの様子を説明するが、電荷注入放出部（容量部CWE）でも同様になる。

10

20

30

40

50

**【0202】**

まず、図58は本実施の形態11のメモリセルMCのデータ書き込み時の容量部Cの基板1Sの第2方向Xに沿った要部断面図を示している。

**【0203】**

データ書き込みに際して、容量部Cのp型のウエルHPW1には、例えば+9V程度の正電圧が印加される。この場合、容量電極FGC2のp<sup>+</sup>型の半導体領域41bには空乏層43が形成されるが、容量電極FGC2のn<sup>+</sup>型の半導体領域40bには空乏層43が形成されない。このため、実効的なカップリング容量を確保することができるので、容量電極FGC2(浮遊ゲート電極FG)の電位を効率的にコントロールすることができる。したがって、データ書き込み速度を向上させることができる。また、データ書き込み速度のバラツキも低減できる。10

**【0204】**

次に、図59は本実施の形態11のメモリセルMCのデータ消去時の容量部Cの第2方向Xに沿った基板1Sの要部断面図を示している。

**【0205】**

データ消去に際して、容量部Cのp型のウエルHPW1には、例えば-9V程度の負電圧が印加される。この場合、容量電極FGC2のn<sup>+</sup>型の半導体領域40bには空乏層43が形成されるが、容量電極FGC2のp<sup>+</sup>型の半導体領域41bには空乏層43が形成されない。このため、実効的なカップリング容量を確保することができるので、容量電極FGC2(浮遊ゲート電極FG)の電位を効率的にコントロールすることができる。したがって、データ消去速度を向上させることができる。また、データ消去速度のバラツキも低減できる。20

**【0206】**

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は上記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

**【0207】**

以上の説明では主として本発明者によってなされた発明をその背景となつた利用分野である半導体装置の製造方法に適用した場合について説明したが、それに限定されるものではなく種々適用可能であり、例えばマイクロマシンの製造方法にも適用できる。この場合、マイクロマシンが形成された半導体基板に上記フラッシュメモリを形成することでマイクロマシンの簡単な情報を記憶することができる。30

**【産業上の利用可能性】****【0208】**

本発明は、不揮発性メモリを有する半導体装置の製造業に適用できる。

**【符号の説明】****【0209】**

1S 半導体基板

4a p<sup>+</sup>型の半導体領域

5a シリサイド層

6, 6a, 6b 絶縁層

7a ~ 7k 導体部

8a n<sup>+</sup>型の半導体領域

10a ゲート絶縁膜

10b ゲート絶縁膜(第2絶縁膜)

10c 容量絶縁膜(第3絶縁膜)

10d 容量絶縁膜(第1絶縁膜)

10e, 10f, 10g ゲート絶縁膜

11SW, 11DW n型の半導体領域

12R n型の半導体領域

10

20

30

40

50

|                               |    |

|-------------------------------|----|

| 1 2 n 型の半導体領域                 |    |

| 1 2 a n - 型の半導体領域             |    |

| 1 2 b n + 型の半導体領域             |    |

| 1 3 p 型の半導体領域                 |    |

| 1 3 a p + 型の半導体領域             |    |

| 1 3 b p - 型の半導体領域             |    |

| 1 5 p 型の半導体領域                 |    |

| 1 5 a p - 型の半導体領域             |    |

| 1 5 b p + 型の半導体領域             |    |

| 2 0 導体膜                       | 10 |

| 2 1 p 型の半導体領域                 |    |

| 2 1 a p - 型の半導体領域             |    |

| 2 1 b p + 型の半導体領域             |    |

| 2 2 n 型の半導体領域                 |    |

| 2 2 a n - 型の半導体領域             |    |

| 2 2 b n + 型の半導体領域             |    |

| 2 3 p 型の半導体領域                 |    |

| 2 3 a p - 型の半導体領域             |    |

| 2 3 b p + 型の半導体領域             |    |

| 2 4 n 型の半導体領域                 | 20 |

| 2 4 a n - 型の半導体領域             |    |

| 2 4 b n + 型の半導体領域             |    |

| 2 8 キャップ絶縁膜                   |    |

| 2 8 b キャップ絶縁膜                 |    |

| 3 0 n 型の半導体領域                 |    |

| 3 0 a n - 型の半導体領域             |    |

| 3 0 b n + 型の半導体領域             |    |

| 3 1 n 型の半導体領域                 |    |

| 3 1 a n - 型の半導体領域             |    |

| 3 1 b n + 型の半導体領域             | 30 |

| 3 5 反転層                       |    |

| 3 6 空乏層                       |    |

| 4 0 a , 4 0 b n + 型の半導体領域     |    |

| 4 1 a , 4 1 b p + 型の半導体領域     |    |

| 4 3 空乏層                       |    |

| T I 分離部                       |    |

| D N W n 型の埋込ウエル(第1ウエル)        |    |

| H P W a , H P W b p 型のウエル     |    |

| H P W 1 p 型のウエル(第4ウエル)        |    |

| H P W 2 p 型のウエル(第2ウエル)        | 40 |

| H P W 3 p 型のウエル(第3ウエル)        |    |

| H N W n 型のウエル                 |    |

| C T コンタクトホール                  |    |

| L , L 1 ~ L 5 活性領域            |    |

| F G 浮遊ゲート電極                   |    |

| Q W データ書き込み・消去用のM I S · F E T |    |

| F G W ゲート電極                   |    |

| Q R データ読み出し用のM I S · F E T    |    |

| F G R ゲート電極(第2電極)             |    |

| C 容量部                         | 50 |

|                               |                      |    |

|-------------------------------|----------------------|----|

| C G W                         | 制御ゲート電極              |    |

| F G C                         | 容量電極                 |    |

| F G C 2                       | 容量電極（第3電極）           |    |

| M R                           | メモリセルアレイ             |    |

| P R                           | 周辺回路領域               |    |

| W B L , W B L 0 , W B L 1     | データ書き込み・消去用のビット線     |    |

| R B L , R B L 0 , R B L 2     | データ読み出し用のビット線        |    |

| C G , C G 0 , C G 1           | 制御ゲート配線              |    |

| S L                           | ソース線                 | 10 |

| G S                           | 選択線                  |    |

| M C                           | メモリセル                |    |

| C W E                         | データ書き込み・消去用の容量部      |    |

| F G C 1                       | 容量電極（第1電極）           |    |

| Q S                           | 選択M I S · F E T      |    |

| F G S                         | ゲート電極                |    |

| D P W                         | p型の埋込ウエル             |    |

| P V                           | p型の半導体領域             |    |

| N V                           | n型の半導体領域             |    |

| P W                           | p型のウエル               |    |

| N W                           | n型のウエル               | 20 |

| F G H                         | ゲート電極                |    |

| F G L                         | ゲート電極                |    |

| Q P H                         | pチャネル型のM I S · F E T |    |

| Q P L                         | pチャネル型のM I S · F E T |    |

| Q N H                         | nチャネル型のM I S · F E T |    |

| Q N L                         | nチャネル型のM I S · F E T |    |

| S W                           | サイドウォール              |    |

| N A , N B , N B 2 , N C , N D | 開口部                  |    |

| P A , P B , P C , P D , P E   | 開口部                  |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図 10】

【図11】

图 10

【図12】

【図13】

图 12

13

【 図 1 4 】

【図16】

【図15】

【図17】

【図18】

【図20】

【図19】

【図21】

【図22】

【図24】

【図23】

【図25】

【図26】

【図28】

【図27】

【図29】

【図30】

【図32】

【図31】

【図33】

【図34】

【図36】

【図35】

【図37】

【 図 3 8 】

【図40】

【図39】

【図41】

【図42】

【図44】

【図43】

【図45】

【図46】

【図47】

【図48】

【図49】

【図 5 0】

【図 5 1】

【図 5 2】

【図 5 3】

【図 5 4】

【図 5 5】

【図 5 6】

【図 5 7】

【図 5 8】

【図 5 9】

---

フロントページの続き

(51)Int.Cl. F I

G 11 C 16/04 (2006.01)

(56)参考文献 特開2007-149947 (JP, A)

特開2005-175411 (JP, A)

特開2001-185633 (JP, A)

特開2003-317497 (JP, A)

特開2001-257324 (JP, A)

米国特許第06788574 (US, B1)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 336

G 11 C 16 / 04

H 01 L 21 / 8247

H 01 L 27 / 115

H 01 L 29 / 788

H 01 L 29 / 792