(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-9817

(P2008-9817A)

(43) 公開日 平成20年1月17日(2008.1.17)

|                   |            |             |

|-------------------|------------|-------------|

| (51) Int.C1.      | F 1        | テーマコード (参考) |

| <b>GO6F 13/28</b> | GO6F 13/28 | 310J        |

| <b>GO6F 13/36</b> | GO6F 13/36 | 310F        |

|                   |            | 5B061       |

審査請求 未請求 請求項の数 8 O L (全 18 頁)

|           |                              |          |                                                   |

|-----------|------------------------------|----------|---------------------------------------------------|

| (21) 出願番号 | 特願2006-180952 (P2006-180952) | (71) 出願人 | 000005223<br>富士通株式会社<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 |

| (22) 出願日  | 平成18年6月30日 (2006.6.30)       | (74) 代理人 | 100092152<br>弁理士 服部 毅麿                            |

|           |                              | (72) 発明者 | 牟田口 浩平<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 富士通株式会社内      |

|           |                              |          | F ターム (参考) 5B061 DD09 DD11 FF01 GG14 RR03         |

(54) 【発明の名称】半導体装置及びデータ転送方法

## (57) 【要約】

【課題】効率のよいDMA転送処理が可能な半導体装置を提供する。

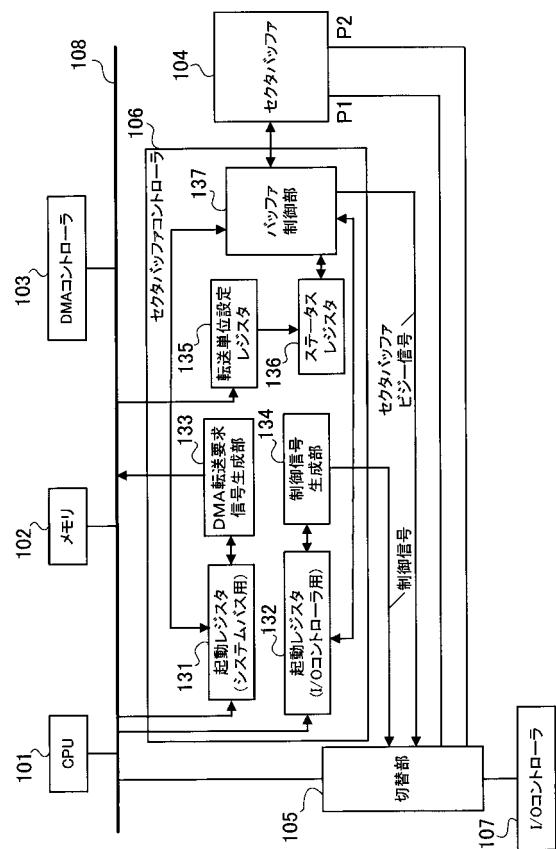

【解決手段】転送中のデータを一時記憶するセクタバッファ104の入出力ポートP1をシステムバス108とのDMA転送に用い、入出力ポートP2をI/Oコントローラ107とのデータ転送に用い、切替部105はシステムバス108とI/Oコントローラ107を接続するか、セクタバッファ104とI/Oコントローラ107またはシステムバス108を接続するかを切り替え、セクタバッファコントローラ106は入出力ポートP1、P2によるデータ転送を別々に起動し、セクタバッファ104とI/Oコントローラ107間での転送単位分のデータの転送の終了を検出すると、セクタバッファ104とI/Oコントローラ107とのデータ転送を遮断しシステムバス108とI/Oコントローラ107とを接続するための制御信号を切替部105に送出する。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

DMA転送処理を行う半導体装置において、

入出力装置とのデータ転送を制御する入出力制御部と、

転送中のデータを一時記憶し、第1の入出力ポートをシステムバスとのDMA転送に用い、第2の入出力ポートを前記入出力制御部とのデータ転送に用いる一時記憶部と、

前記システムバスと前記入出力制御部を接続するか、前記一時記憶部と前記入出力制御部または前記システムバスを接続するかを切り替える切替部と、

前記第1及び前記第2の入出力ポートによるデータ転送を別々に起動し、前記一時記憶部と前記入出力制御部間での転送単位分の前記データの転送の終了を検出すると、前記一時記憶部と前記入出力制御部とのデータ転送を遮断し前記システムバスと前記入出力制御部とを接続するための制御信号を前記切替部に送出する記憶制御部と、

を有することを特徴とする半導体装置。

## 【請求項 2】

前記記憶制御部は、起動ビットをセットすることで、前記第1及び前記第2の入出力ポートによるデータ転送を別々に起動させる2つのレジスタを有していることを特徴とする請求項1記載の半導体装置。

## 【請求項 3】

前記記憶制御部は、前記転送単位を設定するレジスタを有していることを特徴とする請求項1記載の半導体装置。

## 【請求項 4】

前記記憶制御部は、前記転送単位の前記データの転送が終了したか否かの情報を記憶するステータスレジスタを有していることを特徴とする請求項1記載の半導体装置。

## 【請求項 5】

前記記憶制御部は、前記入出力制御部のアクセスサイクルを記憶するレジスタを有し、前記アクセスサイクルに応じた制御信号またはアドレス信号を前記入出力制御部に送出することを特徴とする請求項1記載の半導体装置。

## 【請求項 6】

複数の前記入出力制御部を有し、

前記切替部は、複数の前記入出力制御部のいずれか1つを選択するための情報を記憶するレジスタを有していることを特徴とする請求項1記載の半導体装置。

## 【請求項 7】

前記一時記憶部は、デュアルポートRAMであることを特徴とする請求項1記載の半導体装置。

## 【請求項 8】

DMA転送処理を行うデータ転送方法において、

第1の入出力ポートをシステムバスとのDMA転送に用い、第2の入出力ポートを入出力装置とのデータ転送を制御する入出力制御部とのデータ転送に用いる一時記憶部の、前記第1及び前記第2の入出力ポートによるデータ転送を別々に起動し、

切替部によって前記システムバスと前記入出力制御部を接続するか、前記一時記憶部と前記入出力制御部または前記システムバスを接続するかを切り替え、

前記一時記憶部と前記入出力制御部間での転送単位分のデータの転送の終了を検出すると、前記切替部によって前記一時記憶部と前記入出力制御部とのデータ転送を遮断し、前記システムバスと前記入出力制御部とを接続することを特徴とするデータ転送方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は半導体装置及びデータ転送方法に関し、特に、DMA転送を行う半導体装置及びデータ転送方法に関する。

## 【背景技術】

10

20

30

40

50

## 【0002】

デジタルカメラや携帯電話などの情報端末において、データの記録媒体として、フラッシュメモリなどの不揮発性メモリを内蔵するメモリカードが使われている。

メモリカードは、情報端末に搭載されるシステムLSI (Large Scale Integrated circuit) に組み込まれているカードコントローラにより制御される。

## 【0003】

メモリカードにデータを転送する場合、システムLSI内のCPU (Central Processing Unit) が、カードコントローラを介してI/O (Input/Output) デバイスとしてカードにアクセスする方法 (PIO : Program I/O transfer) がある。PIOでデータ転送を行う場合、データ転送を行っている間、CPUが占有されるため、大きなデータを転送する場合にはシステムの処理能力が低下してしまう。

## 【0004】

一方、CPUを使わずにI/Oデバイスとメモリの間で直接データ転送を行う、DMA (Direct Memory Access) 転送が知られている。DMA転送を用いることで、CPUの処理を妨げることなく、大きなデータを転送することができる。

## 【0005】

ところで、一般的に、DMA転送を行うためには、I/OデバイスがDMAインターフェースを備えている必要がある。DMAインターフェースは、DMAコントローラとの間で送受信されるDMA転送要求信号や、DMA転送許可信号などの信号を解釈するのに必要となるからである。これに対して、DMAインターフェースなしでもDMA転送が可能なDMA転送方法が、例えば、特許文献1に開示されている。

## 【0006】

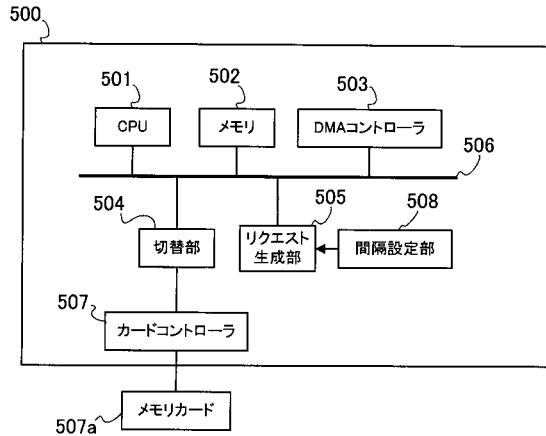

図12は、DMAインターフェースを持たないI/Oデバイスとの間でDMA転送を行う従来の半導体装置の構成を示す図である。

半導体装置500は、CPU501、メモリ502、DMAコントローラ503、切替部504、リクエスト生成部505を有し、これらはシステムバス506に接続されている。図12では、I/Oデバイスとして、メモリカード507aを用いた場合について示しており、半導体装置500は、カードコントローラ507を内蔵している。カードコントローラ507は、切替部504を介してシステムバス506に接続されている。CPU501及びDMAコントローラ503は、システムバス506のマスターであり、カードコントローラ507はスレーブである。

## 【0007】

ここで、切替部504は、CPU501とカードコントローラ507を接続するか、DMAコントローラ503とカードコントローラ507を接続するかを切り替える。具体的には、CPU501がマスターの場合、CPU501とカードコントローラ507とを接続し、アドレス信号や、チップセレクト信号などの制御信号、あるいはデータがカードコントローラ507に伝わるようにする。

## 【0008】

一方、DMAコントローラ503がマスターの場合、切替部504は、CPU501からの制御信号などを遮断し、DMAコントローラ503から入力されるDMA転送許可信号から新たに生成したチップセレクト信号、固定のアドレス信号 (I/Oポートアドレス) 及びシステムバス506に接続したメモリ502のデータをカードコントローラ507に伝える。

## 【0009】

リクエスト生成部505は、間隔設定部508に設定された一定の間隔で、DMA転送要求信号を、DMAコントローラ503に送出する。

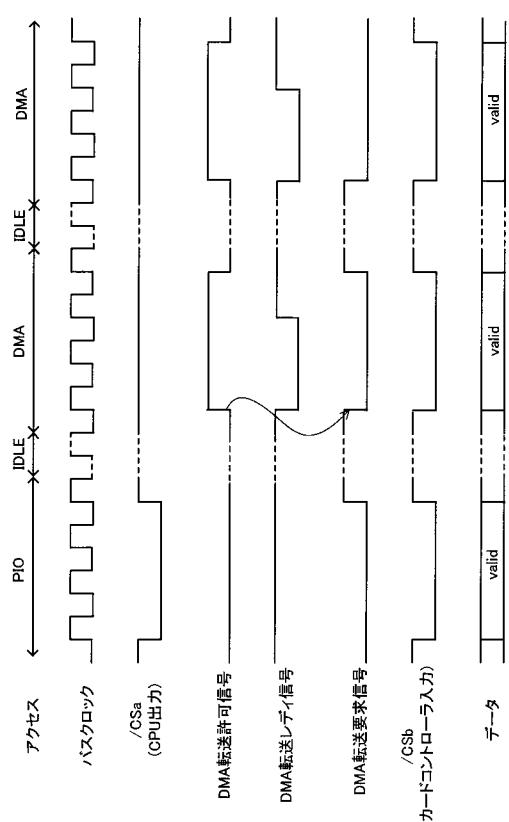

図13は、従来の半導体装置のデータ転送時の信号の様子を示すタイミングチャートである。

## 【0010】

システムバス506を伝わるバスロック、CPU501が出力するチップセレクト信

10

20

30

40

50

号 / C S a、D M A コントローラ 5 0 3 が切替部 5 0 4 に対して発行する D M A 転送許可信号、リクエスト生成部 5 0 5 が D M A コントローラ 5 0 3 に伝える D M A 転送レディ信号及び D M A 転送要求信号、カードコントローラ 5 0 7 に入力されるチップセレクト信号 / C S b、システムバス 5 0 6 のデータの様子を示している。

【 0 0 1 1 】

なお、図 1 3 の例では、カードコントローラ 5 0 7 のアクセスサイクルが 3 クロックサイクルである場合を示している。

P I O 転送中は、C P U 5 0 1 が発行するチップセレクト信号 / C S a がカードコントローラ 5 0 7 のチップセレクト信号 / C S b として使用される。すなわち、切替部 5 0 4 は、C P U 5 0 1 からの制御信号をカードコントローラ 5 0 7 に伝える。これにより、C P U 5 0 1 の制御のもと、データ (図 1 3 の v a l i d ) がメモリ 5 0 2 とカードコントローラ 5 0 7 との間で P I O 転送される。

【 0 0 1 2 】

続いて、リクエスト生成部 5 0 5 によって生成される D M A 転送要求信号が、アサート (図 1 3 では “ H ( High ) ” ) になると、D M A コントローラ 5 0 3 によって生成される D M A 転送許可信号がアサートして、転送が許可されるまでアイドルサイクルとなる。

【 0 0 1 3 】

D M A 転送中、切替部 5 0 4 は、D M A コントローラ 5 0 3 が発行する D M A 転送許可信号をもとにカードコントローラ 5 0 7 のチップセレクト信号 / C S b を生成する。すなわち、切替部 5 0 4 は、D M A コントローラ 5 0 3 からの制御信号をカードコントローラ 5 0 7 に伝える。これにより、D M A コントローラ 5 0 3 の制御のもと、データがメモリ 5 0 2 とカードコントローラ 5 0 7 との間で D M A 転送される。

【 0 0 1 4 】

ところで、D M A 転送においても、カードコントローラ 5 0 7 のアクセスサイクルが、P I O 転送のアクセスサイクルと同じになるように、カードコントローラ 5 0 7 に入力されるチップセレクト信号 / C S b を生成する必要がある。D M A 転送許可信号のみをもとに、チップセレクト信号 / C S b を生成する場合には、D M A コントローラ 5 0 3 から発行される D M A 転送許可信号を、カードコントローラ 5 0 7 のアクセスサイクルの期間 (ここでは 3 クロックサイクル) アクティブとする必要がある。例えば、リクエスト生成部 5 0 5 は、D M A 転送レディ信号を “ L ( Low ) ” にして転送レディ状態であることを D M A コントローラ 5 0 3 に伝えることで、D M A 転送許可信号を必要なサイクルだけアクティブとすることができます。また、D M A 転送レディ信号が使えない場合には、切替部 5 0 4 は、D M A 転送許可信号の立ち上がりに応じて、カードコントローラ 5 0 7 に入力するチップセレクト信号 / C S b を “ L ” にしてアサートし始め、アクセスサイクル分アクティブにしてから “ H ” にしてネガートする。

【 0 0 1 5 】

リクエスト生成部 5 0 5 から D M A コントローラ 5 0 3 に対して発行される D M A 転送要求信号は、D M A 転送許可信号の立ち上がりを検出してネガートにする。D M A 転送要求信号をネガートしてから、次にアサートするまでのサイクル数は間隔設定部 5 0 8 にて設定することができる。図 1 3 では、アクセスサイクルと等しい 3 クロックサイクルを設定した場合について示している。

【 0 0 1 6 】

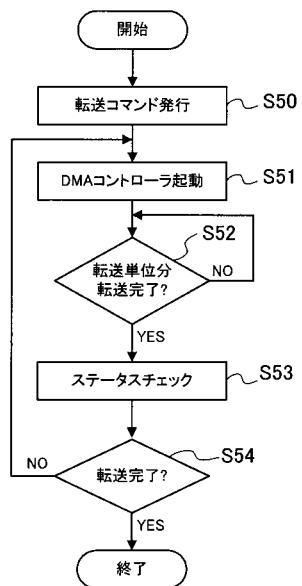

図 1 4 は、従来の半導体装置によるメモリカードへの D M A 転送時の動作を示すフローチャートである。

まず、C P U 5 0 1 から、切替部 5 0 4 を介して、カードコントローラ 5 0 7 に対して転送モードの設定や転送コマンドの発行を行う (ステップ S 5 0 )。

【 0 0 1 7 】

次に、D M A コントローラ 5 0 3 を起動し、D M A 転送を開始する (ステップ S 5 1)。D M A 転送が開始されると、リクエスト生成部 5 0 5 は、間隔設定部 5 0 8 に設定された値をもとに、一定間隔で D M A コントローラ 5 0 3 に対して転送要求を発行し続ける。

10

20

30

40

50

## 【0018】

データ転送の際には、一般に、データが正常に転送されたかどうかを一定のデータ量を転送するごとにチェックする必要がある（以下これをステータスチェックという。）。転送単位分の転送が完了したか否かが判定され（ステップS52）、転送単位分の転送が完了した場合には、このステータスチェックが行われる（ステップS53）。ステータスチェックは、CPU501からカードコントローラ507あるいはメモリカード507aにアクセスしてステータスをリードすることで行われる。

## 【0019】

ステータスチェックが行われた後、データの転送が完了したか否かが判定され（ステップS54）、転送したいデータがまだ残っている場合には、ステップS51の処理に戻り、再びDMAコントローラ503を起動して転送を再開し、全てのデータを転送し終わるまで、ステップS51～S54の処理を繰り返す。

## 【0020】

このような従来の半導体装置500によれば、DMAインターフェースを持たないI/OデバイスでもDMA転送を行うことが可能となる。

## 【特許文献1】特開平8-194660号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0021】

しかし、図12で示したような従来の半導体装置500では、リクエスト生成部505がDMA転送要求を発行している間、切替部504は、DMAコントローラ503からの制御信号をカードコントローラ507に対して伝えているため、CPU501からカードコントローラ507あるいはメモリカード507aに対してアクセスすることができない。CPU501からアクセスするためにはDMA転送を終了させる必要がある。そのため、従来の半導体装置500では、図14のように、ステータスチェックごとに、DMAコントローラ503を再起動しなければならず、オーバーヘッドが大きな処理となってしまう問題があった。

## 【0022】

本発明はこのような点に鑑みてなされたものであり、効率のよい転送処理が可能な半導体装置を提供することを目的とする。

本発明の他の目的は、効率のよい転送処理が可能なデータ転送方法を提供することである。

## 【課題を解決するための手段】

## 【0023】

本発明では上記問題を解決するために、DMA転送処理を行う半導体装置において、図1に示すように、入出力装置（I/Oデバイス107a）とのデータ転送を制御する入出力制御部（I/Oコントローラ107）と、転送中のデータを一時記憶し、入出力ポートP1をシステムバス108とのDMA転送に用い、入出力ポートP2をI/Oコントローラ107とのデータ転送に用いる一時記憶部（図1ではセクタバッファ104としている。）と、システムバス108とI/Oコントローラ107を接続するか、一時記憶部とI/Oコントローラ107またはシステムバス108を接続するかを切り替える切替部105と、入出力ポートP1、P2によるデータ転送を別々に起動し、一時記憶部とI/Oコントローラ107間での転送単位分のデータの転送の終了を検出すると、一時記憶部とI/Oコントローラ107とのデータ転送を遮断しシステムバス108とI/Oコントローラ107とを接続するための制御信号を切替部105に送出する記憶制御部（図1ではセクタバッファコントローラ106としている。）と、を有することを特徴とする半導体装置が提供される。

## 【0024】

上記の構成によれば、I/Oコントローラ107はI/Oデバイス107aとのデータ転送を制御し、一時記憶部は転送中のデータを一時記憶し、入出力ポートP1をシステム

10

20

30

40

50

バス 108 との DMA 転送に用い、入出力ポート P2 を I/O コントローラ 107 とのデータ転送に用い、切替部 105 はシステムバス 108 と I/O コントローラ 107 を接続するか、一時記憶部と I/O コントローラ 107 またはシステムバス 108 を接続するかを切り替え、記憶制御部は入出力ポート P1、P2 によるデータ転送を別々に起動し、一時記憶部と I/O コントローラ 107 間での転送単位分のデータの転送の終了を検出すると、一時記憶部と I/O コントローラ 107 とのデータ転送を遮断しシステムバス 108 と I/O コントローラ 107 とを接続するための制御信号を切替部 105 に送出する。

#### 【0025】

また、DMA 転送処理を行うデータ転送方法において、第 1 の入出力ポートをシステムバスとの DMA 転送に用い、第 2 の入出力ポートを入出力装置とのデータ転送を制御する入出力制御部とのデータ転送に用いる一時記憶部の、前記第 1 及び前記第 2 の前記入出力ポートによるデータ転送を別々に起動し、切替部によって前記システムバスと前記入出力制御部を接続するか、前記一時記憶部と前記入出力制御部または前記システムバスを接続するかを切り替え、前記一時記憶部と前記入出力制御部間での転送単位分のデータの転送の終了を検出すると、前記切替部によって前記一時記憶部と前記入出力制御部とのデータ転送を遮断し、前記システムバスと前記入出力制御部とを接続することを特徴とするデータ転送方法が提供される。

#### 【0026】

上記の方法によれば、第 1 の入出力ポートをシステムバスとの DMA 転送に用い、第 2 の入出力ポートを入出力装置とのデータ転送を制御する入出力制御部とのデータ転送に用いる一時記憶部の、第 1 及び第 2 の入出力ポートによるデータ転送が別々に起動され、切替部によってシステムバスと入出力制御部を接続するか、一時記憶部と入出力制御部またはシステムバスを接続するかが切り替えられ、一時記憶部と入出力制御部間での転送単位分のデータの転送の終了を検出すると、切替部によって一時記憶部と入出力制御部とのデータ転送が遮断され、システムバスと入出力制御部とが接続される。

#### 【発明の効果】

#### 【0027】

本発明は、2 つの入出力ポートを有する一時記憶部を用いて、第 1 の入出力ポートをシステムバスとの DMA 転送に用い、第 2 の入出力ポートを入出力装置とのデータ転送を制御する入出力制御部とのデータ転送に用いる。そして、入出力ポートによるデータ転送を別々に起動し、切替部によってシステムバスと入出力制御部を接続するか、一時記憶部と入出力制御部またはシステムバスを接続するか切り替え、一時記憶部と入出力制御部間での転送単位分のデータの転送の終了を検出すると、切替部によって一時記憶部と入出力制御部とのデータ転送を遮断し、システムバスと入出力制御部とを接続するようにしたので、ステータスチェックの最中にも、第 1 の入出力ポートを用いた DMA 転送を行うことができ、DMA コントローラをステータスチェックのたびに再起動する必要がなくなり、効率のよいデータ転送が可能になる。

#### 【発明を実施するための最良の形態】

#### 【0028】

以下、本発明の実施の形態を図面を参照して詳細に説明する。

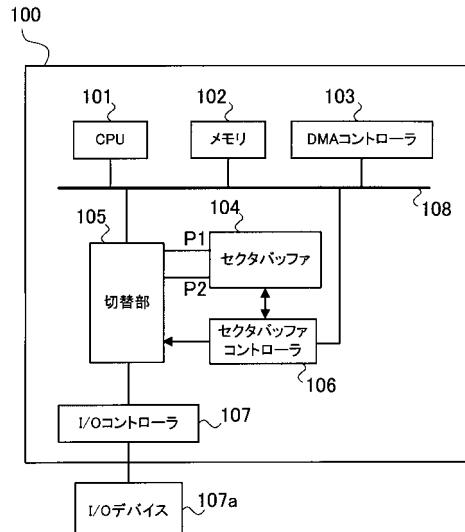

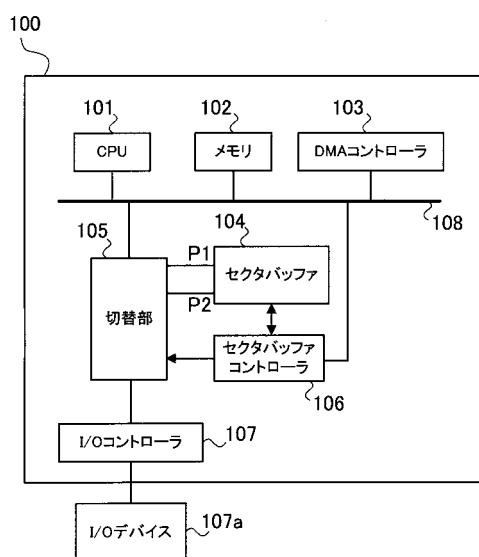

図 1 は、第 1 の実施の形態の半導体装置の構成を示す図である。

第 1 の実施の形態の半導体装置 100 は、CPU 101、メモリ 102、DMA コントローラ 103、セクタバッファ 104、切替部 105、セクタバッファコントローラ 106、I/O コントローラ 107 を有している。また、CPU 101、メモリ 102、DMA コントローラ 103、切替部 105、セクタバッファコントローラ 106 は、システムバス 108 と接続されている。なお、以下では、システムバス 108 は、アドレスを伝送するアドレスバス、データを伝送するデータバス、制御信号を伝送する制御線を含むものとする。CPU 101 及び DMA コントローラ 103 は、システムバス 108 のマスターであり、I/O コントローラ 107 はスレーブである。

#### 【0029】

10

20

30

40

50

C P U 1 0 1 は、システムバス 1 0 8 を介して半導体装置 1 0 0 の各部を制御する。

メモリ 1 0 2 は、I / O コントローラ 1 0 7 に接続された I / O デバイス 1 0 7 a にライ

イトするデータや、I / O デバイス 1 0 7 a からリードされたデータなどを記憶する。

【 0 0 3 0 】

D M A コントローラ 1 0 3 は、D M A 転送を制御する。

セクタバッファ 1 0 4 は、転送中のデータを一時記憶する一時記憶部である。そして、システムバス 1 0 8 との D M A 転送に用いる入出力ポート P 1 と、I / O コントローラ 1 0 7 とのデータ転送に用いる入出力ポート P 2 とを有している。図 1 では、この 2 つの入出力ポート P 1 、 P 2 を切替部 1 0 5 に接続している。このようなセクタバッファ 1 0 4 は、デュアルポート R A M ( Random Access Memory ) を用いることで実現可能である。また、2 つのシングルポート R A M を用いるようにしてもよい。

10

【 0 0 3 1 】

切替部 1 0 5 は、システムバス 1 0 8 と I / O コントローラ 1 0 7 を接続するか、セクタバッファ 1 0 4 と I / O コントローラ 1 0 7 またはシステムバス 1 0 8 を接続するかを切り替える。

【 0 0 3 2 】

セクタバッファコントローラ 1 0 6 は、セクタバッファ 1 0 4 の、2 つの入出力ポート P 1 、 P 2 によるデータ転送を別々に起動する。そして、セクタバッファ 1 0 4 と I / O コントローラ 1 0 7 間での転送したデータの量に応じて、切替部 1 0 5 でバスの接続を切り替えるための制御信号（以下セクタバッファビジー信号という。）を出力する。その他、セクタバッファコントローラ 1 0 6 は、切替部 1 0 5 を介して、I / O コントローラ 1 0 7 に対し、チップセレクト信号、リードストローブ信号、ライトストローブ信号、バイトイネーブル信号などの制御信号やアドレス信号を、I / O コントローラ 1 0 7 のアクセスサイクルに合わせて送出する。

20

【 0 0 3 3 】

I / O コントローラ 1 0 7 は、I / O デバイス 1 0 7 a とのデータ転送を制御する。本実施の形態の半導体装置 1 0 0 において、I / O コントローラ 1 0 7 は、D M A インタフェースを必要としていない。

【 0 0 3 4 】

なお、I / O デバイス 1 0 7 a としては、例えば、フラッシュメモリなどの不揮発性メモリを内蔵するメモリカードや、H D D ( Hard Disk Drive ) 、またはプリンタなど、データ転送を必要とする様々な機器が挙げられる。I / O コントローラ 1 0 7 は、カードコントローラや I D E ( Integrated Drive Electronics ) コントローラなどである。

30

【 0 0 3 5 】

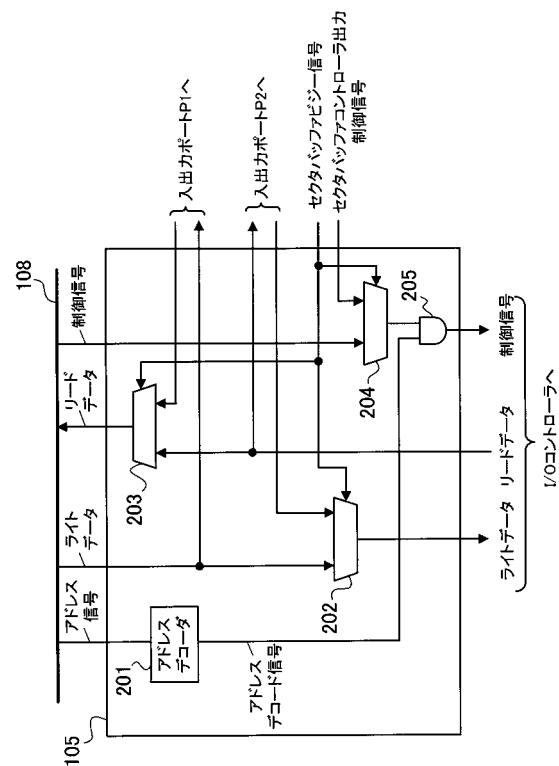

図 2 は、第 1 の実施の形態の半導体装置における切替部の一例の回路構成図である。

切替部 1 0 5 は、アドレスデコーダ 2 0 1 、セレクタ 2 0 2 、 2 0 3 、 2 0 4 、 A N D 回路 2 0 5 を有している。

【 0 0 3 6 】

アドレスデコーダ 2 0 1 は、システムバス 1 0 8 経由でアドレス信号を入力してアドレスデコード信号を生成する。

40

セレクタ 2 0 2 は、I / O デバイス 1 0 7 a へのライトデータとして、システムバス 1 0 8 からのデータか、セクタバッファ 1 0 4 の入出力ポート P 2 からのデータを用いるかを、セクタバッファコントローラ 1 0 6 で生成される制御信号の 1 つであるセクタバッファビジー信号に応じて切り替える。

【 0 0 3 7 】

セレクタ 2 0 3 は、I / O デバイス 1 0 7 a からのリードデータとして、I / O コントローラ 1 0 7 からのデータか、セクタバッファ 1 0 4 の入出力ポート P 1 からのデータを用いるかを、セクタバッファビジー信号に応じて切り替える。

【 0 0 3 8 】

セレクタ 2 0 4 は、システムバス 1 0 8 からの制御信号か、セクタバッファコントロ

50

ラ 1 0 6 で生成されたチップセレクト信号などの制御信号のいずれかを、セクタバッファビジー信号に応じて選択する。

【 0 0 3 9 】

AND回路 2 0 5 は、セレクタ 2 0 4 から出力された制御信号と、アドレスデコード信号とを入力する。I/Oコントローラ 1 0 7 を起動しない場合には、アドレスデコード信号は“0”となり、制御信号をマスクする。

【 0 0 4 0 】

図 3 は、第 1 の実施の形態の半導体装置におけるセクタバッファコントローラの一例の構成を示す図である。

セクタバッファコントローラ 1 0 6 は、システムバス 1 0 8 側とのDMA転送用の起動レジスタ 1 3 1 、I/Oコントローラ 1 0 7 側とのデータ転送用の起動レジスタ 1 3 2 、DMA転送要求信号生成部 1 3 3 、制御信号生成部 1 3 4 、転送単位設定レジスタ 1 3 5 、ステータスレジスタ 1 3 6 、バッファ制御部 1 3 7 を有する。

【 0 0 4 1 】

起動レジスタ 1 3 1 には、システムバス 1 0 8 とセクタバッファ 1 0 4 との間でDMA転送を起動する際に起動ビットがセットされる。起動ビットは、CPU 1 0 1 の制御のもと、システムバス 1 0 8 を介してセットされる。

【 0 0 4 2 】

起動レジスタ 1 3 2 には、I/Oコントローラ 1 0 7 とセクタバッファ 1 0 4 との間でデータ転送を起動する際に起動ビットがセットされる。起動ビットは、CPU 1 0 1 の制御のもと、システムバス 1 0 8 を介してセットされる。

【 0 0 4 3 】

DMA転送要求信号生成部 1 3 3 は、起動レジスタ 1 3 1 に起動ビットがセットされると、DMA転送要求信号を生成し、システムバス 1 0 8 を介してDMAコントローラ 1 0 3 に送出する。

【 0 0 4 4 】

制御信号生成部 1 3 4 は、起動レジスタ 1 3 2 に起動ビットがセットされると、I/Oコントローラ 1 0 7 に送出するチップセレクト信号、リードストローブ信号や、ライトストローブ信号、バイトイネーブル信号などの制御信号をI/Oコントローラ 1 0 7 のアクセスサイクルに合わせて生成し、切替部 1 0 5 に送出する。なお、転送するデータを記憶するI/Oデバイス 1 0 7 a のアドレスを指定するアドレス信号をアクセスサイクルに合わせて生成して、制御信号とともに切替部 1 0 5 に送出するようにしてもよい。以下では、このアドレス信号については説明を省略する。

【 0 0 4 5 】

転送単位設定レジスタ 1 3 5 には、CPU 1 0 1 がステータスチェックを行う転送単位が、システムバス 1 0 8 を介して CPU 1 0 1 により設定される。

ステータスレジスタ 1 3 6 は、転送単位分の転送が終了したか否かの状態を記憶する。

【 0 0 4 6 】

バッファ制御部 1 3 7 は、セクタバッファ 1 0 4 の転送を制御するとともに、起動レジスタ 1 3 1 、1 3 2 に起動ビットがセットされると、セクタバッファ 1 0 4 の入出力ポート P 1 、P 2 によるデータ転送を起動する。また、ステータスレジスタ 1 3 6 の状態を検出し、転送単位分の転送が終了した場合には、CPU 1 0 1 と I/Oコントローラ 1 0 7 間を接続させるためのセクタバッファビジー信号を生成して、切替部 1 0 5 に送出する。

【 0 0 4 7 】

以下、第 1 の実施の形態の半導体装置 1 0 0 の動作を説明する。

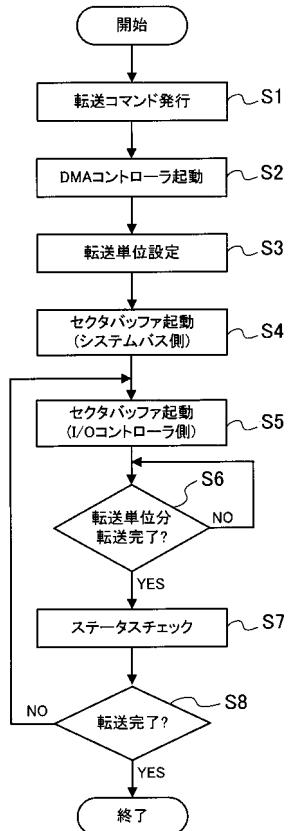

図 4 は、第 1 の実施の形態の半導体装置による転送処理を示すフローチャートである。

まず CPU 1 0 1 は、システムバス 1 0 8 から切替部 1 0 5 を介して I/Oコントローラ 1 0 7 に、転送コマンドを発行する（ステップ S 1）。このときセクタバッファコントローラ 1 0 6 は、図 2 の切替部 1 0 5 のセレクタ 2 0 2 、2 0 3 、2 0 4 に対して、システムバス 1 0 8 と、I/Oコントローラ 1 0 7 を接続させるセクタバッファビジー信号（

10

20

30

40

50

例えば、“0”)を入力している。これにより転送コマンド(制御信号)は、セレクタ204を介して、AND回路205に入力される。I/Oコントローラ107へ制御信号を送出する際、アドレスデコード信号は、“1”となり、転送コマンドは、AND回路205から出力され、I/Oコントローラ107に入力される。

#### 【0048】

次に、DMAコントローラ103に転送モードなどを設定し起動する(ステップS2)。転送モードとして、例えばライト動作、リード動作、転送データ数などを設定する。

DMAコントローラ103を起動すると、セクタバッファコントローラ106の転送単位設定レジスタ135に、ステータスチェックを行う転送単位を設定する(ステップS3)。

10

#### 【0049】

次に、セクタバッファ104の入出力ポートP1によるシステムバス108側とのDMA転送を開始するために、CPU101は、セクタバッファコントローラ106の起動レジスタ131に起動ビットをセットする(例えば、“1”を書き込む。)(ステップS4)。起動ビットがセットされるとセクタバッファコントローラ106の、DMA転送要求信号生成部133は、DMA転送要求信号を、システムバス108を介してDMAコントローラ103に送出してDMAコントローラ103を起動する。例えば、ライト動作の場合、DMAコントローラ103にて転送要求が受け付けられると、メモリ102からDMAコントローラ103を介して、セクタバッファ104へのDMA転送が開始する。

#### 【0050】

システムバス108側の転送が開始されると、セクタバッファコントローラ106のバッファ制御部137は、セクタバッファビジー信号をアサートする(例えば、“1”とする。)。これにより、図2の切替部105のセレクタ202、203、204は、システムバス108と、I/Oコントローラ107との接続を遮断し、セクタバッファ104の入出力ポートP1とシステムバス108、及び、入出力ポートP2とI/Oコントローラ107間を接続させる。ライト動作の場合には、システムバス108を介して、入出力ポートP1によりセクタバッファ104へのDMA転送が開始する。

20

#### 【0051】

次に、セクタバッファの入出力ポートP2によるI/Oコントローラ107側の転送を開始するために、CPU101は、セクタバッファコントローラ106の起動レジスタ132に起動ビットをセットする(例えば、“1”を書き込む。)(ステップS5)。起動ビットがセットされると、セクタバッファコントローラ106の制御信号生成部134は、I/Oコントローラ107のアクセスサイクルに合わせて制御信号を生成し、切替部105に送出する。そして、例えばライト動作の場合には、セクタバッファコントローラ106は、セクタバッファ104に蓄積されたデータを入出力ポートP2からI/Oコントローラ107に転送する。リード動作の場合には、I/Oデバイス107aからI/Oコントローラ107を介してリードデータが切替部105に入力され、入出力ポートP2からセクタバッファ104に蓄積される。このとき、入出力ポートP1から蓄積されたデータがシステムバス108側に転送される。

30

#### 【0052】

セクタバッファ104とI/Oコントローラ107間でのデータ転送の間、セクタバッファコントローラ106では、転送単位設定レジスタ135に設定された転送単位の転送が終了したか否かを監視している(ステップS6)。そして、転送単位の転送が完了すると、ステータスレジスタ136には、転送が完了した旨の情報がセットされる。これにより、セクタバッファコントローラ106は、セクタバッファ104の入出力ポートP2による転送を停止させ、セクタバッファビジー信号をネゲートする(例えば、“0”にする。)。これにより、システムバス108とI/Oコントローラ107とを接続する。さらに、起動レジスタ132の起動ビットをクリアする。

40

#### 【0053】

なお、ライト動作の場合、セクタバッファ104とI/Oコントローラ107との接続

50

が遮断されても、セクタバッファコントローラ 106 は、入出力ポート P1、P2 によるデータ転送を別々に起動しているので、入出力ポート P1 によるライトデータのセクタバッファ 104 への蓄積は続行される。

【0054】

システムバス 108 と I/O コントローラ 107 とが接続されると、CPU 101 は I/O コントローラ 107 にアクセスしてステータスチェックを行う（ステップ S7）。ステータスチェックが正常に終わると、CPU 101 は、全データの転送が終了したか否かを判断し、転送が完了した場合には起動レジスタ 131 の起動ビットをクリアし、転送処理を終了する（ステップ S8）。未転送分のデータがある場合には、起動レジスタ 132 の起動ビットを再びセットし、ステップ S5 からの処理を繰り返す。例えば、転送単位 512 バイトで、4096 バイトのデータを I/O デバイス 107a に転送したい場合、上記の処理を 8 回繰り返すことで転送が完了する。

【0055】

このように、第 1 の実施の形態の半導体装置 100 によれば、全データを転送し終わるまで、ステップ S4 で、DMA 転送要求信号を DMA コントローラ 103 に送出して DMA コントローラ 103 を 1 回だけ起動すればよいので、図 14 に示したような従来の転送処理よりもオーバーヘッドの少ない DMA 転送処理を、DMA インターフェースを搭載していない I/O コントローラ 107 を用いた場合でも実現できる。

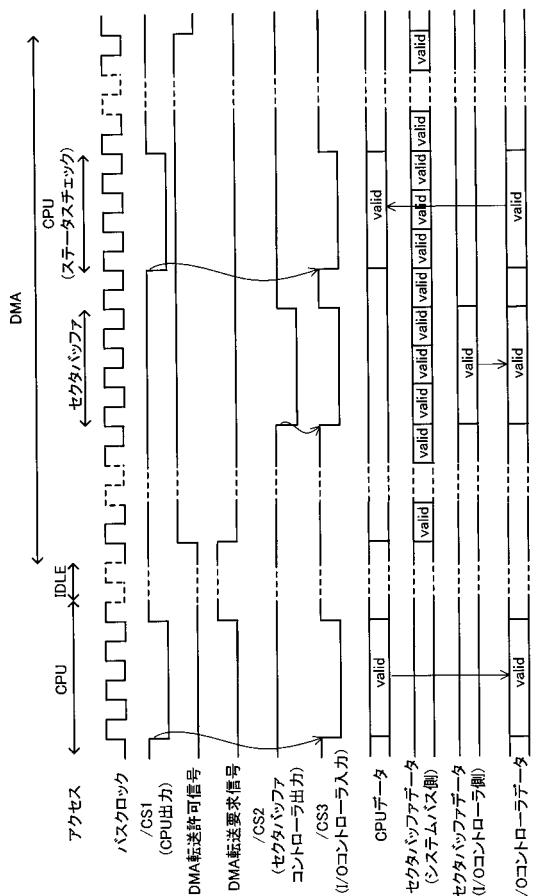

【0056】

次に、図 4 のような DMA 転送処理により、I/O デバイス 107a へデータをライトする際の信号の様子を、タイミングチャートで示す。

図 5 は、第 1 の実施の形態の半導体装置の転送処理時における信号の様子を示すタイミングチャートである。

【0057】

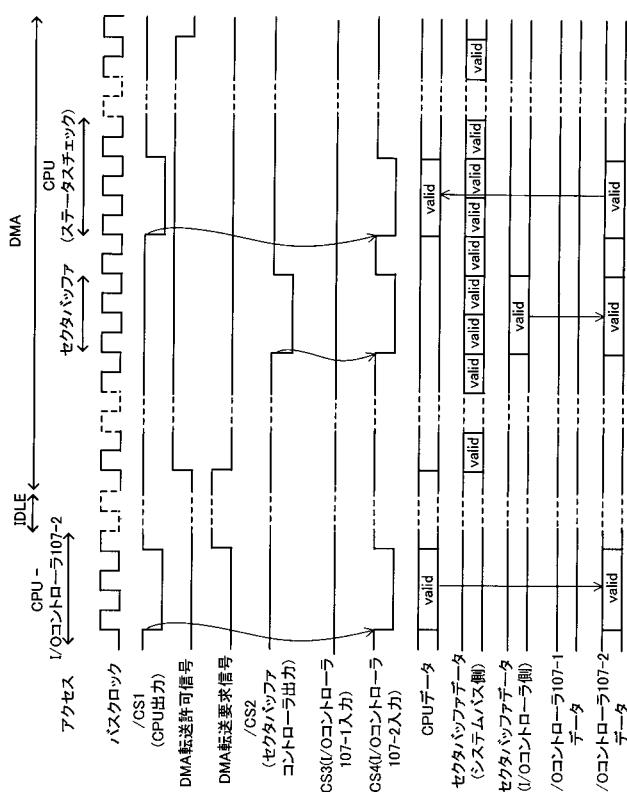

図 5 では、上から、システムバス 108 を伝わるバスロック、CPU 101 が出力するチップセレクト信号 / CS1、DMA コントローラ 103 が発行する DMA 転送許可信号、セクタバッファコントローラ 106 が DMA コントローラ 103 に伝える DMA 転送要求信号、セクタバッファコントローラ 106 が生成する制御信号であるチップセレクト信号 / CS2、I/O コントローラ 107 に入力されるチップセレクト信号 / CS3 を示している。さらに、CPU 101 のデータ、セクタバッファ 104 のシステムバス 108 側及び I/O コントローラ 107 側のデータ、I/O コントローラ 107 のデータを示している。

【0058】

なお、図 5 では、I/O コントローラ 107 のアクセスサイクルが 3 クロックサイクルである場合を示している。

まず、図 4 のステップ S1 の転送コマンド発行のために、CPU 101 による I/O コントローラ 107 へのアクセスが行われる。このとき、CPU 101 から出力されたチップセレクト信号 / CS1 が I/O コントローラ 107 のチップセレクト信号 / CS3 として使用され、CPU 101 からの発行されたコマンドが I/O コントローラ 107 に転送される。

【0059】

続いて、セクタバッファコントローラ 106 の起動レジスタ 131 に起動ビットがセットされると、DMA 転送要求信号がアサートされる。このとき、DMA コントローラ 103 が起動して DMA 転送許可信号がアサートされるまでアイドルサイクルとなる。

【0060】

DMA 許可信号がアサートされると、DMA コントローラ 103 から、システムバス 108 を介してセクタバッファ 104 にデータが転送される。このとき例えば、1 クロックサイクルあたりに 1 アドレス分のデータ転送を行う。

【0061】

続いて、起動レジスタ 132 がセットされると、セクタバッファコントローラ 106 は

10

20

30

40

50

、チップセレクト信号 / CS2 をアサートする（“L”となる。）。このとき、前述した切替部 105 の動作により、この制御信号が I/O コントローラ 107 に伝わり、チップセレクト信号 / CS3 もアサートされる。これによって、セクタバッファ 104 のデータが、入出力ポート P2 から切替部 105 を介して I/O コントローラ 107 に転送される。

#### 【0062】

転送単位のデータの転送が終わると、CPU101 は再びチップセレクト信号 / CS1 をアサートする。転送単位のデータの転送が完了している場合、切替部 105 は前述の動作により、システムバス 108 と I/O コントローラ 107 を接続するので、I/O コントローラ 107 のチップセレクト信号 / CS3 もアサートされる。これにより、CPU101 は、I/O コントローラ 107 にアクセスして、ステータスをリードすることで、ステータスチェックを行う。

#### 【0063】

全てのデータの転送が終わると、DMA コントローラ 103 は、DMA 転送許可信号をネゲートして転送処理を終了する。また、セクタバッファ 104 が一杯になった場合に、セクタバッファコントローラ 106 が、DMA コントローラ 103 に DMA 転送を停止させるための信号を送出するようにしてもよい。

#### 【0064】

第 1 の実施の形態の半導体装置 100 では、セクタバッファ 104 とシステムバス 108 側とのデータ転送と、I/O コントローラ 107 側とのデータ転送を、セクタバッファコントローラ 106 により別々に起動するので、図 5 のように、セクタバッファ 104 から I/O コントローラ 107 にデータ転送や、ステータスチェックを行っている最中にも、セクタバッファ 104 にデータを DMA 転送することができる。

#### 【0065】

また、図 13 で示したように、従来の半導体装置 500 では、PIO 転送のアクセスサイクルと、DMA 転送のアクセスサイクルとが同じであり、DMA 転送の転送効率は PIO 転送と同程度でしかなかったが、第 1 の実施の形態の半導体装置 500 では、システムバス 108 側のアクセスサイクルを、I/O コントローラ 107 側のアクセスサイクルに合わせる必要がないため、システムバス 108 のバス効率を向上させることができる。

#### 【0066】

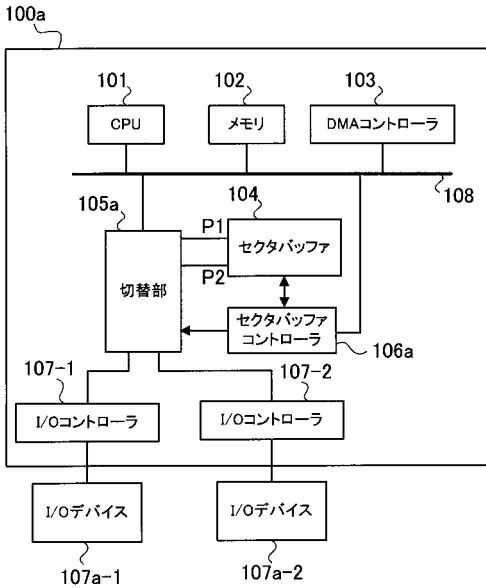

次に、第 2 の実施の形態の半導体装置を説明する。

図 6 は、第 2 の実施の形態の半導体装置の構成を示す図である。

図 1 で示した第 1 の実施の形態の半導体装置 100 と同一の構成要素については同一符号とし、説明を省略する。

#### 【0067】

第 2 の実施の形態の半導体装置 100a は、第 1 の実施の形態の半導体装置 100 と異なり、2 つの I/O デバイス 107a-1、107a-2 に対応した、I/O コントローラ 107-1、107-2 を有している。切替部 105a は、この 2 つの I/O コントローラ 107-1、107-2 とのデータ転送を切り替える必要があり、図 2 で示した第 1 の実施の形態の切替部 105 と異なっている。

#### 【0068】

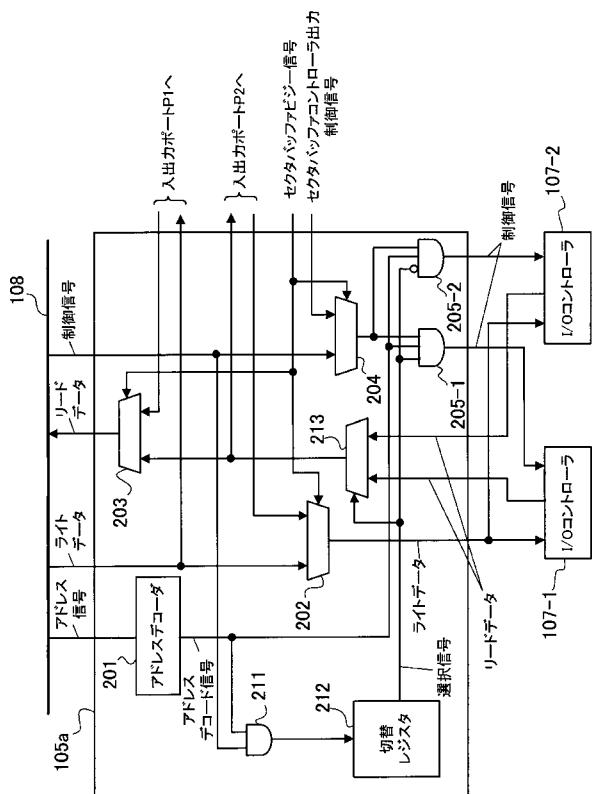

図 7 は、第 2 の実施の形態の半導体装置における切替部の一例の構成を示す図である。

なお、図 2 で示した第 1 の実施の形態の半導体装置 100 の切替部 105 と同様の構成要素については同一符号としている。

#### 【0069】

第 2 の実施の形態の半導体装置 100a の切替部 105a は、2 つの I/O コントローラ 107-1、107-2 に対応して、セレクタ 204 から出力される制御信号を 2 つの AND 回路 205-1、205-2 に入力している。また、図 2 の構成の他に、AND 回路 211、切替レジスタ 212、セレクタ 213 を有している。

#### 【0070】

10

20

30

40

50

AND回路211は、システムバス108からの制御信号（チップセレクト信号など）と、アドレスコード信号を入力して、2つのI/Oコントローラ107-1、107-2のいずれかを選択する情報を生成して切替レジスタ212に記憶する。

【0071】

切替レジスタ212は、記憶された情報をもとに、I/Oコントローラ107-1、107-2のいずれかを選択するための選択信号を出力する。

選択信号は、セレクタ213に入力される。そして、セレクタ213は、リード動作時に、I/Oコントローラ107-1、107-2のリードデータのいずれかを選択信号に応じて選択してセレクタ203に入力する。

【0072】

また、AND回路205-1にも選択信号が入力され、AND回路205-2には、反転された選択信号が入力される。これによって、選択されないI/Oコントローラ107-1、107-2には制御信号が入力されないようにしている。

【0073】

ところで、第2の実施の形態の半導体装置100aにおいて、2つのI/Oコントローラ107-1、107-2が異なるアクセスサイクルの場合には、セクタバッファコントローラ106aは、それぞれに応じたアクセスサイクルの制御信号やアドレス信号を生成する必要がある。

【0074】

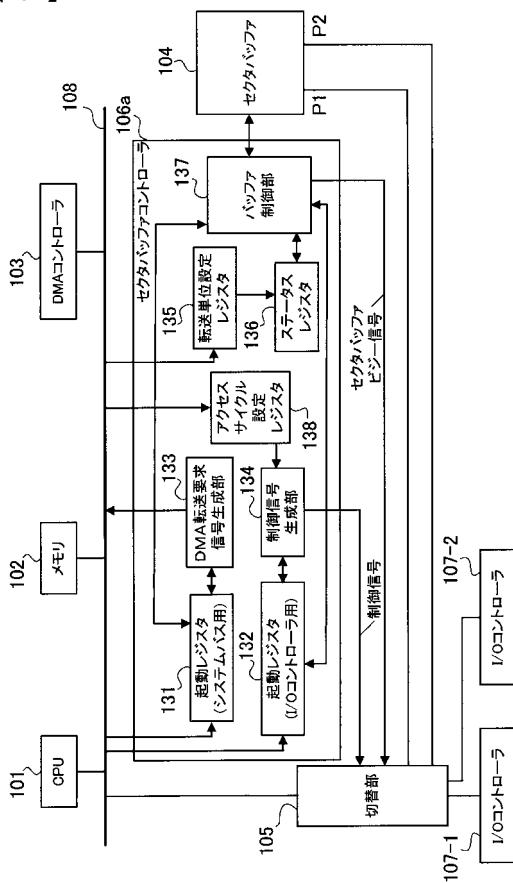

図8は、第2の実施の形態の半導体装置におけるセクタバッファコントローラの一例の構成を示す図である。

図3で示した第1の実施の形態の半導体装置100のセクタバッファコントローラ106と同様の構成要素については同一符号としている。

【0075】

第2の実施の形態の半導体装置100aのセクタバッファコントローラ106aは、アクセスサイクル設定レジスタ138を有している。ここには、システムバス108経由で、それぞれのI/Oコントローラ107-1、107-2に対応したアクセスサイクルが設定される。これによって、制御信号生成部134は、アクセスサイクル設定レジスタ138に設定されたアクセスサイクルで制御信号を生成する。また、アクセスサイクル設定レジスタ138に設定されたアクセスサイクルで、アドレス信号も同様に生成できるが、図示を省略している。

【0076】

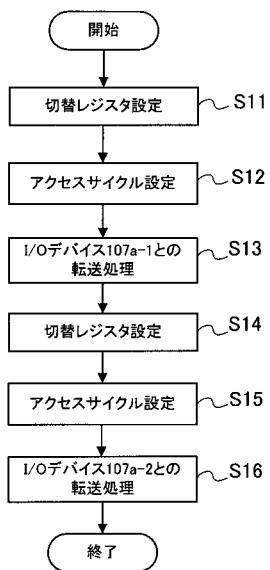

以下、第2の実施の形態の半導体装置100aの動作を説明する。

図9は、第2の実施の形態の半導体装置による転送処理を示すフローチャートである。

まず、切替部105aの切替レジスタ212に、例えば、“1”をセットする。これにより、AND回路205-1の出力は有効になり、AND回路205-2の出力は無効（“0”）となる。すなわち、I/Oコントローラ107-1のバスが有効になる（ステップS11）。

【0077】

次に、セクタバッファコントローラ106aのアクセスサイクル設定レジスタ138に、I/Oコントローラ107-1のアクセスサイクルを設定する（ステップS12）。

そして、図4で示したような転送処理で、I/Oデバイス107a-1との転送処理を行う（ステップS13）。

【0078】

I/Oデバイス107a-1との転送処理を終えると、今度は、切替レジスタ212に“0”をセットする。これにより、AND回路205-1の出力は無効になり、AND回路205-2の出力が有効となる。すなわち、I/Oコントローラ107-2のバスが有効になる（ステップS14）。

【0079】

次に、セクタバッファコントローラ106aのアクセスサイクル設定レジスタ138に

10

20

30

40

50

、 I / O コントローラ 107 - 2 のアクセスサイクルを設定する（ステップ S15）。

そして、図 4 で示したような転送処理で、I / O デバイス 107a - 2 との転送処理を行う（ステップ S16）。

#### 【0080】

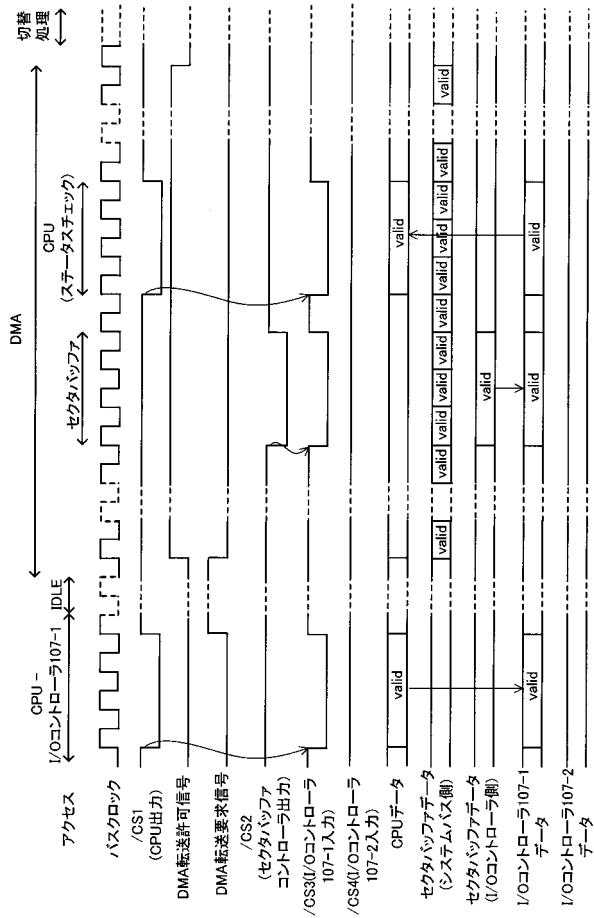

次に、図 9 のような DMA 転送処理により、I / O デバイス 107a - 1、107a - 2 へデータをライトする際の信号の様子を、タイミングチャートで示す。

図 10、図 11 は、第 2 の実施の形態の半導体装置の転送処理時における信号の様子を示すタイミングチャートである。

#### 【0081】

図 10、図 11 では、上から、システムバス 108 を伝わるバスクロック、CPU101 10 が output するチップセレクト信号 / CS1、DMA コントローラ 103 が発行する DMA 転送許可信号、セクタバッファコントローラ 106 が DMA コントローラ 103 に伝える DMA 転送要求信号、セクタバッファコントローラ 106 が生成する制御信号であるチップセレクト信号 / CS2、I / O コントローラ 107 - 1 に入力されるチップセレクト信号 / CS3、I / O コントローラ 107 - 2 に入力されるチップセレクト信号 / CS4 を示している。さらに、CPU101 のデータ、セクタバッファ 104 のシステムバス 108 側及び I / O コントローラ 107 - 1、107 - 2 側のデータ、I / O コントローラ 107 - 1、107 - 2 のデータを示している。

#### 【0082】

なお、I / O コントローラ 107 - 1 のアクセスサイクルが 3 クロックサイクル、I / O コントローラ 107 - 2 のアクセスサイクルが 2 クロックサイクルである場合を示している。

#### 【0083】

まず、始めに切替部 105a によって、I / O コントローラ 107 - 1 のパスが有効になっており、セクタバッファコントローラ 106a のアクセスサイクル設定レジスタ 138 には、I / O コントローラ 107 - 1 のアクセスサイクルである 3 クロックサイクルが設定されているとする。

#### 【0084】

これにより、図 5 で示したタイミングチャートと同様に、CPU101 による 3 クロックサイクルのチップセレクト信号 / CS1 を I / O コントローラ 107 - 1 のチップセレクト信号 / CS3 として入力し、I / O コントローラ 107 - 1 への転送コマンド発行を行う。その後、1 クロックサイクルでの DMA 転送を開始する。

#### 【0085】

セクタバッファコントローラ 106a で生成される 3 クロックサイクルのチップセレクト信号 / CS2 がアサートすると、セクタバッファ 104 に蓄積されたデータが、入出力ポート P2 から切替部 105a を介して I / O コントローラ 107 - 1 に転送される。

#### 【0086】

転送単位のデータの転送が終わると、CPU101 は再びチップセレクト信号 / CS1 をアサートすることで、I / O コントローラ 107 - 1 のチップセレクト信号 / CS3 をアサートする。これにより、CPU101 は、I / O コントローラ 107 - 1 にアクセスして、ステータスをリードすることで、ステータスチェックを行う。

#### 【0087】

その後、切替処理を行う。ここでは、切替部 105a の切替レジスタ 212 を設定して、I / O コントローラ 107 - 2 のパスを有効にする。さらに、セクタバッファコントローラ 106a のアクセスサイクル設定レジスタ 138 に、I / O コントローラ 107 - 2 のアクセスサイクルである、2 クロックサイクルを設定する。

#### 【0088】

その後、図 11 に示すように、CPU101 による 2 クロックサイクルのチップセレクト信号 / CS1 を I / O コントローラ 107 - 2 のチップセレクト信号 / CS4 として入力し、I / O コントローラ 107 - 2 への転送コマンド発行を行う。その後、同様に 1 クロ

ロックサイクルでのDMA転送を開始する。

【0089】

セクタバッファコントローラ106aで生成される2クロックサイクルのチップセレクト信号/CS2がアサートすると、セクタバッファ104に蓄積されたデータが、入出力ポートP2から切替部105aを介してI/Oコントローラ107-2に転送される。

【0090】

転送単位のデータが終わると、CPU101は再びチップセレクト信号/CS1をアサートすることで、I/Oコントローラ107-2のチップセレクト信号/CS4をアサートする。これにより、CPU101は、I/Oコントローラ107-2にアクセスして、ステータスをリードすることで、ステータスチェックを行う。

10

【0091】

全てのデータの転送が終わると、DMAコントローラ103は、DMA転送許可信号をネゲートして転送処理を終了する。また、セクタバッファ104が一杯になった場合に、セクタバッファコントローラ106aが、DMAコントローラ103にDMA転送を停止させるための信号を送出するようにしてもよい。

【0092】

このように、第2の実施の形態の半導体装置100aでは、異なるアクセスサイクルのI/Oコントローラ107-1、107-2が混在しても、第1の実施の形態の半導体装置100と同様に、効率のよい転送処理が可能となる。また、1つのセクタバッファ104を2つのI/Oコントローラ107-1、107-2で共有することができるため、コストパフォーマンスの向上が期待できる。

20

【0093】

なお、上記の第2の実施の形態の半導体装置100aでは、I/Oコントローラ107-1、107-2が2つの場合について示したが、3つ以上のI/Oコントローラを切替部で切り替えるようにしてもよい。また、それに対応してアクセスサイクルも3以上設定するようにしてもよい。

30

【0094】

また、上記のアクセスサイクル設定レジスタ138は、図3で示した第1の実施の形態の半導体装置100におけるセクタバッファコントローラ106に搭載するようにしてもよい。

【図面の簡単な説明】

【0095】

【図1】第1の実施の形態の半導体装置の構成を示す図である。

【図2】第1の実施の形態の半導体装置における切替部の一例の回路構成図である。

【図3】第1の実施の形態の半導体装置におけるセクタバッファコントローラの一例の構成を示す図である。

【図4】第1の実施の形態の半導体装置による転送処理を示すフローチャートである。

【図5】第1の実施の形態の半導体装置の転送処理時における信号の様子を示すタイミングチャートである。

【図6】第2の実施の形態の半導体装置の構成を示す図である。

40

【図7】第2の実施の形態の半導体装置における切替部の一例の構成を示す図である。

【図8】第2の実施の形態の半導体装置におけるセクタバッファコントローラの一例の構成を示す図である。

【図9】第2の実施の形態の半導体装置による転送処理を示すフローチャートである。

【図10】第2の実施の形態の半導体装置の転送処理時における信号の様子を示すタイミングチャートである（その1）。

【図11】第2の実施の形態の半導体装置の転送処理時における信号の様子を示すタイミングチャートである（その2）。

【図12】DMAインターフェースを持たないI/Oデバイスとの間でDMA転送を行う従来の半導体装置の構成を示す図である。

50

【図13】従来の半導体装置のデータ転送時の信号の様子を示すタイミングチャートである。

【図14】従来の半導体装置によるメモリカードへのDMA転送時の動作を示すフローチャートである。

【符号の説明】

【0096】

100 半導体装置

101 CPU

102 メモリ

103 DMAコントローラ

10

104 セクタバッファ

105 切替部

106 セクタバッファコントローラ

107 I/Oコントローラ

107a I/Oデバイス

108 システムバス

P1、P2 入出力ポート

【図1】

【図2】

【図3】

【 図 4 】

【図5】

【 四 6 】

【 図 7 】

【 図 8 】

【図9】

【 図 1 0 】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】