(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5551739号

(P5551739)

(45) 発行日 平成26年7月16日(2014.7.16)

(24) 登録日 平成26年5月30日(2014.5.30)

(51) Int.Cl.

**G 1 1 B 20/18 (2006.01)**

F 1

|         |       |         |

|---------|-------|---------|

| G 1 1 B | 20/18 | 5 5 0 C |

| G 1 1 B | 20/18 | 5 3 4 Z |

| G 1 1 B | 20/18 | 5 7 2 B |

| G 1 1 B | 20/18 | 5 7 2 F |

請求項の数 20 (全 26 頁)

(21) 出願番号 特願2012-171640 (P2012-171640)

(22) 出願日 平成24年8月2日 (2012.8.2)

(65) 公開番号 特開2013-80550 (P2013-80550A)

(43) 公開日 平成25年5月2日 (2013.5.2)

審査請求日 平成25年7月29日 (2013.7.29)

(31) 優先権主張番号 13/251,340

(32) 優先日 平成23年10月3日 (2011.10.3)

(33) 優先権主張国 米国 (US)

早期審査対象出願

前置審査

(73) 特許権者 508243639

エルエスアイ コーポレーション

アメリカ合衆国カリフォルニア州9513

1, サンノゼ, リッダー・パーク・ドライ

ヴ 1320

(74) 代理人 100088904

弁理士 庄司 隆

(72) 発明者 シア, ハイタオ

アメリカ合衆国, カリフォルニア 950

35, サンタ クララ, ユニット 369

, 1760 ハルフォード アヴェニュー

(72) 発明者 ヤン, シャオファ

アメリカ合衆国, カリフォルニア 951

29, サンノゼ, 1477 エルカ エー

ヴィイー.

最終頁に続く

(54) 【発明の名称】効率的なパラメーター修正のためのシステム及び方法

## (57) 【特許請求の範囲】

## 【請求項 1】

データ処理システムであって、

復号化出力によって得られた第1のデータセットにデータ検出アルゴリズムを適用して、データ検出器出力を得るように動作可能なデータ検出器回路と、

第2のデータセットにデータ復号化アルゴリズムを適用して、復号化出力を得るように動作可能なデータ復号化器回路であって、該第2のデータセットは該第1のデータセットから取り出される、データ復号化器回路と、

該復号化出力から取り出された第3のデータセットと該第1のデータセットとからなる群から選択されたデータセットのデータ検出器出力に少なくとも部分的に基づいてエラーレートを計算するように動作可能な信頼性モニター回路と、

パラメーター修正制御回路であって、

該パラメータは、データ検出器回路又はデータ複合化器回路の一つの動作を支配するものであって、該パラメータの値は所定量ずつ変化させて得られる連続する3つのものではなく、

パラメーターの第1の値を選択して該第1の値に対応する該エラーレートの第1のインスタンスを格納し、

該パラメーターの第2の値を選択して該第2の値に対応するエラーレートの第2のインスタンスを格納し、なお、該第2の値を選択することは、該第1の値に少なくとも部分的に基づいて検索方向を確定することと、検索方向とステップサイズとを用いることを含

10

20

み、該第2の値を計算する、

該エラーレートの該第1のインスタンスと該エラーレートの該第2のインスタンスとの比較に少なくとも部分的に基づいて、該第1の値及び該第2の値のうちの一方を選択する、

ように動作可能なパラメーター修正制御回路と、

を備える、データ処理システム。

【請求項2】

エラーレートを計算することは、該第3のデータセットを既知データセットと比較することを含む、請求項1に記載のデータ処理システム。

【請求項3】

第3のデータセットは、硬判定出力のセットである、請求項2に記載のデータ処理システム。

【請求項4】

データ検出アルゴリズムは、最大事後データ検出アルゴリズムとビタビ検出アルゴリズムとからなる群から選択される、請求項1に記載のデータ処理システム。

【請求項5】

データ復号化アルゴリズムは、低密度パリティチェックアルゴリズムである、請求項3に記載のデータ処理システム。

【請求項6】

出力は、該復号化出力から取り出された該第3のデータセットであり、該信頼性モニタ一回路は、

該第3のデータセットのインスタンスを既知データセットと比較するように動作可能な比較器回路と、

該第3のデータセットのインスタンスが該既知データセットの対応するインスタンスと等しくない場合には、インクリメントして該エラーレートを得るように動作可能なカウンター回路と、

を備える、請求項1に記載のデータ処理システム。

【請求項7】

出力は該第1のデータセットであり、該第1のデータセットは軟データを含み、該信頼性モニタ一回路は、

該軟データのインスタンスをしきい値と比較するように動作可能な比較器回路と、

該軟データのインスタンスが該しきい値未満である場合には、インクリメントして該エラーレートを得るように動作可能なカウンター回路と、

を備える、請求項1に記載のデータ処理システム。

【請求項8】

しきい値はプログラマブルである、請求項7に記載のデータ処理システム。

【請求項9】

ステップサイズはプログラマブルである、請求項1に記載のデータ処理システム。

【請求項10】

データ処理システムは、ストレージデバイスと受信デバイスとからなる群から選択されるデバイスの一部として実装される、請求項1に記載のデータ処理システム。

【請求項11】

データ処理システムは、集積回路の一部として実装される、請求項1に記載のデータ処理システム。

【請求項12】

データ処理のための方法であって、

データ検出器回路を用いてデータ検出アルゴリズムを第1のデータセットに対して実行し、データ検出器出力を得ることと、

データ復号化器回路を用いてデータ復号化アルゴリズムを、該第1のデータセットから取り出された第2のデータセットに対して実行し、復号化出力を得ることと、

10

20

30

40

50

該復号化出力から取り出された第3のデータセットと該第1のデータセットとからなる群から選択されたデータセットのデータ検出器出力に少なくとも部分的に基づいてエラーレートを計算することと、

該パラメータは、データ検出器回路又はデータ複合化器回路の一つの動作を支配するものであって、該パラメータの値は所定量ずつ変化させて得られる連続する3つのものではなく、

パラメーターの第1の値を選択して該第1の値に対応する該エラーレートの第1のインスタンスを格納することと、

該パラメーターの第2の値を選択して該第2の値に対応するエラーレートの第2のインスタンスを格納することと、ここで該第2の値を選択することは、該第1の値に少なくとも部分的に基づいて検索方向を確定することと、検索方向とステップサイズとを用いることであって、該第2の値を計算する。10

該エラーレートの該第1のインスタンスと該エラーレートの該第2のインスタンスとの比較に少なくとも部分的に基づいて、該第1の値及び該第2の値のうちの一方を選択することと、

を含む、データ処理のための方法。

【請求項13】

出力は、該復号化出力から取り出された該第3のデータセットであり、該エラーレートを計算することは、

該第3のデータセットのインスタンスを既知データセットと比較することと、20

該既知データセットの対応するインスタンスと等しくない該第3のデータセットのインスタンスの数をカウントすることであって、該エラーレートを得る、カウントすることと、

を含む、請求項12に記載の方法。

【請求項14】

出力は該第1のデータセットであり、該第1のデータセットは軟データを含み、該エラーレートを計算することは、

該軟データのインスタンスをしきい値と比較することと、

該しきい値未満の該軟データのインスタンスの数をカウントすることであって、該エラーレートを得る、カウントすることと、30

を含む、請求項12に記載の方法。

【請求項15】

しきい値はプログラマブルである、請求項14に記載の方法。

【請求項16】

第3のデータセットは硬判定出力のセットである、請求項12に記載の方法。

【請求項17】

ステップサイズはプログラマブルである、請求項12に記載の方法。

【請求項18】

ストレージデバイスであって、

ストレージ媒体と、40

該ストレージ媒体に対して配置され、該ストレージ媒体上の情報に対応する検知された信号を与えるように動作可能なヘッドアセンブリと、

読み取りチャネル回路であって、

該検知された信号から取り出されたアナログ信号をサンプリングして一連のデジタルサンプルを得るように動作可能なアナログ/デジタル変換器回路と、

該デジタルサンプルを等化して第1のデータセットを得るように動作可能な等化器回路と、

データ検出アルゴリズムを該第1のデータセットに適用するように動作可能なデータ検出器回路と、

データ復号化アルゴリズムを第2のデータセットに適用して復号化出力を得るように50

動作可能なデータ復号化器回路であって、該第2のデータセットは、該第1のデータセットから取り出される、データ復号化器回路と、

該復号化出力から取り出された第3のデータセットと該第1のデータセットとからなる群から選択されたデータセットのデータ検出器出力に少なくとも部分的に基づいてエラーレートを計算するように動作可能な信頼性モニター回路と、

パラメーター修正制御回路であって、

該パラメータは、データ検出器回路又はデータ複合化器回路の一つの動作を支配するものであって、該パラメータの値は所定量ずつ変化させて得られる連続する3つのものではなく、

パラメーターの第1の値を選択して該第1の値に対応する該エラーレートの第1のインスタンスを格納し、10

該パラメーターの第2の値を選択して該第2の値に対応するエラーレートの第2のインスタンスを格納し、なお、該第2の値を選択することは、該第1の値に少なくとも部分的に基づいて検索方向を確定することと、検索方向とステップサイズとを用いることであって、該第2の値を計算する、

該エラーレートの該第1のインスタンスと該エラーレートの該第2のインスタンスとの比較に少なくとも部分的に基づいて、該第1の値及び該第2の値のうちの一方を選択する、

ようすに動作可能なパラメーター修正制御回路と、20

を備える、読み取りチャネル回路と、

を備える、ストレージデバイス。

#### 【請求項19】

出力は、該復号化出力から取り出された該第3のデータセットであり、該信頼性モニタ回路は、

該第3のデータセットのインスタンスを既知データセットと比較するように動作可能な比較器回路と、

該第3のデータセットのインスタンスが該既知データセットの対応するインスタンスと等しくない場合には、インクリメントして該エラーレートを得るように動作可能なカウンタ回路と、

を備える、請求項18に記載のストレージデバイス。30

#### 【請求項20】

出力は該第1のデータセットであり、該第1のデータセットは軟データを含み、該信頼性モニタ回路は、

該軟データのインスタンスをしきい値と比較するように動作可能な比較器回路と、

該軟データのインスタンスが該しきい値未満である場合には、インクリメントして該エラーレートを得るように動作可能なカウンタ回路と、

を備える、請求項18に記載のストレージデバイス。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、システム特徴付けのためのシステム及び方法に関し、より詳細には、データ処理システムを調節するためのシステム及び方法に関する。

##### 【背景技術】

##### 【0002】

様々なストレージシステムが、処理性能を改善するために調節することができる1つ又は複数の修正可能な変数を用いて実施されるデータ処理回路部を備える。幾つかの場合には、既知データパターンがデータ処理回路部に与えられ、修正可能な変数のうちの1つ又は複数が変更されている間、データ処理回路部のエラーレートが監視される。このプロセスは、修正可能な変数の許容可能な値が特定されるまで続けられる。そのような手法は、ストレージエリアを既知パターンに利用し、したがって、使用可能なストレージエリアを40

50

減少させ、意味のあるエラーレートを取得するには、かなりの時間をする可能性があり、これによって、ストレージシステムの製造コストが増大する。

#### 【0003】

したがって、少なくとも上述した理由により、データ処理のための先進的なシステム及び方法が当該技術分野において必要とされている。

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0004】

#### 【課題を解決するための手段】

10

#### 【0005】

本発明は、システム特徴付けのためのシステム及び方法に関し、より詳細には、データ処理システムを調節するためのシステム及び方法に関する。

#### 【0006】

本発明の1つ又は複数の実施の形態は、データ検出器回路と、データ復号化器回路と、信頼性モニター回路と、パラメーター修正制御回路とを備えるデータ処理システムを提供する。データ検出器回路は、復号化出力によって誘導される(guided)第1のデータセットにデータ検出アルゴリズムを適用して、検出出力を得るように動作可能である。データ復号化器回路は、第2のデータセットにデータ復号化アルゴリズムを適用して、復号化出力を得るように動作可能である。第2のデータセットは、第1のデータセットから取り出される。信頼性モニター回路は、エラーレートを計算するように動作可能である。エラーレートは、復号化出力又は第1のデータセットから取り出された第3のデータセットに少なくとも部分的に基づいて計算することができる。パラメーター修正回路は、パラメーターの第1の値を選択して該第1の値に対応するエラーレートの第1のインスタンスを格納し、パラメーターの第2の値を選択して該第2の値に対応するエラーレートの第2のインスタンスを格納し、エラーレートの第1のインスタンスとエラーレートの第2のインスタンスとの比較に少なくとも部分的に基づいて、第1の値及び第2の値のうちの一方を選択するように動作可能である。第2の値を選択することは、第1の値に少なくとも部分的に基づいて検索方向を確定することと、検索方向とステップサイズとを用いて、第2の値を計算する、こととを含む。幾つかの場合には、ステップサイズはプログラマブルである。実施の形態は、複数の異なるエンドデバイス又はエンドシステムにおいて実施することができる。例えば、実施の形態は、ストレージデバイス又は受信デバイスにおいて実施することができる。さらに、幾つかの場合には、データ処理システムは、集積回路の一部として実施することができる。

20

#### 【0007】

上述した実施の形態の幾つかの場合には、エラーレートを計算することは、第3のデータセットを既知データセットと比較することを含む。そのような幾つかの場合には、第3のデータセットは硬判定出力のセットである。データ検出アルゴリズムは、最大事後データ検出アルゴリズム又はビタビ検出アルゴリズムとすることができますが、これらに限定されるものではない。幾つかの場合には、データ復号化アルゴリズムは低密度パリティチェックアルゴリズムである。特定の場合には、出力は、復号化出力から取り出された第3のデータセットである。そのような場合には、信頼性モニター回路は、第3のデータセットのインスタンスを既知データセットと比較するように動作可能な比較器回路と、第3のデータセットのインスタンスが既知データセットの対応するインスタンスと等しくない場合には、インクリメントしてエラーレートを得るように動作可能なカウンター回路とを備えることができる。幾つかの場合には、出力は、軟データを含む第1のデータセットである。そのような場合には、信頼性モニター回路は、軟データのインスタンスをしきい値と比較するように動作可能な比較器回路と、軟データのインスタンスがしきい値未満である場合には、インクリメントしてエラーレートを得るように動作可能なカウンター回路とを備えることができる。特定の場合には、しきい値はプログラマブルである。

30

40

50

**【0008】**

本発明の幾つかの実施の形態は、データ処理のための方法を提供する。本方法は、データ検出器回路を用いてデータ検出アルゴリズムを第1のデータセットに対して実行することであって、検出出力を得る、実行することと、データ復号化器回路を用いてデータ復号化アルゴリズムを、第1のデータセットから取り出された第2のデータセットに対して実行することであって、復号化出力を得る、実行することと、該復号化出力から取り出された第3のデータセット又は第1のデータセットのうちの一方に少なくとも部分的に基づいてエラーレートを計算することと、パラメーターの第1の値を選択して該第1の値に対応する該エラーレートの第1のインスタンスを格納することと、パラメーターの第2の値を選択して該第2の値に対応するエラーレートの第2のインスタンスを格納することと、エラーレートの第1のインスタンスとエラーレートの第2のインスタンスとの比較に少なくとも部分的に基づいて、第1の値及び第2の値のうちの一方を選択することとを含む。第2の値を選択することは、第1の値に少なくとも部分的に基づいて検索方向を確定することと、検索方向とステップサイズとを用いて、第2の値を計算する、ことを含む。幾つかの場合には、第3のデータセットは、ハード判定出力のセットである。様々な場合には、ステップサイズはプログラマブルである。

10

**【0009】**

幾つかの場合には、出力は、復号化出力から取り出された第3のデータセットである。そのような幾つかの場合には、エラーレートを計算することは、第3のデータセットのインスタンスを既知データセットと比較することと、該既知データセットの対応するインスタンスと等しくない該第3のデータセットのインスタンスの数をカウントすることであって、エラーレートを得る、カウントすることとを含む。他の場合には、出力は、軟データを含む第1のデータセットである。そのような幾つかの場合には、エラーレートを計算することは、軟データのインスタンスをしきい値と比較することと、しきい値未満の軟データのインスタンスの数をカウントすることであって、エラーレートを得る、カウントすることとを含む。特定の場合には、しきい値はプログラマブルである。

20

**【0010】**

本発明の様々な実施の形態は、データ検出器回路と信頼性モニター回路とを備えるデータ処理システムを提供する。データ検出器回路は、データセットにデータ検出アルゴリズムを適用して、軟データを含む検出出力を得るように動作可能である。信頼性モニター回路は、軟データに少なくとも部分的に基づいてプロキシエラーカウントを確定し、該プロキシエラーカウントに少なくとも部分的に基づいてデータ処理システムの動作を統御するパラメーターを修正するように動作可能である。幾つかの場合には、本発明の上述した実施の形態は、ストレージデバイス又は受信デバイスの一部として実施される。幾つかの場合には、本発明の上述した実施の形態は、集積回路の一部として実施される。

30

**【0011】**

上述した実施の形態の幾つかの場合には、データ検出アルゴリズムは最大事後データ検出アルゴリズムである。他の場合には、データ検出アルゴリズムはビタビ検出アルゴリズムである。幾つかの場合には、データ処理システムは、検出出力から取り出されたものにデータ復号化アルゴリズムを適用して、復号化出力を得るように動作可能なデータ復号化器回路を更に備える。幾つかの場合には、データ復号化アルゴリズムは低密度パリティチェックアルゴリズムである。

40

**【0012】**

幾つかの場合には、信頼性モニター回路は、軟データのインスタンスをしきい値と比較するように動作可能な比較器回路と、軟データのインスタンスがしきい値未満である場合には、インクリメントしてプロキシエラーカウントを得るように動作可能なカウンター回路とを備える。そのような幾つかの場合には、しきい値はプログラマブルである。そのような場合の変形形態では、信頼性モニター回路は、パラメーターの第1の値を選択して該第1の値に対応するプロキシエラーカウントの第1のインスタンスを格納し、パラメーターの第2の値を選択して第1の値に対応するプロキシエラーカウントの第2のインスタン

50

スを格納し、プロキシエラーカウントの第1のインスタンスとプロキシエラーカウントの第2のインスタンスとの比較に少なくとも部分的に基づいての第1の値及び第2の値のうちの一方を選択するように動作可能なパラメーター修正制御回路を更に備える。幾つかの特定の場合には、パラメーターの第2の値を選択することは、第1の値に少なくとも部分的に基づいて検索方向を確定することと、検索方向とステップサイズとを用いて、第2の値を計算する、ことを含む。幾つかの場合には、ステップサイズはプログラマブルである。他の場合には、パラメーターの第1の値を選択することは、検索される複数の値のうちの1つを選択することを含み、パラメーターの第2の値を選択することは、検索される複数の値のうちの別のものを選択することを含む。

## 【0013】

10

本発明の他の実施の形態は、データ処理のための方法であって、データ検出器回路を用いてデータ検出アルゴリズムをデータセットに対して実行することであって、軟データを含む検出出力を得る、実行することと、軟データのインスタンスをしきい値と比較することと、該軟データのインスタンスとしきい値との比較に少なくとも部分的に基づいてプロキシエラーカウント値を修正することと、プロキシエラーカウントに少なくとも部分的に基づいてパラメーター値を選択することであって、該パラメーター値は、データ処理回路の動作を統御する、選択することと、を含む、データ処理のための方法を提供する。上述した実施の形態の幾つかの場合には、データセットは、既知データパターン又は未知データパターンとすることができるデータのパターンを含む。

## 【0014】

20

上述した実施の形態の幾つかの場合には、検出出力は第1の検出出力であり、軟データは第1の軟データであり、パラメーター値は第1のパラメーター値であり、プロキシエラーカウントは第1のプロキシエラーカウントであり、データセットは第1のデータセットである。そのような場合には、本方法は、データ検出アルゴリズムを第2のデータセットに対して実行することであって、第2の軟データを含む第2の検出出力を得る、実行することと、第2の軟データのインスタンスをしきい値と比較することと、第2の軟データのインスタンスとしきい値との比較に少なくとも部分的に基づいて第2のプロキシエラーカウント値を修正することと、第1のプロキシエラーカウントを第2のプロキシエラーカウントと比較することとを更に含むことができる。そのような場合には、第1のパラメーター値を選択することは、第1のプロキシエラーカウントと第2のプロキシエラーカウントとの比較に基づく。幾つかの場合には、第1のパラメーター値は、データ処理回路に適用される一方、データ検出器回路は、データ検出アルゴリズムを第1のデータセットに適用し、第2のパラメーター値は、データ処理回路に適用される一方、データ検出器回路は、データ検出アルゴリズムを第2のデータセットに適用する。

30

## 【0015】

この概要は、本発明の幾つかの実施の形態の概略のみを提供するものである。本発明の多くの他の目的、特徴、利点及び他の実施の形態は、以下の詳細な説明、添付の特許請求の範囲及び添付の図面からより完全に明らかとなるであろう。

## 【0016】

40

図面を参照することにより、本発明の様々な実施形態の更なる理解を実現することができ、これらの実施形態については明細書の残りの部分で説明する。図面において、同様の参照符号がいくつかの図面の全てにわたって類似の構成要素を指すのに用いられている。幾つかの場合には、小文字からなるサブラベルが、複数の類似の構成要素のうちの1つを表すように参照符号に関連付けられている。存在するサブラベルを指定することなく参照符号が参照されるとき、そのような複数の類似の構成要素全てを指すことが意図される。

## 【図面の簡単な説明】

## 【0017】

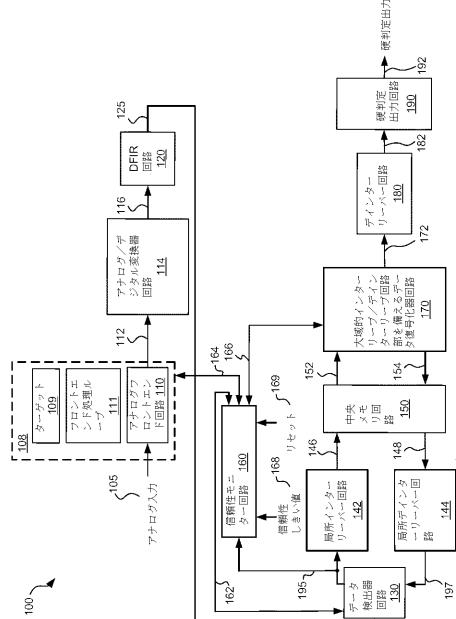

【図1】本発明の1つ又は複数の実施形態による信頼性データに基づく調節回路部を備えるデータ処理回路を示す図である。

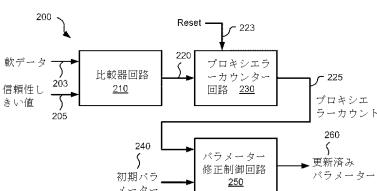

【図2】本発明の幾つかの実施形態による信頼性に基づく調節回路の1つの実施態様を示

50

す図である。

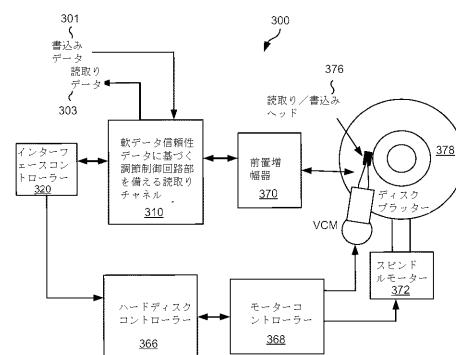

【図3】本発明の1つ又は複数の実施形態による軟データに基づく調節回路部を有する読み取りチャネルを備えるストレージデバイスを示す図である。

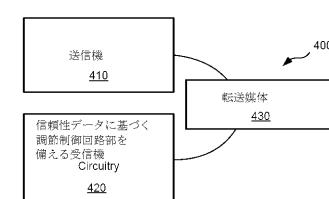

【図4】本発明の幾つかの実施形態による軟データに基づく調節回路部を有する受信機を備えるデータ伝送システムを示す図である。

【図5】本発明の様々な実施形態による信頼性に基づくパラメーター調節のための方法を示す流れ図である。

【図6】本発明の様々な実施形態による信頼性に基づくパラメーター調節のための方法を示す流れ図である。

【図7】本発明の幾つかの実施形態による信頼性に基づくパラメーター調節のための別10

の方法を示す流れ図である。

【図8】本発明の1つ又は複数の実施形態によるストリームライン検索を有する既知データに基づく調節回路部を備えるデータ処理回路を示す図である。

【発明を実施するための形態】

【0018】

本発明は、システム特徴付けのためのシステム及び方法に関し、より詳細には、データ処理システムを調節するためのシステム及び方法に関する。

【0019】

本発明の様々な実施形態は、任意の利用可能なデータセットから生成された信頼性データを用いてデータ処理回路を調節及び／又はテストするためのシステム及び方法を提供する。信頼性データは、規定された既知データセット又は未知のユーザーデータセットを含む任意の利用可能なデータセットから取り出すことができる。幾つかの場合には、調節は、データ処理回路を調節するのに用いられる時間が削減されるように様々なチャネルパラメーターを調節するメトリックの使用を考慮に入れる。本発明の1つ又は複数の実施形態は、既知データパターンを維持するのに必要とされるストレージエリアを削減するという利点を提供し、かつ／又はテスト時間及び／若しくは調節時間の削減を可能にする。

【0020】

図1を参照すると、データ処理回路100が示されている。データ処理回路100は、検出器出力195の一部として含まれる軟データを監視して、監視した軟データに基づいて1つ又は複数のパラメーターを修正するように動作可能な信頼性モニター回路160を備える。データ処理回路100はアナログ処理回路108を備える。アナログ処理回路108は、アナログフロントエンド回路110と、タイミング及び制御をアナログフロントエンド回路110に与えるように動作可能なフロントエンド処理ループ111と、ターゲットに基づくフィルタリングフィードバックをアナログフロントエンド回路110に与えるように動作可能なターゲット回路109とを備える。アナログフロントエンド回路110には、当該技術分野において知られているようなアナログフィルター及び増幅器回路が含まれ得るが、これらに限定されるものではない。本明細書において提供される開示に基づくと、当業者であれば、アナログフロントエンド回路110の一部として含めることができる種々の回路部を認識するであろう。幾つかの場合には、アナログフロント回路110の一部として含まれる可変利得増幅器の利得を修正可能とすることができる、アナログフロントエンド回路110に含まれるアナログフィルターの遮断周波数及びブーストを修正可能とすることができます。フロントエンド処理ループ111は、当該技術分野において知られているアナログフロントエンド回路110のタイミングを与えるように動作可能な任意の処理ループとすることができます。幾つかの場合には、そのようなフロントエンド処理ループ111は、修正可能とすることができますDCループオフセットを含む。ターゲット回路109は、当該技術分野において知られている任意の、ターゲットに基づくフィルター回路とすることができます。様々な場合において、ターゲット回路109によって用いられるターゲットは修正可能とすることができます。本明細書において提供される開示に基づくと、当業者であれば、本発明の異なる実施形態に関して用いることができる種々の、ターゲットに基づくフィルター回路及びフロントエンド処理ループを認識するであろう。

10

20

30

40

50

## 【0021】

アナログフロントエンド回路110は、アナログ信号105を受信する。アナログフロントエンド回路110は、アナログ信号105を処理し、処理済みのアナログ信号112をアナログ／デジタル変換器回路114に与える。幾つかの場合には、アナログ信号105は、ストレージ媒体（図示せず）に対して配置される読み取り／書き込みヘッドアセンブリ（図示せず）から取り出される。他の場合には、アナログ信号105は、伝送媒体（図示せず）からの信号を受信するように動作可能な受信機回路（図示せず）から取り出される。伝送媒体は、有線又は無線とすることができます。本明細書において提供される開示に基づくと、当業者であれば、アナログ入力105を取り出すことができる種々の信号源を認識するであろう。

10

## 【0022】

アナログ／デジタル変換器回路114は、処理済みのアナログ信号112を対応する一連のデジタルサンプル116に変換する。アナログ／デジタル変換器回路114は、アナログ入力信号に対応するデジタルサンプルを生成することが可能な、当該技術分野において知られている任意の回路とすることができます。本明細書において提供される開示に基づくと、当業者であれば、本発明の異なる実施形態に関して用いることができる種々のアナログ／デジタル変換器回路を認識するであろう。デジタルサンプル116は等化器回路120に与えられる。等化器回路120は、デジタルサンプル116に等化アルゴリズムを適用して等化出力125を得る。本発明の幾つかの実施形態では、等化器回路120は、当該技術分野において知られているようなデジタル有限インパルス応答フィルター回路である。等化出力125は、データ検出器回路130に与えられる。幾つかの場合には、等化器120は、データ検出器回路130が処理に利用可能になるまで1つ又は複数の符号語を保持するのに十分なメモリを備える。

20

## 【0023】

データ検出器回路130は、受信した符号語又はデータセットにデータ検出アルゴリズムを適用するように動作可能であり、幾つかの場合には、データ検出器回路130は、2つ以上の符号語を並列に処理することができる。本発明の幾つかの実施形態では、データ検出器回路130は、当該技術分野において知られているようなビタビアルゴリズムデータ検出器回路である。本発明の他の実施形態では、データ検出器回路130は、当該技術分野において知られているような最大事後データ検出器回路である。一般的なフレーズ「ビタビデータ検出アルゴリズム」又は「ビタビアルゴリズムデータ検出器回路」は、任意のビタビ検出アルゴリズム若しくはビタビアルゴリズム検出器回路又はそれらの変形を意味するように、それらの最も広い意味で用いられることに留意されたい。それらの変形には、双方向ビタビ検出アルゴリズム又は双方向ビタビアルゴリズム検出器回路が含まれるが、これらに限定されるものではない。また、一般的なフレーズ「最大事後データ検出アルゴリズム」又は「最大事後データ検出器回路」は、任意の最大事後検出アルゴリズム若しくは最大事後検出器回路又はそれらの変形を意味するようにそれらの最も広い意味で用いられる。それらの変形には、単純化された最大事後データ検出アルゴリズム及び最大対数最大事後データ検出アルゴリズム、又は対応する検出器回路が含まれるが、これらに限定されるものではない。本明細書において提供される開示に基づくと、当業者であれば、本発明の異なる実施形態に関して用いることができる種々のデータ検出器回路を認識するであろう。データ検出器回路130は、等化器回路120又は中央メモリ回路150からのデータセットが利用可能であることに基づいて始動される。

30

## 【0024】

完了すると、データ検出器回路130は検出器出力195を与える。検出器出力195は軟データを含む。フレーズ「軟データ」は、本明細書において用いられるとき、信頼性データを意味するようにその最も広い意味で用いられ、該信頼性データの各インスタンスは、対応するビット位置又はビット位置群が正しく検出されている尤度を示す。本発明の幾つかの実施形態では、軟データ又は信頼性データは当該技術分野において知られているような対数尤度比データである。検出器出力195は局所インターリーバー回路142及び

40

50

信頼性モニター回路 160 に与えられる。局所インターリーバー回路 142 は、検出出力として含まれるデータセットの副部分 (sub-portion) (すなわち局所チャンク) をシャッフルするように動作可能であり、インターリープされた符号語 146 を与え、該インターリープされた符号語 146 は中央メモリ回路 150 に格納される。インターリーバー回路 142 は、データセットをシャッフルして再配列されたデータセットを得ることが可能な、当該技術分野において知られている任意の回路とすることができます。インターリープされた符号語 146 は中央メモリ回路 150 に格納される。

#### 【 0025 】

データ復号化器回路 170 が利用可能になると、以前に格納されたインターリープされた符号語 146 が、復号化器入力 152 として中央メモリ回路 150 からアクセスされ、当該技術分野において知られているように大域的にインターリープされ、データ復号化アルゴリズムが適用される。本発明の幾つかの実施形態では、データ復号化アルゴリズムは当該技術分野において知られているような低密度パリティチェックアルゴリズムである。本明細書において提供される開示に基づくと、当業者であれば、本発明の異なる実施形態に関して用いることができる他の復号化アルゴリズムを認識するであろう。データ復号化アルゴリズムが所与のデータセットに対して完了すると、復号化アルゴリズムが収束した(すなわち、結果のデータセットが、パリティエラーがないことによって示されるようになし、最初に書き込まれたデータと一致する)か否かが判断される。復号化アルゴリズムが収束したと判断された場合、その結果の復号化データセットは硬判定出力 172 としてデインターリーバー回路 180 に与えられる。デインターリーバー回路 180 は、データを再配列して、データに適用された大域インターリープ及び局所インターリープの双方を逆に行い、デインターリープされた出力 182 を得る。デインターリープされた出力 182 は硬判定出力回路 190 に与えられる。硬判定出力回路 190 は、順序がばらばらで完了する可能性があるデータセットを再順序付けし、該データセットの元の順序に戻すように動作可能である。次に、元の順序のデータセットは硬判定出力 192 として与えられる。

#### 【 0026 】

代替的に、データ復号化アルゴリズムが収束しなかったと判断された(すなわち、パリティエラーが残っている)場合、完了したデータセットは、当該技術分野において知られているように大域的にデインターリープされ、復号化器出力 154 として中央メモリ回路 150 に再び書き込まれる。データ検出器回路 130 が利用可能になると、以前に格納された復号化器出力 148 が、中央メモリ回路 150 からアクセスされ、デインターリーバー回路 144 によって局所的にデインターリープされる。デインターリーバー回路 144 は、インターリーバー回路 142 によって最初に実行されたシャッフルを逆にするように復号化器出力 148 を再配列する。その結果のデインターリープされた出力 197 は、データ検出器回路 130 に与えられる。

#### 【 0027 】

幾つかの場合には、信頼性モニター回路 160 は、テスト / 調節期間中にのみ動作する。他の場合には、信頼性モニター回路 160 は連続的に動作される。信頼性モニター回路 160 は、検出器出力 195 を受信し、データ処理回路 100 の動作を統御するのに用いられる 1 つ又は複数のパラメーターを修正する。パラメーターは、入出力 164 を介してアナログ処理回路 108 に通信することができ、入出力 162 を介してデータ検出器回路 130 に通信することができ、かつ / 又は入出力 166 を介してデータ復号化器回路 170 に通信することができる。パラメーターは、アナログフロントエンド回路 110 に含まれる可変利得増幅器の利得、アナログフロントエンド回路 110 に含まれるアナログフィルターの遮断周波数及び / 若しくはブースト、フロントエンド処理ループ 111 の D C ループオフセット、ターゲット回路 109 によって用いられるターゲット、データ検出器回路 130 によって用いられる検出器パラメーター、並びに / 又はデータ復号化器回路 170 によって用いられる復号化器パラメーターとすることができるが、これらに限定されるものではない。本明細書において提供される開示に基づくと、当業者であれば、本発明の異なる実施形態による信頼性モニター回路 160 によって調整することができる種々のパ

10

20

30

40

50

ラメーターを認識するであろう。

**【0028】**

信頼性モニター回路160は、検出器出力195の一部として受信された軟データを比較し、その軟データを信頼性しきい値168と比較する。幾つかの場合には、信頼性しきい値168はユーザープログラマブルである。他の場合には、信頼性しきい値168は固定値である。データが処理されているとき、信頼性モニター回路160は、入出力162、入出力164及び入出力166を介してそれぞれの回路に与えられる1つ又は複数のパラメーターの値（複数の場合もあり）を選択する。次に、データは、選択されたパラメーター値を用いて或る時間期間にわたってデータ処理回路100を通じて処理される。信頼性モニター回路160が、検出出力195からの軟データが信頼性しきい値168未満であると判断した場合、エラーが示される。このエラーはエラーレートに組み込まれる。1つ又は複数のパラメーターの1つ又は複数の新たな値が選択され、少なくとも信頼性モニター回路160が、対応するエラーレートが許容可能であると判断するまで、再テストのプロセスが続く。幾つかの場合には、軟データの移動平均又は他の累算値が、信頼性しきい値168と比較するのに用いられる。そのような場合には、リセット入力169を用いて、パラメーター値が信頼性モニター回路160によって変更されるごとに、累算値又は移動平均をリセットすることができる。様々な場合には、リセット入力169は、信頼性モニター回路160の内部の信号である。

10

**【0029】**

図2を参照すると、本発明の幾つかの実施形態による信頼性に基づく調節回路200の1つの実施態様が示されている。信頼性に基づく調節回路200は、データ処理回路100の信頼性モニター回路160の代わりに用いることができる。信頼性に基づく調節回路200は、検出出力（図示せず）の一部として受信された軟データ203を信頼性しきい値205と比較するように動作可能な比較器回路210を備える。幾つかの場合には、信頼性しきい値205はユーザープログラマブルである。他の場合には、信頼性しきい値205は固定値である。軟データ203のインスタンスが信頼性しきい値205未満である場合、比較器出力220はハイにアサートされる。対照的に、軟データ203のインスタンスが信頼性しきい値205以上である場合、比較器出力220はローにアサートされる。比較器出力220がハイにアサートされる（軟データ203のインスタンスに対応する）各クロック周期において、プロキシエラーカウンター回路230がインクリメントする。プロキシエラーカウンター回路230からのカウントは、パラメーター修正制御回路250に与えられるプロキシエラーカウント225である。

20

30

**【0030】**

パラメーター修正制御回路250は、更新済みパラメーター260として最初に与えられる初期パラメーター値240を受信する。更新済みパラメーター260は、データ処理回路内の1つ又は複数の機能の動作を統御するパラメーターとして与えられる。幾つかの例として、更新済みパラメーター260は、可変利得増幅器の利得、アナログフィルターの遮断周波数及び／若しくはブースト、DCループオフセット、ターゲット、データ検出器回路によって用いられる検出器パラメーター、並びに／又はデータ復号化器回路によって用いられる復号化器パラメーターとすることができるが、これらに限定されるものではない。本明細書において提供される開示に基づくと、当業者であれば、パラメーター修正制御回路250によって調整することができる種々のパラメーターを認識するであろう。

40

**【0031】**

本発明の1つの特定の実施形態では、パラメーター修正制御回路250は、規定されたデータ処理期間数の間、初期パラメーター240を更新済みパラメーター260として用い続けることを可能にする。初期パラメーター240は、事前にプログラムされたデフォルト値とすることができます。その期間が完了すると、プロキシエラーカウント225が格納され、パラメーター修正回路250は、更新済みパラメーター260として与えられる新たな値を選択し、プロキシエラーカウンター回路230は、リセット信号223のアサートによってリセットされる。データ処理は、再び、更新パラメーター260の新たに選

50

択された値を用いて規定された期間数の間、実行できるようになる。このプロセスは、更新済みパラメーター 260 の全ての可能な値がテストされると完了する。最後に、更新済みパラメーター 260 がいかなる回路を制御していようと、最小のプロキシエラーカウント 225 を与えた更新済みパラメーター 260 の値が、その回路の調節されたパラメーターとして選択される。このプロセスは、以下の疑似コードに示されている。

```

/* 初期パラメーター値をテストする

初期パラメーター 240 を更新済みパラメーター 260 として選択する ;

リセット 225 をアサートする ;

リセット 225 をデアサートする ;

For ( i = 0 ~ テスト期間の終了 ) 10

{

If ( 軟データ [ i ] 203 < 信頼性しきい値 205 )

{

プロキシエラーカウント 225 += 1

}

}

パラメーター エラー カウント = プロキシエラーカウント 225 ;

パラメーター 値 = 初期パラメーター 240 ;

/* 全ての他のパラメーター値をテストする */

リセット 225 をアサートする ;

リセット 225 をデアサートする ;

For ( 更新済みパラメーター 260 の各値 ) 20

{

更新済みパラメーター 260 の次の値を選択する ;

For ( i = 0 ~ テスト期間の終了 )

{

If ( 軟データ [ i ] 203 < 信頼性しきい値 205 )

{

プロキシエラーカウント 225 += 1

}

}

If ( プロキシエラーカウント 225 < パラメーター エラー カウント ) 30

{

パラメーター エラー カウント = プロキシエラーカウント 225 ;

パラメーター 値 = 選択された次の値 ;

}

}

パラメーター 値を選択する

【 0032 】 40

```

更に他の場合には、パラメーター修正制御回路 250 は、プロキシエラーカウント 225 が、規定しきい値未満になるまで検索を制限することによってパラメーター検索を制限するように修正することができる。規定しきい値未満のプロキシエラーカウント 225 を与えるパラメーター値が見つかると、そのパラメーター値が選択され、パラメーター検索プロセスは完了する。そのような場合、規定しきい値は、値をプログラマブル又は固定とすることができます。このプロセスは、以下の疑似コードで示される。

```

/* 初期パラメーター値をテストする

初期パラメーター 240 を更新済みパラメーター 260 として選択する ;

リセット 225 をアサートする ;

リセット 225 をデアサートする ; 50

```

```

For ( i = 0 ~ テスト期間の終了 )

{

If ( 軟データ [ i ] 203 < 信頼性しきい値 205 )

{

プロキシエラーカウント 225 += 1

}

}

If ( プロキシエラーカウント < 規定しきい値 ) 10

{

更新済みパラメーター 260 = 初期パラメーター 240 ;

プロセスを終了する

Else

{

パラメーターエラーカウント = プロキシエラーカウント 225 ;

パラメーター値 = 初期パラメーター 240 ;

}

/* 規定しきい値が達成されるまで他のパラメーター値をテストする */

リセット 225 をアサートする ;

リセット 225 をデアサートする ; 20

For ( 更新済みパラメーター 260 の各値 )

{

更新済みパラメーター 260 の次の値を選択する ;

For ( i = 0 ~ テスト期間の終了 )

{

If ( 軟データ [ i ] 203 < 信頼性しきい値 205 )

{

プロキシエラーカウント 225 += 1

}

}

If ( プロキシエラーカウント < 規定しきい値 ) 30

{

更新済みパラメーター 260 = 選択された次の値 ;

プロセスを終了

}

Else If ( プロキシエラーカウント 225 < パラメーターエラーカウント )

{

パラメーターエラーカウント = プロキシエラーカウント 225 ;

パラメーター値 = 選択された次の値 ;

}

}

【 0033 】

```

更に他の場合には、更新済みパラメーター 260 の全て値をテストする必要がないようなより高機能な (sophisticated) テストプロセスを用いることができる。そのようなストリームラインテストプロセスは、以下の図 5 及び図 6 に関して以下で論述するものと一致して行うことができる。そのような場合には、パラメーター修正制御回路 250 の動作は、更新済みパラメーター 260 の許容可能な値を特定するストリームライン手法を用いるように修正することができる。図 5 及び図 6 に関して以下で論述する方法は、既知データセットから取り出された実際のエラーカウントに基づく種々のパラメーター値を検索するように修正することができるに留意されたい。そのような手法は、図 8 ~ 図 10 に關 50

して以下で論述される。

【0034】

図3を参照すると、本発明の1つ又は複数の実施形態による信頼性データに基づく調節回路部を有する読み取りチャネル回路310を備えるストレージデバイス300が示されている。ストレージシステム300は、例えば、ハードディスクドライブとすることができます。ストレージシステム300はまた、前置増幅器370と、インターフェースコントローラー320と、ハードディスクコントローラー366と、モーターコントローラー368と、スピンドルモーター372と、ディスクプラッタ-378と、読み取り／書き込みヘッドアセンブリ376とを備える。インターフェースコントローラー320は、ディスクプラッタ-378へのデータのアドレス指定及びタイミングを制御する。ディスクプラッタ-378上のデータは、読み取り／書き込みヘッドアセンブリ376がディスクプラッタ-378の上方で適切に位置決めされたときに該アセンブリが検出することができる磁気信号の群からなる。1つの実施形態では、ディスクプラッタ-378は、水平記録方式又は垂直記録方式のいずれかに従って記録された磁気信号を含む。

10

【0035】

通常の読み取り動作では、読み取り／書き込みヘッドアセンブリ376は、モーターコントローラー368によってディスクプラッタ-378上の所望のデータトラックの上方に正確に位置決めされる。モーターコントローラー368は、ディスクプラッタ-378に対して読み取り／書き込みヘッドアセンブリ376の位置決めも行うし、ハードディスクコントローラー366の指示のもとでディスクプラッタ-378上の適切なデータトラックに読み取り／書き込みヘッドアセンブリを移動させることによってスピンドルモーター372の駆動も行う。スピンドルモーター372は、定められたスピンドル速度(RPM)でディスクプラッタ-378をスピンドル速度(RPM)で回転させる。読み取り／書き込みヘッドアセンブリ376が適切なデータトラックに隣接して位置決めされると、ディスクプラッタ-378がスピンドルモーター372によって回転されながら、ディスクプラッタ-378上のデータを表す磁気信号が読み取り／書き込みヘッドアセンブリ376によって検知される。検知された磁気信号は、ディスクプラッタ-378上の磁気データを表す連続した微小アナログ信号として与えられる。この微小アナログ信号は、読み取り／書き込みヘッドアセンブリ376から前置増幅器370を介して読み取りチャネル回路310に転送される。前置増幅器370は、ディスクプラッタ-378からアクセスされた微小アナログ信号を增幅するように動作可能である。次に、読み取りチャネル回路310は、受信したアナログ信号を復号化及びデジタル化して、ディスクプラッタ-378に元々書き込まれていた情報を再生する。このデータは、読み取りデータ303として受信回路に与えられる。書き込み動作は、先行する読み取り動作の実質的に逆であり、書き込みデータ301が読み取りチャネル回路310に与えられる。このデータは、その後、符号化され、ディスクプラッタ-378に書き込まれる。

20

30

【0036】

テスト動作中、又は幾つかの場合には標準的なデータ読み取り動作中、信頼性データに基づく調節制御回路部は、読み取りチャネル回路310の動作を統御する1つ又は複数のパラメーターを修正し、信頼性しきい値が満たされるか否かを監視し続ける。このように、読み取りチャネル回路310内のパラメーターを修正して、読み取りチャネル回路310の性能を改善することができる。信頼性データに基づく調節制御回路部を備える処理回路は、図1及び図2に関して上記で論述したものと同様に実施することができ、かつ／又は図5、図6、及び／若しくは図7に関して以下で論述するものと同様に動作することができる。他の場合には、信頼性データに基づく調節制御回路部は、図5及び図6に関して以下で論述するものと同様のストリームライン検索を用いる図8に関して以下で論述するものと同様の既知データに基づく調節制御回路部によって置き換えることができる。

40

【0037】

ストレージシステムは、SATA、SAS又は当該技術分野において知られている他のストレージ技術を利用することに留意すべきである。また、ストレージシステム300は、例えばRAID(低価格ディスク冗長アレイ又は独立ディスク冗長アレイ

50

)に基づくストレージシステム等のより大きなストレージシステムに統合することができるにも留意すべきである。ストレージシステム 300 の様々な機能又はブロックをソフトウェア又はファームウェアのいずれかに実装することができる一方、他の機能又はブロックはハードウェアに実装されることにも留意すべきである。

#### 【0038】

図 4 を参照すると、本発明の幾つかの実施形態による信頼性データに基づく調節回路部を有する受信機 420 を備えるデータ伝送システム 400 が示されている。データ伝送システム 400 は、当該技術分野において知られているような転送媒体 430 を介して符号化された情報を送信するように動作可能な送信機 410 を備える。符号化されたデータは、受信機 420 によって転送媒体 430 から受信される。受信機 420 は、信頼性データに基づく調節回路部を組み込んでいる。受信されたデータを処理している間、受信されたデータは、アナログ信号から一連の対応するデジタルサンプルに変換され、デジタルサンプルは等化されて、等化出力が得られる。等化出力は、次に、データ検出器回路とデータ復号化器回路との双方を備えるデータ処理回路に与えられる。データは、異なるデータセットに適用される処理反復回数間の変動を許容する中央メモリを介してデータ復号化器とデータ検出器回路との間で伝達される。転送媒体 430 は、当該技術分野において知られている任意の転送媒体とすることに留意すべきである。任意の転送媒体には、無線媒体、光媒体、又は有線媒体が含まれるが、これらに限定されるものではない。本明細書において提供される開示に基づくと、当業者であれば、本発明の異なる実施形態について用いることができる種々の転送媒体を認識するであろう。

10

20

#### 【0039】

テスト動作中、又は幾つかの場合には標準的なデータ読み取り動作中、信頼性データに基づく調節制御回路部は、受信機 420 の動作を統御する 1 つ又は複数のパラメーターを修正し、信頼性しきい値が満たされるか否かを監視し続ける。このように、受信機 420 内のパラメーターを修正して受信機 420 の性能を改善することができる。信頼性データに基づく調節制御回路部を備える処理回路は、図 1 及び図 2 に関して上記で論述したものと同様に実施することができ、かつ / 又は図 5、図 6 及び / 若しくは図 7 に関して以下で論述するものと同様に動作することができる。他の場合には、信頼性データに基づく調節制御回路部は、図 5 及び図 6 に関して以下で論述するものと同様のストリームライン検索を用いる図 8 に関して以下で論述するものと同様の既知データに基づく調節制御回路部によつて置き換えることができる。

30

#### 【0040】

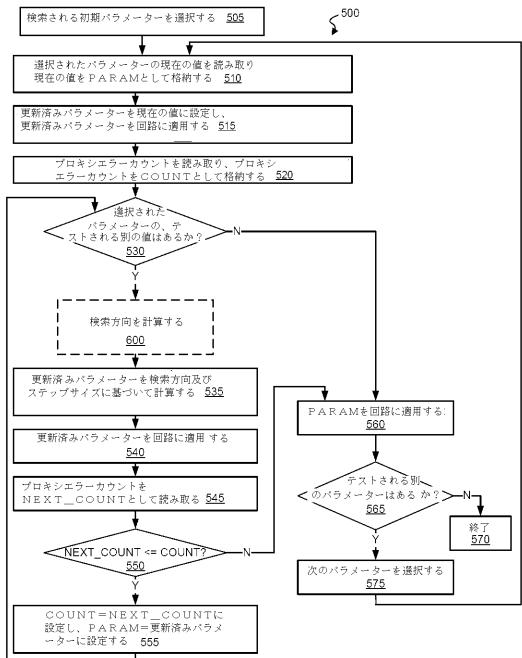

図 5 を参照すると、流れ図 500 が、本発明の様々な実施形態による信頼性に基づくパラメーター調節のための方法を示している。流れ図 500 に従って、初期パラメーターが検索のために選択される( ブロック 505 )。選択されたパラメーターは、データ処理回路の或る部分の動作を統御する任意のパラメーターとすることができます。幾つかの例として、パラメーターは、可変利得増幅器の利得、アナログフィルターの遮断周波数及び / 若しくはブースト、DC ループオフセット、ターゲット、データ検出器回路によって用いられる検出器パラメーター、並びに / 又はデータ復号化器回路によって用いられる復号化器パラメーターとすることができるが、これらに限定されるものではない。本明細書において提供される開示に基づくと、当業者であれば、図 5 の方法によって調整することができる種々のパラメーターを認識するであろう。選択されたパラメーターの現在の値が読み取られ、変数 PARAM として格納される( ブロック 510 )。更新済みパラメーター( すなわち、データ処理回路に適用されるパラメーター ) は、現在の値と等しく設定され、該更新済みパラメーターは、データ処理回路に適用される( ブロック 515 )。更新済みパラメーターを処理回路に適用することは、更新済みパラメーターを用いて或る期間の間、処理回路を動作させることを含む。この処理が行われると、データ検出器回路からの軽データの幾つのインスタンスが、規定しきい値未満であるのかのカウントが行われ、プロキシエラーカウントが得られる。この処理が行われると、プロキシエラーカウントが読み取られ、変数 COUNT として格納される( ブロック 520 )。その後、プロキシエラー

40

50

カウント値はリセットされる。

#### 【0041】

次に、選択されたパラメーターの別の値がテストされずに残っているか否かが判断される（ブロック530）。別の値がテストされずに残っている場合（ブロック530）、検索方向が計算される（ブロック600）。検索方向を選択するこのプロセスは、図6に関して以下でより詳細に論述される。検索方向が特定されると（ブロック600）、更新済みパラメーターの値が検索方向及びステップサイズに基づいて計算される（ブロック535）。幾つかの場合には、ステップサイズはユーザープログラマブルとすることができます一方、他の場合には、ステップサイズは固定とすることができます。本発明の幾つかの実施形態では、更新済みパラメーターの値は、以下の疑似コードに従って計算される。

10

If（検索方向は正である）

{

```

更新済みパラメーター = 更新済みパラメーター + ステップサイズ

```

}

Else

{

```

更新済みパラメーター = 更新済みパラメーター - ステップサイズ

```

}

次に、この新たな更新済みパラメーターは、データ処理回路に適用される（ブロック540）。更新済みパラメーターを処理回路に適用することは、更新済みパラメーターを用いて或る期間の間、処理回路を動作させることを含む。この処理が行われるととき、データ検出器回路からの軟データの幾つのインスタンスが規定しきい値未満であるのかのカウントが行われ、プロキシエラーカウントが得られる。処理が行われると、プロキシエラーカウントが読み取られ、変数NEXT\_COUNTとして格納される（ブロック545）。その後、プロキシエラーカウント値はリセットされる。

20

#### 【0042】

NEXT\_COUNTの値がCOUNTの値以下であるか否かが判断される（ブロック550）。NEXT\_COUNTの値がCOUNTの値以下である場合（ブロック550）、変数COUNTは、NEXT\_COUNTの値と等しく設定され、PARAMの値は、更新済みパラメーターの値と等しく設定される（ブロック555）。ブロック530、600、535、540、545、550、555のプロセスは、選択されたパラメーターの全ての値がテストされるまで繰り返す。

30

#### 【0043】

テストされる、選択されたパラメーターの値がなくなると（ブロック530）、又はNEXT\_COUNTの値がCOUNTの値よりも大きい場合（ブロック550）、選択されたパラメーターの許容可能な値が変数PARAMに格納済みであり、その値は、データ処理回路に適用される（ブロック560）。次に、データ処理回路の別のパラメーターがテストされずに残っているか否かが判断される（ブロック565）。別のパラメーターがテストされずに残っている場合（ブロック565）、テストされる次のパラメーターが選択され（ブロック575）、ブロック510～565（ブロック600を含む）のプロセスが、新たに選択されたパラメーターに対して繰り返される。そうではなく、テストされずに残っている他のパラメーターがない場合（ブロック565）、テストプロセスは終了する（ブロック570）。

40

#### 【0044】

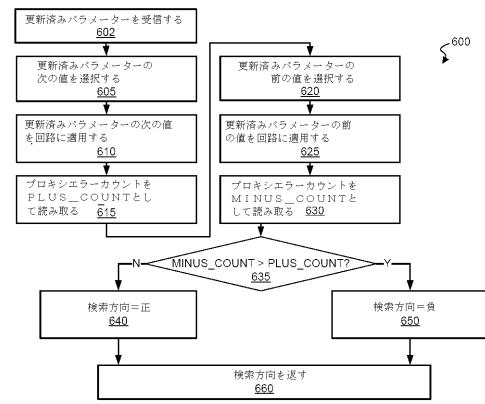

図6を参照すると、流れ図600が、検索方向を確定するための、本発明の幾つかの実施形態による方法を示している。流れ図600は、図5からの同じ番号のブロックの方法を概説している。流れ図600に従って、更新済みパラメーターが流れ図500のプロセスから受信される（ブロック602）。更新済みパラメーターの次の値（すなわち、規定量だけ増加された更新済みパラメーターの値）が選択される（ブロック605）。更新済みパラメーターの次の値は、データ処理回路に適用される（ブロック610）。更新済み

50

パラメーターの次の値を処理回路に適用することは、更新済みパラメーターを用いて或る期間の間、処理回路を動作させることを含む。この処理が行われると、データ検出器回路からの軟データの幾つのインスタンスが規定しきい値未満であるのかのカウントが行われ、プロキシエラーカウントが得られる。この処理が行われると、プロキシエラーカウントが読み取られ、変数 PLUS\_COUNT として格納される（ブロック 520）。その後、プロキシエラーカウント値はリセットされる。

#### 【0045】

次に、更新済みパラメーターの前の値（すなわち、規定量だけ減少された更新済みパラメーターの値）が選択される（ブロック 620）。更新済みパラメーターの前の値がデータ処理回路に適用される（ブロック 625）。更新済みパラメーターの前の値を処理回路に適用することは、更新済みパラメーターを用いて或る期間の間、処理回路を動作させることを含む。この処理が行われると、データ検出器回路からの軟データの幾つのインスタンスが規定しきい値未満であるのかのカウントが行われ、プロキシエラーカウントが得られる。処理が行われると、プロキシエラーカウントが読み取られ、変数 MINUS\_COUNT として格納される（ブロック 630）。その後、プロキシエラーカウント値はリセットされる。

#### 【0046】

次に、PLUS\_COUNT の値が MINUS\_COUNT の値よりも大きいか否かが判断される（ブロック 635）。PLUS\_COUNT の値が MINUS\_COUNT の値よりも大きい場合（ブロック 635）、検索方向は、負と等しく設定される（ブロック 650）。そうでない場合、検索方向は正と等しく設定される（ブロック 640）。次に、検索方向は、図 5 のプロセスについて用いるために返される（ブロック 660）。

#### 【0047】

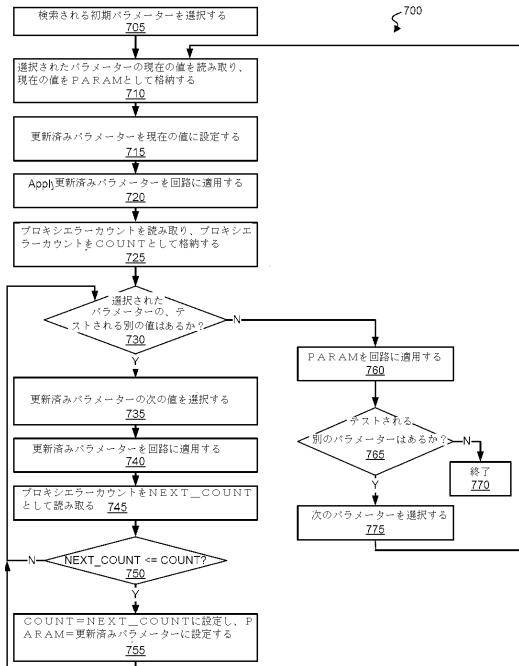

図 7 を参照すると、流れ図 700 が本発明の幾つかの実施形態による信頼性に基づくパラメーター調節のための別の方法を示している。流れ図 700 に従って、初期パラメーターが検索のために選択される（ブロック 705）。選択されたパラメーターは、データ処理回路の或る部分の動作を統御する任意のパラメーターとすることができる。幾つかの例として、パラメーターは、可変利得増幅器の利得、アナログフィルターの遮断周波数及び／若しくはブースト、DC ループオフセット、ターゲット、データ検出器回路によって用いられる検出器パラメーター、並びに／又はデータ復号化器回路によって用いられる復号化器パラメーターとすることができますが、これらに限定されるものではない。本明細書において提供される開示に基づくと、当業者であれば、図 7 の方法によって調整することができる種々のパラメーターを認識するであろう。選択されたパラメーターの現在の値が読み取られ、変数 PARAM として格納される（ブロック 710）。更新済みパラメーター（すなわち、データ処理回路に適用されるパラメーター）は、現在の値と等しく設定され（ブロック 715）、該更新済みパラメーターは、データ処理回路に適用される（ブロック 720）。更新済みパラメーターを処理回路に適用することは、更新済みパラメーターを用いて或る期間の間、処理回路を動作させることを含む。この処理が行われると、データ検出器回路からの軟データの幾つのインスタンスが規定しきい値未満であるのかのカウントが行われ、プロキシエラーカウントが得られる。この処理が行われると、プロキシエラーカウントが読み取られ、変数 COUNT として格納される（ブロック 725）。その後、プロキシエラーカウント値はリセットされる。

#### 【0048】

次に、選択されたパラメーターの別の値がテストされずに残っているか否かが判断される（ブロック 730）。別の値がテストされずに残っている場合（ブロック 730）、更新済みパラメーターの次の値が選択される（ブロック 735）。次に、この新たな更新済みパラメーターは、データ処理回路に適用される（ブロック 740）。更新済みパラメーターを処理回路に適用することは、更新済みパラメーターを用いて或る期間の間、処理回路を動作させることを含む。この処理が行われると、データ検出器回路からの軟データの幾つのインスタンスが規定しきい値未満であるのかのカウントが行われ、プロキシエラ

10

20

30

40

50

ーカウントが得られる。この処理が行われると、プロキシエラーカウントが読み取られ、変数NEXT\_COUNTとして格納される（ブロック745）。その後、プロキシエラーカウント値はリセットされる。

#### 【0049】

NEXT\_COUNTの値がCOUNTの値以下であるか否かが判断される（ブロック750）。NEXT\_COUNTの値がCOUNTの値以下である場合（ブロック750）、変数COUNTは、NEXT\_COUNTの値と等しく設定され、PARAMの値は、更新済みパラメーターの値と等しく設定される（ブロック755）。ブロック730～755のプロセスは、選択されたパラメーターの全ての値がテストされるまで繰り返す。

#### 【0050】

選択されたパラメーターの値の全てがテストされると（ブロック730）、選択されたパラメーターの最良の利用可能な値が変数PARAMに格納され、その値は、データ処理回路に適用される（ブロック760）。次に、データ処理回路の別のパラメーターがテストされずに残っているか否かが判断される（ブロック765）。別のパラメーターがテストされずに残っている場合（ブロック765）、テストされる次のパラメーターが選択され（ブロック775）、ブロック710～765のプロセスが、新たに選択されたパラメーターに対して繰り返される。そうではなく、テストされずに残っている他のパラメーターがない場合（ブロック765）、テストプロセスは終了する（ブロック770）。

#### 【0051】

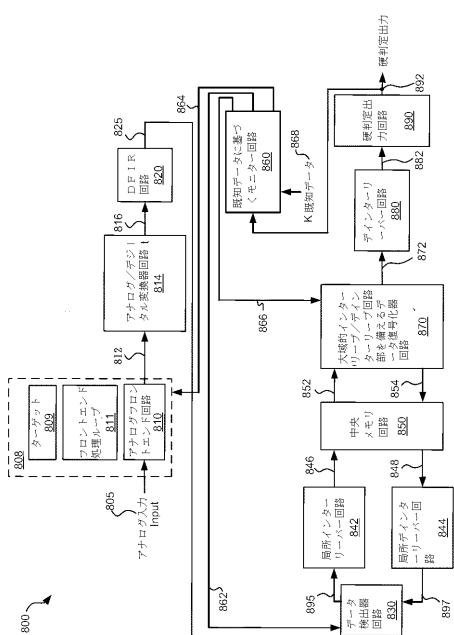

図8は、本発明の1つ又は複数の実施形態によるストリームライン検索を有する既知データに基づくモニター回路860を備えるデータ処理回路800を示している。データ処理回路800は、アナログ処理回路808を備える。アナログ処理回路808は、アナログフロントエンド回路810と、タイミング及び制御をアナログフロントエンド回路810に提供するように動作可能なフロントエンド処理ループ811と、ターゲットに基づくフィルタリングフィードバックをアナログフロントエンド回路810に提供するように動作可能なターゲット回路809とを備える。アナログフロントエンド回路810は、当該技術分野において知られているようなアナログフィルター及び増幅器回路を含むことができるが、これらに限定されるものではない。本明細書において提供される開示に基づくと、当業者であれば、アナログフロントエンド回路810の一部として含めることができる種々の回路部を認識するであろう。幾つかの場合には、アナログフロント回路810の一部として含まれる可変利得増幅器の利得を修正可能とすることことができ、アナログフロントエンド回路810に含まれるアナログフィルターの遮断周波数及びブーストを修正可能とすることができます。フロントエンド処理ループ811は、当該技術分野において知られているアナログフロントエンド回路810にタイミングを提供するように動作可能な任意の処理ループとすることができます。幾つかの場合には、そのようなフロントエンド処理ループ811は、修正可能とすることができますDCループオフセットを含む。ターゲット回路809は、当該技術分野において知られている任意の、ターゲットに基づくフィルター回路とすることができます。様々な場合において、ターゲット回路809によって用いられるターゲットは修正可能とすることができます。本明細書において提供される開示に基づくと、当業者であれば、本発明の異なる実施形態に関して用いることができる種々の、ターゲットに基づくフィルター回路及びフロントエンド処理ループを認識するであろう。

#### 【0052】

アナログフロントエンド回路810は、アナログ信号805を受信する。アナログフロントエンド回路810は、アナログ信号805を処理し、処理済みのアナログ信号812(112)をアナログ/デジタル変換器回路814に提供する。幾つかの場合には、アナログ信号805は、ストレージ媒体（図示せず）に対して配置される読み取り/書き込みヘッドアセンブリ（図示せず）から取り出される。他の場合には、アナログ信号805は、伝送媒体（図示せず）からの信号を受信するように動作可能な受信機回路（図示せず）から取り出される。伝送媒体は、有線又は無線とすることができる。本明細書において提供される開示に基づくと、当業者であれば、アナログ入力805を取り出すことができる種々の信

10

20

30

40

50

号源を認識するであろう。

【0053】

アナログ／デジタル変換器回路814は、処理済みのアナログ信号812を対応する一連のデジタルサンプル816に変換する。アナログ／デジタル変換器回路814は、アナログ入力信号に対応するデジタルサンプルを生成することが可能な、当該技術分野において知られている任意の回路とすることができます。本明細書において提供される開示に基づくと、当業者であれば、本発明の異なる実施形態に関して用いることができる種々のアナログ／デジタル変換器回路を認識するであろう。デジタルサンプル816は等化器回路820に与えられる。等化器回路820は、デジタルサンプル816に等化アルゴリズムを適用して、等化出力825を得る。本発明の幾つかの実施形態では、等化器回路820は、当該技術分野において知られているようなデジタル有限インパルス応答フィルター回路である。等化出力825は、データ検出器回路830に与えられる。幾つかの場合には、等化器820は、データ検出器回路830が処理に利用可能になるまで1つ又は複数の符号語を保持するのに十分なメモリを備える。

10

【0054】

データ検出器回路830は、受信した符号語又はデータセットにデータ検出アルゴリズムを適用するように動作可能であり、幾つかの場合には、データ検出器回路830は、2つ以上の符号語を並列に処理することができる。本発明の幾つかの実施形態では、データ検出器回路830は、当該技術分野において知られているようなビタビアルゴリズムデータ検出器回路である。本発明の他の実施形態では、データ検出器回路830は、当該技術分野において知られているような最大事後データ検出器回路である。本明細書において提供される開示に基づくと、当業者であれば、本発明の異なる実施形態に関して用いることができる種々のデータ検出器回路を認識するであろう。データ検出器回路830は、等化器回路820又は中央メモリ回路850からのデータセットが利用可能であることに基づいて始動される。

20

【0055】

完了すると、データ検出器回路830は検出器出力895を与える。検出出力895は局所インターリーバー回路842及び既知データに基づくモニター回路860に与えられる。局所インターリーバー回路842は、検出出力として含まれるデータセットの副部分（すなわち局所チャンク）をシャッフルするように動作可能であり、インターリープされた符号語846を与え、該インターリープされた符号語846は中央メモリ回路850に格納される。インターリーバー回路842は、データセットをシャッフルして再配列されたデータセットを得ることが可能な、当該技術分野において知られている任意の回路とすることができる。インターリープされた符号語846は中央メモリ回路850に格納される。

30

【0056】

データ復号化器回路870が利用可能になると、以前に格納されたインターリープされた符号語846が、復号化器入力852として中央メモリ回路850からアクセスされ、当該技術分野において知られているように大域的にインターリープされ、データ復号化アルゴリズムが適用される。本発明の幾つかの実施形態では、データ復号化アルゴリズムは当該技術分野において知られているような低密度パリティチェックアルゴリズムである。本明細書において提供される開示に基づくと、当業者であれば、本発明の異なる実施形態に関して用いることができる他の復号化アルゴリズムを認識するであろう。データ復号化アルゴリズムが所与のデータセットに対して完了すると、復号化アルゴリズムが収束した（すなわち、結果のデータセットが、パリティエラーがないことによって示されるよう、最初に書き込まれたデータと一致する）か否かが判断される。復号化アルゴリズムが収束したと判断された場合、その結果の復号化データセットは硬判定出力872としてディンタリーバー回路880に与えられる。ディンタリーバー回路880は、データを再配列して、データに適用された大域インターリープ及び局所インターリープの双方を逆に行い、ディンタリープされた出力882を得る。ディンタリープされた出力882は

40

50

硬判定出力回路 890 に与えられる。硬判定出力回路 890 は、順序がばらばらで完了する場合があるデータセットを再順序付けし、該データセットの元の順序に戻すように動作可能である。次に、元の順序付けされたデータセットは硬判定出力 892 として与えられる。

#### 【0057】

代替的に、データ復号化アルゴリズムが収束しなかったと判断された（すなわち、パリティエラーが残っている）場合、完了したデータセットは、当該技術分野において知られているように大域的にデインターリープされ、復号化器出力 854 として中央メモリ回路 850 に再び書き込まれる。データ検出器回路 830 が利用可能になると、以前に格納され復号化器出力 848 が、中央メモリ回路 850 からアクセスされ、デインターリーバー回路 844 によって局所的にデインターリープされる。デインターリーバー回路 844 は、インターリーバー回路 842 によって最初に実行されたシャフルを逆に行うように復号化器出力 848 を再配列する。その結果のデインターリープされた出力 897 は、データ検出器回路 830 に与えられる。10

#### 【0058】

幾つかの場合には、既知データに基づくモニター回路 860 は、テスト / 調節期間中のみ動作する。他の場合には、既知データに基づくモニター回路 860 は、連続的に動作される。既知データに基づくモニター回路 860 は、検出器出力 895 を受信し、データ処理回路 800 の動作を統御するのに用いられる 1つ又は複数のパラメーターを修正する。パラメーターは、入出力 864 を介してアナログ処理回路 808 に通信することができ、入出力 862 を介してデータ検出器回路 830 に通信することができ、かつ / 又は入出力 866 を介してデータ復号化器回路 870 に通信することができる。パラメーターは、アナログフロントエンド回路 810 に含まれる可変利得増幅器の利得、アナログフロントエンド回路 810 に含まれるアナログフィルターの遮断周波数及び / 若しくはブースト、フロントエンド処理ループ 811 の DC ループオフセット、ターゲット回路 809 によって用いられるターゲット、データ検出器回路 830 によって用いられる検出器パラメーター、並びに / 又はデータ復号化器回路 870 によって用いられる復号化器パラメーターとすることができるが、これらに限定されるものではない。本明細書において提供される開示に基づくと、当業者であれば、本発明の異なる実施形態による既知データに基づくモニター回路 860 によって調整することができる種々のパラメーターを認識するであろう。20

#### 【0059】

既知データに基づくモニター回路 860 は、硬判定出力 892 を既知データセット 868 と比較する。データが処理されているとき、既知データに基づくモニター回路 860 は、入出力 862、入出力 864 及び入出力 866 を介してそれぞれの回路に与えられる 1つ又は複数のパラメーターの値（複数の場合もあり）を選択する。次に、データが、或る時間期間にわたって、選択されたパラメーター値を用いてデータ処理回路 800 を通じて処理される。硬判定出力 892 のインスタンスが既知データセット 868 の対応するインスタンスと等しくないと、既知データに基づくモニター回路 860 が判断した場合、エラーが示される。このエラーはエラーレートに組み込まれる。エラーレートが規定しきい値を超えた場合、1つ又は複数のパラメーターの 1つ又は複数の新たな値が選択され、許容可能なパラメーターが特定されるまで、再テストプロセスが続く。図 2 に関して上記で論述したものと同様の回路を用いて、既知データに基づくモニター回路を実装することができる。異なる点は、図 2 の回路の比較器 210 が、軟データ 203 及び信頼性しきい値 205 の代わりに既知データセット 868 及び硬判定出力 892 を受信するということである。既知データに基づくモニター回路 860 は、図 5 及び図 6 に関して上記で論述したようなストリームラインパラメーター値検索プロセスを組み込む。30

#### 【0060】

上記のアプリケーションにおいて論述した様々なブロックは、他の機能とともに集積回路に実装することができることに留意すべきである。そのような集積回路は、所与のブロック、システム若しくは回路の機能の全て、又はブロック、システム若しくは回路のサブ40

セットのみを含むことができる。また、ブロック、システム又は回路の要素を複数の集積回路にわたって実装することができる。そのような集積回路は、モノリシック集積回路、フリップチップ集積回路、マルチチップモジュール集積回路及び／又は混合信号集積回路を含むが、これらに限定されるものではない、当該技術分野において知られている任意のタイプの集積回路とすることができる。本明細書において論述されたブロック、システム又は回路の様々な機能を、ソフトウェア又はファームウェアのいずれかにおいて実装することができることにも留意すべきである。そのような幾つかの場合には、システム全体、ブロック全体又は回路全体を、そのソフトウェア等価物又はファームウェア等価物を用いて実装することができる。他の場合には、所与のシステム、ブロック又は回路の一部分をソフトウェア又はファームウェアにおいて実装することもできる一方、他の部分はハードウェアにおいて実装される。

## 【0061】

結論として、本発明はデータ処理のための新規なシステム、デバイス、方法及び構成を提供する。本発明の1つ又は複数の実施形態の詳細な説明が上記で与えられたが、本発明の趣旨から逸脱することなく、様々な代替形態、修正形態及び均等物が当業者には明らかであろう。したがって、上記の説明は本発明の範囲を限定するものとして解釈されることはなく、本発明の範囲は添付の特許請求の範囲によって画定される。

## 【符号の説明】

## 【0062】

図1

|     |                                                                             |                                     |    |

|-----|-----------------------------------------------------------------------------|-------------------------------------|----|

| 105 | Analog Input                                                                | アナログ入力                              | 20 |

| 109 | Target                                                                      | ターゲット                               |    |

| 110 | Analog Front End Circuit                                                    | アナログフロントエンド回路                       |    |

| 111 | Front End Processing Loops                                                  | フロントエンド処理ループ                        |    |

| 114 | Analog to Digital Converter Circuit                                         | アナログ／デジタル変換器回路                      |    |

| 120 | DFIR Circuit                                                                | D F I R 回路                          |    |

| 130 | Data Detector Circuit                                                       | データ検出器回路                            |    |

| 142 | Local Interleaver Circuit                                                   | 局所インターリーバー回路                        |    |

| 144 | Local De-Interleaver Circuit                                                | 局所デインターリーバー回路                       |    |

| 150 | Central Memory Circuit                                                      | 中央メモリ回路                             | 30 |

| 160 | Reliability Monitor Circuit                                                 | 信頼性モニター回路                           |    |

| 168 | Reliability Threshold                                                       | 信頼性しきい値                             |    |

| 169 | Reset                                                                       | リセット                                |    |

| 170 | Data Decoder Circuit Including Global Interleaving/De-InterleavingCircuitry | 大域的インターリーブ／デインターリーブ回路部を備えるデータ復号化器回路 |    |

| 180 | De-Interleaver Circuit                                                      | デインターリーバー回路                         |    |

| 190 | Hard Decision Output Circuit                                                | 硬判定出力回路                             |    |

| 192 | Hard Decision Output                                                        | 硬判定出力                               |    |

図2

|     |                                        |                |    |

|-----|----------------------------------------|----------------|----|

| 203 | Soft Data                              | 軟データ           | 40 |

| 205 | Reliability Threshold                  | 信頼性しきい値        |    |

| 210 | Comparator Circuit                     | 比較器回路          |    |

| 223 | Reset                                  | リセット           |    |

| 225 | Proxy Error Count                      | プロキシエラーカウント    |    |

| 230 | Proxy Error Counter Circuit            | プロキシエラーカウンター回路 |    |

| 240 | Initial Parameter                      | 初期パラメーター       |    |

| 250 | Parameter Modification Control Circuit | パラメーター修正制御回路   |    |

| 260 | Updated Parameter                      | 更新済みパラメーター     |    |

10

20

30

40

50

## 図 3

3 0 1 Write Data 書込みデータ

3 0 3 Read Data 読取りデータ

3 1 0 Read Channel Including Soft Data Reliability Data Based TuningControl Ci

rcuitry 軟データ信頼性データに基づく調節制御回路部を備える読み取りチャネル

3 2 0 Interface Controller インターフェースコントローラー

3 6 6 Hard Disk Controller ハードディスクコントローラー

3 6 8 Motor Controller モーター コントローラー

3 7 0 Preamp 前置増幅器

3 7 2 Spindle Motor スピンドルモーター

3 7 6 Read/Write Head 読取り / 書込みヘッド

3 7 8 Disk Platter ディスク プラッター 10

## 図 4

4 1 0 Transmitter 送信機

4 2 0 Receiver Including Reliability Data Based Tuning Control Circuitry 信頼

性データに基づく調節制御回路部を備える受信機

4 3 0 Transfer Medium 転送媒体

## 図 5

5 0 5 Select Initial Parameter to be Searched 検索される初期パラメーターを選

択する

5 1 0 Read Current Value of the Selected Parameter and Store the CurrentValue

as PARAM 選択されたパラメーターの現在の値を読み取り、現在の値を P A R A M として

格納する

5 1 5 Set the Updated Parameter to the Current Value and Apply the UpdatedPara

meter to the Circuit 更新済みパラメーターを現在の値に設定し、更新済みパラメータ

ーを回路に適用する

5 2 0 Read the Proxy Error Count and Store the Proxy Error Count as COUNT プ

ロキシエラー カウントを読み取り、プロキシエラー カウントを C O U N T として格納する 30

5 3 0 Another Value of the Selected Parameter to be Tested? 選択されたパラメ

ーターの、テストされる別の値はあるか?

5 3 5 Calculated Updated Parameter Based on the Search Direction and the Step

Size 更新済みパラメーターを検索方向及びステップサイズに基づいて計算する

5 4 0 Apply the Updated Parameter to the Circuit 更新済みパラメーターを回路に

適用する

5 4 5 Read the Proxy Error Count as NEXT\_COUNT プロキシエラー カウントを N E X

T \_ C O U N T として読み取る

5 5 5 Set COUNT = NEXT\_COUNT and Set PARAM = Updated Parameter C O U N T = N

E X T \_ C O U N T に設定し、P A R A M = 更新済みパラメーターに設定する 40

5 6 0 Apply PARAM to the Circuit P A R A M を回路に適用する

5 6 5 Another Parameter to be Tested? テストされる別のパラメーターはあるか?

5 7 0 End 終了

5 7 5 Select the Next Paramter 次のパラメーターを選択する

6 0 0 Calculate the Search Direction 検索方向を計算する

## 図 6

6 0 2 Receive the Updated Parameter 更新済みパラメーターを受信する

6 0 5 Select the Next Value of the Updated Parameter 更新済みパラメーターの次

の値を選択する 50

6 1 0 Apply the Next Value of the Updated Parameter to the Circuit 更新済みパラメーターの次の値を回路に適用する

6 1 5 Read the Proxy Error Count as PLUS\_COUNT プロキシエラー カウントを P L U S \_ C O U N T として読み取る

6 2 0 Select the Prior Value of the Updated Parameter 更新済みパラメーターの前の値を選択する

6 2 5 Apply the Prior Value of the Updated Parameter to the Circuit 更新済みパラメーターの前の値を回路に適用する

6 3 0 Read the Proxy Error Count as MINUS\_COUNT プロキシエラー カウントを M I N U S \_ C O U N T として読み取る 10

6 4 0 Search Direction = Positive 検索方向 = 正

6 5 0 Search Direction = Negative 検索方向 = 負

6 6 0 Return Search Direction 検索方向を返す

## 図 7

7 0 5 Select Initial Parameter to be Searched 検索される初期パラメーターを選択する

7 1 0 Read Current Value of the Selected Parameter and Store the CurrentValue as PARAM 選択されたパラメーターの現在の値を読み取り、現在の値を P A R A M として格納する 20

7 1 5 Set the Updated Parameter to the Current Value 更新済みパラメーターを現在の値に設定する

7 2 0 Apply the Updated Parameter to the Circuit 更新済みパラメーターを回路に適用する

7 2 5 Read the Proxy Error Count and Store the Proxy Error Count as COUNT プロキシエラー カウントを読み取り、プロキシエラー カウントを C O U N T として格納する

7 3 0 Another Value of the Selected Parameter to be Tested? 選択されたパラメーターの、テストされる別の値はあるか?

7 3 5 Select the Next Value for the Updated Parameter 更新済みパラメーターの次の値を選択する 30

7 4 0 Apply the Updated Parameter to the Circuit 更新済みパラメーターを回路に適用する

7 4 5 Read the Proxy Error Count as NEXT\_COUNT プロキシエラー カウントを N E X T \_ C O U N T として読み取る

7 5 5 Set COUNT = NEXT\_COUNT and Set PARAM = Updated Parameter C O U N T = N E X T \_ C O U N T に設定し、P A R A M = 更新済みパラメーターに設定する

7 6 0 Apply PARAM to the Circuit P A R A M を回路に適用する

7 6 5 Another Parameter to be Tested? テストされる別のパラメーターはあるか?

7 7 0 End 終了

7 7 5 Select the Next Paramter 次のパラメーターを選択する 40

## 図 8

8 0 5 Analog Input アナログ入力

8 0 9 Target ターゲット

8 1 0 Analog Front End Circuit アナログフロントエンド回路

8 1 1 Front End Processing Loops フロントエンド処理ループ

8 1 4 Analog to Digital Converter Circuit アナログ / デジタル変換器回路

8 2 0 DFIR Circuit D F I R 回路

8 3 0 Data Detector Circuit データ検出器回路

8 4 2 Local Interleaver Circuit 局所インターリーバー回路 50

- 8 4 4 Local De-Interleaver Circuit 局所デインターリーバー回路

8 5 0 Central Memory Circuit 中央メモリ回路

8 6 0 Known Data Based Monitor Circuit 既知データに基づくモニター回路

8 6 8 Known Data 既知データ

8 7 0 Data Decoder Circuit Including Global Interleaving/De-Interleaving Circuitry 大域的インターリーブ / デインターリーブ回路部を備えるデータ復号化器回路

8 8 0 De-Interleaver Circuit デインターリーバー回路

8 9 0 Hard Decision Output Circuit 硬判定出力回路

8 9 2 Hard Decision Output 硬判定出力

【図 1】

【図 2】

【図 3】

【図 4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(72)発明者 エム．ホール，ケネス

アメリカ合衆国，カリフォルニア 95060，サンタ クルーズ，60 ブリーマー ドライブ

(72)発明者 エー．ランドレス，マーク

アメリカ合衆国，カリフォルニア 94583，サン ラモン，9965 トルレオン エーヴィ

イー。

審査官 堀 洋介

(56)参考文献 特開2003-006993(JP,A)

特開2001-035085(JP,A)

特開2005-071432(JP,A)

特開2001-034904(JP,A)

特開2005-166200(JP,A)

特表平10-511797(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 11 B 20 / 18