US 20070234159A1

# (19) United States (12) Patent Application Publication (10) Pub. No.: US 2007/0234159 A1 **BUSHARD** et al.

## Oct. 4, 2007 (43) **Pub. Date:**

### (54) METHOD AND APPARATUS FOR TESTING A **RING OF NON-SCAN LATCHES WITH** LOGIC BUILT-IN SELF-TEST

(76) Inventors: LOUIS BERNARD BUSHARD, Rochester, MN (US); Nathan Paul Chelstrom, Cedar Park, TX (US); Naoki Kiryu, Tokyo (JP); David John Krolak, Rochester, MN (US)

> Correspondence Address: **IBM CORP (YA)** C/O YEE & ASSOCIATES PC P.O. BOX 802333 **DALLAS, TX 75380 (US)**

- (21) Appl. No.: 11/278,313

- (22) Filed: Mar. 31, 2006

#### **Publication Classification**

- (51) Int. Cl. G01R 31/28 (2006.01)

- (52)

#### (57)ABSTRACT

A method and apparatus for loading a ring of non-scan latches for a logic built-in self-test. A logic built-in self-test value is loaded into a scannable latch from the logic built-in self-test. An override control signal is asserted in response to loading the logic built-in self-test value into the scannable latch. A non-scan latch is forced to load the logic built-in self-test value from the scannable latch in response to asserting the override control signal. Logic paths in the ring of non-scan latches are exercised. The non-scan latch is part of the logical paths. The test results are captured from the logic paths and the test results are compared against expected test results to determine if the logic paths within the ring of non-scan latches are functioning properly.

#### METHOD AND APPARATUS FOR TESTING A RING OF NON-SCAN LATCHES WITH LOGIC BUILT-IN SELF-TEST

#### BACKGROUND

[0001] 1. Field of the Invention

**[0002]** The present application relates generally to data processing, and more particularly to a computer implemented method and apparatus for testing a ring of non-scan latches with logic built-in self-test.

[0003] 2. Description of the Related Art

**[0004]** Data processing systems use increasingly complex circuitry, logic, and other electronic components to efficiently process data. Many times, it is financially advantageous to build computer chips that may be tested with on board logic built-in self-test (LBIST). Conventional logic built-in self-test allows chips to be tested and reevaluated when installed, during start-up, or at any other time. Logic built-in self-test helps diagnose fabrication problems more effectively, saving time and money.

[0005] However, logic built-in self-test requires the ability to scan or shift data through latch elements of a design in order to load logic built-in self-test patterns and to capture the test results afterwards. The logic built-in self-test test patterns are loaded into the logic to ensure that the logic is functioning properly and to create the expected test data or results. Scannable latches allow data values to be directly loaded to the scannable latch. Non-scan latches are not directly loadable. As a result, a non-scan latch must have a value clocked in. Scannable latches require more area and may be slightly slower than non-scan latches. As a result, it is financially advantageous to use as large a proportion of non-scan latches as possible.

**[0006]** In order to be able to test non-scan latches with logic built-in self-test, the depth of non-scan latches is typically limited to a depth of three or less in a data pipeline. Additionally, no loop-backs from non-scan latches could be tested because such loops prevented loading predictable values in the non-scan latches from predictable scan latches. A loop back refers to an output of a non-scan latch interconnect to an input of another non-scan latch which is located before the non-scan latch with respect to data flow.

[0007] Consequently, a series of non-scan latches or multiple non-scan latches configured in a loop or ring is called a ring of non-scan latches. Testing of this type of circuit has been discouraged because the ring of non-scan latches appears as an infinite number of non-scan latches to the logic built-in self-test. The infinite appearance of the ring of non-scan latches violates the depth limit and no loop requirements of logic built-in self-test. Consequently, testing rings of non-scan latches using logic built-in self-test has been impracticable.

#### SUMMARY

**[0008]** The illustrative embodiments provide a method and apparatus for a logic built-in self-test. A logic built-in self-test value is loaded into a scannable latch from the logic built-in self-test. An override control signal is asserted in response to loading the logic built-in self-test value into the scannable latch. A non-scan latch is forced to load the logic built-in self-test value from the scannable latch in response to asserting the override control signal. Logic paths in the ring of non-scan latches are exercised. The non-scan latch is part of the logical paths. The test results are captured from the logic paths and the test results are compared against expected test results to determine if the logic paths within the ring of non-scan latches are functioning properly.

#### BRIEF DESCRIPTION OF THE DRAWINGS

**[0009]** The novel features believed characteristic of the illustrative embodiments are set forth in the appended claims. The illustrative embodiments themselves, however, as well as a preferred mode of use, further objectives and advantages thereof, will best be understood by reference to the following detailed description of the illustrative embodiments when read in conjunction with the accompanying drawings, wherein:

**[0010]** FIG. **1** is a pictorial representation of a data processing system in which illustrative embodiments may be implemented;

**[0011]** FIG. **2** is a block diagram of a data processing system in which illustrative embodiments may be implemented;

**[0012]** FIG. **3** is a block diagram of a computer chip with logic built-in self-test in accordance with an illustrative embodiment;

**[0013]** FIG. **4** is a block diagram for a current logic pipeline;

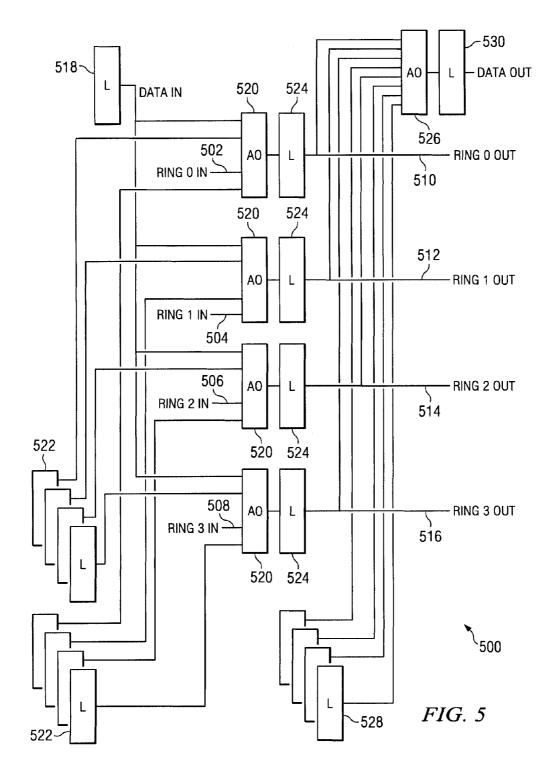

**[0014]** FIG. **5** is a block diagram for a non-scan latch stage in accordance with an illustrative embodiment;

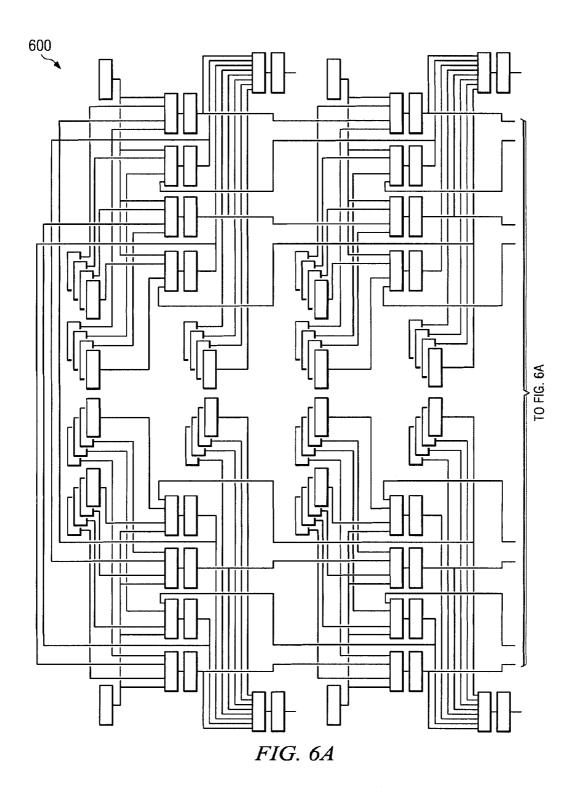

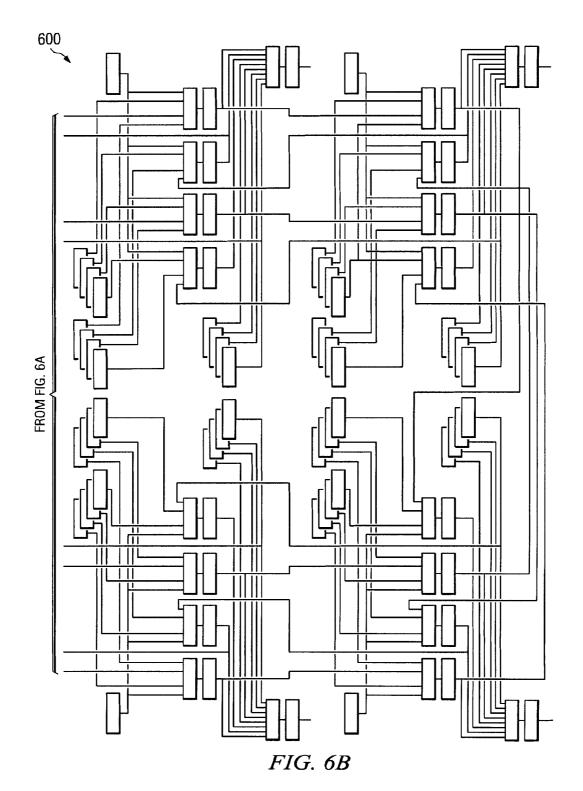

**[0015]** FIGS. **6A-6B** is a block diagram of a non-scan latch ring in accordance with an illustrative embodiment;

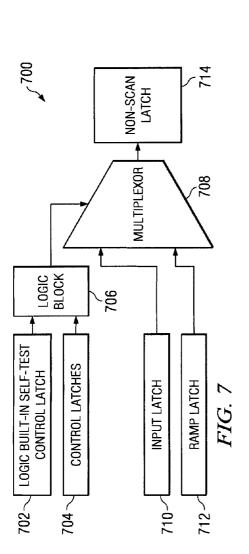

**[0016]** FIG. **7** is a block diagram of a non-scan latch stage for use with logic built-in self-test in accordance with an illustrative embodiment;

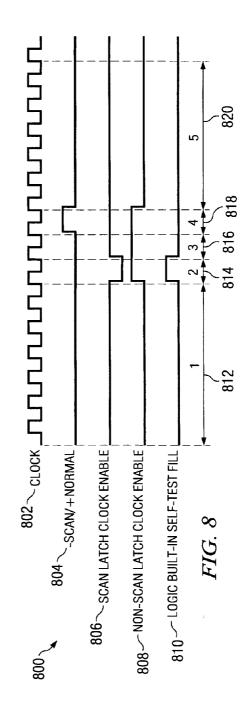

**[0017]** FIG. **8** is a timing diagram illustrating loading a non-scan latch in accordance with an illustrative embodiment; and

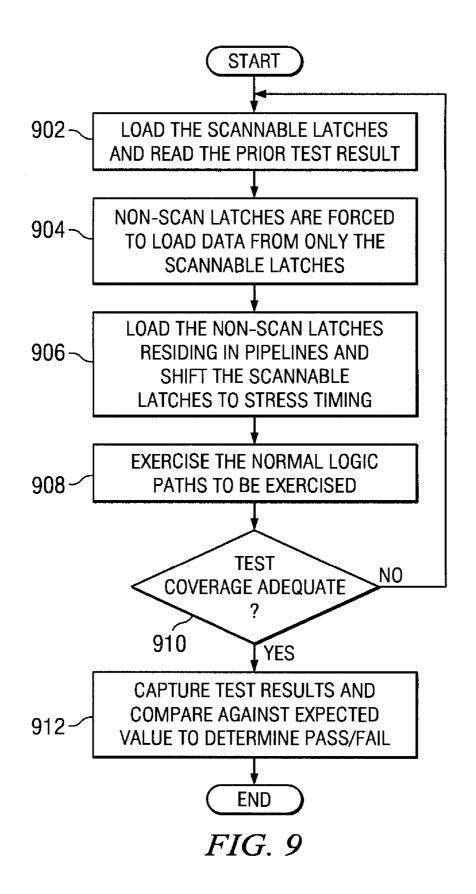

**[0018]** FIG. **9** is a flowchart for loading test pattern values in a non-scan latch ring in accordance with an illustrative embodiment.

#### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

**[0019]** With reference now to the figures and in particular with reference to FIG. **1**, a pictorial representation of a data processing system is shown in which the illustrative embodiments may be implemented. Computer **100** is depicted which includes system unit **102**, video display terminal **104**, keyboard **106**, storage devices **108**, which may include floppy drives and other types of permanent and removable storage media, and mouse **110**. Additional input devices may be included with personal computer **100**, such as, for example, a joystick, touchpad, touch screen, trackball, microphone, and the like. Computer **100** may be any suitable computer, such as an IBM<sup>®</sup> eServer<sup>™</sup> computer or IntelliStation<sup>®</sup> computer, which are products of International Business Machines Corporation, located in Armonk, N.Y. Although the depicted representation shows a personal com-

puter, other embodiments may be implemented in other types of data processing systems, such as a network computer. Computer **100** also preferably includes a graphical user interface (GUI) that may be implemented by means of systems software residing in computer readable media in operation within computer **100**.

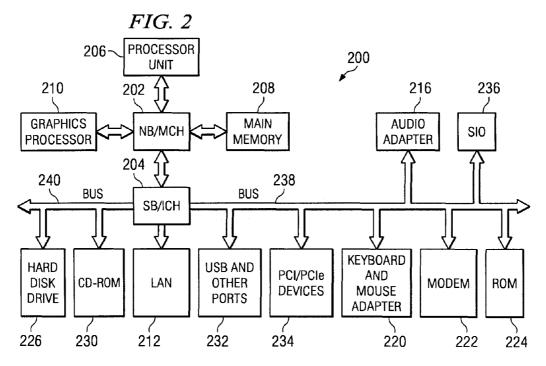

[0020] With reference now to FIG. 2, a block diagram of a data processing system is shown in which illustrative embodiments may be implemented. Data processing system 200 is an example of a computer, such as computer 100 in FIG. 1, in which code or instructions implementing the processes of the illustrative embodiments may be located. In the depicted example, data processing system 200 employs a hub architecture including a north bridge and memory controller hub (MCH) 202 and a south bridge and input/ output (I/O) controller hub (ICH) 204. Processor 206, main memory 208, and graphics processor 210 are coupled to north bridge and memory controller hub 202. Graphics processor 210 may be coupled to the MCH through an accelerated graphics port (AGP), for example.

[0021] In the depicted example, local area network (LAN) adapter 212 is coupled to south bridge and I/O controller hub 204 and audio adapter 216, keyboard and mouse adapter 220, modem 222, read only memory (ROM) 224, universal serial bus (USB) ports and other communications ports 232, and PCI/PCIe devices 234 are coupled to south bridge and I/O controller hub 204 through bus 238, and hard disk drive (HDD) 226 and CD-ROM drive 230 are coupled to south bridge and I/O controller hub 204 through bus 240. PCI/ PCIe devices may include, for example, Ethernet adapters, add-in cards, and PC cards for notebook computers. PCI uses a card bus controller, while PCIe does not. ROM 224 may be, for example, a flash binary input/output system (BIOS). Hard disk drive 226 and CD-ROM drive 230 may use, for example, an integrated drive electronics (IDE) or serial advanced technology attachment (SATA) interface. A super I/O (SIO) device 236 may be coupled to south bridge and I/O controller hub 204.

[0022] An operating system runs on processor 206 and coordinates and provides control of various components within data processing system 200 in FIG. 2. The operating system may be a commercially available operating system such as Microsoft® Windows® XP (Microsoft and Windows are trademarks of Microsoft Corporation in the United States, other countries, or both). An object oriented programming system, such as the Java<sup>TM</sup> programming system, may run in conjunction with the operating system and provides calls to the operating system from Java programs or applications executing on data processing system 200 (Java and all Java-based trademarks are trademarks of Sun Microsystems, Inc. in the United States, other countries, or both).

[0023] Instructions for the operating system, the objectoriented programming system, and applications or programs are located on storage devices, such as hard disk drive 226, and may be loaded into main memory 208 for execution by processor 206. The processes for different embodiments may be performed by processor 206 using computer implemented instructions, which may be located in a memory such as, for example, main memory 208, read only memory 224, or in one or more peripheral devices.

**[0024]** The hardware in FIGS. **1-2** may vary depending on the implementation. Other internal hardware or peripheral

devices, such as flash memory, equivalent non-volatile memory, or optical disk drives and the like, may be used in addition to or in place of the hardware depicted in FIGS. **1-2**. Also, the processes of the illustrative embodiments may be applied to a multiprocessor data processing system.

[0025] In some illustrative examples, data processing system 200 may be a personal digital assistant (PDA), which is generally configured with flash memory to provide nonvolatile memory for storing operating system files and/or user-generated data. A bus system may be comprised of one or more buses, such as a system bus, an I/O bus and a PCI bus. Of course the bus system may be implemented using any type of communications fabric or architecture that provides for a transfer of data between different components or devices attached to the fabric or architecture. A communications unit may include one or more devices used to transmit and receive data, such as a modem or a network adapter. A memory may be, for example, main memory 208 or a cache such as found in north bridge and memory controller hub 202. A processing unit may include one or more processors or CPUs. The depicted examples in FIGS. 1-2 and above-described examples are not meant to imply architectural limitations. For example, data processing system 200 also may be a tablet computer, laptop computer, or telephone device in addition to taking the form of a PDA.

**[0026]** The illustrative embodiments provide for a computer implemented method, apparatus, and computer usable program code for compiling source code. The methods in the depicted embodiments may be performed in a data processing system, such as data processing system **100** shown in FIG. **1** or data processing system **200** shown in FIG. **2**.

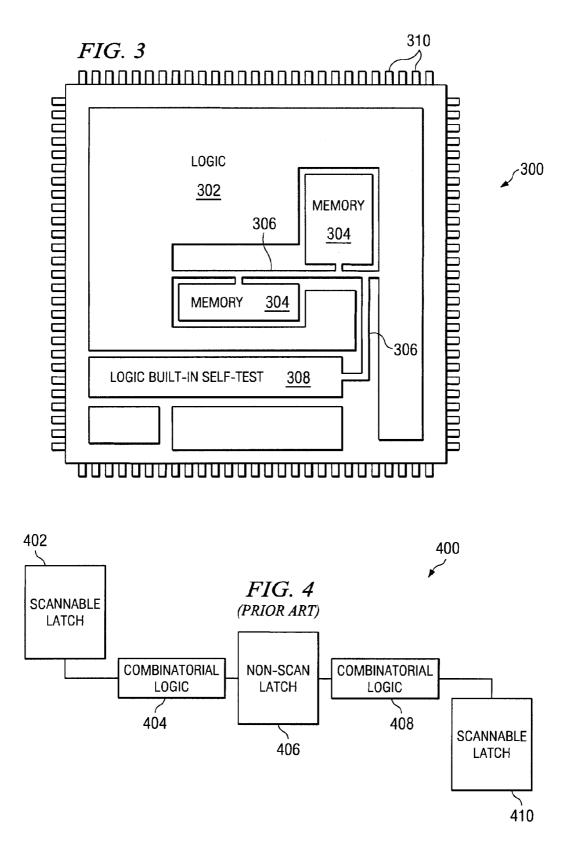

[0027] FIG. 3 is a block diagram of a computer chip with logic built-in self-test in accordance with an illustrative embodiment. FIG. 3 is a chip that may be used in any part of a data processing system, such as data processing system 200 of FIG. 2. Chip 300 may be a processor, communications component, memory, graphics component, or other data processing component. Chip 300 includes logic 302 that implements the functionality of chip 300. Chip 300 may or may not include memory 304. Memory 304 may be used to store, read, and write values in chip 300. Data is passed between memory 304 and logic 302 by bus 306. Logic built-in self-test 308 (LBIST) tests the functionality of chip 300 and ensures that logic 302 processes data properly.

[0028] For example, LBIST 308 may load a logic built-in self-test pattern from memory 304 into logic 302 for testing. The logic built-in self-test pattern includes multiple test values that are loaded into components within logic 302 for functional testing of logic 302. Chip 300 testing may be performed after manufacture, installation, at start-up, or to trouble shoot chip 300. Chip 300 passes the testing if the test data produced by logic 302 match the expected test results. The test results may be in the form of a final signature that is compared against an expected value. Pins 310 may be used to interconnect chip 300 with the data processing system or to interconnect chip 300 with other hardware components.

[0029] Chip 300 may include other components and modules necessary to perform the designated functionality. LBIST 308 contains the apparatus and processes of the illustrative embodiment.

**[0030]** FIG. **4** is a block diagram for a conventional logic pipeline. Pipeline **400** is an example of different latches

within a pipeline stage. Scannable latch **402** inputs data signals into combinatorial logic **404** which in turn inputs the signals to non-scan latch **406**. Non-scan latch **406** inputs the signals to combinatorial logic **408**, which in turn inputs the signals to scannable latch **410**. The data signal is a logic high or a logic low corresponding to a 1 or a 0. The currently available systems allow up to three non-scan latches, such as non-scan latch **406** in pipeline **400** before a scannable latch, such as scannable latch **402** must be inserted. No feedback paths from non-scan latch **406** to its inputs are allowed nor may the output of non-scan latch **406** input to a non-scan latch input at an earlier stage of pipeline **400**.

[0031] During logic built-in self-test testing, the scannable latches, such as scannable latch 402 are loaded or scanned with a test pattern value. Logic built-in self-test logic, such as LBIST 308 of FIG. 3, loads the test pattern in this example. For example, the pattern may be a set of binary values that produce known output results when passed through or processed by components of pipeline 400. Then the non-scan latches, such as non-scan latch 406, are loaded by clocking non-scan latch 406 to load the test pattern value from scannable latch 402 through combinatorial logic 408 to non-scan latch 406. In these examples, one clock pulse per non-scan stage is used to load the non-scan latches. After loading the non-scan latches, one or more clock cycles are run on all the latches to complete the testing using the pattern values. After the clock cycles are run on all the latches, the results of the test are scanned out by logic built-in self-test logic and the next test pattern is scanned in by logic built-in self-test logic.

[0032] To further clarify, the logic built-in self-test tests the functionality of pipeline 400 after loading test pattern values into the scannable latches. In these examples, the test pattern values are loaded during a channel fill operation. This additional operation is a non-scan latch fill step in which non-scan latch 406 is loaded from scannable latches, such as scannable latch 402, in a fixed number of cycles equal to the allowed depth of the non-scan latch 406 fixed number of cycles ensure that non-scan latch 406 contain predictable values prior to the logic built-in self-test functional test.

[0033] In another implementation, additional non-scan latches load non-scan latches, such as non-scan latch 406. When other non-scan latches load non-scan latch 406, non-scan latch 406 cannot be any further than two latches in pipeline 400 away from another scannable latch. The proximity of non-scan latch 406 to scannable latch 402 ensures that enough cycles in length are present to allow all the non-scan latches in pipeline 400 to be loaded.

[0034] A functional test sequence tests non-scan latch 406 after non-scan latch has been loaded. The functional test sequence causes the normal logic paths including combinatorial logic 404 and combinatorial logic 408 to be exercised, with the result loaded into scannable latches, such as scannable latch 410. Typically the functional test runs for one, two, or three cycles prior to completion of the functional test sequence as directed by the logic built-in self-test. The channel fill operation also serves as a channel unload operation in which the state after the tests results of functional test sequence is captured in a component such as a multiple input signature register (MISR) as output from data out scannable latch 410. After the designated number of cycles or iterations has been run, the logic built-in self-test captures the tests results and compares the test results against the expected value to determine pass/fail. Test results are captured by reading the values in data out scannable latch **410**. For example, the value stored in data out scannable latch **410** may be temporarily read and then stored in memory for comparison by logic built-in self-test.

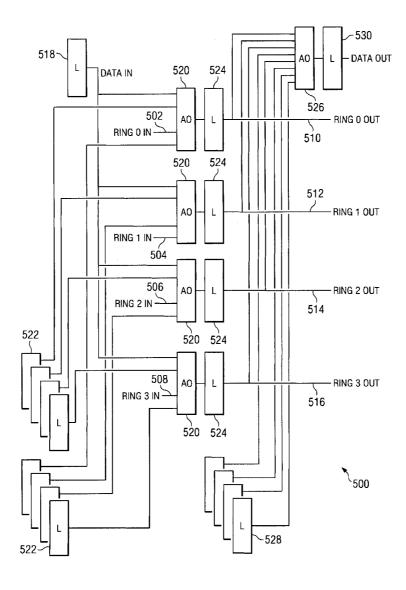

[0035] FIG. 5 is a block diagram for a non-scan latch stage in accordance with an illustrative embodiment. Non-scan latch stage 500 includes various components including exemplary latches and logical gates. Non-scan latch 500 would be untestable when connected in a ring shown in FIG. 6A-6B. Non-scan latch stage 500 includes four rings each with an input and output through non-scan latch stage 500. The ring inputs include ring 0 in 502, ring 1 in 504, ring 2 in 506, and ring 3 in 508. The ring outputs include ring 0 out 510, ring 1 out 512, ring 2 out 514, and ring 3 out 516. Data in latch 518 is a scannable latch with inputs into logic gates 520. Logic gates 520 may be a multiplexor, AND, OR, NAND, NOR, XOR, or other common digital logical gates or combination of gates. Control latches 522 are scannable latches that input data into logic gates 520. Ring 0 in 502, ring 1 in 504, ring 2 in 506, and ring 3 in 508 are also input into logical gates 520.

[0036] Logical gates 520 output passes through ramp latches 524. Ramp latches 524 are non-scan latches. The output of ramp latches 524 passes to logical gate 526. Control latches 528 also have inputs into logical gate 526. The output of logical gate 526 passes to data out latch 530. Data out latch 530 is also a scannable latch.

[0037] Normal logic built-in self-test testing in full scan environments, such as non-scan latch stage 500, includes a channel fill operation. During the channel fill operation, scannable latches such as data in latch 518 may load values from a pseudo random pattern generator (PRPG). Simultaneously, test results or a signature of the prior test are read. The prior test results are typically ignored during the initial load.

[0038] FIG. 6A-6B is a block diagram of a non-scan latch ring in accordance with an illustrative embodiment. Nonscan latch ring 600 includes a ring of non-scan latch stages, such as non-scan latch stage 500 of FIG. 5 interconnected in series to form a ring. The depth of non-scan latch ring 600 appears to be infinite because of the ring architecture as opposed to discrete non-scan latch stages or groups of interconnected non-scan latch stages.

**[0039]** Non-scan latch ring **600** is an exemplary non-scan latch loop. A ring or loop of non-scan latches may take involve different structures or forms in addition to that shown in these examples. Non-scan latch ring is distinguishable by a circular flow of data as outputs of latches, stages, or logic are inputs to other latches, stages or logic.

**[0040]** FIG. 7 is a block diagram of a non-scan latch stage for use with logic built-in self-test in accordance with an illustrative embodiment. Non-scan latch stage 700 may be implemented in a computer chip and more specifically in logic, such as chip 300 and logic 302 of FIG. 3 respectively. Non-scan latch stage 700 is interconnected in a ring to form a ring of non-scan latches, such as non-scan latch ring 600 of FIG. 6. This configuration is easily tested using a logic built-in self-test.

[0041] Logic built-in self-test control latch 702 and control latches 704 are input into logic block 706. Control latches 704 may be control elements, such as control latches 522 of FIG. 5. Logic built-in self-test control latch 702 is connected to logic block 706. Logic block 706 may be logical gates, such as logic gates 520 of FIG. 5. The output of logic block 706 provides a control signal to multiplexor 708. Logic built-in self-test control latch 702 is controlled directly by a logic built-in self-test engine, such as logic built-in self-test 308 of FIG. 3. Multiplexor 708 may be a logic gate, such as logic gate 526 of FIG. 5.

[0042] Multiplexor 708 has two inputs, input latch 710, a scannable latch, and ramp latch 712, a non-scan latch. Logic built-in self-test control latch 702 provides an override control signal that passes through logic block 706 forcing multiplexor 708 to pass the value in input latch 710 through to non-scan latch 714. As a result, at the beginning of a channel fill operation used to load a logic built-in self-test pattern value, a known value is loaded into input latch 710. Logic built-in self-test control latch 702 is used as a control signal to override control latches 704 in order to ensure that input latch 710, a scannable latch with a value of the logic built-in self-test pattern, is loaded into non-scan latch 714. The value in input latch 710 is passed through multiplexor 708 to non-scan latch 714 so that the logic built-in self-test sequence may begin. In other embodiments, logic built-in self-test control latch 702 may be replaced by a scannable latch or other logical component. Additionally, logic built-in self-test logic may be used to pass through the override control signal to logic block 706.

**[0043]** Various illustrative embodiments force a non-scan latch, such as non-scan latch **714** to load a value from a scannable latch, such as input latch **710** so that logic built-in self-test pattern values may be correctly loaded into nonscan latches interconnected in a ring.

[0044] In another illustrative embodiment, non-scan latch 714 may be forced to any known value prior to clocking or executing the first test. As a result, non-scan latch 714 receives the known value and immediately is ready for testing.

[0045] FIG. 8 is a timing diagram illustrating loading a non-scan latch in accordance with an illustrative embodiment. Timing diagram 800 corresponds to a non-scan latch stage, such as non-scan latch stage 700 of FIG. 7. Timing diagram 800 includes various signals, including clock 802, scan 804, scan latch clock enable 806, non-scan latch clock enable 808, and logic built-in self-test fill 810.

[0046] Timing diagram 800 also includes various periods associated with the various signals, including period 1812, period 2814, period 3816, period 4818, period 5820. During period 1812, the logic built-in self-test loads the test pattern and reads the prior test result. The test result is scanned and the pattern values loaded by a logic built-in self-test engine, such as logic built-in self-test 308 of FIG. 3. Period 2814 represents the non-scan latch load. During this step logic built-in self-test fill 810 forces non-scannable latches to load from scannable logic.

[0047] As applied to an exemplary non-scan latch stage, such as non-scan latch stage 700 of FIG. 7, a control signal from logic built-in self-test control latch 702 may be used to pass a value in input latch 710 through multiplexor 708 to non-scan latch 714.

[0048] During period 3816, logic built-in self-test performs a scan shift allowing the logic to be tested at speed during the test cycle of period 4818. The normal logic paths are exercised during period 4818. The test cycle of period 4818 may be multiple cycles. For example, the test cycle is frequently less than four cycles. Period 5820 is the same as period 1812. The test result is read to the logic built-in self-test.

[0049] FIG. 9 is a flowchart for loading test pattern values in a non-scan latch ring in accordance with an illustrative embodiment. FIG. 9 may be implemented in a interconnected ring of non-scan latch stages, such as non-scan latch stage 700 of FIG. 7. The non-scan latch stages may interconnect to form a ring of non-scan latches such as non-scan latch ring 600 of FIG. 6.

**[0050]** The process begins by the logic built-in self-test loading the scannable latches and reading the prior test result (step **902**). The scannable latches are loaded with test pattern values that may be stored in the logic built-in self-test or in a memory controlled by the logic built-in self-test. For example, a logic 1 may be loaded into a scannable latch in step **902**. The scannable latches may be input latches, such as input latch **710** of FIG. **7**. The prior test results of the logic built-in self-test testing of the non-scan latch ring are ignored during step **902** the first time through the loop.

[0051] Next, the logic built-in self-test forces the non-scan latches to load data from only the scannable latches (step 904). Logic built-in self-test forces all non-scan latches with inputs that may come from both scannable and non-scannable latches to load data from only the scannable latches. A non-scan latch, such as logic built-in self-test control latch 702 may be used to force another non-scan latch, such as non-scan latch 714 of FIG. 7 to load a known value for the functional test. The non-scan latch may generate an override control signal that forces a test value through to the latch. For example, the override control signal may be used to force logic between the scannable latch and non-scan latch to pass through the test value stored in the scannable latch.

**[0052]** Next, the process loads the non-scan latches residing in pipelines and shifts the scannable latches to stress timing (step **906**). By stressing timing, the timing response of all logic within the pipeline is tested for conflicts, errors, and unstable logic. As a result, any timing conflicts of components in the logic may cause a different value to be generated for the test results. Incorrect test results indicate that the logic is not functioning correctly for the designed purpose of the logic. Step **906** may be extended enough cycles to allow all the non-scan latches to be loaded for the functional test. The illustrative embodiments allow non-scan latches to be loaded from both non-scan latches and scannable latches. Additionally, non-scan latches within a ring of non-scan latches are not limited to be no more than two latches in the pipeline away from a scannable latch.

[0053] Next, the ring of non-scan latches exercise the normal logic paths to be exercised (step 908). Exercising normal logic paths refers to running or clocking the non-scan circuits as will occur during normal operation of the chip in which the non-scan circuit is embedded. By testing the normal logic paths in step 908, the logic built-in self-test ensures that the ring of non-scan latches produce correct results during practical use. Logic paths represent the dif-

ferent ways data may flow through the ring of non-scan latches. During step **908** the test result are loaded into scannable latches.

[0054] Next, the process determines if the test coverage is adequate (step 910). For example, a programmable limit may be used to control the number of iterations. The logic built-in self-test loop count may be established during design using a test tool. In one example, the test coverage is considered adequate when a number of executions exposes approximately 98 percent of all faults. The number of executions is used by the process in step 910 to ensure that the test coverage is adequate. If the test coverage is not adequate, the process returns to step 902. If the test coverage is adequate in step 910, the process captures the test results and compares against expected value to determine pass/fail (step 912). In these illustrative examples, steps 902-908 may be run for multiple cycles or loops prior to terminating the functional test based on the determination of step 910.

**[0055]** The various illustrative embodiments provide a computer implemented method and apparatus for testing a ring of non-scan latches with logic built-in self-test. Using additional logic built-in self-test logic, non-scan latches are forced to load a logic built-in self-test pattern value from upstream scannable latches. By loading from a non-scan latch or scannable latches, the ring of non-scan latches may be effectively tested using logic built-in self-test.

**[0056]** The illustrative embodiments can take the form of an entirely hardware embodiment, an entirely software embodiment or an embodiment containing both hardware and software elements. The illustrative embodiments are implemented in software, which includes but is not limited to firmware, resident software, microcode, etc.

**[0057]** Furthermore, the illustrative embodiments can take the form of a computer program product accessible from a computer-usable or computer-readable medium providing program code for use by or in connection with a computer or any instruction execution system. For the purposes of this description, a computer-usable or computer readable medium can be any tangible apparatus that can contain, store, communicate, propagate, or transport the program for use by or in connection with the instruction execution system, apparatus, or device.

[0058] The medium can be an electronic, magnetic, optical, electromagnetic, infrared, or semiconductor system (or apparatus or device) or a propagation medium. Examples of a computer-readable medium include a semiconductor or solid state memory, magnetic tape, a removable computer diskette, a random access memory (RAM), a read-only memory (ROM), a rigid magnetic disk and an optical disk. Current examples of optical disks include compact disk-read only memory (CD-ROM), compact disk-read/write (CD-R/ W) and DVD.

**[0059]** A data processing system suitable for storing and/ or executing program code will include at least one processor coupled directly or indirectly to memory elements through a system bus. The memory elements can include local memory employed during actual execution of the program code, bulk storage, and cache memories which provide temporary storage of at least some program code in order to reduce the number of times code must be retrieved from bulk storage during execution. **[0060]** Input/output or I/O devices (including but not limited to keyboards, displays, pointing devices, etc.) can be coupled to the system either directly or through intervening I/O controllers.

**[0061]** Network adapters may also be coupled to the system to enable the data processing system to become coupled to other data processing systems or remote printers or storage devices through intervening private or public networks. Modems, cable modem and Ethernet cards are just a few of the currently available types of network adapters.

**[0062]** The description of the illustrative embodiments have been presented for purposes of illustration and description, and is not intended to be exhaustive or limited to the illustrative embodiments in the form disclosed. Many modifications and variations will be apparent to those of ordinary skill in the art. The embodiment was chosen and described in order to best explain the principles of the illustrative embodiments, the practical application, and to enable others of ordinary skill in the art to understand the illustrative embodiments for various embodiments with various modifications as are suited to the particular use contemplated.

What is claimed is:

**1**. A method for loading a ring of non-scan latches for a logic built-in self-test comprising:

- loading a logic built-in self-test value into a scannable latch from the logic built-in self-test; and

- responsive to loading the logic built-in self-test value into the scannable latch, asserting an override control signal;

- responsive to asserting the override control signal, forcing a non-scan latch to load the logic built-in self-test value from the scannable latch; and

- exercising logic paths in the ring of non-scan latches, wherein the non-scan latch is part of the logical paths; and

- capturing test results from the logic paths and comparing the test results against expected test results to determine if the logic paths within the ring of non-scan latches are functioning properly.

2. The computer implemented method of claim 1, wherein the override control signal is part of logic built-in self-test logic used to force the non-scan latch to load the logic built-in self-test value.

**3**. The computer implemented method of claim 1, further comprising:

shifting the scannable latches to stress timing.

**4**. The computer implemented method of claim 1, wherein the exercising step further comprises:

clocking the logic paths until test coverage of the logical paths is adequate.

**5**. The computer implemented method of claim 1, wherein the override control signal is passed to the non-scan control latch from a logic built-in self-test engine.

**6**. The computer implemented method of claim 1, wherein the logic built-in self-test value is a value of a logic built-in self-test pattern loaded into the ring of non-scan latches to test functionality.

- a plurality of non-scan latch stages, wherein the plurality of non-scan latch stages are interconnected to form the ring of non-scan latches, wherein the plurality of nonscan latch stages includes a plurality of non-scan latches;

- control logic operably connected to at least one of the plurality of non-scan latches, wherein during logic built-in self-test testing, an override control signal passed through the control logic forces the at least one of the plurality of non-scan latches to load a logic built-in self-test value from an input latch operably connected to the at least one of the plurality of non-scan latches, wherein the input latch is a scannable latch.

**8**. The ring of non-scan latches of claim 7, wherein the input latch connects to the at least one of the plurality of non-scan latches through a logic gate.

**9**. The ring of non-scan latches of claim 8, wherein the control logic connects to the at least one of the plurality of non-scan latches through a logic gate.

**10**. The ring of non-scan latches of claim 11, wherein the control logic controls the logic gate.

**11**. The ring of non-scan latches of claim 10, wherein the override control signal controls the control logic.

**12**. The ring of non-scan latches of claim 11, wherein the control logic and logic gate are a logical gate.

**13**. A data processing chip with logic built-in self-test comprising:

- digital logic, wherein the digital logic includes a ring of non-scan latches;

- a logic built-in self-test operably connected to the digital logic;

- wherein the logic built-in self-test in the ring of non-scan latches asserts an override control signal in response to

a scannable latch being loaded with a logic built-in self-test value, wherein the override control signal forces a non-scan latch to load the logic built-in selftest value from the scannable latch for verifying functionality of the ring of non-scan latches and the corresponding digital logic.

14. The data processing chip of claim 13, wherein the chip is any of a processor, communications component, memory, or graphics component.

**15**. The data processing chip of claim 13, wherein the non-scan latch is forced to any known value prior to clocking a first logic built-in self-test pattern for immediately testing the ring of non-scan latches.

**16**. The data processing chip of claim 13, further comprising:

- a memory operably connected to the digital logic for storing and accessing a logic built-in self-test pattern;

- wherein the logic built-in self-test value is a part of the logic built-in self-test pattern.

**17**. The data processing chip of claim 13, wherein a logical gate is operably connected as an input to the non-scan latch.

**18**. The data processing chip of claim 17, wherein the override control signal forces the logical gate to pass the logic built-in self-test value from the scannable latch to the non-scan latch.

**19**. The data processing chip of claim 18, wherein the logical gate is any of an AND, OR, NAND, XOR, and multiplexor.

**20**. The data processing chip of claim 13, wherein results of the logic built-in self-test are captured from the non-scan latch.

\* \* \* \* \*