(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4737470号

(P4737470)

(45) 発行日 平成23年8月3日(2011.8.3)

(24) 登録日 平成23年5月13日(2011.5.13)

(51) Int.Cl.

A63F 7/02 (2006.01)

F 1

A 6 3 F 7/02 3 2 6 Z

A 6 3 F 7/02 3 2 O

請求項の数 3 (全 15 頁)

|            |                                     |           |                                             |

|------------|-------------------------------------|-----------|---------------------------------------------|

| (21) 出願番号  | 特願2009-147748 (P2009-147748)        | (73) 特許権者 | 000148922<br>株式会社大一商会<br>愛知県北名古屋市沖村西ノ川1番地   |

| (22) 出願日   | 平成21年6月22日(2009.6.22)               | (74) 代理人  | 110000028<br>特許業務法人明成国際特許事務所                |

| (62) 分割の表示 | 特願2003-405460 (P2003-405460)<br>の分割 | (72) 発明者  | 市原 高明<br>愛知県西春日井郡西春町大字沖村字西ノ川<br>1番地 株式会社大万内 |

| 原出願日       | 平成15年12月4日(2003.12.4)               | (72) 発明者  | 川上 洋二<br>愛知県西春日井郡西春町大字沖村字西ノ川<br>1番地 株式会社大万内 |

| (65) 公開番号  | 特開2009-207922 (P2009-207922A)       | (72) 発明者  | 中村 昌則<br>愛知県西春日井郡西春町大字沖村字西ノ川<br>1番地 株式会社大万内 |

| (43) 公開日   | 平成21年9月17日(2009.9.17)               |           |                                             |

| 審査請求日      | 平成21年7月21日(2009.7.21)               |           |                                             |

最終頁に続く

(54) 【発明の名称】遊技機

## (57) 【特許請求の範囲】

## 【請求項 1】

遊技の進行に応じて背景画像およびキャラクタ画像と共に複数の図柄画像を変動させて表示する画像表示装置を備え、前記複数の図柄画像の組み合わせに応じて遊技者にとって有利な遊技を実行する遊技機であって、

前記複数の図柄画像を変動させて表示するパターンを指示する変動コマンドを出力する主制御装置と、

前記主制御装置から前記変動コマンドを受け取り、該変動コマンドに基づいて前記画像表示装置に表示される動画像を制御する表示制御装置とを備え、

前記表示制御装置は、

データを取り扱うバスに接続され、前記変動コマンドに応じた動画像フレームの描画を指示する描画指示データを生成する表示制御プロセッサと、

前記表示制御プロセッサから前記描画指示データを受け取り、該描画指示データに基づいて前記動画像フレームを描画する画像表示プロセッサと、

前記バスに接続され、データを記憶する第1および第2のメモリと、

前記バスに接続され、前記第1のメモリから前記第2のメモリへのデータのダイレクトメモリアクセス転送を行う転送コントローラと

を含み、

前記表示制御プロセッサは、前記動画像フレームの描画に用いられる外部画像データを

10

20

生成し、該外部画像データを前記第1のメモリに書き込む手段を含み、

前記転送コントローラは、前記外部画像データが前記第1のメモリに書き込まれた場合、該外部画像データの前記第1のメモリから前記第2のメモリへのダイレクトメモリアクセス転送を、前記画像表示装置に対する垂直同期信号のブランク期間を契機に、前記主制御装置が一出力単位の前記変動コマンドを出力している時間より短い時間で転送可能な転送単位に分割して実行する手段を含み、

前記画像表示プロセッサは、前記描画指示データに基づいて、前記第2のメモリにダイレクトメモリアクセス転送された外部画像データを前記第2のメモリから読み出し、該外部画像データを用いて前記動画像フレームを描画する手段を含む、遊技機。

**【請求項2】**

10

前記画像表示プロセッサ、転送コントローラ、前記第2のメモリは、單一のチップに一体に回路形成されている請求項1に記載の遊技機。

**【請求項3】**

前記外部画像は、前記背景画像、前記キャラクタ画像、前記図柄画像の少なくともいづれかの画像である請求項1または請求項2の遊技機。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、画像表示装置を備えた遊技機に関するものである。

**【背景技術】**

20

**【0002】**

パチンコ機やスロットマシンなどの遊技機には、遊技の進行に応じた動画像を液晶ディスプレイ (Liquid Crystal Display、以下、LCDという)などの画像表示装置に表示することによって、遊技の興趣を高めたものがある。これらの遊技機は、画像表示装置の他、遊技の進行を制御する主制御装置や、遊技の進行に応じた動画像を画像表示装置に表示させる表示制御装置などを備える。

**【0003】**

遊技機の表示制御装置は、主制御装置から出力された表示コマンドに基づいて画像表示装置における動画像の表示態様を制御する表示制御プロセッサと、この表示態様の制御に基づいて画像表示装置によって動画像表示が可能な映像信号を生成する画像表示プロセッサ (Video Display Processor、以下、VDPという)とを備え、表示制御プロセッサ側からVDP側へと種々のデータが転送される。これら転送されるデータは、近年の遊技機に要求される動画像表示の品質の高まりに伴って、比較的大きなデータ量となる場合がある。

30

**【0004】**

従来、データ量が比較的大きなデータについては、表示制御プロセッサの処理負担を軽減するため、表示制御プロセッサ側からVDP側へのデータ転送を、ダイレクトメモリアクセス (Direct Memory Access、以下、DMAという) 転送によって行う遊技機があった。このDMA転送中には表示制御プロセッサの全ての処理が停止するため、実施中の動画像表示に対して表示制御プロセッサの停止が影響しないタイミングでDMA転送を行っていた。下記特許文献1には、表示制御プロセッサ側からVDP側へのDMA転送を行う遊技機が記載されている。

40

**【先行技術文献】**

**【特許文献】**

**【0005】**

**【特許文献1】特開2000-268194号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0006】**

遊技機特有の事情として、主制御装置は、表示制御プロセッサから信号を受け取るとい

50

う形態では、表示コマンドが受信されたか否かを確認できない。そのため、DMA転送中に主制御装置からの表示コマンドの出力が開始され終了してしまった場合には、表示制御プロセッサは、その表示コマンドを受信することができず、取りこぼした表示コマンドに基づいた動画像表示の制御を行うことができない虞があり、設計に多くの時間を費やしていた。

### 【0007】

実施中の動画像表示とは無関係なタイミングで出力される表示コマンドとして、例えば、「あたり」または「はずれ」の表示を行う図柄の変動表示を実施する予定回数の報知（いわゆる保留表示）を画像表示装置で行う遊技機における、その保留表示に関する表示コマンドがある。この保留表示に関する表示コマンドは、遊技球が所定の入賞口に入賞した際に出力されるため、実施中の動画像表示とは無関係なタイミングで出力されることとなる。10

### 【0008】

本発明は、上記の問題を解決することを目的としてなされ、実施中の動画像表示とは無関係なタイミングで主制御装置から出力される表示コマンドの取りこぼしを回避しつつ、表示制御プロセッサ側からVDP側へのDMA転送を実現することができる遊技機を提供することを目的とする。

#### 【課題を解決するための手段】

### 【0009】

上記した課題を解決するため、本発明の遊技機は、遊技の進行に応じて背景画像およびキャラクタ画像と共に複数の図柄画像を変動させて表示する画像表示装置を備え、前記複数の図柄画像の組み合わせに応じて遊技者にとって有利な遊技を実行する遊技機であって20

、前記複数の図柄画像を変動させて表示するパターンを指示する変動コマンドを出力する主制御装置と、

前記主制御装置から前記変動コマンドを受け取り、該変動コマンドに基づいて前記画像表示装置に表示される動画像を制御する表示制御装置とを備え、

前記表示制御装置は、

データをやり取りするバスに接続され、前記変動コマンドに応じた動画像フレームの描画を指示する描画指示データを生成する表示制御プロセッサと、30

前記表示制御プロセッサから前記描画指示データを受け取り、該描画指示データに基づいて前記動画像フレームを描画する画像表示プロセッサと、

前記バスに接続され、データを記憶する第1および第2のメモリと、

前記バスに接続され、前記第1のメモリから前記第2のメモリへのデータのダイレクトメモリアクセス転送を行う転送コントローラとを含み、

前記表示制御プロセッサは、前記動画像フレームの描画に用いられる外部画像データを生成し、該外部画像データを前記第1のメモリに書き込む手段を含み、

前記転送コントローラは、前記外部画像データが前記第1のメモリに書き込まれた場合、該外部画像データの前記第1のメモリから前記第2のメモリへのダイレクトメモリアクセス転送を、前記画像表示装置に対する垂直同期信号のブランク期間を契機に、前記主制御装置が一出力単位の前記変動コマンドを出力している時間より短い時間で転送可能な転送単位に分割して実行する手段を含み、40

前記画像表示プロセッサは、前記描画指示データに基づいて、前記第2のメモリにダイレクトメモリアクセス転送された外部画像データを前記第2のメモリから読み出し、該外部画像データを用いて前記動画像フレームを描画する手段を含むことを特徴とする。ここで、一出力単位の一出力とは、主制御装置が表示制御プロセッサに対して一度に処理可能なデータ量の出力である。

### 【0010】

また、上記した課題を解決するため、上述の発明をDMA転送方法に適用しても良い。

**【0011】**

本発明の遊技機およびDMA転送方法によれば、一出力単位の表示コマンドが出力される時間よりも、一転送単位のDMA転送が行われる時間が短時間であるため、DMA転送中に表示コマンドの出力が開始され終了してしまう事態を回避することができる。その結果、DMA転送中に表示コマンドの出力が開始された場合であっても、そのDMA転送の一転送単位の終了後に再稼動する表示制御プロセッサは、その表示コマンドを受け取ることができる。したがって、実施中の動画像表示とは無関係なタイミングで主制御装置から出力される表示コマンドの取りこぼしを回避しつつ、表示制御プロセッサ側からVDP側へのDMA転送を実現することができる。

10

**【0012】**

上記の構成を有する本発明の遊技機は、以下の態様を探ることもできる。例えば、前記画像表示プロセッサ、転送コントローラ、前記第2のメモリは、单一のチップに一体に回路形成されていても良い。

**【0013】**

また、前記外部画像は、前記背景画像、前記キャラクタ画像、前記図柄画像の少なくともいづれかの画像であっても良い。

**【図面の簡単な説明】**

**【0014】**

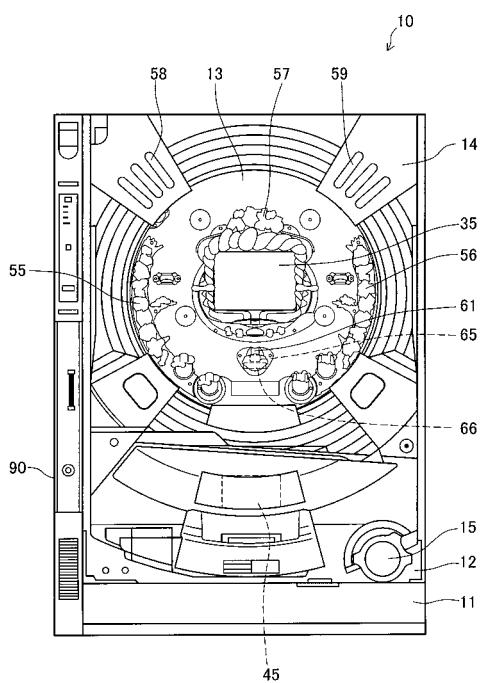

**【図1】**パチンコ機10の正面図である。

20

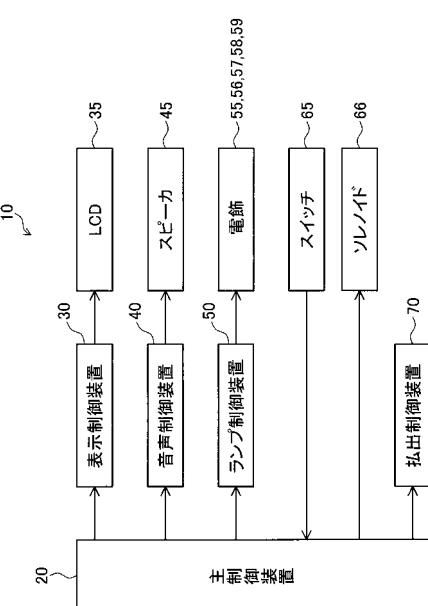

**【図2】**パチンコ機10の電気的な概略構成を機能的に示すブロック図である。

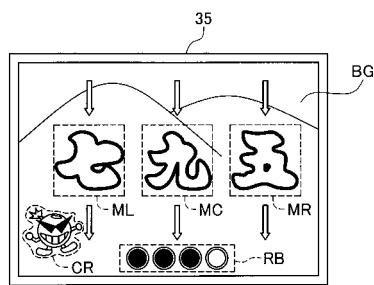

**【図3】**LCD35における動画像表示の一例を示す説明図である。

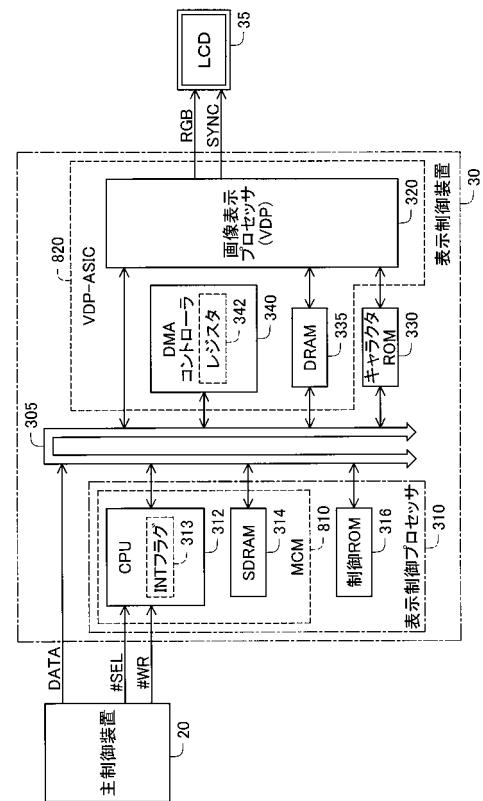

**【図4】**パチンコ機10が備える表示制御装置30の電気的な構成を示すブロック図である。

**【図5】**DMAコントローラ340のレジスタ342の構成を模式的に示す説明図である。

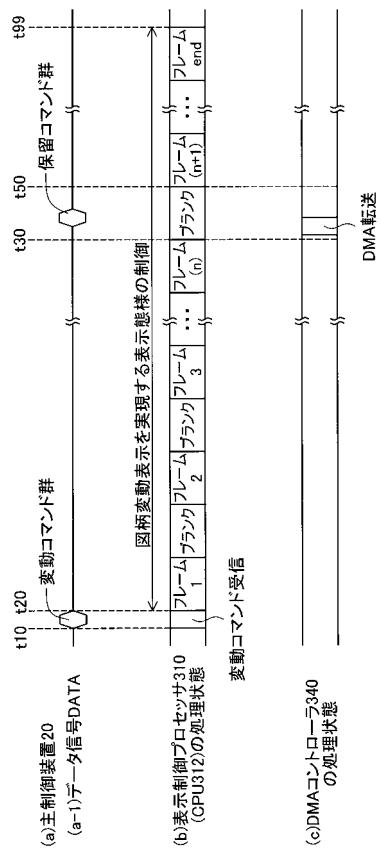

**【図6】**表示制御プロセッサ310における表示コマンドの受信の様子を示す説明図である。

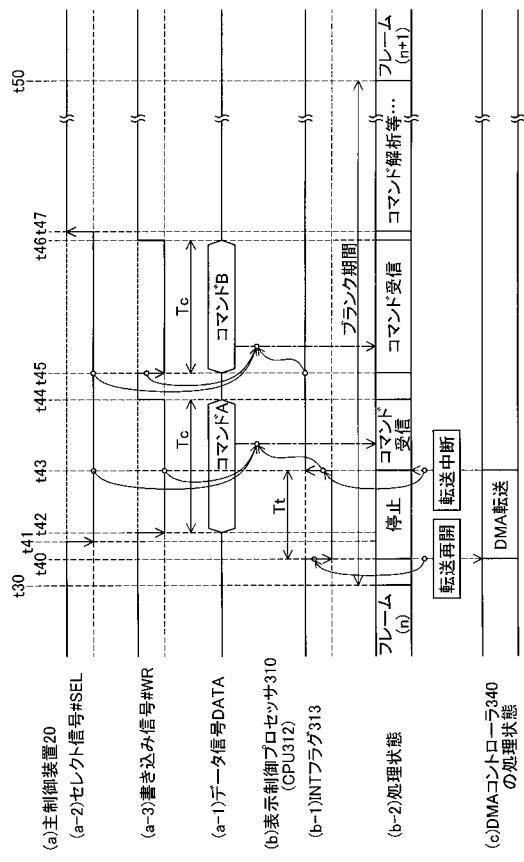

**【図7】**図6におけるタイミングt30～t50の詳細を示す説明図である。

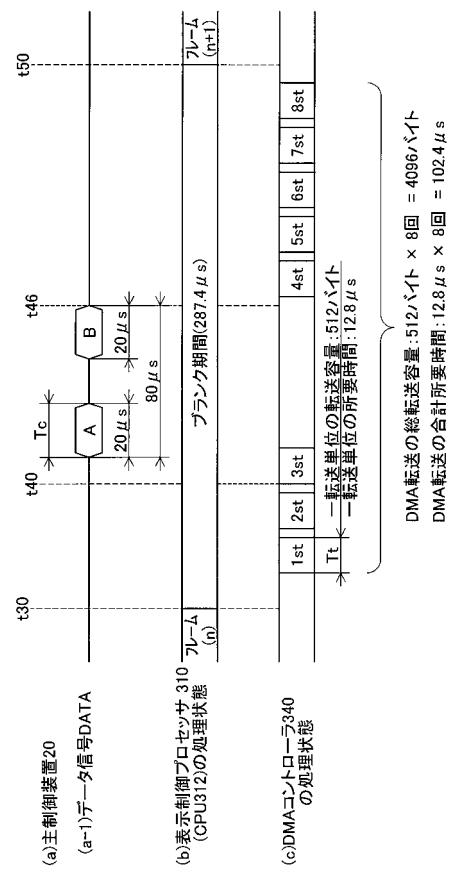

**【図8】**DMA転送の転送容量と所要時間の関係の一例を示す説明図である。

30

**【発明を実施するための形態】**

**【0015】**

以上説明した本発明の構成および作用を一層明らかにするために、以下本発明を適用した遊技機の1つとしてパチンコ機について次の順序で説明する。なお、本明細書において、信号名の先頭に「#」が付されているものは、負論理であることを意味している。「ハイレベル」は2値信号の2つのレベルのうちの「1」レベルを意味し、「ローレベル」は「0」レベルを意味している。

**【0016】**

目次

A . 実施例

40

A - (1) . パチンコ機10の全体構成

A - (2) . パチンコ機10が備える表示制御装置30の構成

A - (3) . 表示制御プロセッサ310における表示コマンドの受信

B . その他の実施形態

**【0017】**

A . 実施例 :

A - (1) . パチンコ機10の全体構成 :

はじめに、本発明の実施例のパチンコ機10の全体構成について説明する。図1は、パチンコ機10の正面図である。パチンコ機10は、パチンコ店の島設備等に固定される外枠11、外枠11に嵌め込まれる内枠12、内枠12の中央上寄りに配置され遊技球によ

50

る遊技が行われる遊技板 13、遊技板 13 の前面に配置され中央部にガラス板を有するガラス枠 14、遊技者による遊技板 13 への遊技球の発射の指示を受け付けるハンドル 15、遊技球の貸し出しを処理するカードユニット 90などを備える。

#### 【0018】

遊技板 13 の中央部には、動画像を表示する画像表示装置である LCD 35 が設けられ、この LCD 35 の下方には、遊技球の入賞を受け付ける入賞口 61 が設けられている。この入賞口 61 は、入賞した遊技球を検知するスイッチ 65、所定の場合に遊技球の導入経路を拡縮するソレノイド 66 を備える。パチンコ機 10 は、発光ダイオード (Light Emitting Diode、以下、LED という) を内蔵し発光する電飾 55, 56, 57, 58, 59 を備える。電飾 55, 56 は遊技板 13 の左右の端にそれぞれ設けられ、電飾 57 は LCD 35 の上部に設けられ、電飾 58, 59 は、ガラス枠 14 の上部の左右にそれぞれ設けられている。内枠 12 の正面中央には、音声を出力するスピーカ 45 が内蔵されている。

10

#### 【0019】

次に、パチンコ機 10 の電気的な概略構成について説明する。図 2 は、パチンコ機 10 の電気的な概略構成を機能的に示すブロック図である。パチンコ機 10 は、遊技の進行を制御する主制御装置 20 を備え、この主制御装置 20 には、表示制御装置 30、音声制御装置 40、ランプ制御装置 50、払出制御装置 70 などの各種制御装置の他、スイッチ 65 やソレノイド 66 などが電気的に接続されている。主制御装置 20 は、スイッチ 65 からの入力信号を受信するとともに、制御信号を出力してソレノイド 66 を駆動する。主制御装置 20 を始めとする種々の制御装置は、図 1 に示した内枠 12 の裏面（図示しない）に設けられている。

20

#### 【0020】

表示制御装置 30 は、遊技の進行に応じた動画像を LCD 35 に表示させる。なお、表示制御装置 30 の詳細については後述する。音声制御装置 40 は、主制御装置 20 の制御信号に基づいてスピーカ 45 における音声の出力を制御する。ランプ制御装置 50 は、主制御装置 20 の制御信号に基づいて電飾 55, 56, 57, 58, 59 の発光を制御する。払出制御装置 70 は、主制御装置 20 の制御信号に基づいて景品球としての遊技球の払い出しを行い、カードユニット 90 の制御信号に基づいて貸出球としての遊技球の払い出しを行う。なお、図 1 および図 2 には、電飾、スイッチ、ソレノイドの全てを示さないが、パチンコ機 10 は、それぞれを複数備える。また、LCD 35 およびスピーカ 45 を複数備えた構成としても良い。

30

#### 【0021】

次に、LCD 35 における動画像表示について説明する。図 3 は、LCD 35 における動画像表示の一例を示す説明図である。パチンコ機 10 は、スイッチ 65 において遊技球の入賞が検知されると、LCD 35 において図柄変動表示を行う。本実施例の図柄変動表示は、LCD 35 における中段部に、左特定図柄表示領域 M\_L、中特定図柄表示領域 M\_C、右特定図柄表示領域 M\_R の 3 つの特定図柄表示領域が、この順に横並びに設けられている。それぞれの特定図柄表示領域には、「一」から「十」の 10 個の漢数字が描かれた特定図柄画像が、LCD 35 の上段から下段へ（図 3 中の矢印方向）、次々に表示された後、いずれかの特定図柄画像が確定表示される。この確定表示された 3 つの特定図柄画像が全て揃った場合には「あたり」を意味し、遊技者にとって有利な遊技が実行される。3 つの特定図柄画像が揃わない場合には「はずれ」を意味し、通常の遊技が継続して実行される。なお、特定図柄画像の確定表示の形態は、横並びに限るものではなく、縦方向や斜め方向に並べても良い。また、特定図柄画像の数は、3 つに限るものではなく、2 つや 3 つ以上の特定図柄画像を並べても良い。また、「あたり」の確定表示の形態は、3 つの特定図柄画像が全て揃う場合ではなく、特定の組み合わせで揃った場合としても良い。

40

#### 【0022】

図柄変動表示を実施中に、更にスイッチ 65 において遊技球の入賞が検知されると、最大 4 つまでの図柄変動表示を記憶し、実施中の図柄変動表示が終了した後、記憶された図

50

柄変動表示を順次実施する。この図柄変動表示を実施する予定回数の報知である保留表示を行うため、LCD35の下段部には、保留表示領域RBが設けられている。本実施例の保留表示は、保留表示領域RBに横一列に4つの円图形が描かれ、1回の図柄変動表示を記憶する毎に、左側の円图形から順に色が反転する。なお、保留表示の形態としては、記憶する図柄変動表示の個数を数字で表しても良い。LCD35では、図柄変動表示や保留表示の他、種々のバックグラウンド画像BGやキャラクタ画像CRが、遊技の進行状態に応じて表示される。

#### 【0023】

A - (2) . パチンコ機10が備える表示制御装置30の構成：

次に、本発明の実施例のパチンコ機10が備える表示制御装置30の構成について説明する。図4は、パチンコ機10が備える表示制御装置30の電気的な構成を示すブロック図である。

#### 【0024】

パチンコ機10の表示制御装置30は、主制御装置20から表示コマンドを受信する。表示コマンドには、LCD35において複数の図柄を用いた図柄変動表示を行う際ににおける図柄変動パターンや各特定図柄画像の種類などを指示する変動コマンドや、LCD35において図柄変動表示の保留表示を行う際ににおける保留数などを指示する保留コマンドなどがある。表示コマンドに関して主制御装置20が表示制御装置30に対して出力する信号としては、表示コマンドを送信するデータ信号DATAと、表示コマンドの送信を実行中であることを伝えるセレクト信号#SELと、表示コマンドの書き込みのタイミングを伝える書き込み信号#WRとがある。

#### 【0025】

パチンコ機10の表示制御装置30は、主制御装置20から受け取った表示コマンドに基づいて、映像信号をLCD35に出力する。映像信号とは、LCD35によって動画像表示が可能な信号であり、赤(Red), 緑(Green), 青(Blue)の各信号から成るRGB信号や、RGB信号をLCD35において展開するための同期信号(SYNC信号)などの信号である。

#### 【0026】

パチンコ機10の表示制御装置30は、主制御装置20から出力された表示コマンドに基づいてLCD35における動画像の表示態様を制御する表示制御プロセッサ310と、この表示制御プロセッサ310の制御に基づいて映像信号を生成するVDP320とを備える。

#### 【0027】

表示制御装置30の表示制御プロセッサ310は、表示態様の制御に必要な動作を規定した制御プログラムを不揮発的に記憶する制御ROM316と、所定のデータを揮発的に記憶可能なSDRAM(Synchronous DRAM)314と、制御ROM316に記憶された制御プログラムをSDRAM314にロードし実行するCPU(Central Processing Unit)312とを備える。CPU312が回路形成されたチップと、SDRAM314が回路形成されたチップとは、MCM(Multi Chip Module)810として単一のパッケージに実装されている。

#### 【0028】

表示制御装置30は、表示制御プロセッサ310やVDP320の他、映像信号の生成に用いられる種々の画像データを不揮発的に記憶するキャラクタROM330と、所定のデータを揮発的に記憶可能なDRAM(Dynamic Random Access Memory)335と、SDRAM314からDRAM335への所定のデータのDMA転送を行うDMAコントローラ340とを備える。VDP320およびDMAコントローラ340, DRAM335は、VDP-AVIC(Application Specified IC)820として1つのチップに一体に回路形成されている。

#### 【0029】

上述したCPU312, SDRAM314, 制御ROM316, VDP320, DMA

10

20

30

40

50

コントローラ340, DRAM335, キャラクタROM330は、表示制御装置30に設けられたバス305にそれぞれ接続されている。

#### 【0030】

CPU312は、主制御装置20などの他の機器からの割り込みの受け付けを制御するINTフラグ313を有し、INTフラグ313がリセットされた状態(ローレベル)では「割り込み禁止状態」となり、INTフラグ313がセットされた状態(ハイレベル)では「割り込み許可状態」となる。つまり、「割り込み許可状態」のCPU312は、主制御装置20からセレクト信号#SELおよび書き込み信号#WRを受け、データ信号DATAに出力された表示コマンドを、バス305を介して受け取ることができる。一方、「割り込み禁止状態」のCPU312は、主制御装置20からの表示コマンドを受信することができない。10

#### 【0031】

CPU312は、表示態様の制御処理を実行することによって、動画像の1フレーム毎の描画指示データを生成し、生成した描画指示データをVDP320に出力する。描画指示データとは、VDP320がキャラクタROM330などに記憶された画像データを用いてRGBデータを生成するためのデータであり、画像データのアドレスや表示位置、色などを指示するデータである。

#### 【0032】

CPU312は、表示態様の制御処理の合間に、外部画像データの生成処理を実行する。この外部画像データの生成処理とは、キャラクタROM330から所定の画像データを読み出し、その画像データにモーフィング処理などの画像処理を施し、その画像処理後の画像データを外部画像データとしてSDRAM314に書き込む処理である。なお、制御ROM316に制御プログラムの他に画像データが記憶されている場合には、外部画像データの生成処理において、キャラクタROM330に記憶された画像データではなく、制御ROM316に記憶された画像データを基に外部画像データを生成することとしても良い。20

#### 【0033】

SDRAM314に記憶された外部画像データは、DMAコントローラ340によってDRAM335にDMA転送される。DRAM335に記憶された外部画像データは、VDP320によって読み出され、RGBデータの生成に用いられる。30

#### 【0034】

CPU312が外部画像データの生成処理を実行するため、キャラクタROM330の容量をいたずらに増加することなく、外部画像データを用いた新たな態様の動画表示を追加することができる。また、CPU312のソフトウェアを更新することによって、VDP320のハードウェアを開発し直すことなく、外部画像データを用いた新たな態様の動画表示を追加することができる。

#### 【0035】

DMAコントローラ340は、CPU312からのDMA転送データを記憶するレジスタ342を有する。図5は、DMAコントローラ340のレジスタ342の構成を模式的に示す説明図である。レジスタ342は、DMA転送先であるDRAM335のアドレスを記憶する転送先設定レジスタと、DMA転送元であるSDRAM314のアドレスを記憶する転送元設定レジスタと、DMA転送を行う外部画像データのデータ容量を記憶する総転送容量設定レジスタと、DMA転送を分割して行う際の一転送単位のデータ容量を記憶する単位転送容量設定レジスタとが設けられている。40

#### 【0036】

このレジスタ342には、CPU312によってDMA転送データが書き込まれ、DMAコントローラ340は、CPU312からDMA転送の開始指示を受けると、レジスタ342に記憶されたDMA転送データに基づいてDMA転送を行う。DMAコントローラ340は、後述するように、主制御装置20が一出力単位の表示コマンドを出力している時間より短い時間で転送可能な転送単位に分割して行う際の一転送単位のデータ容量を記憶する単位転送容量設定レジスタとが設けられている。50

の一出力とは、主制御装置 20 が C P U 312 に対して一度に処理可能なデータ量の出力である。

#### 【0037】

D M A コントローラ 340 のレジスタ 342 に記憶された D M A 転送データを書き換えることによって D M A 転送の分割単位を変更することができるため、パチンコ機 10 のシステム構成に応じて最適な転送単位で D M A 転送を分割して行うことができる。なお、レジスタ 342 の各レジスタの構成は、上記の構成に限るものではなく、「総転送容量設定レジスタ」や「単位転送容量設定レジスタ」の一方を、D M A 転送の分割数を記憶する「分割回数設定レジスタ」に代えた構成としても良い。

#### 【0038】

10

V D P 320 は、1 フレームの描画指示データに基づいて、キャラクタ R O M 330 や D R A M 335 から画像データを読み出し、読み出した画像データを用いて1 フレームの映像信号を生成し L C D 35 に出力する。L C D 35 は、1 フレームの映像信号に基づいて1 フレームの画像表示を行う。この1 フレーム毎の画像表示を繰り返し行うことによって、L C D 35 では遊技の進行に応じた動画像の表示が行われる。前述の L C D 35 において特定図柄画像やバックグラウンド画像 B G , キャラクタ画像 C R を表示するための R G B データの生成には、キャラクタ R O M に予め記憶されている画像データの他、C P U 312 で生成された外部画像データ , V D P 320 で画像処理された画像データなどが用いられる。

#### 【0039】

20

A - (3) . 表示制御プロセッサ 310 における表示コマンドの受信 :

次に、表示制御プロセッサ 310 における表示コマンドの受信について説明する。図 6 は、表示制御プロセッサ 310 における表示コマンドの受信の様子を示す説明図である。

#### 【0040】

図 6 に示すように、表示制御プロセッサ 310 の C P U 312 は、主制御装置 20 が送信した変動コマンド群を受信すると (タイミング t10 ~ t20 ) 、その変動コマンド群に基づいた図柄変動表示を実現するための表示態様の制御を行う (タイミング t20 ~ t99 ) 。この際、C P U 312 は、実現しようとする図柄変動表示に応じて、1 フレーム毎の表示態様の制御の合間であるプランク期間中に、前述した外部画像データの生成を行う。ここで、変動コマンド群とは、1 回の図柄変動表示に関する図柄変動パターンや各特定図柄画像の種類などを指示する複数の変動コマンドから成り、これらの変動コマンドは、主制御装置 20 から一出力単位毎に次々と送信される。

30

#### 【0041】

プランク期間中に生成された外部画像データは、その後のプランク期間中に、D M A コントローラ 340 によって D M A 転送される。外部画像データの D M A 転送は、所定の転送単位に分割して行われる (詳細は後述する) 、外部画像データの全データの D M A 転送は、その外部画像データが V D P 320 によって R G B データの生成に用いられる前に完了する。なお、本明細書において、D M A 転送の中止とは、D M A コントローラ 340 が、D M A 転送すべき全データのうち所定の転送単位分だけの D M A 転送を行った後、C P U 312 にバス 305 を開放し D M A 転送を止めることをいう。D M A 転送の再開とは、D M A 転送が中断された後、D M A コントローラ 340 が、再び C P U 312 からバス 305 の開放を受け、直前の D M A 転送の中止までに転送されていないデータの D M A 転送を引き続き行うことをいう。

40

#### 【0042】

ここで、フレーム (n) とフレーム (n + 1) との間のプランク期間における D M A 転送中に主制御装置 20 から保留コマンド群が送信される場合 (タイミング t30 ~ t50 ) の保留コマンドの受信について詳細に説明する。図 7 は、図 6 におけるタイミング t30 ~ t50 の詳細を示す説明図である。ここで、保留コマンド群とは、1 回分の図柄変動表示の記憶が増えた際の保留表示に関する保留数などを指示する複数の保留コマンドから成り、これらの保留コマンドは、主制御装置 20 から一出力単位毎に次々と送信される。

50

この保留コマンドは、実施中の動画像表示とは無関係なタイミングで主制御装置 20 から送信される。

#### 【 0 0 4 3 】

図 7 に示すように、CPU312 が、フレーム (n) についての表示態様の制御を終えた後 (タイミング t30) 、中断された DMA 転送の再開を DMA コントローラ 340 に指示すると、CPU312 の INT フラグ 313 はリセットされ、CPU312 は「割り込み禁止状態」となる (タイミング t40) 。転送再開の指示を受けた DMA コントローラ 340 は、中断していた DMA 転送を再開し (タイミング t40) 、DMA 転送時間 Tt の間に、前述したレジスタ 342 の設定値に基づいて算出されたワード数 (例えば、16 ビットや 32 ビット) の DMA 転送を行った後、再び DMA 転送を中断する (タイミング t40 ~ t43) 。なお、DMA 転送中には、CPU312 は、バス 305 を DMA コントローラ 340 に開放し、全ての処理を停止した状態となる。

10

#### 【 0 0 4 4 】

DMA 転送中に主制御装置 20 から保留コマンド群の送信が開始されると、セレクト信号 #SEL がリセットされた後 (タイミング t41) 、コマンド出力時間 Tc の間、保留コマンド群における最初の保留コマンド A が、データ信号 DATA に出力されるとともに、書き込み信号 #WR がリセットされる (タイミング t42 ~ t44) 。DMA 転送中は、INT フラグ 313 がリセットされており、CPU312 は保留コマンド A を受信することができない。

20

#### 【 0 0 4 5 】

ここで、DMA 転送時間 Tt の値は、「DMA 転送時間 Tt < コマンド出力時間 Tc」の関係とされている。したがって、DMA 転送の開始直後に保留コマンド A が出力されたとしても、一転送単位の DMA 転送のサイクルが終了した後に、保留コマンド A の出力が継続した状態となる (タイミング t43) 。

#### 【 0 0 4 6 】

DMA 転送の速度が St ビットパーセカンド (bit per second, bps) の場合には、一転送単位の DMA 転送では、「 $S_t \times T_t$ 」ビット (bit) のデータが転送される。つまり、DMA コントローラ 340 は、所定の転送単位として「 $S_t \times T_t$ 」ビット単位に分割して DMA 転送を行う。なお、この所定の転送単位としては、SDRAM 314 と DRAM 335との間で一度に処理可能なデータ量であるワード単位としても良いし、16 ビットや 32 ビット単位などとしても良い。

30

#### 【 0 0 4 7 】

DMA コントローラ 340 が DMA 転送を中断すると、INT フラグ 313 がセットされ、CPU312 が「割り込み許可状態」となる (タイミング t43) 。その後、CPU312 は、リセットされたセレクト信号 #SEL を受けて主制御装置 20 からの割り込みの受け付けを開始し、リセットされた書き込み信号 #WR に従って、データ信号 DATA に出力された保留コマンド A を受信する (タイミング t43 ~ t44) 。

#### 【 0 0 4 8 】

その後、書き込み信号 #WR がセットされるとともに、データ信号 DATA における保留コマンド A の出力が終了しても (タイミング t44) 、セレクト信号 #SEL はリセットされ続けるため、CPU312 は、主制御装置 20 からの割り込みの受け付けを継続する (タイミング t44 ~ t45) 。その後、コマンド出力時間 Tc の間、保留コマンド群における次の保留コマンド B が、データ信号 DATA に出力されるとともに、書き込み信号 #WR がリセットされ、CPU312 は、保留コマンド B を受信する。 (タイミング t45 ~ t46)。

40

#### 【 0 0 4 9 】

その後、主制御装置 20 が保留コマンド群の送信を終え、セレクト信号 #SEL がセットされると、CPU312 は、主制御装置 20 からの割り込みの受け付けを終了する (タイミング t47) 。その後、CPU312 は、受信した保留コマンドの解析や、完了していない DMA 転送の再開などを行った後 (タイミング t50) 、受信した保留コマンドを

50

反映させたフレーム(  $n + 1$  )の表示態様の制御処理を行う。

#### 【0050】

次に、DMA転送の転送容量と所要時間の関係の一例について説明する。図8は、DMA転送の転送容量と所要時間の関係の一例を示す説明図である。なお、図7に示したDMA転送は、図8において分割して行われるDMA転送のうちの3番目に行われる一転送単位のDMA転送に相当する。

#### 【0051】

本実施例では、主制御装置20は、保留コマンド群を80マイクロセカンド(以下、 $\mu s$ と表す)の期間中に出力し、その期間中に2つの保留コマンドA,Bをそれぞれ20 $\mu s$ 間出力する。保留コマンドA,Bは、それぞれ1バイトのデータであり、この保留コマンドA,Bで構成される保留コマンド群は、合計2バイトのデータである。

#### 【0052】

CPU312は、クロック周波数が133メガヘルツ(以下、MHzを表す)であり、287.4 $\mu s$ のブランク期間の間に外部画像データの生成やDMA転送の指示などの処理を行う。このブランク期間は、LCD35に対する垂直方向のSYNC信号のブランク期間に同期した期間である。なお、LCD35は、9インチの表示領域を有し、垂直表示ドットが328ドットであり、垂直総ドットが334ドットであり、水平表示ドットが536ドットであり、水平総ドットが624ドットであり、ドットクロック周波数が13.026MHzである。

#### 【0053】

DMAコントローラ340は、32ビット長のデータ容量あたり100ナノセカンド(以下、nsと表す)を1サイクルとして、SDRAM314からDRAM335へのDMA転送を実行する。

#### 【0054】

本実施例では、「DMA転送時間  $T_t <$  コマンド出力時間  $T_c$ 」とするため、一転送単位の所要時間であるDMA転送時間  $T_t$  は、「コマンド出力時間  $T_c = 20 \mu s$ 」よりも短い12.8 $\mu s$ に設定されている。この間に、DMAコントローラ340は、一転送単位の転送容量として、「 $((12.8 \mu s) \times ((32 \text{ビット}) / (100 ns))) = 4096 \text{ビット}$ 」、すなわち512バイトのデータをDMA転送することができる。なお、CPU312は、少なくとも「 $(20 \mu s) - (12.8 \mu s) = (7.2 \mu s)$ 」の間に保留コマンドAを受信することができる。

#### 【0055】

例えば、データ容量が $64 \times 64$ バイト(すなわち4096バイト)の外部画像データをDMA転送する場合には、DMAコントローラ340は、一転送単位のDMA転送を8回実行することによって、その外部画像データのDMA転送を終えることができる。この場合には、DMA転送の合計所要時間は102.4 $\mu s$ であり、このDMA転送の途中に、保留コマンドの割り込み確認処理や、保留コマンドの受信処理を実行したとしても、1回のブランク期間である287.4 $\mu s$ の間に、その外部画像データのDMA転送を終えることができる。なお、分割したDMA転送の一部が、1回のブランク期間中に終えることができない場合には、次回以降のブランク期間に残りのDMA転送を行えば良い。

#### 【0056】

DMAコントローラ340は、全データのDMA転送を終えると、DMA転送の完了をCPU312に通知する。その後、CPU312は、DMA転送の必要がある場合には、再びDMA転送の設定を行う。

#### 【0057】

以上説明したパチンコ機10によれば、一出力単位の保留コマンドが出力される時間よりも、一転送単位のDMA転送が行われる時間が短時間であるため、DMA転送中に保留コマンドの出力が開始され終了してしまう事態を回避することができる。その結果、DMA転送中に保留コマンドの出力が開始された場合であっても、そのDMA転送の一転

10

20

30

40

50

送単位の終了後に再稼動するCPU312は、その保留コマンドを受け取ることができる。したがって、実施中の動画像表示とは無関係なタイミングで主制御装置20から出力される保留コマンドの取りこぼしを回避しつつ、表示制御プロセッサ310側のSDRAM314からVDP320側のDRAM335へのDMA転送を実現することができる。

#### 【0058】

また、実施中の動画像表示とは無関係なタイミングで主制御装置20から出力される保留コマンドの取りこぼしを回避しつつ、表示制御プロセッサ310で生成したデータ量が比較的大きなビットマップデータなどの外部画像データをDMA転送することができる。

#### 【0059】

また、CPU312は、DMAコントローラ340のレジスタ342に所定のDMA転送データを書き込むことによって、前述した一転送単位に分割してDMA転送をDMAコントローラに行わせることができる。そのため、主制御装置20やLCD35の仕様変更を実施する場合であっても、表示制御装置30におけるソフトウェアおよびハードウェアの大幅な仕様変更を行うことなく、変更後の仕様に適したDMA転送データの設定値を書き込むように制御プログラムを変更することによって、保留コマンドの取りこぼしを回避しつつDMA転送を実現することができる。その結果、主制御装置20やLCD35の仕様変更を実施する際の開発工数を減らすことができる。

10

#### 【0060】

#### B. その他の実施形態 :

以上、本発明の実施の形態について説明したが、本発明はこうした実施の形態に何ら限定されるものではなく、本発明の趣旨を逸脱しない範囲内において様々な形態で実施し得ることは勿論である。例えば、本発明の表示制御装置30を搭載する遊技機は、パチンコ機に限るものではなく、スロットマシンなどの画像表示装置を備えた遊技機に適用しても良い。また、実施中の動画像表示とは無関係なタイミングで主制御装置20から出力される表示コマンドは、保留コマンドに限るものではないことは勿論である。また、CPU312のメインメモリや、VDP320側の外部画像データを記憶するメモリは、SDRAM314やDRAM335に限るものではなく、他のRAMを適用しても良い。また、画像表示装置は、LCDに限るものではなく、CRT(Cathode Ray Tube)ディスプレイ、EL(Electro Luminescent)ディスプレイなどであっても良い。

20

#### 【0061】

30

また、本実施例では、DMAコントローラ340は、CPU312からのDMA転送の開始指示を受けてDMA転送を開始するが、CPU312からのDMA転送データの書き込みを契機にDMA転送を開始するようにしても良い。この場合には、DMAコントローラ340は、垂直SYNC信号のブランク期間に基づいて、CPU312にバス305の開放要求を行うこととしても良い。これによって、CPU312はDMA転送データの書き込みの後に開始指示を行う必要がないため、CPU312の処理効率を向上させることができる。

#### 【符号の説明】

#### 【0062】

10...パチンコ機

40

11...外枠

12...内枠

13...遊技板

14...ガラス枠

15...ハンドル

20...主制御装置

30...表示制御装置

35...LCD

40...音声制御装置

45...スピーカ

50

- 5 0 ... ランプ制御装置

5 5 , 5 6 , 5 7 , 5 8 , 5 9 ... 電飾

6 1 ... 入賞

6 5 ... スイッチ

6 6 ... ソレノイド

7 0 ... 払出制御装置

9 0 ... カードユニット

3 0 5 ... バス

3 1 0 ... 表示制御プロセッサ

3 1 2 ... C P U 10

3 1 3 ... I N T フラグ

3 1 4 ... S D R A M

3 1 6 ... 制御 R O M

3 2 0 ... V D P

3 3 0 ... キャラクタ R O M

3 3 5 ... D R A M

3 4 0 ... D M A コントローラ

3 4 2 ... レジスタ

【図 1】

【図 2】

【図3】

【図4】

【図5】

| <レジスタ342>    |  |

|--------------|--|

| 転送先設定レジスタ    |  |

| 転送元設定レジスタ    |  |

| 総転送容量設定レジスタ  |  |

| 単位転送容量設定レジスタ |  |

【図6】

【図7】

【図8】

---

フロントページの続き

(72)発明者 稲葉 重貴

愛知県西春日井郡西春町大字沖村字西ノ川1番地 株式会社大万内

審査官 鶴岡 直樹

(56)参考文献 特開2002-336490(JP,A)

特開昭63-30951(JP,A)

特開平8-155120(JP,A)

特開2002-186773(JP,A)

(58)調査した分野(Int.Cl., DB名)

A 63 F 7 / 02