Brevet N° **87431**

du 18 janvier 1989

Titre délivré

GRAND-DUCHÉ DE LUXEMBOURG

Monsieur le Ministre

de l'Économie et des Classes Moyennes

Service de la Propriété Intellectuelle

LUXEMBOURG

# Demande de Brevet d'Invention

( 1 )

## I. Requête

La société dite: SIEMENS AKTIENGESELLSCHAFT Berlin und

München, Wittelsbacherplatz 2, D-8000 MÜNCHEN (République

Fédérale d'Allemagne) représentée par Monsieur Jacques de

Muyser agissant en qualité de mandataire

( 2 )

( 3 )

dépose(nt) ce dix-huit janvier 1900 quatre-vingt neuf

( 4 )

à 15 heures, au Ministère de l'Économie et des Classes Moyennes, à Luxembourg:

- la présente requête pour l'obtention d'un brevet d'invention concernant:

"Breitbandsignal-Koppeleinrichtung."

( 5 )

2. la description en langue allemande de l'invention en trois exemplaires;

3. 3 planches de dessin, en trois exemplaires;

4. la quittance des taxes versées au Bureau de l'Enregistrement à Luxembourg, le 18 janvier 1989;

5. la délégation de pouvoir, datée de München le 9 janvier 1989;

6. le document d'ayant cause (autorisation);

déclare(nt) en assumant la responsabilité de cette déclaration, que l'(es) inventeur(s) est (sont):

( 6 )

- Dr. Rüdiger HOFMANN, Fürstenfelder Weg 12,

D-8031 GILCHING (République Fédérale d'Allemagne)

revendique(nt) pour la susdite demande de brevet la priorité d'une (des) demande(s) de

brevet déposée(s) en (8) République Fédérale d'Allemagne

( 7 )

le (9) 8 juin 1988

sous le N° (10) P3819491.0

au nom de (11) la déposante

élit(élisent) domicile pour lui (elle) et, si désigné, pour son mandataire, à Luxembourg

35, Boulevard Royal

( 12 )

sollcite(nt) la délivrance d'un brevet d'invention pour l'objet décrit et représenté dans les annexes susmentionnées,

avec ajournement de cette délivrance à / mois. (13)

Le déposant / mandataire: (14)

## II. Procès-verbal de Dépôt

La susdite demande de brevet d'invention a été déposée au Ministère de l'Économie et des Classes Moyennes,

Service de la Propriété Intellectuelle à Luxembourg, en date du: 18 janvier 1989

à 15 heures

Pr. le Ministre de l'Économie et des Classes Moyennes,

op. d. .

Le chef du service de la propriété intellectuelle,

A 68007

### EXPLICATIONS RELATIVES AU FORMULAIRE DE DÉPÔT

(1) s'il y a lieu "Demande de certificat d'addition au brevet principal, à la demande de brevet principal N° ..... " - (2) inscrire les nom, prénom, profession, adresse du demandeur, lorsque celui-ci est un particulier ou les dénomination sociale, forme juridique, adresse du siège social, lorsque le demandeur est une personne morale - (3) inscrire les nom, prénom, adresse du mandataire autre, conseil en propriété industrielle, muni d'un pouvoir spécial, s'il y a lieu: "représente par ..... agissant en qualité de mandataire" - (4) date de dépôt en toutes lettres - (5) titre de l'invention - (6) inscrire les noms, prénoms, adresses des inventeurs ou l'indication "voir désignation séparée (suivra)", lorsque la désignation se fait ou se fera dans un document séparé, ou encore l'indication "ne pas mentionner", lorsque l'inventeur signe ou signera un document de non-mention à joindre à une désignation présente ou future - (7) brevet, certificat d'addition, modèle d'utilité, brevet européen (CBE), protection internationale (PCT) - (8) Etat dans lequel le premier dépôt a été effectué ou, le cas échéant, Etats désignés dans la demande européenne ou internationale prioritaire - (9) date du premier dépôt - (10) numéro du premier dépôt complet, le cas échéant, par l'indication de l'office récepteur (BE/PCT) - (11) nom du titulaire du premier dépôt - (12) adresse du domicile effectif ou élu au Grand-Duché de Luxembourg - (13) 2. " 12 ou 18 mois - (14)

## BEANSPRUCHUNG DER PRIORITÄT

der Patent/Gbm. - Anmeldung

In: der Bundesrepublik Deutschland

Vom: 8. JUNI 1988 (Nr. P3819491.0)

## PATENTANMELDUNG

in

Luxemburg

Anmelder: SIEMENS AKTIENGESELLSCHAFT Berlin und München

8000 MÜNCHEN (Bundesrepublik Deutschland)

Betr.: "Breitbandsignal-Koppeleinrichtung."

- 1 -

1 Breitbandsignal-Koppeleinrichtung

5 Läßt sich die ECL-Technik durch Eigenschaften wie hohe Arbeitsgeschwindigkeit, (mittel-)hoher Integrationsgrad und (mittel-)hohe Verlustleistung charakterisieren, so zeichnet sich die FET-Technik - bei demgegenüber allerding nur mittleren Arbeitsgeschwindigkeiten - durch einen sehr hohen Integrationsgrad und sehr niedrige Verlustleistungen aus. Diese letzteren Eigenschaften führen zu dem Bemühen, mit integrierten Schaltungen in FET-Technik auch in bislang der Bipolar-10 Technik vorbehaltene Geschwindigkeitsbereiche vorzudringen.

15 Für eine Breitbandsignal-Koppeleinrichtung mit einer Koppelpunktmatrix, die jeweils mit zwei Signalleitern gebildete Matrixeingangsleitungen aufweist, welche einerseits jeweils an zwei Differenz-(Komplementär-)ausgänge einer Eingangsdigitalsignalschaltung angeschlossen sind und andererseits über Koppelpunkte mit ebenfalls jeweils mit zwei Signalleitern gebildeten Matrixausgangsleitungen verbindbar sind, 20 welche jeweils mit ihren beiden Signalleitern zu den beiden Signaleingängen einer mit einem Differenzverstärker gebildeten Ausgangsverstärkerschaltung führen, ist in diesem Zusammenhang (aus EP-A-0 264 046) eine in FET-Technik ausgebildete Koppelpunktmatrix mit in den Koppelpunkten vorgesehenen, 25 jeweils mit zwei jeweils an der Steuerelektrode mit einem Durchschalte- bzw. Sperrsignal beaufschlagten Schalter-Transistoren gebildeten Koppelementpaaren bekannt, deren Schalter-Transistoren jeweils mit einer Hauptelektrode an 30 den einen bzw. anderen Signalleiter der zugehörigen Matrixausgangsleitung angeschlossen sind, die ihrerseits mit einem Ausgangs-Differenzverstärker mit Kippverhalten versehen ist, wobei die Koppelementpaare jeweils zwei jeweils mit einem Schalter-Transistor eine Serienschaltung bildende Vorschalt-35 Transistoren aufweisen, die jeweils mit der Steuerelektrode an den einen bzw. den anderen Signalleiter der zugehörigen Matrixeingangsleitung angeschlossen sind und deren jeweilige der Serienschaltung abgewandte

- 2 -

- 1 Hauptelektrode über einen Abtast-Transistor mit dem einen

Anschluß (Masse) der Betriebsspannungsquelle verbunden ist,

mit deren anderen Anschluß jeder Signalleiter der jeweili-

gen Matrixausgangsleitung jeweils über einen Vorlade-Transi-

5 sistor verbunden ist,

und wobei Vorlade-Transistoren und Abtast-Transistor gegen-

sinnig zueinander jeweils an ihrer Steuerelektrode mit einem

eine Bit-Durchschaltezeitspanne in eine Vorladephase und die

eigentliche Durchschaltephase unterteilenden Koppelfeld-An-

10 steuer-Takt beaufschlagt sind, so daß in jeder Vorphase bei

gesperrtem Abtast-Transistor beide Signalleiter der Matrix-

ausgangsleitung über den jeweiligen Vorlade-Transistor zu-

mindest angenähert auf das an dem genannten anderen Anschluss

der Betriebsspannungsquelle herrschende Potential geladen

15 werden.

- 20 Diese bekannte Breitbandsignal-Koppeleinrichtung bringt zu-

sätzlich zu den Vorteilen, die mit einer in FET-Technik ge-

haltenen Koppelpunktmatrix verbunden sind, den weiteren Vor-

teil mit sich, daß einerseits - bei gesperrtem Koppelpunkt -

auch ohne zusätzliche Dämpfungsmaßnahmen keine störende

Signale über den Koppelpunkt zum Matrixausgang gelangen und

daß andererseits - bei leitendem Koppelpunkt - bei der eigent-

lichen Bitdurchschaltung ggf. stattfindende Umladungen der

25 Matrixausgangsleitung stets von dem dem einen Signalzustand

entsprechenden einen Betriebspotential ausgehend in nur

einer Umladerichtung vor sich gehen und somit bereits mit

einer (dem Überschreiten einer diesem Betriebspotentialwert

benachbarten, dem Kippunkt des Differenzverstärkers entspre-

chenden Schwelle entsprechenden) kleinen Umladung - und da-

30 mit entsprechend schnell - ein eindeutiger Übergang des am

Ausgang der Koppeleinrichtung auftretenden, durchgeschalte-

ten Digitalsignals von dem einen in den anderen Signalzu-

stand verbunden ist.

- 35 Die Erfindung stellt sich nun die Aufgabe, bei einer solchen

Breitbandsignal-Koppeleinrichtung eine weitere Erhöhung der

Arbeitsgeschwindigkeit zu ermöglichen.

- 3 -

1 Die Erfindung betrifft somit eine Breitbandsignal-Koppelein-

richtung mit einer Koppelpunktmatrix in FET-Technik, die je-

weils mit zwei Signalleitern gebildete Matrixeingangsleitun-

gen aufweist, deren jeweils beiden Signalleiter einerseits

5 jeweils an die beiden Differenz-(Komplementär-)ausgänge einer

zwei solche Differenz-(Komplementär-)ausgänge aufweisenden

Eingangsdigitalsignalschaltung angeschlossen sind und anderer-

seits über die mit Koppelementpaaren gebildeten Koppel-

punkte mit ebenfalls jeweils mit zwei Signalleitern gebilde-

10 ten Matrixausgangsleitungen verbindbar sind, die jeweils mit

ihren beiden Signalleitern zu den beiden Signaleingängen

einer mit einem Differenzverstärker mit Kippverhalten gebil-

deten Ausgangsverstärkerschaltung führen,

wobei die Koppelementpaare jeweils mit zwei jeweils an der

15 Steuerelektrode mit einem Durchschalte- bzw. Sperrsignal be-

aufschlagten und mit einer Hauptelektrode an den einen bzw.

anderen Signalleiter der zugehörigen Matrixausgangsleitung

angeschlossenen Schalter-Transistoren gebildet sind,

wobei die Koppelementpaare jeweils zwei jeweils mit einem

20 Schalter-Transistor eine Serienschaltung bildende Vorschalt-

Transistoren aufweisen,

die jeweils mit der Steuerelektrode an den einen bzw. den

anderen Signalleiter der zugehörigen Matrixeingangsleitung

25 angeschlossen sind und deren jeweilige der Serienschaltung

abgewandte Hauptelektrode über einen Abtast-Transistor mit

dem einen Anschluß der Betriebsspannungsquelle verbunden ist,

mit deren anderen Anschluß jeder Signalleiter der jeweili-

gen Matrixausgangsleitung jeweils über einen Vorlade-Transi-

stork 30 verbunden ist,

und wobei Vorlade-Transistoren und Abtast-Transistor gegen-

sinnig zueinander jeweils an ihrer Steuerelektrode mit einem

eine Bit-Durchschaltezeitspanne in eine Vorladephase und die

eigentliche Durchschaltsphase unterteilenden Koppelfeld-An-

steuer-Takt beaufschlagt sind, so daß in jeder Vorphase bei

35 gesperrtem Abtast-Transistor beide Signalleiter der Matrix-

ausgangsleitung über den jeweiligen Vorlade-Transistor zumin-

dest angenähert auf das an dem genannten anderen Anschluß der

- 4 -

1 Betriebsspannungsquelle herrschende Potential geladen

werden; diese Breitbandsignal-Koppeleinrichtung ist erfin-

dungsgemäß dadurch gekennzeichnet, daß die beiden Vorlade-

Transistoren an ihren der jeweiligen Matrixausgangsleitung

5 zugewandten Hauptelektroden miteinander über einen Quertran-

sistor verbunden sind, dessen Steuerelektrode mit den Steuer-

elektroden der Vorlade-Transistoren verbunden ist.

10 Die Erfindung bringt in Verbindung mit dem Vorteil einer Be-

schleunigung der Vorladung der Matrixausgangsleitungen den

weiteren Vorteil einer sehr frühzeitigen Potentialsymmetrie-

rung der Matrixausgangsleitungen mit sich, so daß auch ent-

sprechend frühzeitig die Anfangsbedingungen für eine sichere

15 Verstärkung durch einen nachfolgenden Differenzverstärker

gegeben sind.

20 Eine weitere Erhöhung der Arbeitsgeschwindigkeit der Breit-

bandsignal-Koppeleinrichtung erhält man, wenn in weiterer

Ausgestaltung der Erfindung neben einem matrixeingangs-

leitungs-individuellen Abtast-Transistor ein matrixeingangs-

leitungs-individueller Vorlade-Transistor oder, alternativ

dazu, neben einem matrixausgangsleitungs-individuellen

25 Abtast-Transistor ein matrixausgangsleitungs-individueller

Vorlade-Transistor vorgesehen ist.

25 Weitere Besonderheiten der Erfindung werden aus der nachfol-

genden näheren Erläuterung der Erfindung anhand der Zeich-

nung ersichtlich. Dabei zeigt

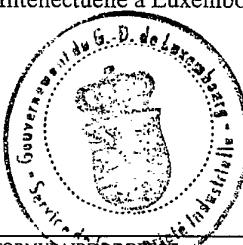

FIG 1 das Schema einer Breitbandsignal-Koppeleinrichtung;

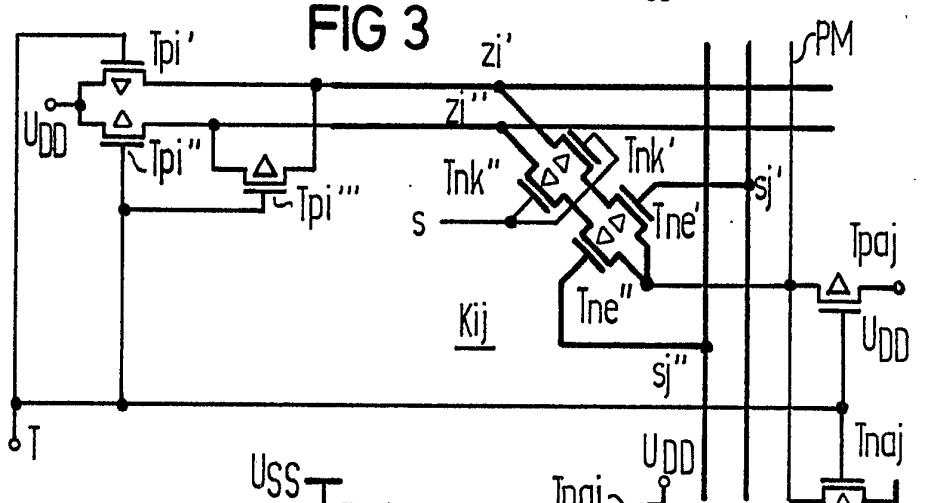

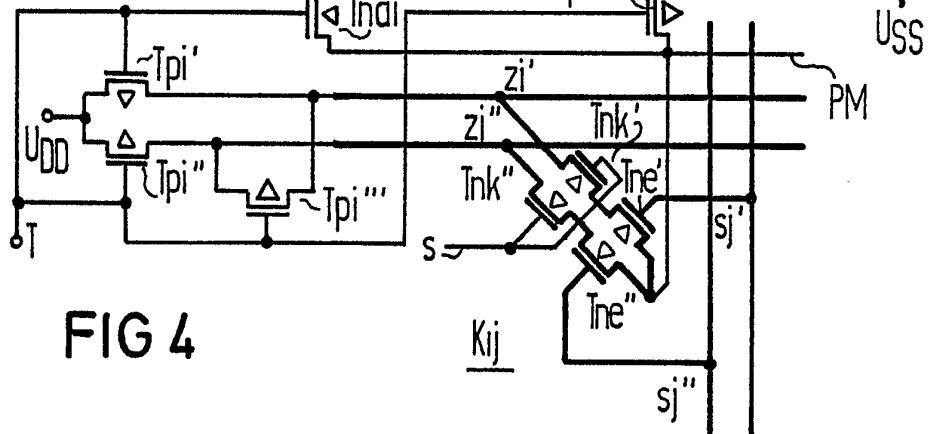

30 FIG 2, FIG 3 und FIG 4 zeigen Beispiele der schaltungs-

technischen Realisierung ihrer Koppelemente gemäß

der Erfindung, und

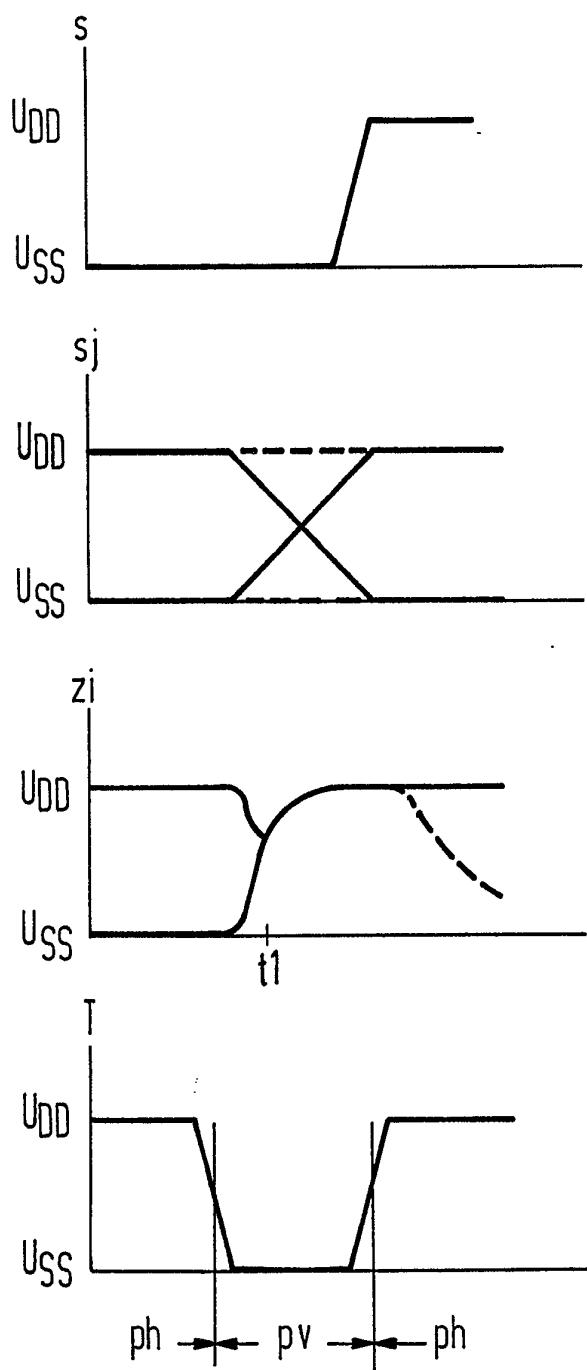

FIG 5 verdeutlicht Signalverläufe darin.

35 In der Zeichnung FIG 1 ist schematisch eine (aus EP-A-0 264-

046) bekannte Breitbandsignal-Koppeleinrichtung skizziert,

an deren zu Spaltenleitungen s1...sj...sn einer Koppelpunkt-

- 5 -

1 matrix führenden Eingängen el...ej...en Eingangsdigital-

signalschaltungen El...Ej...En vorgesehen sind und deren von

Zeilenleitungen z1...zi...zm der Koppelpunktmatrix erreichte

Ausgänge al...ai...am mit Ausgangsverstärkerschaltungen Al...

5 Ai...Am versehen sind. Die Koppelpunktmatrix weist Koppel-

punkte KP11...KPij...KPmn auf, deren Koppelemente, wie

dies beim Koppelpunkt KPij für ein Koppelementepaar Kij

weiter ins Einzelne gehend angedeutet ist, jeweils an einem

10 Steuereingang s von einem (in der Zeichnung nicht mehr darge-

stellten) Adressendecoderelement oder Halte-Speicherelement

gesteuert sein können, was hier indessen nicht weiter erläu-

tert werden muss, da derartige Ansteuerungen von Koppelele-

menten allgemein bekannt sind und entsprechende Erläuterun-

gen sich im Übrigen auch schon an anderer Stelle finden

15 (DE-P 36 31 634.2).

Die Matrixeingangsleitungen (Spaltenleitungen) sind jeweils

mit zwei Signalleitern  $s_1', s_1''$ ; ...;  $s_j', s_j''$ ; ...;  $s_n', s_n''$  ge-

bildet, die jeweils an Komplementär-(Differenz-)ausgänge der

20 jeweils zugehörigen, in FIG 1 als Verstärker mit einem nicht-

invertierenden und einem invertierenden Ausgang, d.h. als sog.

Differenz-Leitungstreiber dargestellten Eingangsdigitalsignal-

schaltung El,...,Ej,..., En angeschlossen sind. Die so einer-

seits von den Komplementärausgängen der Eingangsdigitalsignal-

schaltungen El,..., Ej,..., En ausgehenden Matrixeingangslei-

25 tungen (Spaltenleitungen)  $s_1', s_1''$ ; ...;  $s_j', s_j''$ ; ... ...;  $s_n', s_n''$

sind andererseits über mit Koppelementepaaren (Kij beim

Koppelpunkt KPij in FIG 1) gebildete Koppelpunkte KP11,...,

KPij,...,KPnm mit Matrixausgangsleitungen (Zeilenleitungen)

30 verbunden, die ebenfalls jeweils mit zwei Signalleitern  $z_1'$ ,

$z_1''$ ; ...;  $z_i', z_i''$ ; ...;  $z_m', z_m''$  gebildet sind und mit diesen

jeweils zu den beiden Signaleingängen einer mit einem Diffe-

renzverstärker mit Kippverhalten gebildeten Ausgangsverstär-

kerschaltung Al..., Ai..., Am führen.

35

Ein solcher Differenzverstärker mit Kippverhalten kann mit

einem sog. gated flip-flop realisiert werden, wie es im

- 6 -

1 Prinzip (aus |a| IEEE Journal of Solid-State Circuits,

Oct. 1973, 319...323, Fig.6) und auch schon in verschiedenen

Modifikationen (beispielsweise aus |b| DE-OS 24 22 136,

5 Fig.3 (16') und aus |c| DE-OS 26 08 119, FIG.5) bekannt ist,

wobei ein dort vorgesehener Symmetrietransistor (in |a| und

|b|) ebenso wie dort vorgesehene Vorladetransistoren (in |b|)

bzw. Lasttransistoren (in |c|) zweckmäßigerweise als p-Kanal-

Transistor auszubilden ist; eine weitere Realisierungs-

möglichkeit ist aus EP-A-0 264 046, FIG 5, bekannt.

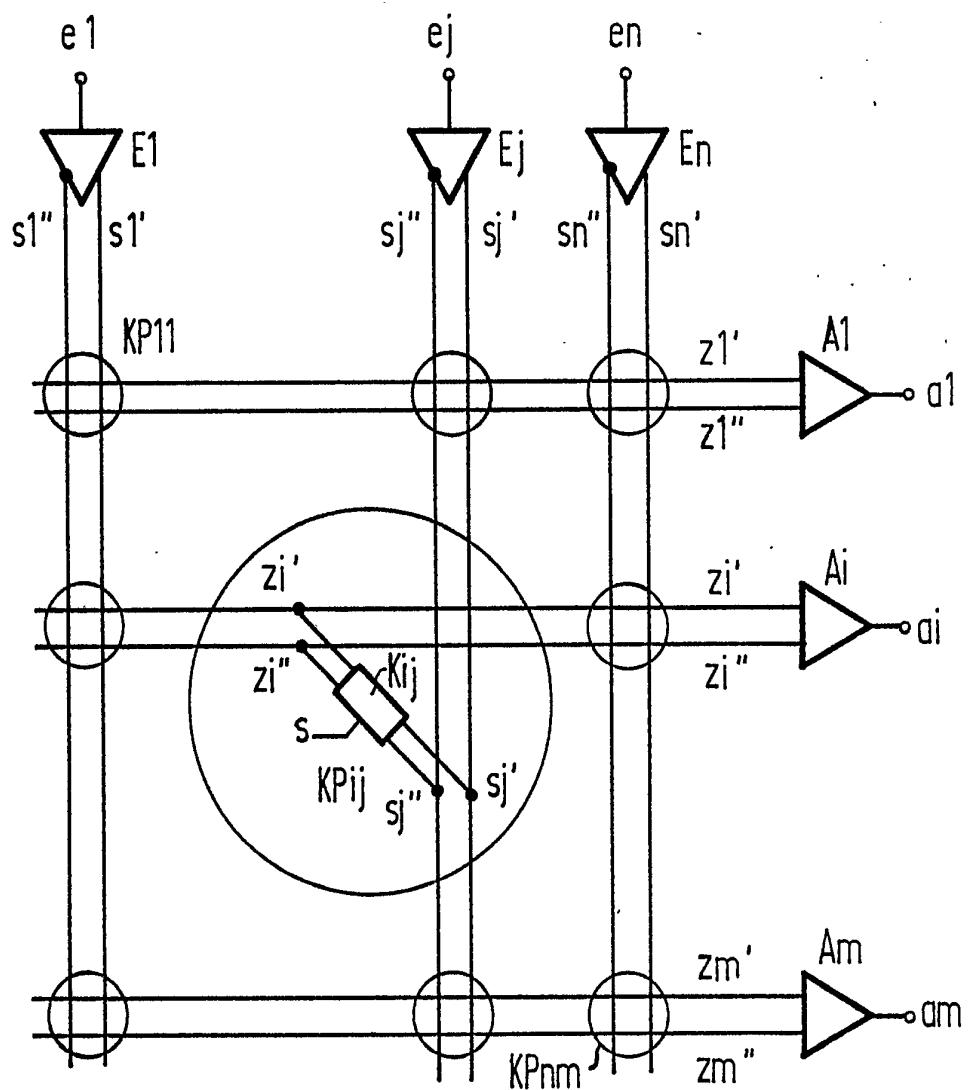

10 Wie die Koppelementepaare ...Kij... schaltungstechnisch

realisiert sein können, wird in FIG 2, FIG 3 und FIG 4 ver-

deutlicht: Die jeweils mit zwei jeweils an der Steuerelek-

trode mit einem Durchschalte- bzw. Sperrsignal beaufschlag-

15 ten und mit einer Hauptelektrode an den einen bzw. den ande-

ren Signalleiter  $z_i'$ ,  $z_i''$  der zugehörigen Matrixausgangslei-

tung angeschlossenen Schalter-Transistoren  $T_{nk'}$ ,  $T_{nk''}$  gebil-

deten Koppelementepaare ...Kij... weisen jeweils zwei je-

weils mit einem Schalter-Transistor  $T_{nk'}$  bzw.  $T_{nk''}$  eine

20 Serienschaltung bildende Vorschalt-Transistoren  $T_{ne'}$  und

$T_{ne''}$  auf, die jeweils mit der Steuerelektrode an den einen

Signalleiter  $s_j'$  bzw. den anderen Signalleiter  $s_j''$  der zuge-

hörigen Matrixeingangsleitung (Spaltenleitung) ...  $s_j...$

angeschlossen sind und deren jeweilige der Serienschaltung

25 abgewandte Hauptelektrode über einen Abtast-Transistor  $T_{na}$

(nämlich  $T_{naij}$  in FIG 2 bzw.  $T_{naj}$  in FIG 3 bzw.  $T_{nai}$  in FIG

4) mit dem einen Anschluß  $U_{SS}$  (Masse) der Betriebsspannungs-

quelle verbunden ist. Mit dem anderen Anschluß  $U_{DD}$  der Be-

triebsspannungsquelle sind die beiden Signalleiter ( $z_i'$ ,  $z_i''$ )

30 der jeweiligen Matrixausgangsleitung (Zeilenleitung) ...  $z_i...$

jeweils über einen Vorlade-Transistor  $T_{pi'}$  bzw.  $T_{pi''}$  ver-

bunden; an ihnen der jeweiligen Matrixausgangsleitung ( $z_i'$ ,

$z_i''$ ) zugewandten Hauptelektroden sind die beiden Vorlade-

Transistoren  $T_{pi'}$ ,  $T_{pi''}$  miteinander über einen Quertransistor

35  $T_{pi'''}$  verbunden, dessen Steuerelektrode mit den Steuerelek-

troden der Vorlade-Transistoren  $T_{pi'}$ ,  $T_{pi''}$  verbunden ist.

- 7 -

1 Wie dies auch FIG 2 verdeutlicht, kann jeweils ein koppel-

elementepaar-individueller Abtast-Transistor Tnaij vorge-

sehen sein; alternativ kann aber auch, wie dies FIG 3 zeigt,

jeweils für alle an ein und derselben Matrixeingangsleitung

5 (Spaltenleitung) ...sj... liegenden Koppelementpaare ein

gemeinsamer und damit matrixeingangsleitungs-individueller

Abtast-Transistor (Tnaj in FIG 3) vorgesehen sein, oder es

kann, wie die aus FIG 4 ersichtlich ist, jeweils ein allen

an ein und derselben Matrixausgangsleitung (Zeilenleitung)

10 ...zi... liegenden Koppelementpaaren gemeinsamer und

damit matrixausgangsleitungs-individueller Abtast-Transistor

(Tnai in FIG 4) vorgesehen sein. Dabei kann, wie dies aus

FIG 3 ersichtlich wird, neben einem matrixeingangsleitungs-

individuellen Abtast-Transistor Tnaj ein matrixeingangs-

15 leitungs-individueller Vorlade-Transistor Tpaj vorgesehen

sein, und es kann, wie dies aus FIG 4 ersichtlich wird,

neben einem matrixausgangsleitungs-individuellen Abtast-

Transistor Tnai ein matrixausgangsleitungs-individueller

Vorlade-Transistor Tpai vorgesehen sein.

20 Wie dies auch in FIG 2 bis FIG 4 angedeutet ist, können - bei

in CMOS-Technik gehaltener Koppelpunktmatrix - die Schalter-

Transistoren Tnk, die Vorschalt-Transistoren Tne und Abtast-

Transistoren Tna n-Kanal-Transistoren sein und die Vorlade-

25 Transistoren Tpi p-Kanal-Transistoren. Vorlade-Transistoren

Tpi und Abtast-Transistoren Tna sind gegensinnig zueinander

jeweils an ihrer Steuerelektrode mit einem eine Bit-Durch-

schaltezeitspanne in in FIG 5, unten, angedeuteter Weise in

30 eine Vorphase pv und eine Hauptphase ph unterteilenden Takt

T beaufschlagt, wie er in FIG 5 in Zeile T angedeutet ist.

35 Während der Vorphase pv (siehe FIG 5, unten) werden jeweils

die beiden Signalleiter (zi',zi") der Matrixausgangsleitun-

gen (Zeilenleitungen) ...zi... Über den jeweiligen Vorlade-

Transistor (Tpi' bzw. Tpi" in FIG 2 bis FIG 4) zumindest an-

genähert auf das  $U_{DD}$ -Betriebspotential geladen, wozu die im

Beispiel durch p-Kanal-Transistoren gebildeten Vorlade-Tran-

- 8 -

1 sistoren  $T_{pi'}$ ,  $T_{pi''}$  im Beispiel durch ein "Low"-Taktsignal  $T$  (siehe FIG 5, Zeile T) leitend gemacht werden.

5 Dabei wird mit der fallenden Flanke des Taktsignals  $T$  zu- gleich auch der zwischen den beiden Signalleitern  $zi'$ ,  $zi''$  liegende Quertransistor  $T_{pi'''}$  leitend mit der Folge eines Kurzschlusses der beiden Signalleiter  $zi'$ ,  $zi''$ , aufgrund dessen es zu Beginn der Vorphase sehr schnell (Zeitpunkt  $t_1$  in FIG 5, Zeile  $zi$ ) zunächst einmal zu einem Potentialaus- gleich der beiden Signalleiter  $zi'$ ,  $zi''$  kommt; danach werden 10 dann beide (nun potentialmäßig ausgeglichene) Signalleiter  $zi'$ ,  $zi''$  über die beiden Vorlade-Transistoren  $T_{pi'}$ ,  $T_{pi''}$  auf das  $U_{DD}$ -Betriebspotential hin geladen, wobei sich die Lade- dauer insgesamt dadurch verkürzt, daß nach dem durch den Quer- 15 transistor  $T_{pi'''}$  herbeigeführten Potentialausgleich nun beide Vorlade-Transistoren  $T_{pi'}$ ,  $T_{pi''}$  in den Aufladungsvorgang ein- bezogen sind.

Zugleich mit der Entriegelung der Vorlade-Transistoren  $T_{pi'}$ , 20  $T_{pi''}$  und des Quertransistors  $T_{pi'''}$  werden die durch n-Kanal- Transistoren gebildeten Abtast-Transistoren  $T_{na}$  ( $T_{naj}$  in FIG 2,  $T_{naj}$  in FIG 3,  $T_{nai}$  in FIG 4) im Beispiel durch das glei- che "Low"-Taktsignal  $T$  im entgegengesetzten Sinne ausgesteu- 25 tert, d.h. gesperrt, so daß die Aufladung der jeweils beiden Signalleiter ( $zi'$ ,  $zi''$ ) der Matrixausgangsleitungen (Zeilen- leitungen) ... $zi...$  unabhängig von der Ansteuerung der jeweili- gen Schalter-Transistoren  $T_{nk'}$ ,  $T_{nk''}$  (in FIG 2 bis FIG 4) und der jeweili- gen Vorschalt-Transistoren  $T_{ne'}$ ,  $T_{ne''}$  (in FIG 2 bis FIG 4) der einzelnen Koppelementepaare ... $K_{ij}...$  vor 30 sich gehen kann. Auf der jeweili- gen Matrixeingangsleitung (Spaltenleitung) ... $sj...$  kann sich dabei ggf. schon das dem jeweils durchzuschaltenden Bit entsprechende Potential auf- bauen (bzw. beibehalten werden), wie dies Zeile  $sj$  in FIG 5 verdeutlicht.

Ist neben einem matrixeingangsleitungs-individuellen Abtast- 35 Transistor  $T_{naj}$  ein matrixeingangsleitungs-individueller Vor- lade-Transistor  $T_{paj}$  vorgesehen, wie dies in FIG 3 dargestellt ist, oder ist neben einem matrixausgangsleitungs-individuellen

- 9 -

1 Abtast-Transistor Tnai ein matrixausgangsleitungs-individu-

eller Vorlade-Transistor Tpai vorgesehen, wie dies in FIG 4

dargestellt ist, so wird während der Vorphase pv über diesen

5 Vorlade-Transistor (Tpaj in FIG 3; Tpai in FIG 4) die Pseudo-

Masseeleitung PM aufgeladen, womit das jeweilige Koppelemente-

tepaar ...Kij... insoweit entlastet wird. Dies führt insbe-

sondere bei umfangreichen Koppelpunktmatrizen mit einer Viel-

zahl von an die Pseude-Masseeleitung PM angeschlossenen Koppel-

elementepaaren ...Kij... zu einer merklichen Ladezeitverkür-

10 zung, die ihrerseits voll in eine entsprechende Erhöhung der

Arbeitsgeschwindigkeit eingeht.

15 Aufgrund der durch den Quertransistor Tpi''' herbeigeführten

Potentialgleichheit der beiden Signalleiter  $z_i'$ ,  $z_i''$  sind

die Anfangsbedingungen für eine sichere Verstärkung durch

den Differenzverstärker  $A_i$  (in FIG 1) entsprechend früher

gegeben, so daß bereits zu einem entsprechend früheren Zeit-

punkt die darauffolgende Hauptphase ph (siehe FIG 5, unten)

einsetzen kann. In dieser Hauptphase ph (siehe FIG 5, unten),

20 werden im Beispiel durch ein "High"-Taktsignal T (siehe FIG 5

Zeile T) Vorlade-Transistoren  $T_{pi'}$ ,  $T_{pi''}$  und Quertransistor

$T_{pi'''}$  (in FIG 2 bis FIG 4) gesperrt und zugleich die Abtast-

Transistoren  $T_{na}$  ( $T_{naij}$  in FIG 2,  $T_{naj}$  in FIG 3,  $T_{nai}$  in FIG

4) entriegelt. Sind nun in einem Koppelementepaar ...Kij...

25 dessen im Beispiel durch n-Kanal-Transistoren gegebene Schalt-

Transistoren  $T_{nk'}$ ,  $T_{nk''}$  (in FIG 2 bis FIG 4) aufgrund eines

am Steuereingang s anliegenden (im Beispiel "High"-) Durch-

schaltesignals (siehe FIG 5, Zeile s) leitend und befindet

sich damit der Koppelpunkt im Durchschaltezustand, so werden

30 jetzt je nach den dem durchzuschaltenden Bit entsprechenden,

auf den beiden Signalleitern  $s_j'$ ,  $s_j''$  der betreffenden Matrix-

eingangsleitung (Spaltenleitung) ... $s_j$ ... herrschenden Signal-

zuständen die Signalleiter  $z_i'$ ,  $z_i''$  der mit dieser Matrixein-

35 gangsleitung (Spaltenleitung) ... $s_j$ ... über das betreffende

Koppelement ..Kij.. verbundene Matrixausgangsleitung (Zei-

lenleitung) ... $z_i$ ... entladen werden bzw. auf dem in der

Vorphase pv angenommenen  $U_{DD}$ -Potential verbleiben:

- 10 -

1 Herrscht auf einem Signalleiter  $sj'$  bzw.  $sj''$  der betreffenden

Matrixeingangsleitung (Spaltenleitung)  $sj$  der "Low"- Signal-

zustand und ist dementsprechend der (n-Kanal-)Vorschalt-Transi-

stor  $Tne'$  bzw.  $Tne''$  (in FIG 2 bis FIG 4) des betreffenden

5 Koppelementepaars  $Kij$  gesperrt, so wird der betreffende

Signalleiter  $zi'$  bzw.  $zi''$  der Matrixausgangsleitung (Zeilen-

leitung)  $zi$  über das betreffende Koppelement dieses Koppel-

elementepaars  $Kij$  nicht entladen, sondern behält, sofern

kein anderer zu dieser Matrixausgangsleitung (Zeilenleitung)

10  $zi$  führender Koppelpunkt sich im Durchschaltezustand befin-

det, den  $U_{DD}$ -Potentialzustand bei.

Herrscht dagegen auf einem gerade betrachteten Signalleiter

15  $sj'$  bzw.  $sj''$  der Matrixeingangsleitung (Spaltenleitung)  $sj$

der "High"-Signalzustand und ist dementsprechend der

Vorschalt-Transistor  $Tne'$  bzw.  $Tne''$  (in FIG 2 bis FIG 4) des

betrachteten Koppelementepaars  $Kij$  ebenso wie der Schalter-

Transistor  $Tnk'$  bzw.  $Tnk''$  und der zugehörige Abtast-

Transistor  $Tna$  leitend, so wird der zugeordnete Signalleiter

20  $zi'$  bzw.  $zi''$  der Matrixausgangsleitung (Zeilenleitung)  $zi$

über dieses Koppelement des Koppelementepaars  $Kij$

entladen und auf das  $U_{SS}$ -Potential gezogen.

Über einen von seinem Steuereingang  $s$  her entriegelten Koppel-

25 punkt wird somit das jeweilige Eingangssignal jeweils inver-

tiert durchgeschaltet.

In den im vorstehenden anhand von FIG 2 bis FIG 4 erläuterten

Ausführungsbeispielen sind die Vorlade-Transistoren ( $Tpi'$ ,

30  $Tpi''$ ) durch p-Kanal-Transistoren gebildet, wobei diese p-

Kanal-Vorlade-Transistoren ( $Tpi$ ) und die durch n-Kanal-Transi-

storen gebildeten Abtast-Transistoren ( $Tna$ ), durch den

unterschiedlichen Kanaltypus bedingt, durch ein und dasselbe

Signal ( $T$ ) gegensinnig zueinander gesteuert werden. In Abwei-

35 chung hiervon ist es aber auch möglich, die Vorlade-Transisto-

ren mit n-Kanal-Transistoren zu realisieren, so daß, wenn

auch die Schalter-Transistoren ( $Tnk$ ), die Vorschalt-Transisto-

- 11 -

1 ren (Tne) und die Abtast-Transistoren (Tna) n-Kanal-Transisto-

ren sind, nur Transistoren ein und desselben Kanaltyps zur

Anwendung kommen; damit dann Vorlade-Transistoren und Abtast-

Transistoren wiederum gegensinnig zueinander jeweils an ihrer

5 Steuerelektrode mit dem Koppelfeld-Ansteuer-Takt beauf-

schlagt werden, ist den Abtast-Transistoren (Tna) wiederum,

wie in den anhand von FIG 2 bis FIG 4 beschriebenen Ausfüh-

rungsbeispielen, das Koppelfeld-Ansteuer-Taktsignal (T)

direkt zuzuführen, den (n-Kanal-)Vorlade-Transistoren dage-

gen das invertierte Koppelfeld-Ansteuer-Taktsignal.

10

15

20

25

30

35

1

## Patentansprüche

1. Breitbandsignal-Koppeleinrichtung mit einer Koppelpunktmatrix in FET-Technik, die jeweils mit zwei Signalleitern (sj', sj") gebildete Matrixeingangsleitungen (sj) aufweist, deren jeweils beiden Signalleiter (sj', sj") einerseits jeweils an die beiden Differenz-(Komplementär-)ausgänge einer zwei solche Differenz-(Komplementär-)ausgänge aufweisenden Eingangsdigitalsignalschaltung (Ej) angeschlossen sind und andererseits über die mit Koppelementpaaren (Kij) gebildeten Koppelpunkte (KPij) mit ebenfalls jeweils mit zwei Signalleitern (zi', zi") gebildeten Matrixausgangsleitungen (zi) verbindbar sind, die jeweils mit ihren beiden Signalleitern (zi', zi") zu den beiden Signaleingängen einer mit einem Differenzverstärker mit Kippverhalten gebildeten Ausgangsverstärkerschaltung (Ai) führen,

wobei die Koppelementpaare (Kij) jeweils mit zwei jeweils an der Steuerelektrode mit einem Durchschalte- bzw. Sperrsignal beaufschlagten und mit einer Hauptelektrode an den einen bzw. anderen Signalleiter (zi', zi") der zugehörigen Matrixausgangsleitung (zi) angeschlossenen Schalter-Transistoren (Tnk', Tnk") gebildet sind,

wobei die Koppelementpaare (Kij) jeweils zwei jeweils mit einem Schalter-Transistor (Tnk', Tnk") eine Serienschaltung bildende Vorschalt-Transistoren (Tne', Tne") aufweisen,

die jeweils mit der Steuerelektrode an den einen bzw. den anderen Signalleiter (sj', sj") der zugehörigen Matrixeingangsleitung (sj) angeschlossen sind und deren jeweilige der Serienschaltung abgewandte Hauptelektrode über einen Abtast-Transistor (Tna) mit dem einen Anschluß (U<sub>SS</sub>, Masse) der Betriebsspannungsquelle verbunden ist, mit deren anderen Anschluß (U<sub>DD</sub>) jeder Signalleiter (zi', zi") der jeweiligen Matrixausgangsleitung (zi) jeweils über einen Vorlade-Transistor (Tpi', Tpi") verbunden ist,

und wobei Vorlade-Transistoren (Tpi', Tpi") und Abtast-

- 13 -

1 Transistor (Tna) gegensinnig zueinander jeweils an ihrer

Steuerelektrode mit einem eine Bit-Durchschaltezeitspanne

in eine Vorladephase (pv) und die eigentliche Durchschalte-

phase (ph) unterteilenden Koppelfeld-Ansteuer-Takt (T)

5 beaufschlagt sind, so daß in jeder Vorphase (pv) bei ge-

sperrtem Abtast-Transistor (Tna) beide Signalleiter der

Matrixausgangsleitung (zi) über den jeweiligen Vorlade-

Transistor (Tp<sup>i</sup>', Tp<sup>i</sup>") zumindest angenähert auf das an dem

10 genannten anderen Anschluss (U<sub>DD</sub>) der Betriebsspannungs-

quelle herrschende Potential geladen werden,

d a d u r c h g e k e n n z e i c h n e t ,

daß die beiden Vorlade-Transistoren (Tp<sup>i</sup>', Tp<sup>i</sup>") an ihren

der jeweiligen Matrixausgangsleitung (zi) zugewandten Haupt-

elektroden miteinander über einen Quertransistor (Tp<sup>i</sup>''') ver-

15 bunden sind, dessen Steuerelektrode mit den Steuerelektroden

der Vorlade-Transistoren (Tp<sup>i</sup>', Tp<sup>i</sup>") verbunden ist.

2. Breitbandsignal-Koppeleinrichtung nach Anspruch 1,

d a d u r c h g e k e n n z e i c h n e t ,

20 daß neben einem matrixeingangsleitungs-individuellen Abtast-

Transistor (Tnaj) ein matrixeingangsleitungs-individueller

Vorlade-Transistor (Tpaj) vorgesehen ist.

3. Breitbandsignal-Koppeleinrichtung nach Anspruch 1,

d a d u r c h g e k e n n z e i c h n e t ,

25 daß neben einem matrixausgangsleitungs-individuellen Abtast-

Transistor (Tnai) ein matrixausgangsleitungs-individueller

Vorlade-Transistor (Tpai) vorgesehen ist.

30

35

FIG 1

**FIG 2**

**FIG 3**

**FIG 4**

FIG 5