(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5160116号

(P5160116)

(45) 発行日 平成25年3月13日(2013.3.13)

(24) 登録日 平成24年12月21日(2012.12.21)

(51) Int.Cl.

F 1

|             |           |

|-------------|-----------|

| HO1L 27/10  | (2006.01) |

| HO1L 27/105 | (2006.01) |

| HO1L 45/00  | (2006.01) |

| HO1L 49/00  | (2006.01) |

| G11C 13/00  | (2006.01) |

|            |     |

|------------|-----|

| HO1L 27/10 | 451 |

| HO1L 27/10 | 448 |

| HO1L 45/00 | A   |

| HO1L 45/00 | Z   |

| HO1L 49/00 | Z   |

請求項の数 20 (全 17 頁) 最終頁に続く

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2007-82210(P2007-82210)    |

| (22) 出願日     | 平成19年3月27日(2007.3.27)        |

| (65) 公開番号    | 特開2007-294925(P2007-294925A) |

| (43) 公開日     | 平成19年11月8日(2007.11.8)        |

| 審査請求日        | 平成22年3月11日(2010.3.11)        |

| (31) 優先権主張番号 | 10-2006-0036408              |

| (32) 優先日     | 平成18年4月21日(2006.4.21)        |

| (33) 優先権主張国  | 韓国(KR)                       |

|           |                                                                                                                                                                |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 390019839<br>三星電子株式会社<br>Samsung Electronics<br>Co., Ltd.<br>大韓民国京畿道水原市靈通区三星路129<br>129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic<br>of Korea |

| (74) 代理人  | 100064908<br>弁理士 志賀 正武                                                                                                                                         |

| (74) 代理人  | 100089037<br>弁理士 渡邊 隆                                                                                                                                          |

| (74) 代理人  | 100108453<br>弁理士 村山 靖彦                                                                                                                                         |

最終頁に続く

(54) 【発明の名称】不揮発性メモリ素子

## (57) 【特許請求の範囲】

## 【請求項1】

半導体基板と、

前記半導体基板の表面付近にそれぞれ形成され、可変抵抗状態を保存する複数の抵抗層と、

前記複数の抵抗層下の前記半導体基板部分にそれぞれ形成され、前記複数の抵抗層とそれぞれ連結された複数の埋め込み電極と、

隣接する前記複数の抵抗層間を連結し、隣接する前記複数の埋め込み電極を連結しないように、前記半導体基板の表面付近に形成された複数のチャネル領域と、

前記半導体基板のチャネル領域上のゲート絶縁膜と、

前記ゲート絶縁膜上に形成され、前記複数の抵抗層上を横切って伸張しているゲート電極とを備えることを特徴とする不揮発性メモリ素子。

## 【請求項2】

前記抵抗層は、両端に印加された電圧により、その抵抗状態が変わる物質を有することを特徴とする請求項1に記載の不揮発性メモリ素子。

## 【請求項3】

前記抵抗層は、Nb<sub>2</sub>O<sub>5</sub>、CrドーピングされたSrTiO<sub>3</sub>、ZrO<sub>x</sub>、GST(GeSb<sub>x</sub>Te<sub>y</sub>)、NiO、ZnO、TiO<sub>2</sub>及びHfOからなる群から選択された少なくとも一つをそれぞれ含むことを特徴とする請求項2に記載の不揮発性メモリ素子。

## 【請求項4】

10

20

前記ゲート絶縁膜は、前記複数の抵抗層上を横切るように伸張していることを特徴とする請求項1に記載の不揮発性メモリ素子。

**【請求項5】**

前記複数の埋め込み電極とそれぞれ連結された複数のビットラインを、前記半導体基板上にさらに備えることを特徴とする請求項1に記載の不揮発性メモリ素子。

**【請求項6】**

前記複数のビットラインは、前記ゲート電極と異なる方向に伸張していることを特徴とする請求項5に記載の不揮発性メモリ素子。

**【請求項7】**

前記複数のビットラインは、前記ゲート電極上に層間絶縁膜を介在して形成されたことを特徴とする請求項5に記載の不揮発性メモリ素子。 10

**【請求項8】**

前記複数の埋め込み電極は、前記半導体基板の一部分を不純物でドーピングしてそれぞれ形成されたことを特徴とする請求項1に記載の不揮発性メモリ素子。

**【請求項9】**

前記半導体基板は、第1導電型の不純物でドーピングされ、前記複数の埋め込み電極は、第2導電型の不純物でドーピングしてそれぞれ形成されたことを特徴とする請求項8に記載の不揮発性メモリ素子。

**【請求項10】**

前記半導体基板は、臨界電圧以上が印加された場合にのみ、電気伝導性を表す金属・絶縁膜転移物質から形成されたことを特徴とする請求項1に記載の不揮発性メモリ素子。 20

**【請求項11】**

前記複数の埋め込み電極は、金属層または金属シリサイド層を含むことを特徴とする請求項1に記載の不揮発性メモリ素子。

**【請求項12】**

ゲート、ソース及びドレインを含む制御素子と、

一端が前記制御素子のソースに連結され、可変抵抗状態を保存することができる第1抵抗ノードと、

一端が前記制御素子のドレインに連結され、可変抵抗状態を保存することができる第2抵抗ノードをそれぞれ備え、マトリックス状に配列された複数の単位セルと。 30

前記複数の単位セルのうち、同じ行に配列された単位セルの前記制御素子のゲートに共通に連結されるように、複数の行に配置された複数のワードラインと、

前記複数の単位セルのうち、隣接する2列に配列された単位セルの隣接する前記第1抵抗ノードの他の端及び前記第2抵抗ノードの他の端に共通に連結されるように、複数の列に配列された複数のビットラインとを備え、

前記第1抵抗ノード及び第2抵抗ノードは、両端に印加された電圧により、その抵抗状態が変わる物質を有することを特徴とする不揮発性メモリ素子。

**【請求項13】**

前記第1抵抗ノード及び第2抵抗ノードは、Nb<sub>2</sub>O<sub>5</sub>、CrドーピングされたSrTiO<sub>3</sub>、ZrO<sub>x</sub>、GST(GeSb<sub>x</sub>Te<sub>y</sub>)、NiO、ZnO、TiO<sub>2</sub>及びHfOからなる群から選択された少なくとも一つをそれぞれ含むことを特徴とする請求項12に記載の不揮発性メモリ素子。 40

**【請求項14】**

前記制御素子は、MOS電界効果トランジスタであることを特徴とする請求項12に記載の不揮発性メモリ素子。

**【請求項15】**

前記複数の単位セルのうち、同じ行に配列された隣接した2単位セルの隣接した前記第1抵抗ノードの他の端及び前記第2抵抗ノードの他の端は、互いに直接連結されたことを特徴とする請求項12に記載の不揮発性メモリ素子。

**【請求項16】**

複数の単位層構造が複数の層に積層され、前記複数の単位層構造のそれぞれは、半導体基板と、前記半導体基板の表面付近にそれぞれ形成され、可変抵抗状態を保存する複数の抵抗層と、前記複数の抵抗層下の前記半導体基板部分にそれぞれ形成され、前記複数の抵抗層とそれぞれ連結された複数の埋め込み電極と、隣接する前記複数の抵抗層間を連結し、隣接する前記複数の埋め込み電極を連結しないように、前記半導体基板の表面付近に形成された複数のチャネル領域と、前記半導体基板のチャネル領域上のゲート絶縁膜と、前記ゲート絶縁膜上に形成され、前記複数の抵抗層上を横切って伸張しているゲート電極とを備えることを特徴とする不揮発性メモリ素子。

10

#### 【請求項 17】

前記複数の単位層構造それぞれの前記抵抗層は、両端に印加された電圧により、その抵抗状態が変わることを特徴とする請求項 1\_6 に記載の不揮発性メモリ素子。

#### 【請求項 18】

前記複数の単位層構造それぞれの前記抵抗層は、Nb<sub>2</sub>O<sub>5</sub>、CrドーピングされたSrTiO<sub>3</sub>、ZrO<sub>x</sub>、GST(GeSb<sub>x</sub>Te<sub>y</sub>)、NiO、ZnO、TiO<sub>2</sub>及びHfOからなる群から選択された少なくとも一つをそれぞれ含むことを特徴とする請求項 1\_7 に記載の不揮発性メモリ素子。

20

#### 【請求項 19】

前記複数の単位層構造のうち、第1層の単位層構造の前記半導体基板は、シリコンウェーハを有し、第2層以上の単位層構造の前記半導体基板は、金属・絶縁体転移物質を有することを特徴とする請求項 1\_6 に記載の不揮発性メモリ素子。

#### 【請求項 20】

前記複数の単位層構造の前記半導体基板は互いに連結され、前記複数の単位層構造の前記ゲート電極は、互いに連結されたことを特徴とする請求項 1\_6 に記載の不揮発性メモリ素子。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、半導体素子に係り、特に抵抗ノードを利用した不揮発性メモリ素子、その動作方法及びその製造方法に関する。

30

##### 【背景技術】

##### 【0002】

不揮発性メモリ素子、例えば、相変化メモリ( P R A M )素子または抵抗メモリ( R R A M )素子は、抵抗ノードの可変抵抗状態を利用して動作する。最近、高容量のデータ処理を要する半導体製品の増加で、このような不揮発性メモリ素子の集積度の増大または動作ビットの増加が要求されている。例えば、マルチ・ビットで動作可能な不揮発性メモリ素子に対する必要性が増大している。

##### 【0003】

一方、不揮発性メモリ素子は、前述のように、高容量化されると共に、高速度化されている。すなわち、高容量のデータを処理するためには、速いデータ処理速度が要求されている。従って、不揮発性メモリ素子の動作速度の増加、例えば、フラッシュメモリ素子のようなブロック消去( block erasing )またはフラッシュ・イレーズ( flash erasing )特性が要求されている。

40

##### 【0004】

また、不揮発性メモリ素子の集積度の増大により、動作電流を減少させるための努力が行われている。しかし、抵抗ノードを利用した不揮発性メモリ素子は、比較的高い動作電流を必要としている。動作電流の減少は、抵抗ノードの可変抵抗状態に影響を及ぼしうる。従って、従来の不揮発性メモリ素子は、動作電流を減少させるにおいて、その限界を有

50

している。

#### 【0005】

例えは、P R A Mは、相変化抵抗体の結晶状態の変化による抵抗変化を利用してデータを保存する。しかし、P R A Mの結晶状態を変化させるためには、高い電流密度が必要であり、これにより動作電流が高まるという問題がある。このような動作電流の増大は、短チャネル効果 (short channel effect) を誘発し、P R A Mの集積度の上昇に障害になる。従って、相変化抵抗体の結晶状態の変化領域を減少させ、少ない動作電流で高い電流密度を得ようとする努力が行われている。

#### 【発明の開示】

##### 【発明が解決しようとする課題】

10

#### 【0006】

従って、本発明が解決しようとする技術的課題は、前述の問題点を克服するためのものであり、低い動作電流、高集積化及び高速度化を提供できる不揮発性メモリ素子を提供するところにある。

本発明が解決しようとする他の技術的課題は、前記不揮発性メモリ素子の高速度の動作方法を提供するところにある。

本発明が解決しようとするさらに他の技術的課題は、前記不揮発性メモリ素子の経済的な製造方法を提供するところにある。

#### 【課題を解決するための手段】

#### 【0007】

20

前記技術的課題を達成するための本発明の一様態による不揮発性メモリ素子は、半導体基板を備える。可変抵抗状態を保存する複数の抵抗層は、前記半導体基板の表面付近にそれぞれ形成される。複数の埋め込み電極 (buried electrode) は、前記複数の抵抗層下の前記半導体基板部分にそれぞれ形成され、前記複数の抵抗層とそれぞれ連結される。複数のチャネル領域は、隣接する前記複数の抵抗層間を連結し、隣接する前記複数の下部電極を連結しないように、前記半導体基板の表面付近に形成される。ゲート絶縁膜は、前記半導体基板のチャネル領域上に提供される。そして、ゲート電極は、前記ゲート絶縁膜上に形成され、前記複数の抵抗層上を横切って伸張している。

#### 【0008】

前記本発明の一例で、前記抵抗層は、両端に印加された電圧により、その抵抗状態が変わる物質を有することができる。さらに、前記抵抗層は、N b<sub>2</sub>O<sub>5</sub>、CrドーピングされたS r T i O<sub>3</sub>、Z r O<sub>x</sub>、G S T ( G e S b<sub>x</sub> T e<sub>y</sub> )、N i O、Z n O、T i O<sub>2</sub>及びH f Oからなる群から選択された少なくとも一つをそれぞれ含むことができる。

30

前記本発明の他の例で、前記不揮発性メモリ素子は、前記複数の埋め込み電極とそれ連結された複数のビットラインを前記半導体基板上にさらに備えることができる。

#### 【0009】

前記技術的課題を達成するための本発明の他の様態による不揮発性メモリ素子は、複数の層に積層された複数の単位層構造を含む。前記複数の単位層構造のそれぞれは、半導体基板と、前記半導体基板の表面付近にそれぞれ形成され、可変抵抗状態を保存する複数の抵抗層と、前記複数の抵抗層下の前記半導体基板部分にそれぞれ形成され、前記複数の抵抗層とそれ連結された複数の埋め込み電極と、隣接する前記複数の抵抗層間を連結し、隣接する前記複数の下部電極を連結しないように、前記半導体基板の表面付近に形成された複数のチャネル領域と、前記半導体基板のチャネル領域上のゲート絶縁膜と、前記ゲート絶縁膜上に形成され、前記複数の抵抗層上を横切って伸張しているゲート電極とを備える。

40

#### 【0010】

前記技術的課題を達成するための本発明のさらに他の様態による不揮発性メモリ素子は、マトリックス状に配列された複数の単位セルを含む。前記複数の単位セルは、ゲート、ソース及びドレインを含む制御素子と、一端が前記制御素子のソースに連結され、可変抵抗状態を保存することができる第1抵抗ノードと、一端が前記制御素子のドレインに連結

50

され、可変抵抗状態を保存することができる第2抵抗ノードとをそれぞれ備える。複数のワードラインは、前記複数の単位セルのうち、同じ行に配列された単位セルの前記制御素子のゲートに共通に連結されるように、複数の行に配置される。そして、複数のビットラインは、前記複数の単位セルのうち、隣接する2列に配列された単位セルの隣接する前記第1抵抗ノードの他の端及び前記第2抵抗ノードの他の端に共通に連結されるように、複数の列に配列される。

#### 【0011】

前記他の技術的課題を達成するための本発明の一様態による不揮発性メモリ素子の動作方法は、前記不揮発性メモリ素子を利用する。プログラム段階で、前記複数の抵抗層のうち、隣接する2つの抵抗層にデータを保存する。そして、フラッシュ・イレーズ段階で、前記複数の抵抗層のうち、所定数の抵抗層に保存されたデータを同時に消す。10

前記本発明の一例で、前記フラッシュ・イレーズ段階は、前記ゲート電極にターンオン電圧を印加する段階と、前記所定数の抵抗層のうち、両エッジにある2つの抵抗層に連結された埋め込み電極間に、イレーズ電圧を印加する段階とを含むことができる。

#### 【0012】

前記さらに他の技術的課題を達成するための本発明による不揮発性メモリ素子の製造方法は、次の段階を含む。半導体基板の表面付近に複数のチャネル領域を限定する。前記複数のチャネル領域間の前記半導体基板内に、前記複数のチャネル領域より深く複数の埋め込み電極を形成する。前記複数の埋め込み電極上に、前記複数のチャネル領域の端部と連結されるように、可変抵抗状態を保存する複数の抵抗層をそれぞれ形成する。前記半導体基板のチャネル領域上にゲート絶縁膜を形成する。そして、前記ゲート絶縁膜上に、前記複数の抵抗層上を横切って伸張しているゲート電極を形成する。20

#### 【発明の効果】

#### 【0013】

本発明による不揮発性メモリ素子は、抵抗層とチャネル領域との接触面積を非常に小さくできる。従って、少ない動作電流で相変化領域に相変化に必要なだけの電流密度を供給できる。例えば、リセット電流を従来よりも1/10以下ほどに減少させることができる。

また、本発明による不揮発性メモリ素子は、高い集積度を有することができる。すなわち、従来には、制御素子と電極構造とが別途に平行して形成されたが、本発明による不揮発性メモリ素子は、制御素子と電極構造とが統合された構造を有する。30

#### 【0014】

また、本発明の実施形態による不揮発性メモリ素子の動作方法は、高速度のフラッシュ・イレーズ速度を有する。従って、不揮発性メモリ素子の動作速度が速まりうる。

また、本発明の実施形態による不揮発性メモリ素子の製造方法は、制御素子と電極構造とを同時に形成できる。従って、製造段階で高コストを占めるフォトリソグラフィ段階の数を減らすことができ、その結果、製造コストを減らすことができる。

#### 【発明を実施するための最良の形態】

#### 【0015】

以下、添付した図面を参照しつつ、本発明による望ましい実施形態について説明することにより、本発明について詳細に説明する。しかし、本発明は、以下で開示される実施形態に限定されるものではなく、互いに異なる多様な形態に具現され、単に本実施形態は、本発明の開示を完全なものにし、当業者に発明の範疇を完全に明らかにするために提供されるものである。図面での構成要素は、説明の便宜のためにその大きさが誇張されていることがある。40

#### 【0016】

本発明の実施形態による不揮発性メモリ素子は、抵抗ノードまたは抵抗層を利用してデータを保存することができる。従って、本発明の実施形態による不揮発性メモリ素子は、その抵抗ノードまたは抵抗層の種類により、他の名称で呼ばれることもある。例えば、本発明の実施形態による不揮発性メモリ素子は、PRAM素子またはRRAM素子を含むこ50

とができるが、本発明の範囲は、このような名称に制限されるものではない。

#### 【0017】

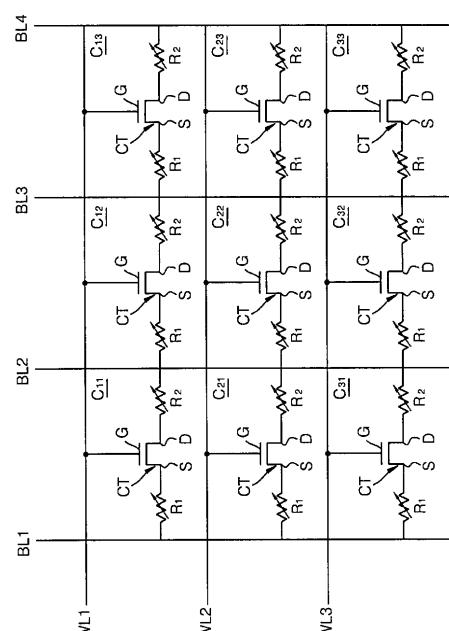

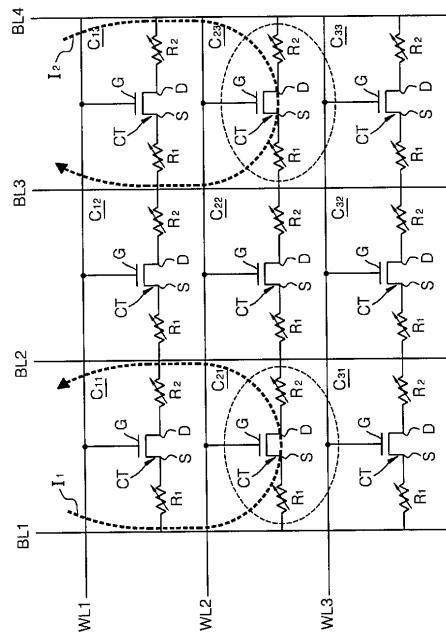

図1は、本発明の一実施形態による不揮発性メモリ素子の配置を示す回路図である。

図1を参照すれば、不揮発性メモリ素子は、マトリックスに配列された複数の単位セル  $C_{11}, C_{12}, C_{13}, C_{21}, C_{22}, C_{23}, C_{31}, C_{32}, C_{33}$  を備える。単位セル  $C_{11}, C_{12}, C_{13}, C_{21}, C_{22}, C_{23}, C_{31}, C_{32}, C_{33}$  は、複数のビットライン  $BL_1, BL_2, BL_3, BL_4$  及び複数のワードライン  $WL_1, WL_2, WL_3$  によって限定され、制御素子  $CT$ 、第1抵抗ノード  $R_1$  及び第2抵抗ノード  $R_2$  をそれぞれ備える。

#### 【0018】

10

制御素子  $CT$  は、ゲート  $G$ 、ソース  $S$  及びドレイン  $D$  を有することができる。第1抵抗ノード  $R_1$  は、その一端が制御素子  $CT$  のソース  $S$  に連結され、第2抵抗ノード  $R_2$  は、その一端が制御素子  $CT$  のドレイン  $D$  に連結されうる。複数のワードライン  $WL_1, WL_2, WL_3$  は、互いに異なる行に配列され、対応する行の制御素子  $CT$  のゲート  $G$  に共通に連結されうる。複数のビットライン  $BL_1, BL_2, BL_3, BL_4$  は、互いに異なる列に配列され、隣接する第1抵抗ノード  $R_1$  及び第2抵抗ノード  $R_2$  に共通に連結される。

#### 【0019】

20

例えば、第1ワードライン  $WL_1$  は、第1行に配列された単位セル  $C_{11}, C_{12}, C_{13}$  の制御素子  $CT$  のゲート  $G$  に共通に連結されるように、第1行に配列されうる。第2ワードライン  $WL_2$  及び第3ワードライン  $WL_3$  も、第1ワードライン  $WL_1$  と類似の方法でそれぞれ第2行及び第3行にそれぞれ配列されうる。

#### 【0020】

また、第1ビットライン  $BL_1$  は、第1列に配列された単位セル  $C_{11}, C_{21}, C_{31}$  の第1抵抗ノード  $R_1$  の他の端に共通に連結されうる。第2ビットライン  $BL_2$  は、第1列に配列された単位セル  $C_{11}, C_{21}, C_{31}$  の第2抵抗ノード  $R_2$  の他の端及び第2列に配列された単位セル  $C_{12}, C_{22}, C_{32}$  の第1抵抗ノード  $R_1$  の他の端に共通に連結されうる。第3ビットライン  $BL_3$  及び第4ビットライン  $BL_4$  にも、第1ビットライン  $BL_1$  及び第2ビットライン  $BL_2$  と類似の原理が適用されうる。

#### 【0021】

30

制御素子  $CT$  は、スイッチング素子として動作し、例えば、MOS電界効果トランジスタ(MOSFET)を含むことができる。ゲート  $G$  は、ソース  $S$  及びドレイン  $D$  間の電気的な連結を制御できる。例えば、ゲート  $G$  にターンオン電圧が印加されれば、ソース  $S$  及びドレイン  $D$  は、電気的に連結されうる。ソース  $S$  及びドレイン  $D$  は、電流の流れによって便宜的に付けられた名称であるだけであり、互いに入れ替わって呼ばれることがあることは自明である。

#### 【0022】

第1抵抗ノード  $R_1$  及び第2抵抗ノード  $R_2$  は、可変抵抗状態を保存することができ、このような可変抵抗状態は、データビットとして保存されうる。例えば、抵抗ノード  $R_1, R_2$  は、低抵抗状態と高抵抗状態とを有することができ、このような低抵抗状態及び高抵抗状態は、それぞれデータ「0」または「1」に対応できる。

40

#### 【0023】

例えば、抵抗ノード  $R_1, R_2$  は、両端に印加された電圧により、その抵抗状態が変わる物質を有することができ、例えば、Nb<sub>2</sub>O<sub>5</sub>、CrドーピングされたSrTiO<sub>3</sub>、ZrO<sub>x</sub>、GST(GeSb<sub>x</sub>Te<sub>y</sub>)、NiO、ZnO、TiO<sub>2</sub>及びHfOからなる群から選択された少なくとも一つをそれぞれ含むことができる。例えば、GSTは、その結晶状態の変化によってその抵抗が変わるという点でPRAMに利用できる。他の例として、Nb<sub>2</sub>O<sub>5</sub>、CrドーピングされたSrTiO<sub>3</sub>、NiOまたはZnOは、結晶状態の変化なしにその抵抗が変わるという点でRRAM素子に利用できる。

#### 【0024】

50

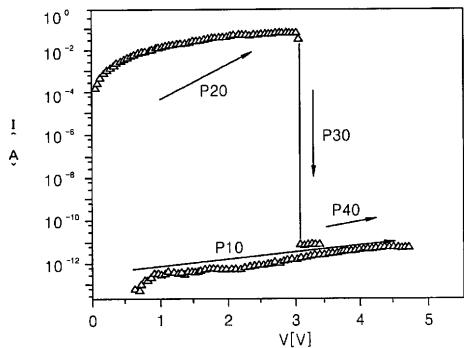

図4を参照し、R R A M素子に利用される抵抗ノードの電圧・電流特性を例示的にさらに詳細に説明する。図4は、抵抗ノードとして、N i Oを例にしたものであり、抵抗層の物質によっては、他の形のグラフが形成されることもある。ただし、印加された電圧によって抵抗が変わりうるという点では共通する。

#### 【0025】

図4を参照すれば、抵抗ノードに初期電圧が印加されれば(経路(P)10)、セット電圧、例えば、N i Oの場合、4.5Vまでは電流がほとんど流れない。すなわち、抵抗ノードは、高い抵抗値を示す(リセット状態)。しかし、セット電圧を超えると、電流が急激に増加する。一旦、セット電圧以上の電圧が加えられた後、再び0から電圧を印加すれば(P20)、高い電流が流れる。すなわち、抵抗ノードは、低い抵抗値を示す(セット状態)。しかし、またリセット電圧以上に電圧が増加すれば、電流は急激に減少する(P30)。すなわち、抵抗ノードの抵抗が再びリセット状態の高い抵抗値に還元される。以後、セット電圧に至るまで電圧を続けて増加させれば(P40)、初期リセット状態と同じ経路を示す。

#### 【0026】

すなわち、抵抗ノードは、臨界電圧、例えば、セット電圧またはリセット電圧を境界に比抵抗(resistivity)が変わり、このような比抵抗変化は、印加電圧がなくなった後でも、一定範囲の電圧区間内では維持される。従って、抵抗ノードは、不揮発性メモリ素子の記録媒体として利用できる。

#### 【0027】

図4の抵抗ノードについての説明は、R R A M素子に利用されるものを例として説明し、P R A Mに利用される抵抗ノードは、他の方式で抵抗変化を経ることができる。P R A Mに利用される抵抗ノードは、相変化抵抗体と呼ばれ、このような相変化抵抗体の抵抗変化特性は、該当技術分野で当業者に周知であるので、その詳細な説明は省略する。

#### 【0028】

一方、前述の単位セルC<sub>11</sub>, C<sub>12</sub>, C<sub>13</sub>, C<sub>21</sub>, C<sub>22</sub>, C<sub>23</sub>, C<sub>31</sub>, C<sub>32</sub>, C<sub>33</sub>の数は例示的なものであり、該当技術分野での当業者により適切に変形されうるということは自明である。これにより、ビットラインBL1, BL2, BL3, BL4及びワードラインWL1, WL2, WL3の数も変形されうる。また、前述の説明での行及び列は例示的なものである。さらに、ビットラインBL1, BL2, BL3, BL4及びワードラインWL1, WL2, WL3が行または列に配列されるといって、必ずしも直線に配列される必要のないことは自明である。

#### 【0029】

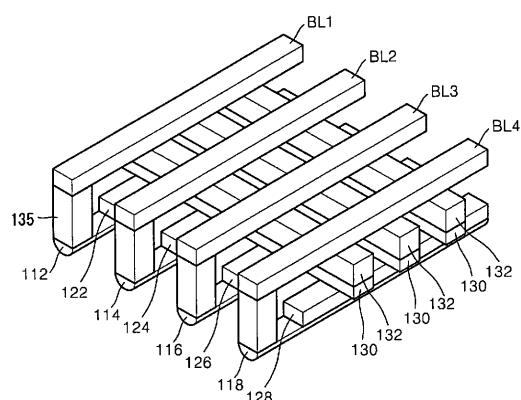

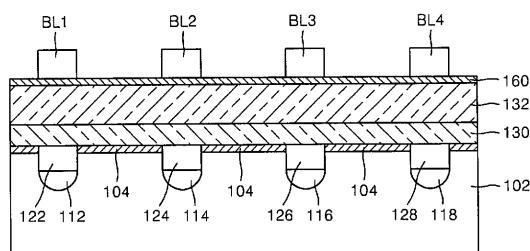

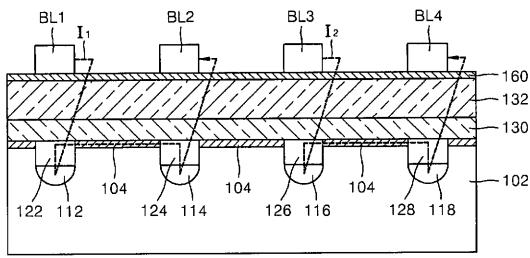

図2は、本発明の一実施形態による不揮発性メモリ素子の構造を示す概略的な斜視図であり、図3は、図2の不揮発性メモリ素子の断面図である。図2及び図3の不揮発性メモリ素子の構造は、図1の不揮発性メモリ素子の回路配置に対応し、重複される説明は省略する。

#### 【0030】

図3を参照すれば、不揮発性メモリ素子は、半導体基板102を備える。ただし、図2には、説明の便宜のために半導体基板102が図示されていない。半導体基板102は、シリコン(Si)ウェーハ、ゲルマニウム(Ge)ウェーハ、または金属・絶縁体転移(MIT: Metal-Insulator Transition)物質を有することができる。例えば、金属・絶縁体転移物質は、遷移金属酸化物、例えばV<sub>2</sub>O<sub>5</sub>、TiO<sub>x</sub>を含むことができる。このような金属・絶縁体転移物質は、所定の臨界電圧以上の電圧が印加されれば、絶縁体から金属に変化しうる。このような金属・絶縁体転移物質は、後述のように、多層半導体素子を形成するのに利用されうる。

#### 【0031】

図2及び図3を共に参照すれば、可変抵抗状態を保存することができる複数の抵抗層122, 124, 126, 128は、半導体基板102の表面付近にそれぞれ形成される。複数の埋め込み電極112, 114, 116, 118は、抵抗層122, 124, 126

10

20

30

40

50

, 128下の半導体基板102部分にそれぞれ形成される。複数のチャネル領域104は、抵抗層122, 124, 126, 128の隣接する二つの間をそれぞれ連結するように、半導体基板102の表面付近に形成される。ゲート絶縁膜130は、チャネル領域104に形成され、選択的に抵抗層122, 124, 126, 128を横切って伸張できる。ゲート電極132は、ゲート絶縁膜130上に形成され、抵抗層122, 124, 126, 128を横切って伸張できる。選択的に、ビットラインBL1, BL2, BL3, BL4が半導体基板102上にさらに形成されうる。

#### 【0032】

埋め込み電極112, 114, 116, 118は、半導体基板102内に埋没された形態に提供されうる。埋め込み電極112, 114, 116, 118は、図1でのソースSまたはドレインDに対応しうる。すなわち、埋め込み電極112, 114, 116, 118は、順にソースS及びドレインDと呼ばれることがある。埋め込み電極112, 114, 116, 118は、その位置上の配置により下部電極と呼ばれることもある。

#### 【0033】

例えば、埋め込み電極112, 114, 116, 118は、半導体基板102に不純物をドーピングして形成されうる。その場合、半導体基板102が第1導電型の不純物でドーピングされた場合、埋め込み電極112, 114, 116, 118は、第2導電型の不純物にドーピングされうる。これにより、埋め込み電極112, 114, 116, 118及び半導体基板102は、ダイオード接合を形成できる。第1導電型及び第2導電型は、n型及びp型からそれぞれ選択されたいずれか一つでありうる。

#### 【0034】

他の例で、埋め込み電極112, 114, 116, 118は、金属層または金属シリサイド層を含むことができる。その場合、埋め込み電極112, 114, 116, 118は、半導体基板102とショットキー(Schottky)接合を形成できる。このようなショットキー接合により、埋め込み電極112, 114, 116, 118及び半導体基板102間の電流の流れは、整流特性を有することができる。

#### 【0035】

複数の抵抗層122, 124, 126, 128は、図1の抵抗ノードR<sub>1</sub>, R<sub>2</sub>に対応しうる。例えば、抵抗層122, 124, 126, 128それぞれは、図1の第1抵抗ノードR<sub>1</sub>及び第2抵抗ノードR<sub>2</sub>が直接連結された構造を有する。すなわち、抵抗層122, 124, 126, 128の左側部分は、第2抵抗ノードR<sub>2</sub>に対応し、抵抗層122, 124, 126, 128の右側部分は、第1抵抗ノードR<sub>1</sub>に対応しうる。たとえ図3で、抵抗層122, 124, 126, 128が半導体基板102の表面までと形成されているとしても、さらに突出しうるということは自明である。抵抗層122, 124, 126, 128の説明は、図1の抵抗ノードR<sub>1</sub>, R<sub>2</sub>の説明を参照できるので、その重複された説明は省略する。

#### 【0036】

複数のチャネル領域104は、抵抗層122, 124, 126, 128間に配置され、抵抗層122, 124, 126, 128を連結する役割を行う。チャネル領域104は、ターンオン状態で、導電層として機能するために、1つの電極の役割を行える。例えば、チャネル領域104は、第1抵抗層112及び第2抵抗層124の共通上部電極になりうる。ただし、チャネル領域104は、埋め込み電極112, 114, 116, 118を通じてのみパワーを印加することができるために、独立的な電極として動作できない。

#### 【0037】

ゲート絶縁膜130は、ゲート電極132をチャネル領域104と絶縁させる役割を行える。さらに、ゲート絶縁膜130が抵抗層112, 114, 116, 118上にさらに伸張していることにより、抵抗層112, 114, 116, 118をゲート電極132とさらに絶縁させる役割を行える。ゲート絶縁膜130の厚さは、動作電圧によって適切に選択され、図2及び図3は、誇張して図示されている。ゲート電極132は、図1のゲートGに対応する。例えば、ゲート電極132は、導電性物質、例えば、ポリシリコン層、

10

20

30

40

50

または金属層を含むことができる。

**【0038】**

ビットラインBL1, BL2, BL3, BL4は、層間絶縁膜160を介在してゲート電極132上に形成される。ビットラインBL1, BL2, BL3, BL4は、プラグ135を介して埋め込み電極112, 114, 116, 118それぞれと連結される。例えば、ビットラインBL1, BL2, BL3, BL4は、ゲート電極132の伸張方向とは異なる方向、例えば、埋め込み電極112, 114, 116, 118と平行した方向に伸張できる。例えば、ビットラインBL1, BL2, BL3, BL4は、金属層を含むことができる。

**【0039】**

前述の不揮発性メモリ素子は、次のような構造的な長所を有することができる。

第一に、抵抗層112, 114, 116, 118とチャネル領域104との接触面積を非常に小さくできる。例えば、抵抗層112, 114, 116, 118が相変化抵抗体を含む場合、チャネル領域104と接触する付近でだけ相変化が起こるために、相変化領域を減少させることができ、電流密度を大きく増加させることができる。従って、少ない動作電流で相変化領域に、相変化に必要なだけの電流密度を供給できる。従来のP R A Mで、相変化領域の大きさは、 $10^3 \text{ nm}^2$ ないし $10^4 \text{ nm}^2$ 近辺である。しかし、本発明の実施形態で、チャネル領域104は、約 $1 \text{ nm} - 2 \text{ nm}$ の厚さと $100 \text{ nm}$ ほどの幅を有することができるので、 $100 \text{ nm}^2 - 200 \text{ nm}^2$ ほどの面積を有することができる。従って、従来よりも、相変化領域の大きさを大幅に縮少させることができるので、動作電流、例えば、リセット電流をおよそ $1/10$ 以下に減少させることができる。

**【0040】**

第二に、不揮発性メモリ素子の集積度を高めることができる。すなわち、従来においては、制御素子と電極構造とが別途に平行に形成されたが、本発明による不揮発性メモリ素子は、制御素子と電極構造とが統合された構造を有する。すなわち、チャネル領域104が上部電極の役割を果たし、抵抗層122, 124, 126, 128が他の導電層を介在させずにチャネル領域104と直接接觸する。従って、従来の制御素子の形成面積で、全体不揮発性メモリ素子を形成でき、その結果、集積度が高まりうる。

**【0041】**

以下、前述の不揮発性メモリ素子の動作特性を説明する。

図5は、本発明の一実施形態による不揮発性メモリ素子のプログラム動作を示す回路図であり、図6は、本発明の一実施形態による不揮発性メモリ素子のプログラム動作を示す断面図である。

**【0042】**

図5を参照すれば、プログラム動作で、選択された2単位セルC<sub>21</sub>, C<sub>23</sub>の抵抗ノードR<sub>1</sub>, R<sub>2</sub>にデータが保存される。例えば、第2ワードラインWL2にターンオン電圧を印加し、第2列に配列された単位セルC<sub>21</sub>, C<sub>22</sub>, C<sub>23</sub>の制御素子CTをいずれもターンオンさせる。そして、第1ビットラインBL1及び第2ビットラインBL2間に、並びに第3ビットラインBL3及び第4ビットラインBL4間に、プログラム電圧を印加することにより、選択された単位セルC<sub>21</sub>, C<sub>23</sub>に第1電流I<sub>1</sub>及び第2電流I<sub>2</sub>の流れをそれぞれ誘導する。これにより、選択された単位セルC<sub>21</sub>, C<sub>23</sub>の抵抗ノードR<sub>1</sub>, R<sub>2</sub>の抵抗状態が変化しうる。このようなプログラム電圧は、抵抗ノードR<sub>1</sub>, R<sub>2</sub>の種類によって適切に選択されうる。

**【0043】**

図6を参照すれば、第1ビットラインBL1及び第2ビットラインBL2間に、第1電流I<sub>1</sub>が誘導されることにより、第1抵抗層122の右側部分、及び第2抵抗層124の左側部分の抵抗状態が変化しうる。同様に、第3ビットラインBL3及び第4ビットラインBL4間に、第2電流I<sub>2</sub>が誘導されることにより、第3抵抗層126の右側部分、及び第4抵抗層128の左側部分の抵抗状態が変化しうる。

**【0044】**

10

20

30

40

50

隣接するビットライン BL 1, BL 2, BL 3, BL 4 のうち、二つに順次にプログラム電圧を印加することにより、前述のプログラム動作を全体的に、または選択的に行うことができる。

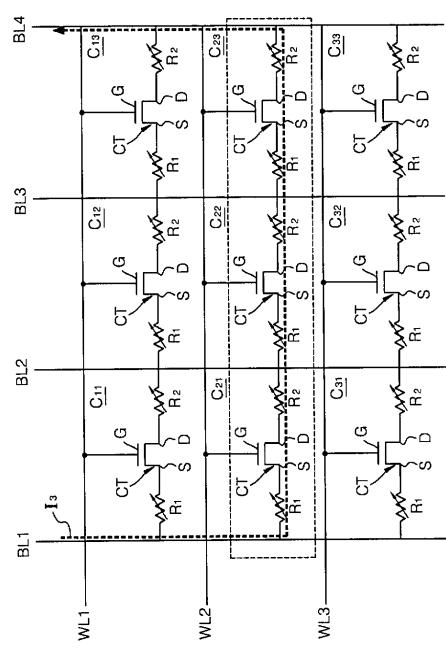

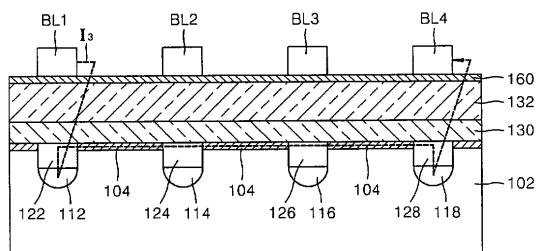

図 7 は、本発明の一実施形態による不揮発性メモリ素子のフラッシュ・イレーズ動作を示す回路図であり、図 8 は、本発明の一実施形態による不揮発性メモリ素子のフラッシュ・イレーズ動作を示す断面図である。

#### 【0045】

図 7 を参照すれば、フラッシュ・イレーズ動作で、第 2 列に配列された複数の単位セル C<sub>2 1</sub>, C<sub>2 2</sub>, C<sub>2 3</sub> の抵抗ノード R<sub>1</sub>, R<sub>2</sub> に保存されたデータが一時に消されうる。図 7 には、3 つの単位セル C<sub>2 1</sub>, C<sub>2 2</sub>, C<sub>2 3</sub> が図示されているが、さらに多くの単位セルのデータが一度に消されることもある。10

さらに具体的に見れば、第 2 ワードライン WL 2 にターンオン電圧を印加し、第 2 列に配列された単位セル C<sub>2 1</sub>, C<sub>2 2</sub>, C<sub>2 3</sub> の制御素子 CT をいずれもターンオンさせる。次に、第 2 列に配列された単位セル C<sub>2 1</sub>, C<sub>2 2</sub>, C<sub>2 3</sub> のエッジに配列された第 1 ビットライン BL 1 及び第 4 ビットライン BL 4 間にイレーズ電圧を印加する。これにより、第 2 列に配列された単位セル C<sub>2 1</sub>, C<sub>2 2</sub>, C<sub>2 3</sub> に第 3 電流 I<sub>3</sub> が誘導され、その結果、第 1 抵抗ノード R<sub>1</sub> 及び第 2 抵抗ノード R<sub>2</sub> に保存されたデータが消されうる。イレーズ電圧は、消そうとするデータの単位セルの数に比例する。この場合、低い動作電流で複数の単位セル C<sub>2 1</sub>, C<sub>2 2</sub>, C<sub>2 3</sub> のデータを一度に消すことができる。20

#### 【0046】

図 8 を参照すれば、第 1 ビットライン BL 1 及び第 4 ビットライン BL 4 間に、第 3 電流 I<sub>3</sub> が誘導されることにより、抵抗層 122, 124, 126, 128 に保存されたデータがいずれも一度に消されうる。20

前述の本発明の実施形態による不揮発性メモリ素子の動作方法は、高速度のフラッシュ・イレーズ速度を有する。従って、不揮発性メモリ素子の動作速度が速めることができる。。20

#### 【0047】

一方、本発明の他の実施形態で、不揮発性メモリ素子は、マルチ・ビットで動作されることもある。その場合、第 1 抵抗ノード（図 5 の R<sub>1</sub>）及び第 2 抵抗ノード（図 5 の R<sub>2</sub>）にプログラム状態を異にすることにより、マルチ・ビット動作を具現できる。例えば、第 1 ビットライン BL 1 及び第 2 ビットライン BL 2 間の電流方向を変え、第 1 抵抗ノード R<sub>1</sub> 及び第 2 抵抗ノード R<sub>2</sub> のプログラム状態を異にすることができます。30

#### 【0048】

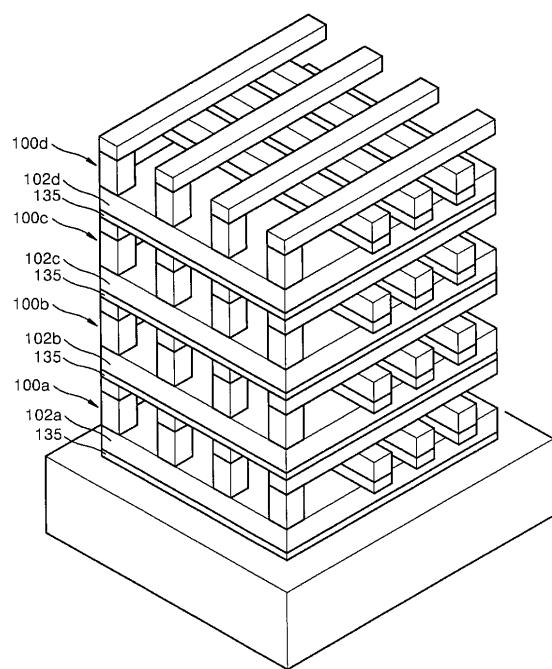

図 9 は、本発明の他の実施形態による不揮発性メモリ素子の構造を示す斜視図である。図 9 の不揮発性メモリ素子は、図 2 及び図 3 の不揮発性メモリ素子を単位層構造とするとき、複数個の単位層構造を積層した構造を有する。従って、図 9 の不揮発性メモリ素子で、単位層の構造は、図 2 及び図 3 の説明を参照でき、重複する説明は省略する。

#### 【0049】

図 9 を参照すれば、複数の単位層構造 100a, 100b, 100c, 100d が順に積層されている。第 1 単位層構造 100a の半導体基板 102a は、シリコンウェーハまたはゲルマニウムウェーハを含むことができる。一方、第 2 単位層構造ないし第 4 単位層構造 100b, 100c, 100d の半導体基板 102b, 102c, 102d は、金属・絶縁体転移物質をそれぞれ含むことができる。これにより、第 2 半導体基板ないし第 4 層の半導体基板 102b, 102c, 102d を物質膜蒸着法を利用して容易に形成できる。半導体基板 102a, 102b, 102c, 102d は、絶縁膜 135 により互いに絶縁されうる。40

#### 【0050】

このような単位層構造 100a, 100b, 100c, 100d の積層構造は、一般的な単層構造に比べて高い集積度を有することができる。さらに、単位層構造 100a, 100b, 100c, 100d のチャネル領域 104 を互いに連結してゲート電極 132 を50

互いに連結し、同じ面積の半導体基板 102a 上に形成される単位セルの数を実質的に増やすこともできる。

#### 【0051】

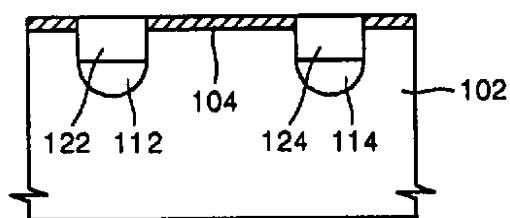

図10ないし図15は、本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。

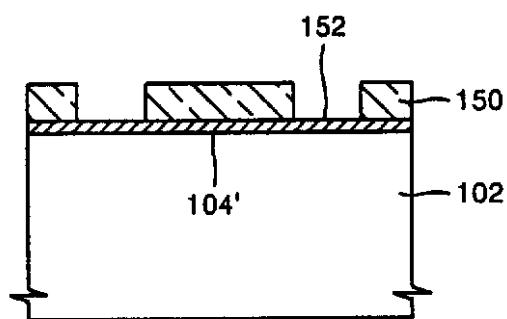

図10を参照すれば、半導体基板表面付近に予備チャネル領域104'を形成する。次に、半導体基板102上に、半導体基板の所定部分152を露出するマスクパターン150を形成する。例えば、シリコン酸化膜(図示せず)を形成した後、フォトリソグラフィ及びエッティング技術を利用し、マスクパターン150を形成できる。

#### 【0052】

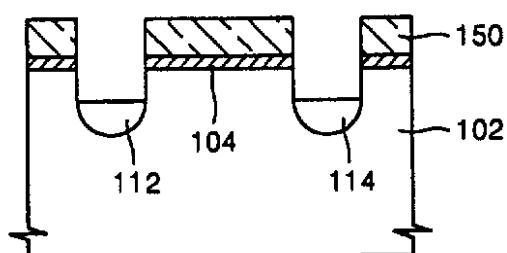

図11を参照すれば、マスクパターン150から露出された半導体基板部分(図10の152)をエッティングし、複数のトレンチ155を形成する。例えば、マスクパターン150をエッティング保護膜とし、ドライエッティングを利用してトレンチ155を形成できる。これにより、予備チャネル領域104'は分離され、複数のチャネル領域104を定義する。

#### 【0053】

図12を参照すれば、トレンチ155の底付近にチャネル領域より深く導電層(図示せず)を形成することにより、複数の埋め込み電極112, 114を形成する。例えば、トレンチ155の底付近の半導体基板102に、不純物をドーピングして導電層を形成できる。他の例として、トレンチ155の底付近の半導体基板102上に、金属層または金属シリサイド層を形成して導電層を形成できる。その場合、チャネル領域を露出するトレンチ155の側壁付近に、金属層または金属シリサイド層が形成されないように、導電層の形成前にトレンチ155側壁にスペーサ絶縁膜(図示せず)を形成することもある。

#### 【0054】

図13を参照すれば、埋め込み電極112, 114上に、複数の抵抗層122, 124を形成する。抵抗層122, 124は、チャネル領域の端部と連結されるように形成される。例えば、トレンチ155を埋め込むように、埋め込み電極112, 114上に抵抗層物質を形成し、これを平坦化することにより、抵抗層122, 124を形成できる。

#### 【0055】

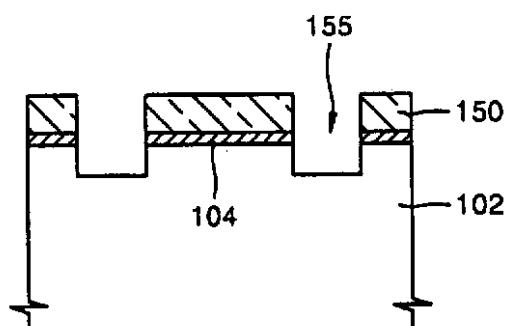

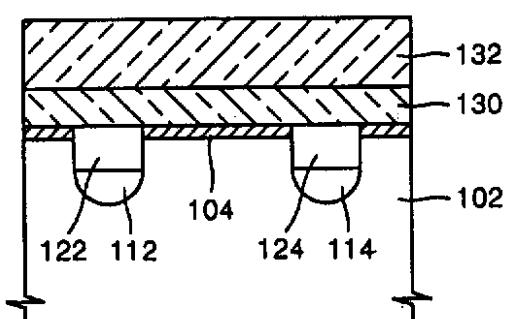

図14を参照すれば、半導体基板102上にゲート絶縁膜130を形成する。例えば、ゲート絶縁膜130は、チャネル領域上に形成され、抵抗層122, 124を横切って伸張されうる。

次に、ゲート絶縁膜130上にゲート電極132を形成する。ゲート電極132は、抵抗層122, 124を横切って伸張でき、複数のラインにパターニングされうる。

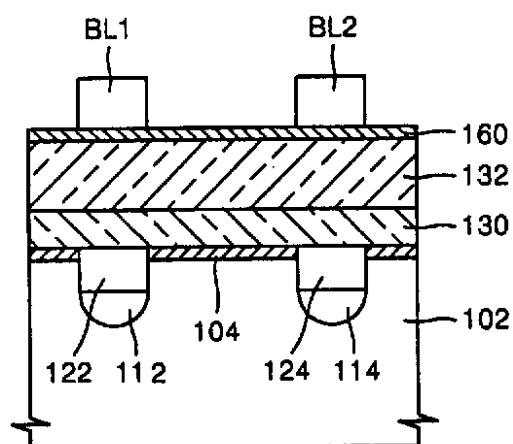

図15を参照すれば、ゲート電極132上に層間絶縁膜160を形成する。例えば、層間絶縁膜160は、シリコン酸化膜またはシリコン窒化膜を含むことができる。次に、層間絶縁膜160上に、複数のビットラインBL1, BL2を形成する。例えば、ビットラインBL1, BL2は、ゲート電極132とは異なる方向、例えば、埋め込み電極112, 114と平行した方向に伸張されうる。さらに具体的に見れば、金属層(図示せず)を層間絶縁膜160上に形成した後、これをパターニングすることにより、ビットラインBL1, BL2を形成できる。

#### 【0056】

このような不揮発性メモリ素子の製造方法は、制御素子と電極構造とを同時に形成できる。従って、製造段階で高いコストを占めるフォトリソグラフィ段階の数を減らすことができ、その結果、製造コストを減らすことができる。また、前述の不揮発性メモリ素子の製造方法は、従来の製造技術をそのまま利用できる。従って、本発明の実施形態による不揮発性メモリ素子の製造方法は高い経済性を有することができる。

#### 【0057】

発明の特定実施形態についての以上の説明は、例示及び説明することを目的に提供された。本発明は、前記実施形態に限定されず、本発明の技術的思想内で該当分野で当業者に

10

20

30

40

50

より、前記実施形態を組み合わせて実施するなど、多様な多くの修正及び変更が可能であるということは明白である。

**【産業上の利用可能性】**

**【0058】**

本発明の不揮発性メモリ素子、その動作方法、及びその製造方法は、例えば、メモリ関連の技術分野に効果的に適用可能である。

**【図面の簡単な説明】**

**【0059】**

【図1】本発明の一実施形態による不揮発性メモリ素子の配置を示す回路図である。

【図2】本発明の一実施形態による不揮発性メモリ素子の構造を示す概略的な斜視図である。 10

【図3】図2の不揮発性メモリ素子の断面図である。

【図4】本発明の一実施形態による不揮発性メモリ素子の抵抗ノードの例示的な電圧・電流特性を示すグラフである。

【図5】本発明の一実施形態による不揮発性メモリ素子のプログラム動作を示す回路図である。

【図6】本発明の一実施形態による不揮発性メモリ素子のプログラム動作を示す断面図である。

【図7】本発明の一実施形態による不揮発性メモリ素子のフラッシュ・イレーズ動作を示す回路図である。 20

【図8】本発明の一実施形態による不揮発性メモリ素子のフラッシュ・イレーズ動作を示す断面図である。

【図9】本発明の他の実施形態による不揮発性メモリ素子の構造を示す斜視図である。そして

【図10】本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。

【図11】本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。

【図12】本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。 30

【図13】本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。

【図14】本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。

【図15】本発明の一実施形態による不揮発性メモリ素子の製造方法を示す断面図である。

**【符号の説明】**

**【0060】**

100 a 第1単位層構造

100 b 第2単位層構造

100 c 第3単位層構造

100 d 第4単位層構造

102 半導体基板

102 a 第1単位層構造の半導体基板

102 b 第2単位層構造の半導体基板

102 c 第3単位層構造の半導体基板

102 d 第4単位層構造の半導体基板

104 チャネル領域

104' 予備チャネル領域

112, 114, 116, 118 埋め込み電極

40

50

|                                |            |

|--------------------------------|------------|

| 1 2 2 , 1 2 4 , 1 2 6 , 1 2 8  | 抵抗層        |

| 1 3 0                          | ゲート絶縁膜     |

| 1 3 2                          | ゲート電極      |

| 1 3 5                          | 絶縁膜        |

| 1 5 0                          | マスクパターン    |

| 1 5 2                          | 半導体基板の一定部分 |

| 1 5 5                          | トレンチ       |

| 1 6 0                          | 層間絶縁膜      |

| B L 1                          | 第1ビットライン   |

| B L 2                          | 第2ビットライン   |

| B L 3                          | 第3ビットライン   |

| B L 4                          | 第4ビットライン   |

| C <sub>1</sub> ~C <sub>3</sub> | 単位セル       |

| C T                            | 制御素子       |

| D                              | ドレイン       |

| G                              | ゲート        |

| I <sub>1</sub>                 | 第1電流       |

| I <sub>2</sub>                 | 第2電流       |

| I <sub>3</sub>                 | 第3電流       |

| R <sub>1</sub>                 | 第1抵抗ノード    |

| R <sub>2</sub>                 | 第2抵抗ノード    |

| S                              | ソース        |

| W L 1 , W L 2 , W L 3          | ワードライン     |

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 9】

【図 10】

【図 12】

【図 11】

【図 13】

【図14】

【図15】

---

フロントページの続き

(51)Int.Cl.

F I

G 1 1 C 13/00 1 1 0 P

G 1 1 C 13/00 1 1 0 R

(74)代理人 100110364

弁理士 実広 信哉

(72)発明者 朴 允童

大韓民国京畿道龍仁市器興區農書洞山14 - 1番地 三星綜合技術院内

(72)発明者 李 明宰

大韓民国京畿道龍仁市器興區農書洞山14 - 1番地 三星綜合技術院内

(72)発明者 金 東徹

大韓民国京畿道龍仁市器興區農書洞山14 - 1番地 三星綜合技術院内

(72)発明者 安 承彦

大韓民国京畿道龍仁市器興區農書洞山14 - 1番地 三星綜合技術院内

審査官 井出 和水

(56)参考文献 特開2004-221546 (JP, A)

特開2004-179619 (JP, A)

米国特許出願公開第2005/0105327 (US, A1)

特開2004-363604 (JP, A)

特開2005-311356 (JP, A)

特開2006-080523 (JP, A)

特開2006-024868 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 27 / 10

G 11 C 13 / 00

H 01 L 27 / 105

H 01 L 45 / 00

H 01 L 49 / 00