(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4030876号

(P4030876)

(45) 発行日 平成20年1月9日(2008.1.9)

(24) 登録日 平成19年10月26日(2007.10.26)

(51) Int.C1.

F 1

|            |           |            |      |

|------------|-----------|------------|------|

| GO6F 12/00 | (2006.01) | GO6F 12/00 | 550K |

| GO6F 12/06 | (2006.01) | GO6F 12/00 | 597U |

| GO6F 12/16 | (2006.01) | GO6F 12/06 | 515H |

| G11C 16/06 | (2006.01) | GO6F 12/16 | 340A |

| GO6K 19/07 | (2006.01) | G11C 17/00 | 632A |

請求項の数 12 (全 13 頁) 最終頁に続く

(21) 出願番号 特願2002-574669 (P2002-574669)

(86) (22) 出願日 平成14年2月8日 (2002.2.8)

(65) 公表番号 特表2004-531801 (P2004-531801A)

(43) 公表日 平成16年10月14日 (2004.10.14)

(86) 國際出願番号 PCT/US2002/003616

(87) 國際公開番号 WO2002/075744

(87) 國際公開日 平成14年9月26日 (2002.9.26)

審査請求日 平成15年12月24日 (2003.12.24)

(31) 優先権主張番号 09/788,120

(32) 優先日 平成13年2月16日 (2001.2.16)

(33) 優先権主張国 米国(US)

前置審査

(73) 特許権者 592012513

サンディスク コーポレイション

Sandisk Corporation

アメリカ合衆国 95035 カリフォルニア州、ミルピタス、マッカーシー ブルバード 601

(74) 代理人 100068755

弁理士 恩田 博宣

(74) 代理人 100105957

弁理士 恩田 誠

(72) 発明者 ゴングワー、ジョフリー スティーブン

アメリカ合衆国 94024 カリフォルニア州 ロス アルトス ビーチウッド

レーン 5328

最終頁に続く

(54) 【発明の名称】メモリシステムにおける供給電圧の発生および分配の方法およびシステム

## (57) 【特許請求の範囲】

## 【請求項1】

外部供給電圧をホストから受け取るメモリシステムであって、前記メモリシステムは、複数のメモリブロックであって、前記メモリブロックのそれぞれは少なくとも複数のデータ記憶要素を含み、少なくとも一つの前記メモリブロックは、該少なくとも一つのメモリブロック内で少なくとも第1のメモリ生成電圧を発生するように動作可能な第1電圧発生回路をさらに含む、メモリブロックと、

前記メモリブロックにアクセスするよう動作可能に結合されたメモリコントローラと、前記メモリブロックのそれぞれに結合された電源バスであって、前記電源バスは前記第1のメモリ生成電圧を前記複数のメモリブロック間に供給する、電源バスと、

を備え、前記第1のメモリ生成電圧は前記メモリコントローラにも供給される、メモリシステム。

## 【請求項2】

請求項1に記載のメモリシステムであって、前記データ記憶要素は、不揮発性データ記憶を提供するメモリシステム。

## 【請求項3】

請求項1に記載のメモリシステムであって、前記データ記憶要素は、EEPROMまたはFLASHであるメモリシステム。

## 【請求項4】

請求項1に記載のメモリシステムであって、前記メモリシステムは、単一のパッケージ 20

の中に提供されるメモリシステム。

【請求項 5】

請求項 1 に記載のメモリシステムであって、前記メモリシステムは前記ホストから取り外し可能なデータ記憶製品であるメモリシステム。

【請求項 6】

請求項 1 に記載のメモリシステムであって、前記メモリシステムが前記ホストに動作可能に接続され、前記外部供給電圧は、少なくとも前記第 1 電圧発生回路を含む前記少なくとも一つの前記メモリブロックに供給されるメモリシステム。

【請求項 7】

請求項 6 に記載のメモリシステムであって、前記メモリシステムは、

前記メモリコントローラと、前記メモリブロックのそれぞれとの間を動作可能に結合する入力 / 出力 (I / O) バス

をさらに備えるメモリシステム。

【請求項 8】

請求項 1 に記載のメモリシステムであって、前記複数のメモリブロックの少なくとも他のものは、前記少なくとも他のメモリブロック内で前記第 1 のメモリ生成電圧と 同じ 第 2 のメモリ生成電圧 であって、前記複数のメモリブロック間に供給される第 2 のメモリ生成電圧を発生するように動作可能な第 2 電圧発生回路をさらに少なくとも含むメモリシステム。

【請求項 9】

請求項 1 に記載のメモリシステムであって、前記メモリシステムはメモリカードであるメモリシステム。

【請求項 10】

請求項 1 に記載のメモリシステムであって、

前記メモリシステムは、

前記メモリコントローラおよび前記メモリブロックから離れた電圧レギュレータであ

って、該電圧レギュレータ内で、前記電源バスに供給される供給電圧を発生する電圧レギ

ュレータをさらに備え、

前記電圧レギュレータで発生された供給電圧は、前記メモリブロック間に前記電源バスを介して供給される、

メモリシステム。

【請求項 11】

電子システムであって、

データ取得デバイスと、

前記データ取得デバイスに取り外し可能に結合されたデータ記憶デバイスであって、前

記データ記憶デバイスは、前記データ取得デバイスによって取得されたデータを記憶し、

前記データ記憶デバイスは、

メモリコントローラと、

前記メモリコントローラに動作可能に結合された複数のメモリブロックであって、

前記メモリブロックのそれぞれは少なくともデータ記憶要素を含む、複数のメモリブロッ

クと、

異なるレベルの供給電圧群を前記メモリブロックのそれぞれの間に動作可能に供給

する電源バスであって、前記異なるレベルの供給電圧群は前記複数のメモリブロックのう

ちの一つによって発生される、電源バスと、

を少なくとも含む、データ記憶デバイスと、

を備え、前記異なるレベルの供給電圧群の少なくとも一つは前記メモリコントローラに

供給される、電子システム。

【請求項 12】

請求項 1 に記載の電子システムであって、前記データ取得デバイスは、カメラ、ネットワークカードまたは装置、ハンドヘルドまたはノートブックコンピュータ、セットトッ

10

20

30

40

50

プボックス、ハンドヘルドまたは他の小型オーディオプレーヤ/レコーダ、および医療モニタのうちの一つである電子システム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は電圧発生に関し、より具体的にはメモリシステム内の電圧発生システムに関する。

【背景技術】

【0002】

メモリカードは一般にさまざまな製品（例えば電子機器）に用いられるディジタルデータを格納するために用いられる。メモリカードの例としては、フラッシュタイプまたはEEPROMタイプメモリセルを用いてデータを格納するフラッシュカードがある。フラッシュカードは比較的小さいフォームファクタを有し、カメラ、ハンドヘルドコンピュータ、セットトップボックス、ハンドヘルドまたは他の小さなオーディオプレーヤ・レコーダ（例えばMP3機器）、および医療モニタのような製品のディジタルデータを格納するために用いられてきた。フラッシュカードの大手供給元としてはカリフォルニア州、サンベールのサンディスク社がある。

【0003】

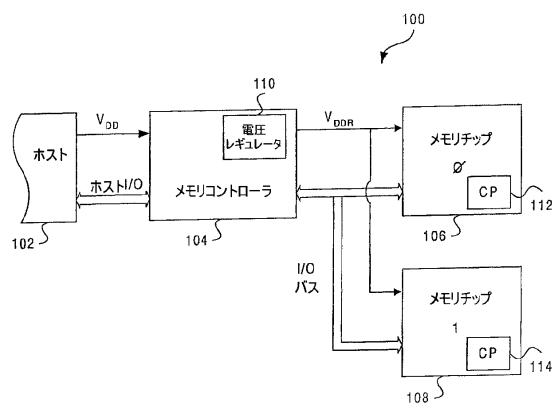

図1は従来のメモリシステム100のブロック図である。従来のメモリシステム100は、不揮発性データ記憶を提供し、例えばメモリカード（例えばフラッシュカード）を表す。従来のメモリシステム100は、ホスト102に結合する。ホスト102は例えばパーソナルコンピュータまたは電子機器でありえる。メモリシステム100はメモリコントローラ104およびメモリチップ106および108を含む。メモリコントローラ104は電圧レギュレータ110を含む。ホスト入力/出力(I/O)バスは、メモリコントローラ104をホスト102に結合する。ホスト102はまた、供給電圧 $V_{DD}$ をメモリコントローラ104に供給する。メモリコントローラ104内の電圧レギュレータ110は供給電圧 $V_{DD}$ を受け取り、供給電圧を制御し、安定化された供給電圧 $V_{DDR}$ を発生する。安定化された供給電圧 $V_{DDR}$ は、メモリチップ106および108のそれぞれに供給される。安定化された供給電圧 $V_{DDR}$ は、メモリチップ106および108に供給される固定された電圧レベル（典型的には許容差の範囲内）である。この実施形態においては、メモリチップ106および108は、メモリチップ106および108に供給される供給電圧がある特定の電圧レベルであることを要求する。メモリシステム100はさまざまな異なるホストに結合するので、供給電圧 $V_{DD}$ は、異なる電圧範囲にわたって、例えば1.8ボルト、3.3ボルトまたは5ボルトと変化しえる。しかし現在のメモリチップは電圧が3.3ボルトであることを要求する。電圧レギュレータ110は、供給電圧 $V_D$ のレベルに依らず、安定化された供給電圧 $V_{DDR}$ がある特定の電圧レベル（例えば3.3ボルト）であることを確実にする。

【0004】

いずれにしてもメモリチップ106および108は、それらの動作のために、メモリコントローラ104から受け取られた特定の電圧レベル（つまり $V_{DDR}$ ）とは異なるさまざまな供給電圧レベルを要求する。よってメモリチップ106および108は、チャージポンプ回路112および114をそれぞれ含む。チャージポンプ回路112および114は、安定化された供給電圧 $V_{DDR}$ を受け取り、それらに関連づけられたメモリチップによって内部で用いられる目的で、独立に内部で追加の供給電圧レベルを発生する。他の実施形態においてはメモリコントローラが電圧安定化を行わないとき、メモリチップは異なる供給電圧を受け取って動作しえる。しかしそうするときに、メモリチップは入力供給電圧レベルを検出してから、入力供給電圧の検出されたレベルに対応する一組の動作パラメータを選択しなければならないので、メモリチップ設計はより複雑になり、最適性能が失われる。

【発明の開示】

10

20

30

40

50

**【発明が解決しようとする課題】****【0005】**

従来のメモリシステム100の一つの問題は、メモリチップのそれぞれがチャージポンプ回路を含むことが必要とされることである。チャージポンプ回路は貴重な半導体ダイエリヤを消費するだけでなく、追加の供給電圧を発生するときにかなりのノイズも発生することになる。ノイズ発生は、メモリチップの敏感なアナログ部分に悪影響を与える。したがってチャージポンプ回路によって加わる追加のノイズはメモリチップの動作性能を低下させる。

**【0006】**

よって不揮発性データ記憶を提供するメモリチップによって用いられる、さまざまな異なる供給電圧レベルを発生するための改良されたアプローチが必要である。

10

**【課題を解決するための手段】****【0007】**

大まかには、本発明は、さまざまな電圧レベルを複数のメモリブロック群（例えばメモリチップ群）を持つメモリシステム内で発生し分配する技術に関する。さまざまな電圧レベルは、電圧発生回路（例えばチャージポンプおよび／またはレギュレータ回路）によってメモリシステム内で発生される。さまざまな電圧レベルは、メモリブロックに、またはメモリブロック間で電源バスを通して供給される。

**【0008】**

本発明は、さまざまな方法で実現可能であり、例えばシステム、装置、デバイス、および方法が含まれる。本発明のいくつかの実施形態が以下に説明される。

20

外部供給電圧をホストから受け取るメモリシステムとして、本発明のある実施形態は、少なくとも複数のメモリブロックを含み、メモリブロックのそれぞれは少なくとも複数のデータ記憶要素を含むメモリブロックと、メモリブロックと動作可能に結合され、メモリシステムがホストに動作可能に接続されるときに外部供給電圧を受け取るように動作可能に結合されたメモリコントローラであって、メモリコントローラは、メモリブロックのそれぞれによって使用されるための少なくとも第1供給電圧を発生するように動作可能な電圧発生回路を少なくとも含む。本発明の実施形態は代替として、少なくとも第1供給電圧をメモリブロック間に供給する、メモリブロックのそれぞれに結合された電源バスを含んでもよい。

30

**【0009】**

ホストから外部供給電圧を受け取るメモリシステムとして、本発明の他の実施形態は、少なくとも複数のメモリブロックであって、メモリブロックのそれぞれは少なくとも複数のデータ記憶要素を含み、メモリブロックの少なくとも一つは、少なくとも一つのメモリで発生された供給電圧を発生するように動作可能な少なくとも第1電圧発生回路をさらに含む、メモリブロックと、メモリブロックに動作可能に結合され、メモリシステムがホストに動作可能に接続されているときに、外部供給電圧を受け取るように動作可能に結合されたメモリコントローラであって、メモリコントローラは、少なくとも一つのコントローラで発生された供給電圧を発生するように動作可能な第2電圧発生回路を少なくとも含む、メモリコントローラと、メモリブロックのそれぞれに結合された電源バスと、を備える。電源バスは少なくとも一つのメモリで発生された供給電圧をメモリブロック間に供給する。

40

**【0010】**

外部供給電圧をホストから受け取るメモリシステムとして、本発明のさらに他の実施形態は、複数のメモリブロックであって、メモリブロックのそれぞれは少なくとも複数のデータ記憶要素を含み、少なくとも一つのメモリブロックは、メモリで発生された少なくとも一つの供給電圧を発生するように動作可能な第1電圧発生回路を少なくともさらに含む、メモリブロックと、メモリブロックにアクセスするよう動作可能に結合されたメモリコントローラと、メモリブロックのそれぞれに結合された電源バスとを備える。電源バスは少なくとも一つの、メモリで発生された供給電圧をメモリブロック間に供給する。

50

**【0011】**

取り外し可能にホストユニットに結合するデータ記憶デバイスとして、本発明のある実施形態は、少なくとも一つのメモリコントローラと、メモリコントローラに動作可能に結合された複数のメモリブロックであって、メモリブロックのそれぞれは少なくともデータ記憶要素を含む、メモリブロックと、異なるレベルの供給電圧群をメモリブロックのそれぞれの間に動作可能に供給する電源バスであって、異なるレベルの供給電圧群は、メモリコントローラ、またはメモリブロックのうちの一つによって中央で発生される、電源バスと、を備える。

**【0012】**

電子システムとして、本発明のある実施形態は、少なくとも一つのデータ取得デバイスと、データ取得デバイスに取り外し可能に結合されたデータ記憶デバイスとを備える。データ記憶デバイスは、データ取得デバイスによって取得されたデータを記憶する。データ記憶デバイスは、メモリコントローラと、メモリコントローラに動作可能に結合された複数のメモリブロックであって、メモリブロックのそれぞれは少なくともデータ記憶要素を含む、メモリブロックと、異なるレベルの供給電圧群をメモリブロックのそれぞれの間に動作可能に供給する電源バスであって、異なるレベルの供給電圧群は、メモリコントローラ、またはメモリブロックのうちの一つによって中央で発生される、電源バスと、を少なくとも含む。

**【0013】**

本発明の他の局面および利点は、本発明の原理を例示的に図示する添付の図面とあわせれば以下の詳細な説明から明らかになるだろう。

**【発明を実施するための最良の形態】****【0014】**

本発明は、複数のメモリブロック（例えばメモリチップ）を有するメモリシステム内でさまざまな電圧レベルを発生し、供給する技術に関する。さまざまな電圧レベルは、メモリシステム内の電圧発生回路（例えばチャージポンプおよび／またはレギュレータ回路）によって発生される。さまざまな電圧レベルは、電源バスを通して複数のメモリブロックに、または複数のメモリブロック間に供給されえる。

**【0015】**

本発明のある局面によれば、チャージポンプおよび／またはレギュレータ回路が、メモリシステムのメモリブロックのうちの一つの中に提供され（故障耐性のために複数のバックアップが提供される場合を除き）、電源バスは発生された電圧レベルをメモリブロックの他の部分へ供給するのに用いられる。この局面の場合はせいぜい、メモリブロックのうちの一つだけがチャージポンプおよび／またはレギュレータ回路を含む必要がある。よって本発明は、チャージポンプおよび／またはレギュレータ回路によって発生される不要ノイズがメモリシステムのメモリブロックの敏感なアナログ要素の動作に影響を与える程度を抑えるようにはたらく。

**【0016】**

本発明の他の局面によれば、メモリコントローラは複数の供給電圧レベルを発生し、これらはメモリブロックのそれぞれに分配される（例えば電源バスを介して）。ここでこの局面においては、メモリブロックはいかなるチャージポンプまたはレギュレータ回路を含む必要はないが、これはメモリコントローラが中央で全ての必要とされる供給電圧群を作り、それらをメモリブロックのそれぞれに分配できるからである。

**【0017】**

本発明のこの局面の実施形態は以下に図2～5を参照して説明される。しかし当業者には容易に理解されるように、ここに与えられたこれらの図面についての詳細な説明は説明のためであって、本発明はこれらの限定された実施形態を超える。

**【0018】**

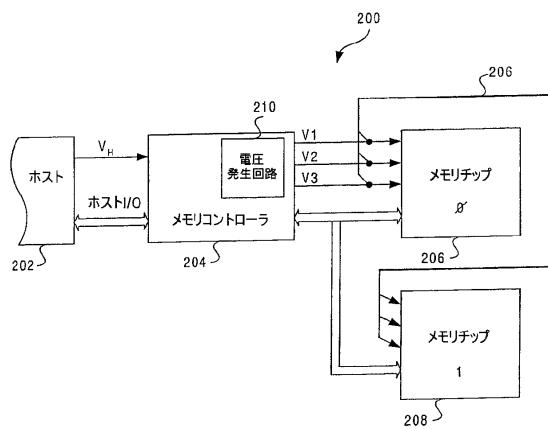

図2は、本発明のある実施形態によるメモリシステム200のブロック図である。メモリシステム200は、例えば、メモリカード（プラグインカードのような）、メモリステ

10

20

30

40

50

イック、または他のデータ記憶製品と関連づけられている。メモリカードの例には、PCカード（以前のPCMCI Aデバイス）、フラッシュカード、フラッシュディスク、マルチメディアカード、およびATAカードがある。

【0019】

メモリシステム200はホスト202と協働する。特にメモリシステム200は、ホスト202によって利用されるデータを記憶する。メモリシステム200およびホスト202は、ホスト入力/出力（I/O）バス上で通信する。ホスト202は、ホスト電圧V<sub>H</sub>（供給電圧）をメモリシステム200に供給する。

【0020】

メモリシステム200は、メモリコントローラ204およびメモリブロック206および208を含む。この実施形態においては、メモリシステム200は、二つのメモリブロックを含む。しかしメモリシステム200は、2つ以上のメモリブロックを含みえることに注意されたい。典型的には、追加のメモリブロックがメモリシステム200に加えられることで、そのデータ記憶容量を増すことができる。

【0021】

メモリコントローラ204は、電圧発生回路210を含む。電圧発生回路210は、ホスト202によって供給されるホスト電圧（V<sub>H</sub>）を受け取り、メモリブロック206および208に供給される複数の供給電圧群を発生する。この実施形態（および以下の他の実施形態）においては、複数の供給電圧は供給電圧V1、V2およびV3として表される。供給電圧V1、V2およびV3は、メモリブロック206および208によってそれらの動作時に利用される電圧レベルを表す。よってメモリブロック206および208は、さらにチャージポンプまたはレギュレータ回路を含まないが、これはこれらのメモリブロック206および208が、メモリコントローラ204から受け取られた供給電圧V1、V2およびV3以外の異なる供給電圧を内部で発生しないからである。したがってメモリコントローラ204は、メモリブロック206および208のために必要とされる全ての供給電圧を発生し、よってチャージポンプレギュレータ回路はメモリブロック206および208の内部には必要とされない。その結果、チャージポンプ回路によって発生されるノイズは、メモリブロック206および208の動作（特に、敏感なアナログ要素の動作）に悪影響を及ぼさない。さらに、メモリブロック206および208に関連づけられた半導体ダイの高価なダイエリアは、チャージポンプレギュレータ回路によって消費される必要がない。

【0022】

さらにメモリコントローラ204によって提供される供給電圧V1、V2およびV3は、メモリブロック206に供給される。電源バス212は、供給電圧V1、V2およびV3をメモリブロック206および208間に供給するように動作する。換言すれば、電源バス212は供給電圧V1、V2およびV3をメモリブロック208に運ぶ。さらにもしメモリシステム200が追加のメモリブロックを含むなら、電源バス212はまた、供給電圧V1、V2およびV3をそれら他の追加メモリブロックに供給する。電源バス212は、供給電圧V1、V2およびV3をメモリブロック206に供給するとも考えられる。

【0023】

典型的にはメモリコントローラ204は、供給電圧V1、V2およびV3を出力する出力接点（例えばピン、パッド、端子など）を持つ。メモリブロック206および208は、供給電圧V1、V2およびV3を受け取る入力接点を持つ。ある実現例においては、メモリコントローラ204の出力接点を、電源バス212のリンクに結合するとともに、メモリブロック206の入力接点にも結合するためにリンク（例えばワイヤ、トレースなど）が用いられる。他の実施形態においては、メモリコントローラ204の出力接点をメモリブロック206および208の両方の入力接点に結合するために電源バス212のリンクが用いられる。

【0024】

供給電圧のレベルは実現例によって変わりえる。ある例では、ホスト電圧（V<sub>H</sub>）は、

10

20

30

40

50

3.3または1.8ボルトであり、供給電圧V1、V2およびV3は2.5ボルト、6.5ボルト、および3.3ボルトでありえる。図2に示されるメモリシステム200の実施形態は供給電圧V1、V2およびV3をメモリコントローラ204において発生するが、メモリコントローラ204は、メモリシステム200の一つ以上のメモリブロックが必要とする複数の供給電圧レベルをいくつ発生してもよいことに注意されたい。

#### 【0025】

メモリブロック206および208のそれぞれは、不揮発性ディジタルデータ記憶を提供するデータ記憶要素のアレイを含む。ある実施形態においては、データ記憶要素は、電気的にプログラム可能で電気的に消去可能である。例えばデータ記憶要素はフローティングゲートデバイスに基づくものでありえる。メモリブロック206および208は、それぞれ別個の半導体ダイ、チップまたは製品である。メモリブロックは例えば、EEPROMまたはFLASHデバイスでありえる。メモリコントローラ204はまたしばしば、別個の半導体ダイ、チップまたは製品である。

#### 【0026】

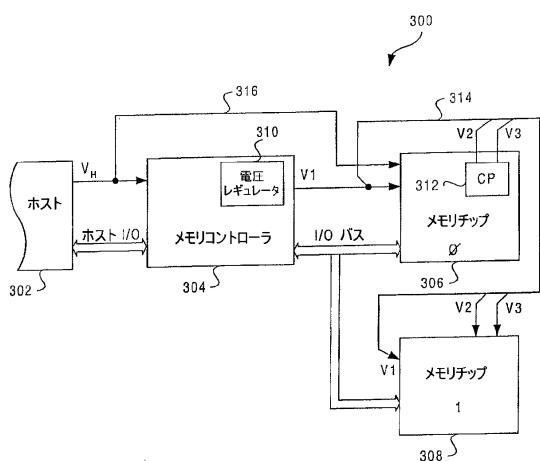

図3は本発明の別の実施形態によるメモリシステム300のブロック図である。メモリシステム300はホスト302に結合する。メモリシステム300およびホスト302間のインターフェースは、ホスト電圧( $V_H$ )およびホストI/Oバスを含む。

#### 【0027】

メモリシステム300は、メモリコントローラ304およびメモリブロック306および308を含む。メモリシステム300は、2つのメモリブロックしか含まないが、追加のメモリブロックがメモリシステム300の中に提供されてもよいことに注意されたい。メモリコントローラ304およびメモリブロック306および308は、I/Oバス上で通信する。さらにメモリコントローラ304内の電圧レギュレータ310は、供給電圧V1を発生する。電圧レギュレータ310によって発生された供給電圧V1は例えば、ホスト電圧 $V_H$ の安定化された電圧を表す。供給電圧V1は、メモリブロック306に供給される。

#### 【0028】

メモリブロック306はまた、チャージポンプ回路312を含む。チャージポンプ回路312は、供給電圧V1をメモリコントローラ304から受け取り、少なくとも一つの追加の供給電圧を発生する。この実施形態においては、チャージポンプ回路312が第2供給電圧V2および第3供給電圧V3を発生すると想定されている。したがってチャージポンプ回路312は2つより多い供給電圧を発生することもでき、あるいは単一の供給電圧を発生することもできることに注意されたい。典型的にはチャージポンプ回路312は、チャージポンプおよび/またはレギュレータを含む。

#### 【0029】

メモリシステム300はまた電源バス314を含む。電源バス314は、供給電圧V1をメモリコントローラ304(またはメモリブロック306)から受け取り、また供給電圧V2およびV3をメモリブロック306から受け取る。電源バス314はそれから、これらの供給電圧群を他のメモリブロック群、すなわちメモリ308に転送する。特にメモリブロック306およびメモリブロック308は、それぞれ供給電圧V1、V2およびV3に結合するためにそれぞれ3つの接点(例えば端子、ピンまたはパッド)を含む。電源バス314は、メモリブロック306および308のそれぞれのこれら3つの接点間をそれぞれ接続する。したがってメモリコントローラ304によって発生された供給電圧V1は、メモリブロック306に結合されることが可能なだけではなく、電源バス314を用いてメモリブロック308にも結合されることが可能である。同様に、チャージポンプ回路312によって発生された供給電圧V2およびV3は、メモリブロック306の内部で用いられることが可能なだけではなく、電源バス314を通してメモリブロック308へと(およびおそらくは他のブロックへと)外部に供給されることも可能である。したがってメモリシステム300は、メモリブロックの一つがチャージポンプ回路を含むことで、さまざまなメモリブロックによって必要とされる追加の供給電圧レベル群を発生すること

を要求するだけである。

【0030】

さらにホスト電圧  $V_H$  はまた、メモリブロック 306 にも供給されえる。チャージポンプ回路 312 はそれから、第1供給電圧  $V_1$  および / またはホスト電圧  $V_H$  を用いて第2および第3供給電圧  $V_2$  および  $V_3$  を発生する。メモリブロック 306 においてホスト電圧  $V_H$  が利用可能であるおかげで、チャージポンプ回路 312 はより効率的に第2および第3供給電圧  $V_2$  および  $V_3$  を発生することができる。例えばもしホスト電圧  $V_H$  が 5.0 ボルトであり、第1供給電圧  $V_1$  が 3.0 ボルトであるとするなら、3.0 ボルトのスタート点と比べ、5.0 ボルトのスタート点から 6.5 ボルトの第3供給電圧を発生するほうがより効率的（すなわちより少ないチャージポンピングで済む）だろう。ホスト電圧  $V_H$  は、リンク 316 を通ってメモリブロック 306 に直接に結合されえる。リンク 316 は、ワイヤ、トレースまたは他の電子的相互接続として実現できる。あるいはホスト電圧  $V_H$  は、メモリコントローラ 310 を通してメモリブロック 306 に間接的に供給されてもよい。

【0031】

さらにメモリブロック 308 内に示された点線の四角は、オプションのチャージポンプ回路 318 を表すことに注意されたい。オプションのチャージポンプ回路 318 は、メモリブロック 308（またはメモリシステム内の他のメモリブロック）内に2次的な、またはバックアップのチャージポンプ回路として提供されえる。ある実施形態においては、そのオプションのチャージポンプ回路 318 は、電源バス 313 からは利用可能でない一つ以上の追加の供給電圧をメモリブロック 308 のために発生するのに用いられる。他の実施形態においては、チャージポンプ回路 318 は、チャージポンプ回路 312 が動作不能な場合に供給電圧  $V_2$  および  $V_3$  を発生し、よって供給電圧  $V_2$  および  $V_3$  をメモリブロック 306 に電源バス 314 を介して供給するために起動されえる。そのようなオプションのチャージポンプ回路を含む実施形態においては、ホスト電圧  $V_H$  はまた、メモリ 308 に電源バス 314 またはリンク 320 を介して結合されえる。

【0032】

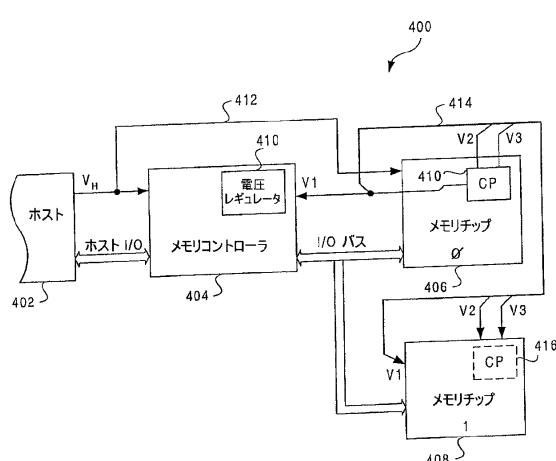

図4は、本発明のさらに他の実施形態によるメモリシステム 400 のブロック図である。メモリシステム 400 はホスト 402 に結合する。ホスト 402 およびメモリシステム 400 は、ホスト I/O バス上で通信する。ホスト 402 はまたホスト電圧  $V_H$  をメモリコントローラ 404 に供給する。メモリシステム 400 は、メモリコントローラ 404 およびメモリブロック 406 および 408 を含む。この実施形態においては、図3に示されたメモリシステム 300 のように、メモリブロック 406 はチャージポンプ回路 410 を含む。しかしメモリシステム 300 とは異なりメモリコントローラ 404 は、電圧レギュレータを含まない。換言すれば、メモリコントローラ 404 は、メモリブロック 406 および 408 によって利用されるいかなる供給電圧も発生しない。その代わりこの実施形態においては、メモリブロック 406 に設けられたチャージポンプ回路 410 がメモリブロック 406 および 408 によって必要とされる全ての供給電圧群を供給する。特にチャージポンプ回路 410 は、複数の供給電圧群、すなわち供給電圧  $V_1$ 、 $V_2$  および  $V_3$  を発生する。チャージポンプ回路 410 は、ホスト 402 によってリンク 412 を通して提供されるホスト電圧  $V_H$  を受け取る。チャージポンプ回路 410 は、供給電圧  $V_1$ 、 $V_2$  および  $V_3$  を発生するのにこのホスト電圧  $V_H$  を用いる。チャージポンプ回路 410 は、もしメモリコントローラによって望まれるなら、供給電圧  $V_1$  をメモリブロック 406 に内部的に供給するだけでなく、メモリコントローラ 404 に外部的に供給することもできる。さらに供給電圧  $V_1$ 、 $V_2$  および  $V_3$ （さらにメモリブロック 406 の内部で用いられるのに加え）は、電源バス 414 に結合される。電源バス 414 は、供給電圧  $V_1$ 、 $V_2$  および  $V_3$  をメモリブロック 406 および 408 間で結合させるように動作する。よって供給電圧  $V_1$ 、 $V_2$  および  $V_3$  は、メモリブロック 408 に電源バス 414 を介して供給される。換言すれば、メモリブロック 408 は、内部的に供給電圧レベル群のいずれかを発生するのではなく、その代わり、供給電圧レベル群を電源バス 414 を通して受け取る

10

20

30

40

50

。

## 【0033】

さらにメモリブロック408内に描かれた点線の四角形は、オプションのチャージポンプ回路416を表す。このオプションのチャージポンプ回路416は、2次チャージポンプ回路またはバックアップチャージポンプ回路としてメモリブロック408の内部に提供されえる。ある実現例においては、オプションチャージポンプ回路416は、メモリブロック408のための、電源バス414からは利用可能ではない一つ以上の追加の供給電圧を発生するのに用いられる。他の実現例においては、チャージポンプ回路416は、チャージポンプ回路410が動作不能の場合に供給電圧V1、V2およびV3を発生し、それにより供給電圧V1、V2およびV3をメモリブロック406に電源バス414を介して供給するためにアクティベートされえる。このようなオプションチャージポンプ回路を含む実施形態においては、ホスト電圧V<sub>H</sub>は、メモリブロック408にも電源バス414を介して結合されえる。10

## 【0034】

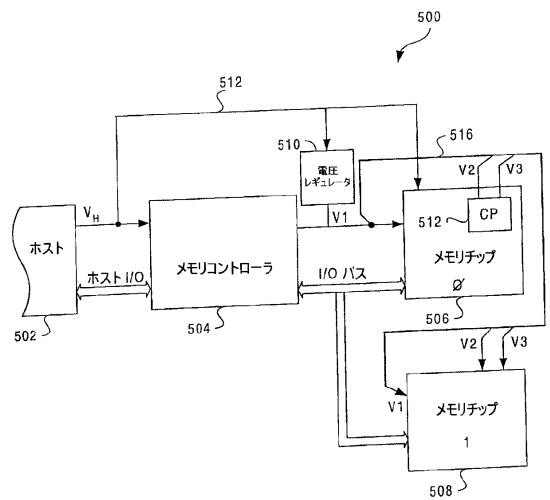

図5は、本発明のさらに他の実施形態によるメモリシステム500のブロック図である。メモリシステム500は、ホスト502に結合する。ホスト502およびメモリシステム500は、ホストI/Oバス上を通信する。ホスト502はまたホスト電圧V<sub>H</sub>をメモリシステム500に供給する。

## 【0035】

メモリシステム500は、メモリコントローラ504およびメモリブロック506および508を含む。メモリコントローラ504およびメモリブロック506および508は、I/Oバス上を通信する。メモリシステム500はまた、電圧レギュレータ510を含む。この実施形態においては、電圧レギュレータ510は、メモリコントローラ504またはメモリブロック506および508から別個の機能ユニットを表す。典型的には、電圧レギュレータ510は、メモリシステム500内の別個の半導体ダイまたはチップとして提供される。電圧レギュレータ510は、ホスト電圧V<sub>H</sub>をリンク512を通して受け取る。リンク512はまた、ホスト電圧V<sub>H</sub>をメモリブロック506に結合できる。電圧レギュレータ510は、第1供給電圧V1を発生する。電圧レギュレータ510は、第1供給電圧V1をメモリコントローラ504およびメモリブロック506に供給する。20

## 【0036】

さらにメモリブロック506は、チャージポンプ回路514を含む。チャージポンプ回路514は、少なくとも一つの追加の供給電圧を発生するように動作する。この実施形態においては、チャージポンプ回路514は、第2供給電圧V2および第3供給電圧V3を発生する。チャージポンプ回路514は、第1供給電圧V1とともにホスト電圧V<sub>H</sub>を受け取り、それによりこれらのソース電圧のいずれか、または両方を用いて供給電圧V2およびV3を発生することができる。ホスト電圧V<sub>H</sub>を用いることによって、チャージポンプ回路514はしばしばより効率的に供給電圧V2またはV3のいずれかを発生することができるが、それはより少ない「チャージポンピング」しか要求されないからである。30

## 【0037】

メモリシステム500は電源バス516も含む。電源バス516は、供給電圧V1、V2およびV3をメモリブロック508に結合する。よって供給電圧V1、V2およびV3は、メモリブロック508に電源バス516を介して入力される。換言すれば、メモリブロック508は、供給電圧群のいずれも発生しない。実際、メモリブロック508は典型的には、いかなるチャージポンプ回路も含まない。しかもしも望ましいならメモリブロック508は、一次チャージポンプ回路514が動作しないときに用いるためのバックアップ用のチャージポンプ回路を含むこともできよう。40

## 【0038】

図2～5に示された本発明の実施形態においては、メモリシステムは2つのメモリブロックを含んだ。しかしメモリシステムは、より一般的には2つ以上のメモリブロックを含みえることに注意されたい。典型的には追加のメモリブロックがメモリシステムに加えら50

れることでそれらのデータ記憶容量が増やされる。これら追加のメモリブロックは通常、メモリブロック208、308、408または508と同様に構成され、および／または動作する。また上述の本発明の実施形態のいずれにおいても、オプションのチャージポンプおよび／またはレギュレータ回路がメモリブロックの一つ以上の中に設けられる。そのようなオプションのチャージポンプおよび／またはレギュレータ回路は、一次チャージポンプおよび／またはレギュレータ回路が動作不能になった場合にバックアップ用として、または二次的機能としてはたらく。追加として、または代替として、オプションのチャージポンプおよび／またはレギュレータ回路は、メモリブロック群によって必要とされる電圧群がメモリブロックに供給されない場合に、メモリブロック内で追加の内部電圧発生を提供するよう動作しえる。

10

#### 【0039】

本発明は単一レベルメモリおよびマルチレベルメモリと用いるのに適している。メモリまたはメモリブロックは、データ記憶要素を含むデータ記憶デバイスである。データ記憶要素は、半導体デバイス（例えばフローティングゲート）、または他のタイプのデバイスに基づきえる。マルチレベルメモリにおいては、それぞれのデータ記憶要素は2つ以上のデータビットを記憶する。

#### 【0040】

本発明はさらに、上述のようにメモリシステムを含む電子システムに関しえる。メモリシステム（すなわちメモリカード）は、さまざまな電子機器とともに用いるためのデジタルデータを記憶するのにふつう用いられる。メモリシステムは、電子システムからしばしば取り外し可能で、それにより格納されたデジタルデータは携帯できる。本発明によるメモリシステムは、比較的小さいフォームファクタを持ちえて、カメラ、ハンドヘルドまたはノート型コンピュータ、ネットワークカード、ネットワーク機器、セットトップボックス、ハンドヘルドまたは他の小さなオーディオプレーヤ・レコーダ（例えばMP3機器）、および医療モニタのような電子製品のデジタルデータを格納するために用いられる。

20

#### 【0041】

本発明の利点は数多くある。異なる実施形態または実現例は、以下の利点の一つ以上を生む。本発明の一つ利点は、供給電圧の発生および分配をより高いコスト効率で行えることである。本発明の他の利点は、異なる電圧レベルの発生からのノイズがメモリアクセスパフォーマンスに悪影響を与えないことである。本発明のさらに他の利点は、信頼性のある、高いパフォーマンスのメモリシステムが得られることである。本発明のさらに他の利点は、メモリシステムが低い電力消費で、かつコントローラ設計についてより高い融通性をもって実現できることである。

30

#### 【0042】

本発明の多くの特徴および利点は、記載された説明から明らかであり、よってそのような本発明の全ての特徴および利点は添付の特許請求の範囲によってカバーされるものと意図される。さらに多くの改変および変更が当業者によって用意になされるであろうために、本発明は図示され記載されたものと同じ構成および動作に限定されるべきものではない。したがってすべての適当な改変および等価物は、本発明の範囲内にあるものとしてなされえる。

40

#### 【図面の簡単な説明】

#### 【0043】

【図1】従来のメモリシステムのブロック図である。

【図2】本発明のある実施形態によるメモリシステムのブロック図である。

【図3】本発明の他の実施形態によるメモリシステムのブロック図である。

【図4】本発明のさらに他の実施形態によるメモリシステムのブロック図である。

【図5】本発明のさらに他の実施形態によるメモリシステムのブロック図である。

【図1】

【図2】

(従来技術)

【図3】

【図4】

【図5】

---

フロントページの続き

(51) Int.Cl. F I

**G 0 6 F 1/26 (2006.01)** G 0 6 K 19/00 J

G 0 6 F 1/00 3 3 0 D

(72) 発明者 コンリー、ケビン エム。

アメリカ合衆国 9 5 1 2 0 カリフォルニア州 サンノゼ アリバード コート 5 9 8 3

(72) 発明者 ワン、チ - ミン

アメリカ合衆国 9 4 5 3 9 カリフォルニア州 フリーモント クワンタナ ウェイ 1 3 0 1

(72) 発明者 ワン、ヨンリヤン

アメリカ合衆国 9 5 0 7 0 カリフォルニア州 サラトガ デ サンカ アベニュー 1 2 3 4

4

(72) 発明者 セルネア、ラウル エイドリアン

アメリカ合衆国 9 5 0 5 4 カリフォルニア州 サンタ クララ マンション パーク ドライ

ブ 5 4 0 ナンバー 3 0 3

審査官 多賀 実

(56) 参考文献 特開平11-296430 (JP, A)

特開平03-144879 (JP, A)

特開平04-132087 (JP, A)

米国特許第05508971 (US, A)

特表2004-526239 (JP, A)

(58) 調査した分野(Int.Cl., DB名)

G06F 1/26

G06F 12/00-06

G06F 13/16-18

G06F 12/16

G06K 19/07

G11C 16/02-06