(12) Ausschließungspatent

(11) DD 288 045 A5

Erteilt gemäß § 17 Absatz 1

Patentgesetz der DDR

vom 27.10.1983

in Übereinstimmung mit den entsprechenden

Festlegungen im Einigungsvertrag

5(51) H 03 M 1/06

DEUTSCHES PATENTAMT

In der vom Anmelder eingereichten Fassung veröffentlicht

(21) DD H 03 M / 332 726 4

(22) 18.09.89

(44) 14.03.91

(71) siehe (73)

(72) Fiegenbaum, Wilfried, Dr. sc. techn. Dipl.-Ing., DE

(73) VEB Mikroelektronik „Karl Marx“ Erfurt, Rudolfstraße 47, O - 5010 Erfurt, DE

## (54) Eingangsschaltungsanordnung in einem AD-Umsetzer

(55) AD-Umsetzer; Eingangsschaltung; Spannungsteiler; Stromteiler; Umsetzungsrechner; Widerstandsfehler; Umsetzungsfehler; Serienanordnung; Parallelanordnung; Zweizyklusumsetzung; Mittelwert; Teilungsfaktor

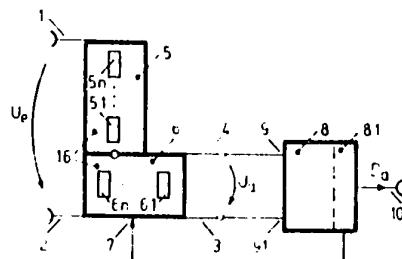

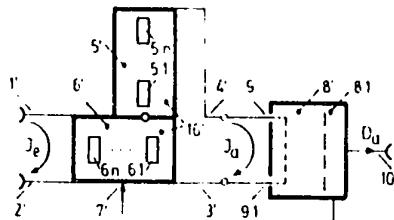

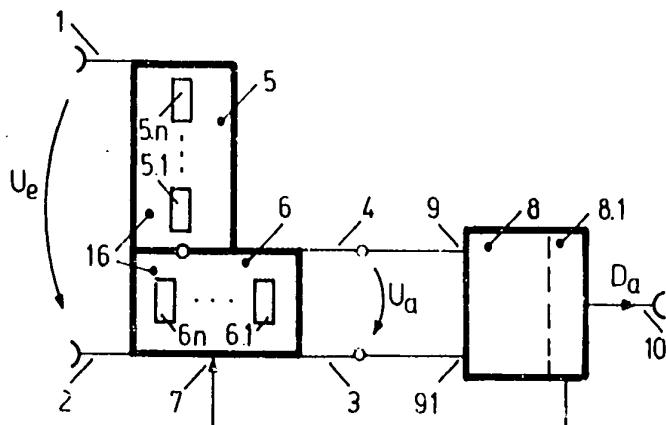

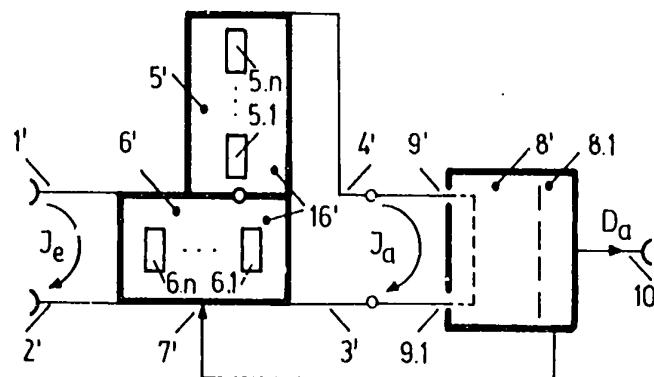

(57) Die Erfindung betrifft die Verringerung widerstandsbedingter Bewertungsfehler in AD-Umsetzern. Erfahrungsgemäß ist innerhalb einer passiven oder/und aktiven Eingangsschaltungsanordnung ein Spannungs- bzw. Stromteiler (16, 16') als Reihen- bzw. Parallelschaltung einer Serienanordnung (5, 5') und einer Parallelanordnung (6, 6') von jeweils n Widerständen (5.1 bis 5.n; 6.1 bis 6.n) gleichen Nennwertes mit zugeordneten Umschaltern angeordnet. Eine vollständige AD-Umsetzung mittels nachfolgendem internem AD-Umsetzer (8, 8') und Umsetzungsrechner (8.1) umfaßt zwei gleichwertige Zyklen – mit einem Austausch der jeweils n Widerstände der Parallelanordnung (6, 6') mit jenen der Serienanordnung (5, 5') – und einen zum Mittelwert beider Zyklusergebnisse proportionalen Ausgangsdigitalwert ( $D_u$ ). Eine zulässige Widerstandsabweichung  $\Delta R/R$  bewirkt in der vollständigen AD-Umsetzung einen Umsetzungsfehler unter  $(\Delta R/R)^2/2$ , so daß sich Präzisionswiderstände und ein Abgleich des Teilungsfaktors  $T = n^2 + 1$  erübrigen. Die Erfindung ist in der Meß- und Testtechnik anwendbar und ist für eine Ausführung als integrierter Schaltkreis geeignet. Fig. 1a, b

Fig. 1a

Fig. 1b

**Patentansprüche:**

1. Eingangsschaltungsanordnung in einem Analog/Digital(AD)-Umsetzer mit einem als Eingangsteiler oder/ur.d Gegenkopplungsteiler gebildeten Spannungsteiler oder Stromteiler, einem Differenzverstärker, einem internen AD-Umsetzer, einem ausgangsseitigen Umsetzungsrechner, einem Eingangsanschluß, einem Bezugsanschluß und einem Ausgangsanschluß, gekennzeichnet dadurch, daß zwischen den eingangsseitigen Anschlüssen (1; 2; oder 1'; 2') des Spannungsteilers (16) oder des Stromteilers (16') eine Reihenschaltung oder eine Parallelschaltung einer Serienanordnung (5 oder 5') und einer Parallelanordnung (6 oder 6') – mit dem Verbindungspunkt zwischen beiden als laststromfreien oder lastspannungsfreien Ausgangsanschluß (4; oder 4') – angeordnet und in eine passive oder aktive Spannungsbewertung oder Strombewertung innerhalb der Eingangsschaltung, an die sich der interne AD-Umsetzer (8 oder 8') anschließt, einbezogen ist, daß im Spannungsteiler (16) oder Stromteiler (16') von 2-n-Widerständen gleichen Nennwertes n Widerstände (5.1 bis 5.n) innerhalb der Serienanordnung (5; 5') in Reihe und weitere n Widerstände (6.1 bis 6.n) innerhalb der Parallelanordnung (6; 6') parallel geschaltet sind, daß im Gegensatz zu der in einem ersten Zyklus der AD-Umsetzung bestehenden Verteilung der 2-n-Widerstände (5.1 bis 5.n; 6.1 bis 6.n) während eines zweiten Zyklus wie n Widerstände der Serienanordnung (5; 5') mit jenen der Parallelanordnung (6; 6') vertauscht angeordnet sind, daß eine vollständige AD-Umsetzung den ersten und zweiten Zyklus in gleicher Häufigkeit und Wertigkeit umfaßt, und daß als Ausgangsdigitalwert ( $D_a$ ) ein zum Mittelwert der Zyklusergebnisse einer vollständigen AD-Umsetzung proportionaler Digitalwert berechnet ist.

2. Schaltungsanordnung nach Anspruch 1, gekennzeichnet dadurch, daß die ausgangsseitigen Anschlüsse des Spannungsteilers (16) oder des Stromteilers (16') jene (3; 4) der Parallelanordnung (6) oder jene (3'; 4') der Serienanordnung (5') sind.

3. Schaltungsanordnung nach den Ansprüchen 1 und 2, gekennzeichnet dadurch, daß der Spannungsteiler (16) oder Stromteiler (16') innerhalb der Eingangsschaltung vor einem als Spannungsfolger oder als Stromfolger gegengekoppelten Differenzverstärker (19 oder 24) an dessen nichtinvertierendem oder invertierendem Verstärkereingang angeordnet ist.

4. Schaltungsanordnung nach den Ansprüchen 1 bis 2, gekennzeichnet dadurch, daß innerhalb der Eingangsschaltung der Spannungsteiler (16) oder der Stromteiler (16') als verstärkungsbestimmender Gegenkopplungsteiler zwischen einem Verstärkerausgang (20' oder 26') und einem invertierenden Verstärkereingang des Differenzverstärkers (19; 24) angeordnet ist, vorzugsweise für eine Verstärkung von  $V = n^2 + 1$ .

5. Schaltungsanordnung nach den Ansprüchen 1 bis 4, gekennzeichnet dadurch, daß die Anzahl n der innerhalb der Parallelanordnung (6; 6') und der Serienanordnung (5; 5') angeordneten Widerstände (6.1 bis 3.n; 5.1 bis 5.n) jeweils  $n = 3$  beträgt.

6. Schaltungsanordnung nach den Ansprüchen 1 bis 5, gekennzeichnet dadurch, daß innerhalb der Eingangsschaltung ein Spannungsteiler (16) oder ein Stromteiler (16') hinsichtlich seiner Eingangsanschlüsse (1; 2 oder 1'; 2') einerseits und seiner Ausgangsanschlüsse (3; 4 oder 3'; 4') andererseits vertauschbar und damit auch als Stromteiler oder Spannungsteiler umsteuerbar ist.

7. Schaltungsanordnung nach den Ansprüchen 1 bis 6, gekennzeichnet dadurch, daß eine vollständige AD-Umsetzung in zwei Zyklen nur während eines Korrekturschrittes – unter Einbezug einer eingangsseitig zuschaltbaren Hilfsspannungsquelle – und im Vergleich mit einem feststehenden Spannungsteiler oder Stromteiler gebildet ist, und daß ein so für letzteren im Umsetzungsrechner (8.1) ermittelter Korrekturfaktor auf zeitlich nachfolgende AD-Umsetzungen mit diesem feststehenden Spannungsteiler oder Stromteiler korrigierend angewendet ist, vorzugsweise mit der in einer von beiden Zyklen feststehenden Anordnung der Widerstände (5.1 bis 5.n; 6.1 bis 6.n) innerhalb der Parallelanordnung (5; 5') und der Serienanordnung (6; 6') als feststehenden Spannungsteiler oder Stromteiler und mit rechnerischer Korrektur im Umsetzungsrechner (8.1).

8. Schaltungsanordnung nach den Ansprüchen 1 bis 6, gekennzeichnet dadurch, daß im Umsetzungsrechner (8.1) – unter Einbeziehung seines Ergebnisspeichers – eine mittelwertproportionale Bewertung über p erste und p zweite Zyklen der AD-Umsetzung erfolgt ( $p \geq 1$ , ganz), vorzugsweise mit nach jedem Zyklus erneuerter Bewertung über die jeweils letzten 2-p-Zyklergebnisse bei regelmäßigem Wechsel von erstem und zweitem Zyklus.

9. Schaltungsanordnung nach den Ansprüchen 1 bis 8, gekennzeichnet dadurch, daß vor dem Eingangsanschluß (1) der Eingangsschaltung und innerhalb des Umsetzungsrechners (8.1) für sich bekannte Korrekturmuschaltungen und -umrechnungen, mindestens eine Offsetgröße betreffend, gebildet und programmäßig implementiert sind und daß jeder damit gebildete Korrekturschritt eine vollständige AD-Umsetzung in zwei Zyklen umfaßt.

10. Schaltungsanordnung nach den Ansprüchen 1 bis 9, gekennzeichnet dadurch, daß für eine Bewertung von Wechselspannungen oder Wechselströmen durch den Spannungsteiler (16) oder den Stromteiler (16') innerhalb der Eingangsschaltung letztere ausgangsseitig einen zugeordneten und vorzugsweise zuschaltbaren Wechselgrößen-/Gleichgrößen-Konverter aufweist.

11. Schaltungsanordnung nach den Ansprüchen 1 bis 10, gekennzeichnet dadurch, daß die jeweils aktivierte Anzahl  $2^n$  der Widerstände (5.1 bis 5.n; 6.1 bis 6.n) innerhalb des Spannungsteilers (16) oder des Stromteilers (16') über Schalter umsteuerbar ist.

12. Schaltungsanordnung nach den Ansprüchen 1 bis 11, gekennzeichnet dadurch, daß vor, nach oder anstelle der eigentlichen Eingangsschaltung, die mindestens aus einem Spannungs- oder Stromteiler (16 oder 16') und einem Differenzverstärker (19; 24) besteht, ein Spannungsteiler oder Stromteiler mit dem Teilungsverhältnis  $(n^2 + 1):1$  – gegebenenfalls in der Gegenkopplung eines Verstärkers der Verstärkung  $n^2 + 1$  – zuschaltbar angeordnet und dafür innerhalb des Umsetzungsrechners (8.1) ein Korrekturprogramm implementiert ist, vorzugsweise zur rechnerischen Ergebniskorrektur.

13. Schaltungsanordnung nach den Ansprüchen 1 bis 12, gekennzeichnet dadurch, daß innerhalb einer Eingangsschaltung eine Anzahl B gleichzeitig und unabhängig bewertender Teiler  $T_b$  ( $b = 1$  bis B; Spannungs- oder/und Stromteiler), jeweils mit interner Serien- und Parallelanordnung von  $2 \cdot n_b$  Widerständen und innerhalb jedes Teilers  $T_b$  gleichem Widerstandsnennwert  $R_b$ , angeordnet ist und daß ein vollständiger AD-Umsetzungszyklus  $2^B$  verschiedene Zyklen mit darüber mittelwertproportionalem Ausgangsdigitalwert ( $D_a$ ) und  $2^B - 1$  verschiedene Kombinationen von Widerstandsvertauschungen zwischen den jeweils zugeordneten der <sup>B</sup> Serien- und Parallelanordnungen umfaßt.

Hierzu 3 Seiten Zeichnungen

#### Anwendungsbereich der Erfindung

Die Erfindung betrifft eine bewertende, mit Spannungs- oder/und Stromteilung ausgestattete passive oder/und aktive Eingangsschaltungsanordnung in einem AD-Umsetzer mit sehr geringem Umsetzungsfehler. Sie ist vor allem in Geräten und Baugruppen der elektronischen Meß- und Testtechnik anwendbar und kann als integrierter Schaltkreis ausgeführt werden.

#### Charakteristik des bekannten Standes der Technik

Hochauflösende Analog/Digital(AD)-Umsetzung mit geringem Umsetzungsfehler erfolgt üblicherweise im Nennaussteuerbereich eines eigentlichen (internen) AD-Umsetzers, vor allem mit im allgemeinen integrierender und damit störunterdrückender Bewertung der mittleren Gleichspannung oder des mittleren Gleichstromes (G. Sahner; Digitale Meßverfahren; VEB Verlag Technik, Berlin, 1987). Dem internen AD-Umsetzer ist eine betriebsarten- und bereichsabhängig bewertende Eingangsschaltung vorangestellt, die das Eingangssignal (Spannung, Strom) verstärkt oder/und teilt sowie gegebenenfalls ergänzt ist durch Aufgaben der normierenden Analoggrößenwandlung für andere analoge Eingangsgrößen. Eingangsspannungsteiler bis etwa 1 000 V und Nanovoltverstärker in Präzisionsdigitalvoltmetern sind typische Ausführungen solcher Eingangsschaltungen. (B. Nicholson; Novel A/D converters, built-in facilities extend DMM accuracies and capabilities; EDN, April 5, 1984, S. 85-91).

Der bezüglich des Eingangssignales innerhalb der Eingangsschaltung wirksame Bewertungsfehler hängt im wesentlichen von den diesbezüglichen Eigenschaften (Temperaturabhängigkeit, Langzeitkonstanz) der als Eingangs- oder/und Gegenkopplungsteiler von Differenzverstärkern eingesetzten Spannungs- oder Stromteiler ab (M. Seifert; Analoge Schaltungen; VEB Verlag Technik, Berlin, 1987). Dabei ist für eine AD-Umsetzung mit sehr geringem Umsetzungsfehler bezüglich des Differenzverstärkers mit einer geringen zeit- und temperaturabhängigen Drift sowie einer sehr hohen Leerlaufverstärkung ein beträchtlicher Aufwand erforderlich (J. Dostal; Operationsverstärker; VEB Verlag Technik, Berlin, 1986). Über die Spannungs- und Stromteiler hängen die Eigenschaften der gesamten AD-Umsetzung dann nahezu vollständig von den verstärkungsbestimmenden Widerständen oder Widerstandsverhältnissen ab, vor allem hinsichtlich der temperaturabhängigen und zeitlichen Stabilität (W. Fiegenbaum; Präzisions-AD- und Präzisions-DA-Umsetzung; radio – fernsehen – elektronik 30 [1981], H. 7, S. 416-421; H. 8, S. 517-522). Für einen Temperaturbereich von 10 K und über ein Jahr ist derzeit mit handelsüblichen Präzisionswiderständen der widerstandsbedingte Bewertungsfehler in einer solchen Eingangsschaltung auf etwa  $1 \cdot 10^{-5}$  begrenzt, mit Widerstandsteilern in monolithisch integrierten Schaltkreisen dagegen nur auf etwa  $1 \cdot 10^{-3}$ .

Eine Thermostatisierung der genauigkeitsbestimmenden Spannungs- oder Stromteiler ist mit sehr hohem Aufwand verbunden und verringert nur den temperaturabhängigen Fehleranteil, wobei langzeitig sogar ein verstärkter Fehler durch Alterung zu verzeichnen ist.

Der Nachteil der bekannten spannungs- oder strombewertenden Eingangsschaltungen in hochauflösenden AD-Umsetzern besteht vor allem in einer prinzipiell begrenzten Bewertungsgenauigkeit durch die widerstandsbestückten Spannungs- oder Stromteiler. Zudem sind ein beträchtlicher Abgleich- und Prüfaufwand erforderlich.

### Ziel der Erfindung

Es ist das Ziel der Erfindung, den Bewertungsfehler von spannungs- oder strombewertenden Eingangsschaltungen in AD-Umsetzern zu verringern.

### Darlegung des Wesens der Erfindung

Aufgabe der Erfindung ist es, eine spannungs- oder strombewertende Eingangsschaltung in AD-Umsetzern zu schaffen, deren widerstandsbedingter Bewertungsfehler innerhalb des AD-Umsetzungsfehlers wesentlich reduziert ist.

Erfindungsgemäß ist die Aufgabe für eine Eingangsschaltung in einem AD-Umsetzer mit einem als Eingangsteiler oder/und Gegenkopplungsteiler gebildeten Spannungsteiler oder Stromteiler, einem Differenzverstärker, einem internen AD-Umsetzer, einem ausgangsseitigen Umsetzungsrechner, einem Eingangsanschluß, einem Bezugsanschluß und einem Ausgangsanschluß dadurch gelöst, daß zwischen den eingangsseitigen Anschlüssen des Spannungsteilers oder des Stromteilers eine Reihenschaltung oder eine Parallelschaltung einer Serienanordnung und einer Parallelanordnung – mit dem Verbindungspunkt zwischen beiden als laststromfrei oder lastspannungsfreiem Ausgangsanschluß – angeordnet und in eine passive oder aktive Spannungsbewertung oder Strombewertung innerhalb der Eingangsschaltung, an die sich der interne AD-Umsetzer anschließt, einbezogen ist. Im Spannungsteiler oder Stromteiler sind von 2-n-Widerständen gleichen Nennwertes n Widerstände innerhalb der Serienanordnung in Reihe und weitere n Widerstände innerhalb der Parallelanordnung parallel geschaltet. Im Gegensatz zu dieser in einem ersten Zyklus der AD-Umsetzung bestehenden Verteilung der 2-n-Widerstände sind während eines zweiten Zyklus – unter Verwendung von Umschaltmitteln – die n Widerstände der Serienanordnung mit jenen der Parallelanordnung vertauscht. Eine vollständige AD-Umsetzung umfaßt den ersten und zweiten Zyklus in gleicher Häufigkeit und Wertigkeit, vorzugsweise jeden von zwei gleichwertigeren Zyklen einmal. Als Ausgangsdigitalwert wird ein zum Mittelwert der Zyklusergebnisse einer vollständigen AD-Umsetzung proportionaler – vorzugsweise gleicher – Digitalwert berechnet.

Es ist zweckmäßig, daß die ausgangsseitigen Anschlüsse des Spannungsteilers oder des Stromteilers jene der Parallelanordnung oder jene der Serienanordnung sind, so daß sich ein Teilungsfaktor von  $(n^2 + 1):1$  ergibt.

Der Teilungsfaktor eines solchen Spannungs- oder Stromteilers, bestehend aus der Serienanordnung und der Parallelanordnung, beträgt allgemein  $n^2 + 1$  oder  $1 - (n^2 + 1)$ , je nach ausgangsseitigen Anschlußanordnungen.

Wegen der vollständigen Parallel/Serien-Widerstandsvertauschung erhält man für eine relative Widerstandsabweichung von  $\Delta R/R$  unter allen 2-n-Widerständen des Spannungsteilers oder Stromteilers bezüglich der über zwei gleiche Zyklen gemittelten AD-Umsetzung betragsmäßig nur einen widerstandsbedingten Teilungs-Restfehler der vollständigen AD-Umsetzung von  $\leq 1/2 \cdot (\Delta R/R)^2$ , beispielsweise  $\leq 5 \cdot 10^{-7}$  für  $|\Delta R/R| \leq 10^{-3}$ .

Es ist zur Realisierung näherungswise idealisierter Tellerlastbedingungen und zur Impedanzwandlung vorteilhaft, daß der Spannungsteiler oder der Stromteiler innerhalb der Eingangsschaltung vor einem als Spannungsfolger oder Stromfolger gegengekoppelten Differenzverstärker an dessen nichtinvertierendem oder invertierendem Verstärkereingang angeschlossen ist.

Es ist vorteilhaft, daß innerhalb der Eingangsschaltung der Spannungsteiler oder der Stromteiler als verstärkungsbestimmender Gegenkopplungsteiler zwischen einem Verstärkerausgang und einem invertierenden Verstärkereingang des Differenzverstärkers in dieser Wirkungsrichtung angeordnet ist, vorzugsweise für eine Verstärkung von  $V = n^2 + 1$ .

Es ist zweckmäßig, daß die Anzahl n der innerhalb der Parallelanordnung und der Serienanordnung angeordneten Widerstände jeweils  $n = 3$  beträgt, womit sich ein fehlerreduziert nutzbarer Teilungs- oder Verstärkungsfaktor von 10 ergibt.

Es ist vorteilhaft, daß innerhalb der gleichen Eingangsschaltung ein Spannungsteiler oder ein Stromteiler hinsichtlich seiner Eingangsanschlüsse einerseits und seiner Ausgangsanschlüsse andererseits mittels Umschaltung mittels vertauschbar und damit – invers betrieben – auch als Stromteiler oder Spannungsteiler umsteuerbar ist, natürlich im Zusammenspiel mit dualen Lastbedingungen (Leerlauf oder Kurzschluß). Diese Verteilbarkeit (Dualität) ist eine spezielle Eigenschaft solcher Spannungs- und Stromteiler mit den voraussetzungsgemäßen Serien- und Parallelanordnungen von jeweils n Widerständen gleichen Nennwertes.

Es ist auch vorteilhaft, daß eine vollständige AD-Umsetzung in zwei Zyklen nur während eines Korrekturschrittes – unter Einbezug einer eingangsseitig zuschaltbaren Hilfsspannungsquelle – und im Vergleich mit einem feststehenden Spannungsteiler oder Stromteiler gebildet ist und daß ein so für letzteren im Umsetzungsrechner ermittelter Korrekturfaktor auf zeltlich nachfolgende AD-Umsetzungen mit diesem feststehenden Spannungsteiler oder Stromteiler korrigierend angewendet ist, vorzugsweise mit der in einer von beiden Zyklen bestehenden Anordnung der Widerstände innerhalb der Parallelanordnung und der Serienanordnung als feststehendem Spannungsteiler oder Stromteiler und mit rechnerischer Korrektur im Umsetzungsrechner.

Zur erhöhten Anzeigeauflösung und Störunterdrückung der vollständigen AD-Umsetzung ist es ferner vorteilhaft, daß im Umsetzungsrechner – unter Einbeziehung seines Ergebnisspeichers – eine mittelwertproportionale Bewertung über p erste und p zweite Zyklen der AD-Umsetzung erfolgt ( $p \geq 1$ , ganz) vorzugsweise mit nach jedem Zyklus erneuter Bewertung über die jeweils letzten 2-p-Zyklusergebnisse bei regelmäßigem Wechsel von erstem und zweitem Zyklus.

Es ist zweckmäßig, daß vor dem Eingangsanschluß der Eingangsschaltung und innerhalb des Umsetzungsrechners für sich bekannte Korrekturmischaltungen und -umrechnungen, mindestens eine Offsetgröße betreffend, gebildet und programmäßig implementiert sind und daß jeder damit gebildete Korrekturschritt eine vollständige AD-Umsetzung in zwei Zyklen umfaßt.

Zweckmäßig ist auch, daß für eine Bewertung (Teilung und/oder Verstärkung) von Wechselspannungen oder Wechselströmen durch den Spannungsteiler oder Stromteiler innerhalb der Eingangsschaltung letztere ausgangsseitig einen zugeordneten und vorzugsweise zuschaltbaren Wechselgrößen-/Gleichgrößen-Konverter aufweist.

Zur Teilungs- oder Verstärkungsveränderung ist es vorteilhaft, daß die jeweils aktivierte Anzahl  $2n$  der Widerstände innerhalb des Spannungsteilers oder des Stromteilers über Schalter umsteuerbar ist, vor allem für den Teilungs- oder Verstärkungsfaktor  $n^2 + 1$ , beispielsweise im Wechsel zwischen  $n = 3$  ( $n^2 + 1 = 10$ ) und  $n = 1$  ( $n^2 + 1 = 2$ ).

Es ist zur Übertragbarkeit des erreichbaren sehr geringen widerstandsbedingten Restfehlers der AD-Umsetzung auf andere Teilungs- oder/und Verstärkungsmittel innerhalb einer allgemeineren Eingangsschaltung zweckmäßig, daß vor, nach oder anstelle der eigentlichen Eingangsschaltung, die mindestens aus einem Spannungs- oder Stromteiler und einem Differenzverstärker besteht, ein Spannungsteiler oder Stromteiler mit dem Teilungsverhältnis  $(n^2 + 1):1$  – gegebenenfalls in der Gegenkopplung eines Verstärkers der Verstärkung  $n^2 + 1$  – zuschaltbar angeordnet und dafür innerhalb des Umsetzungsrechners ein Korrekturprogramm implementiert ist, vorzugsweise zur rechnerischen, oder aber auch zur rückkoppelnd steuernden Korrektur des Ergebnisses oder des korrekturbedürftigen Teilungsfaktors.

Es kann vorteilhaft sein, daß innerhalb einer Eingangsschaltung eine Anzahl  $B$  gleichzeitig und unabhängig bewertender Teiler  $T$  ( $b = 1$  bis  $B$ ; Spannungs- oder/und Stromteiler), jeweils mit interner Serien- und Parallelanordnung von  $2 \cdot n_b$  Widerständen und innerhalb jedes Teilers  $T_b$  gleichem Widerstandswert  $R_b$ , angeordnet ist und daß ein vollständiger AD-Umsetzungszyklus  $2^B$  verschiedene Zyklen mit darüber mittelwertproportionalem Ausgangsdigitalwert ( $D_b$ ) und  $2^B - 1$  verschiedene Kombinationen von Widerstandsvertauschungen zwischen den jeweils zugeordneten der  $B$  Serien- und Parallelanordnungen umfaßt.

Beispielsweise ergeben sich für  $B = 2$  Teiler  $2^2 = 4$  verschiedene Zyklen mit  $2^2 - 1 = 3$  verschiedene Tauschkombinationen und (maximal) 2 verschiedene Widerstandsnnennwerte  $R_1$  und  $R_2$ .

Die erfindungsgemäße Lösung für eine Eingangsschaltung in einem AD-Umsetzer hat den Vorteil, daß widerstandsbedingte Teilungs- oder/und Verstärkungsfehler bezüglich des vollständigen AD-Umsetzungsergebnisses wesentlich reduziert sind, so daß sich Präzisionswiderstände und Abgleicharbeiten erübrigen, und daß auch in Ausführung als integrierter Schaltkreis den diesbezüglichen Präzisionsanforderungen genügt werden kann.

### Ausführungsbeispiel

Die Erfindung soll im folgenden anhand eines Ausführungsbeispiels näher erläutert werden. Die zugehörige Zeichnung zeigt

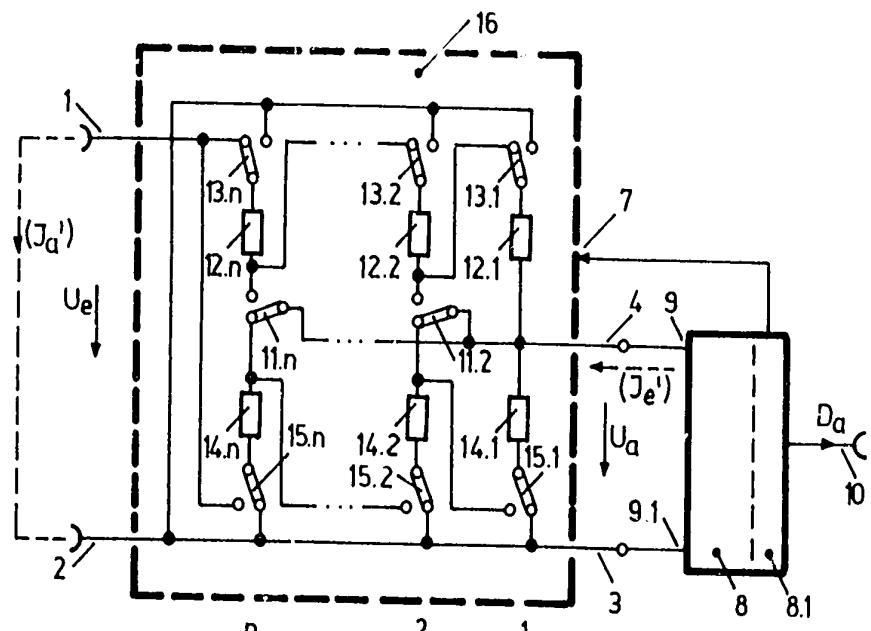

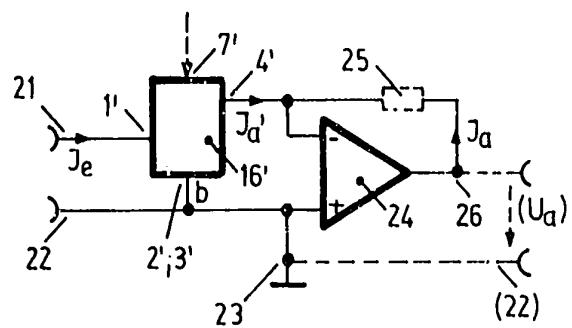

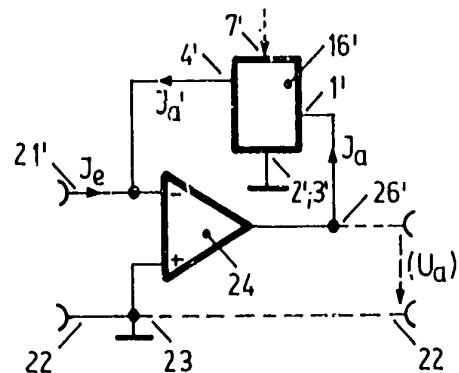

Fig.1: Blockschaltbilder der erfindungsgemäßen Lösung,

Fig.2: eine Detaildarstellung des Spannungsteilers mit den erforderlichen Umschaltern zum Vertauschen von Serien- und Parallelanordnung,

Fig.3: Anwendungsbeispiele mit Spannungsteilern,

Fig.4: Anwendungsbeispiele mit Stromteilern.

Die erfindungsgemäßen Eingangsschaltungen in AD-Umsetzern gemäß den Blockschaltbildern in Fig.1a und Fig.1b weisen jeweils einen Eingangsanschluß 1; 1', einen Bezugsanschluß 2; 2' und einen Schaltungsausgang 10 für einen Ausgangsdigitalwert  $D_b$  auf. Sie enthalten jeweils einen Spannungsteiler 16 oder Stromteiler 16' – mit der Reihenschaltung einer Serienanordnung 5; 5' und einer Parallelanordnung 6; 6' – und einen nachgeordneten internen AD-Umsetzer 8; 8', mit einem ausgangsseitigen Umsetzungsrechner 8.1. Der Spannungsteiler 16 und der Stromteiler 16' werden seitens des Umsetzungsrechners 8.1 über Steuereingänge 7; 7' gesteuert und sind mit ihren Ausgangsanschlüssen 4; 4' an Eingängen 1; 1' und mit ihren Ausgangsbezugsanschlüssen 3; 3' an Bezugseingängen 9.1; 9.1' der internen AD-Umsetzer 8; 8' angeschlossen. Innerhalb des Spannungsteilers 16 und des Stromteilers 16' sind jeweils 2-n-Widerstände 5.1. bis 5.n und 6.1 bis 6.n gleichen Nennwertes angeordnet. Davon sind jeweils  $n$  Widerstände – ein erster 5.1. bis  $n$ -ter 5.n Serienwiderstand – innerhalb der Serienanordnung 5; 5' in Reihe und  $n$  Widerstände – ein erster 6.1 bis  $n$ -ter 6.n Parallelwiderstand – innerhalb der Parallelanordnung 6; 6' parallel angeordnet. Für den Spannungsteiler 16 in Fig.1a bildet der Verbindungsanschluß zwischen der Serienanordnung 5 und der Parallelanordnung 6 den Ausgangsanschluß 4, der äußere Anschluß der Serienanordnung 5 den Eingangsanschluß 1 und der äußere Anschluß der Parallelanordnung 6 zugleich den Eingangsbezugsanschluß 2 und den Ausgangsbezugsanschluß 3. Für den Stromteiler 16' in Fig.1b bildet der Verbindungsanschluß zwischen der Serienanordnung 5' und der Parallelanordnung 6' den Eingangsanschluß 1', der äußere Anschluß der Serienanordnung 5' der Ausgangsanschluß 4' und der äußere Anschluß der Parallelanordnung 6' zugleich den Eingangsanschluß 2' und den Ausgangsbezugsanschluß 3'. Zwischen einer anliegenden Eingangsspannung  $U_b$  und einer laufenden Ausgangsspannung  $U_b$  des Spannungsteilers 16 oder einem einströmenden Eingangstrom  $I_b$  und einem kurzgeschlossenen Ausgangstrom  $I_b$  des Stromteilers 16' entsteht dann ein Teilungsfaktor von  $T = n^2 + 1$ . Dieser Teilungsfaktor ist normalerweise infolge von Toleranzen der Widerstandswerte etwa in gleichem Maße fehlerbehaftet. Zur Reduzierung dieses Teilungsfehlers innerhalb des Fehlers der AD-Umsetzung wird letztere in zwei gleichwertigen Zyklen ausgeführt und ein zum Mittelwert beider Zyklusergebnisse proportionaler Ausgangsdigitalwert  $D_b$  ausgegeben. Über Umschaltmittel (in Fig.1 nicht dargestellt) werden innerhalb des Spannungsteilers 16 oder des Stromteilers 16' zwischen beiden Zyklen der AD-Umsetzung die  $n$  Serienwiderstände 5.1 bis 5.n der Serienanordnung 5; 5' mit den  $n$  Parallel-Widerständen 6.1 bis 6.n der Parallelanordnung 6; 6' vertauscht.

Das Ergebnis der vollständigen AD-Umsetzung (über zwei Zyklen, mittelwertproportional, vertauschte Widerstände) ist von widerstandsbedingten Umsetzungsfehlern (aus fehlerhafter Verstärkung) nahezu befreit, denn für eine relative Abweichung von  $\Delta R/R$  der 2-n-Widerstände 5.1 bis 5.n und 6.1 bis 6.n untereinander ergibt sich der daraus resultierende AD-Umsetzungsfehler im Ausgangsdigitalwert  $D_b$  betragsmäßig nicht größer als  $1/2 \cdot (\Delta R/R)^2$ , beispielsweise  $5 \cdot 10^{-9}$  für  $|\Delta R/R| = 10^{-4}$ , was derzeit auch mit Präzisionswiderständen in feststehenden Spannungs- oder Stromteilern bei weitem nicht erreichbar ist, vor allem nicht zeit- und temperaturunabhängig. Andererseits sind mit entsprechenden integrierten Schaltkreisen bereits für  $|\Delta R/R| \leq 10^{-2}$  teilungsbedingte Umsetzungsfehler unter  $5 \cdot 10^{-6}$  zu erwarten. Von besonderer Bedeutung erscheint die Realisierung dekadischer Spannungs- oder Stromteiler 16; 16' mit  $n = 3$ .

Es erscheint auch zweckmäßig, die so für die vollständige AD-Umsetzung in zwei Zyklen erreichbare Teilungsgenauigkeit in gelegentlichen Korrekturschritten zur davon abgeleiteten Korrektur zeitlich nachfolgender AD-Umsetzungen (dann jedoch nur in einem Zyklus) zu verwenden, rechnerisch oder auch mit rückkoppelnder Korrektursteuerung eines feststehenden Tellers. Dafür ist eine über beide Zyklen kurzzeitstabile Korrekturhilfsspannung zuschaltbar vorzusehen.

In Fig. 2 ist ein mit Widerständen gleichen Nennwertes und mit Umschaltmitteln gebildeter Spannungsteiler 16 zwischen der Eingangsspannung  $U_e$  und der unbelasteten Ausgangsspannung  $U_o$  dargestellt, der bei umgekehrter (Inverser) äußerer Anschlußgestaltung wahlweise auch als Stromteiler 16' zwischen dem dann gültigen Eingangstrom  $I_e$  und dem Ausgangstrom  $I_o$  bei ausgangsseitigem Kurzschluß (gestrichelt dargestellt) verwendbar ist. Für 2-n-Widerstände (Teilungsfaktor  $n^2 + 1$ ) sind in der verallgemeinerungsfähigen Schaltungsanordnung nach Fig. 2 jeweils  $3n - 1$  Umschalter erforderlich. Gleichzeitiges Umschalten aller Umschalter kennzeichnet den Wechsel von einem zum anderen Zyklus der vollständigen AD-Umsetzung in zwei Zyklen.

Für den in Fig. 2 aufgrund der Schalterstellungen dargestellten Zyklus bilden ein erster 12.1, zweiter 12.2 bis n-ter 12.n Serienwiderstand in Reihe die Serienanordnung 5 und ein erster 14.1, zweiter 14.2 bis n-ter 14.n Parallelwiderstand parallel geschaltet die Parallelanordnung 6 nach Fig. 1. Während des anderen Zyklus nach Umschaltung aller Umschalter 11.2...11.n, 13.1...13.n und 15.1...15.n in Fig. 2 werden die bisherigen Parallelwiderstände 14.1 bis 14.n zu Reihe angeordneten Bestandteilen der Serienanordnung 5 und die bisherigen Serienwiderstände 12.1 bis 12.2 zu parallel geschalteten Bestandteilen der Parallelanordnung 6 nach Fig. 1.

Für die zyklusabhängige Umschaltung mit vollständigem Widerstandtausch verbinden ein erster 13.1, zweiter 13.2 bis n-ter 13.n Serienumschalter die zugeordneten ersten 12.1 bis n-ten 12.n Serienwiderstände entweder in Reihe und mit dem Eingangsanschluß 1 (erster Zyklus) oder parallel und mit den Bezugsanschlüssen 2 und 3 (zweiter Zyklus), verbinden ein erster 15.1, zweiter 15.2 bis n-ter 15.n Bezugsumschalter die zugeordneten ersten 14.1 bis n-ten 14.n Parallelwiderstände entweder parallel und mit den Bezugsanschlüssen 2 und 3 (erster Zyklus) oder in Reihe und mit dem Eingangsanschluß 1 (zweiter Zyklus) und verbinden ein zweiter 11.2 bis n-ter 11.n Parallelumschalter entweder die n-1 zugeordneten zweiten 14.2 bis n-ten 14.n Parallelwiderstände (erster Zyklus) oder die n-1 zugeordneten zweiten 12.2 bis n-ten 12.n Serienwiderstände (zweiter Zyklus) mit dem Ausgangsanschluß 4, an dem ferner der erste Serienwiderstand 12.1 und der erste Parallelwiderstand 14.1 ständig angeschlossen sind. Die zyklusabhängige Umschaltung wird über den Steuereingang 7 des Spannungsteilers 16 durch den Umsetzungsrechner 8.1 gesteuert.

In Fig. 3a und Fig. 3b sind Anwendungsbeispiele für das Zusammenspiel des Spannungsteilers 16 nach Fig. 1a bzw. Fig. 2 mit Differenzverstärkern 19 dargestellt. Gemäß Fig. 3a bilden ein Eingangsanschluß 17 und ein Bezugsanschluß 18 den Eingangsanschluß 1 und den Bezugsanschluß 2; 3 des Spannungsteilers 16. Der als Elektrometerverstärker der Verstärkung  $n^2$  (Spannungsfolger) vollständig gegengekoppelte Differenzverstärker 19 mit einem Verstärkerausgang 20 für die Ausgangsspannung  $U_o$  ist mit seinem nichtinvertierenden Eingang am Ausgangsanschluß 4 für eine Ausgangsspannung  $U_o$  des Spannungsteilers 16 angeschlossen und dient beispielsweise einer fehlerarmen Impedanzwandlung.

Dagegen bildet in Fig. 3b der Spannungsteiler 16 mit dem an einem Verstärkerausgang 20' angeschlossenen Eingangsanschluß 1 und dem am Invertierenden Eingang des Differenzverstärkers 19 angeschlossenen Ausgangsanschluß 4 den verstärkungsbestimmenden Gegenkopplungsteiler (Verstärkung  $n^2 + 1$ ). Die Eingangsspannung  $U_e$  liegt an dem nichtinvertierenden Eingang 17' des Differenzverstärkers 19.

Ein in Fig. 4a mit seinem Eingangsanschluß 1' einem Eingangsanschluß 21 und mit seinen Bezugsanschlüssen 2'; 3' einem Bezugsanschluß 22 zugeordneter Stromteiler 16' ist bezüglich seines Ausgangstromes  $I_o$  über den Ausgangsanschluß 4' mit dem invertierenden Eingang eines strommäßig vollständig gegengekoppelten Differenzverstärkers 24 (Spannungsfolger) verbunden, der eingangsseitig nichtinvertierend auf Bezugspotential 23 bezogen ist. Über die Einordnung in die vollständige AD-Umsetzung in zwei Zyklen wird zwischen dem Eingangstrom  $I_e$  und dem Ausgangstrom  $I_o$ , kompensierend vom Verstärkerausgang 26 zum invertierenden Eingang gerichtet, die volle Reduzierung des widerstandsbedingten Umsetzungsfehlers wirksam, während beispielsweise mit einem Lastwiderstand 25 in der Gegenkopplungsverbindung (als Konvertierungsnorm gestrichelt dargestellt) für die Ausgangsspannung  $U_o$  die Fehlerhaftigkeit des Lastwiderstandes 25 auch voll fehlerwirksam wird.

In Fig. 4b bildet der Stromteiler 16' den Gegenkopplungsteiler eines über den auf Bezugspotential 23 bezogenen Differenzverstärkers 24 gebildeten Stromverstärkers mit dem Verstärkungsfaktor  $n^2 + 1$ . Ein Eingangsanschluß 21' ist mit dem invertierenden Eingang des Differenzverstärkers 24 und dem Ausgangsanschluß 4' des Stromteilers 16' verbunden, dessen Eingangsanschluß 1' mit einem Verstärkerausgang 26' für den Ausgangstrom  $I_o$  verbunden ist. Die gegebenenfalls ausgangsseitig entnommene Ausgangsspannung  $U_o$  ist für die vollständige AD-Umsetzung wiederum über den Fehler des wirksamen Konvertierungswiderstandes (Eingangswiderstand des Stromteilers 16') voll fehlerbehaftet, im Gegensatz zum Ausgangstrom  $I_o$ .

288045 6

Fig. 1a

Fig. 1b

288045 8

Fig. 4a

Fig. 4b