(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4129314号

(P4129314)

(45) 発行日 平成20年8月6日(2008.8.6)

(24) 登録日 平成20年5月23日(2008.5.23)

|                |                                      |

|----------------|--------------------------------------|

| (51) Int.Cl.   | F 1                                  |

| G 0 6 F  1/24  | (2006.01)   G 0 6 F  1/00   3 5 0 A  |

| G 0 6 F  13/00 | (2006.01)   G 0 6 F  13/00   3 5 3 V |

| H 0 4 L  29/10 | (2006.01)   H 0 4 L  13/00   3 0 9 Z |

| G 0 6 F  1/12  | (2006.01)   G 0 6 F  1/04   3 4 0 A  |

請求項の数 18 (全 14 頁)

|              |                        |

|--------------|------------------------|

| (21) 出願番号    | 特願平10-147743           |

| (22) 出願日     | 平成10年5月28日(1998.5.28)  |

| (65) 公開番号    | 特開平11-175198           |

| (43) 公開日     | 平成11年7月2日(1999.7.2)    |

| 審査請求日        | 平成17年4月22日(2005.4.22)  |

| (31) 優先権主張番号 | 08/961190              |

| (32) 優先日     | 平成9年10月30日(1997.10.30) |

| (33) 優先権主張国  | 米国(US)                 |

|           |                                                                                                                                                                                                                               |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 591016172<br>アドバンスト・マイクロ・ディバイシズ・<br>インコーポレイテッド<br>A D V A N C E D M I C R O D E V I<br>C E S I N C O R P O R A T E D<br>アメリカ合衆国、94088-3453<br>カリフォルニア州、サンディベイル、ビィ・<br>オウ・ボックス・3453、ワン・エイ・<br>エム・ディ・プレイス、メイル・ストップ<br>・68(番地なし) |

| (74) 代理人  | 100064746<br>弁理士 深見 久郎                                                                                                                                                                                                        |

| (74) 代理人  | 100085132<br>弁理士 森田 俊雄                                                                                                                                                                                                        |

最終頁に続く

(54) 【発明の名称】ネットワークインタフェース、ネットワークインタフェースを初期化するための装置およびネットワークインタフェース内に構成情報をロードする方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ネットワークからネットワーククロックを受信するため構成されるネットワークインタフェースを初期化するための装置であって、前記装置は、

パワーオン条件の検出に応答して前記ネットワークインタフェースに対しリセット信号を生成するため構成されるリセット検出回路を含み、前記リセット検出回路は、ネットワーククロック検出信号を受信するまで前記リセット信号を出力し、前記装置はさらに、

前記ネットワーククロックの検出から予め定められた間隔後に前記ネットワーククロック検出信号を生成するため構成されるネットワーククロック検出回路を含み、

前記ネットワークインタフェースは、前記リセット信号および前記ネットワーククロックに応答して、不揮発性メモリから初期化情報をロードするため構成される、ネットワークインタフェースを初期化するための装置。

## 【請求項 2】

前記ネットワーククロック検出回路は、前記ネットワーククロックに応答して前記リセット信号をストアするため構成される少なくとも1つの遅延フリップフロップを含み、前記遅延フリップフロップは、前記リセット信号のストアに際して前記ネットワーククロック検出信号を出力する、請求項1に記載のネットワークインタフェースを初期化するための装置。

## 【請求項 3】

前記ネットワーククロック検出回路は、前記ネットワーククロックに応答して前記リセ

10

20

ット信号を連続してストアするため構成される複数の前記遅延フリップフロップを含み、選択された1つの前記遅延フリップフロップは、前記リセット信号の対応する連続したストアに際して、対応する前記ネットワーククロック検出信号を前記リセット検出回路へ出力する、請求項2に記載のネットワークインターフェースを初期化するための装置。

【請求項4】

ネットワークからのネットワーククロックを受信するため構成されるネットワークインターフェースを初期化するための装置であって、前記装置は、

前記ネットワークの電力条件に依存せず非依存性クロック信号を出力するクロック源と、

前記非依存性クロック信号と前記ネットワーククロックとの1つを前記ネットワークインターフェースに選択的に供給するために構成されるクロックバイパス回路とを含み、前記クロックバイパス回路は、パワーオンリセット信号に応答して予め定められた間隔にわたって前記非依存性クロック信号を供給し、前記ネットワークインターフェースは、前記パワーオンリセット信号および前記供給されたクロック信号に応答して初期化情報をロードするため構成される、ネットワークインターフェースを初期化するための装置。 10

【請求項5】

前記クロックバイパス回路は、

前記予め定められた間隔にわたって、前記パワーオンリセット信号をアサートされたレベルに保持するためのリセット保持回路と、

前記予め定められた間隔にわたって前記アサートされたレベルの前記パワーオンリセット信号に応答して前記ネットワークインターフェースに前記非依存性クロック信号を供給するためのセレクタとを含む、請求項4に記載のネットワークインターフェースを初期化するための装置。 20

【請求項6】

前記リセット保持回路は、

前記パワーオンリセット信号の検出に応答して前記パワーオンリセット信号をストアするため構成される非同期フリップフロップと、

前記非依存性クロック信号に応答して前記非同期フリップフロップからの前記ストアされたパワーオンリセット信号を連続してストアするための複数の遅延フリップフロップとを含み、選択された1つの前記遅延フリップフロップは、前記パワーオンリセット信号のストアに応答して前記非同期フリップフロップへラッチリセット信号を出力する、請求項5に記載のネットワークインターフェースを初期化するための装置。 30

【請求項7】

前記非同期フリップフロップは、前記ラッチリセット信号に応答して、前記ストアされたパワーオンリセット信号をクリアする、請求項6に記載のネットワークインターフェースを初期化するための装置。

【請求項8】

ホストコンピュータとネットワークとの間でデータを受送信するためのネットワークインターフェースであって、前記ネットワークインターフェースは、

パワーオンリセット信号およびネットワークデータクロックに応答して不揮発性メモリから第1の構成情報をロードするため構成されるレジスタの第1の組と、 40

前記ネットワークに依存しないクロック源信号に応答して前記不揮発性メモリから第2の構成情報をストアするため構成されるレジスタの第2の組と、

前記ネットワークデータクロックの不在にかかわらず、前記第1の構成情報のロードを完了するため前記レジスタの第1の組を可能化するため構成されるバイパス回路とを含む、ネットワークインターフェース。

【請求項9】

前記バイパス回路は、

前記レジスタの第1の組に対し前記パワーオンリセット信号を保持するため構成されるリセット検出回路を含み、前記リセット検出回路は、ネットワーククロック検出信号の受 50

信まで前記パワーオンリセット信号を出力し、前記バイパス回路はさらに、

前記ネットワークデータクロックの検出から予め定められた間隔後に前記ネットワーククロック検出信号を生成するため構成されるネットワーククロック検出回路を含み、前記レジスタの第1の組は、前記リセット検出回路による前記パワーオンリセット信号の出力および前記ネットワークデータクロックの同時アサートの間、前記第1の構成情報をロードする、請求項8に記載のネットワークインターフェース。

【請求項10】

前記ネットワーククロック検出回路は、前記ネットワークデータクロックに応答して前記パワーオンリセット信号を連続してストアするため構成される複数の遅延フリップフロップを含み、選択された1つの前記遅延フリップフロップは、前記パワーオンリセット信号の対応する連続したストアに際して対応する前記ネットワーククロック検出信号を前記リセット検出回路へ出力する、請求項9に記載のネットワークインターフェース。

10

【請求項11】

前記予め定められた間隔は、対応する数のネットワークデータクロックサイクルの検出の後に前記パワーオンリセット信号をストアする前記選択された1つの遅延フリップフロップに基づく、請求項10に記載のネットワークインターフェース。

【請求項12】

前記バイパス回路は、前記パワーオンリセット信号に応答して、予め定められた間隔にわたって、前記レジスタの第1の組に前記非依存性クロック源信号を供給する、請求項8に記載のネットワークインターフェース。

20

【請求項13】

前記バイパス回路は、

前記予め定められた間隔にわたって前記パワーオンリセット信号をアサートされたレベルに保持するためのリセット保持回路と、

前記予め定められた間隔にわたって前記アサートされたレベルの前記パワーオンリセット信号に応答して前記ネットワークインターフェースに前記非依存性クロック信号を供給するためのセレクタとを含む、請求項12に記載のネットワークインターフェース。

【請求項14】

前記リセット保持回路は、

前記パワーオンリセット信号の検出に応答して前記パワーオンリセット信号をストアするため構成される非同期フリップフロップと、

30

前記非依存性クロック信号に応答して前記非同期フリップフロップから前記ストアされたパワーオンリセット信号を連続してストアするための複数の遅延フリップフロップとを含み、前記予め定められた間隔に対応する選択された1つの前記遅延フリップフロップは、前記パワーオンリセット信号のストアに応答して前記非同期フリップフロップへラッチリセット信号を出力する、請求項13に記載のネットワークインターフェース。

【請求項15】

ネットワークデータクロックを受信するため構成されるネットワークインターフェース内に構成情報をロードする方法であって、前記方法は、

ホストコンピュータシステムからのパワーオンリセット信号を検出するステップと、

40

前記パワーオンリセット信号および前記ネットワークデータクロックに応答して前記構成情報をロードするため構成されるネットワークインターフェースレジスタが前記ネットワークデータクロックの不在にかかわらず前記構成情報のロードを完了できるようにするため、予め定められた間隔にわたって前記パワーオンリセット信号を選択的に保持するステップとを含む、ネットワークインターフェース内に構成情報をロードする方法。

【請求項16】

前記選択的に保持するステップは、

前記ネットワークデータクロックの予め定められた数のクロックサイクルを検出するステップと、

前記予め定められた数のサイクルの検出まで前記検出されたパワーオンリセット信号を

50

アサートするステップとを含む、請求項 1\_5 に記載のネットワークインターフェース内に構成情報をロードする方法。

【請求項 1 7】

前記予め定められた数のクロックサイクルを検出するステップは、前記ネットワークデータクロックの不在に続く少なくとも 1 つのクロックサイクルを検出するステップを含む、請求項 1\_6 に記載のネットワークインターフェース内に構成情報をロードする方法。

【請求項 1 8】

前記選択的に保持するステップは、

前記ネットワークデータクロックに依存しない非依存性クロック信号を生成するステップと、

10

前記非依存性クロック信号の予め定められた数のクロックサイクルにわたっての前記パワーオンリセット信号に応答して前記ネットワークインターフェースレジスタに、前記非依存性クロック信号を接続し、かつ前記パワーオンリセット信号を供給するステップと、

前記ネットワークデータクロックを搬送するため構成されるクロック信号経路を、前記予め定められた数のクロックサイクルに続いて前記ネットワークインターフェースレジスタに接続するステップとを含む、請求項 1\_5 に記載のネットワークインターフェース内に構成情報をロードする方法。

【発明の詳細な説明】

【0001】

【発明の分野】

20

この発明は、ネットワークワークステーションにおける電力およびクロック供給管理に関し、より特定的には、異なった電源ドメインからのクロック源を使用してネットワークインターフェースを初期化するためのシステムに関する。

【0002】

【発明の背景】

ワークステーションコンピュータは現在、多数の電源ドメインを有するよう設計されており、たとえば予め定められた非活動間隔の後などにホストコンピュータが待機状態に電源を落としたとしても、ワークステーション内のネットワークインターフェースは動作状態のままである。このような場合、ワークステーション内の内部論理は、外部から供給される電力を異なった電源ドメイン、たとえば、ワークステーションが外部から供給される電力を受取るときは常に選択されたコンポーネントに電力を供給する定電源ドメインと、たとえばユーザが電源ボタンを押すかまたはネットワークインターフェースが遠隔ワークステーションからパワーマネージメントパケットを受取るなどの予め定められた電源条件に応答してコンピュータシステムの残りの部分に電力を供給する主電源とに分割する。

30

【0003】

したがって、ワークステーションは、パケット交換ネットワークへのネットワークインターフェースが定電源に基づいて動作可能であるが一方、ホストコンピュータ（たとえば CPU）は待機モードにあり、システムバスを介してのホストコンピュータとネットワークインターフェースとの間の通信が存在しない状態を有するかもしれない。

【0004】

40

ネットワークインターフェースは、たとえばホストコンピュータからの PCI クロックまたはネットワークからのネットワーククロックなどの供給されたクロックに応答して、不揮発性メモリ内に記憶されている構成情報を初期化時にロードされるのが典型的であろう。従来のシステムでは、初期化の間のネットワークインターフェースの状態は、ホストコンピュータおよびネットワークの両方がネットワークインターフェースの構成を可能にするよう動作できる状態であるとしている。しかし、ホストコンピュータおよび / またはネットワークのそれぞれの電源ドメインから分離された電源ドメインにネットワークインターフェースを分割すると、ネットワークインターフェースの構成レジスタは、ネットワークの送信データクロックまたはネットワークの受信データクロックを使用して予め定められたシーケンスで構成データをロードするよう構成されているため、ネットワークインターフェースが

50

未知の状態になるかもしれない。したがって、必要なときにネットワークインターフェースクロックのいずれかが存在しないと、必要なシーケンスによりネットワークインターフェースを再初期化するためワークステーションおよびネットワークの全システムをリセットしなければ、ネットワークインターフェースが動作不能になるかもしれない。

#### 【0005】

システムをリセットする一般的な技術の1つは、内部構成レジスタのフリップフロップで非同期リセットを使用することである。しかし、非同期リセットを使用すると、この設計の実質的にすべてのフリップフロップをリセットせねばならず、構成レジスタを完全に再ロードすることになるという問題が生じる。さらに、非同期リセットが必要であるとフリップフロップがより大きくなり、より多くのシリコン面積が必要となる。

10

#### 【0006】

##### 【発明の概要】

ネットワークインターフェースの構成レジスタを駆動するためクロックを供給するため関連するネットワークまたはホストワークステーションの電源の立上げを必要とせず、ワークステーション内のネットワークインターフェースの初期化を可能にするシステムが必要である。

#### 【0007】

また、ネットワークインターフェースが外部源からのクロックの受信まで既知の状態におかれる、ネットワークインターフェースの初期化を可能にするシステムが必要である。

#### 【0008】

また、ネットワークインターフェースの動作のために必要な外部から供給されるクロックの存在に依存せず、ネットワークインターフェースの初期化を可能にするシステムが必要である。

20

#### 【0009】

初期化間隔の間の外部データクロックの不在にかかわらず、ネットワークインターフェース内の構成レジスタが構成情報を既知の状態で完全にロードすることを可能にするためバイパス回路が構成される、この発明により、これらのおよび他の必要性が満たされる。

#### 【0010】

この発明の一局面により、ネットワークからネットワーククロックを受信するため構成されるネットワークインターフェースを初期化するため、装置が構成される。この装置は、パワーオン条件の検出に応答してネットワークインターフェースに対しリセット信号を生成するため構成されるリセット検出回路を含み、リセット検出回路は、ネットワーククロック検出信号を受信するまでリセット信号を出力する。この装置はまた、ネットワーククロックの検出から予め定められた間隔後にネットワーククロック検出信号を生成するため構成されるネットワーククロック検出回路を含み、ネットワークインターフェースは、リセット信号およびネットワーククロックに応答して、不揮発性メモリから初期化情報をロードするため構成される。リセット検出回路は、ネットワーククロックの検出から予め定められた間隔後までネットワークインターフェースに対しリセット信号が維持されることを確実にし、ネットワークインターフェースの初期化を完了するためネットワーククロックが利用可能になるまで確実にネットワークインターフェースを既知のリセット状態に維持する。さらに、リセット検出回路は、予め定められた間隔後までリセット信号を維持するので、ネットワークの始めの電源立上げの間断続ネットワーククロック信号はネットワークインターフェースに悪影響を及ぼすことがなく、初期化ルーチンがより強固なものとなる。

30

#### 【0011】

この発明の他局面は、ネットワークからのネットワーククロックを受信するため構成されるネットワークインターフェースを初期化するための装置を提供し、この装置は、ネットワークの電力条件に依存せず非依存性クロック信号を出力するクロック源と、非依存性クロック信号とネットワーククロックとの1つをネットワークインターフェースに選択的に供給するために構成されるクロックバイパス回路とを含み、クロックバイパス回路は、パワーオンリセット信号に応答して予め定められた間隔にわたって非依存性クロック信号を供給

40

50

し、ネットワークインターフェースは、リセット信号および供給されたクロック信号に応答して初期化情報をロードするため構成される。クロックバイパス回路は、ネットワーククロックを供給するネットワークの電力条件に依存せず、ネットワークインターフェースの初期化を可能にする。したがって、ホストコンピュータとネットワークとの間での何らかの前もって調節された初期化なしで、自動的にホストコンピュータを始動させるようネットワークインターフェースを構成することができる。

#### 【0012】

この発明のさらに他の局面は、ホストコンピュータとネットワークとの間でデータを受送信するためのネットワークインターフェースを提供し、このネットワークインターフェースは、パワーオンリセット信号およびネットワークデータクロックに応答して不揮発性メモリから第1の構成情報をロードするため構成されるレジスタの第1の組と、ネットワークに依存しないクロック源信号に応答して不揮発性メモリから第2の構成情報をストアするため構成されるレジスタの第2の組と、ネットワークデータクロックの不在にかかわらず、第1の構成情報のロードを完了するためレジスタの第1の組を可能化するため構成されるバイパス回路とを含む。バイパス回路は、レジスタの第1の組の状態を制御し、初期化手順の間の任意の時点で必要とされるデータクロックが不在であるか否かにかかわらず、対応する第1の構成情報のロードを確実に完了できるようにする。バイパス回路の特定の局面は、必要とされるクロックが利用可能になるまで、レジスタの第1の組を予め定められた状態（たとえばリセット）に保持することである。バイパス回路の他の局面は、パワーオンリセット信号に応答して予め定められた間隔にわたり非依存性クロック源信号を選択的に供給し、必要とされるクロック信号の不在下で、レジスタの第1の組が必要な構成情報をロードすることを可能にする。

#### 【0013】

この発明のさらに他の局面は、ネットワークデータクロックを受信するため構成されるネットワークインターフェース内に構成情報をロードする方法を提供し、この方法は、ホストコンピュータシステムからのパワーオンリセット信号を検出するステップと、予め定められた間隔にわたってパワーオンリセット信号を選択的に保持し、リセット信号およびネットワークデータクロックに応答して構成情報をロードするため構成されるネットワークインターフェースレジスタがネットワークデータクロックの不在にかかわらず構成情報のロードを完了できるようにするステップとを含む。パワーオンリセット信号を選択的に保持することによって、構成手順の少なくとも一部分の間、必要とされる1データクロックが利用不可能である場合に、ネットワークインターフェースレジスタが既知の初期化状態に維持される。選択的保持ステップの一例においては、パワーオンリセット信号は、非依存性クロックに關し予め定められた間隔にわたって選択的に保持され、パワーオンリセット信号および非依存性クロックに応答してのネットワークインターフェースレジスタの構成情報のロードの完了が可能になる。選択的保持ステップの他の例においては、パワーオンリセット信号がサンプリングされ、必要とされる1データクロックから予め定められた数のクロックサイクルが検出されるまで、保持される。

#### 【0014】

この発明のさらなる目的、利点および新規な特徴は、部分的には以下の説明に述べられ、部分的には以下の説明の検討によってまたはこの発明の実施から当業者には明らかになるであろう。この発明の目的および利点は、添付した請求項に特に示した方策および組合せによって達成されるであろう。

#### 【0015】

添付の図面を参照するが、図面中、同じ参照番号を付される要素は図面を通じて同様の要素を表わす。

#### 【0016】

##### 【詳細な説明】

この発明を、イーサネット（IEEE802.3）ネットワークなどのパケット交換ネットワーク内のネットワークインターフェースを例として説明する。始めに、ネットワークイ

10

20

30

40

50

ンタフェースアーキテクチャを説明し、続いて、必要とされるクロックの不在にかかわらず、構成レジスタの構成情報のロードの完了を可能にするバイパス回路を使用したネットワークインタフェースの初期化のためのシステムを説明する。ただし、この発明が他のネットワークインタフェースシステムにも適用可能であることは明らかとなるであろう。

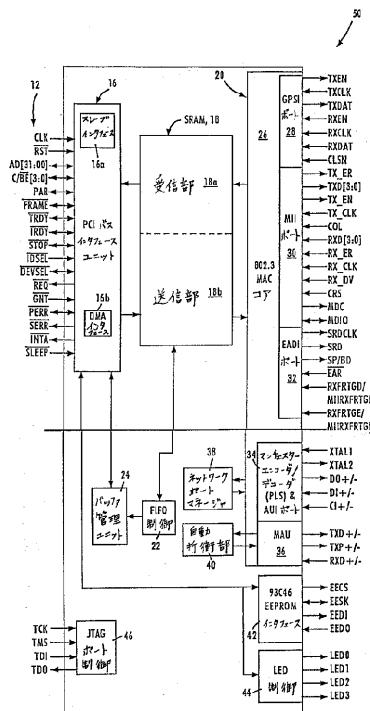

【0017】

図1は、この発明の一実施例により、イーサネット(ANSI/IEEE802.3)ネットワークの媒体にアクセスする例示的なネットワークインタフェース10のブロック図である。

【0018】

好ましくは單一チップの32ビットイーサネットコントローラであるネットワークインタフェース10は、たとえば周辺コンポーネント相互接続(PCB)ローカルバスである、コンピュータのローカルバス12とイーサネットベースの媒体50との間のインターフェースを提供する。

【0019】

インターフェース10は、PCIバスインターフェースユニット16、バッファメモリ部18およびネットワークインターフェース部20を含む。PCIバスインターフェースユニット16は、PCIスレーブインターフェース16aおよびDMAインターフェース16bを含む。スレーブインターフェース16aは、PCI状態レジスタの読み出しおよびプログラミングを含む、PCI制御および状態情報を管理するが、PCIバスを通じてのホストCPUとのスレーブ転送を管理するよう構成されてもよい。DMAインターフェース16bは、ネットワークインターフェース10によるシステムメモリへのおよびシステムメモリからのDMA転送を管理する。したがって、PCIバスインターフェースユニット16を、スレーブおよび/または(DMAなどの)マスタモードでのPCI転送用に選択的に構成することができる。

【0020】

メモリ部18は、ネットワークインターフェースチップ10上に直接実装される16ビットのSRAMを含む。開示される実施例により、このSRAM18は、ファーストインファーストアウト(FIFO)制御ユニット22の制御下でランダムなアクセス様式でアクセスされてもよく、または、それぞれ受信経路および送信経路として受信部18aと送信部18bとに分割されてもよい。

【0021】

ネットワークインターフェース10はまた、DMAインターフェース16bを介してのDMA転送を管理するよう構成されるバッファ管理ユニット24を含む。バッファ管理ユニット24は、開始アドレス、長などを特定するホストメモリ内のDMA記述子に基づいてDMA転送を管理する。バッファ管理ユニット24は、DMAインターフェース16bへ命令を発行することによってシステムメモリから送信バッファ18bへのDMA読み出しを開始し、DMAインターフェースは命令をPCIバスサイクルへ送る。バッファ管理ユニット24は、したがって、DMA転送のための記述子管理および、データの記憶およびメモリ部18からのデータの読み出しに関連するポインタを含む。バッファ管理ユニット24とメモリコントローラ22とは別個の構成要素として図示されているが、この2つのユニットは一体化されて、メモリユニット18へのおよびメモリユニット18からのデータの転送すべてを制御する1つのメモリ管理ユニットを形成してもよい。

【0022】

ネットワークインターフェース20は、メディアアクセスコントロール(MAC)コア26、汎用シリアルインターフェース(GPSI)28、外部の10Mb/sまたは100Mb/sの物理(PHY)トランシーバへの接続のための非媒体依存性インターフェース(MII)30、外部アドレス検出インターフェース(EADI)32、マンチェスタエンコーダおよびデコーダを有する接続ユニットインターフェース(AUI)34および10/100Mb/s撲線対トランシーバメディア接続ユニット(MAU)36を含む。

【0023】

10

20

30

40

50

ネットワークインターフェース 10 はまた、MII ポート 30 を介しての MII バス上での 2 つの装置間の MII ハンドシェイクを実行するよう構成されるネットワークポートマネージャ 38 を含む。このような MII ハンドシェイクは、リンク情報、管理データクロック (MDC) を用いた MII 層でのプログラム情報、および管理データ入力 / 出力 (MDIO) 経路を含んでもよい。

【0024】

自動折衝部 40 は、PHY 層上でリンクパートナーとの IEEE に準拠した折衝を実行し、リンクパートナーが 10 Mb / s、100 Mb / s で動作可能であるか否かおよび、リンクが半二重または全二重であるべきか否かを示すデータを交換する。

【0025】

LED コントローラ 44 は、内部デコード論理およびネットワークインターフェース状態レジスタ (図示せず) に基づき、LED 出力信号の発生を選択的に制御する。ネットワークインターフェース 10 はまた、IEEE 1149.1 - 準拠 JTAG 境界走査テストアクセスポートインターフェース 46 を含む。

【0026】

E PROM インタフェース 42 は、シリアルインターフェースリンクを通じてホストコンピュータのマザーボードまたはネットワークインターフェースアダプタカードのいずれかにおいて EEPROM に接続する。(図 1 には図示しない) EEPROM は、ネットワークインターフェースに関連する構成情報をプログラムされ、初期化の間の EEPROM インタフェース 42 を通じてのネットワークインターフェースの構成を可能にする。一旦初期化されると、ネットワークインターフェースは内部レジスタ (図示せず) 内に構成情報を記憶し、ホストコンピュータの電源が落とされた場合でも、ネットワークインターフェースはホストコンピュータには依存せず動作できる。したがって、ホストコンピュータが待機モードにある間、ネットワークインターフェースが動作するよう構成することができ、ネットワークインターフェースが、ホストコンピュータ内の論理に電源立上げ情報を出力し、ネットワークから受信され以下に説明するような特定のプロトコルを有するデータパケットに応答してホストコンピュータが自動的にオンすることができる。

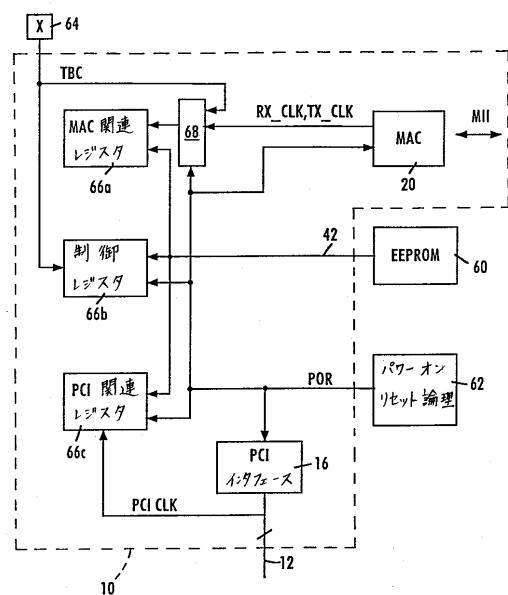

【0027】

図 2 は、この発明の一実施例によるネットワークインターフェース構成レジスタを示すネットワークインターフェースのブロック図である。図 2 に図示するように、EEPROM インタフェース 42 を通じてネットワークインターフェース 10 へ構成情報を供給するため構成されるシリアル EEPROM 60 からネットワークインターフェース 10 は構成情報を受信する。開示される実施例により、たとえば、ワクステーションを 120 ボルトの AC 電源にプラグで接続した際など、外部電源からの電力の受取りに際して電力を供給する定電源により、外部 EEPROM 60 およびネットワークインターフェース 10 は両方とも電力を与えられる。120 ボルト電源を検出すると、マザーボードまたは別個の電源ボード上のワクステーション内に位置づけられてもよい、パワーオンリセット論理 62 によりパワーオンリセット信号 (POR) が出力される。

【0028】

開示される実施例により、ネットワークインターフェースデバイス 10 は電源立上げに際して初期化を行ない、ネットワークメディア 50 上の (たとえば MII インタフェースからの TX\_CLK および RX\_CLK などの) ネットワーククロックおよび PCI バス 12 の速度にかかわらず、ネットワークメディア 50 の起動トラヒックのモニタを開始せねばならない。開示される実施例により、ホストコンピュータまたはネットワークの電源ドメインに依存せず (公称) 20 MHz のクロック信号を出力する、内部で生成されるかまたは外部から供給される継続的に作動するクロック源 64 を使用して、初期化データが EEPROM 60 から読み出される。したがって、ネットワークインターフェース 10 は非依存性クロック源 64 からの非依存性クロックを使用して、ネットワークの起動トラヒックのモニタを開始するため構成レジスタを選択的にロードできる。非依存性クロック源 64 はネットワークインターフェース 10 と同じ定電源で駆動されてもよく、または代替的に、たと

10

20

30

40

50

えばバッテリなどの別個の電源で駆動されてもよい。

【0029】

ネットワークインターフェース10は、パワーオンリセット論理62からのパワーオンリセット信号およびそれぞれのクロック信号に応答して、EEPROM60からの構成情報をストアするための構成レジスタ66を含む。特定的には、ネットワークインターフェース10は、たとえば、MAC20のMIIポート30からの受信クロック(RX\_CLK)または送信クロック(TX\_CLK)などのMACベースのクロック信号に応答して、データをストアおよび出力するため構成されるMAC関連構成レジスタ66aを含む。MAC関連レジスタ66aは、たとえば、ネットワークメディア50へおよび50から送信されるデータに関しての同期を目的として、ネットワーククロックに応答するよう構成されて10もよい。

【0030】

制御レジスタの第2の組66cは、PCIバスインターフェースユニット16の動作に関連する制御、構成および状態情報をストアするため、PCIバス12からのPCIクロックに同期される。制御レジスタの第3の組66bは、ネットワーククロックまたはPCIバスクロックのいずれにも同期させる必要のない制御および構成情報をストアするため構成され、したがって、非依存性クロック源64からの非依存性クロック信号に結合される。

【0031】

EEPROM60は、もしそれぞれのクロックが作動していれば、MAC制御レジスタ66aおよびPCI制御レジスタ66cに情報をロードするのみであろう。しかし、PCIバス12は、ホストシステムの起動に際しリセットを発生し、この時点の間、バスに関連するレジスタ66cはEEPROMによりロードされるであろう。先に説明したように、MAC関連レジスタ66aは、(たとえばTX\_CLK、RX\_CLKなどの)ネットワーククロックの1つに応答するが、これらのネットワーククロックは、もしMAC20に関連するPHYトランシーバまたは行先PHYトランシーバが動作不能であり、検出されるネットワーククロックが存在しない場合には存在しないであろう。このような場合は、MAC関連レジスタ66aは従来、ネットワークが活性になるまでは起動動作を行なうための利用可能なクロックを持たないことになり、ネットワークインターフェース10の初期状態に影響が与えられ兼ねない。したがって、ワークステーションネットワークインターフェース10内に付加的なリセットを設け、ネットワークがシステムを既知の状態に再同期する必要があるだろう。

【0032】

開示される実施例により、ネットワークインターフェース10は、ネットワークデータクロックの不在にかかわらず、MAC関連レジスタ66aのEEPROM60からの構成情報のロードの完了を可能にするため構成されるバイパス回路68を含む。以下に詳細に説明するように、バイパス回路68は、クロック信号が失われているにもかかわらず、MAC関連レジスタ66aが構成情報のロードを完了することを可能にする。第1の実施例において、バイパス回路68は予め定められた検出されたクロックサイクルの最低数にわたってクロック信号の不在が検出されるまではパワーオンリセット信号を保持する。第2の実施例においては、バイパス回路68はリセット信号の検出に続いて特定数の非依存性クロックサイクルにわたり非依存性クロック源と不在のクロック信号とを置換え、続いて、必要とされるクロック信号を供給する信号経路に再び切換える。

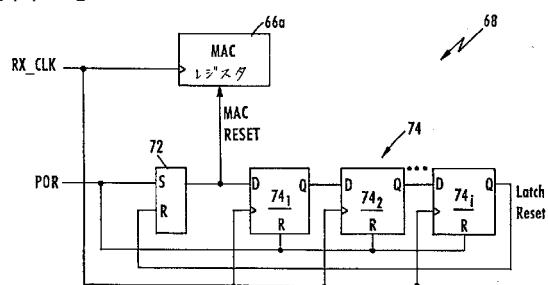

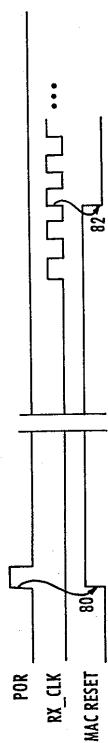

【0033】

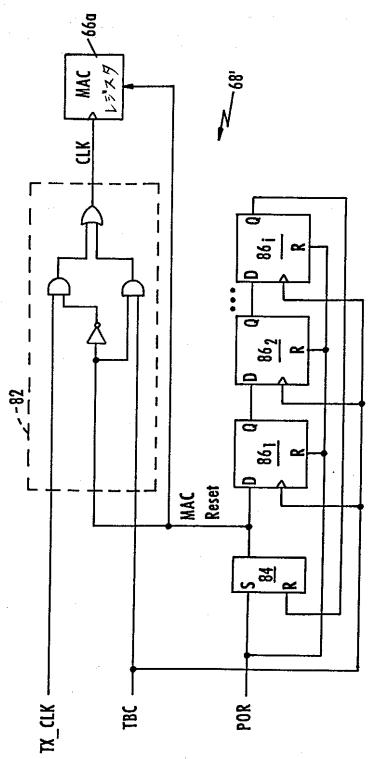

図3および図4は、この発明の第1の実施例により、必要とされるクロック信号が検出されるまで予め定められた間隔にわたりパワーオンリセット信号を保持するシステムを図示するブロック図およびタイミング図である。

【0034】

図3のパワーオンリセット回路68は、パワーオン条件を示すパワーオンリセット(POR)信号の検出に応答して、MAC関連レジスタ66aに対しMACリセット信号を生成するため構成されるリセット検出回路72を含む。リセット検出回路72は、図4の状態

10

20

30

40

50

80にパワーオンリセット信号を非同期にラッチするSRフリップフロップとして構成される。バイパス回路68はまた、予め定められた数のネットワーククロック信号の後に、SRフリップフロップ72のR入力へのラッチリセット信号としてネットワーククロック検出信号を生成するため構成されるネットワーククロック検出回路74を含む。ネットワーククロック検出回路74は、パワーオンリセット信号のアサートに応答してリセットされる複数の遅延フリップフロップ74<sub>1</sub>を含む。

【0035】

SRフリップフロップ72により出力されたMACリセット信号は、第1の遅延フリップフロップ74<sub>1</sub>へ入力として供給される。遅延フリップフロップ74<sub>1</sub>は各々、関連する入力をラッチするため、メディアアクセスコントローラ20から(たとえばRX\_CLKなどの)ネットワーククロック信号も受信する。当業界では認識されているように、ネットワーククロックは、ネットワークの電源が立上げられ作動しているときのみ、たとえばMI-Iインターフェースを通じて、外部物理層トランシーバ(PHY)から供給されるであろう。したがって、パワーオンリセット信号は、SRフリップフロップ72によりラッチされ、状態82において予め定められた数の受信クロック(RX\_CLK)のサイクルが検出されるまで、図4に図示するようにアサートされた状態80に保持される。したがって、リセット検出回路72はMACリセット信号をアサートし、予め定められた数のネットワーククロックサイクルが検出されるまで、MAC関連レジスタ66aを既知のリセット状態に維持し、MACリセット信号がSRフリップフロップ72内でクリアされた後、確実にMACインターフェースレジスタ66aがリセットされるようにする。

【0036】

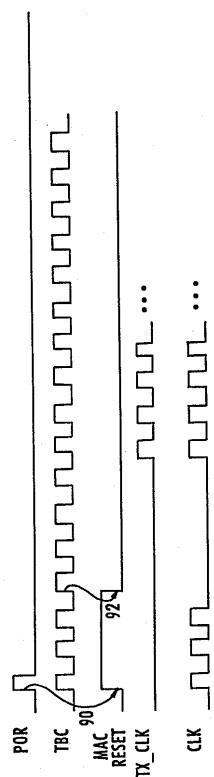

図5および図6は、クロックの不在にかかわらず、MAC関連レジスタ66aの、EEPROM60からの構成情報のロードの完了を可能にするための代替的システムを図示する。図5に図示するように、バイパス回路68は、予め定められた間隔にわたってパワーオンリセット信号をアサートされたレベルに保持するため構成されるリセット保持回路80と、非依存性クロック信号または送信クロック信号のいずれかを(たとえばMAC関連レジスタ66aなどの)ネットワークインターフェースへ選択的に供給するためのセレクタ回路82とを含む。特定的には、リセット保持回路80は、図3のSRフリップフロップ72に類似した、パワーオンリセット(POR)信号をラッチするための非同期SRフリップフロップ84を含む。リセット保持回路80はまた、非依存性クロック源64からの非依存性クロック信号に応答して、SRフリップフロップ84からのストアされたパワーオンリセット信号を連続してストアするための複数の遅延フリップフロップ86<sub>1</sub>を含む。また、遅延フリップフロップ86は各々、パワーオンリセット信号に応答してリセットされる。

【0037】

図5および図6に図示するように、SRフリップフロップ84は、イベント90においてパワーオンリセット信号の検出に応答しMACリセット信号を出力する。SRフリップフロップ84は、イベント92において遅延フリップフロップ86<sub>1</sub>の数に対応する予め定められた数の非依存性クロックサイクルまで、MACリセット信号をアサートし続ける。したがって、MACリセット信号は、予め定められた数の非依存性クロックサイクルにわたってアサートされ、この時間の間、セレクタ82は、MAC関連レジスタ66aへ供給されるクロック信号として非依存性の時間ベースのクロック信号(TBC)を選択する。そして、MAC関連レジスタは、非依存性クロック源を使用してEEPROM60からの構成情報をロードされる。リセット状態の後、セレクタ82は元に切換えを行ない、MI-Iポート30からの送信クロック(TX\_CLK)を搬送するクロック信号経路をMAC関連レジスタ66aに接続し、したがって、MAC関連レジスタ66に供給されるクロック信号(CLK)は非依存性クロック信号と利用可能な送信クロックとの両方を組合せる。したがって、図5のバイパス回路68は送信クロック信号が初めは不在であるのにかかわらず、MAC関連レジスタ66aのロードを可能にし、続いて、送信クロック信号経路への接続により、MAC関連レジスタ66aとネットワークメディアとの間の同期が可

10

20

30

40

50

能になる。

【0038】

この発明を、現在最も実際的で好ましい実施例と考えられるものに関連して説明してきたが、この発明が開示された実施例に限定されるのではなく、添付した請求項の精神および範囲内に含まれるさまざまな修正および均等物をカバーするものと意図されることが理解されねばならない。

【図面の簡単な説明】

【図1】この発明の一実施例により、ネットワークデータクロックに依存しない初期化のため使用されてもよい、例示的ネットワークインターフェースを図示するブロック図である。

10

【図2】この発明の一実施例により、それぞれの電源ドメインの異なったクロック源に応答するネットワークインターフェース構成レジスタを図示するブロック図である。

【図3】この発明の第1の実施例による図2のバイパス回路を説明するブロック図である。

【図4】この発明の第1の実施例による図2のバイパス回路を説明するタイミング図である。

【図5】この発明の第2の実施例による図2のバイパス回路を説明するブロック図である。

【図6】この発明の第2の実施例による図2のバイパス回路を説明するタイミング図である。

20

【符号の説明】

10 ネットワークインターフェース

12 PCIバス

16 PCIバスインターフェースユニット

20 MAC

60 シリアルEEPROM

62 パワーオンリセット論理

64 クロック源

66 構成レジスタ

68 バイパス回路

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(74)代理人 100091409

弁理士 伊藤 英彦

(74)代理人 100096781

弁理士 堀井 豊

(72)発明者 ジェフリー・ロイ・ドゥウォーク

アメリカ合衆国、95124 カリフォルニア州、サン・ノゼ、トゥポロ・ドライブ、1682

(72)発明者 チン・ユ

アメリカ合衆国、95051 カリフォルニア州、サンタ・クララ、ガラ・コート、2952

(72)発明者 ロバート・ウイリアムズ

アメリカ合衆国、95014 カリフォルニア州、クペルティーノ、キャニオン・ビュウ・サークル、22255

(72)発明者 ラジャット・ロイ

アメリカ合衆国、95014 カリフォルニア州、サニイ・ベイル、イートン・ウェイ、927

審査官 杉藤 泰子

(56)参考文献 特開平07-261878(JP, A)

特開平04-156156(JP, A)

特開平02-159613(JP, A)

特開昭61-138356(JP, A)

特開平06-251169(JP, A)

(58)調査した分野(Int.Cl., DB名)

G06F 1/24

G06F 13/00

H04L 29/10

G06F 1/12