United States Patent [19]

Greatbatch

[11] 3,870,050

[45] Mar. 11, 1975

[54] DEMAND PACER

[76] Inventor: Wilson Greatbatch, 5220

Donnington Rd., Clarence, N.Y.

14031

[22] Filed: Nov. 7, 1973

[21] Appl. No.: 413,451

[52] U.S. Cl. 128/419 PG, 128/422

[51] Int. Cl. A61n 1/36

[58] Field of Search 128/419 P, 419 R, 421,

128/422, 423

[56] References Cited

UNITED STATES PATENTS

3,431,912 3/1969 Keller, Jr. 128/419 P

3,460,542 8/1969 Gemmer 128/419 P

3,528,428 9/1970 Berkovits 128/419 P

3,557,796 1/1971 Keller, Jr. et al. 128/419 P

3,618,615 11/1971 Greatbatch 128/419 P

3,703,900 11/1972 Holznagel 128/419 P

Primary Examiner—William E. Kamm

Attorney, Agent, or Firm—Christel & Bean

[57] ABSTRACT

An artificial cardiac pacer which in the absence of natural cardiac electrical activity provides stimulating electrical pulses to the heart at a fixed rate. The stimulating pulses preferably are obtained from a digital clock integrated circuit including a stable frequency source such as a quartz crystal and a binary frequency divider to yield the desired pulse rate. In response to a natural heart signal, a circuit in the pacer inhibits any stimulating pulse that occurs at that instant of time, and for a predetermined interval of time thereafter to provide an adequate safety margin.

10 Claims, 2 Drawing Figures

PATENTED MAR 11 1975

3,870,050

Fig. 1.

Fig. 2.

## DEMAND PACER

## BACKGROUND OF THE INVENTION

This invention relates to the electronic cardiac pacer art, and more particularly to a new and improved electronic cardiac pacer of the demand type.

Early in the development of electronic cardiac pacemaking there appeared the nonsynchronous pacer which provides fixed-rate stimulation, and although the stimulation is not automatically changed in accordance with the body's needs, it has proven effective in alleviating the symptoms of complete heart block. A nonsynchronous pacer, however, has the possible disadvantage of competing with the natural, physiological pacer during episodes of normal sinus conduction.

As a result, the demand-type pacer was developed having the capability that artificial stimuli are initiated only when required and subsequently can be eliminated when the heart returns to the sinus rhythm. The demand pacer solves the problem encountered with the nonsynchronous pacer by inhibiting itself in the presence of ventricular activity but coming "on line" and filling in missed heart beats in the absence of ventricular activity.

Demand pacer circuits heretofore available include free-running multivibrators and sense the occurrence of a natural heart beat and re-time the next pacer impulse to some fixed time following that beat. This, in turn, requires timing capacitors and high megohm resistors which are bulky and can be unreliable. In addition, such arrangements cannot use recently developed digital clock circuitry. Furthermore, with demand pacers heretofore available the stimulation impulses are synchronized with the natural heart rhythm, and the heart will establish a new stimulation time base each time an irregular cardiac event occurs.

## SUMMARY OF THE INVENTION

It is, therefore, an object of this invention to provide a new and improved artificial cardiac pacer of the demand type.

It is a further object of this invention to provide such an artificial pacer wherein pulse generation is locked in timing relation to a source of timing signals which operates at a constant frequency.

It is a further object of this invention to provide such an artificial pacer which encourages the natural heart rate to conform to a precise repetitive signal.

It is a further object of this invention to provide such an artificial cardiac pacer wherein the timing element includes digital clock circuitry of the integrated circuit type.

The present invention provides an artificial cardiac pacer which in the absence of natural cardiac electrical activity provides stimulating electrical pulses to the heart at a fixed rate. The stimulating pulses preferably are obtained from a digital clock circuit including a stable frequency source such as a quartz crystal and a binary frequency divider to yield the desired pulse rate. In response to a natural heart signal the pacer inhibits any stimulating pulse that occurs at that instant of time, and for a predetermined interval of time thereafter to provide an adequate safety margin. As a result, the pacer provides a train of stimulating pulses to the heart which are precisely timed at a fixed frequency and

wherein those pulses which would conflict with a natural heart beat are completely missing from the train.

The foregoing and additional advantages and characterizing features of the present invention will become clearly apparent from a reading of the ensuing detailed description thereof together with the included drawing wherein:

## BRIEF DESCRIPTION OF THE DRAWING FIGURES

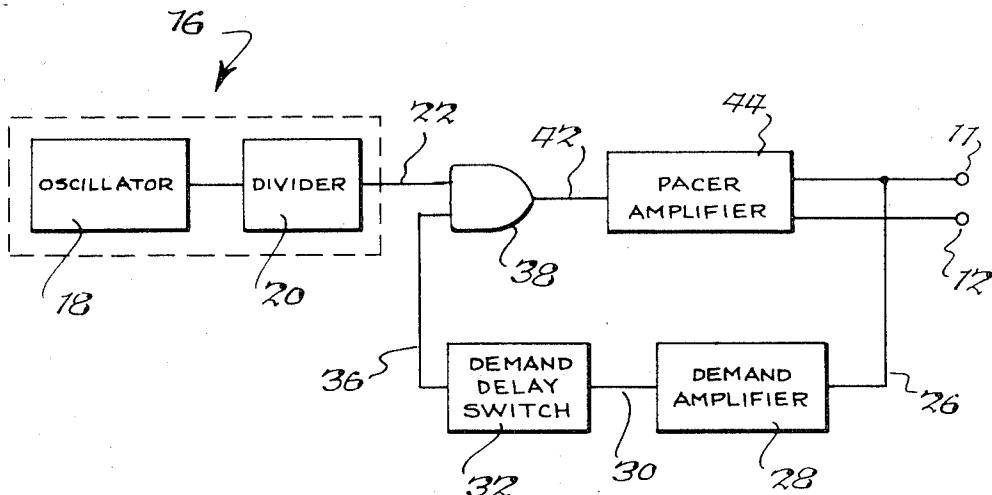

FIG. 1 is a block diagram of a cardiac pacer according to the present invention; and

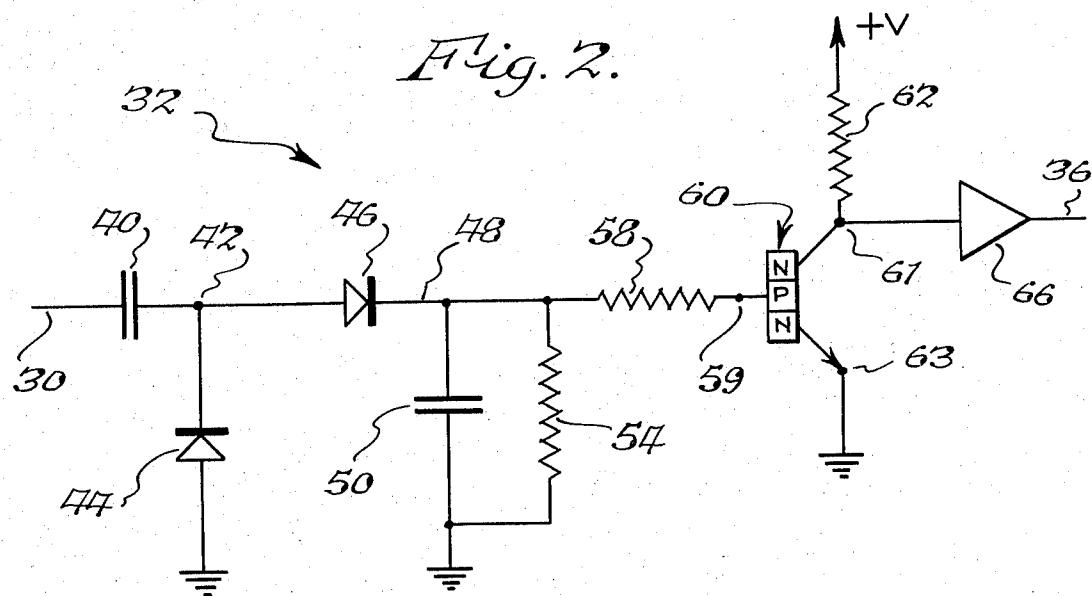

FIG. 2 is a schematic circuit diagram of a portion of the cardiac pacer of FIG. 1.

## DETAILED DESCRIPTION OF THE ILLUSTRATED EMBODIMENT

FIG. 1 shows a cardiac pacer according to the present invention which includes electrode means adapted to be operatively connected to a patient's heart and comprising a pair of electrodes 11, 12 at least one of which is surgically placed in contact with the heart of a patient. In particular, electrode 11 would be placed surgically in contact with the ventricle of the patient's heart and electrode 12 which can function as an indifferent or reference electrode, could be subcutaneously implanted at another part of the patient's body. Alternatively, electrode 12 also can be placed in contact with the patient's heart. Electrodes 11 and 12 are connected to the circuitry of the cardiac pacer by leads or wires which are enveloped by a moisture-proof and human body reaction-free material such as silicone rubber or suitable plastic.

The cardiac pacer of the present invention further comprises a source of electrical pulses having a constant frequency. The source, generally designated 16 in FIG. 1, is a stable frequency source and includes a pulse source 18 such as an oscillator which provides output pulses at a relatively high frequency, together with a divider 20, the input of which is connected to the output of oscillator 18. Divider 20 is in the form of a binary electronic frequency divider which divides frequency of the pulses sequentially down to a relatively lower frequency corresponding to the desired fixed stimulation rate for the heart. Electrical energy for operating oscillator 18 and divider 20 is obtained from a suitable source such as a battery in a known manner. By way of example, oscillator 18 can comprise a crystal oscillator providing output pulses at a frequency of 19,661 hertz and commercially available from the Radio Corporation of America under the product designation RCA TA5987. Divider 20 likewise can comprise a 14 stage binary divider available from the Radio Corporation of America under the commercial designation RCA CD4020A. The output of this particular oscillator-divider combination is a train of pulses having a frequency of 72 pulses per minute. The output frequency can of course be made higher or lower than this example by substituting a different oscillator. For example, a quartz crystal oscillator operating at a frequency of 16,384 hertz in combination with a 14 stage binary divider will yield an output pulse rate of 1 hertz or 60 beats per minute. This train of pulses is present on a line 22 for a connection to another portion of the pacer circuit in a manner which will be described.

The cardiac pacer of the present invention further comprises control means connected to the pacer out-

put electrode means and to the source of pulses for connecting the source to the electrode means in the absence of a natural heartbeat and for temporarily disconnecting the source from the electrode in response to the occurrence of a natural heartbeat. Electrode 11 is connected by a line 26 to the input of an amplifier 28 which is similar in construction and operation to the demand amplifier present in demand cardiac pacer circuits. Because demand amplifiers are well known to those skilled in the art, a detailed description of amplifier 28 is believed unnecessary. Further information and detailed descriptions of demand amplifiers included in cardiac pacers can be found in any of the following U.S. Pat. Nos. 3,478,746 issued Nov. 18, 1969; 3,618,615 issued Nov. 9, 1971 and 3,648,707 issued Mar. 14, 1972. A heartbeat electrical signal sensed or picked up by electrode 11 is applied by line 26 to the input of amplifier 28 which amplifies the heartbeat signal to an amplitude suitable for use in the subsequent circuitry. The output of amplifier 28 is connected by a line 30 to the input of a demand delay switch generally designated 32 in FIG. 1. Switch 32 functions, briefly, to provide a logical one output signal when no heart signal is present in this circuit branch, and it functions to provide a logical zero output signal for a predetermined time, such as about 0.3 seconds, when a heart signal is present in the branch. The construction and operation of demand delay switch 32 will be described in detail presently. The logical signals are applied from the output of switch 32 by line 36 to one input of an AND gate 38. The other input of AND gate 38 is connected to line 22 from pulse generator 16. Thus the pulses present on line 22 are transmitted or passed through gate 38 when a logical one signal is present on line 36, and the pulses on line 22 are inhibited by gate 38 as long as a logical zero signal is present on line 36. The output of gate 38 is connected by a line 42 to the input of an amplifier 44, the output of which is connected to electrode 11. Amplifier 44 like amplifier 28 is of the type commonly found in cardiac pacer circuits for amplifying the stimulating pulses transmitted to the pacer electrode and would be provided with suitable bias voltage from a source (not shown). Because amplifier 44 is of the type well-known to those skilled in the art, a detailed description thereof is believed to be unnecessary. Electrode 12 is connected to the ground or reference portion of the amplifier circuit which is referenced electrically to the remainder of the cardiac pacer circuit in a known manner.

FIG. 2 is a schematic circuit diagram of a preferred form of the demand delay switch 32 of the cardiac pacer of FIG. 1. Demand delay switch 32 comprises an input or coupling capacitor 40, one terminal of which is connected to line 30 leading from amplifier 28 and the other terminal of which is connected to a circuit junction terminal 42. The circuit 32 further comprises a full-wave rectifier in the form of a first rectifier diode 44, the cathode of which is connected to terminal 42 and the anode of which is connected to the circuit reference or ground potential. The rectifier also includes a second rectifier diode 46, the anode of which is connected to circuit terminal 42 and the cathode of which is connected to a lead 48.

The demand delay switch 32 further comprises a timing means in the form of an RC circuit connected between line 48 and the circuit ground or reference point. In particular, a timing capacitor 50 and a timing resis-

tor 52 are connected in parallel and between line 48 and the ground or reference terminal. Line 48 also is connected to one terminal of a resistor 58, the other terminal of which is connected to the base terminal 59 of an NPN silicon transistor 60. The collector terminal 61 of transistor 60 is connected to one terminal of an output resistor 62, the other terminal of which is connected to a source of positive bias voltage for transistor 60, preferably having a magnitude of about 6 volts. The emitter terminal 63 of transistor 60 is connected to the circuit ground or reference potential point. Collector terminal 61 also is connected to the input of an inverter schematically designated 66, the output of which is connected to line 36 in the cardiac pacer of FIG. 1 leading to one input of AND gate 38.

The cardiac pacer of FIG. 1 operates in the following manner. Pulse generating means 16 produces a train of output pulses on line 22 having a constant frequency or repetition rate of a value or magnitude which is desired for heart stimulation, preferably at or near one hertz or 60 pulses or beats per minute. This is accomplished by the combination of oscillator 18 and divider 20 wherein oscillator 18 provides output pulses at an extremely high frequency or repetition rate and divider 20 sequentially divides the pulses to yield the desired lower rate. The quartz crystal oscillator 18 oscillates at a very precise frequency, for example 19,661 hertz according to the foregoing example. This signal is then divided sequentially in 14 successive digital binary dividers included within divider 20 (i.e. first to 9831 then to 4915 and 12 more times until the output is 72 pulses per minute). It is to be understood that the foregoing quantities are merely exemplary, and oscillator 18 can operate at different frequencies thereby providing a different pulse frequency or repetition rate on line 22.

In the absence of a natural heartbeat, the pulses present on line 22 are transmitted or gated through the AND gate 38 and amplified in amplifier 44 whereupon stimulating pulses are applied to the heart through electrode 11. On the other hand, when a natural heartbeat occurs, it is sensed by electrode 11 causing operation of the circuit branch including demand delay switch 32 to inhibit stimulating pulses for a predetermined period of time. That period of time would be about 0.30 seconds so as to prevent the application of a stimulating impulse to the heart during the T wave of a natural heartbeat. In particular, the natural heartbeat sensed by electrodes 11 is applied through line 26 to amplifier 28 wherein it is amplified and applied to the input of demand delay switch 32. Switch 32, in turn, functions to apply a logical zero input through line 36 to AND gate 38 in response to the occurrence of the natural heartbeat signal and for the aforementioned predetermined time period. The logical zero input to gate 38 of course causes gate 38 to block passage or transmission of pulses on line 22 to amplifier 44 and electrode 11. After the predetermined time delay and in the absence of a natural heartbeat sensed by electrode 11, switch 32 applies a logical one input through line 36 to AND gate 38 thereby causing the gate to allow passage or transmission of pulses from line 22 to amplifier 44 and electrode 11.

Referring now to FIG. 2 the detailed operation of demand delay switch 32 is as follows. When a natural heartbeat does not occur, there is no signal on line 30 and transistor 60 in the circuit of FIG. 2 is off or non-conducting. Therefore, the voltage at the collector ter-

terminal 61 is high corresponding to a logical zero level. This, in turn, is converted by inverter 66 to a logical one signal level which is applied through line 36 to an input of AND gate 38. When the natural heartbeat occurs, the corresponding signal is present on line 30 and is rectified by the combination of diodes 44, 46 and applied through line 48 and resistor 58 to base terminal 59 of transistor 60. The signal level is sufficient to turn transistor 60 on thereby allowing current to flow through the collector-emitter path thereof with the result that the voltage at collector terminal 61 falls relatively instantaneously to a low voltage level. This corresponds to a logical one level and is converted by inverter 66 to a logical zero voltage level which then is applied through line 36 to the input of AND gate 38. Capacitor 50 and resistor 54 comprise an RC time delay circuit which serves to hold the signal level above the base-emitter threshold level of transistor 60 for the predetermined time during which it is desired to maintain a logical zero voltage level on line 36. In particular, transistor 60 is of the silicon type having a base-emitter voltage drop of about 0.5 volts, and the magnitudes of capacitor 50 and resistor 54 together with magnitude of base resistor 58 are selected so that transistor 60 remains on or conducting for a predetermined time period, for example about 0.3 seconds after the occurrence of a heart signal. The voltage waveform present on base terminal 59 has a relatively straight, vertical leading edge and a gradual decay which maintains the waveform amplitude above the 0.5 volt threshold level for the predetermined time period as set by the values of capacitor 50 and resistor 54. The provision of the full-wave rectifier comprising diodes 44, 46 connected as shown in FIG. 2 insures that both negative-going and positive-going heart signals will activate the demand delay switch 32.

The cardiac pacer of the present invention is a demand-type pacer providing stimulating impulses which are locked or fixed in timing relationship to a fixed oscillator rate and are not in time step with the natural heart rhythm. In particular, the pacer pulse interval is precisely locked to a stable frequency source, such as the quartz crystal oscillator 18, which oscillates to provide signals or pulses at a relatively high frequency which then is divided sequentially a number of times in a binary digital electronic divider 20 to yield the desired heart stimulation rate which is at or near one hertz or 60 beats per minute. The cardiac pacer of the present invention utilizes the amplified natural heart signal to inhibit any pacer impulse that occurs between that instant and a time about 0.3 seconds later so as to avoid firing into the T wave of a natural heartbeat. Therefore, the pacer impulse train is a string of precisely time impulses at the frequency of the oscillator-frequency divider combination such as one hertz but with some impulses completely missing if those impulses would conflict in time with a natural heartbeat. In other words, the cardiac pacer of the present invention inhibits the train of pulses in time-step with the natural rhythm of the heart as compared to conventional demand-type pacemakers which deliver a stimulating impulse in time-step with the natural rhythm of the heart.

The cardiac pacer of the present invention advantageously utilizes integrated circuit components which are at a high level of sophisticated development. In particular, the oscillator 18 and frequency divider 20 are

provided on integrated circuit chips and therefore provide all the advantages associated therewith. The utilization of such a timer in a cardiac pacer permits elimination of the bulky timing capacitors and high megohm resistors which can be unreliable and are not amendable to integrated circuitry. These capacitors and resistors can be eliminated because the timing element in the digital clock or stable frequency source 16 is a quartz crystal chip which operates at a relatively high frequency, i.e. around 19,000 hertz, rather than bulky RC components which operate at 1 hertz.

Furthermore, there is believed to be a medical advantage in encouraging the heart to conform to a precise repetitive signal rather than allowing the heart to reestablish a new time base each time an untoward event like an extrasystole occurs. Thus there is believed to be an advantage in using a cardiac pacer impulse not in time-step with the natural rhythm of the heart. In other words, the cardiac pacer of the present invention inhibits an existing pacer impulse if it conflicts with a natural heart stimulus but does not disturb the periodicity of the basic rhythm of the oscillator.

It is therefore apparent that the present invention accomplishes its intended objects. While a single embodiment of the present invention has been described in detail, this is for the purpose of illustration, not limitation.

I claim:

1. A cardiac pacer comprising:

- a. electrode means adapted to be operatively connected to a patient's heart;

- b. a source providing an output train of electrical pulses having a constant frequency and comprising oscillator means providing output pulses at a relatively high frequency and means for converting said high frequency pulses to pulses having a relatively lower frequency suitable for heart stimulation; and

- c. means for coupling said train of pulses from said source to said electrode means in a manner such that stimulating pulses are fixed in timing relationship to said source, said coupling means including means for preventing application to the heart those pulses in said train which occur at a time during a predetermined interval in response to the occurrence of a natural heart signal.

2. A cardiac pacer according to claim 1, wherein said oscillator means comprises a quartz crystal oscillator and said converting means comprises a binary frequency divider connected to the output of said oscillator.

3. A cardiac pacer according to claim 1, wherein said means for preventing application of pulses to the heart during a predetermined interval in response to a natural heartbeat includes means for connecting said converting means to said electrode means in the absence of a natural heart signal and for temporarily disconnecting said converting means from said electrode means in response to the occurrence of a natural heart signal.

4. A cardiac pacer according to claim 1, wherein said coupling means comprises:

- a. AND gate means having a pair of inputs and an output;

- b. means for coupling the output of said AND gate means to said electrode means;

- c. means for connecting said converting means to one input of said AND gate means; and

d. means coupled to said electrode means and connected to the other input of said AND gate means for applying a logical one signal to said AND gate input in the absence of a natural heart signal and for applying a logical zero signal to said AND gate input for a predetermined time in response to the occurrence of a natural heart signal.

5 5. A cardiac pacer according to claim 4, wherein said means coupled to said electrode means and connected to the other input of said AND gate means includes means responsive to both positive-going and negative-going heart signals.

10 6. A cardiac pacer according to claim 4, wherein said means coupled to said electrode means and connected to the other input of said AND gate means includes time delay means for maintaining the logical zero signal for said predetermined time.

15 7. A cardiac pacer comprising:

- a. electrode means adapted to be operatively connected to a patient's heart;

- b. a source of electrical pulses having a constant frequency; and

- c. control means connected to said electrode means and to said source for connecting said source to 25

5 heart signal and for temporarily disconnecting said source from said electrode means in response to the occurrence of a natural heart signal and thereafter reconnecting said source to said electrode means, said control means maintaining the periodicity of said source such that the pulse interval of stimulating pulses provided by said pacer is fixed to the constant frequency of said source.

10 8. A cardiac pacer according to claim 7 wherein said control means includes timing means for maintaining said source disconnected from said electrode means a predetermined time after the occurrence of said natural heart signal.

15 9. A cardiac pacer according to claim 7, wherein said source of electrical pulses comprises oscillator means providing output pulses at a fixed and relatively high frequency and means for converting said high frequency pulses to pulses having a relatively lower rate suitable for heart stimulation.

20 10. A cardiac pacer according to claim 7, wherein said source of electrical pulses comprises a quartz crystal oscillator and a binary frequency divider connected to the output of said oscillator.

\* \* \* \* \*

30

35

40

45

50

55

60

65