(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-268814

(P2005-268814A)

(43) 公開日 平成17年9月29日(2005.9.29)

(51) Int.Cl.<sup>7</sup>

H01L 27/146

F 1

H01L 27/14

テーマコード(参考)

A

4M118

審査請求 有 請求項の数 5 O L (全 20 頁)

|              |                                                                  |

|--------------|------------------------------------------------------------------|

| (21) 出願番号    | 特願2005-119658 (P2005-119658)                                     |

| (22) 出願日     | 平成17年4月18日 (2005.4.18)                                           |

| (62) 分割の表示   | 特願2003-159403 (P2003-159403)<br>の分割<br>原出願日 平成15年6月4日 (2003.6.4) |

| (31) 優先権主張番号 | 特願2002-187682 (P2002-187682)                                     |

| (32) 優先日     | 平成14年6月27日 (2002.6.27)                                           |

| (33) 優先権主張国  | 日本国 (JP)                                                         |

| (31) 優先権主張番号 | 特願2002-302912 (P2002-302912)                                     |

| (32) 優先日     | 平成14年10月17日 (2002.10.17)                                         |

| (33) 優先権主張国  | 日本国 (JP)                                                         |

|           |                                                       |

|-----------|-------------------------------------------------------|

| (71) 出願人  | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号            |

| (74) 代理人  | 100090538<br>弁理士 西山 恵三                                |

| (74) 代理人  | 100096965<br>弁理士 内尾 裕一                                |

| (72) 発明者  | 井上 俊輔<br>東京都大田区下丸子3丁目30番2号キヤ<br>ノン株式会社内               |

| (72) 発明者  | 篠原 真人<br>東京都大田区下丸子3丁目30番2号キヤ<br>ノン株式会社内               |

| F ターム(参考) | 4M118 AA05 AB01 BA14 CA03 DD04<br>FA06 FA26 FA28 FA33 |

(54) 【発明の名称】 固体撮像装置及び固体撮像装置を用いたカメラシステム

## (57) 【要約】

【課題】 フォトダイオードよりも下方で発生した信号電荷がフォトダイオード以外の領域に吸収され難く、隣接するフォトダイオードへの信号電荷の漏れこみを低減した固体撮像装置を提供する。

【解決手段】 本発明は、第1導電型の第1の半導体領域と第1導電型と逆導電型の第2導電型の第2の半導体領域とにより形成されるフォトダイオードと、前記第2の半導体領域の表面に絶縁膜を介してゲート電極が形成された第2導電型のトランジスタと、を含む画素の複数を有する固体撮像装置において、隣接する前記フォトダイオード間に、トレンチ内に絶縁膜を形成した素子分離領域が形成されており、前記素子分離領域の側壁に第1導電型の第3の半導体領域が形成され、前記素子分離領域の下部に第1導電型の第4の半導体領域が形成されていることを特徴とする。

【選択図】 図9

**【特許請求の範囲】****【請求項 1】**

第1導電型の第1の半導体領域と第1導電型と逆導電型の第2導電型の第2の半導体領域とにより形成されたフォトダイオードと、前記第2の半導体領域の表面に絶縁膜を介してゲート電極が形成された第2導電型のトランジスタと、を含む画素の複数を有する固体撮像装置において、

隣接する前記フォトダイオード間に、トレンチ内に絶縁膜を形成した素子分離領域が形成されており、前記素子分離領域の側壁に第1導電型の第3の半導体領域が形成され、前記素子分離領域の下部に第1導電型の第4の半導体領域が形成されていることを特徴とする固体撮像装置。

**【請求項 2】**

前記第4の半導体領域は、深さ方向に複数のイオン注入工程で形成されていることを特徴とする請求項1に記載の固体撮像装置。

**【請求項 3】**

更に、前記ゲート電極下部の前記第2の半導体領域内に、第2導電型の第5の半導体領域が形成されていることを特徴とする請求項1または2に記載の固体撮像装置。

**【請求項 4】**

前記第5の半導体領域は、深さ方向に複数のイオン注入工程で形成されていることを特徴とする請求項3に記載の固体撮像装置。

**【請求項 5】**

請求項1から4のいずれか1項に記載の固体撮像装置を有することを特徴とするカメラシステム。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は固体撮像装置及び固体撮像装置を用いたカメラシステムに関するものである。

**【背景技術】****【0002】**

固体撮像装置は近年デジタルスチルカメラ、ビデオカムコーダーを中心とする画像入力用撮像装置として、急速に需要が高まっている。

**【0003】**

これらの固体撮像装置としてCCD(Charge Coupled Device:電荷結合素子)やMOS型固体撮像装置が用いられている。前者は後者と比較して、感度が高くノイズが小さいために、高画質の撮像装置として普及している反面、消費電力が大きく、駆動電圧が高い、汎用の半導体製造プロセスが使えないためにコストが高く、駆動回路等の周辺回路を集積することが困難であるなどの弱点を抱えている。

**【0004】**

上記の理由から、従来から增幅型のMOS型固体撮像装置の開発も行われてきた。増幅型の固体撮像装置とは、フォトダイオードに蓄積された信号電荷を画素に備わった増幅トランジスタの制御電極に導き、信号電荷量に応じた出力を増幅トランジスタの主電極から増幅して出力するものである。特に増幅型の固体撮像装置としては、増幅トランジスタとしてMOSトランジスタを使ったCMOSセンサの開発に力が注がれている。

**【0005】**

今後需要の拡大が予想される携帯機器への応用には、上記のCCDの弱点をカバーできるMOS型固体撮像装置が適用されてくるものと予想されている。

**【0006】**

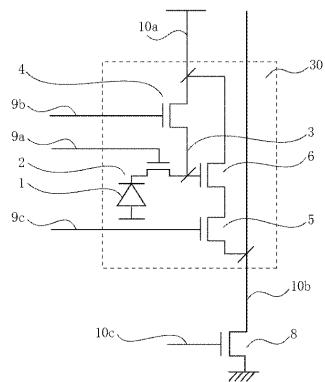

図13は固体撮像装置としてCMOSセンサ画素の典型的な例を示す回路図である。

**【0007】**

図13において30は単位画素、1は入射光によって発生した信号電荷を蓄積するためのフォトダイオード、6は信号電荷量に応じた増幅信号出力を出す増幅MOSトランジス

10

20

30

40

50

タ、3は信号電荷を受け増幅MOSトランジスタ6のゲート電極に接続するフローティングディフュージョン(以下FDと記す)領域、2はフォトダイオード1に蓄積した信号電荷をFD領域3に転送するための転送MOSトランジスタ、4はFD領域3をリセットするためのリセットMOSトランジスタ、5は出力画素を選択するための選択MOSトランジスタ、9aは転送MOSトランジスタ2のゲートにパルスを印加し、電荷転送動作を制御するための制御線、9bはリセットMOSトランジスタ4のゲートにパルスを印加し、リセット動作を制御するための制御線、9cは選択MOSトランジスタ5のゲートにパルスを印加し、選択動作を制御するための制御線、10aは増幅MOSトランジスタ6のドレインおよびリセットMOSトランジスタ4のドレインに接続され、それらに電源電位を供給している電源配線である。10bは選択された画素の増幅信号が出力される出力線、8は定電流源として動作し、増幅MOSトランジスタ6とソースフォロワを形成する定電流用MOSトランジスタ、10cはMOSトランジスタ8が定電流動作するような電位をMOSトランジスタ8のゲート電極に供給する配線である。上記の画素30を2次元的マトリックス状に配列したものは2次元固体撮像装置の画素領域を形成するが、そのマトリックス構成において出力線10bは各列の画素の共通線、制御線9a、9b、9cはそれぞれ各行の画素の共通線となっており、制御線9cによって選択された行の画素のみが出力線10bに信号出力される。

#### 【0008】

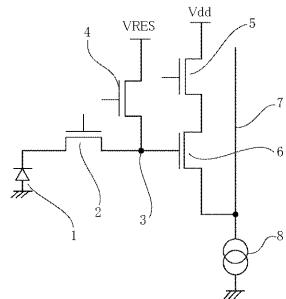

更に、図14は従来の固体撮像装置の他の画素回路を示す図である。図14で1はフォトダイオード、2はフォトダイオードの電荷を転送する転送MOSトランジスタ、3は転送された電荷を一時的に蓄えておくフローティングディフュージョン、4はフローティングディフュージョンおよびフォトダイオードをリセットするためのリセットMOSトランジスタ、5はアレイ中の任意の1行を選択するための選択MOSトランジスタ、6はフローティングディフュージョンの電荷を電圧の変換してソースフォロワー型増幅器で増幅するソースフォロワーMOSトランジスタ、7は1つの列で共通化され画素電圧信号を読み出す読み出し線、8は読み出し線7を定電流とするための定電流源である。

#### 【0009】

動作を簡単に説明する。入射光はフォトダイオード1により電荷に変換され、電荷は転送MOSトランジスタ2により、フローティングディフュージョン3に蓄えられる。フローティングディフュージョン3および、フォトダイオード1は予めリセットMOSトランジスタ4および転送MOSトランジスタ2を開とすることで一定電位にリセットされているので、フローティングディフュージョン3の電位は入射光により発生した電荷に応じて変化する。フローティングディフュージョン3の電位はソースフォロワーMOSトランジスタ6により増幅され、読み出し線7に出力される。当該画素は選択MOSトランジスタ5を開とすることで選ばれる。不図示の出力回路ではフローティングディフュージョン3のリセット電位と光信号蓄積後の電位の差分演算を行うことで、光信号分を検出する。

#### 【0010】

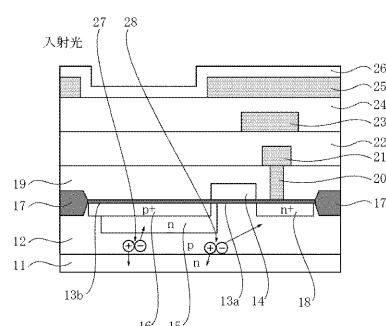

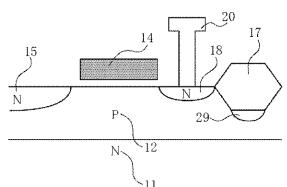

図15は図13に示す固体撮像装置の模式的断面図である。尚、図15はフォトダイオード、転送MOSトランジスタ及びFD領域を含む断面の模式的断面図である。同図において、11はN型の半導体基板、12はP型ウエル、15はP型ウエル12中に形成されたN型半導体領域であり、P型ウエル12とN型半導体領域15とでフォトダイオードが形成され、N型半導体領域15には入射光によって発生した信号電荷が蓄積される。18はP型ウエル内に形成されたN型半導体領域からなるFD領域、14は図13に示す転送MOSトランジスタ2のゲート電極、又、FD領域18は転送MOSトランジスタのドレイン領域でもある。尚、転送MOSトランジスタのソース領域はN型半導体領域15である。20はFD領域18と接続する配線であり、図示されていない増幅MOSトランジスタのゲート電極に接続している。17はLOCOS酸化膜といわれる素子分離用絶縁膜、29は素子分離用絶縁膜17の下に形成されたP型ウエル12よりも不純物濃度の高いP+型のチャンネルストッパーである。

#### 【0011】

図16は図14に示す固体撮像装置の模式的断面図である。この断面図16は図14のフォトダイオード1と転送MOSトランジスタ2の部分を表わしたものである。11はn型シリコン基板、12はP型ウエル、13aはMOSトランジスタのゲート酸化膜、13bは受光部上の薄い酸化膜、14は転送MOSトランジスタのゲート電極、15はフォトダイオード1のN型カソード、16はフォトダイオードを埋め込み構造とするための表面P型領域、17は素子分離のためのLOCOS酸化膜、18はフローティングディフュージョンを形成し転送MOSトランジスタ2のドレイン領域ともなっているN型高濃度領域、19はゲート電極とメタル第一層を絶縁するシリコン酸化膜、20はコンタクトプラグ、21はメタル第一層、22はメタル第一層とメタル第二層を絶縁する層間絶縁膜、23はメタル第二層、24はメタル第二層とメタル第三層を絶縁する層間絶縁膜、25はメタル第三層、26はパッシベーション膜である。カラー用光電変換装置では、パッシベーション膜26の上層に更に不図示のカラーフィルター層、さらに感度向上のためのマイクロレンズを形成する。表面から入射した光はメタル第3層のない開口部を通して、フォトダイオードに入る。光はフォトダイオードのN型カソード15或いはP型ウエル12内で吸収され、電子・ホール対を生成する。このうち電子はN型カソード領域に蓄積されてゆく。

。

10

#### 【0012】

また、特許文献1には、n型基板から所定の深さにp型埋め込み層を形成し、その上側のn型基板に光電変換部を形成した固体撮像装置が開示されている。

#### 【0013】

更に、特許文献2には、フォトダイオードの一端を読み出しゲートの下部にまで延在させて形成し、パンチスルーストッパ領域をドレイン領域に相当する信号検出部の下部に、ゲート電極に対して自己整合して形成した固体撮像装置が開示されている。

#### 【特許文献1】特開2000-150848号公報

#### 【特許文献2】特開2001-15727号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0014】

しかしながら、図15、図16の従来構造の場合、フォトダイオードよりも下方で発生した信号電荷の一部がフォトダイオードに吸収されずFD領域18や画素内のトランジスタのソース・ドレイン領域に吸収されていた。その結果、感度が低下していた。

#### 【0015】

また、CMOS型固体撮像装置はさまざまな改良にも拘わらず、特に小さい画素サイズの装置で感度が低いという課題がある。本発明は新規な構造により、微細な画素でも高感度が得られるCMOS型固体撮像装置を提供するものである。

#### 【0016】

図16の従来構造で感度が低い理由を説明する。図16で開口部に入射した光線27により発生した電子は、首尾よくN型カソード領域に蓄積され、有効な信号電荷として働くが、例えば光線28のようにフォトダイオードから多少離れた位置で発生した電子は、N型カソード領域ではなく、よりポテンシャルの低いN+型フローティングディフュージョン領域18に捉えられる場合がある。また、フォトダイオードの直下であっても、電子は拡散とドリフトを繰り返す結果、ある確率で、フォトダイオード以外の低ポテンシャル領域に吸収され、光電変換信号としては寄与しない。N型カソード15をシリコン表面に対しより深い位置に形成すれば、フォトダイオードにより電子を集めやすくなるが、N型カソード領域はP型ウエル領域12中のイオン注入により形成するために、不純物濃度をあまり低くできない。N型カソード15は空乏化動作をするという制約から、あまり深い位置に高い濃度を形成する構造がとれないと従来構造の課題があった。

#### 【0017】

このように、フォトダイオードとなるN型カソードの体積に限界があるため、入射光により発生した電子を収集する能力が充分でなかつたため、感度が低い。

20

30

40

50

**【 0 0 1 8 】**

また、特許文献 1 に開示された従来構造でも、信号読み出しゲートの下部にポテンシャル障壁を設けていないため、入射光により深い位置で発生した電子がフローティングディフュージョン領域 1 8 などに吸収されてしまうのをやはり防ぐことができず、感度が低くなってしまう課題を有する。

**【 0 0 1 9 】**

更に、特許公報 2 に開示された従来構造でも、パンチスルーストップ領域が信号検出部の下部のみに形成されているだけなので、入射光により発生した電子の一部が、画素内の他のトランジスタのソース、ドレインに吸収されたり、隣接画素へ吸収されてしまうことを防ぐことができず、同様に感度が低くなってしまう課題を有する。

10

**【 0 0 2 0 】**

そこで本発明は、微小な画素でも高感度な固体撮像装置を提供することを目的とする。

**【 課題を解決するための手段 】****【 0 0 2 1 】**

上記課題を解決するために、本発明の固体撮像装置は、第 1 導電型の第 1 の半導体領域と第 1 導電型と逆導電型の第 2 導電型の第 2 の半導体領域とにより形成されたフォトダイオードと、前記第 2 の半導体領域の表面に絶縁膜を介してゲート電極が形成された第 2 導電型のトランジスタと、を含む画素の複数を有する固体撮像装置において、隣接する前記フォトダイオード間に、トレンチ内に絶縁膜を形成した素子分離領域が形成されており、前記素子分離領域の側壁に第 1 導電型の第 3 の半導体領域が形成され、前記素子分離領域の下部に第 1 導電型の第 4 の半導体領域が形成されていることを特徴とする。

20

**【 発明の効果 】****【 0 0 2 2 】**

本発明の固体撮像装置によれば、隣接する素子間での分離性を向上させることができるとなり、素子分離領域を形成してから素子分離層下に隣接するフォトダイオードとの分離構造を形成することができるため、分離構造が熱拡散で広がらない微細なパターンを形成することが可能となる。

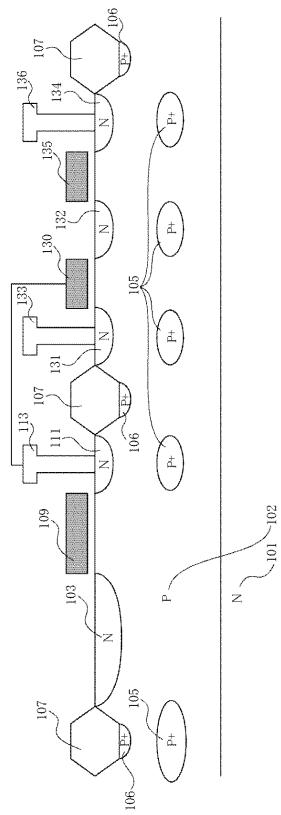

**【 発明を実施するための最良の形態 】****【 0 0 2 3 】****( 第 1 実施形態 )**

30

図 1 は本発明の第 1 実施形態の固体撮像装置の模式的断面図である。

**【 0 0 2 4 】**

図 1 において、1 0 1 は第 1 導電型（ここでは例示として N 型）の半導体基板、1 0 2 は第 2 導電型半導体領域として P 型ウエル、1 0 3 は P 型ウエル 1 0 2 中に形成された第 1 導電型半導体領域として N 型半導体領域であり、P 型ウエル 1 0 2 と N 型半導体領域 1 0 3 とでフォトダイオードが形成され、N 型半導体領域 1 0 3 には入射光によって発生した信号電荷が蓄積される。1 1 1 は第 1 トランジスタとしてフォトダイオードで発生した信号電荷を転送する転送トランジスタの第 1 導電型のドレイン領域であって、P 型ウエル 1 0 2 中に形成された N 型半導体領域の F D 領域である。1 0 9 は転送トランジスタのゲート電極であり、N 型半導体領域 1 0 3、1 1 1 はそれぞれ転送トランジスタのソース、ドレイン領域である。1 1 3 は N 型半導体領域 1 1 1 と接続する配線であり、第 2 トランジスタとしての増幅トランジスタのゲート電極 1 3 0 に接続している。尚、増幅トランジスタは、ソース領域 1 3 1・ドレイン領域 1 3 2 間にゲート電極 1 3 0 を形成して構成される。1 3 3 はソース電極 1 3 1 に接続される垂直信号線である。尚、1 3 2 は増幅トランジスタのドレイン電極でもあって、別の第 2 トランジスタとしての選択トランジスタのソース領域である。1 3 4 は選択トランジスタのドレイン電極であって、ソース・ドレイン電極間にゲート電極 1 3 5 が形成されている。1 3 6 は選択トランジスタのドレイン電極 1 3 4 に接続されるドレイン線である。1 0 7 は厚い酸化膜で形成された素子分離用絶縁膜であり、1 0 6 は素子分離用絶縁膜 1 0 7 の下に形成された P 型ウエル 1 0 2 より不純物濃度の高い P + 型のチャンネルストッパー、1 0 5 は P 型ウエル 1 0 2 と同じ導

40

50

電型のP型半導体領域で形成されたポテンシャル障壁である。

【0025】

尚、本明細書では、転送トランジスタを第1トランジスタとし、画素内に形成された転送トランジスタ以外のトランジスタを第2トランジスタと表する。

【0026】

尚、N型半導体領域103に蓄積された信号電荷は転送動作時にFD領域111に転送され、転送直後にはN型半導体領域103は空乏化するよう、N型半導体領域103におけるN型の不純物濃度が設定されている。

【0027】

又、本実施形態の固体撮像装置は、1画素がフォトダイオード、転送トランジスタ、増幅トランジスタ及び選択トランジスタで構成されるが、1画素の構成は本実施形態に限定されない。例えば、1画素がフォトダイオード、転送トランジスタ及び増幅トランジスタで構成されていても良い。或いは、1画素がフォトダイオード、転送トランジスタ、増幅トランジスタ、選択トランジスタ及びリセットトランジスタで構成されていても良い。

【0028】

本発明のポテンシャル障壁105は、第1トランジスタのドレイン領域下及び第2トランジスタのソース及び/又はドレイン領域下に設けられていることを特徴とする。第2トランジスタが複数形成されている場合は、少なくとも1つ以上のソース及び/又はドレイン領域に設けられている。

【0029】

尚、ポテンシャル障壁105の不純物濃度は、P型ウエル102の不純物濃度よりも高いP+型である。又、チャンネルスットバー106及びポテンシャル障壁105は同じP+型の半導体領域であるが、その不純物濃度は当然異なっても良く、ポテンシャル障壁105はイオンインプランテーションによって例えばボロンやガリウムをP型ウエル102に打ち込む事で設けられる。

【0030】

図1に示すように本発明のポテンシャル障壁105は、FD領域111、増幅トランジスタ及び選択トランジスタのソース・ドレイン領域131、132及び134の下に形成されている。

【0031】

本発明の様に、ポテンシャル障壁105をFD領域や各トランジスタのソース・ドレイン電極下に設けることで、ポテンシャル障壁105よりも下方で発生した信号電荷はFD領域111や、ポテンシャル障壁が設けられた各トランジスタのソース・ドレイン領域へ吸収されないので感度が向上する。

【0032】

従って、ポテンシャル障壁105をより多くの第2トランジスタのソース・ドレイン領域の直下に設けることで、より信号電荷がフォトダイオード以外の領域に吸収され難い構造となるのでより好適である。

【0033】

尚、ポテンシャル障壁105は素子分離領域107の下に設けてあっても良い。素子分離領域107の下にポテンシャル障壁105を設けることで隣接する画素内のフォトダイオード或はトランジスタに信号電荷が吸収されにくい構造となり、隣接画素間の信号電荷の混入が防止ができる。

【0034】

(第2実施形態)

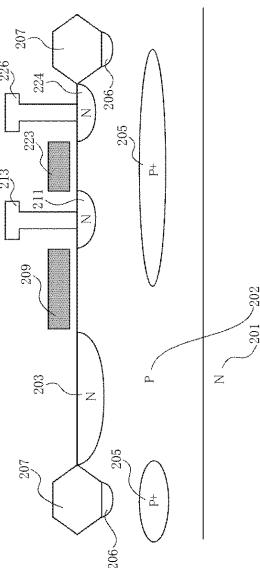

図2は本発明の第2実施形態の固体撮像装置の模式的断面図である。

【0035】

図2はフォトダイオード、転送トランジスタ及びFD電極211をリセットするリセットトランジスタを有する固体撮像装置の模式的断面図であって、第2トランジスタとしてFD電極をリセットするリセットトランジスタが設けられている。

10

20

30

40

50

## 【0036】

図2において、223はFD電極211をリセットするリセット用トランジスタのゲート電極、224は電源線226と接続するFD電極211をリセットするリセット用トランジスタのドレイン領域である。

## 【0037】

本実施形態が実施形態1と異なる点は、本実施形態ではポテンシャル障壁205が第2トランジスタのゲート電極の下にも設けられている点である。従って、ポテンシャル障壁205によってフォトダイオード以外のN型半導体領域に吸収される信号電荷が減少するので、感度が向上する。

## 【0038】

尚、本実施形態は第2トランジスタとしてリセットトランジスタを一例に上げているが、第1実施形態と同様に第2トランジスタは増幅或いは選択リセットトランジスタであっても良い。或いは、複数の第2トランジスタが形成されてあってもよい。

## 【0039】

例えば、本発明のポテンシャル障壁205が、フォトダイオード、転送トランジスタ、リセットトランジスタ、増幅トランジスタ及び選択トランジスタで1画素が構成される固体撮像装置に設けられても良い。

## 【0040】

尚、画素内に形成された全トランジスタのゲート電極、ソース及びドレイン領域の下にポテンシャル障壁205を設けると、より信号電荷がフォトダイオード以外の領域に吸収され難いので感度が向上する。

## 【0041】

さらには、素子分離領域207の下にもポテンシャル障壁205を設けることで、フォトダイオードの周囲にトランジスタのソース・ドレイン領域より深い領域のポテンシャル障壁205が設けられた固体撮像装置となる。

## 【0042】

以上のようにポテンシャル障壁205をフォトダイオードの周囲に設けることで、フォトダイオードで形成された信号電荷が隣接するトランジスタのソース又はドレイン領域に吸収されにくいので感度が向上する。

## 【0043】

又、フォトダイオードの周囲を囲むように設けられたポテンシャル障壁205は1つ以上の開口部が設けられていても良い。

## 【0044】

開口部を設けずにフォトダイオードの周囲にポテンシャル障壁205を設けると、フォトダイオードから信号電荷があふれ出た場合、ポテンシャル障壁205によってあふれ出た信号電荷が周辺のN形半導体領域に吸収されにくく、ブルーミングを起こしやすくなる。そこで、フォトダイオード周辺の少なくとも一部分にポテンシャル障壁205が設けられていない開口部を設けることで、フォトダイオードからあふれ出た信号電荷を吸収させてブルーミングを抑制するとより好適である。

## 【0045】

(第3実施形態)

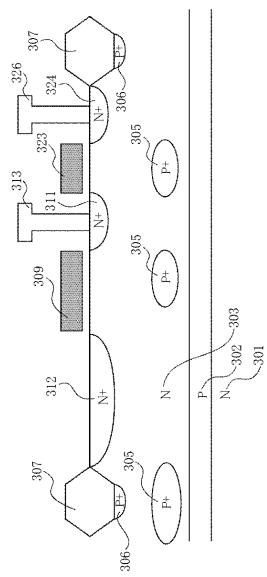

図3は本発明の第3実施形態の固体撮像装置の模式的断面図である。

## 【0046】

図3は、フォトダイオード、転送トランジスタ及びFD電極311をリセットするリセットトランジスタを有する固体撮像装置の模式的断面図である。

## 【0047】

図3において、303は第1導電型半導体領域としてN型ウエル或いはN型半導体基板301の上層部であるN型半導体領域、302はN型半導体領域303とフォトダイオードを構成する第2導電型半導体領域としてのP型半導体領域、312はフォトダイオードで発生した信号電荷を集めて蓄積するための第1導電型の信号電荷蓄積領域であり、N形

10

20

30

40

50

半導体領域303より不純物濃度が濃い領域である。

【0048】

図3が図2と異なる点は、図2においてはP型ウエル202内に反対導電型のN型のソース・ドレイン領域を有するトランジスタが形成され、さらにはポテンシャル障壁205はP型ウエル202と同一導電型であったのに対して、本実施形態では、第1導電型半導体領域としてのN型半導体領域303内に同一導電型のN型のソース・ドレイン領域を有するトランジスタが形成され、さらにN型半導体領域と反対導電型のP型のポテンシャル障壁305を設けている点である。

【0049】

尚、本実施形態においては、フォトダイオードと共に、画素を構成するトランジスタとして、フォトダイオードで発生した信号電荷を転送する転送トランジスタ、及びFD電極をリセットするリセットトランジスタとしているが、トランジスタはこれに限定されない。例えば、画素内のトランジスタは、転送トランジスタ、リセットトランジスタ、増幅トランジスタ或いは選択トランジスタ等のいずれか、或いはその組み合わせでも良い。尚、本実施形態においては、画素を形成するN型トランジスタのゲート電極の下に設けられたポテンシャル障壁305は、ソース、ドレイン間がショートすることを防ぎ、N型半導体領域303中であってもN型トランジスタが動作することを可能にする働きを兼ねている。

【0050】

尚、ゲート電極の下に設けられたポテンシャル障壁305は、ゲート領域に対応した大きさを有するポテンシャル障壁であっても良いし、ゲート電極の一部の下に形成されたポテンシャル障壁であっても良い。

【0051】

従って、本実施形態においては、転送トランジスタのゲート電極309の下のポテンシャル障壁はゲート電極309の一部の下に設けられており、リセットトランジスタのゲート電極323の下にはゲート電極323の大きさに対応したポテンシャル障壁が設けられている。

【0052】

尚、同様に本明細書で言うところのソース・ドレイン領域の下に設けられたポテンシャル障壁は、ソース・ドレイン領域の一部の下に設けられていても良い。

【0053】

又、図3のような画素構造においては、フォトダイオードのN型領域が光の進行方向に對して深く形成されるので、信号電荷に関する量子効率が第1実施形態と比べても高くなる。

【0054】

本実施形態においては、画素中N型トランジスタはN型半導体領域中に形成されるため、そのしきい電位は従来例のN型トランジスタのしきい電位よりも下がり、したがって増幅トランジスタの入出力レンジを広くとることができる。

【0055】

又、本実施形態におけるトランジスタのしきい電位は、バックゲート効果による変動を小さくして、増幅ゲインが従来のものよりも高くすることができる。

【0056】

尚、ポテンシャル障壁305は素子分離領域307の下に設けてあっても良い。素子分離領域307の下にポテンシャル障壁305を設けることで隣接する画素内のフォトダイオード或はトランジスタに信号電荷が吸収されにくい構造となり、隣接画素間の信号電荷の混入が防止ができる。

【0057】

(第4実施形態)

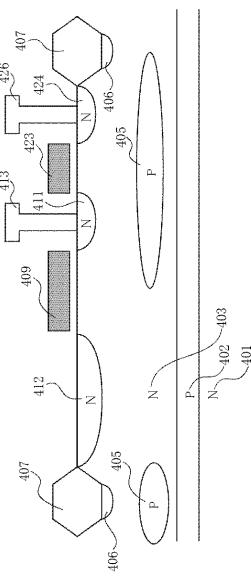

図4は本発明の第4実施形態の固体撮像装置の模式的断面図である。

【0058】

10

20

30

40

50

本実施形態が図3と異なる点は、本実施形態はポテンシャル障壁405がトランジスタのゲート下のみには限らず、画素内に存在するトランジスタのソース及び／又はドレイン領域の下にも設けられている点である。

#### 【0059】

ゲートの下のみだけではなく、ソース及び／又はドレイン領域の下にもポテンシャル障壁405を設けることで、ポテンシャル障壁405よりも下方で発生した信号電荷がトランジスタのソース及び／又はドレイン領域へ吸収され難い構造となるので、さらに感度が向上する。

#### 【0060】

尚、本実施形態においては、画素内のトランジスタとして、フォトダイオードで発生した信号電荷を転送する転送トランジスタ、及びFD電極をリセットするリセットトランジスタとしているが、トランジスタはこれに限定されない。例えば、画素内のトランジスタは、転送トランジスタ、リセットトランジスタ、増幅トランジスタ或いは選択トランジスタ等のいずれか、或いはその組み合わせでも良い。

#### 【0061】

尚、ポテンシャル障壁405は素子分離領域407の下に設けてあっても良い。素子分離領域407の下にポテンシャル障壁405を設けることで隣接する画素内のフォトダイオード或はトランジスタに信号電荷が吸収されにくい構造となり、隣接画素間の信号電荷の混入が防止ができる。

#### 【0062】

以上のようにポテンシャル障壁405をフォトダイオードの周囲に設けることで、フォトダイオードで形成された信号電荷が隣接するトランジスタのソース又はドレイン領域に吸収されにくいのでポテンシャル障壁のない場合に比べて感度が上がる。又、フォトダイオードの周囲を囲むように設けられたポテンシャル障壁405には1つ以上のポテンシャル障壁が設けられていない開口部が設けられていても良い。

#### 【0063】

開口部を設けずにフォトダイオードの周囲全面にポテンシャル障壁405を設けると、フォトダイオードから信号電荷があふれ出た場合、ポテンシャル障壁405によってあふれ出た信号電荷が周辺のN形半導体領域に吸収されにくく、ブルーミングを起こしやすくなる。そこで、フォトダイオード周辺の少なくとも一部分にポテンシャル障壁405が設けられていない開口部を設けることで、フォトダイオードからあふれ出た信号電荷を吸収させてブルーミングを抑制することができる。

#### 【0064】

又、ブルーミングを抑える別の形態としては、P型半導体領域402の不純物濃度を、ポテンシャル障壁405の不純物濃度よりも薄くし、フォトダイオードからあふれ出た信号電荷をN型半導体基板401に逃がす、いわゆる縦型オーバーフロードレイン構造がある。このような構造にすることで、上述のような開口部を設けずに済むので、開口部を設けない場合に比べて感度が向上する。

#### 【0065】

又、本実施形態では信号電荷蓄積領域412を設けているがなくても良い。又、信号電荷が蓄積されるN型半導体領域、或は、信号電荷蓄積領域412の半導体界面部にP型の半導体領域が形成されるいわゆる埋め込みフォトダイオードであってもよい。

#### 【0066】

以上、第1乃至第4実施形態における画素構造としては、N型、P型の極性をすべて反転したものであってもよい。

#### 【0067】

(第5実施形態)

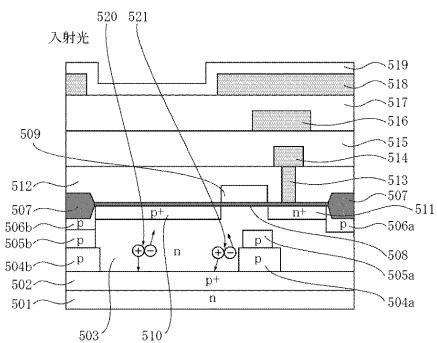

図5は本発明の第5実施形態の固体撮像装置の模式的断面図である。

#### 【0068】

第5実施形態を説明する断面図を図5に示す。図5は従来例の図16と同様に、画素内

10

20

30

40

50

のフォトダイオード部と転送MOSトランジスタ部、フローティングディフュージョン部を示したものである。501はN型シリコン基板、502は埋め込みP型高濃度層、503はフォトダイオードのカソードとなるN型エピタキシャル層、504a、504bはP型分離層、505a、505bはP型ウエル層である。また、506aはフィールド酸化膜下のチャンネルトップP型層である。507はフィールド酸化膜、508はMOSトランジスタのゲート酸化膜、509は転送MOSトランジスタのゲートポリシリコン、510はフォトダイオードを埋め込み型とするための表面P型層である。また511は転送MOSトランジスタのN型ドレイン拡散領域であり、転送された電荷を一時的に蓄えておく、フローティングディフュージョンの役割を果たしている。さらに、512は第一の層間絶縁膜、513はコンタクトプラグ、514は第一層目の配線層、515は第二の絶縁膜、516は第二層目の配線層、517は第三の層間絶縁膜、518は第三層目の配線層、519はパッシベーション膜である。本実施例では配線層は3層形成したが、センサの仕様によっては、光学特性を確保する上で、配線層を1層、或いは2層とすることも本発明の主旨と矛盾はない。なお、カラー撮像装置として使用する場合にパッシベーション膜上に色フィルター層を形成したり、色フィルターのさらに上部にマイクロレンズを形成することにより光感度を向上させることは従来の撮像装置同様に行うことができる。P型分離層504a、504bそして、P型ウエル層505a、505bは埋め込みP型高濃度層と相まって、フォトダイオードのカソードとなるN型エピタキシャル領域503を囲うことで、隣接画素のフォトダイオード同士を電気的に分離している。画素へ入射光520および521によって発生した電子・ホール対のうち、電子はN型エピタキシャル層を囲んでいる種々のP型層によるポテンシャルバリアによって、確実に信号電荷としてフォトダイオードに蓄積される。またP型ウエル層505aは転送MOSトランジスタのほぼ直下に位置し、N型エピタキシャル層503に蓄積された電子を転送MOSのチャネルを通してフローティングディフュージョンに転送される際の転送路をも制御している。P型ウエル層の濃度、深さ、横方向位置を適切に設計することで、MOSゲート509に読み出力電圧を印加したときに、N型エピタキシャル層503が完全に空乏化するように、動作させることができる。P型分離層504aと電気的につながったP型ウエル層は電荷転送MOSトランジスタのウエルとして作用することにより、該MOSトランジスタの閾値電圧をも制御する。また、P型ウエル層505aは画素内の他のトランジスタの下にも配置され、これらのMOSトランジスタのウエルとしても作用する。P型高濃度埋め込み層502の深さはセンサに必要な分光特性が得られる深さに設計する。ポテンシャルバリアを形成する上では、ピークとなる不純物濃度が $1E15$ (/cm<sup>3</sup>)以上あればよい。電気抵抗を下げるために高濃度で形成できるほうがよい。高エネルギーで高ドーズのイオン注入をすることは製造コストを上昇させるので、現実的には濃度上限は決まる。また、P型分離層504a、504bはフォトダイオードの開口面積と入射する光が到達しする位置を考慮して、横方向の位置を決める。不純物濃度はポテンシャルバリアが形成できる $1E15$ (/cm<sup>3</sup>)以上あればよい。また、N型エピタキシャル層の厚さが本実施例より更に厚い場合には、さらに第二のP型分離層を追加することで、深さ方向にP型層が連結する構造とすることができます。本実施例の構造を作るための製造方法を記述する。P型高濃度埋め込み層502を形成する方法は概略2通りある。第一の方法では、n型シリコン基板501表面にボロンをイオン注入した後、n型シリコン層503をエピタキシャル成長させる。n型基板501の不純物濃度は $1E13$ ~ $1E15$ (/cm<sup>3</sup>)の範囲が適当である。またP型埋め込み層502は $1E15$ ~ $1E20$ (/cm<sup>3</sup>)が可能である。N型エピタキシャル層503の不純物濃度は $1E14$ ~ $1E16$ (/cm<sup>3</sup>)が可能である。N型エピタキシャル層503の厚さは必要な分光感度により設定される。通常の可視光の撮像装置であれば、2μm~6μm程度が適当である。第二の方法では、不純物濃度 $1E14$ ~ $1E16$ (/cm<sup>3</sup>)のn型シリコン基板、またはn型シリコン基板にエピタキシャル成長させた基板表面から、1MeV~5MeVの加速エネルギーでボロンをイオン注入することで、P型高濃度埋め込み層502を形成する。P型高濃度埋め込み層502より表面側が、図5のN型エピタキシャル層503となる。次にパターニングとイオン注入に

より、P型分離層504a、504b、続いてP型ウエル層505a、505bを形成する。P型分離層504a、504bの不純物濃度は下地のN型シリコンのN型不純物濃度を相殺して、ネットでP型1E15～1E18( / cm<sup>3</sup>)が可能である。有効な設計ではN型エピタキシャル層の不純物濃度の濃度より高い濃度とすることにより、フォトダイオードのPN接合が逆バイアスされたときにも、P型層が空乏化せずに、ポテンシャルバリアとして有效地に働くようにする。本実施例の様にエピタキシャル層の厚さが4μm程度の場合、P型分離層504a、504bはイオン注入の飛程としては1.5～3.0μmが好適である。本実施例ではイオン種としてボロンを用い、1200KeVのエネルギーで6E11(cm<sup>-2</sup>)のdose量を注入した。この条件によりボロンの飛程は1.9μmとなり、P型高濃度埋め込みと電気的に接続させることができる。P型ウエル層505a、505bはイオン注入の飛程としては0.5～1.5μmが好適である。本実施例ではイオン種としてボロンを用い、500KeVのエネルギーで1E12(cm<sup>-2</sup>)のdose量を注入した。この条件によりボロンの飛程は1.0μmとなり、P型分離層504a、504bと電気的に接続させることができる。なお、エピタキシャル層の厚さが変わると、P型分離層、P型ウエル層の作製条件は変わってくる。P型ウエル層が電気的にP型高濃度埋め込み層と接続されるためには、エピタキシャル層の厚さが6μm以上では、P型分離層を2層構成にするのが好適である。また、エピタキシャル層の厚さが2μm以下の場合はP型分離層は不要となる。エピタキシャル層の厚さは撮像素子の長波長側の分光感度を決めているが、通常の可視光域ではエピタキシャルの厚さは4μmあれば充分であるので、本実施例の構造は可視光域の撮像素子には好適である。次に、イオン注入によりチャネルトップ層506a、506bを形成した後、通常のLOCOS分離法あるいはリセスルOCOS法などによりフィールド酸化膜507を形成する。ポリシリコン電極509を形成した後、イオン注入により、フォトダイオード表面にP型表面層510、N型高濃度層511を形成する。コンタクト開口工程以降の製造方法は従来の撮像素子と同様であるので、省略する。本実施例により従来フォトダイオードで捉えることができなかった光キャリアをも捕獲することができ、感度が向上する。なお、本実施例では、エピタキシャル層の導電型をN型としたが、これをP型とし、他の全ての導電型を反転することにより、ホール蓄積型画素を構成した場合にも本発明を適用できることは言うまでもない。

## 【0069】

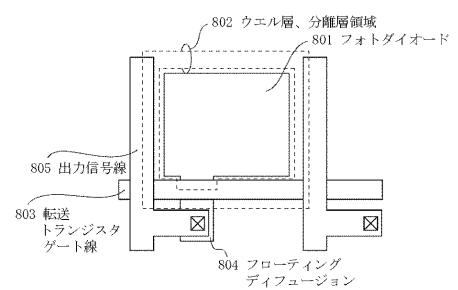

図8は平面図の一例である。フォトダイオード801を取り囲むようにP型ウエル層および分離層802が破線の領域に配置されている。フォトダイオード801の一端に電荷を転送するための転送トランジスタゲート線803が配置される。また804は転送された電荷を一時的に蓄積するフローティングディフュージョンがある。本平面図では増幅用MOSトランジスタ、リセット用MOSトランジスタ、あるいは行選択用MOSトランジスタは図示していないが、本発明を実現する上でこれらの素子の配置に新たな制約が加わるわけではない。本平面の要点は、ウエル層、分離層がフォトダイオードを取り囲むことで、隣接画素との分離を行っている点である。

## 【0070】

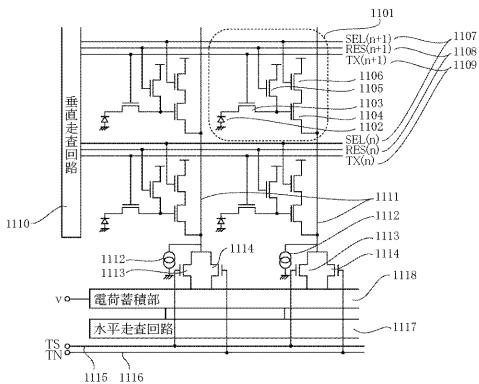

図11は本発明の画素回路を多数個二次元に配置したときの回路構成の略図である。ひとつの中の画素1101にはフォトダイオード1102、転送MOSトランジスタ1103、増幅MOSトランジスタ1104、リセットMOSトランジスタ1105、選択MOSトランジスタ1106がある。同じ行の選択MOSトランジスタのゲートは選択線1107、リセットMOSトランジスタのゲートはリセット線1108、そして転送MOSトランジスタのゲートは転送線1109でそれぞれ接続され、垂直走査回路1110により、走査・選択される。同じ列の出力線1111には電流源1112が接続され、出力線の電位をソースフォロワー動作で読み出すことができる。出力線上の光信号は光信号読み出し線1115で選択された光信号転送MOSトランジスタ1113、ノイズ信号はノイズ信号読み出し線1116選択されたノイズ信号転送MOSトランジスタ1114により、それぞれ電荷蓄積部1118に蓄えられる。電荷蓄積部1118に蓄積された信号は水平走査

10

20

30

40

50

回路で順次走査・読み出され、不図示の差動増幅回路により、光信号とノイズ信号の差分が output される。

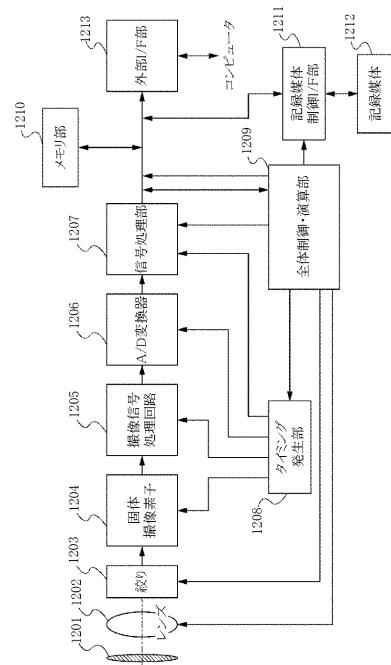

#### 【0071】

図12は本発明による固体撮像装置をカメラに応用する場合の回路ブロックの例を示したものである。撮影レンズ1202の手前にはシャッター1201があり、露出を制御する。絞り1203により必要に応じ光量を制御し、固体撮像素子1204に結像させる。固体撮像素子1204から出力された信号は信号処理回路1205で処理され、A/D変換器によりアナログ信号からデジタル信号に変換される。出力されるデジタル信号はさらに信号処理部1207で演算処理される。処理されたデジタル信号はメモリー1210に蓄えられたり、外部I/F1213を通して外部の機器に送られる。固体撮像装置1204、撮像信号処理回路1205、A/D変換器1206、信号処理部1207はタイミング発生部1208により制御される他、システム全体は全体制御部・演算部1209で制御される。記録媒体1212に画像を記録するために、出力デジタル信号は全体制御部・演算部で制御される記録媒体制御I/F部1211を通して、記録される。10

#### 【0072】

本発明により、CMOS型固体撮像装置の感度を大幅に向上できるほか、より従来と比較してN型層の体積の大きいフォトダイオードを構成することができるので、撮像素子の飽和電荷をも大きくすることができます。また、埋め込みフォトダイオードの表面P型層510と接するN型エピタキシャル層503の接合部分の不純物濃度が従来より低いために、画素欠陥の発生率を低下させることができます。品質面でも従来例より改善する。20

#### 【0073】

##### (第6実施形態)

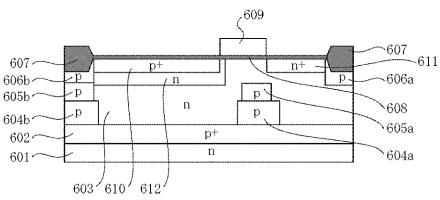

図6は本発明の第6実施形態の固体撮像装置の模式的断面図である。

#### 【0074】

第6実施形態を説明する断面図を図6に示す。ゲート電極を除いた配線部分は第5実施形態と同じなので、不図示とした。

#### 【0075】

第5実施形態と異なる点は、フォトダイオードの構造でN型エピタキシャル層603の表面付近に別のN型層612を追加したことである。このN型層はP型表面層610の下に存在し、また、ゲート電極609の下にも一部入り込む構造になっている。N型層612の不純物濃度はN型エピタキシャル層より高く $1E15 \sim 1E17$ 程度が好適である。このようにN型層612は電子にとってはボテンシャルが低い個所になるので、電荷蓄積中に電子はN型層612に集まってくる。したがって、MOSトランジスタにより電荷転送する際に、電子を完全に転送するのに適した構造である。電荷を完全に転送することで、フォトダイオードに残存する電子数のゆらぎが無くなるのでランダムノイズの小さい撮像素子が構成できる。N型層612は、ゲートポリシリコン電極609を形成する以前の工程でパターニングとイオン注入により形成する、あるいは、ゲートポリシリコン電極609形成後に斜めイオン注入法により、ゲートポリシリコン電極609の下にもぐりこませることができる。図6の断面図の他の部分は第5実施形態と同じである。本発明の要である、P型分離層604a, 604b、およびP型ウエル層605a, 605bの形成方法は第5実施形態と同じ方法を用いることができる。他の部分も同様であるので説明を省略する。3040

#### 【0076】

本実施例の効果は、フォトダイオードのカソード部の表面側に他の部分より不純物濃度の高い部分を設けることで、蓄積中の電子を転送MOSトランジスタで転送しやすくなることである。この構造により、フォトダイオード電荷の完全転送が容易になり、ランダムノイズの少ない装置が実現できる。なお、本実施形態も図8, 11, 12に示す平面構造と回路構成、そしてブロック構成により撮像システムとして有効に働く。

#### 【0077】

##### (第7実施形態)

図7は本発明の第7実施形態の固体撮像装置の模式的断面図である。

【0078】

第7実施形態を説明する断面図を図7に示す。

【0079】

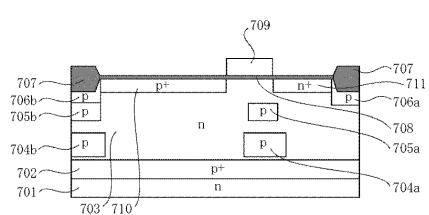

本実施例ではP型分離層704a、704bは、P型ウエル層705a、705bおよびP型高濃度埋め込み層702と不純物濃度の上では完全に接触していない構造を示した。このような構造であっても、これらのP型領域がフォトダイオードのN型領域(N型エピタキシャル層703)に対して、充分なポテンシャル障壁を形成していれば使用可能である。ポテンシャル障壁はフォトダイオードに蓄積したい電荷数より決定することができる。なお、第5実施形態でN型エピタキシャル層の厚さを2um~6umとしたが、P型層でポテンシャル障壁を形成するために、分離層の数を深さ方向に複数個に増やすことができる。

10

【0080】

図7の断面図の他の部分は第5実施形態と同じであるので説明を省略する。

【0081】

本実施例では分離層がPウエル層やP型埋め込み層と接触していないとも、充分なポテンシャル障壁が形成されれば、本発明が適用可能であることを示した。N型エピタキシャル層の厚さに応じ、必要な分離層の数と濃度を本実施例の指針に従って設計すればよいことが示された。

20

【0082】

(第8実施形態)

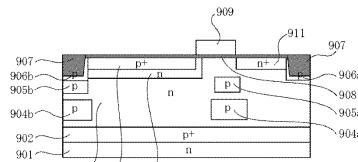

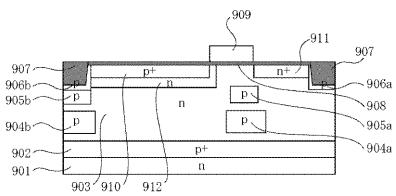

図9は本発明の第8実施形態の固体撮像装置の模式的断面図である。

【0083】

第8実施形態を説明する断面図を図9に示す。

【0084】

本実施例では素子分離方法として、STI(Shallow Trench Isolation)を用いた場合を示す。P型分離層904a、904bは、P型ウエル層905a、905bおよびP型高濃度埋め込み層902と不純物濃度の上では完全に接触していない構造を示した。この構造は第7実施形態と同じである。図9中、STI酸化膜907の下部にはSTI酸化膜907とシリコンの界面を空乏化させないためのP型領域906a、906bがある。このP型領域はSTI酸化膜の側面部を空乏化させないために特に重要である。P型ウエル層905、905bは第7実施形態と同じ深さに形成されており、隣接画素への電荷のもれこみを防止するとともに、転送MOSトランジスタの転送路を制御し、転送MOSトランジスタの閾値をも制御する。また、STI酸化膜907の直下にあるP型ウエル層905bは素子分離直下にポテンシャルバリアを形成すると同時に、STI酸化膜907下のチャネルストッパーの役割も果たしている。P型分離層904a、904bは他の実施形態と同様に、P型ウエル領域905a、905bとP型高濃度埋め込み領域902の間にポテンシャルバリアを形成している。

30

【0085】

他の構造は第6実施形態乃至第7実施形態と同じであるので説明を省略する。

40

【0086】

本実施形態では素子分離をSTIとすることにより、以下の効果がある：隣接フォトダイオード間の分離性が向上。表面が平坦であるので微細な加工でもレジスト形状が安定する。STIを形成してからP型分離層、P型ウエル層をイオン注入で形成することができるので、P型分離層、P型ウエル層が酸化時の熱拡散で広がらない微細なパターンを形成できる。

【0087】

STIを用いた本実施例は微細な画素の撮像素子の製造に適している。

【0088】

(第9実施形態)

50

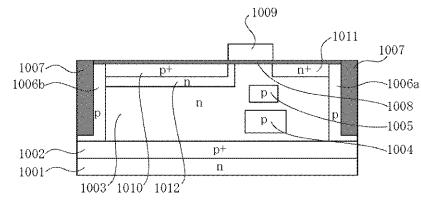

図10は本発明の第9実施形態の固体撮像装置の模式的断面図である。

【0089】

第9実施形態を説明する断面図を図10に示す。

【0090】

本実施例では素子分離方法として、深いトレンチ分離(Deep Trench Isolation)法を用いた場合を示す。本実施形態でも、P型分離層1004、P型ウエル層1005は、P型高濃度埋め込み層1002と不純物濃度の上では完全に接触していない構造を示した。この構造は第7、第8実施形態と同じである。トレンチ分離酸化膜1007はシリコン内3μmの深さまで達しており、トレンチ分離酸化膜1007とシリコンの界面を空乏化させないためのP型領域1006a、1006bが界面を覆っている。このP型領域1006a、1006bは暗電流を防止すると同時に、トレンチ分離酸化膜1007とP型高濃度埋め込み層1002にポテンシャルバリアを形成している。

10

【0091】

他の構造は第6実施形態乃至第8実施形態と同じであるので説明を省略する。

【0092】

本実施例では素子分離を深いトレンチ分離とすることにより、以下の効果がある：隣接フォトダイオード間の分離性がSTIより更に向上去る。分離領域の幅が小さく、かつ深い領域まで分離できるので、微細な画素に適した構造である。

20

【図面の簡単な説明】

【0093】

20

【図1】本発明の第1実施形態の固体撮像装置の模式的断面図である。

【図2】本発明の第2実施形態の固体撮像装置の模式的断面図である。

【図3】本発明の第3実施形態の固体撮像装置の模式的断面図である。

【図4】本発明の第4実施形態の固体撮像装置の模式的断面図である。

【図5】本発明の第5実施形態の固体撮像装置の模式的断面図である。

【図6】本発明の第6実施形態の固体撮像装置の模式的断面図である。

【図7】本発明の第7実施形態の固体撮像装置の模式的断面図である。

【図8】本発明による固体撮像装置の画素平面図である。

【図9】本発明の第8実施形態の固体撮像装置の模式的断面図である。

【図10】本発明の第9実施形態の固体撮像装置の模式的断面図である。

30

【図11】本発明による固体撮像装置の回路図の一部である。

【図12】本発明による固体撮像装置を用いたカメラシステムのブロック図である。

【図13】固体撮像装置としてCMOSセンサ画素の典型的な例を示す回路図である。

【図14】従来の固体撮像装置の画素回路を示す図である。

【図15】図13に示す固体撮像装置の模式的断面図である。

【図16】図14に示す固体撮像装置の模式的断面図である。

30

【符号の説明】

【0094】

40

1、801 フォトダイオード

2 転送MOSトランジスタ

3、804 フローティングディフュージョン

4 リセットMOSトランジスタ

5 選択MOSトランジスタ

6 ソースフォロワーMOSトランジスタ

7、10b 読み出し線

8 定電流源

9a, 9b, 9c 制御線

10a 電源配線

10c 配線

11 n型シリコン基板

50

|                                                                               |                    |    |

|-------------------------------------------------------------------------------|--------------------|----|

| 1 2                                                                           | p 型ウエル             |    |

| 1 3 a                                                                         | ゲート酸化膜             |    |

| 1 3 b                                                                         | 薄い酸化膜              |    |

| 1 4                                                                           | 転送MOSトランジスタゲート電極   |    |

| 1 5                                                                           | フォトダイオードn型カソード     |    |

| 1 6                                                                           | 表面p型領域             |    |

| 1 7                                                                           | LOCOS酸化膜           |    |

| 1 8                                                                           | ドレインn型高濃度領域        |    |

| 1 9                                                                           | シリコン酸化膜            |    |

| 2 0                                                                           | コントラクトプラグ          | 10 |

| 2 1                                                                           | メタル第一層             |    |

| 2 2                                                                           | メタル第一層とメタル第二層層間絶縁膜 |    |

| 2 3                                                                           | メタル第二層             |    |

| 2 4                                                                           | メタル第二層とメタル第三層層間絶縁膜 |    |

| 2 5                                                                           | メタル第三層             |    |

| 2 6                                                                           | パッシベ - シヨン膜        |    |

| 2 7 , 2 8                                                                     | 入射光                |    |

| 2 9                                                                           | チャンネルストッパー         |    |

| 3 0                                                                           | 単位画素               |    |

| 1 0 1 , 2 0 1 , 3 0 1 , 4 0 1                                                 | N型シリコン基板           | 20 |

| 1 0 2 , 2 0 2                                                                 | P型ウエル層             |    |

| 1 0 3 , 2 0 3                                                                 | N型半導体領域            |    |

| 1 0 5 , 2 0 5 , 3 0 5 , 4 0 5                                                 | ポテンシャル障壁           |    |

| 1 0 6 , 2 0 6 , 3 0 6 , 4 0 6                                                 | チャンネルストッパー         |    |

| 1 0 7 , 2 0 7 , 3 0 7 , 4 0 7                                                 | 素子分離用絶縁膜           |    |

| 1 0 9 , 2 0 9 , 3 0 9 , 4 0 9                                                 | 転送トランジスタのゲート電極     |    |

| 1 1 1 , 2 1 1 , 3 1 1 , 4 1 1                                                 | F D領域              |    |

| 3 1 2 , 4 1 2                                                                 | 信号電荷蓄積領域           |    |

| 1 1 3 , 2 1 3 , 3 1 3 , 4 1 3                                                 | 配線                 |    |

| 1 3 0                                                                         | 増幅トランジスタのゲート電極     | 30 |

| 1 3 1                                                                         | 増幅トランジスタのソース領域     |    |

| 1 3 2                                                                         | 増幅トランジスタのドレイン領域    |    |

| 1 3 3                                                                         | 垂直信号線              |    |

| 1 3 4                                                                         | 選択トランジスタのドレイン領域    |    |

| 1 3 5                                                                         | 選択トランジスタのゲート電極     |    |

| 1 3 6                                                                         | 選択トランジスタのドレイン電極    |    |

| 2 2 3 , 3 2 3 , 4 2 3                                                         | リセット用トランジスタのゲート電極  |    |

| 2 2 4 , 3 2 4 , 4 2 4                                                         | リセット用トランジスタのドレイン電極 |    |

| 2 2 6 , 3 2 6 , 4 2 6                                                         | 電源線                |    |

| 5 0 1 , 6 0 1 , 7 0 1 , 9 0 1 , 1 0 0 1                                       | N型シリコン基板           | 40 |

| 5 0 2 , 6 0 2 , 7 0 2 , 9 0 2 , 1 0 0 2                                       | P型高濃度埋め込み層         |    |

| 5 0 3 , 6 0 3 , 7 0 3 , 9 0 3 , 1 0 0 3                                       | N型エピタキシャル層         |    |

| 5 0 4 a , 5 0 4 b , 6 0 4 a , 6 0 4 b , 7 0 4 a , 7 0 4 b , 9 0 4 a , 9 0 4 b |                    |    |

| 、 1 0 0 4                                                                     | P型分離層              |    |

| 5 0 5 a , 5 0 5 b , 6 0 5 a , 6 0 5 b , 7 0 5 a , 7 0 5 b , 9 0 5 a , 9 0 5 b |                    |    |

| 、 1 0 0 5                                                                     | P型ウエル層             |    |

| 5 0 6 a , 5 0 6 b , 6 0 6 a , 6 0 6 b , 7 0 6 a , 7 0 6 b                     | チャンネルストップ層         |    |

| 5 0 7 , 6 0 7 , 7 0 7                                                         | フィールド酸化膜           |    |

| 5 0 8 , 6 0 8 , 7 0 8 , 9 0 8 , 1 0 0 8                                       | ゲート酸化膜             | 50 |

|                                           |             |    |

|-------------------------------------------|-------------|----|

| 5 0 9 , 6 0 9 , 7 0 9 、 9 0 9 、 1 0 0 9   | ゲートポリシリコン電極 |    |

| 5 1 0 、 6 1 0 、 7 1 0 、 9 1 0 、 1 0 1 0   | 表面 P 型層     |    |

| 5 1 1 , 6 1 1 , 7 1 1 , 9 1 1 , 1 0 1 1   | N 型ドレイン領域   |    |

| 5 1 2 第一の層間絶縁膜                            |             |    |

| 5 1 3 コンタクトプラグ                            |             |    |

| 5 1 4 第一の配線層                              |             |    |

| 5 1 5 第二の層間絶縁膜                            |             |    |

| 5 1 6 第二の配線層                              |             |    |

| 5 1 7 第三の層間絶縁膜                            |             |    |

| 5 1 8 第三の配線層                              |             | 10 |

| 5 1 9 パッシベ - ション膜                         |             |    |

| 5 2 0 、 5 2 1 入射光                         |             |    |

| 6 1 2 、 9 1 2 、 1 0 1 2                   | 表面 N 型層     |    |

| 8 0 2 ウエル層、分離層領域                          |             |    |

| 8 0 3 転送トランジスタゲート線                        |             |    |

| 8 0 5 出力信号線                               |             |    |

| 1 1 0 1 単位画素                              |             |    |

| 1 1 0 2 フォトダイオード                          |             |    |

| 1 1 0 3 転送MOSトランジスタ                       |             |    |

| 1 1 0 4 増幅用MOSトランジスタ                      |             | 20 |

| 1 1 0 5 リセットMOSトランジスタ                     |             |    |

| 1 1 0 6 選択MOSトランジスタ                       |             |    |

| 1 1 0 7 行選択線                              |             |    |

| 1 1 0 8 リセット線                             |             |    |

| 1 1 0 9 転送線                               |             |    |

| 1 1 1 0 垂直走査回路                            |             |    |

| 1 1 1 1 出力線                               |             |    |

| 1 1 1 2 定電流源                              |             |    |

| 1 1 1 3 光信号読み出しMOSトランジスタ                  |             |    |

| 1 1 1 4 ノイズ信号読み出しMOSトランジスタ                |             | 30 |

| 1 1 1 5 光信号読み出し線                          |             |    |

| 1 1 1 6 ノイズ信号読み出し線                        |             |    |

| 1 1 1 7 水平走査回路                            |             |    |

| 1 1 1 8 電荷蓄積部                             |             |    |

| 9 0 6 a 、 9 0 6 b 、 1 0 0 6 a 、 1 0 0 6 b | P型領域        |    |

| 9 0 7 シャロートレンチ分離酸化膜                       |             |    |

| 1 0 0 7 深いトレンチ分離酸化膜                       |             |    |

| 1 2 0 1 シャッター                             |             |    |

| 1 2 0 2 レンズ                               |             |    |

| 1 2 0 3 紋り                                |             | 40 |

| 1 2 0 4 固体撮像装置                            |             |    |

| 1 2 0 5 撮像信号処理回路                          |             |    |

| 1 2 0 6 A / D 変換器                         |             |    |

| 1 2 0 7 信号処理部                             |             |    |

| 1 2 0 8 タイミング発生部                          |             |    |

| 1 2 0 9 全体制御・演算部                          |             |    |

| 1 2 1 0 メモリ部                              |             |    |

| 1 2 1 1 記録媒体制御I / F部                      |             |    |

| 1 2 1 2 記録媒体                              |             |    |

| 1 2 1 3 外部I / F部                          |             | 50 |

【 図 1 】

【 四 2 】

【図3】

【 図 4 】

【 図 5 】

【 図 6 】

【図7】

【 図 8 】

【 図 9 】

【 図 1 0 】

【 図 1 1 】

【 図 1 2 】

【図13】

【図14】

【図15】

【図16】