(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4627651号

(P4627651)

(45) 発行日 平成23年2月9日(2011.2.9)

(24) 登録日 平成22年11月19日(2010.11.19)

(51) Int.Cl.

F 1

G05F 3/24 (2006.01)

H03F 3/343 (2006.01)G05F 3/24

H03F 3/343A

A

請求項の数 8 (全 16 頁)

(21) 出願番号 特願2004-285925 (P2004-285925)

(22) 出願日 平成16年9月30日 (2004. 9. 30)

(65) 公開番号 特開2006-99507 (P2006-99507A)

(43) 公開日 平成18年4月13日 (2006. 4. 13)

審査請求日 平成19年9月28日 (2007. 9. 28)

(73) 特許権者 000001960

シチズンホールディングス株式会社

東京都西東京市田無町六丁目1番12号

(74) 代理人 100104190

弁理士 酒井 昭徳

(72) 発明者 人見 正彦

東京都西東京市田無町六丁目1番12号

シチズン時計株式会社内

(72) 発明者 下鶴 雅士

東京都西東京市田無町六丁目1番12号

シチズン時計株式会社内

審査官 梶木澤 昌司

最終頁に続く

(54) 【発明の名称】定電圧発生回路

## (57) 【特許請求の範囲】

## 【請求項 1】

電源電圧を降圧して得られたレギュレート電圧を出力する定電圧発生回路であって、

電源電圧に基づいて、レギュレート電圧を生成するための基準電圧を発生する基準電圧

発生源と、

一方の入力端子に前記基準電圧発生源の出力電位が入力され、他方の入力端子に、レギ

ュレート電圧出力端子の電位に所定の電位差を加算した電位が入力され、前記レギュレー

ト電圧出力端子の電位を、前記2つの入力端子に入力される電位に基づいて一定に保つよ

うに動作する差動アンプと、

電源投入直後の一定期間、前記基準電圧発生源の出力端子の電流量が増えるように前記

基準電圧発生源の出力電位を制御する基準電圧制御手段と、

を備えることを特徴とする定電圧発生回路。

## 【請求項 2】

前記基準電圧制御手段は、前記基準電圧発生源の出力端子を差動アンプの前記他方の入

力端子に接続可能なスイッチ手段を含むことを特徴とする請求項1に記載の定電圧発生回

路。

## 【請求項 3】

前記基準電圧制御手段は、電源投入直後の一定期間だけ前記スイッチ手段を閉状態にす

るスイッチ制御手段をさらに有することを特徴とする請求項2に記載の定電圧発生回路。

## 【請求項 4】

前記基準電圧制御手段は、前記基準電圧発生源の出力端子を負の電源ラインに接続可能なことを特徴とする請求項 1 に記載の定電圧発生回路。

**【請求項 5】**

前記基準電圧制御手段は、前記基準電圧発生源の出力端子を定電圧発生回路の出力に接続可能なことを特徴とする請求項 1 に記載の定電圧発生回路。

**【請求項 6】**

前記基準電圧制御手段は、前記基準電圧発生源の出力電位に基づいてオン状態とオフ状態との切り替えが制御されるNチャネルのトランジスタを含むことを特徴とする請求項 1 に記載の定電圧発生回路。

**【請求項 7】**

前記基準電圧制御手段は、差動アンプの前記他方の入力端子に入力される電位に基づいてオン状態とオフ状態との切り替えが制御されるPチャネルのトランジスタを含むことを特徴とする請求項 1 に記載の定電圧発生回路。

10

**【請求項 8】**

前記基準電圧発生源は、カレントミラー回路を含み、

前記基準電圧制御手段は、前記カレントミラー回路を構成するトランジスタのゲートの電位を制御して前記カレントミラー回路に流れる電流量が増えるようにすることを特徴とする請求項 1 ~ 7 のいずれか 1 つに記載の定電圧発生回路。

**【発明の詳細な説明】**

**【技術分野】**

20

**【0001】**

この発明は、定電圧発生回路に関し、特に、電源電圧に基づいて所定の基準電圧を発生し、その基準電圧に基づいてレギュレート電圧を出力する定電圧発生回路に関する。

**【背景技術】**

**【0002】**

従来より、時計用 I C のように、消費電流が少ない、すなわち低電力であるという特性が求められるシステムでは、内部回路用の電源として、定電圧発生回路（レギュレータ）が用いられている。定電圧発生回路は、外部より供給された電源電圧を降圧して、レギュレート電圧を発生する。時計用 I C 等の内部回路は、このレギュレート電圧により駆動される。また、このような定電圧発生回路は、アナログ的なバイアス電源として用いられることがある。

30

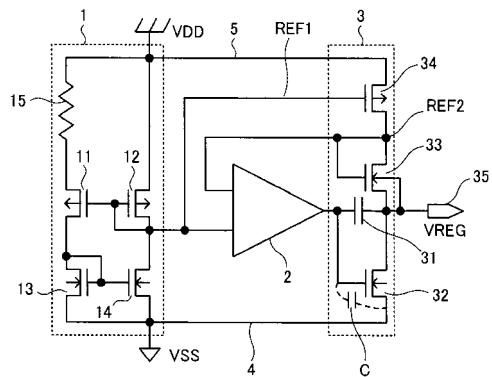

**【0003】**

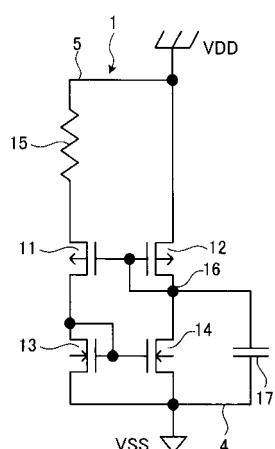

図 16 は、典型的な定電圧発生回路の構成を示す回路図である。図 16 に示すように、定電圧発生回路は、電源電圧に基づいて基準電圧発生源（バンドギャップリファレンス型）1 で基準電圧を発生し、差動アンプ 2 で電流增幅を行い、出力段 3 で所望の出力電圧となるように微調とフィードバック制御とを行う。電源電圧は、正の電源電位 V D D と負の電源電位 V S S との電位差で与えられる。正の電源ライン 5 には正の電源電位 V D D の電位が与えられており、負の電源ライン 4 には負の電源電位 V S S の電位が与えられている。一般に、時計用 I C の場合には、正の電源電位 V D D を接地電位とする負電源が用いられる。

40

**【0004】**

基準電圧発生源 1 は、カレントミラー回路を構成する 2 個の P チャネルの M O S トランジスタ（以下、P M O S トランジスタとする）1 1 , 1 2 および 2 個の N チャネルの M O S トランジスタ（以下、N M O S トランジスタとする）1 3 , 1 4 と抵抗 1 5 とを有する。第 1 の P M O S トランジスタ 1 1 のソースは、抵抗 1 5 の一端に接続されている。抵抗 1 5 の他端は、正の電源ライン 5 に接続している。第 1 の P M O S トランジスタ 1 1 のゲートは、第 2 の P M O S トランジスタ 1 2 のゲートおよびドレインと、第 2 の N M O S トランジスタ 1 4 のドレインとに接続されている。

**【0005】**

第 1 の P M O S トランジスタ 1 1 のドレインは、第 1 の N M O S トランジスタ 1 3 のド

50

レインおよびゲートと、第2のN MOSトランジスタ14のゲートとに接続されている。第2のPMOSトランジスタ12のソースは、正の電源ライン5に接続している。第1のN MOSトランジスタ13のソースおよび第2のN MOSトランジスタ14のソースは、負の電源ライン4に接続している。第2のPMOSトランジスタ12のドレインと第2のN MOSトランジスタ14のドレインとの接続ノードが、基準電圧発生源1の出力端子となり、ここから基準電圧として第1の電位REF1が出力される。

#### 【0006】

基準電圧発生源1の出力端子となるノードは、差動アンプ2の一方の入力端子と、出力段3とに接続されている。差動アンプ2の他方の入力端子および出力端子は、出力段3に接続されている。出力段3は、位相補償コンデンサ31、出力ドライブ用の第3のN MOSトランジスタ32、レギュレート電圧出力端子35の電位(レギュレート電圧VRREG)に所定の電位差(ここでは、N MOSトランジスタの正のしきい値Vth)を加算するための第4のN MOSトランジスタ33、および定電流源となる第3のPMOSトランジスタ34を有する。

#### 【0007】

差動アンプ2の出力端子は、位相補償コンデンサ31を介して、レギュレート電圧出力端子35と、第3のN MOSトランジスタ32のドレインと、第4のN MOSトランジスタ33のソースおよびバルクとに接続されている。また、差動アンプ2の出力端子は、第3のN MOSトランジスタ32のゲートに接続されている。第3のN MOSトランジスタ32のソースは、負の電源ライン4に接続されている。第4のN MOSトランジスタ33のドレインおよびゲートは、差動アンプ2の前記他方の入力端子と、第3のPMOSトランジスタ34のドレインとに接続されている。つまり、差動アンプ2の前記他方の入力端子には、第4のN MOSトランジスタ33のドレインから出力される第2の電位REF2が印加される。

#### 【0008】

第3のPMOSトランジスタ34のゲートは、基準電圧発生源1の出力端子となるノードに接続されている。つまり、第3のPMOSトランジスタ34のゲートには、第1の電位REF1が印加される。第3のPMOSトランジスタ34のソースは、正の電源ライン5に接続されている。以上のような構成により、差動アンプ2は、レギュレート電圧出力端子35の電位を、第1の電位REF1に第4のN MOSトランジスタ33の正のしきい値Vthを加算した電位に保つように動作する。この動作がレギュレータ動作である。

#### 【0009】

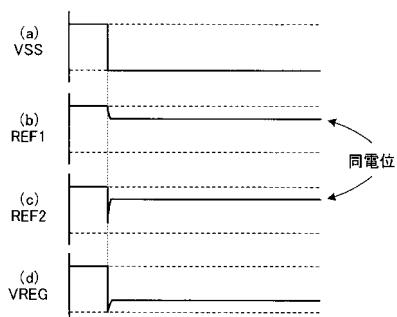

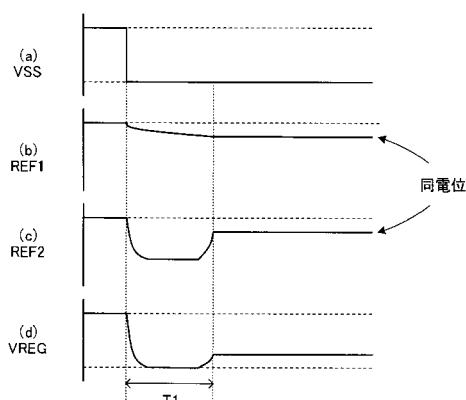

図16に示す定電圧発生回路の起動時の各部の電位変化を図17に示す。図17(b)に示すように、電源が投入されて負の電源ライン4の電位が負の電源電位VSSになる(図17(a))と、第1の電位REF1は、正の電源電位VDDから徐々に負の電源電位VSS側へ変位し、電源投入時から期間T1が経過した後に、一定電位で安定する。また、図17(c)に示すように、第2の電位REF2は、一旦、負の電源電位VSS側に引かれた後、第1の電位REF1の安定電位と同じ電位で安定する。第1の電位REF1と第2の電位REF2とが同じ電位で安定した状態になると、図17(d)に示すように、レギュレート電圧VRREGが安定した電位となる。

#### 【0010】

レギュレート電圧VRREGの電位が安定するまでの過渡期の動作を詳細に説明すると、次のようになる。電源投入直後では、位相補償コンデンサ31と第3のN MOSトランジスタ32とのゲート-バルク容量Cが無電荷状態である。そのため、レギュレート電圧VRREGの電位には、ほぼ負の電源電位VSSが現れる(図17(d))。また、電源投入直後では、第3のPMOSトランジスタ34のゲートバイアス(第1の電位REF1)が浅い。そのため、第3のPMOSトランジスタ34の電流供給能力は僅かであり、位相補償コンデンサ31と第3のN MOSトランジスタ32とのゲート-バルク容量Cを急速に充電することができない。

#### 【0011】

10

20

30

40

50

従って、レギュレート電圧 V<sub>REG</sub> がほぼ電源電圧となる期間 T<sub>1</sub> が存在する。基準電圧発生源 1 の出力電位（第 1 の電位 R<sub>EF1</sub>）が安定して、第 3 の PMOS トランジスタ 3<sub>4</sub> が所定の電流供給能力を得ると、位相補償コンデンサ 3<sub>1</sub> と第 3 の NMOS トランジスタ 3<sub>2</sub> とのゲート - バルク容量 C が充電される。それによって、レギュレート電圧 V<sub>REG</sub> の電位が所望の電位となる。上述したように、図 16 に示す構成の定電圧発生回路では、その起動性は、基準電圧発生源 1 の起動性に依存している。特に、低消費電流特性が要求される時計用 IC の場合には、基準電圧発生源 1 が、高抵抗の抵抗 1<sub>5</sub> と、高インピーダンス化（チャネル長 L が大きい）された MOS トランジスタ 1<sub>1</sub>, 1<sub>2</sub>, 1<sub>3</sub>, 1<sub>4</sub> とにより構成されるため、動作電流が小さく、安定動作点に収束するまでの時間（期間 T<sub>1</sub>）が長くなる。

10

#### 【0012】

この期間 T<sub>1</sub> は、MOS トランジスタ 1<sub>1</sub>, 1<sub>2</sub>, 1<sub>3</sub>, 1<sub>4</sub> のしきい値 V<sub>th</sub>、環境温度および印加する負の電源電位 V<sub>SS</sub> の値によっても変動するが、室温で数百ミリ秒程度であり、低温では数～数十秒になることもある。従って、図 16 に示す構成の定電圧発生回路を内部回路用の電源として用いる場合には、レギュレート電圧 V<sub>REG</sub> がほぼ電源電圧と等しくなっているから起動時の消費電流が増大するという問題点がある。また、この定電圧発生回路をアナログ的なバイアス電源として用いる場合には、少なくとも期間 T<sub>1</sub> においては適切なバイアス電圧を供給することができないため、誤動作の原因となるという問題点がある。

20

#### 【0013】

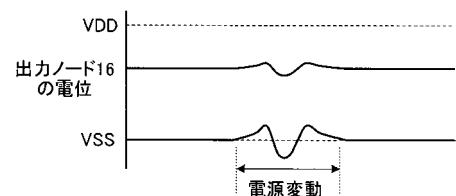

これらの問題点は、電源投入直後に基準電圧発生源 1 に流れる電流を一時的に増加させ、安定動作点への収束を加速することによって解決することができる。そこで、本出願人は、先に、基準電圧発生源 1 の起動性を改善するための考案を提案している（例えば、特許文献 1 参照。）。この考案では、図 18 に示すように、基準電圧発生源 1 の出力端子となる出力ノード 1<sub>6</sub> と負の電源ライン 4 との間にコンデンサ 1<sub>7</sub> が接続されている。電源投入時には、コンデンサ 1<sub>7</sub> は、無電荷状態である。そのため、出力ノード 1<sub>6</sub> は、強制的に負の電源電位 V<sub>SS</sub> に引かれる。それによって、基準電圧発生源 1 に一時的に多くの電流が流れ、短時間で安定動作点に収束する。

#### 【0014】

【特許文献 1】登録実用新案第 2594470 号公報

30

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0015】

しかしながら、その後、上記考案には、以下のような問題点のあることが判明した。例えば、太陽電池システムにより駆動されるソーラー時計のように、発電素子によって二次電池に蓄電された電源を用いてシステムを駆動する場合、発電量によって電源電圧が変動する。このようなシステムに上記考案を適用した場合、図 19 に示すように、負の電源電位 V<sub>SS</sub> が変動すると、コンデンサ 1<sub>7</sub> の充電電圧が保持されるので、基準電圧発生源 1 の出力ノード 1<sub>6</sub> の電位が電源変動に追従してしまう。そのため、電源変動に対する安定性が低い。一方、コンデンサ 1<sub>7</sub> の容量を小さくすれば、電源変動の影響を緩和させることができるが、その場合には、起動性改善の効果が十分に得られない。

40

#### 【0016】

この発明は、上述した従来技術による問題点を解消するため、電源変動の影響がなく、かつ電源投入直後から安定したレギュレート電圧を出力することが可能な定電圧発生回路を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0017】

上述した課題を解決し、目的を達成するため、請求項 1 の発明にかかる定電圧発生回路は、電源電圧を降圧して得られたレギュレート電圧を出力する定電圧発生回路であって、電源電圧に基づいて、レギュレート電圧を生成するための基準電圧を発生する基準電圧発

50

生源と、一方の入力端子に前記基準電圧発生源の出力電位が入力され、他方の入力端子に、レギュレート電圧出力端子の電位に所定の電位差を加算した電位が入力され、前記レギュレート電圧出力端子の電位を、前記2つの入力端子に入力される電位に基づいて一定に保つように動作する差動アンプと、電源投入直後の一定期間、前記基準電圧発生源の出力端子の電流量が増えるように前記基準電圧発生源の出力電位を制御する基準電圧制御手段と、を備えることを特徴とする。

【0018】

請求項2の発明にかかる定電圧発生回路は、請求項1に記載の発明において、前記基準電圧制御手段は、前記基準電圧発生源の出力端子を差動アンプの前記他方の入力端子に接続可能なスイッチ手段を含むことを特徴とする。

10

【0019】

請求項3の発明にかかる定電圧発生回路は、請求項2に記載の発明において、前記基準電圧制御手段は、電源投入直後の一定期間だけ前記スイッチ手段を閉状態にするスイッチ制御手段をさらに有することを特徴とする。

【0020】

請求項4の発明にかかる定電圧発生回路は、請求項1に記載の発明において、前記基準電圧制御手段は、前記基準電圧発生源の出力端子を負の電源ラインに接続可能なことを特徴とする。

20

【0021】

請求項5の発明にかかる定電圧発生回路は、請求項1に記載の発明において、前記基準電圧制御手段は、前記基準電圧発生源の出力端子を定電圧発生回路の出力に接続可能なことを特徴とする。

【0022】

請求項6の発明にかかる定電圧発生回路は、請求項1に記載の発明において、前記基準電圧制御手段は、前記基準電圧発生源の出力電位に基づいてオン状態とオフ状態との切り替えが制御されるNチャネルのトランジスタを含むことを特徴とする。

【0023】

請求項7の発明にかかる定電圧発生回路は、請求項1に記載の発明において、前記基準電圧制御手段は、差動アンプの前記他方の入力端子に入力される電位に基づいてオン状態とオフ状態との切り替えが制御されるPチャネルのトランジスタを含むことを特徴とする。

30

【0024】

請求項8の発明にかかる定電圧発生回路は、請求項1～7のいずれか1つに記載の発明において、前記基準電圧発生源は、カレントミラー回路を含み、前記基準電圧制御手段は、前記カレントミラー回路を構成するトランジスタのゲートの電位を制御して前記カレントミラー回路に流れる電流量が増えるようにすることを特徴とする。

【0025】

上記の構成によれば、電源投入直後の一定期間、差動アンプの2つの入力端子を短絡することによって、直ちに所望の安定したレギュレート電圧が出力されるとともに、基準電圧発生源に含まれるカレントミラー回路に流れる電流量が増えるので、短時間で基準電圧発生源の出力電位が所望の電位に安定する。また、基準電圧発生源の出力端子と負の電源ラインとの間にコンデンサが接続されないので、基準電圧発生源の出力が電源変動の影響を受けずに済む。従って、レギュレート電圧が安定する。

40

【発明の効果】

【0044】

本発明にかかる定電圧発生回路によれば、電源変動の影響を受けることなく、電源投入直後から安定したレギュレート電圧を出力することができるという効果を奏する。

【発明を実施するための最良の形態】

【0045】

以下に添付図面を参照して、この発明にかかる定電圧発生回路の好適な実施の形態を詳

50

細に説明する。特に限定しないが、ここでは、図16に示す典型的な定電圧発生回路に本発明を適用した例について説明する。従って、以下の各実施の形態において、図16に示す構成と同一の構成については、同一の符号を付して説明を省略する。

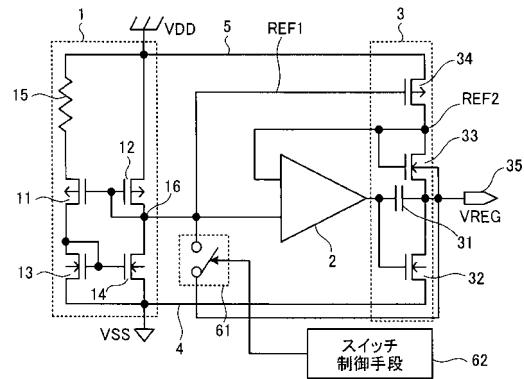

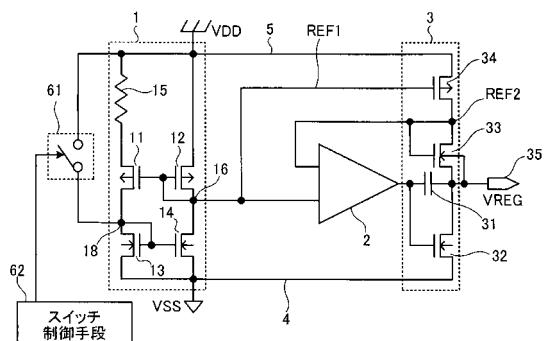

【0046】

実施の形態1.

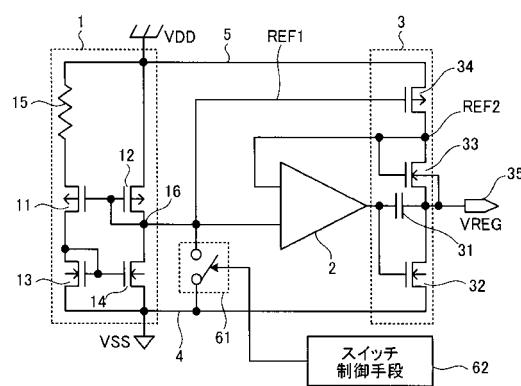

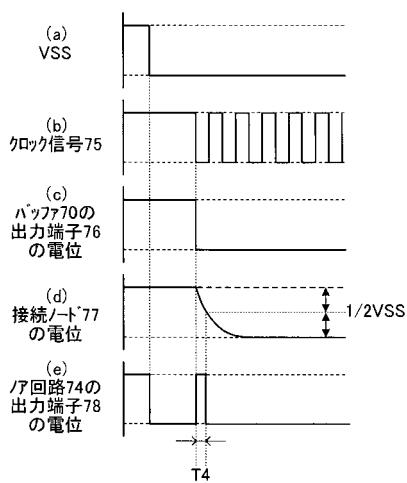

図1は、実施の形態1の定電圧発生回路の構成を示す回路図である。図1に示すように、実施の形態1は、従来同様の定電圧発生回路にスイッチ手段61と、スイッチ手段61の開閉制御を行うスイッチ制御手段62とを設けたものである。スイッチ手段61は、基準電圧発生源1のカレントミラー回路を構成する第1および第2のPMOSトランジスタ11, 12の各ゲート、すなわち基準電圧発生源1の出力端子となる出力ノード16と、負の電源ライン4との間に接続されている。

10

【0047】

スイッチ制御手段62は、電源投入直後に瞬間にスイッチ手段61を開（オン）状態にする制御信号を出力する。それによって、スイッチ手段61は、電源投入直後の一定期間だけ閉状態となり、その後、開（オフ）状態となる。スイッチ手段61は、例えば、MOSトランジスタにより構成される。スイッチ制御手段62の構成については、後述する。

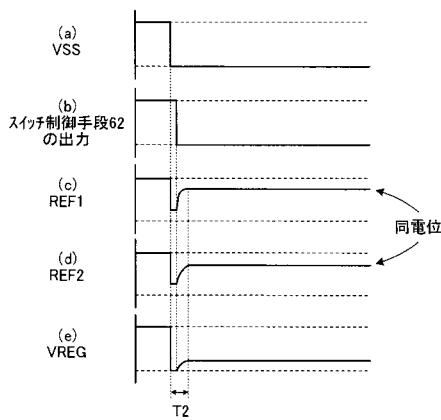

【0048】

図2は、図1に示す定電圧発生回路の起動時の各部の電位変化を示す波形図である。図2(b)に示すように、スイッチ制御手段62の出力電位は、電源が投入されて負の電源ライン4の電位が負の電源電位VSSになる（図2(a)）と同時に、スイッチ手段61を開状態にする電位（図示例では、正の電源電位VDD）となる。その後、一定期間、例えば、システムクロックの1パルス分のようなくるめて短い期間が経過した後に、スイッチ制御手段62の出力電位は、スイッチ手段61を開状態にする電位（図示例では、負の電源電位VSS）となる。

20

【0049】

図2(c)に示すように、第1の電位REF1は、スイッチ制御手段62の出力電位の変化に応じて、電源投入直後に、一時的に負の電源電位VSS側に引かれる。それによって、スイッチ手段61が閉状態となる。スイッチ手段61が閉じている間、第1のPMOSトランジスタ11のゲート電位および第2のPMOSトランジスタ12のゲート電位が負の電源電位VSS側に引かれるので、カレントミラー回路に流れる電流量が増える。その後、スイッチ制御手段62の出力電位がスイッチ手段61を開状態にする電位に変位する。これ以降、スイッチ手段61は開状態となる。それによって、第1の電位REF1は、徐々に正の電源電位VDD側へ変位し、電源投入から期間T2が経過した後に、一定電位で安定する。期間T2には、スイッチ手段61が閉（オン）状態の時間も含まれる。しかしながら、この時間は前述の通り極めて短いために、第1の電位REF1が安定する時間には影響しない。

30

【0050】

同様に、第2の電位REF2は、図2(d)に示すように、一旦、負の電源電位VSS側に引かれた後、徐々に正の電源電位VDD側へ変位し、期間T2の経過後に、第1の電位REF1の安定電位と同じ電位で安定する。第1の電位REF1と第2の電位REF2とが同じ電位で安定した状態になると、図2(e)に示すように、レギュレート電圧VR EGが安定した電位となる。つまり、レギュレート電圧VR EGは、電源投入後、期間T2が経過した時点で安定する。この期間T2は、従来の期間T1に比べて極めて短く、例えば、室温で1ミリ秒程度であり、この値は低温でもほとんど変化しない。

40

【0051】

上述したように、電源投入直後の一定期間、第1のPMOSトランジスタ11のゲート電位および第2のPMOSトランジスタ12のゲート電位は、スイッチ手段61およびスイッチ制御手段62により制御される。従って、スイッチ手段61およびスイッチ制御手段62は、ゲート制御手段としての機能を有する。また、スイッチ手段61とスイッチ制

50

御手段 6 2 とは、電源投入直後の一定期間、基準電圧発生源 1 の出力端子となる出力ノード 1 6 を負の電源ライン 4 に接続するので、基準電圧制御手段としての機能を有する。

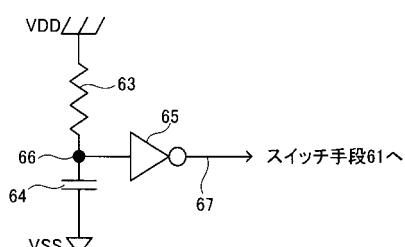

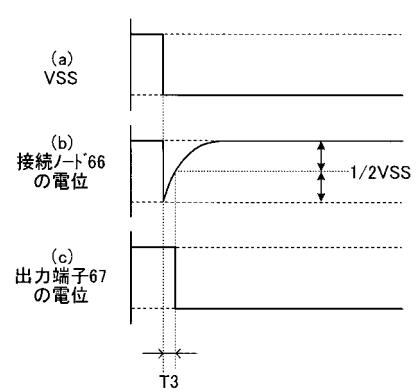

【 0 0 5 2 】

図 3 は、スイッチ制御手段 6 2 の第 1 の例を示す回路図である。図 3 に示すように、この第 1 の例は、抵抗 6 3、コンデンサ 6 4 およびインバータ 6 5 により構成されている。抵抗 6 3 とコンデンサ 6 4 とは、正の電源電位 V DD と負の電源電位 V SS との間に、直列に接続されている。インバータ 6 5 の入力端子は、抵抗 6 3 とコンデンサ 6 4 との接続ノード 6 6 に接続されている。インバータ 6 5 の出力端子 6 7 からは、スイッチ手段 6 1 の開閉を制御する制御信号が出力される。

【 0 0 5 3 】

図 4 は、図 3 に示すスイッチ制御手段 6 2 の起動時の電位変化を示す波形図である。図 4 ( b ) に示すように、接続ノード 6 6 の電位は、電源が投入されて負の電源ライン 4 の電位が負の電源電位 V SS になる ( 図 4 ( a ) ) と同時に、負の電源電位 V SS となる。その後、接続ノード 6 6 の電位は、徐々に正の電源電位 V DD 側へ変位する。

【 0 0 5 4 】

図 4 ( c ) に示すように、インバータ 6 5 の出力端子 6 7 の電位は、電源投入後、接続ノード 6 6 の電位が電源電圧の 2 分の 1 ( V SS / 2 ) に達するまでは正の電源電位 V DD であり、接続ノード 6 6 の電位が電源電圧の 2 分の 1 ( V SS / 2 ) よりも正の電源電位 V DD 側になると、負の電源電位 V SS になる。スイッチ手段 6 1 は、電源投入から、インバータ 6 5 の出力端子 6 7 の電位が正の電源電位 V DD から負の電源電位 V SS に反転するまでの期間 T 3 の間、閉状態となる。

【 0 0 5 5 】

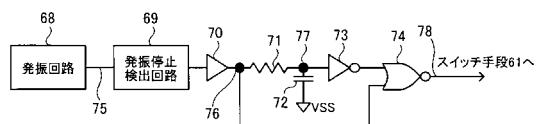

図 5 は、スイッチ制御手段 6 2 の第 2 の例を示す回路図である。図 5 に示すように、この第 2 の例は、発振回路 6 8 、発振停止検出回路 6 9 、バッファ 7 0 、抵抗 7 1 、コンデンサ 7 2 、インバータ 7 3 およびノア回路 7 4 により構成されている。発振回路 6 8 は、このスイッチ制御手段 6 2 を含むシステムのクロック信号 7 5 を出力する。発振停止検出回路 6 9 は、発振回路 6 8 に接続されており、発振回路 6 8 からのクロック信号 7 5 の出力が停止したこと、換言すれば、発振回路 6 8 が発振していることを検出する。

【 0 0 5 6 】

バッファ 7 0 の入力端子は、発振停止検出回路 6 9 に接続されている。バッファ 7 0 の出力端子 7 6 は、ノア回路 7 4 の一方の入力端子に接続されている。また、バッファ 7 0 の出力端子 7 6 は、抵抗 7 1 の一端に接続されている。抵抗 7 1 の他端は、インバータ 7 3 の入力端子に接続されている。抵抗 7 1 とインバータ 7 3 との接続ノード 7 7 と、負の電源電位 V SS との間には、コンデンサ 7 2 が接続されている。インバータ 7 3 の出力端子は、ノア回路 7 4 のもう一方の入力端子に接続されている。ノア回路 7 4 の出力端子 7 8 からは、スイッチ手段 6 1 の開閉を制御する制御信号が出力される。

【 0 0 5 7 】

図 6 は、図 5 に示すスイッチ制御手段 6 2 の起動時の電位変化を示す波形図である。図 6 ( b ) に示すように、発振回路 6 8 は、電源が投入されて負の電源ライン 4 の電位が負の電源電位 V SS になった ( 図 6 ( a ) ) 後、しばらくしてから発振を開始し、クロック信号 7 5 を出力する。図 6 ( c ) に示すように、クロック信号 7 5 が出力されると、発振停止検出回路 6 9 から出力される検出信号の電位が反転し、バッファ 7 0 の出力端子 7 6 の電位が正の電源電位 V DD から負の電源電位 V SS になる。

【 0 0 5 8 】

抵抗 7 1 およびコンデンサ 7 2 により遅延回路が構成されているため、図 6 ( d ) に示すように、抵抗 7 1 とインバータ 7 3 ( コンデンサ 7 2 ) との接続ノード 7 7 の電位は、バッファ 7 0 の出力端子 7 6 の電位変化から遅れて、正の電源電位 V DD から徐々に負の電源電位 V SS へ変位する。図 6 ( e ) に示すように、ノア回路 7 4 の出力端子 7 8 の電位は、電源投入後に負の電源電位 V SS となる。その後、発振回路 6 8 の発振が開始され、抵抗 7 1 とインバータ 7 3 との接続ノード 7 7 の電位が負の電源電位 V SS 側に引かれ

10

20

30

40

50

始める同時に、ノア回路 74 の出力端子 78 の電位は、正の電源電位 VDD となる。

【0059】

そして、ノア回路 74 の出力端子 78 の電位は、接続ノード 77 の電位が電源電圧の 2 分の 1 (VSS/2) に達するまでは正の電源電位 VDD のままであり、接続ノード 77 の電位が電源電圧の 2 分の 1 (VSS/2) よりも負の電源電位 VSS 側になると、負の電源電位 VSS となる。つまり、スイッチ制御手段 62 からワンショットのパルスが発生する。スイッチ手段 61 は、このワンショットのパルスが発生している期間 T4 の間、閉状態となる。

【0060】

実施の形態 2 .

10

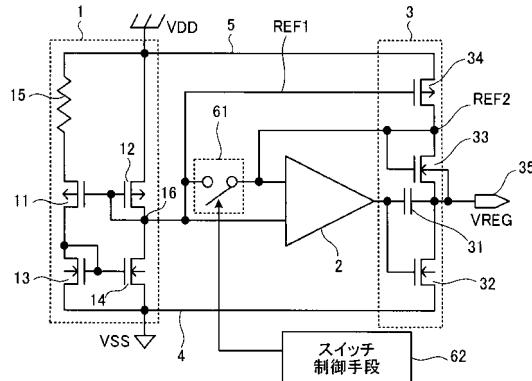

図 7 は、実施の形態 2 の定電圧発生回路の構成を示す回路図である。図 7 に示すように、実施の形態 2 は、実施の形態 1 と同様のスイッチ手段 61 を第 1 および第 2 の PMOS ドラゴンジスタ 11, 12 の各ゲート (出力ノード 16) とレギュレート電圧出力端子 35 との間に設け、実施の形態 1 と同様のスイッチ制御手段 62 によりスイッチ手段 61 の開閉制御を行うものである。図 7 に示す定電圧発生回路の起動時の各部の電位変化は、実施の形態 1 と同じであり、その波形図は図 2 に示す通りである。

【0061】

実施の形態 2 では、実施の形態 1 と同様に、スイッチ手段 61 およびスイッチ制御手段 62 は、ゲート制御手段としての機能を有する。また、スイッチ手段 61 とスイッチ制御手段 62 とは、電源投入直後の一定期間、基準電圧発生源 1 の出力端子となる出力ノード 16 をレギュレート電圧出力端子 35 に接続するので、基準電圧制御手段としての機能を有する。実施の形態 2 には、スイッチ手段 61 を MOS ドラゴンジスタで構成した場合に、その MOS ドラゴンジスタがオフ状態であるときのリーク電流が実施の形態 1 よりも少ないという利点がある。その理由は、レギュレート電圧 VREG が負の電源電位 VSS よりも低いので、安定状態、すなわち、その MOS ドラゴンジスタがオフ状態であるときのリーク電流が少ないためである。

20

【0062】

実施の形態 3 .

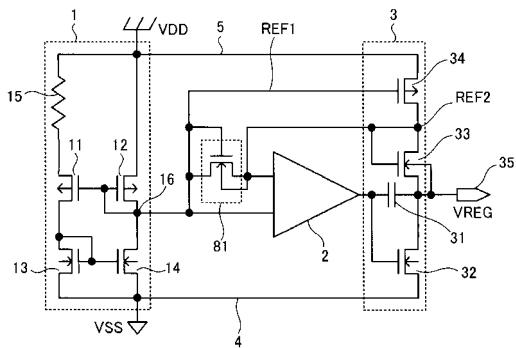

図 8 は、実施の形態 3 の定電圧発生回路の構成を示す回路図である。図 8 に示すように、実施の形態 3 は、実施の形態 1 と同様のスイッチ手段 61 を差動アンプ 2 の二つの入力端子の間に設け、実施の形態 1 と同様のスイッチ制御手段 62 によりスイッチ手段 61 の開閉制御を行うものである。

30

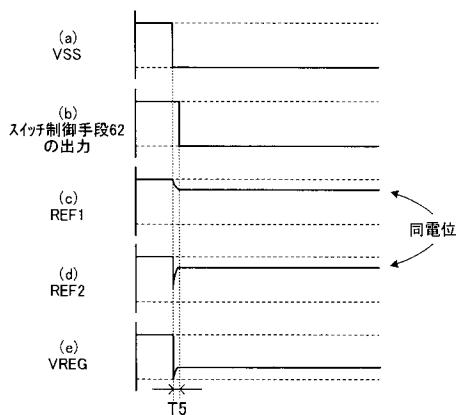

【0063】

図 9 は、図 8 に示す定電圧発生回路の起動時の各部の電位変化を示す波形図である。図 9 (b) に示すように、スイッチ制御手段 62 の出力電位は、電源が投入されて負の電源ライン 4 の電位が負の電源電位 VSS になる (図 9 (a)) と同時に、スイッチ手段 61 を閉状態にする電位 (図示例では、正の電源電位 VDD) となる。その後、一定期間、例えば、システムクロックの 1 パルス分のような極めて短い期間が経過した後に、スイッチ制御手段 62 の出力電位は、スイッチ手段 61 を開状態にする電位 (図示例では、負の電源電位 VSS) となる。

40

【0064】

図 9 (c) に示すように、第 1 の電位 REF1 は、電源投入直後に、第 2 の電位 REF2 に引かれる。それによって、カレントミラー回路に流れる電流量が増える。そして、第 1 の電位 REF1 は、正の電源電位 VDD から負の電源電位 VSS 側に急速に変位して、電源投入から期間 T5 が経過した後に、一定電位で安定する。一方、図 9 (d) に示すように、第 2 の電位 REF2 は、電源投入直後に、一旦、負の電源電位 VSS 側に引かれた後、急速に正の電源電位 VDD 側へ変位し、期間 T5 の経過後に、第 1 の電位 REF1 の安定電位と同じ電位で安定する。スイッチ手段 61 は、電源投入から期間 T5 が経過するまでは閉状態となり、期間 T5 の経過後は開状態となる。

【0065】

50

第1の電位REF1と第2の電位REF2とが同じ電位で安定した状態になると、図9(e)に示すように、レギュレート電圧VREGが安定した電位となる。つまり、レギュレート電圧VREGは、電源投入後、期間T5が経過した時点で安定する。この期間T5は、従来の期間T1に比べて極めて短く、例えば、室温で1ミリ秒程度であり、この値は、低温でもほとんど変化しない。

#### 【0066】

実施の形態3では、実施の形態1と同様に、スイッチ手段61およびスイッチ制御手段62は、ゲート制御手段としての機能を有する。また、スイッチ手段61とスイッチ制御手段62とは、電源投入直後の一定期間、基準電圧発生源1の出力端子となる出力ノード16を差動アンプ2の、第2の電位REF2が入力される入力端子に接続するので、基準電圧制御手段としての機能を有する。

10

#### 【0067】

実施の形態4。

図10は、実施の形態4の定電圧発生回路の構成を示す回路図である。図10に示すように、実施の形態4は、実施の形態1と同様のスイッチ手段61を第1および第2のNMOSトランジスタ13, 14の各ゲート(基準電圧発生源1の前記出力ノード16と対をなすもう一つの出力ノード18)と正の電源ライン5との間に設け、実施の形態1と同様のスイッチ制御手段62によりスイッチ手段61の開閉制御を行うものである。実施の形態4では、電源投入直後に、基準電圧発生源1のもう一つの出力ノード18が、一時的に正の電源電位VDD側に引かれるので、第1および第2のNMOSトランジスタ13, 14がオン状態となり、カレントミラー回路に流れる電流量が増える。

20

#### 【0068】

従って、図10に示す定電圧発生回路の起動時の各部の電位変化は、実施の形態1と同じであり、その波形図は図2に示す通りである。実施の形態4では、実施の形態1と同様に、スイッチ手段61およびスイッチ制御手段62は、ゲート制御手段としての機能を有する。また、スイッチ手段61とスイッチ制御手段62とは、電源投入直後の一定期間、基準電圧発生源1のもう一方の出力ノード18を正の電源ライン5に接続するので、基準電圧制御手段としての機能を有する。

#### 【0069】

実施の形態5。

30

図11は、実施の形態5の定電圧発生回路の構成を示す回路図である。図11に示すように、実施の形態5は、実施の形態3において、スイッチ手段61をNMOSトランジスタ81で構成し、このNMOSトランジスタ81のオン状態とオフ状態との切り替えを定電圧発生回路内の信号により制御するようにしたものである。従って、実施の形態5では、スイッチ制御手段62は設けられていない。

#### 【0070】

NMOSトランジスタ81のゲートおよびドレインは、基準電圧発生源1の出力ノード16に接続されている。NMOSトランジスタ81のソースおよびバルクは、差動アンプ2の前記他方の入力端子に接続されている。つまり、NMOSトランジスタ81のゲートおよびドレインには、第1の電位REF1が印加され、そのソースおよびバルクには、第2の電位REF2が印加される。

40

#### 【0071】

図12は、図11に示す定電圧発生回路の起動時の各部の電位変化を示す波形図である。図12(a)に示すように、電源が投入されて負の電源ライン4の電位が負の電源電位VSSになった時点では、図12(b)および(c)に示すように、第1の電位REF1と第2の電位REF2とには電位差が存在する。この電位差がある間、NMOSトランジスタ81がオン状態となり、第1の電位REF1が第2の電位REF2に引き下げられるので、カレントミラー回路に流れる電流量が増える。

#### 【0072】

そして、第1の電位REF1と第2の電位REF2とが同じ電位で安定した状態になる

50

と、図12(d)に示すように、レギュレート電圧VREGが安定した電位となる。この安定状態になるまでに要する時間は、従来の期間T1に比べて極めて短く、例えば、室温で1ミリ秒程度であり、低温で10ミリ秒程度である。また、安定状態になると、第1の電位REF1と第2の電位REF2とが同電位になるので、NMOSトランジスタ81はオフ状態となる。従って、貫通電流が流れたり、レギュレート電圧VREGに影響を及ぼすなどの不都合は、一切ない。

#### 【0073】

実施の形態5では、電源投入直後の一定期間、第1のPMOSトランジスタ11のゲート電位および第2のPMOSトランジスタ12のゲート電位は、NMOSトランジスタ81により制御される。従って、NMOSトランジスタ81は、ゲート制御手段としての機能を有する。また、NMOSトランジスタ81は、電源投入直後の一定期間、基準電圧発生源1の出力端子となる出力ノード16を差動アンプ2の、第2の電位REF2が入力される入力端子に接続するので、基準電圧制御手段としての機能を有する。

10

#### 【0074】

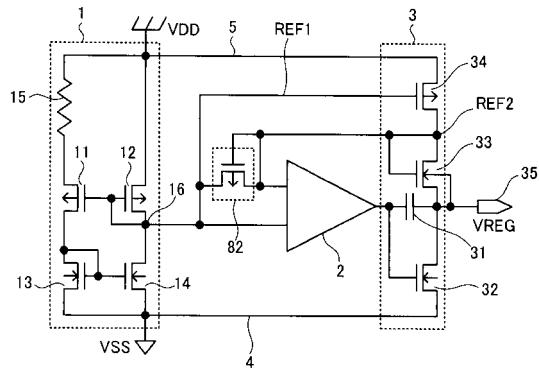

実施の形態6.

図13は、実施の形態6の定電圧発生回路の構成を示す回路図である。図13に示すように、実施の形態6は、実施の形態3において、スイッチ手段61をPMOSトランジスタ82で構成し、このPMOSトランジスタ82のオン状態とオフ状態との切り替えを定電圧発生回路内の信号により制御するようにしたものである。従って、実施の形態6では、スイッチ制御手段62は設けられていない。

20

#### 【0075】

PMOSトランジスタ82のソースは、基準電圧発生源1の出力ノード16に接続されている。PMOSトランジスタ82のゲートおよびドレインは、差動アンプ2の前記他方の入力端子に接続されている。バルクは、正の電源ライン5もしくは基準電圧発生源1の出力ノード16のどちらかに接続する。つまり、PMOSトランジスタ82のソースには、第1の電位REF1が印加され、そのゲートおよびドレインには、第2の電位REF2が印加され、そのバルクには、正の電源電位VDDもしくは第1の電位REF1が印加される。バルクを正の電源ライン5に接続し、VDDの電位にした場合、起動後は、PMOSトランジスタ82にバックゲートがかかるので、このトランジスタはONしにくくなる。PMOSトランジスタ82は、電源投入直後の一定期間のみオンさせたいので、役目を終えた起動後にオンしにくくなつて都合がよい。後述する実施の形態7および8におけるPMOSトランジスタ83、84においても同様である。図13に示す定電圧発生回路の起動時の各部の電位変化は、実施の形態5と同じであり、その波形図は図12に示す通りである。

30

#### 【0076】

実施の形態6では、電源投入直後の一定期間、第1のPMOSトランジスタ11のゲート電位および第2のPMOSトランジスタ12のゲート電位は、PMOSトランジスタ82により制御される。従って、PMOSトランジスタ82は、ゲート制御手段としての機能を有する。また、PMOSトランジスタ82は、電源投入直後の一定期間、基準電圧発生源1の出力端子となる出力ノード16を差動アンプ2の、第2の電位REF2が入力される入力端子に接続するので、基準電圧制御手段としての機能を有する。

40

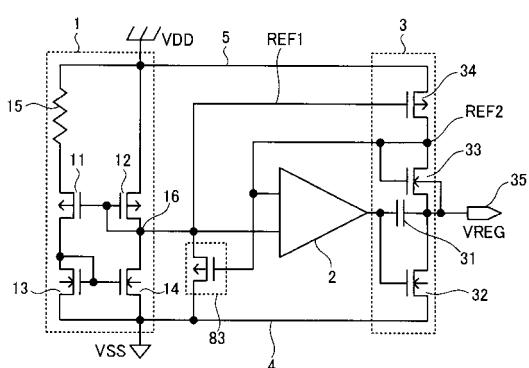

#### 【0077】

実施の形態7.

図14は、実施の形態7の定電圧発生回路の構成を示す回路図である。図14に示すように、実施の形態7は、実施の形態1において、スイッチ手段61をPMOSトランジスタ83で構成し、このPMOSトランジスタ83のオン状態とオフ状態との切り替えを定電圧発生回路内の信号により制御するようにしたものである。従って、実施の形態7では、スイッチ制御手段62は設けられていない。

#### 【0078】

PMOSトランジスタ83のソース、ゲートおよびドレインは、それぞれ、基準電圧発

50

生源 1 の出力ノード 16、差動アンプ 2 の前記他方の入力端子および負の電源ライン 4 に接続されている。なお、バルクは、正の電源ライン 5 もしくは基準電圧発生源 1 の出力ノード 16 のどちらかに接続する。つまり、PMOSトランジスタ 83 のソースには、第1の電位REF1が印加され、そのゲートには、第2の電位REF2が印加され、そのドレインには、負の電源電位VSSが印加され、そのバルクには、正の電源電位VDDもしくは第1の電位REF1が印加される。図14に示す定電圧発生回路の起動時の各部の電位変化は、実施の形態5と同じであり、その波形図は図12に示す通りである。

#### 【0079】

実施の形態7では、電源投入直後の一定期間、第1のPMOSトランジスタ11のゲート電位および第2のPMOSトランジスタ12のゲート電位は、PMOSトランジスタ83により制御される。従って、PMOSトランジスタ83は、ゲート制御手段としての機能を有する。また、PMOSトランジスタ83は、電源投入直後の一定期間、基準電圧発生源1の出力端子となる出力ノード16を負の電源ライン4に接続するので、基準電圧制御手段としての機能を有する。実施の形態7には、スイッチ手段61がNMOSトランジスタで構成されている場合に比べて、システムに接続される負荷への過電流などによって電源電圧に変動があった場合でも、その変動が第1の電位REF1に伝達されにくいという利点がある。

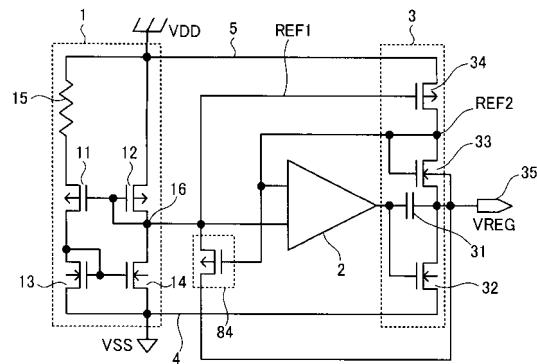

#### 【0080】

実施の形態8。

図15は、実施の形態8の定電圧発生回路の構成を示す回路図である。図15に示すように、実施の形態8は、実施の形態2において、スイッチ手段61をPMOSトランジスタ84で構成し、このPMOSトランジスタ84のオン状態とオフ状態との切り替えを定電圧発生回路内の信号により制御するようにしたものである。従って、実施の形態8では、スイッチ制御手段62は設けられていない。

#### 【0081】

PMOSトランジスタ84のソース、ゲートおよびドレインは、それぞれ、基準電圧発生源1の出力ノード16、差動アンプ2の前記他方の入力端子およびレギュレート電圧出力端子35に接続されている。バルクは、正の電源ライン5もしくは基準電圧発生源1の出力ノード16のどちらかに接続する。つまり、PMOSトランジスタ84のソースには、第1の電位REF1が印加され、そのゲートには、第2の電位REF2が印加され、そのドレインには、レギュレート電圧VREGの電位が印加され、そのバルクには、正の電源電位VDDもしくは第1の電位REF1が印加される。図15に示す定電圧発生回路の起動時の各部の電位変化は、実施の形態5と同じであり、その波形図は図12に示す通りである。

#### 【0082】

実施の形態8では、電源投入直後の一定期間、第1のPMOSトランジスタ11のゲート電位および第2のPMOSトランジスタ12のゲート電位は、PMOSトランジスタ84により制御される。従って、PMOSトランジスタ84は、ゲート制御手段としての機能を有する。また、PMOSトランジスタ84は、電源投入直後の一定期間、基準電圧発生源1の出力端子となる出力ノード16をレギュレート電圧出力端子35に接続するので、基準電圧制御手段としての機能を有する。実施の形態8には、レギュレート電圧VREGが負の電源電位VSSよりも低いので、安定状態、すなわちPMOSトランジスタ84がオフ状態であるときのPMOSトランジスタ84のリーク電流が、実施の形態7のPMOSトランジスタ83のリーク電流よりも少ないという利点がある。

#### 【0083】

以上説明したように、各実施の形態によれば、電源を投入した後、短時間で基準電圧発生源1の出力電位REF1が所望の電位で安定するので、直ちに所望の安定したレギュレート電圧VREGが出力されるという効果を奏する。また、基準電圧発生源1の出力端子となる出力ノード16と負の電源ライン4との間にコンデンサが接続されないので、基準電圧発生源1の出力が電源変動の影響を受けずに済む。従って、レギュレート電圧VREG

10

20

30

40

50

G が安定するという効果を奏する。また、各実施の形態は、電源電圧が例えば 3 V 程度であり、その半分程度のレギュレート電圧 V R E G で駆動される、低消費電力の小型電子機器の定電圧発生回路として有効であり、例えば時計に内蔵される定電圧発生回路に用いられる。

【 0 0 8 4 】

以上において、本発明は、上述した実施の形態に限らず、種々変更可能である。例えば、定電圧発生回路の基本的な構成は、図 1 6 に示す構成に限らない。スイッチ手段 6 1 は、MOSトランジスタに限らない。また、スイッチ制御手段 6 2 は、図 3 ~ 図 6 に示す構成に限らない。

【 産業上の利用可能性 】

10

【 0 0 8 5 】

以上のように、本発明にかかる定電圧発生回路は、電源電圧を降圧したレギュレート電圧で駆動される小型電子機器に有用であり、特に、例えばソーラー時計を含む時計全般に適している。

【 図面の簡単な説明 】

【 0 0 8 6 】

【図 1】実施の形態 1 の定電圧発生回路の構成を示す回路図である。

【図 2】図 1 に示す定電圧発生回路の起動時の電位変化を示す波形図である。

【図 3】スイッチ制御手段の第 1 の例を示す回路図である。

【図 4】図 3 に示すスイッチ制御手段の起動時の電位変化を示す波形図である。

20

【図 5】スイッチ制御手段の第 2 の例を示す回路図である。

【図 6】図 5 に示すスイッチ制御手段の起動時の電位変化を示す波形図である。

【図 7】実施の形態 2 の定電圧発生回路の構成を示す回路図である。

【図 8】実施の形態 3 の定電圧発生回路の構成を示す回路図である。

【図 9】図 8 に示す定電圧発生回路の起動時の電位変化を示す波形図である。

【図 10】実施の形態 4 の定電圧発生回路の構成を示す回路図である。

【図 11】実施の形態 5 の定電圧発生回路の構成を示す回路図である。

【図 12】図 1 1 に示す定電圧発生回路の起動時の電位変化を示す波形図である。

【図 13】実施の形態 6 の定電圧発生回路の構成を示す回路図である。

30

【図 14】実施の形態 7 の定電圧発生回路の構成を示す回路図である。

【図 15】実施の形態 8 の定電圧発生回路の構成を示す回路図である。

【図 16】典型的な定電圧発生回路の構成を示す回路図である。

【図 17】図 1 6 に示す定電圧発生回路の起動時の電位変化を示す波形図である。

【図 18】従来の起動性を改善した基準電圧発生源の構成を示す回路図である。

【図 19】図 1 8 に示す基準電圧発生源の出力ノードの電位変化を示す波形図である。

【 符号の説明 】

【 0 0 8 7 】

V D D 正の電源電位

V R E G レギュレート電圧

V S S 負の電源電位

40

1 基準電圧発生源

2 差動アンプ

4 負の電源ライン

5 正の電源ライン

1 1 , 1 2 , 1 3 , 1 4 カレントミラー回路を構成するトランジスタ

1 6 基準電圧発生源の出力端子となる出力ノード

3 5 レギュレート電圧出力端子

6 1 スイッチ手段、ゲート制御手段、基準電圧制御手段

6 2 スイッチ制御手段、ゲート制御手段、基準電圧制御手段

8 1 , 8 2 , 8 3 , 8 4 スイッチ手段となるトランジスタ

50

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図11】

【図12】

【図10】

【図13】

【 図 1 5 】

### 【図14】

【図16】

【図17】

【 四 1 8 】

〔 四 19 〕

---

フロントページの続き

(56)参考文献 特開平03-288217(JP, A)

特開2001-042960(JP, A)

特開2003-051187(JP, A)

特許第3561716(JP, B1)

特開平07-250437(JP, A)

特開2000-075947(JP, A)

実用新案登録第2594470(JP, Y2)

(58)調査した分野(Int.Cl., DB名)

G 05 F 3 / 24

H 03 F 3 / 343