(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4385268号

(P4385268)

(45) 発行日 平成21年12月16日(2009.12.16)

(24) 登録日 平成21年10月9日(2009.10.9)

(51) Int.Cl.

G 0 1 D 5/244 (2006.01)

F 1

G 0 1 D 5/244

J

請求項の数 4 (全 7 頁)

(21) 出願番号 特願2000-11070 (P2000-11070)

(22) 出願日 平成12年1月19日 (2000.1.19)

(65) 公開番号 特開2001-201367 (P2001-201367A)

(43) 公開日 平成13年7月27日 (2001.7.27)

審査請求日 平成18年11月13日 (2006.11.13)

(73) 特許権者 000006622

株式会社安川電機

福岡県北九州市八幡西区黒崎城石2番1号

(72) 発明者 勝田 信一

福岡県北九州市八幡西区黒崎城石2番1号

株式会社 安川

電機内

(72) 発明者 古谷 彰浩

福岡県北九州市八幡西区黒崎城石2番1号

株式会社 安川

電機内

審査官 岡田 卓弥

最終頁に続く

(54) 【発明の名称】エンコーダ信号処理回路とそのヒステレシス補償方法およびその方法を記録したコンピュータ用記録媒体

## (57) 【特許請求の範囲】

## 【請求項 1】

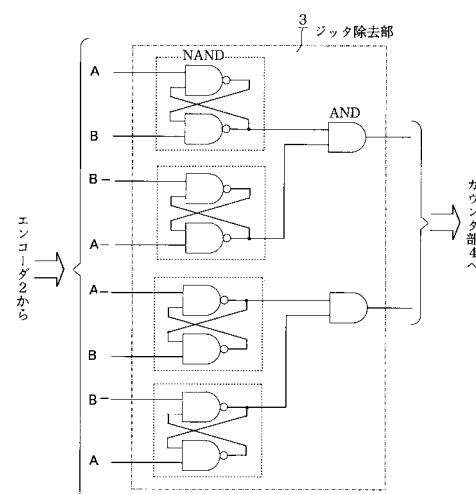

モータの回転によりエンコーダが出力する90度位相の異なる2相の矩形波信号と、この矩形波信号の反転信号を4組のRSフリップフロップの入力信号とし、前記4組のRSフリップフロップの出力のうち2組のRSフリップフロップの出力の論理積信号をとり、前記2組のRSフリップフロップとは異なる別の2組のRSフリップフロップの出力の論理積信号をとることにより、ジッタのない90度位相の異なる2相の矩形波信号を出力するジッタ除去回路と、前記ジッタ除去回路の出力である2相の矩形波信号のエッジをカウントするカウンタを備えたエンコーダ信号処理回路において、

前記カウンタのカウント値と記憶された前回カウント値の差分の符号がモータの反転によって変化したと判断したときは、前記カウント値に前記差分の符号に応じて+1もしくは-1を加えて出力することを特徴とするエンコーダ信号処理回路のヒステレシス補償方法。

## 【請求項 2】

今回のカウント値と前回カウント値の差分をとるとその差分がゼロか否かを判断し、ゼロであれば今回のカウント値を記憶して補正は行わず、次回のカウント値との差分をとる操作を繰り返し、

前記差分がゼロでなければ、前回の差分と符号が違うか否かを判断し、前記符号が違えば差分の符号に応じて、+1または-1を補正量として前記今回のカウント値に加えて出力する

10

20

ことを特徴とする請求項 1 記載の エンコーダ信号処理回路のヒステレシス補償方法。

【請求項 3】

モータの回転によりエンコーダが出力する 90 度位相の異なる 2 相の矩形波信号と、この矩形波信号の反転信号を 4 組の RS フリップフロップの入力信号とし、前記 4 組の RS フリップフロップの出力のうち 2 組の RS フリップフロップの出力の論理積信号をとり、前記 2 組の RS フリップフロップとは異なる別の 2 組の RS フリップフロップの出力の論理積信号をとることにより、ジッタのない 90 度位相の異なる 2 相の矩形波信号を出力するジッタ除去回路と、前記ジッタ除去回路の出力である 2 相の矩形波信号のエッジをカウントするカウンタを備えたエンコーダ信号処理回路において、

前記カウンタのカウント値と記憶された前回カウント値の差分の符号がモータの反転によって変化したと判断したときは、前記カウント値に前記差分の符号に応じて +1 もしくは -1 を加えて出力する補償演算部を備えたことを特徴とする エンコーダ信号処理回路。

【請求項 4】

モータの回転によりエンコーダが出力する 90 度位相の異なる 2 相の矩形波信号と、この矩形波信号の反転信号を 4 組の RS フリップフロップの入力信号とし、前記 4 組の RS フリップフロップの出力のうち 2 組の RS フリップフロップの出力の論理積信号をとり、前記 2 組の RS フリップフロップとは異なる別の 2 組の RS フリップフロップの出力の論理積信号をとることにより、ジッタのない 90 度位相の異なる 2 相の矩形波信号を出力するジッタ除去回路と、前記ジッタ除去回路の出力である 2 相の矩形波信号のエッジをカウントするカウンタを備えたエンコーダ信号処理回路において、

前記カウンタのカウント値と記憶された前回カウント値の差分の符号がモータの反転によって変化したと判断したときは、前記カウント値に前記差分の符号に応じて +1 もしくは -1 を加えて出力する手順を記録したことを特徴とする コンピュータプログラム用記録媒体。

【発明の詳細な説明】

【0001】

【産業上の利用分野】

本発明は、回転体例えはモータの速度・位置の検出に使われるエンコーダの信号処理回路において、モータの反転時に生じるパルスのヒステレシスを補償するジッタ除去手段を改良するジッタ除去回路のパルスヒステレシス補償方法とその装置ならびにその手順をコンピュータプログラムとして記録した媒体に関する。

【0002】

【従来の技術】

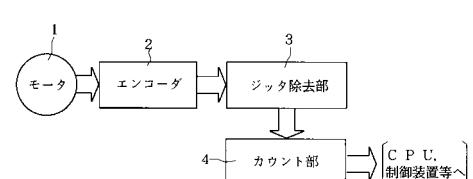

図 3 は、従来例としてのジッタ除去回路を用いたエンコーダの位置検出方法を示す装置のブロック図である。全ての図面において、同一符号は同一若しくは相当部材を示す。

また、図 4 はそのジッタ除去回路の回路構成を示す論理回路図である。

モータ 1 の回転により、エンコーダ 2 で出力された 90 度位相の異なる 2 相パルスは、ジッタ除去回路 3 でジッタを除去されたパルスとしてカウント部 4 に入力され、カウント部 4 ではパルスのエッジをカウントし出力する。その出力された値は中央演算装置 (CPU) や記憶装置へ入力され、モータの制御に利用されていた。

【0003】

ところが、このような従来例の方法では、モータ反転時にパルスヒステレシスが発生するという問題があった。

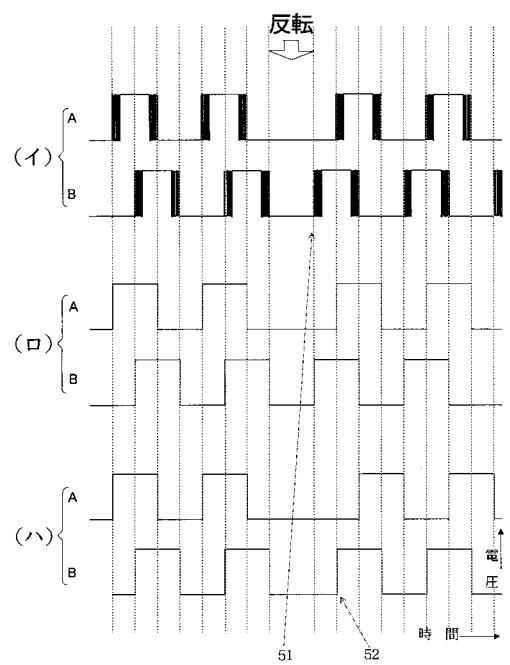

図 5 は、このパルスヒステレシスを示す電圧波形のタイムチャートである。

モータ反転時のエンコーダ 2 相出力パルスは一般に図 5 (イ) のようになり、パルスの立ち上がり立ち下がりの部分にジッタがある波形となる。

そこで、ジッタ除去回路が挿入されるのだが、ジッタを取り除くことが目的であるから、ジッタ除去回路から出力される 2 組のパルスは図 5 (ロ) のように成るべきである。

【0004】

【発明が解決しようとする課題】

10

20

30

40

50

しかしながら、先の図4のジッタ除去回路を用いると出力される2相出力パルスは図5(ハ)のようになる。

これらの図5(ロ), (ハ)で明らかのように、従来例のジッタ除去回路を用いたエンコーダ信号処理では、図5(ロ)に示すモータ反転後最初のB相立ち上がりで[図5の51参照]、2相出力パルス図5(ハ)に示すの出力もB相が立ち上がるべきところを、図5(ロ)に示すA相の立ち上がりで図5(ハ)に示すの出力のB相が立ち上がっている[図5の52参照]。

つまり、モータ反転後最初の2カウント目で初めて1カウント目が制御装置等へ出力されており、ここにヒステレシスがあることがわかる。

そこで、本発明はこのヒステレシスを補償することを目的とする。

10

#### 【0005】

##### 【課題を解決するための手段】

上記目的を達成するために本発明の請求項1の発明は、モータの回転によりエンコーダが<sup>出力する</sup>90度位相の異なる2相の矩形波信号と、この矩形波信号の反転信号を4組のRSフリップフロップの入力信号とし、前記4組のRSフリップフロップの出力のうち2組のRSフリップフロップの出力の論理積信号をとり、前記2組のRSフリップフロップとは異なる別の2組のRSフリップフロップの出力の論理積信号をとることにより、ジッタのない90度位相の異なる2相の矩形波信号を出力するジッタ除去回路と、前記ジッタ除去回路の出力である2相の矩形波信号のエッジをカウントするカウンタを備えたエンコーダ信号処理回路において、前記カウンタのカウント値と記憶された前回カウント値の差分の符号がモータの反転によって変化したと判断したときは、前記カウント値に前記差分の符号に応じて+1もしくは-1を加えて出力することを特徴とするエンコーダ信号処理回路のヒステレシス補償方法である。

20

このように本発明の請求項1の発明によれば、モータの反転時に生じるパルスヒステレシスを補償することができ、モータの回転を反転し、繰り返し運転を行う場合などに、オフセットすることなく正確な位置に停止することができるという特段の効果を奏する。

#### 【0006】

本発明の請求項2の発明は、請求項1のジッタ除去回路のパルスヒステレシス補償方法において、今回のカウント値と前回カウント値の差分をとるとその差分がゼロか否かを判断し、ゼロであれば今回のカウント値を記憶して補正は行わず、次回のカウント値との差分をとる操作を繰り返し、前記差分がゼロでなければ、前回の差分と符号が違うか否かを判断し、前記符号が違えば差分の符号に応じて、+1または-1を補正量として前記今回のカウント値に加えて出力することを特徴とする請求項1記載のエンコーダ信号処理回路のヒステレシス補償方法である。

30

#### 【0007】

本発明の請求項3の発明は、モータの回転によりエンコーダが<sup>出力する</sup>90度位相の異なる2相の矩形波信号と、この矩形波信号の反転信号を4組のRSフリップフロップの入力信号とし、前記4組のRSフリップフロップの出力のうち2組のRSフリップフロップの出力の論理積信号をとり、前記2組のRSフリップフロップとは異なる別の2組のRSフリップフロップの出力の論理積信号をとることにより、ジッタのない90度位相の異なる2相の矩形波信号を出力するジッタ除去回路と、前記ジッタ除去回路の出力である2相の矩形波信号のエッジをカウントするカウンタを備えたエンコーダ信号処理回路において、前記カウンタのカウント値と記憶された前回カウント値の差分の符号がモータの反転によって変化したと判断したときは、前記カウント値に前記差分の符号に応じて+1もしくは-1を加えて出力する補償演算部を備えたことを特徴とするエンコーダ信号処理回路である。

40

#### 【0008】

本発明の請求項4の発明は、モータの回転によりエンコーダが<sup>出力する</sup>90度位相の異なる2相の矩形波信号と、この矩形波信号の反転信号を4組のRSフリップフロップの入力信号とし、前記4組のRSフリップフロップの出力のうち2組のRSフリップフロップ

50

の出力の論理積信号をとり、前記 2 組の R S フリップフロップとは異なる別の 2 組の R S フリップフロップの出力の論理積信号をとることにより、ジッタのない 90 度位相の異なる 2 相の矩形波信号を出力する ジッタ除去回路 と、前記 ジッタ除去回路 の出力である 2 相の矩形波信号のエッジをカウントするカウンタを備えたエンコーダ信号処理回路において、前記 カウンタ のカウント値と記憶された前回カウント値の差分の符号がモータの反転によって変化したと判断したときは、前記カウント値に前記差分の符号に応じて + 1 もしくは - 1 を加えて出力する手順を記録したことを特徴とするコンピュータプログラム用記録媒体である。

#### 【 0 0 0 9 】

##### 【発明の実施の形態】

本発明の実施の形態について図面を参照して説明する。

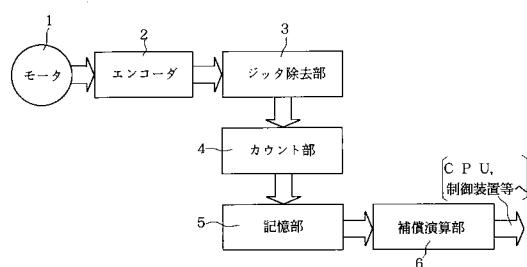

図 1 は、本発明の実施の形態における回路構成を示すブロック図である。

この図 1 は、従来例の図 3 にカウント記憶部 5 とヒステレシス補償部 6 が追加して配置された構成である。

#### 【 0 0 1 0 】

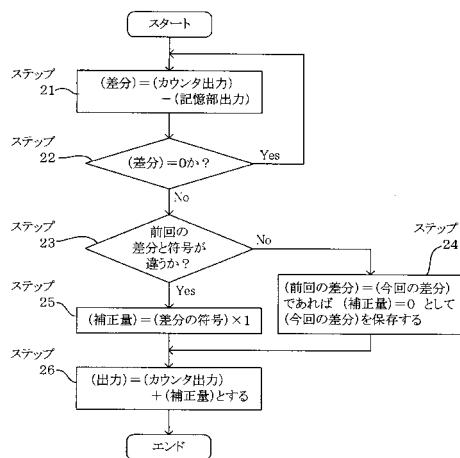

図 2 は、本発明に係る演算部における補償方法の操作手順を示すフローチャートである。手順に従って図 1, 図 2 を説明する。

[1] モータ 1 が回転し、その変位に対応して 90 度位相の異なる 2 相のパルスがエンコーダ 2 より出力され、ジッタ除去部 3 においてパルスの立ち上がり、立ち下がりの部分が排除される。

[2] カウント部 4 では、ジッタの除去されたパルスの立ち上がり、立ち下がりを検出し、併せて 2 相パルスの方向も検出し、カウントの増減を行う。

ここまででは、従来例と同じである。そして、

[3] 記憶部 5 では、カウント部 4 より前回出力された値を保持しておく。この記憶部 5 の値が更新されるのは、一定時間が経過した後、若しくはカウント部 4 の出力が更新されたときである。

#### 【 0 0 1 1 】

[4] 補償演算部 6 では、

ステップ 21 として、カウント部 4 より現在出力されている値から、記憶部 5 より出力されるカウント出力の前回値を引いて差分を取る。

ステップ 22 では、前記差分がゼロであれば(Yes) ステップ 21 に戻り、ゼロでなければ(No) 次のステップ 23 へ進む。

ステップ 23 として、前記差分の符号が前回のものと異なっていれば、すなわちモータ 1 が反転していれば(Yes) ステップ 25 へ、前回の差分の符号と同じであれば(No) つまりモータ 1 の回転方向が変わっていないければ、ステップ 24 へ進む。

ステップ 24 では、今回の差分値を前回の差分値として保存する。さらに補正值はゼロにしてステップ 26 へ移る。

ステップ 25 として、モータ 1 が反転しているので、今回の差分値が正であれば + 1、負であれば - 1 を補正量として、ステップ 26 へ進む。さらに今回の差分値を前回の差分値として保存する [ 図示のように、差分符号に 1 を乗じたものを補正量としている ]。

ステップ 26 では、補正出力として、カウンタ部 4 の出力に補正量を加えた値を出力する。

#### 【 0 0 1 2 】

このようにして、モータ 1 の反転後 2 つ目のエッジ [ 図 5 の 51 参照 ] が、カウンタ部 4 に入力されたときに、補正を加えて出力され、制御等に用いられる。

また、本発明の操作手順をコンピュータプログラムとして記述し、それを読み取ったコンピュータがヒステリシス補償部 6 として機能するようにしてもよいことは勿論である。

#### 【 0 0 1 3 】

##### 【発明の効果】

以上述べたように本発明によれば、モータの反転時に生じるパルスヒステリシスを補償することができ、モータの回転を反転し、繰り返し運転を行う場合などに、オフセットする

10

20

30

40

50

ことなく正確な位置に停止することができるという特段の効果を奏する。

【図面の簡単な説明】

【図1】本発明の実施の形態における回路構成を示すブロック図

【図2】本発明に係る演算部における補償方法の操作手順を示すフローチャート

【図3】従来例としてのジッタ除去回路を用いたエンコーダの位置検出方法を示す装置のブロック図

【図4】図4は図3のジッタ除去回路の回路構成を示す論理回路図

【図5】従来例のパルスヒステレシスを示す電圧波形のタイムチャート

【符号の説明】

- 1 モータ

- 2 エンコーダ

- 3 ジッタ除去部

- 4 カウント部

- 5 記憶部

- 6 補償演算部

10

【図1】

【図3】

【図2】

【図4】

【図5】

---

フロントページの続き

(56)参考文献 特開平11-248488(JP, A)

実開平5-81635(JP, U)

実開昭62-14558(JP, U)

(58)調査した分野(Int.Cl., DB名)

G01D 5/00- 5/62