(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2004-507081

(P2004-507081A)

(43) 公表日 平成16年3月4日(2004.3.4)

(51) Int.Cl.<sup>7</sup>

H01L 29/78

H01L 21/316

H01L 21/8234

H01L 21/8238

H01L 27/088

F1

H01L 29/78

H01L 21/316

H01L 29/78

H01L 27/08

H01L 27/08

301B

M

301G

102C

321D

テーマコード(参考)

5F048

5F058

5F140

審査請求 未請求 予備審査請求 有 (全 39 頁) 最終頁に続く

|               |                              |           |                                                                                                        |

|---------------|------------------------------|-----------|--------------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2002-520272 (P2002-520272) | (71) 出願人  | 503043894<br>プラドック, ウォルター, デビッド,<br>IV<br>アメリカ合衆国 55906 ミネソタ州<br>, ロチェスター, エヌ. イー.,<br>ファースト ストリート 300 |

| (86) (22) 出願日 | 平成13年8月10日 (2001.8.10)       | (74) 代理人  | 100107010<br>弁理士 橋爪 健                                                                                  |

| (85) 翻訳文提出日   | 平成15年2月7日 (2003.2.7)         | (72) 発明者  | プラドック, ウォルター, デビッド,<br>IV<br>アメリカ合衆国 55906 ミネソタ州<br>, ロチェスター, エヌ. イー.,<br>ファースト ストリート 300              |

| (86) 國際出願番号   | PCT/US2001/025150            | F ターム(参考) | 5F048 AC01 AC03 BA15 BB04 BB08<br>BB09 BB11 BG11 DA23                                                  |

| (87) 國際公開番号   | W02002/015233                |           | 最終頁に続く                                                                                                 |

| (87) 國際公開日    | 平成14年2月21日 (2002.2.21)       |           |                                                                                                        |

| (31) 優先権主張番号  | 09/636,484                   |           |                                                                                                        |

| (32) 優先日      | 平成12年8月10日 (2000.8.10)       |           |                                                                                                        |

| (33) 優先権主張国   | 米国(US)                       |           |                                                                                                        |

(54) 【発明の名称】集積トランジスタ素子

## (57) 【要約】

自己整合エンハンスマード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ10は、Ga<sub>2</sub>O<sub>3</sub>、Ga<sub>2</sub>O<sub>3</sub>、および他の酸化ガリウム(ガリウム酸化物(膜))化合物の混合物である下部酸化膜層30、III-V族化合物半導体ウェハ構造13の上部面14上に配置したガリウム酸素層の真上に配置される第二絶縁層を含む。下部酸化ガリウム(ガリウム酸化物(膜))化合物層と第二絶縁層は全体的に酸化ガリウム(ガリウム酸化物(膜))ゲート絶縁構造を形成する。酸化ガリウム(ガリウム酸化物(膜))ゲート絶縁構造と下地化合物半導体ガリウム砒素層15は化合物半導体ウェハ構造14との面である原子的アラブト界面で会合する。初期の基本的なガリウム酸素層は第二絶縁酸化膜層から下地化合物半導体面を不動態化したり保護するのに役立つ。リフラクトリメタルゲート電極層17は第二絶縁酸化膜層の上部面18上に配置される。リフラクトリメタルは高温で第二絶縁酸化膜層上で安定である。自己整合ソースおよびドレイン領域、ソースおよびドレイン接点19、20は素子のソースおよびドレイン領域21、22上に

## 【特許請求の範囲】

## 【請求項 1】

エンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、上部面を有する化合物半導体ウェハ構造と；

前記化合物半導体ウェハ構造の上部面に配置した、 $\text{Ga}_2\text{O}_3$ 、 $\text{Ga}_2\text{O}$ および他のガリウム酸素化合物 (gallium oxygen compounds) の混合物を含むが、これに限らないものを含むガリウムと酸素の化合物を含む層と；

初期支持 (initial supporting) ガリウム酸素層の上部に堆積した絶縁層を形成する、ガリウムと酸素と少なくとも一つ以上の希土類元素の化合物を含む第二絶縁層で、前記第一および第二層は、化合物半導体構造に隣接して、且つ、この上部にゲート絶縁体構造を形成し；

前記ゲート絶縁体構造層の上部面に配置した安定なリフラクトリメタル (refractory metal、高融点金属、耐熱性金属、超硬合金) ゲート電極と；

ゲート電極に対し自己整合した (self-aligned) ソースおよびドレインイオンインプラントと；および

イオン注入ソースおよびドレイン領域上に配置したソースおよびドレインオーミックコンタクトと；

前記リフラクトリメタルゲート電極は、W、WN又はWSi又はその組合せから成るグループから選択したリフラクトリメタルを含み；

モノリシック構造 (monolithically) 集積回路を形成する前記トランジスタの配線手段と、

を備えた前記エンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

## 【請求項 2】

請求項 1 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

ガリウム酸素化合物の初期層が、化合物半導体ウェハ構造の上部面と原子的アブラプト (abrupt) 界面 (Interface、接合面、境界面) を形成するエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

## 【請求項 3】

請求項 1 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

ゲート絶縁体構造が、初期ガリウム酸素化合物層、ガリウム酸素と少なくとも一つの希土類元素の種々の (varying、変化する、いろいろな) 組成を含む段階層 (graded layer)、および、ガリウムと酸素および一つ以上の希土類元素との化合物を主に含む第三絶縁体層、の三つの層を含むエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

## 【請求項 4】

請求項 1 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

ゲート絶縁体構造が三つ以上の多層膜 (multiple layers)、初期 (initial) ガリウム酸素化合物層、および、絶縁酸化ガリウム (ガリウム酸化物 (膜)) ゲート絶縁体構造を共に形成する一つ以上の希土類元素の有無にかかわらずガリウムおよび酸素を含む多層膜を含むエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

## 【請求項 5】

請求項 1 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

初期ガリウム酸素化合物層が 10 より大きく 25 未満の厚みを持つエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

10

20

30

40

50

## 【請求項 6】

請求項 1 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

ゲート絶縁体構造が 20 ~ 300 の総厚さを持つエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

## 【請求項 7】

請求項 1 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

初期ガリウム酸素化合物層が四原子層 (four atomic layers) 未満の構造的界面変調 (structural Interface modulation) の深さに伸びる、化合物半導体構造とともに、原子的アブラプト (abrupt) 界面を形成するエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。10

## 【請求項 8】

請求項 1 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

初期ガリウムおよび酸素化合物層とゲート絶縁体構造とが、化合物半導体ウェハ構造の上部面を保護するエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

## 【請求項 9】

請求項 1 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、20

リフラクトリメタルゲート電極が、700 以上の高温でゲート絶縁体構造の上部層の存在の下で安定なリフラクトリメタルを含むエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

## 【請求項 10】

請求項 1 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

前記エンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタを含むソースおよびドレインイオンインプラントが、n チャネル素子又は p チャネル素子であるエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。30

## 【請求項 11】

請求項 1 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

前記ソースおよびドレインイオンインプラントは、Be / F 又は C / F を含み、前記エンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタは、p チャネル素子であるエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。40

## 【請求項 12】

請求項 1 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

化合物半導体ウェハ構造の上部面が GaAs を含むエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

## 【請求項 13】

請求項 1 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

化合物半導体ウェハ構造の上部面が  $In_x Ga_{1-x} As$  を含むエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

## 【請求項 14】

エンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、上部面を有する化合物半導体ウェハ構造と；50

前記化合物半導体ウェハ構造の上部面に配置した、 $\text{Ga}_2\text{O}_3$ 、 $\text{Ga}_2\text{O}$ および他のガリウム酸素化合物の混合物を含むが、これに限らないものを含むガリウムおよび酸素化合物の化合物を含む層と；

ガリウム、酸素、および一つ以上の希土類元素の標準化相対組成 (normalized relative composition) が前記絶縁層内の厚さの関数として単調に (monotonic manner) 変化するようにした、ガリウムと酸素と少なくとも一つ以上の希土類元素の化合物を含む第一層上に堆積した第二絶縁体層と；

ガリウム酸素と少なくとも一つ以上の希土類元素を含む前記第二層の上部に堆積した第三絶縁層で；前記第一、第二および第三層が化合物半導体構造に隣接してその上部に堆積したゲート絶縁体構造を形成し；

前記ゲート絶縁体構造層の上部面に配置した安定なリフラクトリメタルゲート電極と；

ゲート電極に対し自己整合したソースおよびドレインイオンインプラントと；およびイオン注入ソースおよびドレイン領域上に配置したソースおよびドレインオーミックコンタクトと；、

前記リフラクトリメタルゲート電極は、 $\text{W}$ 、 $\text{WN}$ 又は $\text{WSi}$ 又はその組合せから成るグループから選択したリフラクトリメタルを含み；

モノリシック構造集積回路を形成する前記トランジスタの配線手段と、

を備えた前記エンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

#### 【請求項 15】

請求項 14 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

ガリウム酸素化合物の初期層が、化合物半導体ウェハ構造の上部面と原子的アブラプト界面を形成するエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

#### 【請求項 16】

請求項 14 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

ゲート絶縁体構造が、初期ガリウム酸素化合物層、ガリウム酸素および少なくとも一つの希土類元素の種々の (varying、変化する、いろいろな) 組成を含む段階層、および、ガリウム、酸素および一つ以上の希土類元素の化合物を主に含む第三絶縁体層、の三つ以上の層を含むエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

#### 【請求項 17】

請求項 14 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

初期ガリウム酸素化合物層が 10 より大きく 25 未満の厚さを持つエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

#### 【請求項 18】

請求項 14 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

ゲート絶縁体構造が 20 ~ 300 の総厚さを持つエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

#### 【請求項 19】

請求項 14 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

初期ガリウム酸素化合物層が四原子層未満の前記界面変調の深さに伸びる、化合物半導体構造とともに、原子的アブラプト (abrupt) 界面を形成するエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

#### 【請求項 20】

10

20

30

40

50

請求項 1 4 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

初期ガリウムおよび酸素化合物層とゲート絶縁体構造とが、化合物半導体ウェハ構造の上部面を保護するエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

【請求項 2 1】

請求項 1 4 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

リフラクトリメタルゲート電極が、700 以上 の高温でゲート絶縁体構造の上部層の存在の下で安定なリフラクトリメタルを含むエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。 10

【請求項 2 2】

請求項 1 4 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

前記エンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタを含むソースおよびドレインイオンインプラントが、n チャネル素子であるエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

【請求項 2 3】

請求項 1 4 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

前記ソースおよびドレインイオンインプラントは、Be / F および C / F を含み、前記エンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタは、p チャネル素子であるエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。 20

【請求項 2 4】

請求項 1 4 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

化合物半導体ウェハ構造の上部面が GaAs を含むエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。 30

【請求項 2 5】

請求項 1 4 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

化合物半導体ウェハ構造の上部面が  $In_x Ga_{1-x} As$  を含むエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

【請求項 2 6】

エンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、上部面を有する化合物半導体ウェハ構造と；

前記化合物半導体ウェハ構造の上部面に配置された電子中間ギャップ欠陥密度 (electronic midgap defect density) の低いゲート絶縁膜を形成する、ガリウム、酸素、少なくとも一つの希土類元素を含む交互層 (alternating layers) を含む多層膜ゲート絶縁体構造と； 40

前記ゲート絶縁体構造層の上部面に配置された安定な耐熱性 (リフラクトリメタル) 金属ゲート電極と；

ゲート電極に自己整合した (self-aligned) ソースおよびドレインインプラントと；および

イオン注入ソースおよびドレイン領域上に配置したソースおよびドレインオーミックコンタクトと

を備え、誘電体 (dielectric) スペーサが安定な耐熱性ゲート金属電極の側壁に配置される前記エンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。 50

## 【請求項 27】

エンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、上部面を有する化合物半導体ウェハ構造と；

前記化合物半導体ウェハ構造の上部面に配置されたゲート絶縁体構造と；

前記ゲート絶縁体構造の上部面に配置された安定な耐熱性金（リフラクトリメタル）属ゲート電極と；

ゲート電極に対し自己整合したソースおよびドレインイオンインプラントと；およびイオン注入ソースおよびドレイン領域に配置したソースおよびドレインオーミック>Contactと

を備え、

10

前記化合物半導体ウェハ構造が広帯域（wide band）ギャップスペーサ層と狭帯域ギャップチャネル層を備えた前記エンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

## 【請求項 28】

請求項 27 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

広帯域ギャップスペーサが、ゲート酸化膜層と狭帯域ギャップチャネル層の間に配置されるエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

## 【請求項 29】

請求項 27 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

広帯域ギャップスペーサ層が 3 ~ 200 の厚みを持つエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

20

## 【請求項 30】

請求項 27 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

広帯域ギャップスペーサ層が、 $Al_x Ga_{1-x} As$ 、 $InP$ 、又は $In_z Ga_{1-z} P$ 、又はその組合せを含むエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

30

## 【請求項 31】

請求項 27 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

狹帯域ギャップチャネル層が 10 ~ 300 の厚みを持つエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

## 【請求項 32】

請求項 27 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

狹帯域ギャップチャネル層が、広帯域ギャップスペーサ層とバッファ層の間に配置されるエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

40

## 【請求項 33】

請求項 27 に記載のエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

狹帯域ギャップチャネル層が、 $In_y Ga_{1-y} As$  を含むエンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタ。

## 【請求項 34】

エンハンスマントモード金属 - 酸化物 - 化合物半導体電界効果型トランジスタであって、

上部面を有する化合物半導体ウェハ構造と；

前記化合物半導体ウェハ構造の上部面に配置したゲート絶縁体構造と；

前記ゲート絶縁体構造層の上部面に配置した安定な耐熱性（リフラクトリメタル）金属ゲート電極と；

50

ゲート電極に対し自己整合された (self-aligned) ソースおよびドレインイオンインプラント；およびイオン注入ソースおよびドレイン領域に配置したソースおよびドレインオーミックコンタクトとを備えて、

前記化合物半導体ウェハ構造が、 $Al_xGa_{1-x}As$ ,  $In_yGa_{1-y}As$ ,  $InP$ , あるいは  $In_zGa_{1-z}P$  層を含み、前記層が、化合物半導体基板の上部面に配置されたエンハンスマントモード金属-酸化物-化合物半導体電界効果型トランジスタ。

【請求項 3 5】

請求項 3 4 に記載のエンハンスマントモード金属-酸化物-化合物半導体電界効果型トランジスタであって、

前記化合物半導体基板が  $GaAs$  ベース半導体ウェハを含むエンハンスマントモード金属-酸化物-化合物半導体電界効果型トランジスタ。

【請求項 3 6】

請求項 3 4 に記載のエンハンスマントモード金属-酸化物-化合物半導体電界効果型トランジスタであって、

前記化合物半導体基板が  $InP$  ベース半導体ウェハを含むエンハンスマントモード金属-酸化物-化合物半導体電界効果型トランジスタ。

【請求項 3 7】

請求項 1、13、26 又は 33 項に記載のエンハンスマントモード金属-酸化物-化合物半導体電界効果型トランジスタであって、

類似および相補型 (complementary) トランジスタ素子と共に集積化ができ、相補型金属-酸化物化合物半導体集積回路を形成する前記エンハンスマントモード金属-酸化物化合物半導体電界効果型トランジスタ。

【発明の詳細な説明】

【0001】

(発明の分野)

本発明は、電界効果型トランジスタ、より具体的にはエンハンスマントモード自己整合 (self-aligned) 金属-酸化物-化合物半導体 (metal-oxide-compound semiconductor) トランジスタと空乏 (depletion) モード自己整合金属-酸化物-化合物半導体トランジスタとを合わせて含む相補型 (complementary) 電界効果トランジスタを利用する化合物半導体分野の低電力および高速集積回路と、材料育成と前記構造の作製および前記トランジスタの超大規模集積化の方法に関する。

【0002】

(発明の背景)

ガリウム砒素およびリン化インジウム集積回路業工業は相補型電界効果型トランジスタ素子と低ゲート漏れ電流をもつトランジスタの集積化を同時に可能にする技術がなくて制約を受けていた。非常に成熟し、且つ有用な相補型金属酸化物半導体 (CMOS) 技術を持つシリコン技術とは対照的である。III-V 族半導体工業において広く用いられる電界効果型トランジスタ (FETs) は数マイクロアンペアを超える静止状態漏れ電流を持つ金属ゲートおよびショックレーゲート接点を採用する。化合物半導体技術に金属ゲートを用いると、個々のトランジスタおよび集積回路のワット損を過剰に高くし、トランスコンダクタンスを減らし、ロジックスイングを減らし、単一電源での動作を不能にし、且つ、性能特性を制限してしまう。静止漏れ電流の振幅が高いので、当業者においては  $GaAs$  素子の最大集積化をトランジスタ数十万個の回路に限定する。対照的に、数百万個のトランジスタの同時集積化はシリコン CMOS 技術によって高集積密度で可能である。これらの超高集積化密度とレベルは化合物半導体 FETs で絶縁されない金属、ショットキー型ゲートでは得られない。それゆえ、Si-CMOS 技術は個々のゲート漏れ電流、集積化レベルおよびコストに関して顕著な利点を提供する。

10

20

30

40

50

## 【0003】

しかしシリコンに比べると、相補型G a A sおよびI n P回路技術は1 Vおよび1 V以下の低電源電圧で高速で最適な速度／電力性能および効率を示す。これらのG a A sおよびI n P集積回路技術の市場での支持は低いままである。その理由は動作電力量が低い状態で高集積化密度を実証することができないからである。したがって、シリコンC M O Sがデジタル集積回路の分野で優位に立ち、G a A sおよびI n P技術はどちらもこの市場に上手く進出できない。

## 【0004】

必要とされるものは、新しい改善された化合物半導体電界効果型トランジスタ(F E T)である。また、必要とされるものは、新しい改善された金属-酸化物-化合物半導体接合部による化合物半導体F E T s(M O S F E T)である。また、必要とされるものは、新しい改善された自己整合ゲート構造による化合物半導体M O S F E T sである。また、必要とされるものは、新しい改善されたエンハンスメントモードおよび空乏モード動作を用いる自己整合化合物半導体M O S F E T sである。また、必要とされるものは、新しい改善された安定で信頼性のある素子動作を行う自己整合化合物半導体M O S F E T sである。また、必要とされるものは、新しい改善された最適化合物半導体素子性能を可能にする自己整合化合物半導体M O S F E T sである。また、必要とされるものは、新しい改善されたR Fおよびマイクロ波用の最適効率と出力電力を有する自己整合化合物半導体M O S F E T sである。また、必要とされるものは、新しい改善された相補型回路と構造に使用する自己整合化合物半導体M O S F E T sである。また、必要とされるものは、新しい改善された低出力／高性能相補型回路と構造用の自己整合化合物半導体M O S F E T sである。また、必要とされるものは、新しい改善された相補型構造の設計を柔軟なものにする自己整合化合物半導体M O S F E T sである。また、必要とされるものは、新しい改善されたおよび超大規模集積化の配線遅延(interconnection delay)を制御する自己整合化合物半導体M O S F E T sである。必要とされるものは、新しい有用な相補型集積回路であり、各個々のトランジスタの漏れ電流は10<sup>-12</sup>アンペアに近く。必要なものは、本当に有用な化合物半導体のU L S Iデジタル集積回路の有効で経済的な動作を可能にするG a A sとI n Pの真に有用な集積回路技術である。必要とされるものは、新しい改善された正味のワット損が非常に低い化合物半導体M O S F E T集積回路である。また、必要とされるものは、新しい改善された無数のトランジスタを含む超大規模集積回路を形成するために共に集積化される、ゲート漏れ電流の低い化合物半導体M O S F E T素子である。また、必要とされるものは、新しい改善されたおよび従来技術において既に存在するシリコンC M O S設計の直接使用、移転(transfer)、および応用を可能にする化合物半導体内の相補型M O S F E T素子および回路である。

## 【0005】

さらに必要とするものは、新しい改善された自己整合化合物半導体M O S F E T sの作製方法；確立された相補型G a A sヘテロ構造F E T s技術と互換性のある自己整合化合物半導体M O S F E T sの作製方法；および比較的容易に作製および使用できる化合物半導体M O S F E T sである。

## 【0006】

## 【発明の実施の形態】

本発明のより完全な理解は、図と関連させて考えるときに詳細な説明とクレームを参照することにより得られる。同じ番号は図中で同じ項目を示す。

ここに示した事例は本発明の実施例をその一形態において示すもので、このような事例はいかなる方法においても限定的なものとして構成されるものではない。

本発明は、特に自己整合エンハンスメントモード金属-酸化物-化合物半導体F E Tを提供する。このF E Tは少なくとも二つの明確な層を含むガリウム酸素絶縁構造を含む。第一層は厚みが10 nmを超えるが25 nm未満であり、化学量論的組成のG a<sub>2</sub>O<sub>3</sub>とG a<sub>2</sub>O<sub>5</sub>(これらに限定されるものではないが)を含む実質的にガリウム酸素化合物(gallium oxygen compounds)、あるいは少数の他のガリウム酸素化合物を

10

20

30

40

50

含む。酸化ガリウム(ガリウム酸化物(膜)、gallium oxide)絶縁構造の上部絶縁層は下地ガリウム酸素絶縁構造と混ざらない絶縁膜を含む。この上部層は優れた絶縁特性を持ち、一般的にガリウム酸素と第三希土類元素とで構成され、三元(ternary)絶縁材料を形成する。それゆえ、酸化ガリウム(ガリウム酸化物(膜))希土類ゲート絶縁構造全体は少なくとも二つの層から成り、上部絶縁材料と初期層(initial layer)を構成するガリウム酸素化合物との混合物から成る第三中間段階層(graded layer、連続層)を含む。初期ガリウム酸素層、中間段階層、および上部絶縁領域の全体は酸化ガリウム(ガリウム酸化物(膜))絶縁構造と金属-酸化物-化合物半導体電界効果トランジスタのゲート絶縁領域の両方を形成する。実質的に初期ガリウム酸素層は化合物半導体ウェハ構造の上部層と原子的アラプト(abrupt)界面(interface、境界面、接合面)を形成し、化合物半導体材料に中間ギャップ面状態を導入しない。リフラクトリメタル(refractory metal、高融点金属、耐熱性金属、超硬合金)ゲート電極はゲート絶縁体構造層の上面に配置される。リフラクトリメタルは高温でゲート絶縁体構造層上で安定である。自己整合ソースとドレイン領域、およびソースとドレイン接点はソースおよびドレイン領域上に配置される。全ての実施例やその他では、金属-酸化物-化合物半導体トランジスタは、化合物半導体ヘテロ構造の上部面に配置された、ゲート絶縁体構造を形成する初期ガリウム酸素層、中間遷移層、および厚み30~250の上部絶縁層を含む多層ゲート絶縁体構造を含む。この実施例では、化合物半導体ヘテロ構造は、化合物半導体基板上にn型および/あるいはp型電荷供給層を成長させたり、させないGaAs, Al<sub>x</sub>Ga<sub>1-x</sub>As、およびIn<sub>y</sub>Ga<sub>1-y</sub>As層、W, WN、やWSiのリフラクトリメタルゲート、自己整合ドナー(n-チャネルFET)やアクセプタ(p-チャネルFET)インプラント、および、ソースとドレインのオーミックコンタクトを含む。別の実施例では、化合物半導体ヘテロ構造は、In<sub>y</sub>Ga<sub>1-y</sub>As, Al<sub>x</sub>In<sub>1-x</sub>As、およびInP化合物半導体ヘテロ構造、InP基板上に成長させたn型および/あるいはp型電荷供給層、およびW, WN、やWSiのリフラクトリメタルゲート、自己整合ドナー(n-チャネルFET)やアクセプタ(p-チャネルFET)インプラント、およびソースとドレインのオーミックコンタクトを含む。

## 【0007】

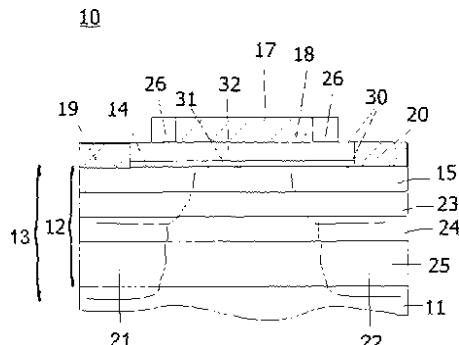

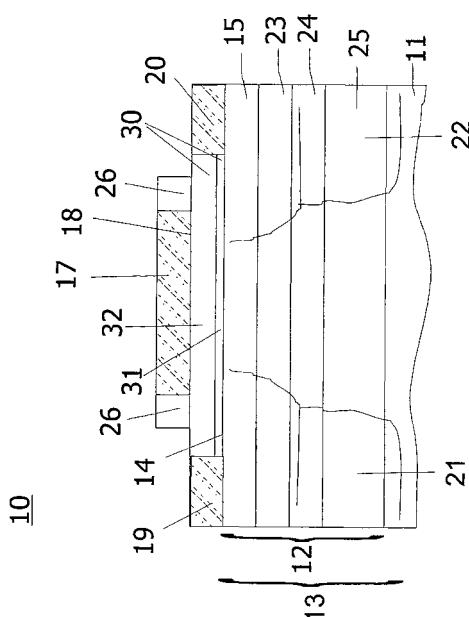

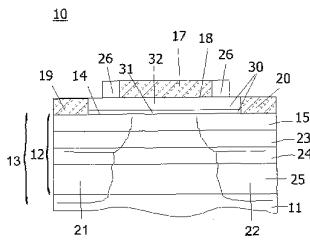

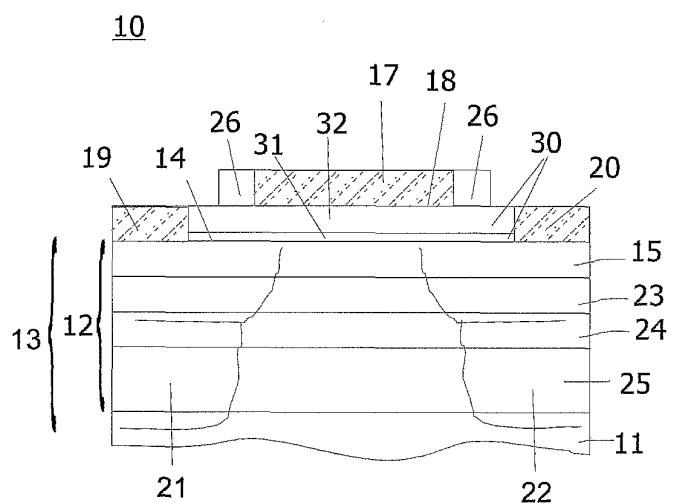

図1は、本発明の実施例による自己整合エンハンスメントモード化合物半導体MOSFETの簡略化断面図である。素子10はIII-V族半導体基板11と化合物半導体エピタキシャル層構造12により表示された半導体素子に使用されるIII-V族材料のような化合物半導体材料を含む。この内容の説明のために、基板11とその上に形成したエピタキシャル層構造12を化合物半導体ウェハ構造(図1では13と表示する)と呼ぶことにする。半導体ウェハ構造13の製造方法には分子線エピタキシャル成長法(MBE)と金属有機化学気相蒸着法(MOCVD)があるが、これらに限定されるものではない。勿論、特定の用途においては、エピタキシャル層が存在しないこともあります。上部層15の上部面は単に基板11の上部面になることもある。

## 【0008】

また、素子10は少なくとも二つ以上の層を含むゲート絶縁膜構造(30)を含む。このゲート絶縁膜構造の第一層(31)は酸化ガリウム(ガリウム酸化物(膜))化合物で全体が構成され、化合物半導体構造に直接に隣接し、化合物半導体構造上に蒸着される。ゲート絶縁膜構造の第二層(32)はガリウム、酸素、および周期律表の一つ以上の希土類元素の化合物を含む。初期ガリウム酸素層(31)は化合物半導体構造の上部層15の上部面とで原子的アラプト界面14を形成する。高温で上部絶縁材料の存在で安定になるリフラクトリメタルゲート電極17はゲート絶縁膜構造の上部面18に配置される。誘電体スペーサ26は金属ゲート電極17の側壁をカバーするように配置される。ソースおよびドレイン接点19と20は自己整合ソースおよびドレイン領域21と22上にそれぞれ堆積される。

## 【0009】

10

20

30

40

50

具体的な実施例では、化合物半導体エピタキシャル層構造は 11 未満の GaAs 上部層 (15)、101 未満の  $Al_xGa_{1-x}As$  スペーサ層 (23)、251 未満の  $In_yGa_{1-y}As$  チャネル層 (24)、および GaAs 基板 (11) 上に育成した GaAs バッファ層 (25) から成る。上部 GaAs 層 (15) は欠陥密度 (defect density) の低いアラート界面をもつゲート絶縁膜構造とで原子的アラート層を形成するのに用いられる。

## 【0010】

本発明の実施例による自己整合エンハンスメントモード化合物半導体 MOSFET を製造する簡略化事例として、上部層 15 の原子的配列で化学的に清潔な (clean) 上部面を備えた III-V 族化合物半導体ウェハ構造 13 を超高真空半導体育成室で作製し、超高真空運搬室 (transfer chamber、トランسفر室、転写室) 経由で第二超高真空酸化膜および絶縁膜蒸着室に移送する。初期ガリウム酸素層 (31) は、高純度  $Ga_2O_3$  源から、あるいは結晶ガドリニウムガリウムガーネット  $Ga_3Gd_5O_12$  から熱蒸着により上部化合物半導体表面層 15 上に蒸着される。この初期ガリウム酸素層の蒸着時には化合物半導体構造の基板温度は 580 未満に、好ましくは 495 未満に保持される。5~8 分の時間周期で絶縁膜蒸着室内でガリウム酸素化合物を約 18 蒸着した後に、第二絶縁膜層の蒸着が始まる。酸素プラズマ流出および種が初期ガリウム酸素層のある前記化合物半導体構造に主に向けられて衝突するように低電力酸素プラズマ源からの流束を超高真空室内に向けることにより第二絶縁膜層の蒸着は始まる。酸素プラズマ源からの流束を 2~5 秒間で表面に向ける必要があり、その後に  $Ga_2O_3$  からのガリウム酸素化合物と希土類元素を含む第二熱蒸発源との同時蒸着を行う。酸素源、 $Ga_2O_3$  および希土類蒸発源熱蒸発源からの流束ビームが平衡に保たれ、前記化合物半導体構造上の初期ガリウム酸素層の上部に三成分絶縁体層を形成する。第二の三成分絶縁体層の蒸着が始まると、基板温度が同時に調整され、この層の蒸着に最適な基板温度になる。この事例では、ガリウム + 酸素 + 希土類層を蒸着するのに必要な基板温度は 530 未満である。この第二絶縁体層の蒸着は絶縁体膜全体の厚さが 200~250 に達するまで続く。シャッタとバルブを用いて、この絶縁体層の所要厚みが蒸着されたときに三成分 (ガリウム + 酸素 + 希土類) 層の蒸着を停止する。基板温度は真空中で約 200 に冷却され、WSi や WN のようなゲート絶縁体構造の上部層において高温で安定で、且つ混じり合うことのないリフラクトリメタルの堆積物は酸化膜層 32 の上部面 18 上に蒸着され、その後で標準リソグラフィによりパターン形成される。酸化膜層 31 がフッ素利用ドライエッティングプロセスのようなリフラクトリメタルエッティング技術により暴露されるまでリフラクトリメタル層はエッティングされる。リフラクトリメタルエッティング手法は酸化膜層 31 をエッティングしない。それゆえ、酸化膜層 31 は、上部層 15 の上部面が酸化膜層 31 により保護されて残るようなエッチ停止層として機能する。全ての処理ステップは損傷の少ないプラズマプロセシングにより遂行される。自己整合ソースおよびドレイン領域 21 と 22 はそれぞれ、インプランテーションマスクとしてリフラクトリメタルゲート電極 17 と誘電体スペーサ 26 を用いて Si (n-チャネル素子) と Be/F や C/F (p-チャネル素子) のイオン注入によって実現される。このようなイオン注入 (ion implantation、イオンインプラント、イオン打込み) 方式は相補型化合物半導体ヘテロ構造 FET 技術の標準プロセシングと互換性があり、当業者には周知である。上部層 15 と酸化膜層 31 の間に確立された界面 16 の劣化を完全に排除するために、インプラント (implants、打込み、注入) は超高真空環境での高速熱アニーリングにより 700~900 で活性化される。最後に、ソースとドレインのオーミックコンタクト 19 と 20 は自己整合ソースおよびドレイン領域 21 と 22 上にそれぞれ蒸着される。その後で、この素子は集積マイクロエレクトロニクスと集積回路製造の当業者にとって標準的な方法により相互接続される。

## 【0011】

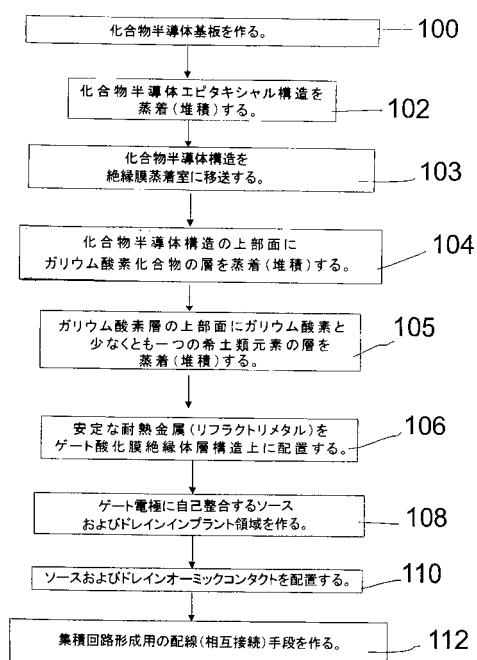

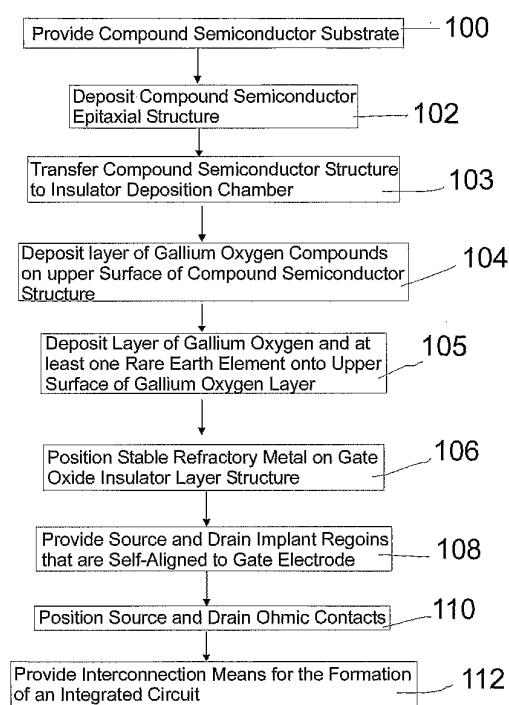

図 2 は、本発明の実施例による自己整合エンハンスメントモード化合物半導体 MOSFET を製造する方法を説明する簡略化フローチャートである。ステップ 102 で、化合物半

10

20

30

40

50

導体ウェハ構造は標準エピタキシャル成長法の技術により作製される。ステップ103で、 $Ga_2O_3$ と $Ga_2O$ ( $Ga_2O_3$ と $Ga_2O$ に限定するものではないが)を含むガリウム酸素化合物から成る層は前記化合物半導体ウェハ構造の上部面上に蒸着される。ステップ104で、ガリウム酸素と一つ以上の希土類元素から成る絶縁層は初期ガリウム酸素化合物層の上部面上に蒸着される。酸化ガリウム(ガリウム酸化物(膜))ゲート絶縁体構造はステップ104と105から形成される。ステップ106で、安定な耐熱性ゲート金属は前記ゲート絶縁体構造の上部面に配置される。ステップ108で、ソースおよびドレインイオン注入はゲート電極に対して自己整合を作る。ステップ110で、ソースおよびドレインオーミックコンタクトはイオン注入ソースおよびドレイン領域上に配置される。

10

### 【0012】

この実施例では、ステップ100では、 $GaAs$ や $InP$ のような化合物半導体基板を作成する(provide、作製する)。ステップ102では、化合物半導体ウェハ構造の原子的配列および化学的清潔上部面の作製およびエピタキシャル成長を行う。ステップ103では、好ましくは化合物半導体ウェハ構造の原子的配列および化学的清潔上部面に精製および結晶性ガドリニウムガリウムガーネットや $Ga_2O_3$ 源から熱蒸着を行う。ステップ104では、他の熱蒸発源と同時に組み合わせて基板100の方に向けた酸素ガスプラズマ源の流出による同時酸化を伴って、ガリウム酸素種とガドリニウムのような少なくとも一つの希土類元素を同時に真空蒸着することにより(ガリウム+酸素+希土類元素)絶縁層を形成する。ゲート絶縁体構造の初期ガリウム酸素化合物層は、好ましくは化合物半導体ウェハ構造の上部面がゲート金属エッチング中や、その後にゲート酸化膜により保護されて残るようにエッチ停止層として機能する。耐熱性ゲート金属は自己整合ソースおよびドレインイオンインプラントの高温アニーリング中にゲート酸化膜層と反応せず、あるいはゲート酸化膜層内に拡散しないことが望ましい。ゲート酸化膜層と化合物半導体構造の上部面とにより形成された界面特性は自己整合ソースおよびドレインイオンインプラントの高温アニーリング中に維持されるのが望ましい。自己整合ソースおよびドレインイオンインプラントは超高真空環境において約700でアニールされるのが望ましい。自己整合ソースおよびドレインインプラントは耐熱性ゲート金属の側壁上に誘電体スペーサを配置することにより実現されるのが望ましい。

20

### 【0013】

したがって、新しい、改善された化合物半導体素子と製造方法を開示する。この新しい、改善された自己整合エンハンスマントモード金属-酸化物-化合物半導体ヘテロ構造電界効果型トランジスタは素子の動作を安定で信頼性のあるものにし、低出力/高性能相補回路および構造に対して最適な化合物半導体素子性能を与える、ULSIにおける配線遅延を統御し、さらに超高集積密度を要するディジタル集積回路用に加え、RFおよびマイクロ波用途にも最適効率および出力電力を与える。

30

### 【0014】

これらの改善は基本的に従来技術の課題、例えば、化合物半導体FET素子の高ゲート漏洩現象、低集積密度、dc電気的不安定性、および電気的ヒステリシスを解決し克服するので、極めて有効な発明となる。本発明の特定の実施例を示し説明してきたが、別の修正や改善は当業者の心に浮かぶこともある。それゆえに、この発明がここに示した特定の形態に限定されるものではないことを理解されることを望む。添付クレームは本発明の精神と範囲から逸脱しない全ての改善に及ぶものである。

40

### 【図面の簡単な説明】

【図1】本発明の実施例による自己整合エンハンスマントモード化合物半導体MOSFETの簡略化断面図である。

【図2】本発明の実施例による自己整合エンハンスマントモード化合物半導体MOSFETを製造する方法を示す簡略化フローチャートである。

【図1】

【図2】

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

21 February 2002 (21.02.2002)

PCT

(10) International Publication Number

WO 02/15233 A2

(51) International Patent Classification: H01L

CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TR, TT, TZ, UA, UG, US, UZ, VN, YU, ZA, ZW.

(21) International Application Number: PCT/US01/25150

(22) International Filing Date: 10 August 2001 (10.08.2001)

(25) Filing Language: English

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

(26) Publication Language: English

(28) Priority Data: 09/636,484 10 August 2000 (10.08.2000) US

(71) Applicant and

(84) Published:

(72) Inventor: WALTER, Walter, David, IV [US/US]; 300

— without international search report and to be republished upon receipt of that report

First St. N.E., Rochester, MN 55906 (US).

(74) Agents: BRADDOCK, Christopher, T. et al.; 217 East

Seventh Avenue, Denver, CO 80203 (US).

(81) Designated States (national): AE, AG, AL, AM, AT, AU,

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU,

(54) Title: INTEGRATED TRANSISTOR DEVICES

WO 02/15233 A2

(57) Abstract: A self-aligned enhancement mode metal-oxide-compound semiconductor field effect transistor (10) includes a lower oxide layer that is a mixture of  $Ga_2O_3$ ,  $Ga_2O_3$ , and other gallium oxide compounds (30), and a second insulating layer that is positioned immediately on top of the gallium oxygen layer together positioned on upper surface (14) of a III-V compound semiconductor wafer structure (13). Together the lower gallium oxide compound layer and the second insulating layer form a gallium oxide gate insulating structure (17). The gallium oxide gate insulating structure and underlying compound semiconductor gallium arsenide layer (15) meet at an atomically abrupt interface at the surface of the with the compound semiconductor wafer structure (14). The initial essentially gallium oxygen layer serves to passivate and protect the underlying compound semiconductor surface from the second insulating oxide layer. A refractory metal gate electrode layer (17) is positioned on upper surface (18) of the second insulating oxide layer. The refractory metal is stable on the second insulating oxide layer at elevated temperature. Self-aligned source and drain areas, and source and drain contacts (19, 20) are positioned on the source and drain areas (21, 22) of the device. Multiple devices are then positioned in proximity and the appropriate interconnection metal layers and insulators are utilized in concert with other passive circuit elements to form a integrated circuit structure.

WO 02/15233

PCT/US01/25150

**Integrated Transistor Devices****FIELD OF THE INVENTION**

The present invention pertains to low power and high speed integrated circuits in the compound semiconductor field utilizing field effect transistors and more specifically complementary field effect transistors used in concert including enhancement mode self-aligned metal-oxide-compound semiconductor transistors and depletion mode self-aligned metal-oxide-compound semiconductor transistors and methods of materials growth and fabrication of said structures and the ultra large scale integration of said transistors.

10

**BACKGROUND OF THE INVENTION**

The gallium arsenide and indium phosphide integrated circuit industry has been limited without a technology that simultaneously allows the integration of complementary field effect transistor devices and transistors with low gate leakage currents. In contrast to silicon technology that has a very mature and useful complementary metal oxide semiconductor (CMOS) technology. Field effect transistor (FETs) widely used in the III-V semiconductor industry employ metal gates and Schotky gate contacts that are have quiescent-state leakage currents exceeding many microamps. The use of metal gates in compound semiconductor technology further results in individual transistors and integrated circuits that have excessively high power dissipation, reduced transconductance, reduced logic swing and the inability to operate on a single power supply, and generally limited performance characteristics. The high magnitude of the quiescent leakage current limits the maximum integration of GaAs devices to circuits of several hundred thousand transistors for those skilled in the art. In contrast, the simultaneous integration of many millions of transistors is possible at high integration densities using silicon CMOS technology. These

WO 02/15233

PCT/US01/25150

ultra high integration densities and levels cannot be obtained using metal, Schotky-style gates that are not insulated in compound semiconductor FETs. Thus Si CMOS technology offers significant advantages in terms of individual gate leakage, circuit integration level and cost.

5 However when compared to silicon, complementary GaAs and InP circuit technology exhibits faster and more optimized speed/power performance and efficiency at a low supply voltage of 1V and below. The market acceptance of these GaAs and InP integrated circuit technologies remains low because of the lack of ability to demonstrate high integration densities with low amounts of operating power. Thus, silicon CMOS dominates the field of

10 digital integrated circuitry and neither GaAs nor InP technologies can successfully penetrate this market.

What is needed are new and improved compound semiconductor field effect transistors (FET). What is also needed are new and improved compound semiconductor FETs using metal-oxide-semiconductor junctions (MOSFET). What is also needed are new and

15 improved compound semiconductor MOSFETs using a self-aligned gate structure. What is also needed are new and improved self-aligned compound semiconductor MOSFETs using enhancement mode and depletion mode operation. What is also needed are new and improved self-aligned compound semiconductor MOSFETs with stable and reliable device operation. What is also needed are new and improved self-aligned compound semiconductor MOSFETs

20 which enable optimum compound semiconductor device performance. What is also needed are new and improved self-aligned compound semiconductor MOSFETs with optimum efficiency and output power for RF and microwave applications. What is also needed are new and improved self-aligned compound semiconductor MOSFETs for use in complementary circuits and architectures. What is also needed are new and improved self-aligned compound

25 semiconductor MOSFETs for low power/high performance complementary circuits and

WO 02/15233

PCT/US01/25150

architectures. What is also needed are new and improved self-aligned compound semiconductor MOSFETs which offer the design flexibility of complementary architectures. What is also needed are new and improved self-aligned compound semiconductor MOSFETs which keep interconnection delays in ultra large scale integration under control. What is 5 needed are new and useful complementary integrated circuits where each individual transistor has a leakage current approaching  $10^{-12}$  amp. What is needed is a truly useful integrated circuit technology for GaAs and InP that allows for the useful and economical operation of ULSI digital integrated circuits in compound semiconductors. What is needed are new and improved compound semiconductor MOSFET integrated circuits with very low net power 10 dissipation. What is needed are new and improved compound semiconductor MOSFET devices with low gate leakage currents that may be integrated together to form ultra large scale integrated circuits that include millions of transistors. What is needed are new and improved complementary MOSFET devices and circuits in compound semiconductors that allow the direct use, transfer and application of silicon CMOS design that already exists in the 15 art.

What is also needed are new and improved methods of fabrication of self-aligned compound semiconductor MOSFETs. What is also needed is new and improved methods of fabrication of self-aligned compound semiconductor MOSFETs which are compatible with established complementary GaAs heterostructure FETs technologies. What is also needed 20 are new and improved compound semiconductor MOSFETs which are relatively easy to fabricate and use.

## BRIEF DESCRIPTION OF THE DRAWINGS

25 A more complete understanding of the present invention may be derived by referring to the

WO 02/15233

PCT/US01/25150

detailed description and claims when considered in connection with the figures, wherein like reference numbers refer to similar items throughout the figures, and:

FIG. 1 is simplified cross sectional view of a self-aligned enhancement mode compound

5 semiconductor MOSFET in accordance with a preferred embodiment of the present invention;

FIG. 2 is a simplified flow chart illustrating a method of manufacturing a self-aligned enhancement mode compound semiconductor MOSFET in accordance with a preferred embodiment of the present invention.

10 The exemplification set out herein illustrates a preferred embodiment of the invention in one form thereof, and such exemplification is not intended to be construed as limiting in any manner.

#### DETAILED DESCRIPTION OF THE DRAWINGS

15

The present invention provides, among other things, a self-aligned enhancement mode metal-oxide-compound semiconductor FET. The FET includes a gallium oxygen insulating structure that is composed of at least two distinct layers. The first layer is most preferably more than 10 angstroms thick but less than 25 angstroms in thickness and composed

20 substantially of gallium oxygen compounds including but not limited to stoichiometric  $\text{Ga}_2\text{O}_3$  and  $\text{Ga}_2\text{O}$ , and possibly a lesser fraction of other gallium oxygen compounds. The upper insulating layer in the gallium oxide insulating structure is composed of an insulator that does not intermix with the underlying gallium oxygen insulating structure. This upper layer must possess excellent insulating qualities, and is most typically composed of gallium oxygen and

25 a third rare earth element that together form a ternary insulating material. Therefore the entire

WO 02/15233

PCT/US01/25150

gallium oxide rare earth gate insulator structure is composed of at least two layers and may contain a third intermediate graded layers that consists of a mixture of the upper insulating material and the gallium oxygen compounds that compose the initial layer. Together the initial gallium oxygen layer, any intermediate graded layer and the top insulating region form

- 5 both a gallium oxide insulating structure and the gate insulator region of a metal-oxide-compound semiconductor field effect transistor. The initial substantially gallium oxygen layer forms an atomically abrupt interface with the top layer of the compound semiconductor wafer structure, and does not introduce midgap surface states into the compound semiconductor material. A refractory metal gate electrode is preferably positioned on the

- 10 upper surface of the gate insulator structure layer. The refractory metal is stable on the gate insulator structure layer at elevated temperature. Self-aligned source and drain areas, and source and drain contacts are positioned on the source and drain areas. In all embodiments preferred and otherwise, the metal-oxide-compound semiconductor transistor includes multi-layer gate insulator structure including an initial gallium oxygen layer, intermediate transition

- 15 layer, and upper insulating layer of 30-250 angstroms in thickness positioned on upper surface of a compound semiconductor heterostructure that form the gate insulator structure. The preferred embodiment also comprises a compound semiconductor heterostructure including a GaAs, Al<sub>x</sub> Ga<sub>1-x</sub> As and In<sub>y</sub> Ga<sub>1-y</sub> As layers with or without n-type and/or p-type charge supplying layers which are grown on a compound semiconductor substrate, a

- 20 refractory metal gate of W, WN, or WSi, self aligned donor (n-channel FET) or acceptor (p-channel FET) implants, and source and drain ohmic contacts. In another preferred embodiment, the compound semiconductor heterostructure comprises an In<sub>x</sub> Ga<sub>1-y</sub> As, Al<sub>x</sub> In<sub>1-x</sub> As, and InP compound semiconductor heterostructure and n-type and/or p-type charge supplying layers which are grown on an InP substrate, and a refractory metal gate of W, WN,

WO 02/15233

PCT/US01/25150

or WSi, self aligned donor (n-channel FET) or acceptor (p-channel FET) implants, and source and drain ohmic contacts.

FIG. 1 is simplified cross sectional view of a self-aligned enhancement mode compound semiconductor MOSFET in accordance with a preferred embodiment of the 5 present invention. Device 10 includes a compound semiconductor material, such as any III-V material employed in any semiconductor device, represented herein by a III-V semiconductor substrate 11 and a compound semiconductor epitaxial layer structure 12. For the purpose of this disclosure, the substrate 11 and any epitaxial layer structure 12 formed thereon will be referred to simply as a compound semiconductor wafer structure which in FIG. 1 is 10 designated 13. Methods of fabricating semiconductor wafer structure 13 include, but are not limited to, molecular beam epitaxy (MBE) and metal organic chemical vapor deposition (MOCVD). It will of course be understood that in some specific applications, there may be no epitaxial layers present and upper surface of top layer 15 may simply be the upper surface of substrate 11.

15 Device 10 further comprises a gate insulator structures (30) that includes at least two or more layers. The first layer of the gate insulator structure (31) is composed entirely of gallium oxide compounds and is directly adjacent to and deposited upon the compound semiconductor structure. The second layer of the gate insulator structure (32) is composed of a compound of gallium, oxygen, and one or more rare earth elements from the periodic table.

20 The initial gallium oxygen layer (31) forms an atomically abrupt interface 14 with the upper surface of top layer 15, the top layer of the compound semiconductor structure. A refractory metal gate electrode 17 which is stable in the presence of top insulating material at elevated temperature is positioned on upper surface 18 of the gate insulator structure. Dielectric spacers 26 are positioned to cover the sidewalls of metal gate electrode 17. Source and drain

WO 02/15233

PCT/US01/25150

contacts 19 and 20 are deposited on self-aligned source and drain areas 21 and 22, respectively.

In a specific embodiment, the compound semiconductor epitaxial layer structure consists of a <11 angstrom GaAs top layer (15), a <101 angstrom  $Al_xGa_{1-x}As$  spacer layer (23), a <251 angstrom  $In_xGa_{1-x}As$  channel layer (24), and a GaAs buffer layer (25) grown on a GaAs substrate (11). Top GaAs layer (15) is used to form an atomically abrupt layer with the gate insulator structure with an abrupt interface with low defect density.

As a simplified example of fabricating a self-aligned enhancement mode compound semiconductor MOSFET in accordance with a preferred embodiment of the present

- 10 invention, a III-V compound semiconductor wafer structure 13 with an atomically ordered and chemically clean upper surface of top layer 15 is prepared in an ultra-high vacuum semiconductor growth chamber and transferred via a ultra high vacuum transfer chamber to a second ultra high vacuum oxide and insulator deposition chamber. The initial gallium oxygen layer (31) is deposited on upper compound semiconductor surface layer 15 using thermal evaporation from a high purity  $Ga_2O_3$  source or from crystalline gadolinium gallium garnet,  $Ga_3Gd_5O_{12}$ . This initial gallium oxygen layer is deposited while holding the substrate temperature of the compound semiconductor structure at <580°C, and most preferably at a substrate temperature <495°C. After the deposition of approximately 18 angstroms of gallium oxygen compounds in the insulator deposition chamber over a 5 to 8 minute period of time,

- 20 deposition of the second insulator layer is initiated. The deposition of the second insulator layer starts by directing the flux from a low power oxygen plasma source into the ultra high vacuum system such that the oxygen plasma effluent and species are largely directed toward and impinging upon said compound semiconductor structure with initial gallium oxygen layer. The flux from the oxygen plasma source should be directed at the surface for between

- 25 2-5 seconds, subsequently followed by the co-evaporation of gallium oxygen compounds

WO 02/15233

PCT/US01/25150

from  $\text{Ga}_2\text{O}_3$  and a second thermal evaporation source that contains a rare-earth element. The flux beams from the oxygen source,  $\text{Ga}_2\text{O}_3$  and rare-earth evaporation source thermal evaporation sources are carefully balanced to provide a ternary insulator layer on top of the initial gallium oxygen layer on said compound semiconductor structure. As the deposition of 5 the second ternary insulator layer is initiated, the substrate temperature is simultaneously adjusted to provide an optimized substrate temperature for the deposition of this layer. In this example the substrate temperature required to deposit the gallium+oxygen+rare earth layer is <530°C. The deposition of this second insulator layer proceeds until the total insulator thickness of 200-250 angstroms is achieved. Shutters and valves are utilized to stop the 10 deposition of the ternary gallium+oxygen+rare earth layer upon the deposition of the required thickness of the insulator layer. The substrate temperature is cooled in-vacuum to approximately 200°C, and the deposition of a refractory metal which is stable and does not interdiffuse with on the top layer of the gate insulator structure at elevated temperature such as WSi or WN is deposited on upper surface 18 of oxide layer 32 and subsequently patterned 15 using standard lithography. The refractory metal layer is etched until oxide layer 31 is exposed using a refractory metal etching technique such as a fluorine based dry etching process. The refractory metal etching procedure does not etch the oxide layer 31, thus, oxide layer 31 functions as an etch stop layer such that upper surface of top layer 15 remains protected by oxide layer 31. All processing steps are performed using low damage plasma 20 processing. Self-aligned source and drain areas 21 and 22, respectively are realized by ion implantation of Si (n-channel device) and Be/F or C/F (p-channel device) using the refractory metal gate electrode 17 and the dielectric spacers 26 as implantation masks. Such ion implantation schemes are compatible with standard processing of complementary compound 25 semiconductor heterostructure FET technologies and are well known to those skilled in the art. The implants are activated at 700-900°C using rapid thermal annealing in an ultra high

WO 02/15233

PCT/US01/25150

vacuum environment such that degradation of the interface 16 established between top layer 15 and oxide layer 31 is completely excluded. Finally, ohmic source and drain contacts 19 and 20 are deposited on the self-aligned source and drain areas 21 and 22, respectively. The devices may then be interconnected using the standard methods to those skilled in the art of integrated microelectronics and integrated circuit manufacture.

FIG. 2 is a simplified flow chart illustrating a method of manufacturing a self-aligned enhancement mode compound semiconductor MOSFET in accordance with a preferred embodiment of the present invention. In step 102, a compound semiconductor wafer structure is produced using standard epitaxial growth methods in the art. In step 103, a layer consisting of gallium oxygen compounds including but not limited to  $\text{Ga}_2\text{O}_3$  and  $\text{Ga}_2\text{O}$  is deposited on upper surface of said compound semiconductor wafer structure. In step 104, an insulating layer of gallium oxygen and one or more rare earth elements is deposited on the upper surface of the initial gallium oxygen compound layer. The gallium oxide gate insulator structure is formed in steps 104 and 105. In step 106, a stable refractory gate metal is positioned on upper surface of said gate insulator structure. In step 108, source and drain ion implants are provided self-aligned to the gate electrode. In step 110, source and drain ohmic contacts are positioned on ion implanted source and drain areas.

In a preferred embodiment, step 100 provides a compound semiconductor substrate such as GaAs or InP. Step 102 includes the preparation and epitaxial growth of an atomically ordered and chemically clean upper surface of the compound semiconductor wafer structure. Step 103 preferably comprises thermal evaporation from a purified and crystalline gadolinium gallium garnet or  $\text{Ga}_2\text{O}_3$  source on an atomically ordered and chemically clean upper surface of the compound semiconductor wafer structure. Step 104 comprises the formation of a gallium+oxygen+rare earth elemental insulating layer formed through the simultaneous vacuum evaporation of gallium oxygen species and at least one rare earth

WO 02/15233

PCT/US01/25150

element such as Gadolinium with the simultaneous oxidation using the effluent of an oxygen gas plasma source directed in simultaneous combination with other thermal evaporation sources toward substrate 100. The initial gallium oxygen compound layer of the gate insulator structure preferably functions as an etch stop layer such that the upper surface of the

5 compound semiconductor wafer structure remains protected by the gate oxide during and after gate metal etching. The refractory gate metal desirably does not react with or diffuse into the gate oxide layer during high temperature annealing of the self-aligned source and drain ion implants. The quality of the interface formed by the gate oxide layer and the upper surface of the compound semiconductor structure is desirably preserved during high

10 temperature annealing of the self-aligned source and drain ion implants. The self-aligned source and drain implants are desirably annealed at approximately 700°C in an ultra high vacuum environment. The self-aligned source and drain implants are desirably realized by positioning dielectric spacers on the sidewalls of the refractory gate metal.

Thus, new and improved compound semiconductor devices and methods of

15 fabrication are disclosed. The new and improved self-aligned enhancement mode metal-oxide-compound semiconductor heterostructure field effect transistors enable stable and reliable device operation, provide optimum compound semiconductor device performance for low power/high performance complementary circuits and architectures, keep interconnection delay in ULSI under control, and provide optimum efficiency and output power for RF and

20 microwave applications as well as for digital integrated circuits that require very high integration densities.

These improvements essentially solve or overcome the problems of the prior art, such as high gate leakage in compound semiconductor FET devices, low integration densities, dc electrical instability, and electrical hysteresis, and therefore provide a highly useful invention.

25 While we have shown and described specific embodiments of the present invention, further

WO 02/15233

PCT/US01/25150

modifications and improvements will occur to those skilled in the art. We desire it to be understood, therefore, that this invention is not limited to the particular forms shown and we intend in the appended claims to cover all modifications that do not depart from the spirit and scope of this invention.

WO 02/15233

PCT/US01/25150

## What is claimed:

1. An enhancement mode metal-oxide-compound semiconductor field effect transistor comprising:

- a compound semiconductor wafer structure having an upper surface;

- 5 a layer composed of the compounds of gallium and oxygen including but not limited to mixtures of Ga<sub>2</sub>O<sub>3</sub>, Ga<sub>2</sub>O and other gallium oxygen compounds positioned on upper surface of said compound semiconductor wafer structure;

- a second insulating layer composed of the compounds of gallium and oxygen and at least one or more rare earth elements that form an insulating layer deposited on top of the initial

- 10 supporting gallium oxygen layer, with said first and second layers forming a gate insulator structure adjacent to and on top of the compound semiconductor structure;

- a stable refractory metal gate electrode positioned on upper surface of said gate insulator structure layers;

- source and drain ion implants self-aligned to the gate electrode; and

- 15 source and drain ohmic contacts positioned on ion implanted source and drain areas; wherein the refractory metal gate electrode comprises a refractory metal selected from the group consisting of W, WN or WSi or combinations thereof;

- means of interconnection of said transistors forming a monolithically integrated circuit.

2. An enhancement mode metal-oxide-compound semiconductor field effect transistor as claimed in claim 1 wherein the initial layer of gallium oxygen compounds forms an atomically abrupt interface with the upper surface of the compound semiconductor wafer structure.

3. An enhancement mode metal-oxide-compound semiconductor field effect transistor as claimed in claim 1 wherein the gate insulator structure is composed of three layers, an initial

- 25 gallium oxygen compound layer, a graded layer that contains varying compositions of

WO 02/15233

PCT/US01/25150

gallium oxygen and at least one rare-earth element, and a third insulator layer that is composed largely of a compound of gallium, oxygen and one or more rare earth elements.

4. An enhancement mode metal-oxide-compound semiconductor field effect transistor as claimed in claim 1 wherein the gate insulator structure is composed of more than three

5 multiple layers, an initial gallium oxygen compound layer, and multiple layers containing gallium and oxygen with or without the inclusion of one or more rare earth elements that together form an insulating gallium oxide gate insulator structure.

5. An enhancement mode metal-oxide-compound semiconductor field effect transistor as claimed in claim 1 wherein the initial gallium oxygen compound layer has a thickness of

10 more than 10 angstroms and less than 25 angstroms.

6. An enhancement mode metal-oxide-compound semiconductor field effect transistor as claimed in claim 1 wherein the gate insulator structure has an overall total thickness of 20-300 angstroms.

7. An enhancement mode metal-oxide-compound semiconductor field effect transistor as

15 claimed in claim 1 wherein the initial gallium oxygen compound layer forms an atomically abrupt interface with the compound semiconductor structure that extend less than four atomic layers in depth of structural interface modulation.

8. An enhancement mode metal-oxide-compound semiconductor field effect transistor as

claimed in claim 1 wherein the initial gallium and oxygen compound layer and the gate

20 insulator structure protects the upper surface of the compound semiconductor wafer structure.

9. An enhancement mode metal-oxide-compound semiconductor field effect transistor as

claimed in claim 1 wherein the refractory metal gate electrode comprises a refractory metal which is stable in presence of the top layer of the gate insulator structure at an elevated

temperature of 700°C and above.

25 10. An enhancement mode metal-oxide-compound semiconductor field effect transistor as

WO 02/15233

PCT/US01/25150

claimed in claim 1 wherein the source and drain ion implants comprising said enhancement mode metal-oxide-compound semiconductor field effect transistor being an n-channel device or p-channel device.

11. An enhancement mode metal-oxide-compound semiconductor field effect transistor as

5 claimed in claim 1 wherein the source and drain ion implants comprise and Be/F or C/F, said enhancement mode metal-oxide-compound semiconductor field effect transistor being a p-channel device.

12. An enhancement mode metal-oxide-compound semiconductor field effect transistor as

claimed in claim 1 wherein the upper surface of the compound semiconductor wafer structure

10 comprises GaAs.

13. An enhancement mode metal-oxide-compound semiconductor field effect transistor as

claimed in claim 1 wherein the upper surface of the compound semiconductor wafer structure

comprises  $In_xGa_{1-x}As$ .

14. An enhancement mode metal-oxide-compound semiconductor field effect transistor

15 comprising:

a compound semiconductor wafer structure having an upper surface;

a layer composed of the compounds of gallium and oxygen compounds including but not

limited to mixtures of  $Ga_2O_3$ ,  $Ga_2O$  and other gallium oxygen compounds positioned on

upper surface of said compound semiconductor wafer structure;

20 a second insulating layer deposited upon the first composed of the compounds of gallium and

oxygen and at least one or more rare earth elements such that the normalized relative

composition of gallium, oxygen, and one or more rare earth elements are changing in a

monotonic manner as a function of the thickness within said insulating layer;

a third insulating layer deposited on top of said second layer composed of gallium oxygen

25 and at least one or more rare earth elements wherein said first, second and third layers form a

WO 02/15233

PCT/US01/25150

gate insulator structure adjacent to and deposited on top of the compound semiconductor structure;

a stable refractory metal gate electrode positioned on upper surface of said gate insulator structure layers;

5 source and drain ion implants self-aligned to the gate electrode; and

source and drain ohmic contacts positioned on ion implanted source and drain areas;

wherein the refractory metal gate electrode comprises a refractory metal selected from the group consisting of W, WN or WSi or combinations thereof;

means of interconnection of said transistors forming a monolithic integrated circuit.

10 15. An enhancement mode metal-oxide-compound semiconductor field effect transistor as claimed in claim 14 wherein the initial layer of gallium oxygen compounds forms an atomically abrupt interface with the upper surface of the compound semiconductor wafer structure.

16. An enhancement mode metal-oxide-compound semiconductor field effect transistor as

15 claimed in claim 14 wherein the gate insulator structure is composed of three or more layers, an initial gallium oxygen compound layer, a graded layer that contains varying compositions of gallium oxygen and at least one rare-earth element, and a third insulator layer that is composed largely of a compound of gallium, oxygen and one or more rare earth elements.

17. An enhancement mode metal-oxide-compound semiconductor field effect transistor as

20 claimed in claim 14 wherein the initial gallium oxygen compound layer has a thickness of more than 10 angstroms and less than 25 angstroms.

18. An enhancement mode metal-oxide-compound semiconductor field effect transistor as

claimed in claim 14 wherein the gate insulator structure has an overall total thickness of 20-300 angstroms.

WO 02/15233

PCT/US01/25150

19. An enhancement mode metal-oxide-compound semiconductor field effect transistor as claimed in claim 14 wherein the initial gallium oxygen compound layer forms an atomically abrupt interface with the compound semiconductor structure that extend less than four atomic layers in depth of modulation of said interface.

- 5 20. An enhancement mode metal-oxide-compound semiconductor field effect transistor as claimed in claim 14 wherein the initial gallium and oxygen compound layer and the gate insulator structure protects the upper surface of the compound semiconductor wafer structure.

21. An enhancement mode metal-oxide-compound semiconductor field effect transistor as claimed in claim 14 wherein the refractory metal gate electrode comprises a refractory metal 10 which is stable in presence of the top layer of the gate insulator structure at an elevated temperature of 700°C and above.

22. An enhancement mode metal-oxide-compound semiconductor field effect transistor as claimed in claim 14 wherein the source and drain ion implants comprising said enhancement mode metal-oxide-compound semiconductor field effect transistor being an n-channel device.

- 15 23. An enhancement mode metal-oxide-compound semiconductor field effect transistor as claimed in claim 14 wherein the source and drain ion implants comprise and Be/F and C/F, said enhancement mode metal-oxide-compound semiconductor field effect transistor being a p-channel device.

24. An enhancement mode metal-oxide-compound semiconductor field effect transistor as 20 claimed in claim 14 wherein the upper surface of the compound semiconductor wafer structure comprises GaAs.

25. An enhancement mode metal-oxide-compound semiconductor field effect transistor as claimed in claim 14 wherein the upper surface of the compound semiconductor wafer structure comprises  $In_xGa_{1-x}As$ .

WO 02/15233

PCT/US01/25150

26. An enhancement mode metal-oxide-compound semiconductor field effect transistor comprising:

a compound semiconductor wafer structure having an upper surface;

a multilayer gate insulator structure composed of alternating layers comprised of gallium,

5 oxygen, at least one rare-earth element forming a gate insulator with low electronic midgap defect density positioned on upper surface of said compound semiconductor wafer structure;

a stable refractory metal gate electrode positioned on upper surface of said gate insulator structure layer;

source and drain ion implants self-aligned to the gate electrode; and

10 source and drain ohmic contacts positioned on ion implanted source and drain areas,

wherein dielectric spacers are positioned on sidewalls of the stable refractory gate metal electrode.

27. An enhancement mode metal-oxide-compound semiconductor field effect transistor comprising:

15 a compound semiconductor wafer structure having an upper surface;

a gate insulator structure positioned on upper surface of said compound semiconductor wafer structure;

a stable refractory metal gate electrode positioned on upper surface of said gate insulator structure;

20 source and drain ion implants self-aligned to the gate electrode; and

source and drain ohmic contacts positioned on ion implanted source and drain areas,

wherein the compound semiconductor wafer structure comprises a wider band gap spacer layer and a narrower band gap channel layer.

28. An enhancement mode metal-oxide-compound semiconductor field effect transistor as

25 claimed in claim 27 wherein the wider band gap spacer layer is positioned between the gate

WO 02/15233

PCT/US01/25150

oxide layer and the narrower band gap channel layer.

29. An enhancement mode metal-oxide-compound semiconductor field effect transistor as claimed in claim 27 wherein the wider band gap spacer layer has a thickness of between 3-200 angstroms

5 30. An enhancement mode metal-oxide-compound semiconductor field effect transistor as claimed in claim 27 wherein the wider band gap spacer layer comprises either  $Al_xGa_{1-x}As$ ,  $InP$ , or  $In_xGa_{1-x}P$  or a combination thereof.

31. An enhancement mode metal-oxide-compound semiconductor field effect transistor as claimed in claim 27 wherein the narrower band gap channel layer has a thickness of 10-300 10 angstroms.

32. An enhancement mode metal-oxide-compound semiconductor field effect transistor as claimed in claim 27 wherein the narrower band gap channel layer is positioned between the wider band gap spacer layer and a buffer layer.

33. An enhancement mode metal-oxide-compound semiconductor field effect transistor as claimed in claim 27 wherein the narrower band gap channel layer comprises  $In_yGa_{1-y}As$ .

15 34. An enhancement mode metal-oxide-compound semiconductor field effect transistor comprising:

a compound semiconductor wafer structure having an upper surface;

a gate insulator structure positioned on upper surface of said compound semiconductor wafer 20 structure;

a stable refractory metal gate electrode positioned on upper surface of said gate insulator structure layer;

source and drain ion implants self-aligned to the gate electrode; and

source and drain ohmic contacts positioned on ion implanted source and drain areas,

25

WO 02/15233

PCT/US01/25150

wherein the compound semiconductor wafer structure comprises a  $Al_xGa_{1-x}As$ ,  $In_yGa_{1-y}As$ ,  $InP$ , or  $In_xGa_{1-x}P$  layer, said layer being positioned on upper surface of a compound semiconductor substrate.

35. An enhancement mode metal-oxide-compound semiconductor field effect transistor as

5 claimed in claim 34 wherein the compound semiconductor substrate includes a GaAs based semiconductor wafer.

36. An enhancement mode metal-oxide-compound semiconductor field effect transistor as

claimed in claim 34 wherein the compound semiconductor substrate includes a InP based semiconductor wafer.

10 37. An enhancement mode metal-oxide-compound semiconductor field effect transistor as

claimed in claim 1, 13, 26, and 33 that may be integrated together with similar and

complementary transistor devices to form complementary metal-oxide compound

semiconductor integrated circuits.

15

19

Figure 1

Figure 2

## 【国際公開パンフレット（コレクトバージョン）】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

21 February 2002 (21.02.2002)

PCT

(10) International Publication Number

WO 02/15233 A3(51) International Patent Classification: H01L 31/0328,

31/0336, 31/072, 31/109CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH,

GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC,

LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW,

MX, MZ, NO, NZ, PL, PT, RO, RU, SD, SE, SG, SI, SK,

SL, TJ, TM, TR, TT, TZ, UA, UG, US, UZ, VN, YU, ZA,

ZW.

(21) International Application Number: PCT/US01/25150

(22) International Filing Date: 10 August 2001 (10.08.2001)

(25) Filing Language:

English

(84) Designated States (regional): ARIPO patent (GH, GM,

KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZW), Eurasian

patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European

patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE,

IT, LU, MC, NL, PT, SE, TR), OAPI patent (BF, BJ, CF,

CG, CL, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD,

TG).

(26) Publication Language:

English

(30) Priority Data:

09/636,484 10 August 2000 (10.08.2000) US

(71) Applicant and

(72) Inventor: BRADDOCK, Walter David IV [US/US]; 300

First St. N.E., Rochester, MN 55906 (US).

Published:

— with international search report

(88) Date of publication of the international search report:

27 June 2002(74) Agents: BRADDOCK, Christopher, T. et al.; 217 East

Seventh Avenue, Denver, CO 80203 (US).(81) Designated States (nationally): AE, AG, AL, AM, AT, AU,

AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU,

ES, GE, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC,

LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW,

MX, MZ, NO, NZ, PL, PT, RO, RU, SD, SE, SG, SI, SK,

SL, TJ, TM, TR, TT, TZ, UA, UG, US, UZ, VN, YU, ZA,

ZW.

(54) Title: INTEGRATED TRANSISTOR DEVICES

WO 02/15233 A3

(57) Abstract: A self-aligned enhancement mode metal-oxide-compound semiconductor field effect transistor (10) includes a lower oxide layer that is a mixture of  $\text{Ga}_2\text{O}_3$ ,  $\text{Ga}_2\text{O}_5$ , and other gallium oxide compounds (30), and a second insulating layer that is positioned immediately on top of the gallium oxygen layer together positioned on upper surface (14) of a III-V compound semiconductor wafer structure (13). Together the lower gallium oxide compound layer and the second insulating layer form a gallium oxide gate insulating structure. The gallium oxide gate insulating structure and underlying compound semiconductor gallium arsenide layer (15) meet at an atomically abrupt interface at the surface of the with the compound semiconductor wafer structure (14). The initial essentially gallium oxygen layer serves to passivate and protect the underlying compound semiconductor wafer from the second insulating oxide layer. A refractory metal gate electrode layer (17) is positioned on upper surface (18) of the second insulating oxide layer. The refractory metal is stable on the second insulating oxide layer at elevated temperature. Self-aligned source and drain areas, and source and drain contacts (19, 20) are positioned on the source and drain areas (21, 22) of the device. Multiple devices are then positioned in proximity and the appropriate interconnection metal layers and insulators are utilized in concert with other passive circuit elements to form a integrated circuit structure.

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                    | International application No.<br>PCT/US01/25150                   |            |                                                                                    |                       |   |                                                                        |       |     |  |       |   |                                                                     |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------|------------------------------------------------------------------------------------|-----------------------|---|------------------------------------------------------------------------|-------|-----|--|-------|---|---------------------------------------------------------------------|------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>IPC(7) : H01L 31/0328, 31/0336, 31/072, 31/109<br>US CL : 257/192, 392, 410, 411, 631; 438/216, 261, 285, 421, 591, 590, 595<br>According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                    |                                                                   |            |                                                                                    |                       |   |                                                                        |       |     |  |       |   |                                                                     |      |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>U.S. : 257/192, 392, 410, 411, 631; 438/216, 261, 285, 421, 591, 590, 595                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                    |                                                                   |            |                                                                                    |                       |   |                                                                        |       |     |  |       |   |                                                                     |      |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched<br>NONE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                    |                                                                   |            |                                                                                    |                       |   |                                                                        |       |     |  |       |   |                                                                     |      |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br>Please See Continuation Sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                    |                                                                   |            |                                                                                    |                       |   |                                                                        |       |     |  |       |   |                                                                     |      |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b> <table border="1" style="width: 100%; border-collapse: collapse;"> <thead> <tr> <th style="width: 10%;">Category *</th> <th style="width: 60%;">Citation of document, with indication, where appropriate, of the relevant passages</th> <th style="width: 30%;">Relevant to claim No.</th> </tr> </thead> <tbody> <tr> <td>X</td> <td>US 5,945,718 A (PASSLACK et al) 31 August 1999 (31.08.1999), Figure 1.</td> <td>27-37</td> </tr> <tr> <td>---</td> <td></td> <td>-----</td> </tr> <tr> <td>A</td> <td>US 5,665,658 A (PASSLACK) 09 September 1997 (09.09.1997), Figure 5.</td> <td>1-26</td> </tr> </tbody> </table> |                                                                                    |                                                                   | Category * | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No. | X | US 5,945,718 A (PASSLACK et al) 31 August 1999 (31.08.1999), Figure 1. | 27-37 | --- |  | ----- | A | US 5,665,658 A (PASSLACK) 09 September 1997 (09.09.1997), Figure 5. | 1-26 |

| Category *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No.                                             |            |                                                                                    |                       |   |                                                                        |       |     |  |       |   |                                                                     |      |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | US 5,945,718 A (PASSLACK et al) 31 August 1999 (31.08.1999), Figure 1.             | 27-37                                                             |            |                                                                                    |                       |   |                                                                        |       |     |  |       |   |                                                                     |      |

| ---                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                    | -----                                                             |            |                                                                                    |                       |   |                                                                        |       |     |  |       |   |                                                                     |      |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | US 5,665,658 A (PASSLACK) 09 September 1997 (09.09.1997), Figure 5.                | 1-26                                                              |            |                                                                                    |                       |   |                                                                        |       |     |  |       |   |                                                                     |      |

| <input type="checkbox"/> Further documents are listed in the continuation of Box C. <input type="checkbox"/> See patent family annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                    |                                                                   |            |                                                                                    |                       |   |                                                                        |       |     |  |       |   |                                                                     |      |

| * Special categories of cited documents:<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier application or patent published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed                                                       |                                                                                    |                                                                   |            |                                                                                    |                       |   |                                                                        |       |     |  |       |   |                                                                     |      |

| Date of the actual completion of the international search<br>02 March 2002 (02.03.2002)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                    | Date of mailing of the international search report<br>04 APR 2002 |            |                                                                                    |                       |   |                                                                        |       |     |  |       |   |                                                                     |      |