(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6152014号

(P6152014)

(45) 発行日 平成29年6月21日(2017.6.21)

(24) 登録日 平成29年6月2日(2017.6.2)

(51) Int.Cl.

H04N 1/028 (2006.01)

G06T 1/00 (2006.01)

F 1

H04N 1/028

G06T 1/00 460Z

請求項の数 10 (全 12 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2013-169924 (P2013-169924) |

| (22) 出願日  | 平成25年8月19日 (2013.8.19)       |

| (65) 公開番号 | 特開2015-39148 (P2015-39148A)  |

| (43) 公開日  | 平成27年2月26日 (2015.2.26)       |

| 審査請求日     | 平成28年6月16日 (2016.6.16)       |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100076428<br>弁理士 大塚 康徳                     |

| (74) 代理人  | 100112508<br>弁理士 高柳 司郎                     |

| (74) 代理人  | 100115071<br>弁理士 大塚 康弘                     |

| (74) 代理人  | 100116894<br>弁理士 木村 秀二                     |

| (74) 代理人  | 100130409<br>弁理士 下山 治                      |

| (74) 代理人  | 100134175<br>弁理士 永川 行光                     |

最終頁に続く

(54) 【発明の名称】スペクトラム拡散クロック生成回路、クロック乗せ換え回路、集積回路及び画像読み取り装置

## (57) 【特許請求の範囲】

## 【請求項 1】

入力された基準クロックに基づいてスペクトラム拡散クロックを生成して出力する生成部と、

1つの基準時刻について、当該基準時刻以降に前記生成部に入力された基準クロックのパルス数と、当該基準時刻以降に前記生成部から出力されたスペクトラム拡散クロックのパルス数との差を監視する監視部と、

前記差が所定の範囲に含まれるように、前記生成部によって生成されるスペクトラム拡散クロックの周波数を制御する制御部とを備え、

前記監視部は、

10

前記基準クロックによって駆動される第1巡回シフトレジスタと、

前記スペクトラム拡散クロックによって駆動される第2巡回シフトレジスタと、

前記第1巡回シフトレジスタからの出力と前記第2巡回シフトレジスタからの出力とによって内部状態が決まるセットリセットフリップフロップ回路群と、

前記セットリセットフリップフロップ回路群からの出力に基づいて前記差を取得する取得部とを含み、

前記基準クロックの周波数は時間を通じて一定であることを特徴とするスペクトラム拡散クロック生成回路。

## 【請求項 2】

前記制御部は、前記差が閾値を超えたかどうかの判定を行い、前記差が前記閾値を超え

20

た場合に、前記差が低減するように、前記生成部によって生成されるスペクトラム拡散クロックの周波数を制御することを特徴とする請求項1に記載のスペクトラム拡散クロック生成回路。

**【請求項3】**

前記制御部は、前記差が変化するごとに前記判定を行うことを特徴とする請求項2に記載のスペクトラム拡散クロック生成回路。

**【請求項4】**

前記制御部は、前記生成部に前記基準クロックが入力されるごと及び前記生成部から前記スペクトラム拡散クロックが出力されるごとに前記判定を行うことを特徴とする請求項2又は3に記載のスペクトラム拡散クロック生成回路。

10

**【請求項5】**

前記制御部は、基準クロックのパルス数とスペクトラム拡散クロックのパルス数との前記差が、前記第1巡回シフトレジスタの段数以下、かつ、前記第2巡回シフトレジスタの段数以下に收まるように、スペクトラム拡散クロックの周波数を制御することを特徴とする請求項1乃至4の何れか1項に記載のスペクトラム拡散クロック生成回路。

**【請求項6】**

前記第1巡回シフトレジスタの段数と、前記第2巡回シフトレジスタの段数とは互いに等しく、

前記セットリセットフリップフロップ回路群は、前記第1巡回シフトレジスタの段数に等しい個数のセットリセットフリップフロップ回路を含むことを特徴とする請求項1乃至5の何れか1項に記載のスペクトラム拡散クロック生成回路。

20

**【請求項7】**

請求項1乃至6の何れか1項に記載のスペクトラム拡散クロック生成回路と、

前記スペクトラム拡散クロック生成回路に供給される基準クロックを生成する発振回路と、

前記スペクトラム拡散クロック生成回路から出力されたスペクトラム拡散クロックによって駆動される回路素子とを備えることを特徴とする集積回路。

**【請求項8】**

請求項1乃至6の何れか1項に記載のスペクトラム拡散クロック生成回路と、

メモリと、

30

基準クロックに従って入力データを前記メモリに書き込む書き込み部と、

前記スペクトラム拡散クロック生成回路から出力されたスペクトラム拡散クロックに従って前記メモリからデータを読み出して出力する読み出し部とを備えることを特徴とするクロック乗せ換え回路。

**【請求項9】**

請求項1乃至6の何れか1項に記載のスペクトラム拡散クロック生成回路と、

メモリと、

前記スペクトラム拡散クロック生成回路から出力されたスペクトラム拡散クロックを受け、前記スペクトラム拡散クロックのパルスが入力されるごとに前記メモリからデータを読み出す読み出し部とを備えるクロック乗せ換え回路であって、

40

前記第1巡回シフトレジスタの段数及び前記第2巡回シフトレジスタの段数はそれぞれM段であり、

前記メモリは、少なくともM個のデータを保持し、

前記制御部は、前記メモリ内の出力待ちのデータ数がM個以下となるように、前記スペクトラム拡散クロックの周波数を制御することを特徴とするクロック乗せ換え回路。

**【請求項10】**

請求項8又は9に記載のクロック乗せ換え回路と、

前記クロック乗せ換え回路に供給される基準クロックを生成する発振回路と、

原稿を読み取って画像データを生成し、当該画像データを前記クロック乗せ換え回路に供給する読み取り部と、

50

前記クロック乗せ換え回路から出力された画像データを処理する処理部とを備えることを特徴とする画像読み取り装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スペクトラム拡散クロック生成回路、クロック乗せ換え回路、集積回路及び画像読み取り装置に関する。

【背景技術】

【0002】

EMI(電磁障害)を低減するために、周波数が一定の基準クロックに対してスペクトラム拡散を行って、周波数が変動するスペクトラム拡散クロックを生成するスペクトラム拡散クロック生成回路が知られている。特許文献1は、画像処理の前半を基準クロックに従って動作する画像処理前半ブロックで行い、画像処理の後半をスペクトラム拡散クロックに従って動作する画像処理後半ブロックで行う画像形成装置を提案する。画像処理前半ブロックからの出力データは外部メモリコントローラに供給され、外部メモリコントローラはこのデータを外部メモリに格納する。その後、外部メモリコントローラは外部メモリからデータを読み出して、画像処理後半ブロックへ供給する。このように、外部メモリコントローラはクロック乗せ換え回路として動作する。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2007-150560号公報

20

【発明の概要】

【発明が解決しようとする課題】

【0004】

外乱等の影響でスペクトラム拡散クロック生成回路の周波数制御が乱れ、スペクトラム拡散クロックが生成されるべき周波数から外れた場合に、特許文献1の外部メモリコントローラは外部メモリから正しいデータを読み出せなくなることがある。例えば、スペクトラム拡散クロックの周波数が、生成されるべき周波数よりも高い場合には、外部メモリに書き込まれるデータよりも読み出されるデータが多くなり、外部メモリが空になる。一方、スペクトラム拡散クロックの周波数が、生成されるべき周波数よりも低い場合には、外部メモリに書き込まれるデータよりも読み出されるデータが少なくなり、外部メモリがフルになる。外部メモリのサイズを大きくすればスペクトラム拡散クロックの大きな変動を許容できるが、コストが高くなる。そこで、本発明は、クロック乗せ換え回路が使用するメモリのサイズを低減可能なスペクトラム拡散クロックを生成するための技術を提供することを目的とする。

30

【課題を解決するための手段】

【0005】

上記課題に鑑みて、本発明の一部の実施形態によるスペクトラム拡散クロック生成回路は、入力された基準クロックに基づいてスペクトラム拡散クロックを生成して出力する生成部と、1つの基準時刻について、当該基準時刻以降に前記生成部に入力された基準クロックのパルス数と、当該基準時刻以降に前記生成部から出力されたスペクトラム拡散クロックのパルス数との差を監視する監視部と、前記差が所定の範囲に含まれるように、前記生成部によって生成されるスペクトラム拡散クロックの周波数を制御する制御部とを備え、前記監視部は、前記基準クロックによって駆動される第1巡回シフトレジスタと、前記スペクトラム拡散クロックによって駆動される第2巡回シフトレジスタと、前記第1巡回シフトレジスタからの出力と前記第2巡回シフトレジスタからの出力とによって内部状態が決まるセットリセットフリップフロップ回路群と、前記セットリセットフリップフロップ回路群からの出力に基づいて前記差を取得する取得部とを含み、前記基準クロックの周波数は時間を通じて一定である。

40

50

**【発明の効果】****【0006】**

上記手段により、クロック乗せ換え回路が使用するメモリのサイズを低減可能なスペクトラム拡散クロックを生成するための技術が提供される。

**【図面の簡単な説明】****【0007】**

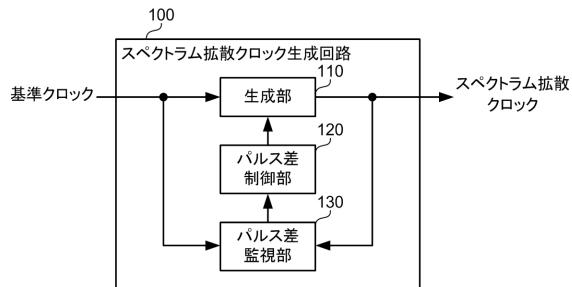

【図1】本発明の一部の実施形態のスペクトラム拡散クロック生成回路のブロック図。

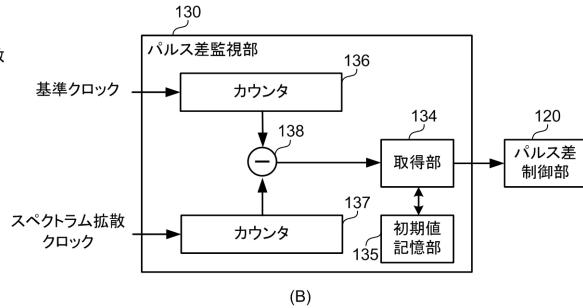

【図2】図1のスペクトラム拡散クロック生成回路の生成部のブロック図。

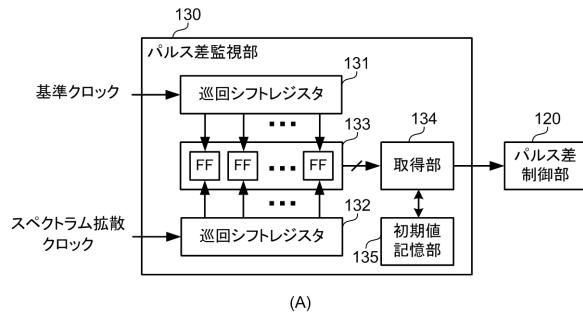

【図3】図1のスペクトラム拡散クロック生成回路のパルス差監視部のブロック図。

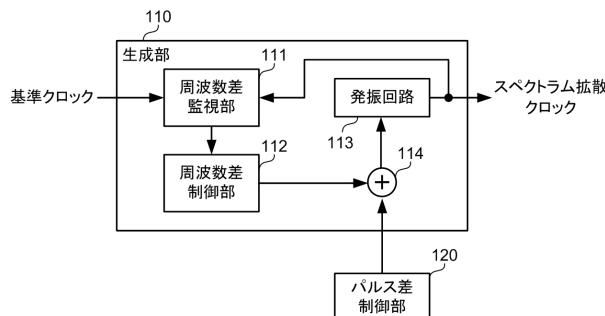

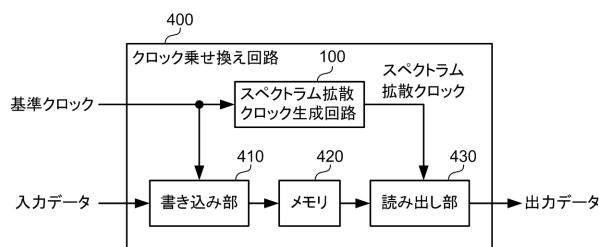

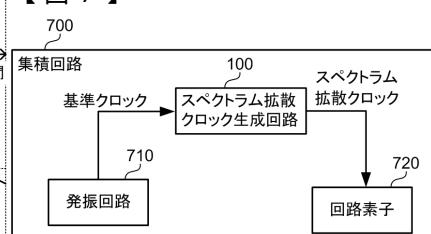

【図4】本発明の一部の実施形態のクロック乗せ換え回路のブロック図。 10

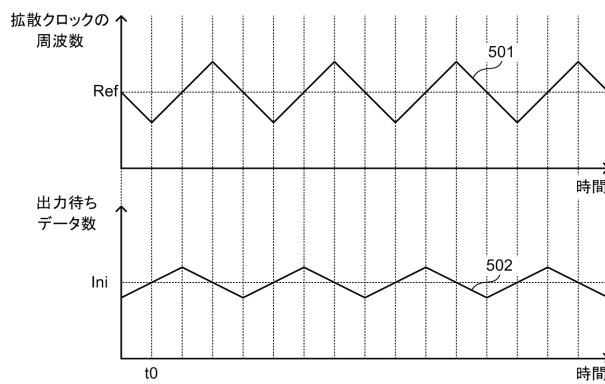

【図5】図4のクロック乗せ換え回路のメモリ状態を説明する図。

【図6】図4のクロック乗せ換え回路のメモリ状態を説明する図。

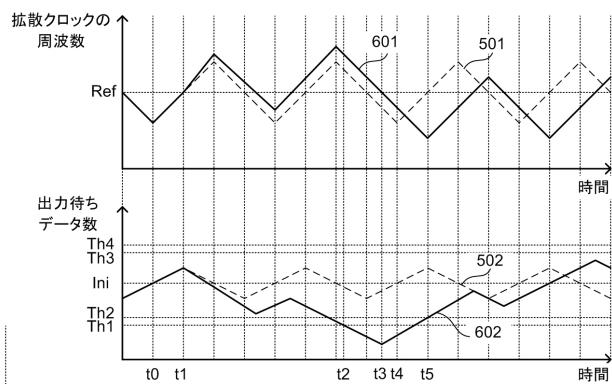

【図7】本発明の一部の実施形態の集積回路のブロック図。

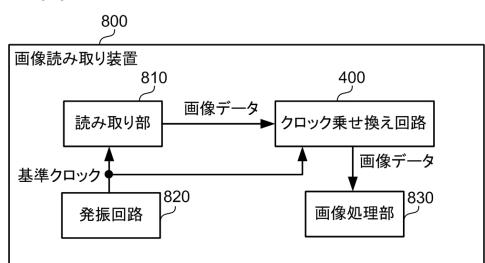

【図8】本発明の一部の実施形態の画像読み取り装置のブロック図。

**【発明を実施するための形態】****【0008】**

添付の図面を参照しつつ本発明の実施形態について以下に説明する。様々な実施形態を通じて同様の要素には同一の参照符号を付して重複する説明を省略する。また、各実施形態は適宜変更、組み合わせが可能である。

**【0009】**

図1のブロック図を参照して、本発明の一部の実施形態に係るスペクトラム拡散クロック生成回路100の構成例を説明する。スペクトラム拡散クロック生成回路100は、外部から入力された基準クロックに基づいてスペクトラム拡散クロックを生成し、このスペクトラム拡散クロックを外部へ出力する。基準クロックとは、時間を通じて周波数が一定のクロックのことである。スペクトラム拡散クロックとは、基準クロックに対してスペクトラム拡散を行うことによって得られるクロックのことであり、時間を通じて周波数が変動する。

**【0010】**

スペクトラム拡散クロック生成回路100は、生成部110と、パルス差制御部120と、パルス差監視部130とを有する。スペクトラム拡散クロック生成回路100に入力された基準クロックは、生成部110とパルス差監視部130とのそれぞれに供給される。生成部110は、供給された基準クロックに基づいてスペクトラム拡散クロックを生成する。生成部110は、生成したスペクトラム拡散クロックを外部へ出力するとともに、パルス差監視部130へ供給する。生成部110は、基準クロックの平均周波数と、出力されるスペクトラム拡散クロックの平均周波数とが一致するようにスペクトラム拡散クロックを生成する。パルス差監視部130は、ある時刻以降に生成部110に入力された基準クロックのパルス数と、同じ時刻以降に生成部110から出力されたスペクトラム拡散クロックの波数との差を継続的に監視する。以下の説明において、この起点となる時刻を基準時刻と呼び、両者のパルス数の差を単にパルス差と呼ぶ。パルス差は、基準クロックのパルス数からスペクトラム拡散クロックのパルス数を減算した値として定義されてもよいし、その逆にスペクトラム拡散クロックのパルス数から基準クロックのパルス数を減算した値として定義されてもよい。パルス差監視部130はパルス差を表す信号をパルス差制御部120へ供給する。パルス差制御部120は、パルス差が所定の範囲内に含まれるように生成部110を制御して生成部110から出力されるスペクトラム拡散クロックの周波数を調整する。パルス差制御部120の動作の詳細は後述する。 40

**【0011】**

続いて、図2のブロック図を参照して、図1の生成部110の構成例を説明する。生成部110は、周波数差監視部111と、周波数差制御部112と、発振回路113と、加算器114とを有する。周波数差監視部111は、生成部110に入力された基準クロックの平均周波数と、生成部110から出力されたスペクトラム拡散クロックの平均周波 50

数との差を継続的に監視する。以下では、両者の平均周波数の差を単に平均周波数差と呼ぶ。周波数差監視部 111 は、平均周波数差を表す信号を周波数差制御部 112 へ供給する。周波数差制御部 112 は、発振回路 113 の発振周波数をあらかじめ決められた範囲及び周期で変動させる信号を加算器 114 へ供給する。加算器 114 は、周波数差制御部 112 から供給された信号と、パルス差制御部 120 から供給された信号とを加算して発振回路 113 へ供給する。パルス差制御部 120 から有意な信号が加算器 114 へ供給されていない場合に、発振回路 113 は周波数差制御部 112 からの信号に従って動作する。発振回路 113 は、加算器 114 から供給された信号に従ってスペクトラム拡散クロックを生成して出力する。周波数差制御部 112 は、周波数差監視部 111 から供給された平均周波数差に基づいて、基準クロックの平均周波数と一致するように、発振回路 113 が生成するスペクトラム拡散クロックの平均周波数を調整する。10

#### 【0012】

基準クロックの周波数は時間の経過を通じて一定であるので、どの期間で平均周波数を測定してもその値はほぼ一定である。一方、スペクトラム拡散クロックの周波数は時間の経過とともに変化するので、その平均周波数は測定する期間によって変わりうる。そこで、周波数差監視部 111 は、生成部 110 が外乱等の影響を受けずに定常状態で動作している場合にスペクトラム拡散クロックの平均周波数が時間の経過を通じてほぼ一定となるような期間で平均周波数を測定しうる。例えば、周波数差制御部 112 がスペクトラム拡散クロックの周波数を周期的に変動させる場合に、その周期（以下、拡散変調周期と呼ぶ。）又はその周期の整数倍を測定期間として平均周波数を取得してもよい。20

#### 【0013】

一部の実施形態では、周波数差監視部 111 は 3 つのカウンタを有しうる。第 1 カウンタは基準クロックのパルス数をカウントし、第 2 カウンタはスペクトラム拡散クロックのパルス数をカウントする。第 3 カウンタは、これらのカウンタのうちの一方のカウンタが所定のカウント値に達してから他方のカウンタがその値に達するまでの時間をカウントする。周波数差監視部 111 は、第 3 カウンタからの出力を平均周波数差として周波数差制御部 112 へ供給する。

#### 【0014】

基準クロックと周波数拡散クロックとは非同期であるので、両者の平均周波数が一致している場合であっても、同じ期間におけるカウント値に 1 カウント程度の誤差が生じる可能性がある。また、周波数拡散クロックは時間の経過とともに周波数が変動するので、カウントする期間に依存して基準クロックとスペクトラム拡散クロックとの間のカウント時間の差が変動する。そこで、周波数差監視部 111 は、これらの誤差や変動を許容できるよう動作しうる。例えば、上述の所定のカウント値が周波数の拡散変調周期よりも長く設定されるとともに、第 3 カウンタのカウント値が閾値を超えた場合にのみ周波数差制御部 112 の出力を変化させてよい。このように周波数差制御部 112 が動作することにより、低い周波数で観測した場合に、発振回路 113 が出力するスペクトラム拡散クロックの平均周波数を基準クロックの周波数に一致させることができる。30

#### 【0015】

生成部 110 は、基準クロックの平均周波数とスペクトラム拡散クロックの平均周波数を一致させるために、基準クロックを分周した信号の位相と、周波数拡散クロックを分周した信号の位相とを一致させる PLL（位相同期回路）を使用してもよい。PLL を使用する場合にも、スペクトラム拡散クロックの周波数変調が意図どおりに行われるよう、フィードバックループの時定数を拡散変調周期よりも大きくしてもよい。40

#### 【0016】

続いて、図 3 (A) のブロック図を参照して、図 1 のパルス差監視部 130 の構成例を説明する。図 3 (A) に示すパルス差監視部 130 は、2 つの巡回シフトレジスタ 131、132 と、セットリセットフリップフロップ回路群 133 と、取得部 134 と、初期値記憶部 135 とを有しうる。巡回シフトレジスタ 131 は基準クロックによって駆動され、巡回シフトレジスタ 132 はスペクトラム拡散クロックによって駆動される。巡回シフ50

トレジスタ 131、132 はそれぞれ、パルス差の許容範囲以上の段数を有しうる。例えば、パルス差が a 以上 b 以下 ( a、b は整数 ) となるようにスペクトラム拡散クロック生成回路 100 が動作すべきである場合に、巡回シフトレジスタ 131、132 はそれぞれ、( b - a ) 以上の段数を有しうる。巡回シフトレジスタ 131、132 はどちらも、ちょうど ( b - a ) 段を有してもよい。以下の説明では、パルス差の許容範囲の幅 ( 上記の例では ( b - a ) ) を M で表し、巡回シフトレジスタ 131、132 がどちらも M 段であるとする。巡回シフトレジスタ 131、132 は、M 個の出力のうちの 1 つのみに H ( ハイ ) を出力し、その他に L ( ロー ) を出力する。そして、巡回シフトレジスタ 131、132 は、パルスが入力されるごとに、H を出力する端子を 1 つずつ移動する。例えば、M = 3 の場合に、巡回シフトレジスタ 131、132 の出力はパルスの入力ごとに以下のように変化する。

( L L H ) ( L H L ) ( H L L ) ( L L H ) ...

#### 【 0017 】

セットリセットフリップフロップ回路群 133 は、M 個のセットリセットフリップフロップ回路を有しうる。巡回シフトレジスタ 131 の M 個の出力端子と M 個のセットリセットフリップフロップ回路の M 個のセット端子は 1 対 1 に対応しており、セットリセットフリップフロップ回路は巡回シフトレジスタ 131 の出力端子から H が供給されるとセットされる。巡回シフトレジスタ 132 の M 個の出力端子と M 個のセットリセットフリップフロップ回路の M 個のリセット端子は 1 対 1 に対応しており、セットリセットフリップフロップ回路は巡回シフトレジスタ 132 の出力端子から H が供給されるとリセットされる。M 個のセットリセットフリップフロップ回路のそれぞれの出力端子は取得部 134 に接続されている。各セットリセットフリップフロップ回路は、自身の内部状態がセット状態である場合に H を出力し、自身の内部状態がリセット状態である場合に L を出力する。

#### 【 0018 】

取得部 134 は、セットリセットフリップフロップ回路群 133 からの M 個の出力のうち、H であるもの又は L であるものの個数をカウントする。以下では、取得部 134 が H であるものの個数をカウントする場合を説明する。取得部 134 はまず、基準時刻における H の個数を初期値記憶部 135 に格納する。そして、取得部 134 は、セットリセットフリップフロップ回路群 133 からの M 個の出力の何れかが変化するごとに、その時刻での H の個数から、初期値記憶部 135 に格納されている値を減算して得られた値をパルス差制御部 120 へ供給する。この値がパルス差を表す。パルス差制御部 120 は取得部 134 から供給されたパルス差に基づいて、このパルス差が所定の範囲内に含まれるように生成部 110 へ制御信号を供給する。

#### 【 0019 】

続いて、図 3 ( B ) のブロック図を参照して、図 1 のパルス差監視部 130 の他の構成例を説明する。図 3 ( B ) に示すパルス差監視部 130 は、2 つのカウンタ 136、137 と、減算器 138 と、取得部 134 と、初期値記憶部 135 とを有しうる。カウンタ 136 は基準クロックのパルス数をカウントし、カウント値を減算器 138 へ供給する。カウンタ 137 はスペクトラム拡散クロックのパルス数をカウントし、カウント値を減算器 138 へ供給する。カウンタ 136、137 はそれぞれ、パルス差の許容範囲の幅 ( 上述の M ) 以上の数をカウント可能である。減算器 138 は、カウンタ 136 から供給されたカウント値から、カウンタ 137 から供給されたカウント値を減算して、取得部 134 へ供給する。基準クロックと非同期に動作するカウンタ 137 はカウント値をグレイコードで出力してもよい。グレイコードで出力することによって、減算器 138 で取り込まれるカウント値の誤差を 1 以下にすることができる。

#### 【 0020 】

取得部 134 はまず、基準時刻における減算器 138 の出力値を初期値記憶部 135 に格納する。そして、取得部 134 は、減算器 138 からの出力値が変化するごとに、その時刻での出力値から、初期値記憶部 135 に格納されている値を減算して得られた値をパルス差制御部 120 へ供給する。この値がパルス差を表す。パルス差制御部 120 は取得

10

20

30

40

50

部 134 から供給されたパルス差に基づいて、このパルス差が所定の範囲内に含まれるように生成部 110 へ制御信号を供給する。

#### 【0021】

続いて、図 4 のブロック図を参照して、本発明の一部の実施形態に係るクロック乗せ換え回路 400 の構成例を説明する。クロック乗せ換え回路 400 は、スペクトラム拡散クロック生成回路 100 と、書き込み部 410 と、メモリ 420 と、読み出し部 430 とを有しうる。クロック乗せ換え回路 400 には外部から基準クロックと入力データとが供給される。入力データは例えば N ビットデジタルデータでありうる。メモリ 420 は N ビットデジタルデータを M 個格納可能である。書き込み部 410 は、基準クロックのパルスが入力されるごとに、格納場所を 1 つずつずらして入力データをメモリ 420 に書き込む。スペクトラム拡散クロック生成回路 100 は、上述のように基準クロックに基づいてスペクトラム拡散クロックを生成し、読み出し部 430 へ供給する。読み出し部 430 は、スペクトラム拡散クロックのパルスが入力されるごとに、先入れ先出し (FIFO) 方式でメモリ 420 からデータを読み出し、外部へ出力する。10

#### 【0022】

続いて、図 5、図 6 のグラフを参照して、スペクトラム拡散クロック生成回路 100 のパルス差制御部 120 の動作例について説明する。以下では、スペクトラム拡散クロック生成回路 100 がクロック乗せ換え回路 400 に搭載されている文脈で説明される。スペクトラム拡散クロック生成回路 100 に含まれる周波数差制御部 112 の制御によって、20

基準クロックの平均周波数とスペクトラム拡散クロックの平均周波数とは一致する。そのため、長期的（例えば、拡散変調周期以上の長さ）にはクロック乗せ換え回路 400 に入力されるデータの個数とクロック乗せ換え回路 400 から出力されるデータの個数とは一致しうる。しかしながら、スペクトラム拡散クロックは時間の経過とともに周波数が変化するので、短期間で観察した場合に、メモリ 420 内の出力待ちのデータ数は変動する。ここで、出力待ちのデータとは、メモリ 420 に書き込まれた後、まだ読み出されていないデータを表す。

#### 【0023】

図 5 を参照して、メモリ 420 内の出力待ちのデータ数の変動の様子を説明する。図 5 の上図は時間の経過に対するスペクトラム拡散クロックの周波数の変化を表すグラフ 501 を示す。スペクトラム拡散クロックは、基準クロック（図 5 の Ref）の上下を周期的に変動する。図 5 では、外乱がない場合を想定しており、そのためスペクトラム拡散クロックの周波数の平均周波数は基準クロックの平均周波数と等しくなる。図 5 の下図は時間の経過に対するメモリ 420 内の出力待ちのデータ数の変化を表すグラフ 502 を示す。スペクトラム拡散クロックの周波数が基準クロックの周波数よりも大きい場合に、出力待ちデータ数は減少する。スペクトラム拡散クロックの周波数が基準クロックの周波数よりも小さい場合に、出力待ちデータ数は増加する。そのため、出力待ちデータ数は時刻 t0 における値 Inj を中心として変動する。30

#### 【0024】

次に、図 6 を参照して、外乱がある場合のメモリ 420 内の出力待ちのデータ数の変動の様子を説明する。図 6 の上図は時間の経過に対するスペクトラム拡散クロックの周波数の変化を表すグラフ 601 を示す。図 6 の下図は時間の経過に対するメモリ 420 内の出力待ちのデータ数の変化を表すグラフ 602 を示す。図 6 の例では、時刻 t1 で外乱が発生し、生成されたスペクトラム拡散クロックの周波数が、本来生成すべき周波数（点線のグラフ 501）よりも大きくなっている。そのため、メモリ 420 から読み出されるデータ数が多くなる。この状態が継続すると、出力待ちデータ数が 0 となり、読み出しエラーが発生する。このような外乱の影響は、周波数差制御部 112 による制御によっても解消されうる。しかし、周波数差制御部 112 による制御はフィードバックループの時定数が大きいので、外乱がこの時定数よりも早く変化する場合に対応できない場合がある。例えば、発振回路 113 の周辺の回路で発生する熱により、フィードバックループの応答時間よりも速く温度が上昇した場合に、発振回路 113 の生成する周波数は温度特性に従って40

50

、本来生成すべき周波数よりも大きくなる。一方、発熱のおさまる速さがフィードバックループの応答時間よりも遅い場合に、本来生成すべき周波数からの逸脱は小さい。この結果、スペクトラム拡散クロックの平均周波数が一時的に基準クロックの周波数から外れてしまう。また、平均周波数を取得するタイミングによっては、基準時刻からのパルス差の平均値が初期値  $I_{n_i}$  から外れていたとしても、基準クロックの平均周波数とスペクトラム拡散クロックの平均周波数とが一致してしまう場合がある。このような誤差の蓄積によって、書き込みエラー・読み出しえラーが発生してしまう可能性がある。

#### 【0025】

そこで、パルス差制御部 120 は、基準時刻以降 ( $t_0$  以降) のパルス差が、 $-I_{n_i}$  以上 ( $M - I_{n_i}$ ) 以下となるように発振回路 113 の生成するスペクトラム拡散クロックの周波数を調整する。基準時刻  $t_0$  以降のパルス差がこの範囲内に含まれる場合に、メモリ 420 内の出力待ちデータ数は 1 以上  $M$  以下となり、読み出しえラー・書き込みエラーは発生しない。 $I_{n_i}$  の値は例えば  $M / 2$  としてもよい。例えば、パルス差監視部 130 は、出力待ちのデータ数が  $M / 2$  となった時刻 ( $t_0$ ) を基準時刻として、パルス差を継続して監視する。

#### 【0026】

続いて、パルス差制御部 120 の詳細な動作の具体例を説明する。パルス差制御部 120 は、4 つの閾値  $T_{h1} \sim T_{h4}$  を格納している。これらの閾値はいずれも、パルス差が含まれるべき範囲に含まれる。これらの閾値はパルス差が含まれるべき範囲とともに設定されてもよい。以下の説明では、4 つの閾値  $T_{h1} \sim T_{h4}$  が小さいものから順に並んでいるとする。また、初期値  $I_{n_i}$  は  $T_{h2}$  と  $T_{h3}$  との間にあるとする。

#### 【0027】

パルス差制御部 120 は、パルス差が変化するごとに、パルス差が初期値  $I_{n_i}$  から変化した結果として、出力待ちデータ数が  $T_{h1}$  を下回ったかどうか及び  $T_{h4}$  を上回ったかどうかを判定する。パルス差監視部 130 の出力するパルス差は、基準クロックのパルスが入力されるごと及びスペクトラム拡散クロックのパルスが出力されるごとに変化する。図 6 の例では、時刻  $t_2$  で、パルス差制御部 120 は、パルス差が ( $T_{h1} - I_{n_i}$ ) を下回ったこと、すなわち出力待ちデータ数が  $T_{h1}$  を下回ったことを判定する。時刻  $t_2$  の時点で、スペクトラム拡散クロックの周波数は減少傾向にあるので、パルス差制御部 120 は現在の動作を継続する。時刻  $t_3$  で、スペクトラム拡散クロックの周波数が基準クロックの周波数を下回ると、出力待ちデータ数は増加し始める。時刻  $t_4$  で、グラフ 501 に示すように、周波数差制御部 112 はスペクトラム拡散クロックの周波数を増加させる制御信号を発振回路 113 に供給する。そこで、パルス差制御部 120 は、周波数差制御部 112 の制御を打ち消すように、スペクトラム拡散クロックの周波数を減少させる制御信号を発振回路 113 に供給する。その結果、発振回路 113 が output するスペクトラム拡散クロックの周波数は時刻  $t_3$  を過ぎても減少し続ける。その後、時刻  $t_5$  で、パルス差制御部 120 は、出力待ちデータ数が  $T_{h2}$  を上回ったことを判定し、スペクトラム拡散クロックの周波数が増加するように制御する。

#### 【0028】

上記の例では、パルス差が所定の範囲に含まれ、その結果としてメモリ 420 内の出力待ちデータ数が 1 以上  $M$  以下となるように、パルス差制御部 120 は、パルス差が閾値を超えた場合に、パルス差が低減するようにスペクトラム拡散クロックの周波数を制御した。このような制御は上記の例に限られない。例えば、パルス差制御部 120 は、初期値  $I_{n_i}$  の上下に 1 つずつ設定された閾値に基づいて、これらの閾値を超えた場合に、パルス差が 0 に近づくように、所定の時間及びパターンによってスペクトラム拡散クロックの周波数を制御してもよい。パターンの例として、通常の制御範囲の最大周波数又は最小周波数を超えて一定の期間、周波数の増減を継続してもよいし、最大周波数又は最小周波数を超えた周波数を一定期間維持してもよい。また、パルス差制御部 120 は、通常制御時の平均周波数の上下で変調速度を変えることで、平均周波数を変化させてもよい。上述の例では、パルス差制御部 120 はスペクトラム拡散クロックの周波数を連続的に変化させて

10

20

30

40

50

いるが、離散的に変化させてもよい。

【0029】

上述のように、スペクトラム拡散クロック生成回路100は、外乱等が発生した場合であってもパルス差が所定の範囲に含まれるようにスペクトラム拡散クロックを制御できる。そのため、事前に決定されたメモリ420のサイズに応じてパルス差の許容可能な範囲を設定することで、クロック乗せ換え回路400が使用するメモリのサイズを低減可能となる。

【0030】

続いて、図7のブロック図を参照して、本発明の一部の実施形態に係る集積回路700の構成例を説明する。集積回路700は半導体集積回路でありうる。集積回路700は、スペクトラム拡散クロック生成回路100と、発振回路710と、回路素子720とを有しうる。発振回路710は、基準クロックを生成してスペクトラム拡散クロック生成回路100へ供給する。スペクトラム拡散クロック生成回路100は、上述のように、基準クロックに基づいてスペクトラム拡散クロックを生成し、回路素子720へ供給する。回路素子720は、供給されたスペクトラム拡散クロックに従って動作する。回路素子720は、例えばフリップフロップ回路等でありうる。

10

【0031】

続いて、図8のブロック図を参照して、本発明の一部の実施形態に係る画像読み取り装置800の構成例を説明する。画像読み取り装置800は、例えばMFP(多機能周辺装置)や、スキャナ、複写機でありうる。画像読み取り装置800は、クロック乗せ換え回路400と、読み取り部810と、発振回路820と、画像処理部830とを有しうる。読み取り部810は、原稿を読み取って画像データを生成する。読み取り部810は、光源、縮小光学部品、ラインセンサ、アナログ/デジタル変換器、コントローラ等で構成されうる。発振回路820は、基準クロックを生成して読み取り部810とクロック乗せ換え回路400とへ供給する。読み取り部810は供給された基準クロックに従って動作する。基準クロックの周波数は例えば数100MHzでありうる。クロック乗せ換え回路400は、上述のように、基準クロックに従って読み取り部810から画像データを受け取り、スペクトラム拡散クロックに従って画像データを画像処理部830へ供給する。画像処理部830は供給された画像データの処理を行う。読み取り部810、発振回路820及びクロック乗せ換え回路400は画像読み取り装置800の可動部に搭載されてもよく、画像処理部830は画像読み取り装置800の本体部に搭載されてもよい。クロック乗せ換え回路400と画像処理部830とは例えば数十センチメートルのワイヤーハーネスによって接続されうる。

20

30

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(72)発明者 白井 誉浩

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 橋爪 正樹

(56)参考文献 特開2007-225863(JP,A)

特開平10-229399(JP,A)

特開2010-220148(JP,A)

特開2001-094734(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 1/024 - 1/207

H04N 5/14 - 5/378

G06T 1/00