## 【特許請求の範囲】

## 【請求項 1】

チップ支持面を備えたチップ搭載部と、

前記チップ搭載部の周囲に配置された複数のリードと、

前記チップ搭載部の前記チップ支持面上に配置されたペースト材と、

前記チップ搭載部の前記チップ支持面上に前記ペースト材を介して搭載された半導体チップと、

前記半導体チップの複数の電極と前記複数のリードとをそれぞれ電気的に接続する複数のワイヤと、

前記半導体チップと前記複数のワイヤと前記複数のリードそれぞれの一部と前記チップ搭載部の一部を樹脂封止する封止体とを有し、

前記チップ搭載部の前記チップ支持面の外形サイズは、前記半導体チップの裏面より小さく、

前記チップ搭載部の前記チップ支持面と反対側の裏面は前記封止体から露出し、

前記チップ搭載部の前記チップ支持面の周縁部に前記チップ支持面より高さの低い段差部が形成されていることを特徴とする半導体装置。

## 【請求項 2】

請求項 1 記載の半導体装置において、前記複数のリードそれぞれのチップ側の端部は、前記半導体チップの裏面と対向していることを特徴とする半導体装置。

## 【請求項 3】

請求項 2 記載の半導体装置において、前記複数のリードそれぞれのチップ側の端部に第1肉薄部が形成され、前記第1肉薄部が前記半導体チップの裏面と対向していることを特徴とする半導体装置。

## 【請求項 4】

請求項 1 記載の半導体装置において、前記チップ搭載部の前記チップ支持面と、前記複数のリードそれぞれのワイヤ接続面は同じ高さであることを特徴とする半導体装置。

## 【請求項 5】

請求項 1 記載の半導体装置において、前記チップ搭載部と連結する吊りリードを有し、前記吊りリードはエッティングによって形成された第2肉薄部を備え、前記第2肉薄部は前記封止体内に埋め込まれていることを特徴とする半導体装置。

## 【請求項 6】

請求項 1 記載の半導体装置において、前記チップ搭載部の前記チップ支持面の全面に前記ペースト材が配置されていることを特徴とする半導体装置。

## 【請求項 7】

請求項 1 記載の半導体装置において、前記チップ搭載部の前記段差部に前記半導体チップに向かって突出した突起部が形成されていることを特徴とする半導体装置。

## 【請求項 8】

請求項 7 記載の半導体装置において、前記チップ搭載部の前記チップ支持面が四角形を成し、前記四角形の前記チップ支持面の各辺にこの各辺に設けられた前記突起部から遠ざかる方向に抉れた抉れ部が形成されていることを特徴とする半導体装置。

## 【請求項 9】

請求項 7 記載の半導体装置において、前記突起部は、四角形の前記チップ搭載部の1つの辺に対応した前記段差部の中央部に形成されていることを特徴とする半導体装置。

## 【請求項 10】

請求項 7 記載の半導体装置において、前記突起部は、四角形の前記チップ搭載部の1つの辺に対応した前記段差部に1つずつ形成されていることを特徴とする半導体装置。

## 【請求項 11】

(a) チップ支持面の周縁部に前記チップ支持面より高さの低い段差部が形成されたチップ搭載部と、前記チップ搭載部の周囲に配置された複数のリードとを有するリードフレームを準備する工程と、

10

20

30

40

50

( b ) 前記チップ搭載部の前記チップ支持面上にペースト材を塗布する工程と、

( c ) 半導体チップの裏面より外形サイズが小さな前記チップ搭載部の前記チップ支持面上に前記ペースト材を介して半導体チップを接合する工程と、

( d ) 前記半導体チップの複数の電極と前記複数のリードとをそれぞれ電気的に接続する工程と、

( e ) 複数の半導体装置形成領域を樹脂成形金型の1つのキャビティで覆った状態で封止用樹脂を前記キャビティ内に注入し、前記半導体チップと前記チップ搭載部の前記段差部との間に封止用樹脂を周り込ませ、かつ前記チップ搭載部の前記チップ支持面と反対側の裏面及び前記複数のリードそれぞれの一部が露出するように前記半導体チップと複数のワイヤを樹脂封止して一括封止体を形成する工程と、

( f ) 前記一括封止体及び前記リードフレームを切断して各半導体装置に個片化する工程とを有することを特徴とする半導体装置の製造方法。

【請求項12】

請求項11記載の半導体装置の製造方法において、前記(e)工程で、接着層を有するテープを前記リードフレームの裏面に貼り付けた状態で前記樹脂成形金型をクランプし、この状態で前記封止用樹脂を前記キャビティ内に注入して前記一括封止体を形成することを特徴とする半導体装置の製造方法。

【請求項13】

請求項11記載の半導体装置の製造方法において、前記(e)工程の後、前記リードフレームの裏面から前記テープを剥離する剥離工程を有することを特徴とする半導体装置の製造方法。

【請求項14】

請求項11記載の半導体装置の製造方法において、前記(e)工程の後、前記リードフレームの裏面から前記テープを剥離する剥離工程を有し、さらに前記剥離工程の後に、前記リードフレームの裏面を洗浄する洗浄工程を有することを特徴とする半導体装置の製造方法。

【請求項15】

請求項14記載の半導体装置の製造方法において、前記洗浄工程で、有機系溶剤によって前記リードフレームの裏面を洗浄することを特徴とする半導体装置の製造方法。

【請求項16】

請求項14記載の半導体装置の製造方法において、前記洗浄工程の後に、前記一括封止体から露出する前記チップ搭載部の裏面及び前記複数のリードそれぞれの一部に外装めつきを形成するめつき処理工程を有することを特徴とする半導体装置の製造方法。

【請求項17】

請求項11記載の半導体装置の製造方法において、前記チップ搭載部の前記段差部に前記半導体チップに向かって突出した突起部がエッチングにより形成されていることを特徴とする半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造技術に関し、特に、タブ(チップ搭載部)を露出させる半導体装置に適用して有効な技術に関する。

【背景技術】

【0002】

ダイパッドの外形寸法をその上に搭載する半導体チップの外形寸法よりも小さくすることにより、半導体チップと樹脂との接着面積を大きくし、また、半導体チップの外形寸法に応じてリードの先端を適宜の長さに切断することにより、外形寸法の異なる各種半導体チップをダイパッド上に搭載可能とした技術がある(例えば、特許文献1参照)。

【0003】

また、外部端子が下方に突出したQFNにおいて、ダイパッドに半切断部が形成されて

10

20

30

40

50

中央部が周辺部よりもアップセットされていることにより、吊りリードとの干渉を招くことなく半導体チップのサイズを自由に選択することが可能になる技術がある（例えば、特許文献2参照）。

【特許文献1】特開平6-216303号公報

【特許文献2】特開2000-243891号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

QFN (Quad Flat Non-leaded Package) 等のノンリード型の半導体装置では、各リードの一部が封止体の裏面の周縁部に露出して配置され、これらが外部端子となっている。このようなQFNにおいて、更なる小型化・薄型化にともなってチップサイズを可能な限りパッケージサイズに近づけた半導体装置が要求されている。また、近年の半導体装置は高機能化の傾向にあるため、半導体チップから発生する熱量も大きくなる。そのため、半導体装置の信頼性を考慮した場合、放熱性の向上も要求される。さらには、これらの要求に加えて、製造コストの増加を抑制する必要もある。

【0005】

そこで、これらの要求に応えるために、本願発明者は以下のように検討した。

【0006】

まず、半導体装置の小型化を実現するためには、QFN構造では、可能な限り大きな半導体チップを搭載できるようにタブ（チップ搭載部）の周囲に配置されたリード上に、半導体チップの外周部をオーバーラップさせる構造を検討した。すなわち、半導体チップの下部に各リードのチップ側の端部をもぐり込ませた構造である。

【0007】

これにより、半導体装置の小型化に対応することができるが、このような構造では、タブは、必然的にその外形の大きさが半導体チップの外形サイズより小さな、いわゆる小タブ構造となる。

【0008】

次に、半導体装置の放熱性を考慮すると、タブの裏面を封止体の裏面に露出させる、いわゆるタブ露出型のQFNが考えられる。すなわち、この場合、小タブ構造でタブ露出型のQFNとなる。ここで、タブを封止体から露出することで放熱性は向上するが、封止体から露出したタブを実装基板の電極に接合材を介して接続することで、より放熱性を向上することができる。

【0009】

ところが、このような小タブ構造のQFNでは、タブのチップ支持面の面積が比較的小さくなる。そのため、このような外形サイズの小さいタブに確実に半導体チップを固定するためには、半導体チップとタブとの間にダイボンド材を隙間無く設ける必要がある。これにより、ダイボンド材である銀ペースト（ペースト材）がチップ支持面からはみ出ることがあり、半導体チップのダイボンド工程において、チップ支持面からはみ出した銀ペーストがタブの側面を伝って、タブの裏面に流出してしまう。その結果、タブ露出型の構造の場合、タブの裏面に外装めつきを施す必要があるが、パッケージ裏面に銀ペーストが付着してしまうため、タブの裏面に外装めつきを形成することが困難となる。これにより、放熱性を十分に向上することができる。

【0010】

その際、ダイボンド材として、フィルムタイプの接着材を用いることでダイボンド材のはみ出し・流出を防ぐことも考えられるが、フィルムタイプの接着材は、ペースト材に比べると材料コストが高く、製造コストの低減化が困難となる。また、フィルムタイプを使用する場合、タブのチップ支持面に対してフィルムを正確に配置することも困難である。

【0011】

なお、前記特許文献1（特開平6-216303号公報）には、小タブ構造の半導体装置の例が記載されているが、小タブ構造では前記したようにペースト材がはみ出る現象が

10

20

30

40

50

起こり易くペースト材が流出する要因をつくりだすことが問題である。

【0012】

また、前記特許文献2（特開2000-243891号公報）に記載されたパッケージ構造では、ダイパッド（タブ）がオフセット加工されている。すなわち、ダイパッドの中央部を裏面側からプレスで押し上げるオフセット加工が施されており、その結果、ダイパッドの中央部の正面（チップ支持面）がリードの正面（ワイヤ接続面）より高い位置となっており、パッケージの薄型化が困難な構造になっている。

【0013】

さらに、ダイパッドのオフセット加工によって形成される外周部は、オフセット加工から成るため、段差の幅を大きくとる必要がある。これらより、ダイパッドの中央部の面積が小さくなり、半導体チップとの接合面積も小さくなる。その結果、半導体チップの接合信頼性や放熱性が低下するという問題が起こる。

10

【0014】

本発明の目的は、ダイボンド材の流出を防いで半導体装置の品質・信頼性を向上させることができる技術を提供することにある。

【0015】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0016】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

20

【0017】

すなわち、本発明は、チップ搭載部の周囲に配置された複数のリードと、チップ搭載部のチップ支持面上に配置されたペースト材と、チップ搭載部のチップ支持面上にペースト材を介して搭載された半導体チップと、半導体チップの複数の電極と複数のリードとをそれぞれ接続する複数のワイヤと、半導体チップと複数のワイヤと複数のリードそれぞれの一部とチップ搭載部の一部を樹脂封止する封止体とを有するものである。さらに、本発明は、チップ搭載部のチップ支持面の外形サイズは、半導体チップの裏面より小さく、チップ搭載部のチップ支持面と反対側の裏面は封止体から露出し、チップ搭載部のチップ支持面の周縁部にチップ支持面より高さの低い段差部が形成されているものである。

30

【0018】

また、本発明は、チップ支持面の周縁部にチップ支持面より高さの低い段差部が形成されたチップ搭載部と、チップ搭載部の周囲に配置された複数のリードとを有するリードフレームを準備する工程と、チップ搭載部のチップ支持面上にペースト材を塗布する工程と、半導体チップの裏面より外形サイズが小さなチップ搭載部のチップ支持面上にペースト材を介して半導体チップを接合する工程とを有するものである。さらに、本発明は、半導体チップの複数の電極と複数のリードとを電気的に接続する工程と、複数の半導体装置形成領域を樹脂成形金型の1つのキャビティで覆った状態で封止用樹脂をキャビティ内に注入し、半導体チップとチップ搭載部の段差部との間に封止用樹脂を周り込ませ、かつチップ搭載部のチップ支持面と反対側の裏面及び複数のリードそれぞれの一部が露出するよう半導体チップを樹脂封止する工程とを有するものである。

40

【発明の効果】

【0019】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下のとおりである。

【0020】

チップ搭載部のチップ支持面の周縁部にチップ支持面より高さの低い段差部が形成されていることにより、チップ搭載部からはみ出したペースト材（ダイボンド材）をこの段差部に留めることができ、ペースト材の封止体の裏面への流出を防ぐことができる。これに

50

より、パッケージ裏面の外装めっきにペースト材が付着することを阻止することができ、さらに外装めっきが形成できなくなるという問題を引き起こさなくなる。その結果、半導体装置の品質や信頼性を向上させることができる。

【0021】

チップ搭載部の段差部に半導体チップに向かって突出した突起部が形成されていることにより、アンカー効果によって樹脂とチップ搭載部の密着性を高めることができる。これにより、チップ搭載部の段差部での剥離を抑制することができる。その結果、チップ搭載部と樹脂の界面に不純物が入りにくくなり、不純物の流出による外装めっきの変色を防ぐことができる。したがって、半導体装置の品質や信頼性を向上させることができる。

【発明を実施するための最良の形態】

【0022】

以下の実施の形態では特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

【0023】

さらに、以下の実施の形態では便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明などの関係にある。

【0024】

また、以下の実施の形態において、要素の数など（個数、数値、量、範囲などを含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合などを除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良いものとする。

【0025】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。

【0026】

（実施の形態1）

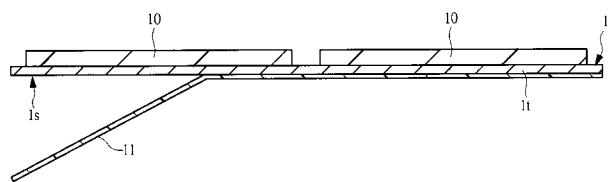

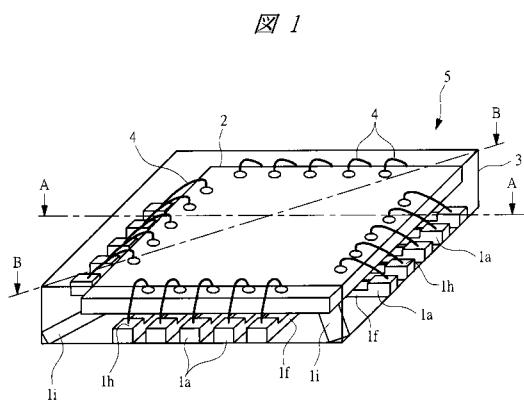

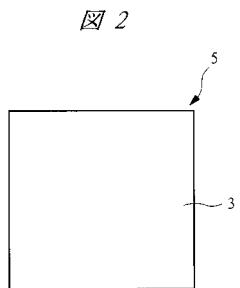

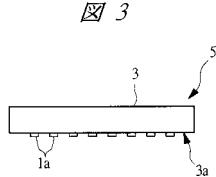

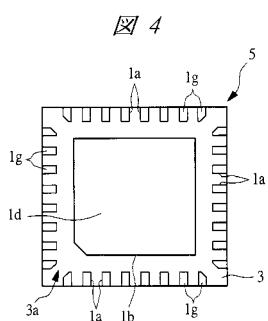

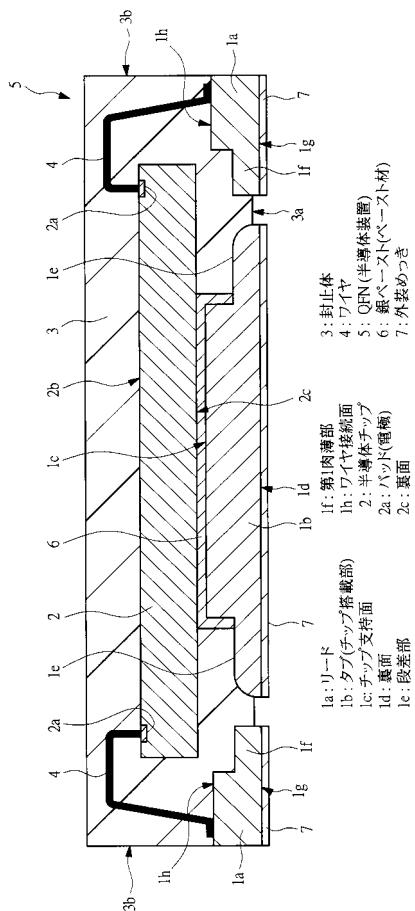

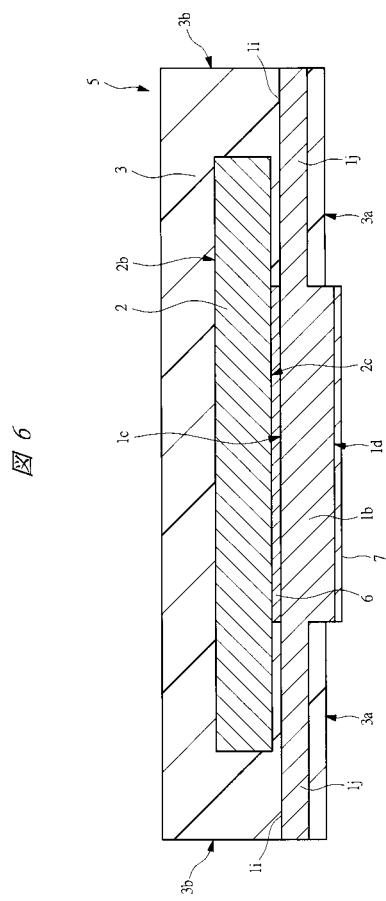

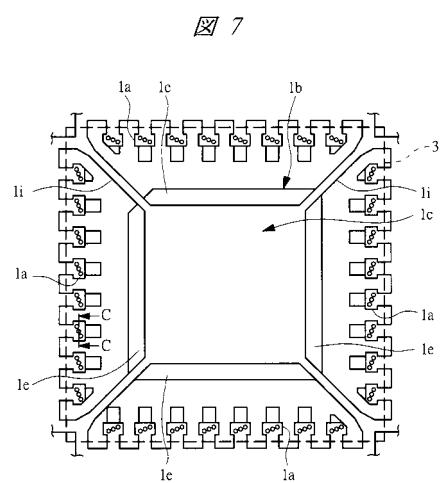

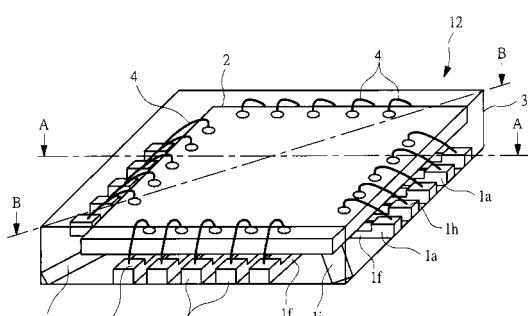

図1は本発明の実施の形態1の半導体装置の構造の一例を封止体を透過して示す斜視図、図2は図1に示す半導体装置の構造を示す平面図、図3は図1に示す半導体装置の構造を示す側面図、図4は図1に示す半導体装置の構造を示す裏面図、図5は図1に示すA-A線に沿って切断した構造の一例を示す断面図、図6は図1に示すB-B線に沿って切断した構造の一例を示す断面図、図7は図1に示す半導体装置におけるタブ、吊りリード、及びリードの構造を封止体を透過して示す部分平面図、図8は図7に示すC-C線に沿って切断した断面図、図9は図8の変形例図である。

【0027】

図1～図9に示す本実施の形態1の半導体装置は、樹脂封止型で、かつ小型の半導体パッケージであり、封止体3の裏面3aの周縁部に複数のリード1aがそれぞれの実装面1gが露出して並んで配置されたノンリード型のものである。本実施の形態1では、前記半導体装置の一例として、QFN5を取り上げて説明する。なお、本実施の形態1のQFN5は、小型の半導体パッケージであるが、搭載される半導体チップ2の大きさを可能な限りパッケージの大きさに近づけたものである。

【0028】

QFN5の構成について説明すると、半導体チップ2を搭載可能なチップ支持面1cを備えたチップ搭載部であるタブ（ダイパッドともいう）1bと、タブ1bと一体に形成された複数の吊りリード1iと、複数の吊りリード1iの間に位置し、タブ1bの周囲に配置された複数のリード1aと、タブ1bのチップ支持面1c上に配置されたペースト材である銀ペースト6と、タブ1bのチップ支持面1c上に銀ペースト6を介して搭載された半導体チップ2とを有している。さらに、QFN5は、半導体チップ2の複数のパッド（

10

20

30

40

50

電極 ) 2 a と複数のリード 1 a とをそれぞれ電気的に接続する複数の金線である導電性のワイヤ 4 と、半導体チップ 2 と複数のワイヤ 4 と複数のリード 1 a それぞれの一部とタブ 1 b の一部を樹脂封止する封止体 3 とを有している。

【 0 0 2 9 】

また、タブ 1 b 、吊りリード 1 i 、及び複数のリード 1 a は、同じ一枚のリードフレームから構成される。

【 0 0 3 0 】

なお、Q F N 5 では、タブ 1 b のチップ支持面 1 c の外形サイズ（外形寸法、面積）は、図 5 に示すように半導体チップ 2 の裏面 2 c より小さく形成されている。また、タブ 1 b のチップ支持面 1 c と反対側の裏面 1 d は、図 4 に示すように封止体 3 から露出している。さらに、図 5 に示すようにタブ 1 b のチップ支持面 1 c の周縁部にチップ支持面 1 c より高さの低い段差部 1 e が形成されている。

10

【 0 0 3 1 】

すなわち、Q F N 5 は、小タブ構造で、かつタブ露出型の半導体パッケージであり、タブ 1 b のチップ支持面 1 c の周縁部における吊りリード 1 i を除く箇所（図 7 参照）に、チップ支持面 1 c より高さの低い段差部 1 e が形成されているものである。

【 0 0 3 2 】

タブ 1 b の周縁部の段差部 1 e は、例えば、ハーフエッチング加工によって形成されるものであり、例えば、リードフレームの板厚が 0.2 mm の場合、タブ 1 b の厚さも 0.2 mm であり、その際、段差部 1 e は、ハーフエッチング加工により、板厚 0.1 mm となる。すなわち、段差部 1 e の高さは、チップ支持面 1 c より 0.1 mm 低い位置となる。段差部 1 e は、タブ 1 b のチップ支持面 1 c から溢れてはみ出した銀ペースト 6 を受け止めるものであり、はみ出した銀ペースト 6 を段差部 1 e に停留させて封止体 3 の裏面 3 a に露出しないようにするためのものである。

20

【 0 0 3 3 】

Q F N 5 は、タブ 1 b の裏面 1 d が、図 4 に示すように封止体 3 の裏面 3 a から露出しているため、放熱性を高めることができる。

【 0 0 3 4 】

なお、本実施の形態 1 の Q F N 5 のタブ 1 b には、段差部 1 e は形成されているものの、オフセット加工等のプレス加工は施されていない。したがって、Q F N 5 では、図 5 に示すように、タブ 1 b のチップ支持面 1 c と、複数のリード 1 a それぞれのワイヤ接続面 1 h は同じ高さとなっている。

30

【 0 0 3 5 】

すなわち、Q F N 5 では、タブ 1 b にはオフセット加工のような曲げ加工は施されていないため、オフセット加工が施されてダイパッドの中央部付近がリードのワイヤ接続面より高い位置となった半導体パッケージに比較して、パッケージ（Q F N 5 ）の薄型化を図ることができる。

【 0 0 3 6 】

また、本実施の形態 1 の Q F N 5 は小型の半導体パッケージであるが、更なる小型化・薄型化に対応可能なように、チップサイズを可能な限りパッケージサイズに近づけたものである。

40

【 0 0 3 7 】

したがって、可能な限り大きな半導体チップ 2 を搭載できるようにタブ 1 b の周囲に配置されたリード 1 a 上に、半導体チップ 2 の外周部をオーバーラップさせて配置した構造となっている。

【 0 0 3 8 】

すなわち、図 1 及び図 5 に示すように、複数のリード 1 a それぞれのチップ側の端部は、半導体チップ 2 の裏面 2 c の周縁部と対向している。その際、複数のリード 1 a それぞれのチップ側の端部に第 1 肉薄部 1 f が形成され、この第 1 肉薄部 1 f が半導体チップ 2 の裏面 2 c と対向している。これにより、リード 1 a の表面（ワイヤ接続面）とタブ 1 b

50

のチップ支持面（主面）1cが同じ高さとなっていても、半導体チップ2の裏面2cにおける周縁部と各リード1aのチップ側に位置する端部との接触不良を抑制することができる。この結果、半導体装置の小型化・薄型化を維持しつつ、パッケージサイズに近い大きさの半導体チップ2を搭載することができる。

【0039】

なお、第1肉薄部1fは、例えば、ハーフエッティング加工によって形成される。例えば、リードフレームの板厚が0.2mmの場合、各リード1aの厚さも0.2mmであり、その際、第1肉薄部1fは、ハーフエッティング加工により、板厚0.1mmとなる。

【0040】

このように半導体チップ2の裏面2cの外周部の下部に、複数のリード1aそれぞれの第1肉薄部1fをもぐり込ませた構造であるため、必然的にタブ1bはその外形の大きさが半導体チップ2の裏面2cの外形サイズより小さな、いわゆる小タブ構造となっている。

【0041】

また、各リード1aのチップ側と反対側の端部は、図1及び図5に示すように封止体3の側面3bに露出して終端している。

【0042】

また、QFN5では、ダイボンド材として銀ペースト6を採用しており、フィルムタイプの接着材を用いることに比較して製造コストの低減化を図ることができるが、銀ペースト6の採用により、その流出対策が必要となるため、この銀ペースト6の流出対策として、タブ1bの周縁部に段差部1eが形成されている。

【0043】

なお、QFN5では、タブ1bの周縁部に段差部1eが形成されているため、タブ1bのチップ支持面1cを銀ペースト6で十分に濡らすことができる。すなわち、QFN5においては、図5に示すように、タブ1bのチップ支持面1cの全面に銀ペースト6が配置されている。

【0044】

このようにタブ1bのチップ支持面1cの全面に銀ペースト6が配置されていることで、タブ1bと半導体チップ2の間に隙間が形成されにくくなるため、銀ペースト6内にボイドが形成されることを低減できる。

【0045】

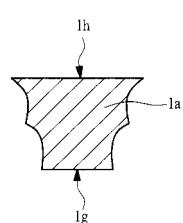

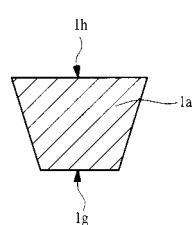

次に、リード1aは、図8に示すように、ハーフエッティングにより、ワイヤ接続面1hの幅が、封止体3から露出する実装面1gの幅よりも太くなるように形成されている。簡略すると、その断面形状が逆台形状に形成されている。

【0046】

これにより、複数のリード1aが封止体3から脱落する問題を抑制している。ここで、本実施の形態1では、ハーフエッティングにより形成することについて説明したが、これに限定されるものではなく、図9に示すように、プレス加工により形成してもよい。但し、上記したように、タブ1bや段差部1eはハーフエッティング加工により形成するため、複数のリード1aもハーフエッティング加工により形成することで、工程の簡略化を図ることが出来る。

【0047】

一方、タブ1bについては、はみ出した銀ペースト6を停留させるための段差部1eを、上面（チップ支持面）側からハーフエッティング加工により形成するため、その断面形状を逆台形形状に形成することが困難である。

【0048】

そこで、本実施の形態1では、タブ1bと連結する複数の吊りリード1iに、タブ1bの脱落を防止する対策を施している。

【0049】

すなわち、タブ1bと連結するとともにコーナー部に向かって延在する吊りリード1i

10

20

30

40

50

は、図 6 に示すようにその裏面側がハーフエッティングによって削られて薄く形成された第 2 肉薄部 1 j を備えている。これにより、第 2 肉薄部 1 j は封止体 3 内に埋め込まれており、その端部は封止体 3 のコーナー部の側面 3 b に露出して終端している。このとき、図 7 に示すように、吊りリード 1 i の先端部を分岐させ、隣接する封止体のそれぞれの側面から露出させることで、複数のリード 1 a と吊りリード 1 i と同じダイシング工程により切断することが可能となり、工程の簡略化が図れる。

【0050】

このように、タブ 1 b とその 4 つの角部で連結する吊りリード 1 i の第 2 肉薄部 1 j が封止体 3 内に埋め込まれていることで、吊りリード 1 i と連結しているタブ 1 b の封止体 3 からの抜け落ち（脱落）を防止することができる。

10

【0051】

なお、図 5 及び図 6 に示すように、タブ 1 b の裏面 1 d とリード 1 a の実装面 1 g には、外装めっき 7 が形成されている。すなわち、封止体 3 から露出するリード部分であるタブ 1 b の裏面 1 d とリード 1 a の実装面 1 g には、例えば、錫・ビスマス等の Pb フリー半田からなる外装めっき 7 が形成されている。

【0052】

なお、半導体チップ 2 は、例えば、シリコンから成り、その正面 2 b に半導体素子及び複数の電極であるパッド 2 a が形成されており、これらのパッド 2 a と各パッド 2 a に対応するリード 1 a とがそれぞれ導電性のワイヤ 4 によって電気的に接続されている。ワイヤ 4 は、例えば、金線である。

20

【0053】

また、各リード 1 a、タブ 1 b 及び吊りリード 1 i は、例えば、銅合金から成り、それぞれの厚さは、例えば、0.2 mm 程度である。

【0054】

また、封止体 3 は、例えば、エポキシ系の熱硬化性樹脂から成る。

【0055】

本実施の形態 1 の半導体装置（QFN5）によれば、タブ 1 b のチップ支持面 1 c の周縁部にチップ支持面 1 c より高さの低い段差部 1 e が形成されていることにより、タブ 1 b からはみ出した銀ペースト 6（ダイボンド材）をこの段差部 1 e で受け止めて段差部 1 e に停留させることができる。

30

【0056】

これにより、銀ペースト 6 の封止体 3 の裏面 3 a への流出を防ぐことができ、その結果、パッケージ裏面の外装めっき 7 に銀ペースト 6 が付着することを阻止できる。さらに、外装めっき 7 が形成できなくなるという問題を引き起こさなくなる。

【0057】

その結果、QFN5（半導体装置）の品質や信頼性を向上させることができる。

【0058】

（実施の形態 2）

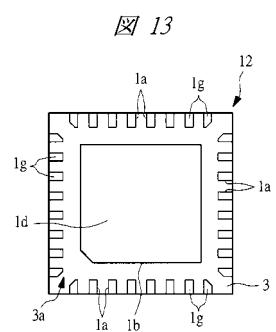

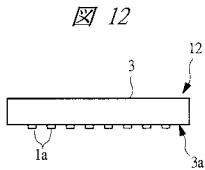

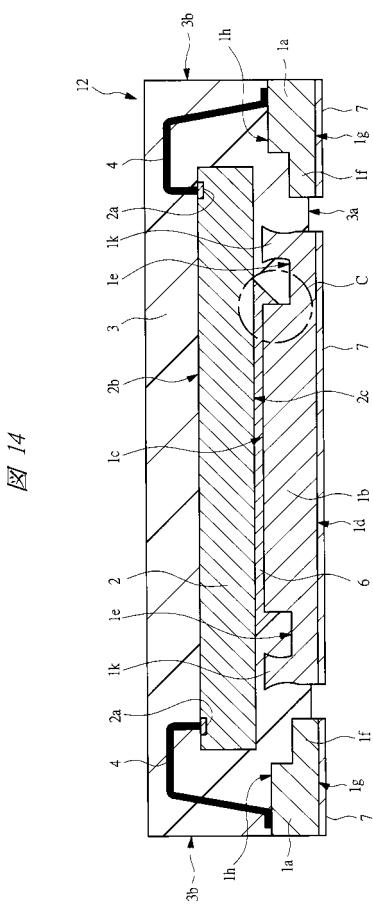

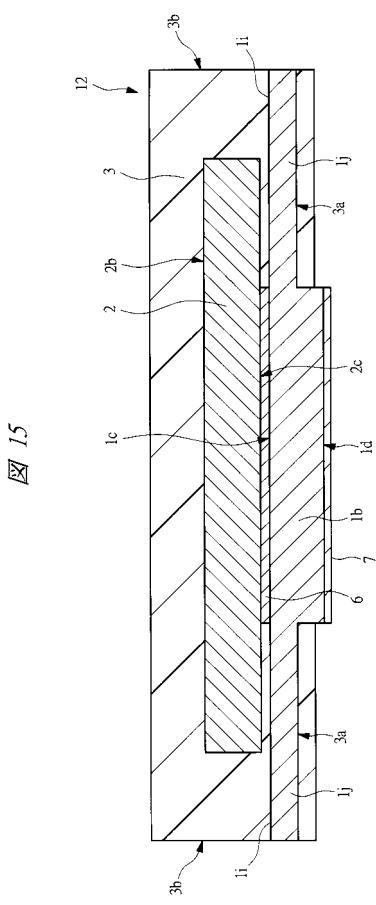

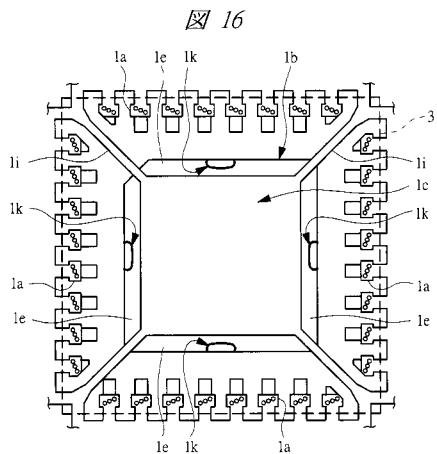

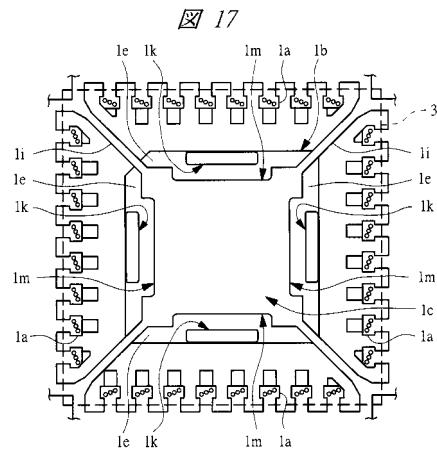

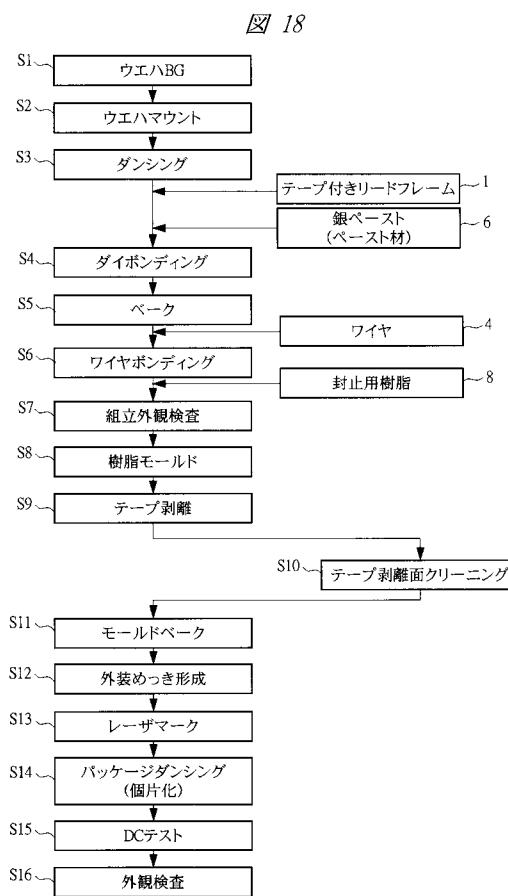

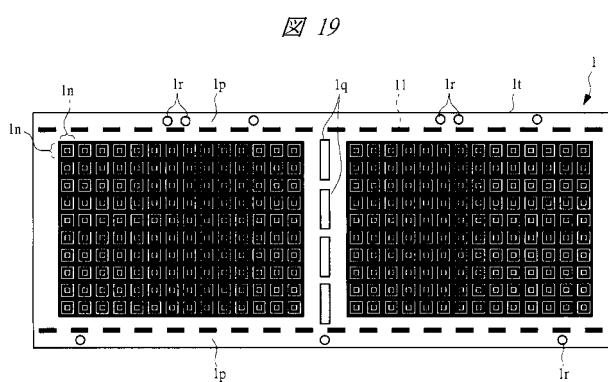

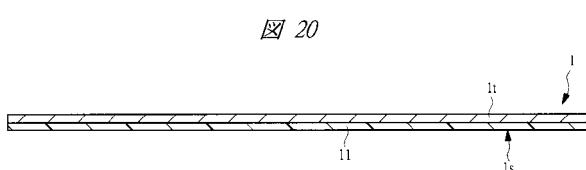

図 10 は本発明の実施の形態 2 の半導体装置の構造の一例を封止体を透過して示す斜視図、図 11 は図 10 に示す半導体装置の構造を示す平面図、図 12 は図 10 に示す半導体装置の構造を示す側面図、図 13 は図 10 に示す半導体装置の構造を示す裏面図、図 14 は図 10 に示す A - A 線に沿って切断した構造の一例を示す断面図、図 15 は図 10 に示す B - B 線に沿って切断した構造の一例を示す断面図である。また、図 16 は図 10 に示す半導体装置におけるタブと突起部の構造を封止体を透過して示す部分平面図、図 17 は本発明の実施の形態 2 の変形例の半導体装置におけるタブと突起部の構造を封止体を透過して示す部分平面図、図 18 は本発明の実施の形態 2 の半導体装置の組み立て順の一例を示す製造フロー図である。さらに、図 19 は本発明の実施の形態 2 の半導体装置の組み立てに用いられるテープ付きリードフレームの構造の一例を示す平面図、図 20 は図 19 に示すテープ付きリードフレームの構造の一例を示す断面図、図 21 は図 19 に示すテープ付きリードフレームに貼り付けられたテープの構造の一例を示す断面図である。

40

50

## 【0059】

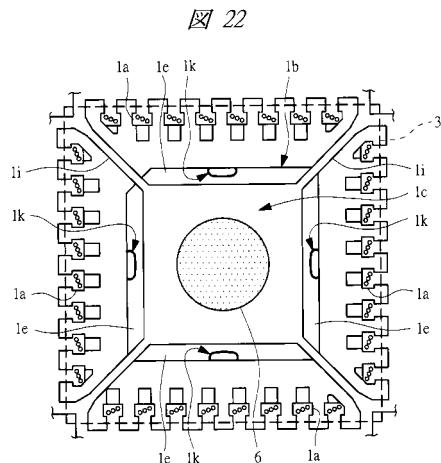

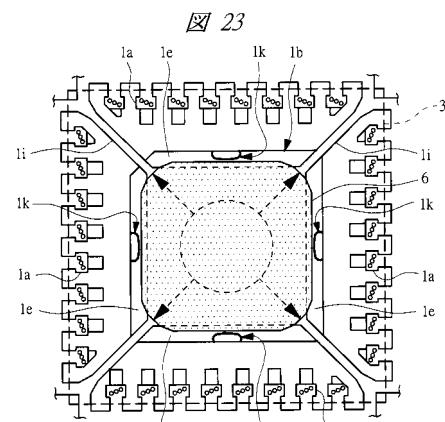

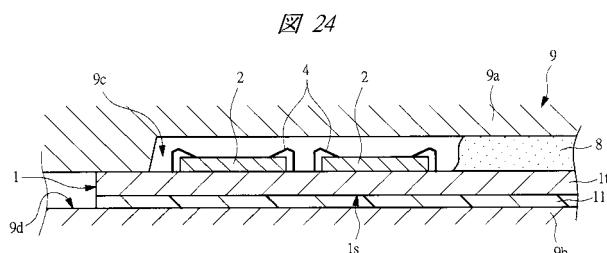

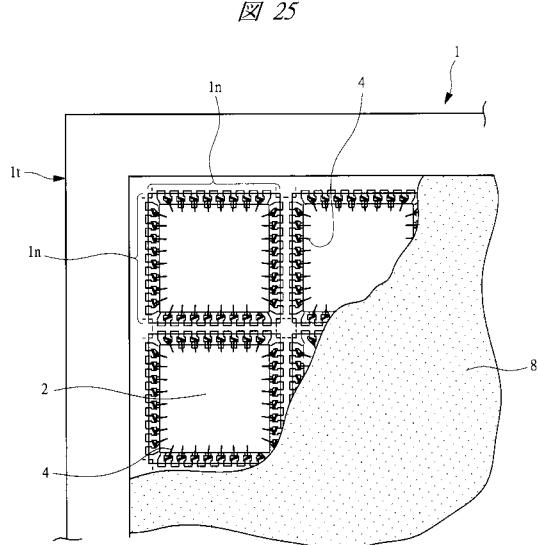

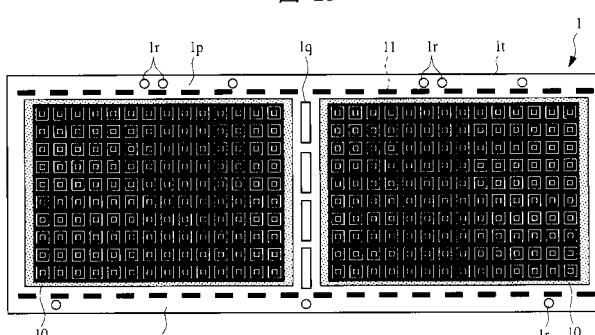

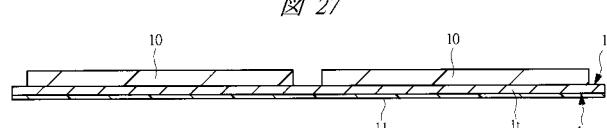

また、図22は本発明の実施の形態2の半導体装置の組み立てのダイボンディング工程におけるペースト材塗布状態の一例を示す部分平面図、図23は本発明の実施の形態2の半導体装置の組み立てのダイボンディング工程におけるペースト材塗布後の濡れ広がり状態の一例を示す部分平面図である。さらに、図24は本発明の実施の形態2の半導体装置の組み立てのモールド工程における樹脂注入状態の一例を示す部分断面図、図25は図24に示す樹脂注入状態を示す部分平面図、図26は本発明の実施の形態2の半導体装置の組み立てのモールド完了後の構造の一例を示す平面図、図27は図26に示すモールド完了後の構造を示す断面図である。また、図28は本発明の実施の形態2の半導体装置の組み立てのテープ剥離工程におけるテープ剥離状態の一例を示す断面図である。

10

## 【0060】

本実施の形態2は、実施の形態1のQFN5と同様に、小タブ構造で、かつタブ露出型の半導体装置(QFN12)の構造とその組み立てについて説明するものであり、特に説明しない箇所については、本実施の形態1と同様の構成とする。

## 【0061】

小型化を図ったQFN12を組み立てる場合、その生産効率の高さからMAP(Mold Array Package)方式を採用する場合が多い。すなわちMAP方式を用いることで1フレーム当たりの製品の取り数を各段に増やして生産効率を高めるものである。

20

## 【0062】

なお、QFN12をMAP(Mold Array Package)方式で組み立てる際には、そのモールド工程において、図28に示すようにリードフレームの裏面1sからテープ11を剥離する際に、接着層11b付きのテープ11を用いるため、タブ(ダイパッドともいう)1bに対して引っ張る力が作用し、タブ1bの段差部1eと封止体3との間で剥離が発生し易くなる。

20

## 【0063】

ここで、QFN12の組み立てにおける接着層11b付きのテープ11の必要性について説明する。MAP方式でQFN12を組み立てる場合、そのモールド工程での樹脂成形金型9のクランプ時には、リードフレーム上の製品領域の外側の外周部しかクランプできない。この状態で樹脂成形金型内への樹脂の注入を行うと、樹脂注入時の圧力によって、リードフレームの外周部から遠い製品領域の中央付近では、リードフレームからテープ11が浮いてしまい、リードフレームとテープ11の間に樹脂が入り込んで、リードフレームの裏面1sに樹脂バリが形成される。

30

## 【0064】

したがって、リードフレームの裏面1s側に前記樹脂バリが形成されないように、接着層11b付きのテープ11を用いて、接着層11bを介してリードフレームにしっかりとテープ11を接着した状態で樹脂モールディングを行う。

## 【0065】

すなわち、QFN12の組み立てでは、樹脂バリ対策として、接着層11b付きのテープ11を用いることが必要となる。

40

## 【0066】

したがって、モールド工程における樹脂封止後のテープ11の剥離工程で、テープ11が接着層11bを介してリードフレームにしっかりと接着されているため、テープ11を剥離する際に、タブ1bも引っ張られて脱落する方向に力が作用し、タブ1bの段差部1eと封止体3との間で剥離が発生し易くなる。特に、タブ1bの段差部1eには銀ペースト6が流出している場合があり、その場合、タブ1bと封止体3の密着性は低下しており、剥離し易い。結果的には、そこに隙間ができ易い。

## 【0067】

なお、タブ1bの段差部1eと封止体3との間で剥離が発生すると、そこに隙間が形成され、モールド後の工程で隙間にめっき液等の不純物が入り込み、さらにその後の工程で隙間に入り込んだ不純物がしみ出して外装めっき7が変色する等の問題が起こる。

50

## 【0068】

また、テープ剥離後のテープ剥離面クリーニング工程で洗浄のために使用する有機系溶剤等の薬液が前記隙間に入り込んで、前記同様、その後の工程で隙間に入り込んだ前記薬液等の不純物がしみ出して外装めっき7が剥離する等の問題が起こる。

## 【0069】

そこで、本実施の形態2のQFN12は、実施の形態1のQFN5と同様に、タブ1bに段差部1eを設けたことで、銀ペースト6(ペースト材)の封止体3への流出を阻止するとともに、タブ1bの段差部1eと封止体3の剥離を抑制するものである。

## 【0070】

ここで、本実施の形態2のQFN12の構成について説明する。ここでは、QFN12の実施の形態1のQFN5との相違点のみ説明する。

10

## 【0071】

図10～図15に示す本実施の形態2のQFN12は、実施の形態1のQFN5と同様に小型で、小タブ構造、かつタブ露出型の半導体パッケージである。QFN12にも、QFN5と同様に、タブ1bのチップ支持面1cの周縁部にハーフエッチング加工によって段差部1eが形成されている。この段差部1eは、図16に示すように、タブ1bのチップ支持面1cの周縁部における吊りリード1iを除く箇所に、チップ支持面1cより低い位置に形成されている。

## 【0072】

図14のC部に示すように、段差部1eが設けられていることで、チップ支持面1cから溢れてはみ出した銀ペースト6は、段差部1eに向かう箇所で停留しており、銀ペースト6が封止体3の裏面3aに流出することは無い。

20

## 【0073】

本実施の形態2のQFN12の特徴は、タブ1bの段差部1eに半導体チップ2に向かって段差部1eから突出した突起部1kが形成されていることである。

## 【0074】

この突起部1kは、タブ1bの段差部1eと封止体3のアンカー効果を高めて両者の密着性を高めるものであり、タブ1bの段差部1eと封止体3の剥離を抑制するものである。

30

## 【0075】

なお、タブ1bの段差部1eのハーフエッチング加工時にこの突起部1kの箇所にマスクを配置した状態で、突起部1kの周囲をハーフエッチングによって削ることで突起部1kの箇所を残す方法で形成したものである。したがって、突起部1kの高さは、タブ1bのチップ支持面1cの高さと同じ高さになっている。

## 【0076】

また、突起部1kは、図14に示すように、その先端部付近が中央部付近より幅広となっており、逆台形形状となっている。すなわち、ハーフエッチング時に、突起部1kの高さ方向の中央付近は、マスクが配置された先端付近よりエッチングレートが大きいため、先端付近より多く削られ、結果的に逆台形形状になる。突起部1kの先端付近の形状が逆台形形状であることにより、アンカー効果をさらに高めることができる。

40

## 【0077】

また、QFN12では、図16に示すように、タブ1bのチップ支持面1cが四角形を成し、突起部1kは、四角形のタブ1bの1つの辺に対応した段差部1eの中央部に形成されている。さらに、四角形のタブ1bの1つの辺に対応した段差部1eに1つずつ形成されている。

## 【0078】

ただし、突起部1kの数については、アンカー効果のみを向上させるのであれば、四角形のタブ1bの1つの辺に対応した段差部1eに複数個形成した方が好ましいが、封止用樹脂8(図24参照)の流動性を阻害しないようにするためには、図16に示すように、1つの辺に対応した各段差部1eの中央部付近に1つずつ形成されていることが好ましい

50

。

## 【0079】

なお、突起部1kとタブ1bの距離は、例えば、リードフレームの板厚が0.2mmの場合、封止用樹脂8やエッティング液を通し易くするために、例えば、0.2mm程度必要である。

## 【0080】

そこで、図17は突起部1kの変形例を示すものであり、細長い突起部1kをそれぞれの辺の段差部1eに形成した場合であり、突起部1kとタブ1bの間に、封止用樹脂8やエッティング液を十分に通すだけの距離が保てない場合には、チップ支持面1cの各辺に各辺の突起部1kから遠ざかる方向に抉れた抉れ部(窪み部)1mを形成してもよい。

10

## 【0081】

このようにチップ支持面1cに抉れ部1mを形成することで、細長い突起部1k(タブ1bの水平方向への窪み)を形成しても封止用樹脂8やエッティング液を十分に通すことが可能になるとともに、タブ1bと封止体3のアンカー効果をより高めることができる。

## 【0082】

次に、本実施の形態2のQFN12(半導体装置)の製造方法を、図18に示す組み立てフロー図に沿って説明する。

## 【0083】

まず、ウエハを供給して図18のステップS1に示すウエハBGを行う。すなわち、ウエハの裏面研磨を行ってウエハを所望の厚さにする。

20

## 【0084】

その後、ダイシング治具にウエハを固定するステップS2に示すウエハマウントを行う。

。

## 【0085】

その後、ステップS3に示すダイシングを行う。すなわち、ダイシングによってウエハを切断し、各半導体チップ2に個片化する。

## 【0086】

次に、図19及び図20に示すテープ付きリードフレーム(リードフレーム)1を準備し、このテープ付きリードフレーム1を供給して、さらに銀ペースト6を供給してステップS4に示すダイボンディングを行う。なお、本実施の形態2のQFN12の組み立てに用いられるリードフレームは、テープ付きリードフレーム1である。

30

## 【0087】

すなわち、QFN12をMAP方式による樹脂モールディングを行って組み立てるため、前述したように、リードフレームの裏面1s側に前記樹脂バリが形成されないようにテープ付きリードフレーム1を用いる。

## 【0088】

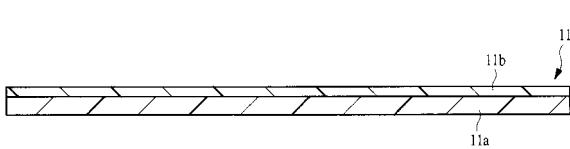

なお、テープ付きリードフレーム1は、例えば、銅合金等から成る金属のリードフレームであるフレーム本体1tの裏面1sに、図21に示すような基材11aと接着層11bとから成るテープ11を貼り付けたものである。すなわち、フレーム本体1tの裏面1sに接着層11bを有するテープ11を貼り付けたものである。また、テープ付きリードフレーム1の主面(チップ搭載側の面)には、図19に示すようにマトリクス配列で複数のデバイス領域(半導体装置形成領域)1nが隣接して形成されている。

40

## 【0089】

また、各デバイス領域1nには、チップ支持面1cの周縁部にチップ支持面1cより高さの低い段差部1eが形成されたタブ1bと、タブ1bの周囲に配置された複数のリード1aと、段差部1eに形成された突起部1kとが形成されている。さらに、テープ付きリードフレーム1のフレーム本体1tの長手方向に平行な方向の枠部1pには複数のガイド孔1rが形成されており、さらに複数のデバイス領域1nの集合体同士の間にはスリット1qが形成されている。

## 【0090】

50

なお、ステップS4に示すダイボンディング工程では、まず、タブ1bのチップ支持面1c上に銀ペースト6を塗布する。なお、タブ1bは半導体チップ2の裏面2cより外形サイズが小さな、所謂小タブである。図22に示すように、まず、タブ1bの中央部に銀ペースト6を塗布する。その後、タブ1bのチップ支持面1c上に銀ペースト6を介して半導体チップ2を接合する。その際、チップ支持面1c上に半導体チップ2を搭載すると、図23に示すように、チップ支持面1cの略全面に亘って銀ペースト6が漏れ広がった状態となる。なお、銀ペースト6を十分に塗布して、例え、銀ペースト6がチップ支持面1cからはみ出して垂れてもタブ1bの周縁部には段差部1eが形成されているため、垂れた銀ペースト6を受け止めることができ、封止体3の裏面3aに銀ペースト6が流出することを防止できる。

10

## 【0091】

これによりダイボンディング工程を完了する。

## 【0092】

その後、ステップS5に示すベークを行って銀ペースト6を熱処理する。

## 【0093】

その後、ステップS6に示すワイヤボンディングを行う。ここでは、ワイヤ4を供給して、図14に示すように、半導体チップ2の複数のパッド2aそれぞれと、これに対応するリード1aそれぞれのワイヤ接続面1hとを金線等のワイヤ4によって電気的に接続する。

20

## 【0094】

その後、ステップS7に示す組立外観検査を行う。

## 【0095】

その後、ステップS8に示す樹脂モールドを行う。ここでは、図24及び図25に示すように、複数のデバイス領域（半導体装置形成領域）1nを樹脂成形金型9の1つのキャビティ9cで覆った状態で封止用樹脂8をキャビティ9c内に注入する。

30

## 【0096】

その際、接着層11bを有するテープ11がフレーム本体1t（リードフレーム）の裏面1sに貼り付けられた状態で、図24に示すように、このテープ付きリードフレーム1を下型9bの金型面9d上に配置し、その後、上型9aのキャビティ9cで図25に示す複数のデバイス領域1nを覆うようにして樹脂成形金型9の上型9aと下型9bをクランプし、この状態で封止用樹脂8をキャビティ9c内に注入する。

## 【0097】

封止用樹脂8の注入により、図14に示すように、半導体チップ2とタブ1bの段差部1eとの間に封止用樹脂8を周り込ませ、かつタブ1bのチップ支持面1cと反対側の裏面1d及び複数のリード1aそれぞれの実装面1g（一部）が露出するように半導体チップ2と複数のワイヤ4を樹脂封止し、これによって図26及び図27に示すように一括封止体10を形成する。

## 【0098】

その後、図18に示すステップS9のテープ剥離を行う。ここでは、図28に示すように、テープ付きリードフレーム1のフレーム本体1tの裏面1sからテープ11を引っ張って剥離する。

40

## 【0099】

この時、QFN12では、タブ1bの段差部1eに半導体チップ2に向かって突出した突起部1kが形成されており、この突起部1kにより、タブ1bの段差部1eと封止体3のアンカー効果が高められている。すなわち、タブ1bの段差部1eと封止体3の密着性が高められているため、テープ11を剥離する際に、タブ1bが封止体3から脱落する方向に引っ張られてもタブ1bの段差部1eと封止体3の剥離を抑制することができる。

## 【0100】

これによって、テープ剥離時に、タブ1bと封止体3の間に隙間が形成されることを抑制できる。

50

## 【0101】

その後、ステップS10に示すテープ剥離面クリーニングを行う。すなわち、テープ付きリードフレーム1のフレーム本体1tの裏面1sを洗浄する。ここでは、例えば、アセトン等の有機系溶剤を用いてテープ11の接着層11bの残りを除去する。その際、本実施の形態2のQFN12では、タブ1bの段差部1eに突起部1kが形成されており、そのアンカー効果により、タブ1bと封止体3の間に隙間が形成され難くなっている。

## 【0102】

したがって、有機系溶剤等の薬液を使用してもこの薬液がタブ1bと封止体3の間には入りにくくなっている。その結果、後の処理工程で、前記有機系溶剤等の薬液(不純物)がしみ出す(流出する)ことを抑制できる。

10

## 【0103】

その後、ステップS11に示すモールドベークを行う。ここでは、熱処理により封止体3を硬化させる。

## 【0104】

その後、ステップS12に示す外装めっき形成を行う。ここでは、一括封止体10から露出するタブ1bの裏面1d及び複数のリード1aそれぞれの実装面1gに外装めっき7を形成する。外装めっき7は、例えば、錫-ビスマス等のPbフリー半田である。なお、QFN12の組立てでは、タブ1bの段差部1eに突起部1kが形成されたことで、アンカー効果により、タブ1bと封止体3の間に隙間が形成され難くなっているため、外装めっき形成工程で、薬液等の不純物がタブ1bと封止体3の間には入りにくくなっているため、外装めっき形成工程で、薬液等の不純物がしみ出すことを抑制できる。

20

## 【0105】

したがって、本実施の形態2のQFN12の組立てでは、段差部1eと封止体3の間に不純物が入り難いため、外装めっき形成工程で前記不純物がしみ出して外装めっき7を変色させることを抑制できる。また、不純物がしみ出すことによって外装めっき7が剥離することも抑制できる。

## 【0106】

その後、ステップS13に示すレーザマーキングを行って、封止体3の表面に所望のマークを付ける。

30

## 【0107】

その後、ステップS14に示すパッケージダイシングを行う。ここでは、一括封止体10及びリードフレーム(フレーム本体1t)を切断して各QFN12に個片化する。

## 【0108】

その後、ステップS15のDCテスト、ステップS16の外観検査を行ってQFN12の組立て完了となる。

## 【0109】

本実施の形態2のQFN12及びその製造方法によれば、タブ1bの段差部1eに半導体チップ2に向かって突出した突起部1kが形成されていることにより、アンカー効果によって封止体3とタブ1bの密着性を高めることができる。

40

## 【0110】

これにより、タブ1bの段差部1eでの剥離を抑制することができる。すなわち、タブ1bと封止体3との隙間を可能な限り小さくすることで、タブ1bの封止体3との界面に薬液等の不純物が入りにくくなり、したがって、前記不純物の流出による外装めっき7の変色を抑制することができる。また、前記不純物の流出による外装めっき7の剥離も抑制することができる。

## 【0111】

その結果、QFN12(半導体装置)の品質や信頼性を向上させることができる。

## 【0112】

本実施の形態2のQFN12及びその製造方法によって得られるその他の効果については、実施の形態1と同様であるため、その重複説明は省略する。

50

## 【0113】

以上、本発明者によってなされた発明を発明の実施の形態に基づき具体的に説明したが、本発明は前記発明の実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

## 【0114】

例えば、前記実施の形態2では、タブ1bの段差部1eに設けられている突起部1kの高さが、タブ1bのチップ支持面1cと同じ高さの場合について説明したが、突起部1kの高さは、封止体3との間でアンカー効果を得ることが可能な高さであれば、チップ支持面1cより低くてもよい。

## 【産業上の利用可能性】

10

## 【0115】

本発明は、小型の電子装置およびその製造技術に好適である。

## 【図面の簡単な説明】

## 【0116】

【図1】本発明の実施の形態1の半導体装置の構造の一例を封止体を透過して示す斜視図である。

【図2】図1に示す半導体装置の構造を示す平面図である。

【図3】図1に示す半導体装置の構造を示す側面図である。

【図4】図1に示す半導体装置の構造を示す裏面図である。

20

【図5】図1に示すA-A線に沿って切断した構造の一例を示す断面図である。

【図6】図1に示すB-B線に沿って切断した構造の一例を示す断面図である。

【図7】図1に示す半導体装置におけるタブ、吊りリード、及びリードの構造を封止体を透過して示す部分平面図である。

【図8】図7に示すC-C線に沿って切断した断面図である。

【図9】図8の変形例図である。

【図10】本発明の実施の形態2の半導体装置の構造の一例を封止体を透過して示す斜視図である。

【図11】図10に示す半導体装置の構造を示す平面図である。

30

【図12】図10に示す半導体装置の構造を示す側面図である。

【図13】図10に示す半導体装置の構造を示す裏面図である。

【図14】図10に示すA-A線に沿って切断した構造の一例を示す断面図である。

【図15】図10に示すB-B線に沿って切断した構造の一例を示す断面図である。

【図16】図10に示す半導体装置におけるタブと突起部の構造を封止体を透過して示す部分平面図である。

【図17】本発明の実施の形態2の変形例の半導体装置におけるタブと突起部の構造を封止体を透過して示す部分平面図である。

【図18】本発明の実施の形態2の半導体装置の組み立て順の一例を示す製造フロー図である。

【図19】本発明の実施の形態2の半導体装置の組み立てに用いられるテープ付きリードフレームの構造の一例を示す平面図である。

40

【図20】図19に示すテープ付きリードフレームの構造の一例を示す断面図である。

【図21】図19に示すテープ付きリードフレームに貼り付けられたテープの構造の一例を示す断面図である。

【図22】本発明の実施の形態2の半導体装置の組み立てのダイボンディング工程におけるペースト材塗布状態の一例を示す部分平面図である。

【図23】本発明の実施の形態2の半導体装置の組み立てのダイボンディング工程におけるペースト材塗布後の濡れ広がり状態の一例を示す部分平面図である。

【図24】本発明の実施の形態2の半導体装置の組み立てのモールド工程における樹脂注入状態の一例を示す部分断面図である。

【図25】図24に示す樹脂注入状態を示す部分平面図である。

50

【図26】本発明の実施の形態2の半導体装置の組み立てのモールド完了後の構造の一例を示す平面図である。

【図27】図26に示すモールド完了後の構造を示す断面図である。

【図28】本発明の実施の形態2の半導体装置の組み立てのテープ剥離工程におけるテープ剥離状態の一例を示す断面図である。

【符号の説明】

【0117】

|       |                       |    |

|-------|-----------------------|----|

| 1     | テープ付きリードフレーム(リードフレーム) |    |

| 1 a   | リード                   | 10 |

| 1 b   | タブ(チップ搭載部)            |    |

| 1 c   | チップ支持面                |    |

| 1 d   | 裏面                    |    |

| 1 e   | 段差部                   |    |

| 1 f   | 第1肉薄部                 |    |

| 1 g   | 実装面                   |    |

| 1 h   | ワイヤ接続面                |    |

| 1 i   | 吊りリード                 |    |

| 1 j   | 第2肉薄部                 |    |

| 1 k   | 突起部                   |    |

| 1 m   | 抉れ部                   | 20 |

| 1 n   | デバイス領域(半導体装置形成領域)     |    |

| 1 p   | 枠部                    |    |

| 1 q   | スリット                  |    |

| 1 r   | ガイド孔                  |    |

| 1 s   | 裏面                    |    |

| 1 t   | フレーム本体                |    |

| 2     | 半導体チップ                | 20 |

| 2 a   | パッド(電極)               |    |

| 2 b   | 正面                    |    |

| 2 c   | 裏面                    | 30 |

| 3     | 封止体                   |    |

| 3 a   | 裏面                    |    |

| 3 b   | 側面                    |    |

| 4     | ワイヤ                   |    |

| 5     | QFN(半導体装置)            |    |

| 6     | 銀ペースト(ペースト材)          |    |

| 7     | 外装めつき                 |    |

| 8     | 封止用樹脂                 |    |

| 9     | 樹脂成形金型                |    |

| 9 a   | 上型                    | 40 |

| 9 b   | 下型                    |    |

| 9 c   | キャビティ                 |    |

| 9 d   | 金型面                   |    |

| 1 0   | 一括封止体                 |    |

| 1 1   | テープ                   |    |

| 1 1 a | 基材                    |    |

| 1 1 b | 接着層                   |    |

| 1 2   | QFN(半導体装置)            |    |

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【図 6】

図 6

【図 7】

図 7

【図 8】

図 8

【図 9】

図 9

【図 10】

図 10

【図 1 1】

【図 1 3】

【図 1 2】

【図 1 4】

【図 1 5】

【図16】

図16

【図17】

図17

【図18】

図18

【図19】

図19

【図20】

図20

【図21】

図21

【図 2 2】

図 22

【図 2 3】

図 23

【図 2 4】

図 24

【図 2 5】

図 25

【図 2 6】

図 26

【図 2 7】

図 27

【図28】

図28