(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-78161

(P2005-78161A)

(43) 公開日 平成17年3月24日(2005.3.24)

(51) Int.C1.<sup>7</sup>

**G06F 3/06**

**G06F 3/08**

**G06K 17/00**

**H04N 5/225**

**H04N 5/907**

F 1

G06F 3/06

G06F 3/08

G06F 3/06

G06F 3/08

G06K 17/00

301B

301M

302Z

C

D

テーマコード(参考)

5B058

5B065

5C022

5C052

審査請求 未請求 請求項の数 10 O L (全 18 頁) 最終頁に続く

(21) 出願番号

(22) 出願日特願2003-304622 (P2003-304622)

平成15年8月28日 (2003.8.28)

(71) 出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100090538

弁理士 西山 恵三

(74) 代理人 100096965

弁理士 内尾 裕一

(72) 発明者 嶋嶋 吉博

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

Fターム(参考) 5B058 CA23 CA26 KA04 YA20

5B065 BA09 CA01 CA40 CC08 CE03

CE07 CH02 CH20

5C022 AB00 AC69

5C052 AA17 AB02 EE08 GA02 GB01

GE08 GF01

(54) 【発明の名称】記録装置

## (57) 【要約】

【課題】 メモリカードと装置の間のデータ転送を短時間に完了することを可能とする。

【解決手段】 本発明では、第1のサイズの画像データをメモリカードに書き込むにあたり、DMA回路は第1のサイズの画像データの書き込みが完了するまでカードI/Fに対して画像データを転送すると共に、カードI/Fは、メモリカードに対する第1のサイズよりも小さい第2のサイズの画像データの書き込みが完了する度にメモリカードのステータスが所定の状態であることをチェックし、メモリカードに対して第1のサイズの画像データの書き込みが完了したことに応じてマイクロプロセッサに対して割り込み要求信号を出力する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

マイクロプロセッサと、

メモリデバイスに対してデータを書き込むメモリ制御手段と、

前記マイクロプロセッサの指示に従い、前記メモリ制御手段に対して前記データを転送処理するDMA手段とを備え、

第1のサイズの前記データを前記メモリデバイスに書き込むにあたり、前記DMA手段は前記第1のサイズのデータの書き込みが完了するまで前記メモリ制御手段に対して前記データを転送すると共に、前記メモリ制御手段は、前記メモリデバイスに対する前記第1のサイズよりも小さい第2のサイズの前記データの書き込みが完了する度に前記メモリデバイスの状態が所定の状態であることをチェックし、前記メモリデバイスに対して前記第1のサイズのデータの書き込みが完了したことに応じて前記マイクロプロセッサに対して割り込み要求信号を出力することを特徴とする記録装置。10

**【請求項 2】**

前記メモリ制御手段は、前記記録媒体の状態が前記所定の状態ではない場合、前記記録媒体に対する前記データの書き込みを停止することを特徴とする請求項1記載の記録装置。

**【請求項 3】**

前記メモリ制御手段は、前記記録媒体から読み出したステータスデータと予め設定した比較値とを比較する比較手段を有し、前記比較手段の出力に基づいて前記メモリデバイスの状態をチェックすることを特徴とする請求項1記載の記録装置。20

**【請求項 4】**

前記メモリデバイスは前記第2のサイズのデータが書き込まれる度に割り込み要求を出し、前記メモリ制御手段は前記メモリデバイスが割り込み要求を発生したことに応じて前記ステータスデータを前記メモリデバイスより読み出すことを特徴とする請求項3記載の記録装置。

**【請求項 5】**

前記メモリ制御手段は、前記第1のサイズのデータの書き込み開始の指示に応じて前記メモリデバイスより前記ステータスデータを読み出すことを特徴とする請求項4記載の記録装置。

**【請求項 6】**

前記DMA手段による前記データの転送を行うか否かを制御するステート制御手段を備えたことを特徴とする請求項1記載の記録装置。30

**【請求項 7】**

前記データは画像データを含み、前記ステート制御手段は前記画像データを出力する撮像手段の動作状態に応じて前記DMA手段による前記データの転送を行うか否かを制御することを特徴とする請求項6記載の記録装置。

**【請求項 8】**

前記ステート制御手段は、前記画像データの垂直同期期間に同期した所定期間の間、前記DMA手段による前記データの転送を停止することを特徴とする請求項7記載の記録装置。40

**【請求項 9】**

前記第2のサイズは前記メモリデバイスに従って決定されることを特徴とする請求項1～8記載の記録装置。

**【請求項 10】**

マイクロプロセッサと、

メモリデバイスからデータを読み出すメモリ制御手段と、

前記マイクロプロセッサの指示に従い、前記メモリ制御手段により読み出されたデータを転送処理するDMA手段とを備え、

第1のサイズの前記データを前記メモリデバイスから読み出すにあたり、前記DMA手段は前記第1のサイズのデータの読み出しが完了するまで前記メモリ制御手段から読み出50

された前記データを転送すると共に、前記メモリ制御手段は、前記メモリデバイスからの前記第1のサイズよりも小さい第2のサイズの前記データの読み出しがする度に前記メモリデバイスの状態が所定の状態であることをチェックし、前記メモリデバイスから前記第1のサイズのデータの読み出しが完了したことに応じて前記マイクロプロセッサに対して割り込み要求信号を出力することを特徴とする再生装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は記録媒体に対してデータを記録再生する装置に関する。

【背景技術】

【0002】

従来、画像信号をデジタル信号として記録再生するデジタルカメラにおいては、画像データなどの記録媒体としてメモリカードを用いている。メモリカードの代表例としてPCカード、コンパクトフラッシュ（登録商標）などがある。これらのカードはATA規格で定められたコマンドを用いてデータのライト、リードを制御する。

【0003】

これらのメモリカードのうち、コンパクトフラッシュ（登録商標）の制御方法に関しては、CompactFlash Associationが発行する、CF+and CompactFlash Specification Revision 1.4に開示され、PCカードについてはPCMCIAJEIDAが発行するPC Card Standard Release 7に開示されている。

【0004】

例えばデータライトを行うときには、ホストはまずメモリカードに対してライトセクタコマンドを発行する。次にカードの状態がデータ書き込み可能状態になることを待つ。カードの状態がデータ書き込み可能状態になったことは、カードが出力する割り込み要求信号（IREQ信号）とカードのステータスレジスタを用いて検出することが可能である。ホストはIREQ信号のアサートを検出すると、カードのステータスレジスタをリードし、レディフラグがレディ状態であること、データリクエストフラグがデータリクエスト状態であること、エラーフラグがエラー状態でないこと、などを確認する。これが確認された場合、ホストがカードに対して1セクタのデータライトを行うことが可能となる。

【0005】

ホストがカードに対して複数セクタのデータを連続書き込みする場合においても、1セクタごとに上記のようなカードステータスの確認を行う必要がある。

【0006】

また、ホストがメモリカードからデータリードを行う場合も同様に、セクタリードコマンド、IREQ信号の確認、ステータスレジスタ値の確認の後に1セクタのデータリードが可能となる。

【0007】

このようなメモリカードのインターフェースを備えたシステムの例が、特許文献1に開示されている。メモリカードへのデータ転送はDMAコントローラによって制御される。

【0008】

このようにメモリカードとの間のデータ転送にはDMAを使用することが可能である。

【0009】

一方で、コンパクトフラッシュ（登録商標）やPCMCIAI/OカードといったATA規格を使用するメモリカードは、例えば1セクタといった所定のデータサイズを転送するごとに、カードのステータスをチェックすることを要求している。

【0010】

従って、メモリカードのインターフェースの制御を目的としてDMAを用いる場合、ホストはDMAによるデータ転送の単位を1セクタとし、1セクタ転送毎にステータスリードとチェックとDMAの起動を繰り返し行う必要がある。

10

20

30

40

50

**【0011】**

メモリカードはデータ転送の単位ごとに割り込み要求信号（I REQ 信号）を出力することが可能である。これをCPUの割り込み要求入力に接続することにより、CPUは1セクタごとにステータスチェックを行うことが可能となる。

**【0012】**

I REQ 信号がアサートされたとき、CPUはまず、それまで実行していたタスクを一時停止し、そのタスクに関するレジスタやスタックの値をメモリに退避する。そして割り込み処理を開始し、ステータスリードとステータス値のチェックを行う。そしてステータスレジスタのレディフラグがレディ状態であること、デタリクエストフラグがデタリクエスト状態であること、エラーフラグがエラー状態でないこと、などを期待値との比較によって行う。10

**【0013】**

期待値との比較が一致した場合、CPUはDMAの起動を行い、割り込み処理を終了する。これによって1セクタ分のデータをシステムメモリからメモリカード、あるいはメモリカードからシステムメモリに対する転送が達成できる。

**【0014】**

CPUは所望のデータ転送が終了するまでの間、これらの処理を繰り返し行うことで、データ転送を達成する。

**【特許文献1】特開平6-337840号公報**

20

**【発明の開示】****【発明が解決しようとする課題】****【0015】**

この様に、従来は、DMAを1セクタを単位として動作させ、さらに1セクタごとにカードのステータスレジスタの値を確認する必要がある。

**【0016】**

このため、CPUは1セクタごとに割り込み処理を実行する必要がある。

**【0017】**

通常、CPUは、メモリカードの処理のみでなく、電源制御、シリアル通信、デジタルカメラの場合では撮像制御といったさまざまなデバイスがアサートする割り込み要求を処理する。さらにはCPUはスタックやレジスタの退避も行う。30

**【0018】**

従って、カードがI REQ をアサートしても、CPUがそれに対してカードステータスのリードを開始するまでの間に、上記の処理も実行することになるため、数百マイクロ秒といった時間が消費されてしまう。

**【0019】**

これにより、メモリカードがI REQ をアサートしてからDMAがメモリカードに対するデータ転送を開始するまでの間に、数百マイクロ秒といった無駄な時間が発生し、ホストとカード間における所望のデータ全てを転送する時間が長大化する。

**【0020】**

特に、デジタルカメラにおいてはこの問題が重要になる。40

**【0021】**

デジタルカメラは、撮影を行うと画像ファイルを生成し、これをメモリカードに記録する。メモリカードへの記録時間が長大化した場合、カメラのユーザーは撮影後、次の撮影が可能となるまでの時間まで待たされることになり、シャッターチャンスを逃してしまう。

**【0022】**

また、CPUは1セクタ転送ごとに割り込み処理を起動するため、その間行われる他のタスクがその都度停止され、他のタスクの実行速度が低下する。

**【0023】**

例えばデジタルカメラにおいては、ユーザーインターフェースのレスポンスが低下した50

り、動画撮影の能力が低下することによって動画中の自動露出やオートホワイトバランスの処理が達成できず、画質の低下が起こる。

#### 【0024】

更に、デジタルカメラでは、通常、撮像素子は所定の周期に同期して水平ラインを読み出し、さらにこれを垂直方向に繰り返し読み出すことによって画像信号を得る。その際、画像の明るさやホワイトバランスを適切に制御する必要がある。このためデジタルカメラは生成した一画面の画像データを解析し、この結果を撮像回路にパラメータとしてセットすることにより、画像の明るさやホワイトバランスを適切に制御している。

#### 【0025】

従って、一般的に垂直プランキング期間と呼ばれる1フレームと1フレームの間の時間に画像データの解析から撮像回路に対するパラメータのセットを完了しなければならない。

#### 【0026】

このようなときにメモリカードに対するデータ転送を行っている場合、データ転送の間はこれがシステムのバスを占有するため、上記のような処理が次のフレームまでに完了できない場合があり、この場合画質が低下してしまう。

#### 【0027】

本発明はこのような問題を解決し、ホストとメモリカードの間のデータ転送時間を短縮するとともに情報機器がメモリカードに対するデータ転送を行っている間の処理能力を向上することで、レスポンスや撮像能力を向上することを目的とする。

#### 【課題を解決するための手段】

#### 【0028】

このような目的を達成するため、本発明においては、マイクロプロセッサと、メモリデバイスに対してデータを書き込むメモリ制御手段と、前記マイクロプロセッサの指示に従い、前記メモリ制御手段に対して前記データを転送処理するDMA手段とを備え、第1のサイズの前記データを前記メモリデバイスに書き込むにあたり、前記DMA手段は前記第1のサイズのデータの書き込みが完了するまで前記メモリ制御手段に対して前記データを転送すると共に、前記メモリ制御手段は、前記メモリデバイスに対する前記第1のサイズよりも小さい第2のサイズの前記データの書き込みが完了する度に前記メモリデバイスの状態が所定の状態であることをチェックし、前記メモリデバイスに対して前記第1のサイズのデータの書き込みが完了したことに応じて前記マイクロプロセッサに対して割り込み要求信号を出力する構成とした。

#### 【発明の効果】

#### 【0029】

本発明によれば、メモリデバイスとの間のデータ転送を短時間に完了することが可能となる。

#### 【発明を実施するための最良の形態】

#### 【0030】

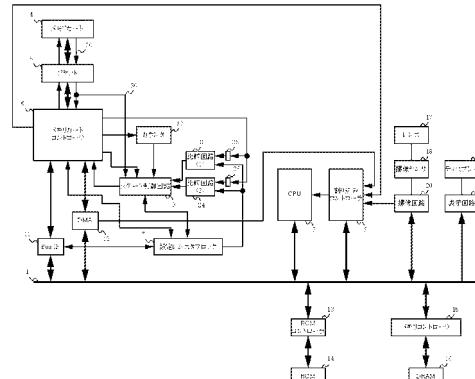

図1は、本発明の実施の形態のデジタルカメラの構成を示す図である。

#### 【0031】

1はシステムバスで、アドレスバス、データバス、制御信号から成る。2はCPUで、カメラのシーケンスをコントロールする。14はROMで、カメラが動作するためのプログラムが書き込まれている。CPU2はシステムバス1及びROMコントローラ13を通してROM14をリードすることが可能であり、これによりCPU2はROM14に記録された命令を実行することが可能である。

#### 【0032】

15はメモリコントローラ、16はDRAMで、メモリコントローラはシステムバスからのDRAMアクセス要求を受け、DRAM16へのアクセス信号を生成し、さらにDRAM16へのデータの書き込みやDRAM16からのデータの読み出しを実行する回路である。DRAM16はCPU2がプログラムを実行する際のワークデータを保持し、また

10

20

30

40

50

カメラの撮影動作によって生成される画像データやディスプレイに再生するための画像データを保持する。また、CPU2はDRAM16に記録された命令を実行することも可能である。

#### 【0033】

17は被写体像を結像させるためのレンズで18は撮像センサである。20は撮像回路で撮像センサ18より得たデジタル画像信号を処理することによりデジタル画像データを生成する回路である。撮像回路20は所定周期で行われる撮像処理に同期した信号を割り込みコントローラ3に対して出力する。

#### 【0034】

23は表示回路でDRAM16上のデジタル画像データより画像信号を生成し、ディスプレイ21に対して出力する。ディスプレイ21はカラー液晶表示パネルなどによって構成されるディスプレイで、画像を表示する。10

#### 【0035】

4はメモリカードで、主に撮影によって得られた画像ファイルを保存する。メモリカードは例えばP C M C I A I / Oカードやコンパクトフラッシュ（登録商標）等の記録再生可能なカードであり、例えばA T Aコマンドといったコマンドによりデータライト、データリードを制御し、さらにデータ転送は例えば1セクタ、512バイトといった所定の数を単位として行われる。

#### 【0036】

5はメモリカードのソケットであり、メモリカード4の着脱を可能とするための装置である。例えばコンパクトフラッシュ（登録商標）のデータバスは16ビットのデータ線およびアドレス線や制御信号線から構成されている。20

#### 【0037】

6はメモリカードコントローラで、メモリカードのデータ線、アドレス線、制御信号を制御する回路で、メモリカード4に対するコマンドの発行、メモリカードの各レジスタに対するライト及びリードアクセス、メモリカード4に対するデータライト、データリードが可能である。また、メモリカードコントローラ6はバスインターフェース11によりシステムバス1に接続され、CPU2によってメモリカードコントローラ6の制御及びメモリカードに対するライトアクセス、リードアクセスが可能である。

#### 【0038】

更に、メモリカードコントローラ6にはDMA(D i r e c t M e m o r y A c c e s s)回路12が接続されている。DMA12は予めCPU2によってセットされた転送開始アドレスと転送データ長を用いて所定のアドレスから所定の数のデータを転送する回路である。DMA12はバスマスターとしてシステムバス1に対して制御信号とアドレスを生成することが可能であり、さらにメモリカードコントローラ6に対してもライトアクセス要求、リードアクセス要求を発行することが可能である。30

#### 【0039】

これにより例えばDRAM16のように所定のアドレスにマッピングされたデバイスとメモリカードコントローラ6の間において、CPU2がデータ転送アクセスを実行することなく、メモリカードコントローラ6のデータアクセスに同期してデータを転送することが可能となる。40

#### 【0040】

メモリカードコントローラ6にはカウンタ10が接続されている。メモリカードコントローラ6はメモリカード4に対するデータリードまたはデータライト処理が発生したとき、カウンタ10に対してカウントアップ信号を出力する。カウンタ10はメモリカードコントローラ6が行ったデータリードまたはデータライトの回数をカウントし、1セクタ相当のアクセス回数がカウントされたとき、ステート制御回路9に対して信号を出力する。

#### 【0041】

また、メモリカードの種類によっては一度のステータスチェックにより複数セクタ相当の数のデータを転送することを許容するものもある。50

**【 0 0 4 2 】**

この場合、カウンタ10が、一度のステータスチェックにより転送を許可されている最大のデータ数をカウントした際に信号を発生するよう設定することも可能である。

**【 0 0 4 3 】**

メモリカードコントローラ6には比較回路8、及び比較回路24が接続されている。メモリカードコントローラ6はメモリカード4より読み取ったメモリカードのステータスレジスタの値を比較回路8と比較回路24に出力する。

**【 0 0 4 4 】**

設定レジスタブロック7はメモリカード4の制御動作に関する設定値を記憶するレジスタブロックであり、CPU2からシステムバス1及びバスインターフェース11を経由してライトアクセス、リードアクセスすることが可能である。10

**【 0 0 4 5 】**

設定レジスタブロック7はその中の一つのレジスタにカードステータスの期待値1を記憶し、これを比較回路8に出力し、また他の一つのレジスタにカードステータスの期待値2を記憶し、これを比較回路24に出力している。

**【 0 0 4 6 】**

比較回路8とメモリカードコントローラ6の間にはマスク回路25が、また比較回路24とメモリカードコントローラ6の間にはマスク回路26がある。マスク回路25及び26は、入力データ中の特定のビットのみを通過させる論理回路であり、マスク回路25に通過させるビットは選択可能であり、その設定値は設定レジスタブロック7が保持する。同様にマスク回路26に通過させるビットは選択可能であり、その設定値は設定レジスタブロック7が保持する。これらによりCPU2はマスク回路25及び26に通過させるビットをそれぞれ独立に設定することが可能である。20

**【 0 0 4 7 】**

比較回路8はメモリカード4より読み取ったメモリカード4のステータスレジスタの値と期待値1とを比較し、比較結果をステート制御回路9に出力する。同様に比較回路24はメモリカード4より読み取ったメモリカード4のステータスレジスタの値と期待値2と比較し、比較結果をステート制御回路9に出力する。

**【 0 0 4 8 】**

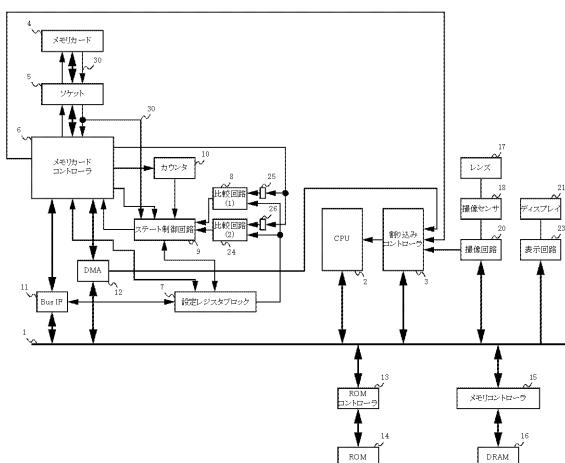

ステート制御回路9はメモリアクセスのシーケンスを制御するステートマシンであり、その動作の詳細については後で述べる。30

**【 0 0 4 9 】**

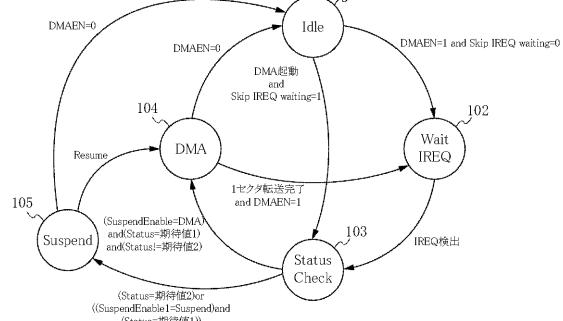

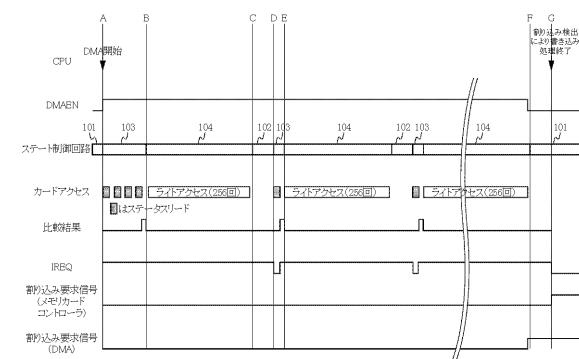

次に、図1、図2、図3、図4を用いてメモリカード4に対してデータライトを行う時の動作を説明する。図2はステート制御回路9の動作を示し、図3はCPU2の動作を示す図である。

**【 0 0 5 0 】**

図3の1000において、CPU2はデータライト処理を開始する。

**【 0 0 5 1 】**

CPU2はまずS1001にてメモリカードに対してこれから行うデータ転送に関する、論理ブロックアドレスの設定、更にS1002にて転送セクタ数、S1003にて転送するデータが記録される先頭セクタ番号の設定を行う。これらはCPU2による設定値のライト指示がシステムバス1とバスインターフェース11を経由してメモリカードコントローラ6に伝達され、メモリカードコントローラがメモリカード4を制御することによって行われる。40

**【 0 0 5 2 】**

次にCPU2はS1004において、メモリカードコントローラ6に対してDMA転送先アドレスを指定する。このDMA転送先アドレスとは、メモリカード4上でマッピングされたアドレスを指し、ここではデータレジスタを示すアドレスを指定する。このアドレス値は設定レジスタブロック7に記憶される。

**【 0 0 5 3 】**

10

20

30

40

50

S1005においてCPU2は、Skip IREQ Waitingレジスタに1を、転送終了割り込みイネーブルレジスタに1をセットする。Skip IREQ Waitingレジスタは設定レジスタブロック7に存在する一つのレジスタであり、この値が0であるか1であるかによってステート制御回路9の動作を決定する。転送終了割り込みイネーブルレジスタは、メモリカードコントローラ6が全てのデータをメモリカード4に転送し終わった時に割り込み要求をアサートする機能の動作を決定するための値を保持し、この値が1であるとき、メモリカードコントローラ6は全ての転送の終了を、DMAEがネゲートされたこと、1セクタ単位の転送が終了していること、メモリカードがIREQをアサートしたことにより判断したとき、割り込み要求信号をアサートする。

## 【0054】

10

S1006においてCPU2は、メモリカードコントローラ6に対して1セクタのデータ数すなわち1セクタの転送に必要なデータライトの回数を設定する。

## 【0055】

一般的なファイルシステムの元でメモリカードを使用する場合、1セクタは512バイトであり、メモリカードのデータバスが16bitである場合、データライトの回数は256回である。この値は設定レジスタブロック7に記憶される。

## 【0056】

S1007及びS1008においてCPU2は、メモリカード4のステータスレジスタのアドレスとこれの期待値を設定する。メモリカード4のステータスレジスタとはメモリカード4の状態を示すレジスタで、これをリードすることによりレディ状態であるか、データリクエスト状態であるか、エラーステータスであるか、等を知ることができる。

20

## 【0057】

データライトやデータリードを行う場合はこのレジスタの値が所定の値、例えばレディ状態かつデータリクエスト状態であり、かつエラー状態ではないこと、である必要があり、期待値としてこのような値を設定レジスタブロックの期待値1にセットし、メモリカード4から読み出したステータスレジスタの値と期待値を比較することによりこれらをチェックする。また、エラーの検出のため、エラービットを設定レジスタブロックの期待値2としてセットし、さらにエラービット以外はマスクされるようマスク回路26を設定する。

## 【0058】

30

更にCPU2は比較回路が比較一致を示した場合のステートマシンの振る舞いを設定することが可能であり、これを設定するレジスタとしてSuspendEnableレジスタが存在する。SuspendEnableレジスタの設定値としてはDMA続行とDMAサスペンドの二種類から選択が可能である。ここでは比較回路8が一致を示したときはDMA続行を選択し、比較回路24が一致を示したときはDMAサスペンドを選択し、これをSuspendEnableレジスタに設定する。

## 【0059】

S1009においてCPU2は、メモリカード4に対してライトセクタコマンドを発行する。これによりメモリカード4は後にライト可能な状態となるが、それについては後で説明する。

40

## 【0060】

S1010にてCPU2は、DMA12に対してDMAの転送対象となるデータが存在する、先頭アドレスを設定する。ここではメモリカード4に対して転送するデータはDRAM16に存在する。従って、ここでDMA12にセットされるDMA転送開始アドレスとは、DRAM16上に存在する転送対象データの先頭アドレスである。更にCPU2はDMA12に対してDMA転送対象となるデータのサイズを設定する。

## 【0061】

S1011にてCPU2はDMA12に対してDMAによるデータ転送の方向をDRAM16からメモリカード4の方向にセットする。

## 【0062】

50

ここで、CPU2は図3のS1012、図4のAにおいて、DMA12に対してDMA転送開始を指示する。これにより、DMA12はDMAEN信号を1にアサートする。

#### 【0063】

更にCPU2はS1013にて割り込みコントローラ3に対して、メモリカードコントローラ6が発生する転送終了割り込みをCPU2に対する割り込み要求として設定する。これによってCPU2はメモリカードコントローラがデータ転送終了を示すまでの間、メモリカード4とDRAM16間のデータ転送に関する処理を行う必要は無くなる。

#### 【0064】

更にマルチタスクOSによりシステムのタスクを制御することにより、割り込み発生までの間、CPU2は他のタスクを処理することが可能となる。

10

#### 【0065】

このとき、割り込み要因としてDMA12ではなくメモリカードコントローラ6を選択するのは、メモリカードコントローラ6はメモリカード4を制御するので全てのデータがメモリカード4に転送されたことを検出することが可能であるためである。

#### 【0066】

図2において、ステート制御回路9は、デジタルカメラが起動してからここまでの一連の操作では101のアイドルステートをとる。そしてCPU2がS1012にてDMA12に対してDMA転送開始を指示したことにより、DMA12はDMAEN信号をアサートし、これはメモリカードコントローラ6を経由してステート制御回路9に伝達される。ステート制御回路9はDMAEN信号がアサートされかつ事前にSkipREQ Waitingレジスタの値が1にセットされていることにより、状態を103のステータスチェックステートに遷移する。

20

#### 【0067】

本形態ではデータライトまたはリード時の最初のセクタに関して、SkipREQ Waitingレジスタによって、IREQがアサートされることを待つ機能を動作させるか否かを選択可能である。これは、コンパクトフラッシュ（登録商標）やPQMCA-I/OカードといったATA規格を用いるメモリカードが、データリードとデータライトにおいて異なるIREQの振る舞いをとるためである。

#### 【0068】

これらのメモリカードはデータリード時にはリードコマンド発行後最初のセクタに関してもIREQをアサートするが、一方データライト時ライトコマンド発行後、最初のセクタに関してはIREQをアサートしない。

30

#### 【0069】

ステート制御回路9のステートが103である場合、メモリカードコントローラ6はメモリカード4のステータスレジスタを繰り返しリードする。リードした値は比較回路8において事前にセットされた期待値と比較される。比較結果が不一致である場合、ステート制御回路は状態103をとり、メモリカードコントローラ6は比較結果が一致するまで繰り返しステータスレジスタをリードする。

#### 【0070】

この様に図4のAからBまでの間ににおいて、メモリカード4のステータスレジスタを繰り返しリードする。そしてメモリカード4がステータスの値を所望の値に変化させたことにより、Bにて比較回路8の比較結果が期待値1との一致を示した場合、ステート制御回路9は図4のBにて状態を図2のステート104のDMAに遷移させる。

40

#### 【0071】

ステート制御回路9の状態が104であるとき、メモリカードコントローラ6はDMA12がアサートするDMAリクエスト信号に同期してDMA12よりデータを受け取り、これをメモリカード4のデータレジスタに対してライトアクセスする。ここでメモリカードコントローラ6がデータレジスタに対してデータをライトするのは、事前にS1004にてデータ転送先がデータレジスタを示すアドレスに設定されているためである。

#### 【0072】

50

ステート制御回路9の状態が104である間、メモリカードコントローラ6は繰り返しデータライトを行う。これと同時にカウンタ10はデータライトの回数をカウントする。

【0073】

カウンタ10はデータライトの回数が1セクタ分となった場合、これを示す信号をステート制御回路9に対してアサートする。

【0074】

図4のCにおいてカウンタ10が1セクタのデータライトが完了したことを示し、さらに最後の転送が完了していたとする。ここで、ステート制御回路9はDMAENの値を評価する。DMAENは転送開始によって1にアサートされ、予めセットされたデータサイズ全ての転送が終了したときに0にネゲートされる信号である。

10

【0075】

従って、1セクタの転送完了後にDMAENがアサート状態である場合、まだ転送すべきデータが残っていることを示す。

【0076】

ステート制御回路9はこれにより図4のCにおいて状態を図2のステート102に遷移させる。ステート制御回路9の状態が102のWaitREQである場合、メモリカードコントローラ6はメモリカード4がIREQ信号をアサートすることを待つ。

【0077】

メモリカード4はデータ転送可能な状態となったとき、IREQ信号をアサートする。IREQ信号は0でアサート状態すなわち割り込み要求状態であり、1でネゲート状態である。図4のDにおいてメモリカード4がIREQ信号をアサートしたとする。これによりステート制御回路9は状態を103に遷移させる。メモリカードコントローラ6はメモリカード4のステータスレジスタをリードし、比較回路8はメモリカード4のステータスと期待値を再び比較する。そして図4のEにおいて再びステートを104に遷移させ、1セクタ分のデータライトをDMAに同期して行う。

20

【0078】

以上の処理を繰り返し行い、図4のFにて予定していた全てのデータがDRAM16からメモリカードコントローラ6に転送されたとする。ここでは1セクタ分の転送が完了していると同時にDMAENは0にネゲートされているので、ステート制御回路9は状態を101のアイドル状態に遷移させる。

30

【0079】

更にこの後、メモリカードコントローラ6は図4のGにおいて、DMAENがネゲートされたこと、1セクタ単位の転送が終了していること、メモリカード4がIREQをアサートしたことなどを判断すると、割り込み要求信号を割り込みコントローラ3に対して出力し、さらに割り込みコントローラ3はこれをCPU2に対してアサートする。

40

【0080】

これにより、CPU2はメモリカード4に対するデータライトが確実に完了したことを知ることが可能となり、メモリカードに対する次のコマンドを誤ってデータ転送完了前に発行するなどの事故を防止することが可能となる。また、通常デジタルカメラでは、メモリカードへのデータ書き込み動作中は、ユーザーによるメモリカードの抜き取りを防止するために警告を表示する。本形態ではデータの書き込みが完全に終了したときにCPUに割り込み要求を出力するため、このような警告表示の終了を確実に行うこと可能である。

【0081】

データ書き込み終了割り込みによりCPU2は他のタスクの実行を停止し、実行処理を図3のセクタライト処理のS1014に戻す。これによりCPU2はメモリカードに対するデータライトの処理をS1015にて終了する。

【0082】

以上の様に、メモリカード4に対するデータライトは完了する。

【0083】

50

このとき、メモリカード4に対するデータ転送を開始した直後であるS1013からデータ転送が完了するS1014間での間、CPU2はメモリカード4に関する処理は一切必要ない。そのため、CPU2はこの間別のタスクを実行することが可能である。

#### 【0084】

また、メモリカード4に対するデータ転送において、CPU2はステータスの確認を行う必要は無く、IREQ信号によって割り込み処理を起動する必要も無いのでステータスが期待値と一致したことは瞬時に判断され、DMA12はメモリカード4のステータスがレディとなった直後にデータ転送を開始することが可能となる。

#### 【0085】

ここで、データ転送中においてメモリカード4がステータス値としてエラー状態を示した場合について説明する。10

#### 【0086】

予め期待値2にはエラービットの値が設定され、マスク回路26はエラービット以外をマスクするよう設定されている。

#### 【0087】

図2の103においてメモリカード4のステータスレジスタがリードされ、この値のエラービットが真である場合、比較回路24はその結果をステート制御回路9に伝達する。ステート制御回路9は状態を図2の105に遷移させる。そして、DMAは起動され、かつデータ転送をリクエストした状態であるが、メモリカードコントローラ6はメモリカード4へのアクセスを行わず、DMA処理を一時停止させた状態をとる。20

#### 【0088】

もしエラーを回避することが可能なのであればCPU2はメモリカードコントローラ6にレジューム指令を行い、データ転送を再開することも可能である。また、エラーに対してこれを回避することが不可能である場合は、DMA処理を停止する。その結果DMAEN信号が0になり、ステート制御回路9は101の初期状態に遷移するため、データ転送は中止され、例えばカードを初期化するといったことが可能である。

#### 【0089】

もしカードに書き込むべきデータがDRAM16上に存在するのであれば、論理アドレスを変更した上で再びデータのライトを試みればよい。

#### 【0090】

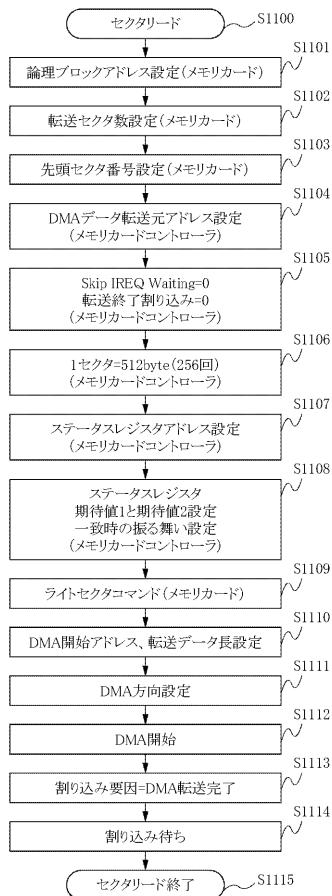

次に、図1、図2、図5、図6を用いてメモリカードに対するデータリード時の動作を説明する。30

#### 【0091】

図3の1100において、CPU2はデータリード処理を開始する。

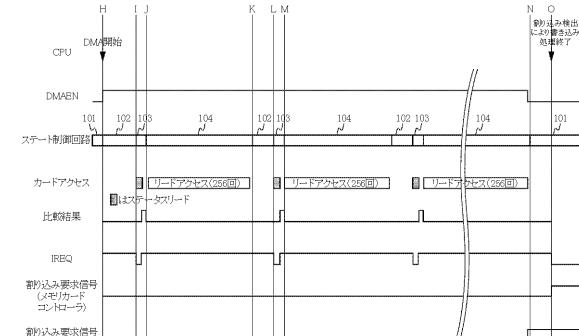

#### 【0092】

CPU2はまずS1101にてメモリカード4に対してこれから行うデータ転送に関する、論理ブロックアドレスの設定、さらにS1102にて転送セクタ数、S1103にて転送するデータが記録される先頭セクタ番号の設定を行う。

#### 【0093】

更にCPU2はS1104において、メモリカードコントローラ6に対してDMA転送元アドレスとしてメモリカード4のデータレジスタを示すアドレスを指定する。40

#### 【0094】

S1105においてCPU2は、Skip IREQ Waitingレジスタに0をセットする。これはメモリカード4がリードセクタ時においては最初のセクタに関してもIREQをアサートするためである。また、このときCPU2は、転送終了割り込みインプルレジスタに0をセットする。

#### 【0095】

S1106においてCPU2は、メモリカードコントローラ6に対して1セクタのデータ数として512バイトを設定する。また、S1107及びS1108においてCPU2は、メモリカード4のステータスレジスタのアドレスとこれの期待値を設定する。S1150

09においてCPU2は、メモリカード4に対してリードコマンドを発行する。

【0096】

S1110にてCPU2は、DMA12に対してデータを記録するアドレスとしてDRAM16上に存在するデータ保存領域の先頭アドレスを指定する。さらにCPU2はDMA12に対してDMA転送対象となるデータのサイズを設定する。

【0097】

S1111にてCPU2はDMA12に対してDMAによるデータ転送の方向をメモリカード4からDRAM16の方向にセットする。

【0098】

ここで、CPU2は図5のS1112、図6のHにおいて、DMA12に対してDMA転送開始を指示する。これにより、DMA12はDMAEN信号を1にアサートする。

10

【0099】

更にCPU2はS1113にて割り込みコントローラ3に対して、DMA12が発生する転送終了割り込みをCPU2に対する割り込み要求として設定する。これによってCPU2はDMA12がデータ転送終了を示すまでの間、メモリカード4とDRAM16間のデータ転送に関する処理を行う必要は無くなる。

【0100】

更にマルチタスクOSによりシステムのタスクを制御することにより、割り込み発生までの間、CPU2は他のタスクを処理することが可能となる。

【0101】

このとき、割り込み要因としてDMAを選択するのは、メモリに対してトランザクションを発生するDMA12は全てのデータがDRAM16に転送されたことを検出することが可能であるためである。

【0102】

図2において、ステート制御回路9は、デジタルカメラが起動してからここまで間は101のアイドルステートをとる。そしてCPU2がS1112にてDMA12に対してDMA転送開始を指示したことにより、DMA12はDMAEN信号をアサートし、これはメモリカードコントローラ6を経由してステート制御回路9に伝達される。

20

【0103】

ステート制御回路9はDMAEN信号がアサートされかつ事前にSkipIREQWaitingレジスタの値が0にセットされていることにより、状態を102のWaitIREQ状態に遷移させる。これによりメモリカードコントローラはカードがIREQ信号をアサートすることを待つ。IREQ信号がアサートされた場合、図6のIにおいて状態を103のステータスチェックステートに遷移する。

30

【0104】

ステート制御回路9のステートが103である場合、メモリカード4のステータスレジスタを繰り返しリードする。ここで、メモリカード4がステータスの値を所望の値に変化させたことにより、Jにて比較回路の比較結果が期待値との一致を示し、ステート制御回路9は図6のJにて状態を図2のステート104のDMAに遷移させる。

【0105】

ステート制御回路9の状態が104であるとき、メモリカードコントローラ6はDMA12がアサートするDMAリクエスト信号に同期してメモリカードのデータレジスタよりデータを受け取り、これをDRAM16に対して転送する。ステート制御回路9の状態が104である間、メモリカードコントローラ6は繰り返しデータリードを行う。これと同時にカウンタ10はデータリードの回数をカウントする。

40

【0106】

カウンタ10はカウント値が1セクタ分のデータライトの回数と一致した場合、これを示す信号をステート制御回路9に対してアサートする。

【0107】

図6のKにおいてカウンタ10が1セクタのデータリードが完了したことを示し、さら

50

に最後の転送が完了していたとする。ここで、ステート制御回路9はDMAENの値を評価する。1セクタの転送完了後にDMAENがアサート状態である場合、まだ転送すべきデータが残っていることを示す。

#### 【0108】

ステート制御回路9はこれにより図6のKにおいて状態を図2のステート102に遷移させる。ステート制御回路9の状態が102のWait IREQである場合、メモリカードコントローラ6はメモリカード4がIREQ信号をアサートすることを待つ。

#### 【0109】

メモリカード4はデータ転送可能な状態となったとき、IREQ信号をアサートする。

図4のLにおいてメモリカード4がIREQ信号をアサートした場合、ステート制御回路9は状態を103に遷移させる。メモリカードコントローラ6はメモリカード4のステータスレジスタをリードし、比較回路8はメモリカード4のステータスと期待値を再び比較する。そして図6のMにおいて再びステートを104に遷移させ、1セクタ分のデータリードをDMAに同期して行う。

#### 【0110】

これらの動作を繰り返し行い、図6のNにて予定していた全てのデータがメモリカードコントローラ6からDRAM16に転送されたとする。ここでは1セクタ分の転送が完了していると同時にDMAENは0にネガートされている。これによりステート制御回路は状態を101のアイドル状態に遷移させる。

#### 【0111】

ここではメモリカードコントローラ6は、転送終了割り込みをアサートしない。一方DMA12は全データがDRAM16に転送されたとき、転送終了割り込みをアサートする。CPU2は全データの転送終了をDMA12の転送終了割り込みがアサートされたことによって検出する。

#### 【0112】

これによりCPU2は図3のS1114において割り込みを検出し、メモリカード4からのデータリードの処理をS1115にて終了する。

#### 【0113】

以上によってメモリカード4からのデータリードは完了する。

#### 【0114】

このとき、メモリカード4からのデータ読み出しを開始した直後であるS1113からデータ転送が完了するS1114間での間、CPU2はメモリカード4に関する処理は一切行うことなしに複数セクタのデータリードを完了することが可能である。そのため、CPU2はこの間別のタスクを実行することが可能である。

#### 【0115】

また、メモリカード4からのデータ転送において、CPU2はステータスの確認を行う必要は無く、IREQ信号によって割り込み処理を起動する必要も無いのでステータスが期待値と一致したことは瞬時に判断され、DMAは直後にデータ転送を開始することが可能となる。

#### 【0116】

以上のように、本形態では、IREQ信号の検出、ステータスレジスタ値のチェック、DMAの起動の間に、CPUが行う割り込み処理が介在しないため、これらの処理を瞬時に完了することが可能となり、メモリカードと装置の間のデータ転送を短時間に完了することが可能となり、これにより撮影間隔時間が短く使い勝手のよいデジタルカメラを実現することが可能となる。

#### 【0117】

更に、メモリカードとの間でデータ転送している間、CPUは他のタスクを実行することが可能であり、かつこのタスクはデータ転送のセクタ単位によって中断されることも無い。これによりCPUの処理能力が向上し、例えばユーザーからの操作に対してレスポンスよく動作する使い勝手のよいデジタルカメラを実現することが可能となる。

10

20

30

40

50

## 【0118】

なお、本形態では、所定の期間、メモリカードとDRAMの間のデータ転送を一時的に中止し、その期間の終了によりデータ転送を再開することも可能である。

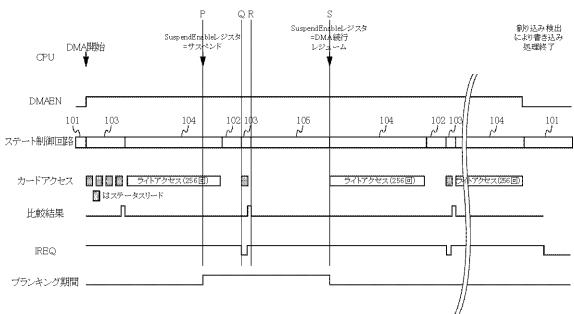

## 【0119】

本形態では、比較回路が比較一致を示した場合のステートマシンの振る舞いを設定するSuspendEnableレジスタが存在し、振る舞いはDMA続行とDMAサスPENDの二種類から選択が可能である。

## 【0120】

図7はデータ転送実行中の動作を示す図である。

## 【0121】

データ転送実行中であるPにおいて、CPU2は比較回路8の比較結果に関するSuspendEnableレジスタの値をDMA続行からサスPENDに変更する。ステート制御回路9はQにおいてステートを103に遷移しステータスレジスタをリードする。さらに比較回路8はこれらのデータの一致を示す。

## 【0122】

Rにおいてステート制御回路9はこのような設定が行われたことにより状態を105のサスPENDステートに遷移する。これによってメモリカード4とDRAM16間のDMA転送は一時停止状態となる。

## 【0123】

次にCPU2はSにおいてSuspendEnableレジスタの値をDMA続行に戻し、さらにメモリカードコントローラ6に対してレジュームを指令する。これによってステート制御回路9はデータ転送を再開する。

## 【0124】

デジタルカメラにおいては、撮像動作の動作に同期して、CPUのプログラム実行を優先させたい場面がある。

## 【0125】

例えば撮像時、撮像画像の露出やホワイトバランスを調整する必要がある。撮像処理は水平同期信号や垂直同期信号に同期して行われ、一画面と一画面の間の時間をVプランキング期間と呼んでいる。露出やホワイトバランスの処理は、撮像素子より得られた一画面分の画像データを用いて演算を行い、この露出やホワイトバランス制御のための制御値を次の画面の撮像が開始されるより前に撮像回路に対して設定する必要がある。したがって演算からパラメータセットまでの処理をVプランキング期間中に完了することが必要となる。

## 【0126】

そのためVプランキングの期間中は露出やホワイトバランス制御のためにシステムバスやROM、DRAMを優先的に使用することが好ましく、メモリカードに対するデータ転送のために使用することは好ましくない。

## 【0127】

そのため、Vプランキング期間が開始されるより前にSuspendEnableレジスタをDMAサスPENDに変更し、Vプランキング期間終了とともにSuspendEnableレジスタの値をDMA続行に戻し、さらにメモリカードコントローラ6に対してレジュームを指令すればよい。

## 【0128】

撮像回路20はVプランキング期間の開始よりちょうどメモリカードアクセス1セクタ分の時間前に、割り込み要求を、またVプランキング終了時も割り込み要求を割り込みコントローラ3に出力する。CPU2はVプランキング期間開始前であることを割り込みによって検出した場合、SuspendEnableレジスタをDMAサスPENDに変更する。また、CPU2はVプランキング期間終了を割り込みによって検出した場合、SuspendEnableレジスタをDMA続行に戻し、さらにメモリカードコントローラ6に対してレジュームを指令する。

## 【0129】

これにより、メモリカード4に対するデータ転送はVプランキング期間には行われず、Vプランキング期間、CPUは撮像に関する処理を最大限に処理することが可能となる。しかもVプランキング以外の時間はメモリカード4に対するデータ転送を短時間で行うことが可能である。

## 【0130】

この様に、本形態では、撮像時において撮像に必要な処理をメモリカードに対するデータ転送より優先して行うことが可能であり、撮像処理を確実に行うことにより高画質なデジタルカメラを実現することも可能である。

## 【図面の簡単な説明】

10

## 【0131】

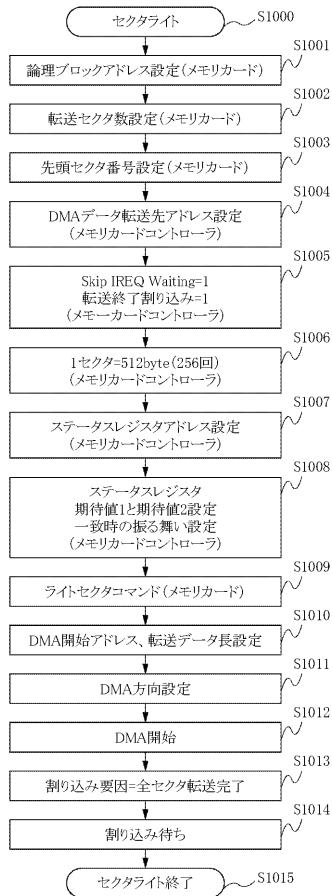

【図1】実施形態の装置の構成を示す図である

【図2】ステート制御回路の状態遷移を示す図である

【図3】データライト時の処理の流れを示す図である

【図4】データライト時の動作を示す図である

【図5】データリード時の処理の流れを示す図である

【図6】データリード時の動作を示す図である

【図7】データ転送一時停止の動作を示す図である

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き(51)Int.Cl.<sup>7</sup>

F I

H 04N 5/225

H 04N 5/907

テーマコード(参考)

F

B