(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2019년01월02일

(11) 등록번호 10-1933849

(24) 등록일자 2018년12월24일

- (51) 국제특허분류(Int. Cl.)

*G06F 1/32* (2006.01) *H02M 3/00* (2006.01)

- (21) 출원번호 10-2012-0054606

(22) 출원일자 2012년05월23일

심사청구일자 2017년05월10일

(65) 공개번호 10-2012-0134021

(43) 공개일자 2012년12월11일

(30) 우선권주장

JP-P-2011-121231 2011년05월31일 일본(JP)

(56) 선행기술조사문현

JP2006351141 A\*

(뒷면에 계속)

전체 청구항 수 : 총 9 항

(54) 발명의 명칭 DCDC 컨버터, 전원 회로 및 반도체 장치

심사관 : 순경완

- (73) 특허권자

가부시키가이샤 한도오따이 에네루기 켄큐쇼

일본국 가나가와Ken 아쓰기시 하세 398

(72) 발명자

오마루 다쿠로

일본 243-0036 가나가와Ken 아쓰기시 하세 398 가

부시키가이샤 한도오따이 에네루기 켄큐쇼 내

(74) 대리인

장훈

**(57) 요 약**

DCDC 컨버터는 제어 회로와, 스위칭 소자와, 스위칭 소자에 의하여 입력 전압의 공급이 제어되고, 스위칭 소자의 드라이버 비율에 걸맞은 크기의 출력 전압을 생성하는 정전압 생성부를 갖는다. 제어 회로는, 입력 전압 및 출력 전압을 아날로그 값으로부터 디지털 값으로 변환하는 AD 컨버터와, 출력 전압의 디지털 값을 사용하여 드라이버 비율을 정하는 신호 처리 회로와, 드라이버 비율에 따라 스위칭 소자의 스위칭을 제어하는 신호를 생성하는 필스 변조 회로와, 입력 전압 및 출력 전압의 디지털 값에 따라 신호 처리 회로로의 전원 전압의 공급 유무를 선택하는 전원 제어 회로를 갖는다. 상기 신호 처리 회로는 드라이버 비율을 기억하는 기억 장치를 갖고, 상기 기억 장치는, 기억 소자와, 상기 기억 소자의 데이터를 기억하는 용량 소자와, 상기 용량 소자에 있어서의 전하의 공급, 유지, 방출을 제어하는 트랜지스터를 갖고, 트랜지스터는 산화물 반도체를 채널 형성 영역에 포함한다.

**대 표 도** - 도1

(56) 선행기술조사문현

JP2010017022 A\*

JP2010051066 A\*

JP2007318655 A

JP2011103453 A

KR1020100115087 A

KR1020030068409 A

JP2011097504 A

JP2011072156 A

\*는 심사관에 의하여 인용된 문현

---

## 명세서

### 청구범위

#### 청구항 1

스위칭 소자;

듀티 비율(duty ratio)에 걸맞은 크기의 출력 전압을 생성하기 위한 정전압 생성부로서, 입력 전압의 공급이 상기 스위칭 소자에 의하여 제어되는 상기 정전압 생성부; 및

상기 스위칭 소자의 스위칭의 듀티 비율을 제어하기 위한 제어 회로를 포함하는, DC-DC 컨버터에 있어서,

상기 제어 회로는,

상기 입력 전압을 변환하는 제 1 AD 컨버터;

상기 출력 전압을 변환하는 제 2 AD 컨버터;

상기 출력 전압의 디지털 값에 따라 상기 듀티 비율을 정하는 신호 처리 회로;

상기 듀티 비율에 따라 상기 스위칭 소자의 스위칭을 제어하는 신호를 생성하기 위한 펄스 변조 회로; 및

상기 신호 처리 회로에 전원 전압을 공급하는지 여부를 판단하기 위한 전원 제어 회로를 포함하고,

상기 신호 처리 회로는 상기 듀티 비율을 기억하기 위한 기억 장치를 포함하고,

상기 기억 장치는,

기억 소자;

트랜지스터; 및

상기 트랜지스터를 통하여 상기 기억 소자에 전기적으로 접속되어 있는 용량 소자를 포함하는, DC-DC 컨버터.

#### 청구항 2

스위칭 소자;

상기 스위칭 소자를 통하여 입력 전압이 공급되고 출력 전압을 생성하는 정전압 생성부; 및

제어 회로를 포함하는, DC-DC 컨버터에 있어서,

상기 제어 회로는,

상기 입력 전압을 변환하는 제 1 AD 컨버터;

상기 출력 전압을 변환하는 제 2 AD 컨버터;

상기 출력 전압의 디지털 값에 따라 상기 스위칭 소자의 스위칭의 듀티 비율을 정하는 신호 처리 회로;

상기 스위칭 소자의 상기 스위칭을 제어하기 위한 신호를 생성하는 펄스 변조 회로; 및

상기 입력 전압의 디지털 값과 상기 출력 전압의 상기 디지털 값에 따라 상기 신호 처리 회로에 공급되는 전원 전압을 제어하는 전원 제어 회로를 포함하고,

상기 신호 처리 회로는 기억 장치를 포함하고,

상기 기억 장치는,

상기 듀티 비율의 데이터를 기억하는 기억 소자;

트랜지스터; 및

상기 트랜지스터를 통하여 상기 기억 소자에 전기적으로 접속되고, 상기 듀티 비율의 상기 데이터를 기억하는 용량 소자를 포함하는, DC-DC 컨버터.

### 청구항 3

스위칭 소자;

상기 스위칭 소자의 스위칭의 듀티 비율을 제어하기 위한 제어 회로; 및

상기 듀티 비율에 걸맞은 크기의 출력 전압을 생성하기 위한 정전압 생성부로서, 입력 전압의 공급이 상기 스위칭 소자에 의하여 제어되는 상기 정전압 생성부를 포함하는, DC-DC 컨버터에 있어서,

상기 제어 회로는,

상기 입력 전압의 아날로그 값을 사용하여 상기 입력 전압의 디지털 값을 얻는 제 1 AD 컨버터;

상기 출력 전압의 아날로그 값을 사용하여 상기 출력 전압의 디지털 값을 얻는 제 2 AD 컨버터;

상기 출력 전압의 상기 디지털 값을 사용하여 상기 듀티 비율을 정하기 위한 신호 처리 회로;

상기 듀티 비율에 따라 상기 스위칭 소자의 스위칭을 제어하는 신호를 생성하기 위한 펄스 변조 회로;

및

상기 입력 전압의 상기 디지털 값과 상기 출력 전압의 상기 디지털 값에 따라 상기 신호 처리 회로에 전원 전압을 공급하는지 여부를 판단하기 위한 전원 제어 회로를 포함하고,

상기 신호 처리 회로는 상기 듀티 비율을 기억하기 위한 기억 장치를 포함하고,

상기 기억 장치는,

상기 전원 전압의 공급에 의하여 데이터가 기억된 기억 소자;

상기 기억 소자에 유지된 상기 데이터에 의하여 전하를 유지하기 위한 용량 소자; 및

상기 용량 소자에 있어서의 상기 전하의 공급, 유지, 및 방출을 제어하기 위한 트랜지스터를 포함하고,

상기 기억 소자는,

제 1 논리 소자; 및

제 2 논리 소자를 포함하고,

상기 제 1 논리 소자의 출력 단자는 상기 제 2 논리 소자의 입력 단자와 전기적으로 접속되어 있는, DC-DC 컨버터.

### 청구항 4

제 3 항에 있어서,

상기 제 1 논리 소자 및 상기 제 2 논리 소자는 인버터 또는 클록드(clocked) 인버터인, DC-DC 컨버터.

### 청구항 5

제 1 항 내지 제 3 항 중의 어느 한 항에 따른 상기 DC-DC 컨버터 및 정류 회로를 포함하는, 전원 회로.

### 청구항 6

제 1 항 내지 제 3 항 중의 어느 한 항에 따른 상기 DC-DC 컨버터를 포함하는, 반도체 장치.

### 청구항 7

제 1 항 내지 제 3 항 중의 어느 한 항에 있어서, 상기 트랜지스터는 산화물 반도체를 포함하는, DC-DC 컨버터.

### 청구항 8

제 7 항에 있어서,

상기 산화물 반도체의 밴드 갭은 2eV 이상인, DC-DC 컨버터.

### 청구항 9

제 3 항에 있어서,

상기 제 1 논리 소자는 상기 제 1 논리 소자에 입력되는 신호의 논리값을 반전시키고,

상기 제 2 논리 소자는 상기 제 2 논리 소자에 입력되는 신호의 논리값을 반전시키는, DC-DC 컨버터.

### 청구항 10

삭제

### 청구항 11

삭제

### 청구항 12

삭제

### 청구항 13

삭제

### 청구항 14

삭제

## 발명의 설명

### 기술 분야

[0001] 본 발명은 디지털 제어형의 DCDC 컨버터와, 상기 DCDC 컨버터를 사용한 전원 회로 및 반도체 장치에 관한 것이다.

### 배경 기술

[0002] DCDC 컨버터는 입력 전압값에 관계없이, 일정한 출력 전압을 얻을 수 있는 정전압 회로이며, 정류 회로 등과 함께 전원 회로에 사용되고 있다. 특히, 스위칭 방식의 DCDC 컨버터를 사용한 전원 회로는 스위칭 전원 또는 스위칭 레귤레이터로 불리고 있다.

[0003] 스위칭 방식의 DCDC 컨버터는 스위칭 소자에 의하여 입력 전압으로부터 펄스상의 파형을 갖는 전압을 형성하고, 이 전압을 코일이나 용량 소자 등에 있어서 평활화 또는 유지함으로써, 원하는 값의 출력 전압을 얻는 것이다. 그리고, 상기 스위칭 소자가 온 상태인 기간의 비율, 소위 드티 비율은, DCDC 컨버터 내의 제어 회로에 있어서 제어되어 있다. 상기 드티 비율의 값을 제어 회로에 있어서 제어함으로써, 출력 전압의 값을 제어할 수 있다.

[0004] 또한, DCDC 컨버터로서 주류를 이루고 있던 것은 제어 회로를 아날로그 회로로 구성하는 아날로그 제어형이었다. 그러나, 근년에는 DSP(Digital Signal Processor) 등의 신호 처리 회로가 제어 회로에 사용된 디지털 제어형의 DCDC 컨버터가 실현화되어 있다. 디지털 제어형의 DCDC 컨버터는, 스위칭 소자를 고속으로 스위칭시킬 수 있고, 제어 회로에 있어서의 신호 처리의 정밀도를 높이고, 또 제어 회로의 구성을 간소화할 수 있다.

[0005] 하기 특허 문헌 1에는 디지털 제어 방식을 채용한 전원 제어에 대하여 기재되어 있다.

### 선행기술문헌

### 특허문헌

[0006] (특허문헌 0001) 일본국 특개2009-9386호 공보

## 발명의 내용

### 해결하려는 과제

[0007] 그런데, 전자 기기의 성능을 평가하는 데에 저소비 전력인 것은 중요한 포인트의 하나이다. 특히, 휴대 전화 등의 휴대형 전자 기기는, 소비 전력의 크기가 연속 사용 시간의 단축화라는 단점으로 이어지기 때문에, 저소비 전력화를 도모하는 것이 강하게 요구된다. 그리고, DCDC 컨버터는 2차 전지로부터 출력되는 전압을 제어하는 목적으로 휴대용의 전자 기기에 많이 사용되어 있는 경우도 있어, 소비 전력의 저감이 요구되고 있다.

[0008] 상기 특허 문헌 1에서는, 정보 처리 장치가 절전 모드로 이행될 때, DSP의 클록을 정지함으로써 DSP를 정지하고, 저소비 전력화를 도모하는 기술에 대하여 기재되어 있다. 그러나, DSP 등의 접적 회로에서는, 클록 신호 등의 구동 신호의 공급을 정지하는 상태라도, 접적 회로에 전원 전압이 공급되기 때문에, 트랜지스터의 오프 전류 등에 의하여 전력이 소비된다. 따라서, DCDC 컨버터의 저소비 전력화를 더욱 도모하기 위해서는 DSP로의 구동 신호의 공급을 정지할 뿐만이 아니라 DSP로의 전원 전압의 공급도 정지할 필요가 있다.

[0009] 그러나, DSP로의 전원 전압의 공급을 정지하는 경우, DSP 내의 레지스터에 유지되어 있는 듀티 비율의 데이터가 소실된다. 그래서, DSP로의 전원 전압의 공급을 재개하였을 때, DCDC 컨버터로부터 출력되는 전압이 일시적으로 불안정한 상태로 되기 쉽다. 상기 상태로 되는 것을 방지하기 위하여, DSP로의 전원 전압의 공급을 정지하기 전에 플래시 메모리 등의 비휘발성을 갖는 외부 기억 장치에 듀티 비율의 데이터를 퇴피시켜 두는 것은 가능하다. 그러나, 상기 외부 기억 장치로부터 DSP 내의 레지스터에 데이터를 되돌리는 데는 시간을 필요로 하기 때문에, 상기 방법은 소비 전력의 저감을 목적으로 한 단시간의 전원 전압의 공급 정지에는 적합하지 않다.

[0010] 상술한 바와 같은 기술적 배경에 의거하여 본 발명에서는 소비 전력을 억제할 수 있는 DCDC 컨버터와, 상기 DCDC 컨버터를 사용한 전원 회로 또는 반도체 장치의 제공을 과제의 하나로 한다. 특히, 단시간의 전원 전압의 공급 정지에 의하여 소비 전력을 억제할 수 있는 DCDC 컨버터와, 상기 DCDC 컨버터를 사용한 전원 회로 또는 반도체 장치의 제공을 과제의 하나로 한다.

### 과제의 해결 수단

[0011] 상기 과제를 해결하기 위하여, 본 발명의 일 형태에서는 제어 회로에 있어서 듀티 비율을 정하는 DSP 등의 신호 처리 회로 내에 하기 구성을 갖는 기억 장치를 제공한다. 상기 기억 장치는, 기억 소자와, 상기 기억 소자의 데이터를 기억하는 용량 소자와, 상기 용량 소자에 있어서의 전하의 공급, 유지, 방출을 제어하는 트랜지스터를 갖는다.

[0012] 상기 트랜지스터는 실리콘보다 밴드 갭이 넓고, 전성 캐리어 밀도가 실리콘보다 낮은 산화물 반도체 등의 반도체를, 채널 형성 영역에 포함한다. 상기 특성을 갖는 반도체를 채널 형성 영역에 포함한 트랜지스터는, 실리콘이나 게르마늄 등의 일반적인 반도체로 형성된 트랜지스터와 비교하여 오프 전류가 매우 작다.

[0013] 구체적으로, 상기 기억 소자는, 인버터 또는 클록드 인버터 등의 입력된 신호의 논리값을 반전시켜 출력하는 논리 소자를 사용하여 구성할 수 있다.

[0014] 그리고, 본 발명의 일 형태에서는, DCDC 컨버터에 인가되는 입력 전압 및 출력 전압의 크기에 따라, 신호 처리 회로로의 전원 전압의 공급을 정지하는지 여부를 선택하는 전원 제어 회로를 제어 회로 내에 제공한다. 구체적으로, 전원 제어 회로는, 출력 전압이 원하는 값으로 유지되고, 또 입력 전압의 변동이 작은 경우에 있어서, 신호 처리 회로로의 전원 전압의 공급을 정지한다. 또한, 전원 제어 회로는, 입력 전압의 변동이 큰 경우에 있어서, 또는 출력 전압이 원하는 값으로 유지되지 않은 경우에 있어서, 신호 처리 회로에 전원 전압을 공급한다.

[0015] 신호 처리 회로에 있어서 정해진 듀티 비율의 데이터는, 기억 장치가 갖는 기억 소자에서 유지된다. 그리고, 기억 소자에 유지된 듀티 비율의 데이터는, 신호 처리 회로로의 전원 전압의 공급이 정지되기 전에 기억 장치가 갖는 용량 소자에 퇴피시킨다. 구체적으로, 데이터의 퇴피는 용량 소자에 있어서의 전하의 유지에 의하여 행하고, 상기 전하의 유지는 상기 오프 전류가 낮은 트랜지스터를 오프 상태로 함으로써 행한다. 그리고, 신호 처리 회로로의 전원 전압의 공급이 재개된 후에 퇴피시켜 둔 데이터를 기억 소자에 되돌린다. 상기 구성에 의하여 전원 전압의 공급이 정지되어도 기억 장치 내의 데이터의 소실을 방지할 수 있다. 따라서, 외부 기억 회로

에 데이터를 퇴피시킬 필요가 없기 때문에, 신호 처리 회로 또는 신호 처리 회로를 포함하는 제어 회로에 있어서, 짧은 시간이라도 전원 전압의 공급을 정지할 수 있다. 결과적으로, DCDC 컨버터의 소비 전력을 저감시킬 수 있다. 또한, 전원 전압의 공급이 정지되어도 드티 비율의 데이터는 기억 장치 내에 있어서 유지되기 때문에, 전원 전압의 공급이 재개된 후에도 DCDC 컨버터의 출력 전압이 불안정하게 되는 것을 방지할 수 있다.

[0016] 구체적으로 본 발명의 일 형태에 따른 DCDC 컨버터는, 스위칭 소자와, 스위칭 소자의 드티 비율을 제어하는 제어 회로와, 스위칭 소자에 의하여 입력 전압의 공급이 제어되고, 드티 비율에 걸맞은 크기의 출력 전압을 생성하는 정전압 생성부를 갖는다. 상기 제어 회로는, 출력 전압을 아날로그 값으로부터 디지털 값으로 변환하는 AD 컨버터와, 입력 전압을 아날로그 값으로부터 디지털 값으로 변환하는 AD 컨버터와, 상기 출력 전압의 디지털 값을 사용하여 드티 비율을 정하는 신호 처리 회로와, 상기 드티 비율에 따라 스위칭 소자의 스위칭을 제어하는 신호를 생성하는 펄스 변조 회로와, 입력 전압의 디지털 값과 출력 전압의 디지털 값에 따라 신호 처리 회로로의 전원 전압의 공급 유무를 선택하는 전원 제어 회로를 갖는다. 신호 처리 회로는, 상기 드티 비율을 기억하는 기억 장치를 갖는다. 그리고, 상기 기억 장치는, 결정성을 갖는 실리콘, 또는 게르마늄 등의 반도체를 채널 형성 영역에 갖는 트랜지스터를 사용한 기억 소자와, 상기 기억 소자의 데이터를 기억하는 용량 소자와, 상기 용량 소자에 있어서의 전하의 공급, 유지, 방출을 제어하는 트랜지스터를 갖고, 상기 트랜지스터는 실리콘보다 밴드 갭이 넓고 진성 캐리어 밀도가 실리콘보다 낮은 반도체를 채널 형성 영역에 포함한다.

### 발명의 효과

[0017] 본 발명의 일 형태에서는, 상기 구성에 의하여 소비 전력을 억제할 수 있는 DCDC 컨버터와, 상기 DCDC 컨버터를 사용한 전원 회로, 또는 반도체 장치를 제공할 수 있다.

### 도면의 간단한 설명

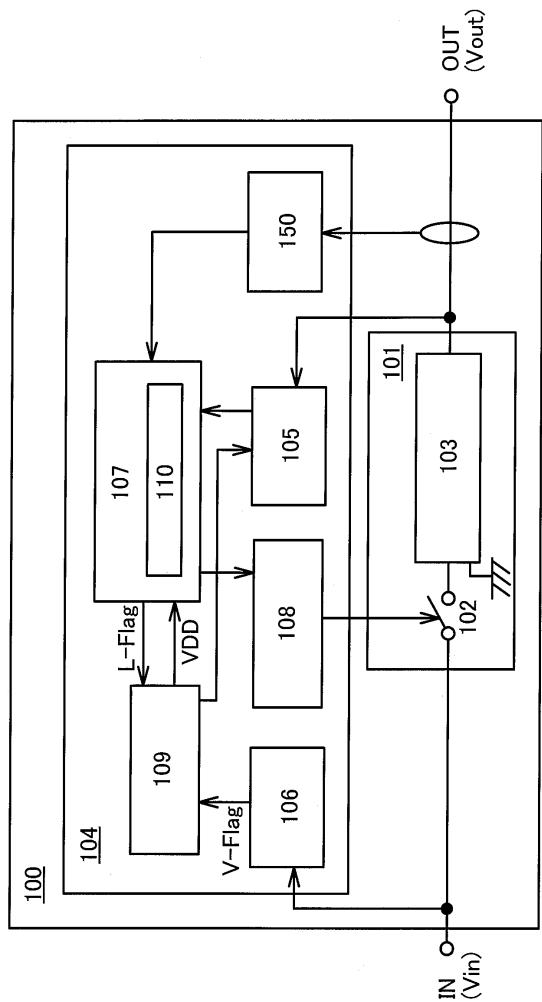

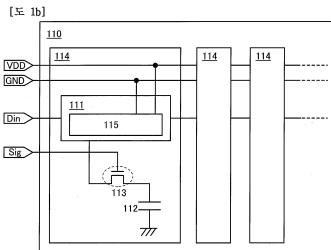

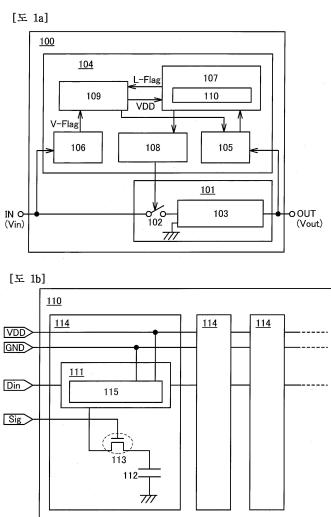

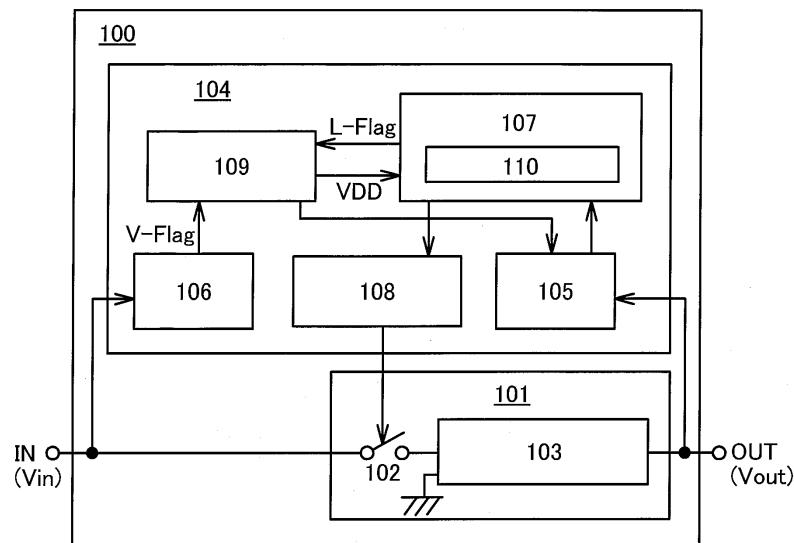

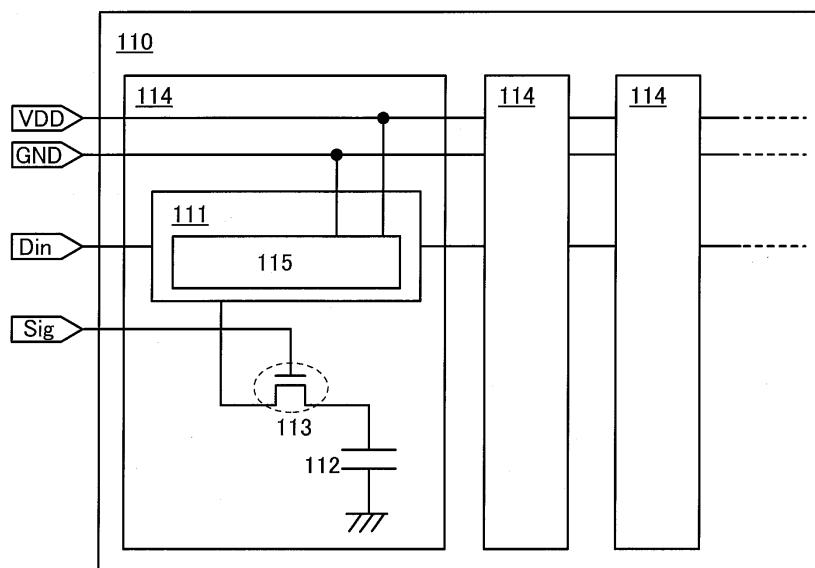

[0018] 도 1a 및 도 1b는 DCDC 컨버터의 구성과 기억 장치의 구성을 도시한 도면.

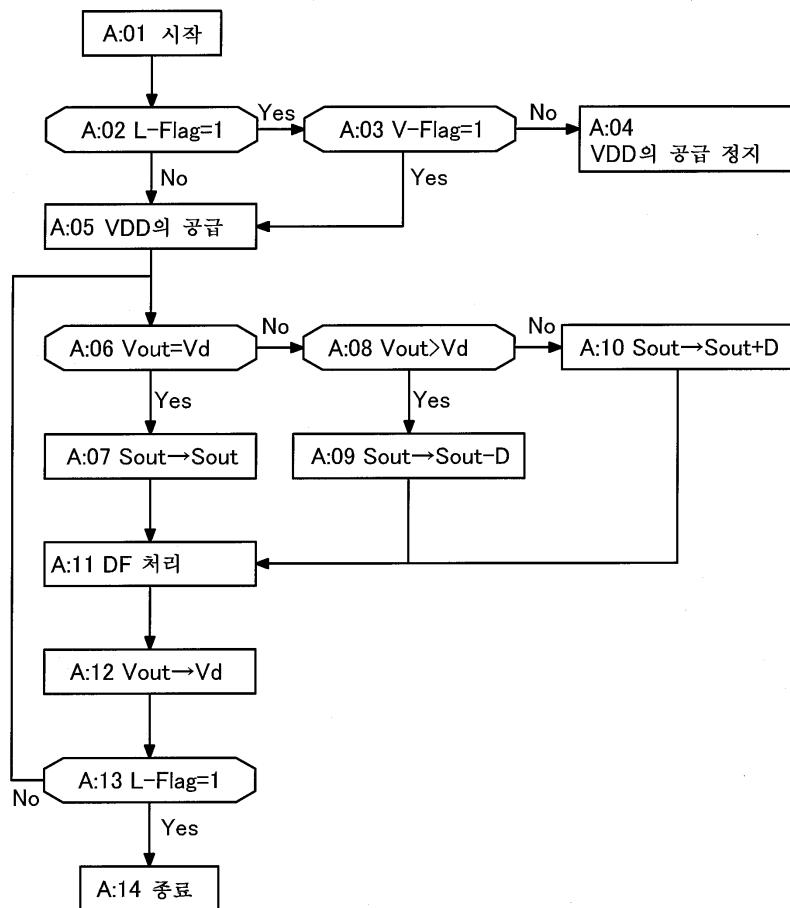

도 2는 DCDC 컨버터의 동작을 도시한 도면.

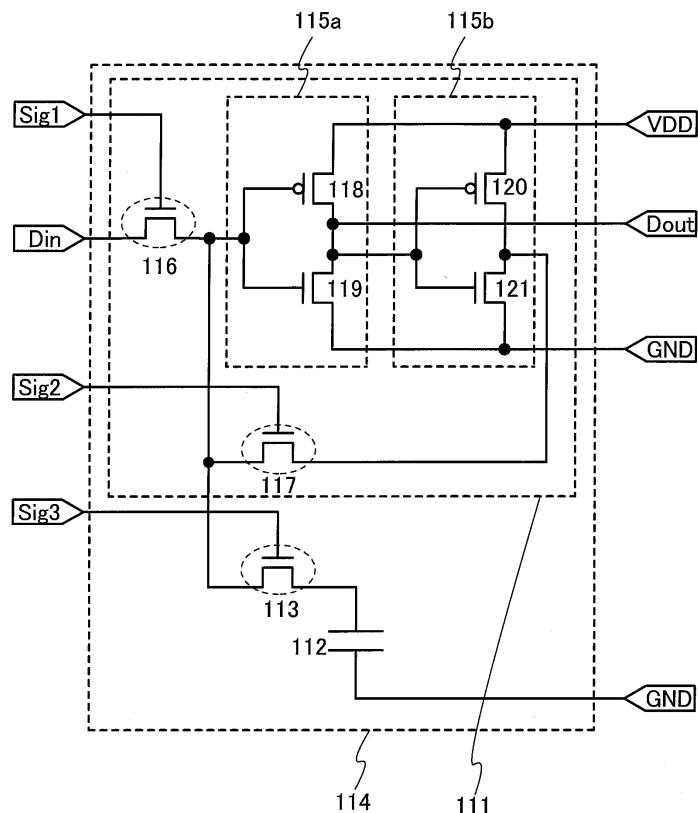

도 3은 기억 회로의 회로도.

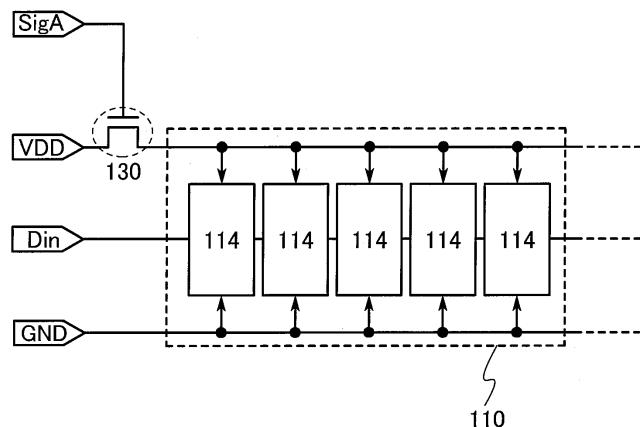

도 4a 및 도 4b는 기억 회로의 구성을 도시한 도면.

도 5는 신호 처리 회로의 블록도.

도 6은 기억 회로의 단면도.

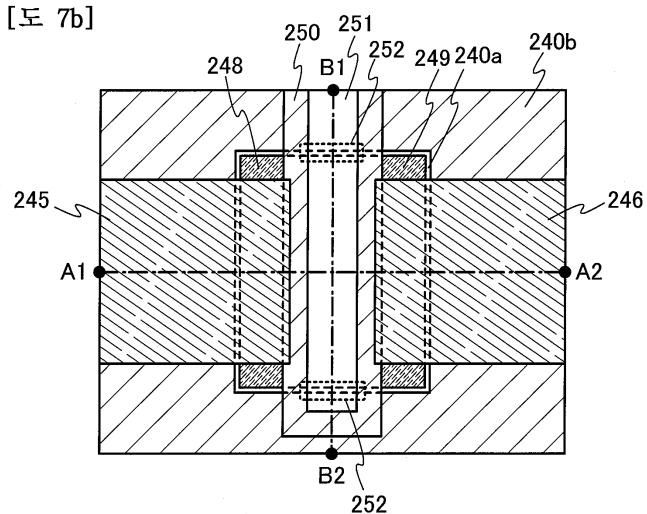

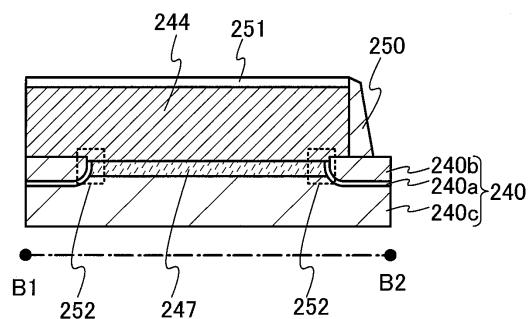

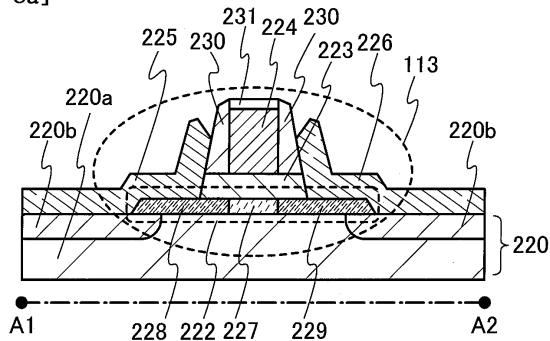

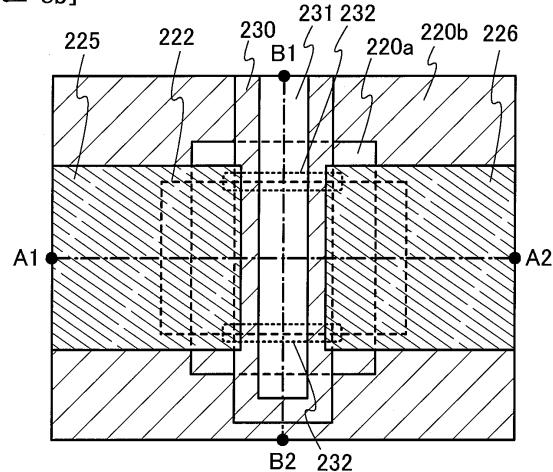

도 7a 내지 도 7c는 트랜지스터의 단면도 및 상면도.

도 8a 내지 도 8c는 트랜지스터의 단면도 및 상면도.

도 9a 내지 도 9e는 산화물 반도체의 구조를 설명하는 도면.

도 10a 내지 도 10c는 산화물 반도체의 구조를 설명하는 도면.

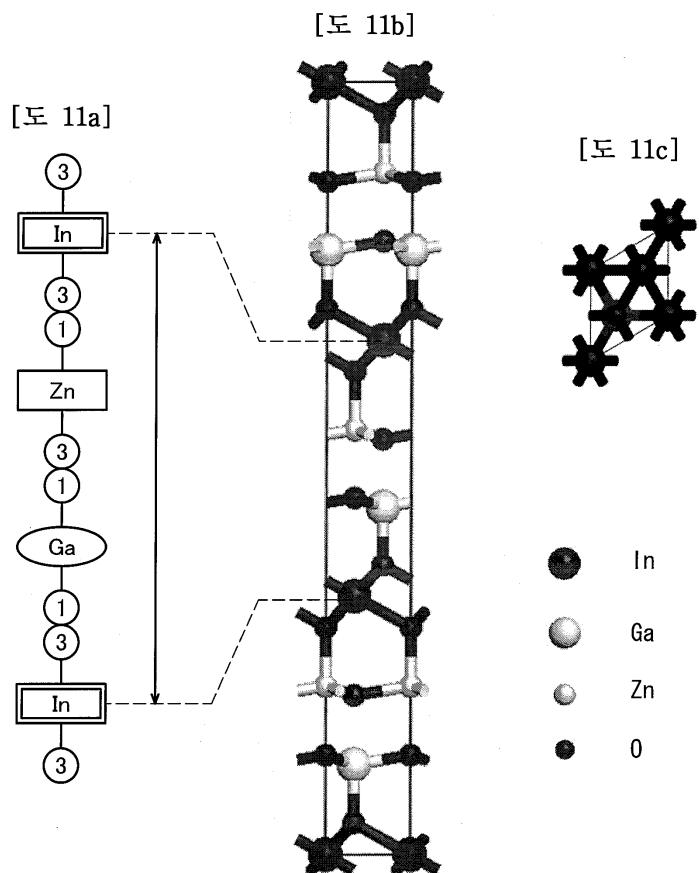

도 11a 내지 도 11c는 산화물 반도체의 구조를 설명하는 도면.

도 12a 및 도 12b는 DCDC 컨버터의 구성의 일례를 도시한 도면.

도 13a 및 도 13b는 DCDC 컨버터의 구성의 일례를 도시한 도면.

도 14a 및 도 14b는 DCDC 컨버터를 사용한 반도체 장치의 도면.

도 15a 내지 도 15f는 전자 기기의 도면.

도 16은 DCDC 컨버터의 구성을 도시한 도면.

### 발명을 실시하기 위한 구체적인 내용

[0019] 이하에서는, 본 발명의 실시형태 및 실시예에 대하여 도면을 사용하여 자세히 설명한다. 다만, 본 발명은 이하의 설명에 한정되지 않고, 본 발명의 취지 및 그 범위에서 일탈하지 않고 그 형태 및 상세를 다양하게 변경할 수 있는 것은, 당업자라면 용이하게 이해된다. 따라서, 본 발명은 이하에 개시하는 실시형태의 기재 내용에 한정하여 해석되는 것은 아니다.

- [0020] 또한, 마이크로 프로세서, 화상 처리 회로 등의 집적 회로나, RF 태그, 기억 매체, 태양 전지, 발광 소자를 사용한 발광 장치, 반도체 표시 장치 등, DCDC 컨버터 또는 전원 회로를 사용할 수 있는 모든 반도체 장치가 본 발명의 범주에 포함된다. 또한, 반도체 표시 장치에는, 액정 표시 장치, 유기 발광 소자(OLED)로 대표되는 발광 소자를 구비한 발광 장치, 전자 페이퍼, DMD(Digital Micromirror Device), PDP(Plasma Display Panel), FED(Field Emission Display) 등, DCDC 컨버터 또는 전원 회로를 갖는 반도체 표시 장치가 그 범주에 포함된다.

- [0021] (실시형태 1)

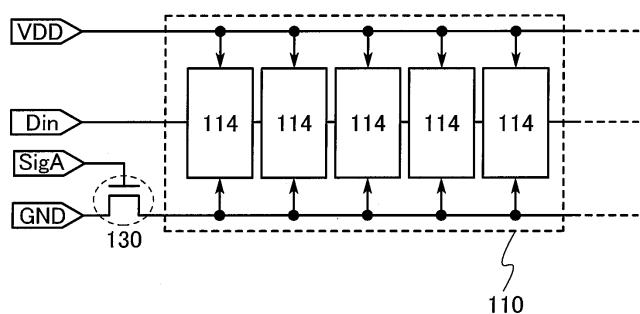

- [0022] 도 1a는 본 발명의 일 형태에 따른 DCDC 컨버터의 구성을 일례로서 도시한 것이다.

- [0023] 도 1a에 도시된 DCDC 컨버터(100)는, 입력 단자(IN)에 인가되는 입력 전압(Vin)을 사용하여, 일정한 출력 전압(Vout)을 생성하여 출력 단자(OUT)로부터 출력되는 전력 변환 회로(101)를 갖는다. 또한, 전력 변환 회로(101)는 스위칭 소자(102)와, 정전압 생성부(103)를 갖는다. 또한, 도 1a에 도시된 DCDC 컨버터(100)는, 스위칭 소자(102)가 온 상태인 기간의 비율, 즉 듀티 비율을 제어하기 위한 제어 회로(104)를 갖는다.

- [0024] 스위칭 소자(102)는, 제어 회로(104)에 의하여 정해진 듀티 비율에 따라 스위칭한다. 그리고, 스위칭 소자(102)가 온 상태일 때 정전압 생성부(103)에 입력 전압(Vin)을 공급하고, 오프 상태일 때 그 공급을 정지한다. 스위칭 소자(102)가 오프 상태로 되면, 정전압 생성부(103)에는 그라운드 등의 기준 전압이 인가된다. 따라서, 스위칭 소자(102)의 스위칭에 따라 입력 전압과 기준 전압이 교차로 출현하는 펄스상의 신호가, 정전압 생성부(103)로 공급된다.

- [0025] 정전압 생성부(103)는 코일, 용량 소자, 다이오드 중 어느 하나 또는 복수를 갖는다. 정전압 생성부(103)는 펄스상의 신호가 공급되면, 상기 신호의 전압을 평활화 또는 유지함으로써, 일정한 출력 전압을 생성한다.

- [0026] 또한, 제어 회로(104)에 의하여 정해진 듀티 비율이 변화되면, 출력 전압의 값도 변화된다. 구체적으로는, 입력 전압을 갖는 펄스가 출현하는 기간의 비율이 클수록, 출력 전압과 기준 전압의 차는 커진다. 반대로, 입력 전압에 의한 펄스가 출현하는 기간의 비율이 작을수록, 출력 전압과 기준 전압의 차는 작아진다.

- [0027] 또한, 본 발명의 일 형태에서는, 스위칭 소자(102)의 스위칭은, 펄스 폭 제어(PWM: Pulse Width Modulation control)에 의하여 행하여도 좋고, 펄스 주파수 제어(PFM: Pulse Frequency Modulation control)에 의하여 행하여도 좋다.

- [0028] 또는, 본 발명의 일 형태에서는, 펄스 폭 제어와 펄스 주파수 제어를 조합하여, 스위칭 소자(102)의 스위칭에 의한 출력 전압의 조정을 행하여도 좋다. 예를 들어, 출력 전압이 작은 경우는, 펄스 주파수 제어를 사용하면 스위칭 소자(102)의 스위칭의 주파수를 더 낮게 억제할 수 있어 스위칭 소자(102)의 스위칭에 의한 전력 손실을 작게 억제할 수 있다. 반대로, 출력 전압이 큰 경우는, 펄스 폭 제어를 사용하면 스위칭 소자(102)의 스위칭의 주파수를 더 낮게 억제할 수 있어 스위칭 소자(102)의 스위칭에 의한 전력 손실을 작게 억제할 수 있다. 따라서, 출력 전압의 크기에 맞추어, 펄스 폭 제어와 펄스 주파수 제어를 전환함으로써, 전력 변환 효율의 향상을 도모할 수 있다.

- [0029] 제어 회로(104)는, AD 컨버터(105)와, AD 컨버터(106)와, 신호 처리 회로(107)와, 펄스 변조 회로(108)와, 전원 제어 회로(109)를 갖는다. 또한, 신호 처리 회로(107)는, 기억 장치(110)를 갖는다.

- [0030] AD 컨버터(105)는, 출력 전압(Vout)을 아날로그 값으로부터 디지털 값으로 변환하는 기능을 갖는다. 신호 처리 회로(107)는 상기 출력 전압(Vout)의 디지털 값을 사용하여 듀티 비율을 정하는 기능을 갖는다. 정해진 듀티 비율의 데이터는, 신호 처리 회로(107) 내의 기억 장치(110)에 있어서 유지된다. 펄스 변조 회로(108)는 상기 듀티 비율에 따라, 스위칭 소자(102)의 스위칭을 제어하는 제어 신호를 생성하는 기능을 갖는다. AD 컨버터(106)는, 입력 전압(Vin)을 아날로그 값으로부터 디지털 값으로 변환하는 기능을 갖는다. 전원 제어 회로(109)는 상기 입력 전압(Vin)의 디지털 값 및 출력 전압(Vout)의 디지털 값에 따라, 신호 처리 회로(107)로의 전원 전압(VDD)의 공급의 유무를 선택하는 기능을 갖는다.

- [0031] 다음에, 도 1b는 기억 장치(110)의 구성의 일례를 블록도로 도시한 것이다. 도 1b에 도시된 바와 같이, 기억 장치(110)는 기억 소자(111)와, 상기 기억 소자(111)의 데이터를 기억하는 용량 소자(112)와, 상기 용량 소자(112)에 있어서의 전하의 공급, 유지, 방출을 제어하는 트랜지스터(113)를 갖는다. 기억 소자(111)는 입력된 신호의 논리값을 반전시켜 출력하는 논리 소자(115)를 복수로 사용한다. 기억 소자(111)와 용량 소자(112)와 트랜지스터(113)로, 1 비트의 데이터를 기억할 수 있는 단위 기억 회로(114)가 구성되어 있고, 기억 장치(110)

는 단위 기억 회로(114)를 단수로 또는 복수로 갖는다.

[0032] 또한, 논리 소자(115)에는 인버터, 클록드 인버터 등을 사용할 수 있다.

[0033] 또한, 단위 기억 회로(114)는, 필요에 따라, 다이오드, 저항 소자, 인덕터 등의 기타 회로 소자를 더 가져도 좋다.

[0034] 신호(Din)가 갖는 1 비트의 듀티 비율의 데이터가 초단의 단위 기억 회로(114)에 입력되면, 상기 데이터는 기억 소자(111)에 입력된다. 기억 소자(111)는 기준 전압(GND)과 하이 레벨의 전원 전압(VDD)이 인가되는 한, 상기 데이터를 유지한다. 그리고, 상기 1 비트의 데이터가 후단의 단위 기억 회로(114)에 입력되면, 신호(Din)가 갖는 다음의 1 비트의 듀티 비율의 데이터가 초단의 단위 기억 회로(114)에 입력된다. 상기 동작을 반복함으로써, 신호(Din)가 갖는 모든 비트의 데이터가 복수의 단위 기억 회로(114)에 의하여 유지된다.

[0035] 용량 소자(112)는 단위 기억 회로(114)에 입력된 신호(Din)의 데이터를 필요에 따라 기억할 수 있도록 트랜지스터(113)를 개재(介在)하여 기억 소자(111)에 접속되어 있다. 구체적으로, 용량 소자(112)는 한 쌍의 전극간에 유전체를 갖는 콘덴서이고, 그 전극 중 한쪽은 트랜지스터(113)를 개재하여 기억 소자(111)에 접속되고, 전극 중 다른 쪽은 그라운드 등의 기준 전압이 인가되는 노드에 접속되어 있다. 트랜지스터(113)는 그 게이트 전극에 인가되는 신호(Sig)에 의하여 스위칭이 제어된다.

[0036] 또한, 도 1a에 도시된 전원 제어 회로(109)는, 상술한 바와 같이, 입력 전압(Vin) 및 출력 전압(Vout)의 디지털 값에 따라 신호 처리 회로(107)로의 전원 전압(VDD)의 공급의 유무를 선택한다. 구체적으로는, 출력 전압(Vout)이 원하는 값으로 유지되고, 입력 전압(Vin)의 변동이 작은 경우에 있어서, 전원 제어 회로(109)는 신호 처리 회로(107)로의 전원 전압(VDD)의 공급을 정지한다. 또한, 입력 전압(Vin)의 변동이 큰 경우에 있어서, 또는 입력 전압(Vout)이 원하는 값으로 유지되지 않은 경우에 있어서, 전원 제어 회로(109)는 신호 처리 회로(107)로 전원 전압(VDD)을 공급한다.

[0037] 그리고, 전원 제어 회로(109)에 의하여 신호 처리 회로(107)로의 전원 전압(VDD)의 공급이 정지되는 경우, 기억 장치(110)에서는 전원 전압(VDD)의 공급이 정지되기 전에 기억 소자(111)에 유지된 듀티 비율의 데이터를 용량 소자(112)에 퇴피시킨다. 구체적으로 데이터의 퇴피는, 용량 소자(112)에 있어서의 전하의 유지에 의하여 행하고, 상기 전하는 상기 오프 전류가 낮은 트랜지스터(113)를 오프 상태로 함으로써 유지된다. 그리고, 신호 처리 회로(107)로의 전원 전압(VDD)의 공급이 재개된 후에 퇴피시켜 둔 데이터를 기억 소자(111)로 되돌린다. 상기 구성에 의하여 기억 장치(110)에 유지된 듀티 비율의 데이터가 전원 전압(VDD)의 공급이 정지됨으로써 소실하는 것을 방지할 수 있다.

[0038] 도 1a 및 도 1b에 도시된 구성을 갖는 DCDC 컨버터(100)의 구체적인 동작의 일례에 대하여 도 2에 도시된 플로우 차트를 사용하여 설명한다.

[0039] 우선, 신호 처리 회로(107)로의 전원 전압(VDD)의 공급을 정지하는지 여부의 판단과, 출력 전압(Vout)의 조정이 시작된다(A: 01 시작). 상기 판단의 시작은, DCDC 컨버터(100)의 외부로부터 입력된 명령에 따라 행하여도 좋고, 소정의 타이밍으로 자동적으로 행하도록 하여도 좋다. 또한, 신호 처리 회로(107)에 미리 전원 전압(VDD)이 공급된 상태라는 전제로, 신호 처리 회로(107)로의 전원 전압(VDD)의 공급을 정지하는지 여부의 판단과, 출력 전압(Vout)의 조정을 행한다.

[0040] 신호 처리 회로(107)는 AD 컨버터(105)로부터 출력된 출력 전압(Vout)의 디지털 값과, 원하는 출력 전압(Vd)의 디지털 값을 비교한다. 그리고, 출력 전압(Vout)이 원하는 출력 전압(Vd)으로 유지되어 있는지 여부를 판단한 결과를 데이터로서 포함한 신호(L-Flag)가 신호 처리 회로(107)로부터 출력된다. 또한, AD 컨버터(106)는 입력 전압(Vin)의 디지털 값을 생성함으로써, 입력 전압(Vin)이 변동되어 있는지 여부를 판단한 결과를 데이터로서 포함한 신호(V-Flag)를 출력한다.

[0041] 예를 들어, 신호(L-Flag)의 디지털 값이 1인 경우, 출력 전압(Vout)이 원하는 출력 전압(Vd)으로 유지되어 있는 것으로 한다. 신호(L-Flag)의 디지털 값이 0인 경우, 출력 전압(Vout)이 원하는 출력 전압(Vd)으로 유지되어 있지 않은 것으로 한다. 또한, 예를 들어 신호(V-Flag)의 디지털 값이 1인 경우, 입력 전압(Vin)이 변동되어 있는 것으로 한다. 신호(V-Flag)의 디지털 값이 0인 경우, 입력 전압(Vin)이 변동되어 있지 않은 것으로 한다.

[0042] 전원 제어 회로(109)에서는, 신호(L-Flag)의 디지털 값과 신호(V-Flag)의 디지털 값에 따라, 전원 전압(VDD)을 신호 처리 회로(107)로 공급하는지 여부를 판단한다. 구체적으로는, 신호(L-Flag)의 디지털 값이 1인지 여부를 판단하고(A: 02 L-Flag=1), 신호(V-Flag)의 디지털 값이 1인지 여부를 판단한다(A: 03 V-Flag=1). 또한, 신호

(L-Flag)의 디지털 값이 1이고, 신호(V-Flag)의 디지털 값이 0인 경우, 신호 처리 회로(107)로의 전원 전압(VDD)의 공급을 정지한다(A: 04 VDD의 공급을 정지). 또한, 신호(L-Flag)의 디지털 값이 0인 경우, 또는 신호(L-Flag)의 디지털 값 및 신호(V-Flag)의 디지털 값이 1인 경우, 신호 처리 회로(107)로의 전원 전압(VDD)의 공급을 행한다(A: 05 VDD를 공급).

[0043] 또한, 신호(L-Flag)의 디지털 값이 1이고, 신호(V-Flag)의 디지털 값이 1인 경우, 입력 전압(Vin)의 변동에 맞춰 출력 전압(Vout)을 원하는 출력 전압(Vd)에 가깝게 할 필요가 있다. 또한, 신호(L-Flag)의 디지털 값이 0이고, 신호(V-Flag)의 디지털 값이 1 또는 0인 경우, 입력 전압(Vin)의 변동의 유무에 상관 없이 출력 전압(Vout)이 원하는 출력 전압(Vd)으로 유지되어 있지 않은 상태이기 때문에, 출력 전압(Vout)을 원하는 출력 전압(Vd)에 가깝게 할 필요가 있다. 신호 처리 회로(107)에서는, AD 컨버터(105)로부터 출력된 출력 전압(Vout)의 디지털 값과, 원하는 출력 전압(Vd)의 디지털 값을 비교한 결과에 따라 듀티 비율을 정한다.

[0044] 구체적으로, 신호 처리 회로(107)에 있어서, 출력 전압(Vout)이 원하는 출력 전압(Vd)과 일치하는지 여부를 판단한다(A: 06 Vout=Vd). 일치한 경우, 출력 전압의 디지털 값(Sout)의 보정은 행하지 않는다(A: 07 Sout → Sout). 즉, 이 경우, 보정되기 전의 디지털 값(Sout)이 보정된 후의 디지털 값(Sout')과 같게 된다.

[0045] 일치하지 않은 경우, 출력 전압(Vout)이 원하는 출력 전압(Vd)보다 큰지 여부를 판단한다(A: 08 Vout>Vd). 출력 전압(Vout)이 원하는 출력 전압(Vd)보다 큰 경우, 듀티 비율이 크게 되도록 출력 전압의 디지털 값(Sout)으로부터 보정값(D)을 뺏으로써 디지털 값(Sout)을 보정하여 디지털 값 Sout' = Sout - D를 생성한다(A: 09 Sout → Sout - D).

[0046] 출력 전압(Vout)이 원하는 출력 전압(Vd)보다 작은 경우, 듀티 비율이 크게 되도록 출력 전압의 디지털 값(Sout)에 보정값(D)을 가산함으로써 디지털 값(Sout)을 보정하여 디지털 값 Sout' = Sout + D를 생성한다(A: 10 Sout → Sout + D).

[0047] 다음에, 신호 처리 회로(107)에서는 보정된 후의 디지털 값(Sout')에 디지털 필터 처리를 실시하고(A: 11 DF 처리), 디지털 필터 처리를 실시한 후의 디지털 값(Sout')을 데이터로서 포함한 신호를 펄스 변조 회로(108)로 송신한다. 또한, 디지털 값(Sout')에는 원하는 출력 전압(Vd)을 얻기 위하여 필요한 듀티 비율이 데이터로서 포함되어 있다. 펄스 변조 회로(108)는 스위칭 소자(102)가 원하는 듀티 비율에 따라 스위칭하도록 신호 처리 회로(107)로부터 송신된 상기 신호에 따라 스위칭 소자(102)를 제어하기 위한 제어 신호를 생성한다.

[0048] 또한, 전력 변환 회로(101)에서는, 상기 제어 신호에 따라 스위칭 소자(102)가 스위칭함으로써, 출력 전압(Vout)이 원하는 출력 전압(Vd)에 가깝게 되도록 출력 전압(Vout)이 조정된다(A: 12 Vout → Vd).

[0049] 또한, 출력 전압(Vout)이 조정된 후, 신호 처리 회로(107)는 AD 컨버터(105)로부터 출력된 출력 전압(Vout)의 디지털 값과, 원하는 출력 전압(Vd)의 디지털 값을 다시 비교한다. 그리고, 출력 전압(Vout)이 원하는 출력 전압(Vd)으로 유지되어 있는지 여부를 판단한 결과를 데이터로서 포함한 신호(L-Flag)가 신호 처리 회로(107)로부터 출력된다.

[0050] 전원 제어 회로(109)에서는, 신호(L-Flag)의 디지털 값에 따라, 출력 전압(Vout)이 원하는 출력 전압(Vd)에 가깝게 된지 여부를 판단한다. 구체적으로는, 신호(L-Flag)의 디지털 값이 1인지 여부를 판단한다(A: 13 L-Flag=1). 그리고, 신호(L-Flag)의 디지털 값이 1인 경우, 신호 처리 회로(107)로의 전원 전압(VDD)의 공급을 정지하는지 여부의 판단과, 출력 전압(Vout)의 조정이 종료한다(A: 14 종료). 신호(L-Flag)의 디지털 값이 0인 경우, 신호 처리 회로(107)에 있어서 AD 컨버터(105)로부터 출력된 출력 전압(Vout)의 디지털 값과, 원하는 출력 전압(Vd)의 디지털 값을 비교한 결과에 따라 듀티 비율을 다시 정한다. 구체적으로는 DCDC 컨버터(100)는 신호 처리 회로(107)가, 출력 전압(Vout)이 원하는 출력 전압(Vd)과 일치하는지 여부를 판단(A: 06 Vout=Vd)하는 것으로부터 신호(L-Flag)의 디지털 값이 1인지 여부를 판단(A: 13 L-Flag=1)하기까지를 다시 반복한다. 또한, 상기 반복의 횟수는 설계자가 적절히 설정할 수 있다.

[0051] 본 발명의 일 형태에서는, 외부 기억 회로에 데이터를 퇴피시킬 필요가 없기 때문에, 신호 처리 회로(107)에 있어서 짧은 시간이라도 전원 전압(VDD)의 공급을 정지할 수 있다. 결과적으로, DCDC 컨버터(100)의 소비 전력을 저감시킬 수 있다. 또한, 전원 전압(VDD)의 공급이 정지되어도 듀티 비율의 데이터는 기억 장치(110) 내에 있어서 유지되어 있기 때문에, 전원 전압의 공급이 재개된 후에도 DCDC 컨버터(100)의 출력 전압(Vout)이 불안정하게 되는 것을 방지할 수 있다.

[0052] 따라서, DCDC 컨버터(100)에 있어서 오프 전류에 기인하는 소비 전력을 대폭으로 저감할 수 있고, DCDC 컨버터

(100)를 사용한 전원 회로 또는 반도체 장치의 소비 전력을 낮게 억제할 수 있게 된다.

[0053] 또한, 도 1a, 도 1b, 및 도 2에서는, 출력 전압(Vout)이 원하는 값으로 유지되고, 입력 전압(Vin)의 변동이 작은 경우에 있어서 전원 제어 회로(109)가 신호 처리 회로(107)로의 전원 전압(VDD)의 공급을 정지시키는 경우를 예시하였다. 그러나, 본 발명의 일 형태에서는 전원 제어 회로(109)가 신호 처리 회로(107)로의 전원 전압(VDD)을 공급할 뿐만 아니라 AD 컨버터(105)로의 전원 전압(VDD)의 공급을 정지시켜도 좋다. 상기 구성에 의하여 DCDC 컨버터(100)의 소비 전력을 더 저감시킬 수 있다.

[0054] 본 발명의 일 형태에서는, 트랜지스터(113)가 실리콘보다 밴드 갭이 넓고, 실리콘보다 진성 캐리어 밀도가 낮은 산화물 반도체 등의 반도체를 채널 형성 영역에 포함한다. 산화물 반도체를 채널 형성 영역에 갖는 트랜지스터는, 실리콘이나 게르마늄 등의 일반적인 반도체로 형성된 트랜지스터와 비교하여, 오프 전류가 현저히 작다. 용량 소자(112)에 있어서의 데이터의 유지 기간의 길이는, 용량 소자(112)에 축적되어 있는 전하가 트랜지스터(113)를 통하여 누설되는 양에 의존한다. 따라서, 오프 전류가 현저히 작은 트랜지스터(113)에 의하여 용량 소자(112)에 축적된 전하를 유지함으로써, 용량 소자(112)로부터의 전하의 누설을 방지할 수 있어 데이터의 유지 기간을 길게 확보할 수 있다.

[0055] 또한, 특별히 언급하지 않는 한, 본 명세서에서 오프 전류란, n채널형 트랜지스터에 있어서는, 드레인을 소스와 게이트 전극보다 높은 전압으로 한 상태에 있어서, 소스의 전압을 기준으로 하였을 때의 게이트 전극의 전압이 0 이하일 때에, 소스와 드레인 사이에 흐르는 전류를 의미한다. 또는, 본 명세서에서 오프 전류란, p채널형 트랜지스터에 있어서는, 드레인을 소스와 게이트 전극보다 낮은 전압으로 한 상태에 있어서, 소스의 전압을 기준으로 하였을 때의 게이트 전극의 전압이 0 이상 일 때에, 소스와 드레인 사이에 흐르는 전류를 의미한다.

[0056] 또한, 도 1b에서는, 트랜지스터(113)가 싱글 게이트 구조인 경우를 예시하고 있지만, 상기 트랜지스터는 전기적으로 접속된 복수의 게이트 전극을 가짐으로써, 채널 형성 영역을 복수로 갖는 멀티 게이트 구조라도 좋다.

[0057] 도 1b에서는, 트랜지스터(113)를 하나만 사용하여 용량 소자(112)에 있어서의 전하의 공급, 유지, 방출을 제어하는 구성을 도시하였지만, 본 발명은 이 구성을 한정되지 않는다. 본 발명의 일 형태에서는, 복수의 트랜지스터(113)를 사용하여 용량 소자(112)에 있어서의 전하의 공급, 유지, 방출을 제어하는 구성을 채용하여도 좋다. 트랜지스터(113)를 복수로 사용하는 경우, 상기 복수의 트랜지스터(113)는 병렬로 접속되어도 좋고, 직렬로 접속되어도 좋고, 직렬과 병렬이 조합되어 접속되어도 좋다.

[0058] 또한, 본 명세서에 있어서 트랜지스터가 직렬로 접속되는 상태란, 제 1 트랜지스터의 소스와 드레인 중 어느 한 쪽만이 제 2 트랜지스터의 소스와 드레인 중 어느 한쪽에만 접속되는 상태를 의미한다. 또한, 트랜지스터가 병렬로 접속되는 상태란, 제 1 트랜지스터의 소스와 드레인 중 어느 한쪽이 제 2 트랜지스터의 소스와 드레인 중 어느 한쪽에 접속되고, 제 1 트랜지스터의 소스와 드레인 중 다른 쪽이 제 2 트랜지스터의 소스와 드레인 중 다른 쪽에 접속되는 상태를 의미한다.

[0059] 또한, 트랜지스터가 갖는 소스와 드레인은, 트랜지스터의 극성 및 소스와 드레인에 인가되는 전압의 고저에 따라, 그 호칭이 바뀐다. 일반적으로, n채널형 트랜지스터에서는, 소스와 드레인 중, 낮은 전위가 인가되는 쪽이 소스라고 불리고, 높은 전위가 인가되는 쪽이 드레인이라고 불린다. 또한, p채널형 트랜지스터에서는, 소스와 드레인 중, 낮은 전압이 인가되는 쪽이 드레인이라고 불리고, 높은 전압이 인가되는 쪽이 소스라고 불린다. 본 명세서에서는, 편의상 소스와 드레인이 고정되는 것으로 가정하면서 트랜지스터의 접속 관계를 설명할 경우가 있지만, 실제적으로는 상기 전압의 관계에 따라 소스와 드레인의 호칭이 바뀐다.

[0060] 또한, 본 발명의 일 형태에서는, 기억 소자(111)를 구성하는 트랜지스터가 결정성을 갖는 실리콘, 또는 게르마늄 등의 반도체를 채널 형성 영역에 포함하여도 좋고, 트랜지스터(113)와 마찬가지로 실리콘보다 밴드 갭이 넓고, 실리콘보다 진성 캐리어 밀도가 낮은 산화물 반도체 등의 반도체를 채널 형성 영역에 포함하여도 좋다. 결정성을 갖는 실리콘, 또는 게르마늄 등의 반도체의 이동도가 산화물 반도체보다 높은 경우, 기억 소자(111)를 구성하는 트랜지스터가 결정성을 갖는 실리콘, 또는 게르마늄 등의 반도체를 채널 형성 영역에 포함함으로써 기억 장치(110), 나아가서는 DCDC 컨버터(100)의 고속 동작을 확보할 수 있다.

[0061] 또한, 도 1a에서는, 출력 전압(Vout)만을 사용하여 스위칭 소자(102)의 드라이버 비율을 제어하지만, 본 발명의 일 형태에 따른 DCDC 컨버터에서는 출력 전압(Vout)뿐만 아니라 출력 전류를 사용하여 스위칭 소자(102)의 드라이버 비율을 제어하도록 하여도 좋다.

[0062] 도 16은 본 발명의 일 형태에 따른 DCDC 컨버터(100)의 구성을 일례로서 도시한 것이다. 도 16에 도시된 DCDC 컨버터(100)는 AD 컨버터(150)가 제어 회로(104)에 추가되는 점에 있어서, 도 1a에 도시된 DCDC 컨버터(100)와

구성이 상이하다. AD 컨버터(150)는 CT 센서(커런트 트랜스 센서) 등으로 검출된 출력 전류를 아날로그 값으로 부터 디지털 값으로 변환한 후, 상기 디지털 값을 신호 처리 회로(107)로 송신한다. DCDC 컨버터(100)에서는, 출력 전압(Vout)의 디지털 값과 출력 전류의 디지털 값에 따라 스위칭 소자(102)의 듀티 비율을 제어한다.

[0063] DCDC 컨버터(100)의 출력 전압(Vout) 및 출력 전류 양쪽을 검출하고, 이들의 디지털 값에 따라 듀티 비율을 제어함으로써, DCDC 컨버터의 출력 전압뿐만 아니라 출력 전력도 원하는 값으로 유지할 수 있도록 듀티 비율을 적절한 값으로 설정할 수 있다.

[0064] (실시형태 2)

[0065] 본 실시형태에서는, 신호 처리 회로와, 신호 처리 회로가 갖는 기억 장치의 구성에 대하여 설명한다.

[0066] 본 발명의 일 형태에서는, 기억 장치가, 1 비트의 데이터를 기억할 수 있는 단위 기억 회로를 단수 또는 복수로 갖는다. 도 3은 단위 기억 회로(114)의 회로도의 일례를 도시한 것이다.

[0067] 도 3에 도시된 단위 기억 회로(114)는, 기억 소자(111)와 용량 소자(112)와 트랜지스터(113)를 갖는다. 기억 소자(111)는 입력된 신호의 논리값을 반전시켜 출력하는 제 1 논리 소자(115a) 및 제 2 논리 소자(115b)와, 트랜지스터(116)와 트랜지스터(117)를 갖는다.

[0068] 단위 기억 회로(114)에 입력된 데이터를 포함한 신호(Din)는, 트랜지스터(116)를 통하여 제 1 논리 소자(115a)의 입력 단자에 인가된다. 제 1 논리 소자(115a)의 출력 단자는, 제 2 논리 소자(115b)의 입력 단자에 접속된다. 제 2 논리 소자(115b)의 출력 단자는 트랜지스터(117)를 개재하여 제 1 논리 소자(115a)의 입력 단자에 접속된다. 제 1 논리 소자(115a)의 출력 단자 또는 제 2 논리 소자(115b)의 입력 단자의 전압이, 신호(Dout)로서 후단의 단위 기억 회로(114) 또는 다른 회로에 출력된다.

[0069] 또한, 도 3에서는, 제 1 논리 소자(115a) 및 제 2 논리 소자(115b)로서 인버터를 사용하는 예를 도시하지만, 제 1 논리 소자(115a) 또는 제 2 논리 소자(115b)로서 인버터 외에 클록드 인버터를 사용할 수도 있다.

[0070] 용량 소자(112)는, 단위 기억 회로(114)에 입력된 신호(Din)의 데이터를 필요에 따라 기억할 수 있도록 트랜지스터(116) 및 트랜지스터(113)를 개재하여 단위 기억 회로(114)의 입력 단자, 즉 신호(Din)의 전압이 인가되는 노드에 접속된다. 구체적으로는, 용량 소자(112)가 갖는 한 쌍의 전극 중, 한쪽의 전극은 트랜지스터(113)를 개재하여 제 1 논리 소자(115a)의 입력 단자에 접속되고, 다른 쪽의 전극은 그라운드 등의 기준 전압이 인가되는 노드에 접속된다.

[0071] 또한, 트랜지스터(113)는 실리콘이나 게르마늄 등의 일반적인 반도체로 형성된 트랜지스터와 비교하여 오프 전류가 매우 작다. 용량 소자(112)에 있어서의 데이터의 유지 기간의 길이는 용량 소자(112)에 축적되는 전하가 트랜지스터(113)를 통하여 누설되는 양에 의존한다. 따라서, 상술한 바와 같이 오프 전류가 매우 작은 트랜지스터(113)에 의하여 용량 소자(112)에 축적된 전하를 유지함으로써, 용량 소자(112)로부터의 전하의 누설을 방지할 수 있고, 데이터의 유지 기간을 길게 확보할 수 있다.

[0072] 또한, 도 3에서는 트랜지스터(113)를 구성하는 트랜지스터가 싱글 게이트 구조인 경우를 예시하고 있지만, 상기 트랜지스터는 전기적으로 접속된 복수의 게이트 전극을 가짐으로써 채널 형성 영역을 복수로 갖는 멀티 게이트 구조이어도 좋다.

[0073] 또한, 도 3에서는 트랜지스터(113)를 하나만 사용하여 용량 소자(112)에 있어서의 전하의 공급, 유지, 방출을 제어하는 구성을 도시하였지만, 본 발명은 이 구성을 한정되지 않는다. 본 발명의 일 형태에서는 복수의 트랜지스터(113)를 사용하여 용량 소자(112)에 있어서의 전하의 공급, 유지, 방출을 제어하는 구성을 채용하여도 좋다. 트랜지스터(113)를 복수로 사용하는 경우, 상기 복수의 트랜지스터(113)는 병렬로 접속되어도 좋고, 직렬로 접속되어도 좋고, 직렬과 병렬이 조합되어 접속되어도 좋다.

[0074] 또한, 단위 기억 회로(114)는, 필요에 따라, 다이오드, 저항 소자, 인덕터 등의 기타 회로 소자를 더 가져도 좋다.

[0075] 제 1 논리 소자(115a)는 게이트 전극이, 서로 접속된 p채널형 트랜지스터(118)와 n채널형 트랜지스터(119)가 하이 레벨의 전원 전압(VDD)이 공급되는 제 1 노드와 로우 레벨의 기준 전압(GND)이 인가되는 제 2 노드 사이에서, 직렬로 접속된 구성을 갖는다. 구체적으로는, p채널형 트랜지스터(118)의 소스가 전원 전압(VDD)이 인가되는 제 1 노드에 접속되고, n채널형 트랜지스터(119)의 소스가 기준 전압(GND)이 인가되는 제 2 노드에 접속된다. 또한, p채널형 트랜지스터(118)의 드레인과, n채널형 트랜지스터(119)의 드레인이 접속되고, 상기 2개

의 드레인의 전압은 제 1 논리 소자(115a)의 출력 단자의 전압으로 간주할 수 있다. 또한, p채널형 트랜지스터(118)의 게이트 전극 및 n채널형 트랜지스터(119)의 게이트 전극의 전압은, 제 1 논리 소자(115a)의 입력 단자의 전압으로 간주할 수 있다.

[0076] 제 2 논리 소자(115b)는 게이트 전극이, 서로 접속된 p채널형 트랜지스터(120)와 n채널형 트랜지스터(121)가 하이 레벨의 전원 전압(VDD)이 공급되는 제 1 노드와 로우 레벨의 기준 전압(GND)이 인가되는 제 2 노드 사이에서, 직렬로 접속된 구성을 갖는다. 구체적으로는, p채널형 트랜지스터(120)의 소스가 전원 전압(VDD)이 인가되는 제 1 노드에 접속되고, n채널형 트랜지스터(121)의 소스가 기준 전압(GND)이 인가되는 제 2 노드에 접속된다. 또한, p채널형 트랜지스터(120)의 드레인과, n채널형 트랜지스터(121)의 드레인이 접속되고, 상기 2개의 드레인의 전압은 제 2 논리 소자(115b)의 출력 단자의 전압으로 간주할 수 있다. 또한, p채널형 트랜지스터(120)의 게이트 전극 및 n채널형 트랜지스터(121)의 게이트 전극의 전압은, 제 2 논리 소자(115b)의 입력 단자의 전압으로 간주할 수 있다.

[0077] 또한, 트랜지스터(116)는 그 게이트 전극에 인가되는 신호(Sig1)에 의하여 스위칭이 제어된다. 또한, 트랜지스터(117)는 그 게이트 전극에 인가되는 신호(Sig2)에 의하여 스위칭이 제어된다. 트랜지스터(113)에 사용되는 트랜지스터는 그 게이트 전극에 인가되는 제어 신호(Sig3)에 의하여 스위칭이 제어된다.

[0078] 또한, 도 3에 도시된 단위 기억 회로(114)에 있어서, 트랜지스터(116) 대신에 복수의 트랜지스터로 구성되는 스위칭 소자를 사용하여도 좋다. 트랜지스터(116) 대신에 복수의 트랜지스터로 구성되는 스위칭 소자를 사용하는 경우, 상기 복수의 트랜지스터는 병렬로 접속되어도 좋고, 직렬로 접속되어도 좋고, 직렬과 병렬이 조합되어 접속되어도 좋다. 또한, 도 3에 도시된 단위 기억 회로(114)에 있어서, 트랜지스터(117) 대신에 복수의 트랜지스터로 구성되는 스위칭 소자를 사용하여도 좋다. 트랜지스터(117) 대신에 복수의 트랜지스터로 구성되는 스위칭 소자를 사용하는 경우, 상기 복수의 트랜지스터는 병렬로 접속되어도 좋고, 직렬로 접속되어도 좋고, 직렬과 병렬이 조합되어 접속되어도 좋다.

[0079] 또한, 제 1 논리 소자(115a) 및 제 2 논리 소자(115b)에는, 고속 동작이 요구된다. 따라서, 결정성을 갖는 실리콘 또는 게르마늄을 채널 형성 영역에 갖는 트랜지스터를, 제 1 논리 소자(115a)가 갖는 n채널형 트랜지스터(119), 또는 p채널형 트랜지스터(118)로서 사용하거나, 또는 제 2 논리 소자(115b)가 갖는 n채널형 트랜지스터(121), 또는 p채널형 트랜지스터(120)로서 사용하는 것이 바람직하다.

[0080] 또한, 트랜지스터(116) 또는 트랜지스터(117)는 결정성을 갖는 실리콘 또는 게르마늄을 채널 형성 영역에 가져도 좋다.

[0081] 다음에, 도 3에 도시된 단위 기억 회로(114)의 동작의 일례에 대하여 설명한다.

[0082] 우선, 데이터를 기록할 때, 트랜지스터(116)는 온 상태, 트랜지스터(117)는 오프 상태, 트랜지스터(113)는 오프 상태로 한다. 또한, 제 1 노드에 전원 전압(VDD)을 인가하고, 제 2 노드에 기준 전압(GND)을 인가함으로써, 기억 소자(111)에 전원 전압이 인가된다. 단위 기억 회로(114)에 인가되는 신호(Din)의 전압은, 트랜지스터(116)를 통하여 제 1 논리 소자(115a)의 입력 단자에 인가되므로, 제 1 논리 소자(115a)의 출력 단자는 신호(Din)의 논리값이 반전된 전압이 된다. 그리고, 트랜지스터(117)를 온 상태로 하여, 제 1 논리 소자(115a)의 입력 단자와 제 2 논리 소자(115b)의 출력 단자를 접속시킴으로써, 제 1 논리 소자(115a) 및 제 2 논리 소자(115b)에 데이터가 기록된다.

[0083] 다음에, 입력된 데이터의 유지를 제 1 논리 소자(115a) 및 제 2 논리 소자(115b)에 의하여 행하는 경우, 트랜지스터(117)는 온 상태, 트랜지스터(113)는 오프 상태로 한 채, 트랜지스터(116)를 오프 상태로 한다. 트랜지스터(116)를 오프 상태로 함으로써, 입력된 데이터는 제 1 논리 소자(115a) 및 제 2 논리 소자(115b)에 의하여 유지된다. 이 때, 제 1 노드에 전원 전압(VDD)을 인가하고 제 2 노드에 기준 전압(GND)을 인가함으로써, 제 1 노드와 제 2 노드 사이에 전원 전압이 인가되는 상태를 유지한다.

[0084] 그리고, 제 1 논리 소자(115a)의 출력 단자의 전압에는, 제 1 논리 소자(115a) 및 제 2 논리 소자(115b)에 의하여 유지되는 데이터가 반영된다. 따라서, 상기 전압을 판독함으로써 데이터를 단위 기억 회로(114)로부터 판독할 수 있다.

[0085] 또한, 데이터를 유지할 때에 있어서 전원 전압의 공급을 정지하는 경우, 전원 전압의 공급이 정지되기 전에, 데이터의 유지를 용량 소자(112)에 있어서 행한다. 용량 소자(112)에 있어서 데이터의 유지를 행하는 경우, 우선 트랜지스터(116)는 오프 상태, 트랜지스터(117)는 온 상태, 트랜지스터(113)는 온 상태로 한다. 그리고, 트랜지스터(113)를 통하여 제 1 논리 소자(115a) 및 제 2 논리 소자(115b)에 의하여 유지되는 데이터의 값에 대응한

양의 전하가 용량 소자(112)에 축적됨으로써 용량 소자(112)에 데이터가 기록된다. 용량 소자(112)에 데이터가 기억된 후, 트랜지스터(113)를 오프 상태로 함으로써, 용량 소자(112)에 기억된 데이터는 유지된다. 트랜지스터(113)를 오프 상태로 한 후에는, 제 1 노드와 제 2 노드에 예를 들어 기준 전압(GND)을 인가하여 등전압으로 함으로써, 제 1 노드와 제 2 노드간의 전원 전압의 인가를 정지한다. 또한, 용량 소자(112)에 데이터가 기억된 후에는, 트랜지스터(117)를 오프 상태로 하여도 좋다.

[0086] 이와 같이, 입력된 데이터의 유지를 용량 소자(112)에서 행하는 경우는, 제 1 노드와 제 2 노드간에 전원 전압을 인가할 필요가 없기 때문에, 제 1 논리 소자(115a)가 갖는 p채널형 트랜지스터(118) 및 n채널형 트랜지스터(119), 또는 제 2 논리 소자(115b)가 갖는 p채널형 트랜지스터(120) 및 n채널형 트랜지스터(121)를 통하여, 제 1 노드와 제 2 노드 사이에 흐르는 오프 전류를 최대한 0에 가깝게 할 수 있다. 따라서, 데이터를 유지할 때의 기억 소자(111)의 오프 전류에 기인한 소비 전력을 대폭적으로 삭감할 수 있고, 기억 장치, 나아가서는 기억 장치를 사용한 DCDC 컨버터의 소비 전력을 낮게 억제할 수 있게 된다.

[0087] 또한, 상술한 바와 같이, 트랜지스터(113)는 오프 전류가 매우 작다. 따라서, 상기 트랜지스터(113)가 오프일 때 용량 소자(112)에 축적된 전하는 누설되기 어렵기 때문에 데이터는 유지된다.

[0088] 또한, 용량 소자(112)에 기억된 데이터를 판독하는 경우에는, 트랜지스터(116)를 오프 상태로 한다. 또한, 다시 제 1 노드에 전원 전압(VDD)을 인가하고, 제 2 노드에 기준 전압(GND)을 인가함으로써, 제 1 노드와 제 2 노드 사이에 전원 전압이 인가된다. 또한, 트랜지스터(113)를 온 상태로 함으로써, 데이터가 반영된 전압을 갖는 신호(Dout)를 단위 기억 회로(114)로부터 판독할 수 있다.

[0089] 또한, 산화물 반도체를 채널 형성 영역에 갖는 트랜지스터를 사용하여 제 1 노드와 제 2 노드 사이의 전원 전압의 인가를 제어하는 구성으로 하여도 좋다. 도 4a는 상기 구성을 갖는 기억 장치를 일례로서 도시한 것이다.

[0090] 도 4a에 도시된 기억 장치(110)는, 단위 기억 회로(114)를 복수로 갖는다. 구체적으로, 각 단위 기억 회로(114)에는 도 3에 도시된 단위 기억 회로(114)를 사용할 수 있다. 또한, 스위칭 소자(130)는 전원 제어 회로(109)에 포함되고, 기억 장치(110)가 갖는 각 단위 기억 회로(114)에는 스위칭 소자(130)를 통하여 하이 레벨의 전원 전압(VDD)이 공급된다. 또한, 기억 장치(110)가 갖는 각 단위 기억 회로(114)에는 신호(Din)의 전압과 로우 레벨의 기준 전압(GND)의 전압이 인가된다.

[0091] 도 4a에서는, 스위칭 소자(130)로서, 산화물 반도체를 채널 형성 영역에 갖는 트랜지스터를 사용하고, 상기 트랜지스터는, 그 게이트 전극에 인가되는 신호(SigA)에 의하여 스위칭이 제어된다. 스위칭 소자(130)에 사용하는 트랜지스터는 산화물 반도체를 채널 형성 영역에 갖기 때문에, 그 오프 전류는 상술한 바와 같이 매우 작다.

[0092] 또한, 도 4a에서는, 스위칭 소자(130)가 트랜지스터를 하나만 갖는 구성을 도시하였지만, 본 발명은 이 구성에 한정되지 않는다. 본 발명의 일 형태에서는, 스위칭 소자(130)가, 트랜지스터를 복수로 가져도 좋다. 스위칭 소자(130)가, 트랜지스터를 복수로 갖는 경우, 상기 복수의 트랜지스터는 병렬로 접속되어 있어도 좋고, 직렬로 접속되어 있어도 좋고, 직렬과 병렬이 조합되어 접속되어도 좋다.

[0093] 또한, 도 4a에서는, 스위칭 소자(130)에 의하여, 기억 장치(110)가 갖는 각 단위 기억 회로(114)로의 하이 레벨의 전원 전압 VDD의 공급이 제어되고 있지만, 스위칭 소자(130)에 의하여, 로우 레벨의 기준 전압 GND의 공급이 제어되어도 좋다. 도 4b는 기억 장치(110)가 갖는 각 단위 기억 회로(114)에 스위칭 소자(130)를 통하여 로우 레벨의 기준 전압 GND가 공급되는 기억 장치(110)의 일례를 도시한 것이다. 스위칭 소자(130)에 의하여, 기억 장치(110)가 갖는 각 단위 기억 회로(114)로의 로우 레벨의 기준 전압 GND의 공급을 제어할 수 있다.

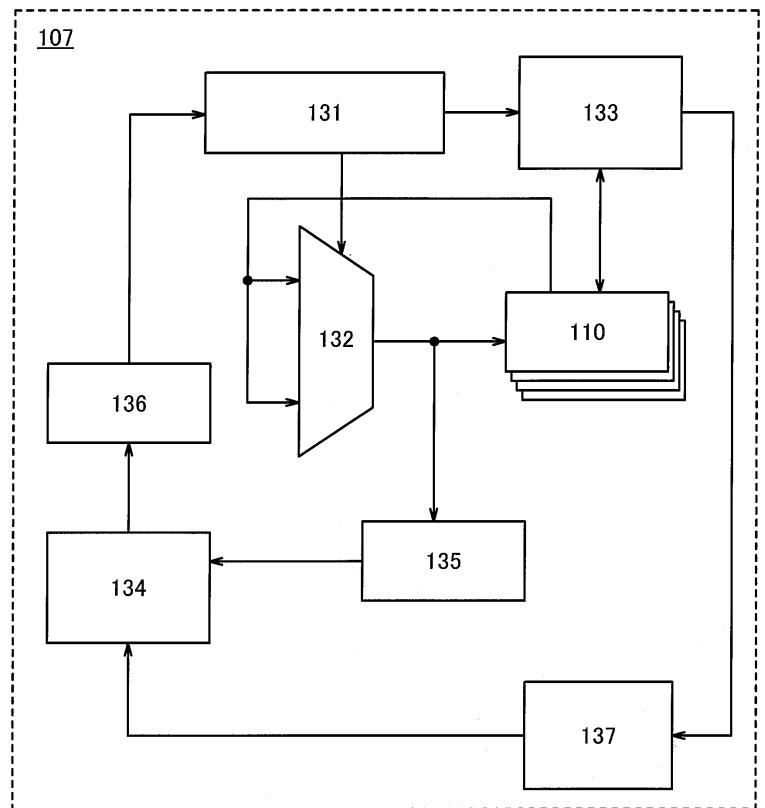

[0094] 다음에, 본 발명의 DCDC 컨버터가 갖는 신호 처리 회로의 구체적인 일 형태에 대하여 설명한다. 도 5는 반도체 장치의 구성을 블록으로 일례로서 도시한 것이다.

[0095] 신호 처리 회로(107)는 제어 장치(131)와, 연산 장치에 상당하는 ALU(Arithmetic logic unit)(132)와, 데이터 캐쉬(133)와, 명령 캐쉬(134)와, 프로그램 카운터(135)와, 명령 레지스터(136)와, 비휘발성 기억 장치(137)와 기억 장치(110)를 갖는다.

[0096] 제어 장치(131)는 입력된 명령을 디코드하여 실행하는 기능을 갖는다. ALU(132)는 사칙 연산, 논리 연산 등의 각종 연산 처리를 행하는 기능을 갖는다. 데이터 캐쉬(133)는 사용 빈도가 높은 데이터를 일시적으로 기억해 두는 완충 기억 장치이다. 명령 캐쉬(134)는 제어 장치(131)로 송신되는 명령(프로그램) 중, 사용 빈도가 높은 명령을 일시적으로 기억해 두는 완충 기억 장치이다. 프로그램 카운터(135)는 다음에 실행할 명령의 어드레스를 기억하는 레지스터이다. 명령 레지스터(136)는 다음에 실행할 명령을 기억하는 레지스터이다. 비휘발성 기

역 장치(137)에는, ALU(132)에 있어서의 연산 처리에 사용되는 데이터나, 제어 장치(131)에 있어서 실행되는 명령이 기억되어 있다. 기억 장치(110)는, ALU(132)의 연산 처리의 결과 얻어진 보정 후의 디지털 값(Sout')의 데이터, 신호(L-Flag)의 디지털 값의 데이터 등의 외, 비휘발성 기억 장치(137)로부터 판독된 데이터, ALU(132)의 연산 처리의 도중에 얻어진 데이터 등을 기억할 수 있다.

[0097] 이어서, 신호 처리 회로(107)의 동작에 대하여 설명한다.

[0098] 제어 장치(131)는 프로그램 카운터(135)에 기억되어 있는, 다음에 실행할 명령의 어드레스에 따라, 명령 캐쉬(134)의 대응하는 어드레스로부터 명령을 판독하고, 명령 레지스터(136)에 상기 명령을 기억시킨다. 명령 캐쉬(134)의 대응하는 어드레스에, 해당하는 명령이 기억되어 있지 않은 경우에는, 비휘발성 기억 장치(137)의 대응하는 어드레스에 액세스하여 비휘발성 기억 장치(137)로부터의 명령을 판독하고, 명령 레지스터(136)에 기억시킨다. 이 경우, 상기 명령을 명령 캐쉬(134)에도 기억시켜 둔다.

[0099] 제어 장치(131)는 명령 레지스터(136)에 기억되어 있는 명령을 디코드하여 명령을 실행한다. 구체적으로는, 상기 명령에 따라 ALU(132)의 동작을 제어하기 위한 각종 신호를 생성한다.

[0100] 실행해야 할 명령이 연산 명령인 경우에는, 기억 장치(110)에 기억되어 있는 데이터를 사용하여 ALU(132)에 연산 처리를 실시시키고, 그 연산 처리의 결과를 기억 장치(110)에 저장한다.

[0101] 실행해야 할 명령이 로드 명령인 경우에는, 제어 장치(131)는 우선 데이터 캐쉬(133)의 대응하는 어드레스에 액세스하여 해당되는 데이터가 데이터 캐쉬(133) 중에 있는지 여부를 확인한다. 해당되는 데이터가 있는 경우에는 상기 데이터를 데이터 캐쉬(133)의 대응하는 어드레스로부터 기억 장치(110)에 복사한다. 해당되는 데이터가 없는 경우에는, 상기 데이터를 비휘발성 기억 장치(137)의 대응하는 어드레스로부터 데이터 캐쉬(133)의 대응하는 어드레스에 복사한 후, 데이터 캐쉬(133)의 대응하는 어드레스로부터 기억 장치(110)에 상기 데이터를 복사한다. 또한, 해당되는 데이터가 없는 경우에는 저속의 비휘발성 기억 장치(137)에 액세스할 필요가 있기 때문에, 데이터 캐쉬(133) 등의 완충 기억 장치에만 액세스하는 경우보다 명령을 실행하는 데에 시간이 필요하다. 그러나, 상기 데이터의 복사에 더하여 비휘발성 기억 장치(137)에서의 상기 데이터의 어드레스 및 그 근방의 어드레스 데이터도 완충 기억 장치에 복사해 둠으로써 비휘발성 기억 장치(137)에서의 상기 데이터의 어드레스 및 그 근방의 어드레스에 대한 2번째 이후의 액세스를 고속으로 행할 수 있다.

[0102] 실행해야 할 명령이 스토어 명령인 경우에는, 기억 장치(110)의 데이터를, 데이터 캐쉬(133)의 대응하는 어드레스에 기억시킨다. 이 때, 제어 장치(131)는, 우선 데이터 캐쉬(133)의 대응하는 어드레스에 액세스하여 해당되는 데이터를 데이터 캐쉬(133) 중에 저장할 수 있는지 여부를 확인한다. 저장할 수 있는 경우에는, 상기 데이터를 기억 장치(110)로부터 데이터 캐쉬(133)의 대응하는 어드레스에 복사한다. 저장할 수 없는 경우에는, 데이터 캐쉬(133)의 일부 영역에 새롭게 대응하는 어드레스를 배정하고, 상기 데이터를 기억 장치(110)로부터 데이터 캐쉬(133)의 대응하는 어드레스에 복사한다. 또한, 데이터 캐쉬(133)에 데이터를 복사하면 즉시, 비휘발성 기억 장치(137)에도 상기 데이터를 복사하는 구성도 가능하다. 또한, 여러 데이터를 데이터 캐쉬(133)에 복사한 후, 그들의 데이터를 통합하여 비휘발성 기억 장치(137)에 복사하는 구성도 가능하다.

[0103] 또한, 제어 장치(131)는 명령의 실행이 종료되면, 프로그램 카운터(135)에 다시 액세스하고, 명령 레지스터(136)로부터 판독된 명령을 디코드, 실행한다는 상기 동작을 반복한다.

[0104] 또한, ALU(132)는 기억 장치(110)에 있어서의 유지 동작의 선택을 행한다. 즉, 기억 장치(110)에 있어서, 기억 소자(111)에 데이터를 유지하는지, 또는 용량 소자(112)에 데이터를 유지하는지를 선택한다. 구체적으로는, DCDC 컨버터의 입력 전압의 변동이 큰 경우, 또는 DCDC 컨버터의 출력 전압이 원하는 값으로 유지되지 않은 경우에 있어서, 기억 소자(111)에 의한 데이터의 유지가 선택된다. 또한, 출력 전압이 원하는 값으로 유지되고, 또 입력 전압의 변동이 작은 경우에 있어서, 기억 장치(110) 내의 기억 소자(111)로의 전원 전압의 공급이 정지되기 전에 용량 소자(112)에 있어서의 데이터의 유지가 선택되고, 용량 소자(112)로의 데이터의 재기록이 행해진다. 전원 전압의 공급 정지에 관해서는, 도 4a 및 도 4b에 도시된 바와 같이, 단위 기억 회로(114)과 전원 전압(VDD) 또는 기준 전압(GND)이 인가되는 노드간에 스위칭 소자를 제공함으로써 행할 수 있다.

[0105] 본 발명의 일 형태에서는, 오프 전류가 매우 작은 트랜지스터를 용량 소자의 전하를 유지하기 위한 스위칭 소자로서 사용하는 구성으로 함으로써 용량 소자로부터 누설되는 전하의 양을 작게 억제할 수 있다. 따라서, 본 발명의 일 형태에서는, 기억 장치(110)로의 전원 전압의 공급을 정지하여도 데이터의 소실을 방지할 수 있다. 따라서, 신호 처리 회로(107) 전체, 또는 신호 처리 회로(107)를 구성하는 제어 장치(131), ALU(132) 등의 논리 회로에 있어서, 짧은 시간이라도 전원 전압의 공급을 정지할 수 있다. 따라서, 신호 처리 회로(107)의 소비 전

력을 작게 억제할 수 있다.

[0106] 본 실시형태는 상기 실시형태와 적절히 조합하여 실시할 수 있다.

[0107] (실시형태 3)

[0108] 본 실시형태에서는, 기억 장치의 구체적인 구성의 일례에 대하여 설명한다. 또한, 본 실시형태에서는, 기억 소자가 결정성을 갖는 실리콘을 채널 형성 영역에 갖는 트랜지스터를 갖고, 용량 소자에 있어서의 전하의 공급, 유지, 방출을 제어하는 트랜지스터가 산화물 반도체를 채널 형성 영역에 갖는 경우를 예시한다.

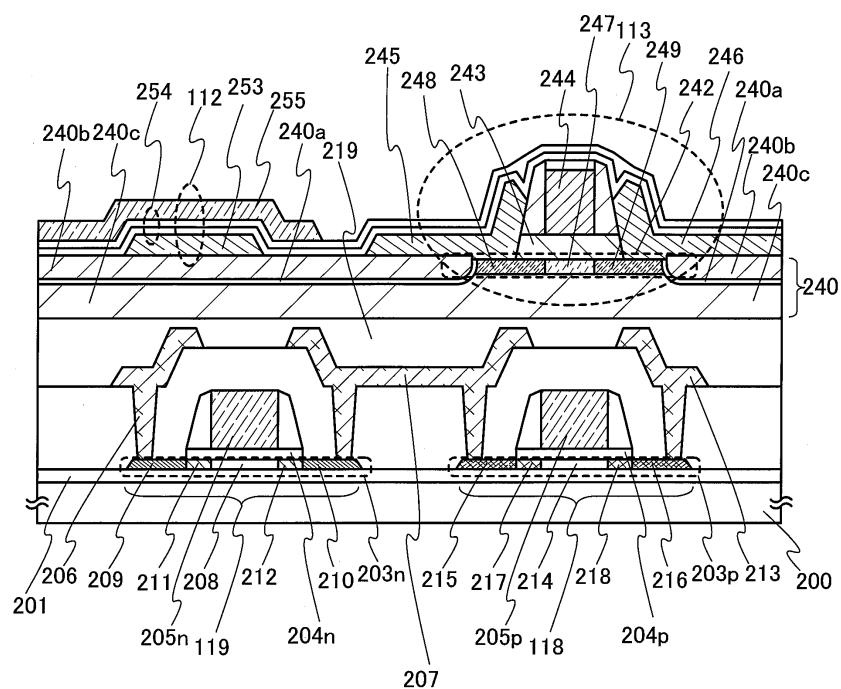

[0109] 도 6은 기억 소자가 갖는 p채널형 트랜지스터(118) 및 n채널형 트랜지스터(119)와, 용량 소자(112)와, 트랜지스터(113)의構成을 일례로서 단면도로 도시한 것이다.

[0110] 도 6에 도시된 기억 장치는, 표면에 절연막(201)이 형성된 기판(200) 위에 n채널형 트랜지스터(119)와 p채널형 트랜지스터(118)를 갖는다.

[0111] n채널형 트랜지스터(119)는, 결정성을 갖는 실리콘을 갖는 반도체막(203n)과, 반도체막(203n) 위의 게이트 절연막(204n)과, 게이트 절연막(204n)을 개재하여 반도체막(203n)과 중첩되는 위치에 제공된 게이트 전극(205n)과, 반도체막(203n)에 접속된 도전막(206) 및 도전막(207)을 갖는다. 또한, 반도체막(203n)은 채널 형성 영역으로서 기능하는 제 1 영역(208)과 소스 또는 드레인으로서 기능하는 제 2 영역(209) 및 제 2 영역(210)을 갖는다. 제 2 영역(209) 및 제 2 영역(210)은 제 1 영역(208)을 사이에 끼운다. 또한, 도 6에서는, 반도체막(203n)이 제 1 영역(208)과 제 2 영역(209) 및 제 2 영역(210) 사이에 LDD(Light Doped Drain) 영역으로서 기능하는 제 3 영역(211) 및 제 3 영역(212)을 갖는 경우를 예시한다.

[0112] 또한, p채널형 트랜지스터(118)는, 결정성을 갖는 실리콘을 갖는 반도체막(203p)과, 반도체막(203p) 위의 게이트 절연막(204p)과, 게이트 절연막(204p)을 개재하여 반도체막(203p)과 중첩되는 위치에 제공된 게이트 전극(205p)과, 반도체막(203p)에 접속된 도전막(207) 및 도전막(213)을 갖는다. 또한, 반도체막(203p)은 채널 형성 영역으로서 기능하는 제 1 영역(214)과 소스 또는 드레인으로서 기능하는 제 2 영역(215) 및 제 2 영역(216)을 갖는다. 제 2 영역(215) 및 제 2 영역(216)은 제 1 영역(214)을 사이에 끼운다. 또한, 도 6에서는, 반도체막(203p)이 제 1 영역(214)과 제 2 영역(215) 및 제 2 영역(216) 사이에 LDD 영역으로서 기능하는 제 3 영역(217) 및 제 3 영역(218)을 갖는 경우를 예시한다.

[0113] 또한, 도 6에서는 n채널형 트랜지스터(119)와 p채널형 트랜지스터(118)가 도전막(207)을 공유한다.

[0114] 또한, 도 6에서는 n채널형 트랜지스터(119)와 p채널형 트랜지스터(118)가 박막의 반도체막을 사용하는 경우를 예시하였지만, n채널형 트랜지스터(119)와 p채널형 트랜지스터(118)가 벌크의 반도체 기판에 채널 형성 영역을 갖는 트랜지스터이어도 좋다. 박막의 반도체막으로서는, 예를 들어 비정질 실리콘을 레이저 결정화시킴으로써 얻어지는 다결정 실리콘, 단결정 실리콘 웨이퍼에 수소 이온 등을 주입하여 표층부를 박리한 단결정 실리콘 등을 사용할 수 있다.

[0115] 또한, 도 6에 도시된 기억 장치는, 도전막(206), 도전막(207) 및 도전막(213) 위에 절연막(219)이 제공되어 있다. 또한, 절연막(219) 위에는, 제 1 산화 절연막(240a), 제 2 산화 절연막(240b), 및 제 3 산화 절연막(240c)을 갖는 절연막(240)이 제공되어 있다. 절연막(240) 위에는, 트랜지스터(113)가 제공되어 있다.

[0116] 제 1 산화 절연막(240a) 및 제 3 산화 절연막(240c)은, 가열됨으로써 산소의 일부가 탈리되는 산화 절연막을 사용하여 형성된다. 가열됨으로써 산소의 일부가 탈리되는 산화 절연막으로서는, 화학량론적 조성 비율을 만족시키는 산소보다 더 많은 산소를 함유한 산화 절연막을 사용하는 것이 바람직하다. 제 1 산화 절연막(240a) 및 제 3 산화 절연막(240c)으로서 산화 실리콘, 산화질화 실리콘, 질화산화 실리콘, 산화 갈륨, 산화 하프늄, 산화 이트륨 등을 사용할 수 있다.

[0117] 제 2 산화 절연막(240b)은, 산소의 확산을 방지하는 산화 절연막으로 형성한다. 제 2 산화 절연막(240b)의 일례로서는, 산화 알루미늄, 산화질화 알루미늄 등이 있다. 또한, 산화 알루미늄은 화학량론적 조성 비율을 만족시키는 산소를 함유하는 산화 알루미늄, 또는 화학량론적 조성 비율을 만족시키는 산소보다 더 많은 산소를 함유한 산화 알루미늄( $Al_{10x}$ , x는 3/2 이상)으로 하는 것이 바람직하다. 또한, 산화질화 알루미늄은 화학량론적 조성 비율을 만족시키는 산소를 함유한 산화 알루미늄의 산소의 일부가 질소로 치환되어 있다.

[0118] 또한, “가열됨으로써 산소의 일부가 탈리된다”라는 것은, TDS(Thermal Desorption Spectroscopy: 승온 탈리 가스 분광법) 분석에서, 산소 원자로 환산한 산소의 방출량이  $1.0 \times 10^{18} \text{ atoms/cm}^3$  이상, 바람직하게는  $3.0 \times$

$10^{20}$  atoms/cm<sup>3</sup> 이상인 것을 말한다.

[0119] TDS 분석에서 산소 원자로 환산한 산소의 탈리량을 측정하는 방법에 대하여 이하에서 설명한다.

[0120] TDS 분석으로 측정하였을 때의 기체의 탈리량은, 스펙트럼의 적분값에 비례한다. 따라서, 절연막의 스펙트럼의 적분값과, 표준 시료의 기준값에 대한 비율에 의하여, 기체의 방출량을 계산할 수 있다. 표준 시료의 기준값이란, 소정의 원자를 포함하는 시료의 스펙트럼의 적분값에 대한 원자의 밀도 비율이다.

[0121] 예를 들어, 표준 시료인 소정의 밀도의 수소를 함유하는 실리콘 웨이퍼의 TDS 분석 결과 및 절연막의 TDS 분석 결과로부터, 절연막의 산소 분자의 탈리량( $N_{O_2}$ )은, 하기의 수학식 1로 구할 수 있다. 질량수가 32인 기체로서  $CH_3OH$ 가 있지만, 절연막 중에 존재할 가능성은 낮다. 따라서, TDS 분석에서 얻어진 질량수 32에서 검출된 스펙트럼 전체가 산소 분자 유래라고 가정한다. 또한, 산소 원자의 동위체인 질량수 17의 산소 원자 및 질량수 18의 산소 원자를 포함하는 산소 분자에 대해서도, 자연계에 있어서의 존재 비율이 극미량이기 때문에 존재하지 않는 것으로 가정한다.

[0122] [수학식 1]

$$N_{O_2} = N_{H_2} / S_{H_2} \times S_{O_2} \times \alpha$$

[0124]  $N_{H_2}$ 는 표준 시료로부터 탈리된 수소 분자를 밀도로 환산한 값이다.  $S_{H_2}$ 는 표준 시료를 TDS 분석으로 측정하였을 때의 스펙트럼의 적분값이다. 표준 시료의 기준값은  $N_{H_2} / S_{H_2}$ 로 한다.  $S_{O_2}$ 는 절연막을 TDS 분석하였을 때의 스펙트럼의 적분값이다.  $\alpha$ 는 TDS 분석에서의 스펙트럼 강도에 영향을 주는 계수이다. 수학식 1의 상세 사항에 대해서는, 일본국 특개평6-275697 공보를 참조한다. 또한, 상기 절연막의 산소의 탈리량은 승온 탈리 분석 장치 EMD-WA1000S/W(전자과학 주식회사(ESCO, Ltd.) 제조)을 사용하고, 표준 시료로서  $1 \times 10^{16}$  atoms/cm<sup>3</sup>의 수소 원자를 포함하는 실리콘 웨이퍼를 사용하여 측정하였다.

[0125] 또한, TDS 분석에 있어서, 산소의 일부는 산소 원자로서 검출된다. 산소 분자와 산소 원자의 비율은, 산소 분자의 이온화율로부터 산출할 수 있다. 또한, 상술한  $\alpha$ 는 산소 분자의 이온화율을 포함하기 때문에, 산소 분자의 방출량을 평가함으로써, 산소 원자의 탈리량도 어림잡을 수 있다.

[0126] 또한,  $N_{O_2}$ 는 산소 분자의 탈리량이다. 절연막에 있어서는, 산소 원자로 환산하였을 때의 산소의 방출량은 산소 분자의 탈리량의 2배가 된다.

[0127] 상기 구성에 있어서, 가열됨으로써 산소가 방출되는 절연막은 산소가 과잉 함유된 산화 실리콘( $SiO_x (X > 2)$ )이라도 좋다. 산소가 과잉 함유된 산화 실리콘( $SiO_x (X > 2)$ )이란, 실리콘 원자수의 2배보다 많은 산소 원자를 단위 체적당에 포함한 것이다. 단위 체적당의 실리콘 원자수 및 산소 원자수는, 러더포드 후방산란법(Rutherford backscattering spectrometry)에 의하여 측정한 값이다.

[0128] 또한, 구체적으로 트랜지스터(113)는 산화물 반도체막(242)과, 산화물 반도체막(242) 위의 게이트 절연막(243)과, 게이트 절연막(243)을 개재하여 산화물 반도체막(242)과 중첩되는 위치에 제공된 게이트 전극(244)과, 산화물 반도체막(242)에 접속된 도전막(245) 및 도전막(246)을 갖는다. 산화물 반도체막(242)은, 게이트 전극(244)과 중첩되고, 적어도 일부가 채널 형성 영역으로서 기능하는 제 1 영역(247)과, 소스 또는 드레인으로서 기능하고 제 1 영역(247)을 끼우는 제 2 영역(248) 및 제 2 영역(249)을 갖는다.

[0129] 실리콘 반도체보다 밴드 갭이 넓고, 진성 캐리어 밀도가 실리콘보다 낮은 반도체 재료의 일례로서, 산화물 반도체 외에 탄화 실리콘( $SiC$ ), 질화 갈륨(GaN) 등의 화합물 반도체 등이 있다. 산화물 반도체는, 탄화 실리콘이나 질화 갈륨과 달리 스퍼터링법이나 습식법에 의하여 제작할 수 있고, 양산성이 뛰어나다는 이점을 갖는다. 또한 탄화 실리콘 또는 질화 갈륨과 달리, 산화물 반도체는 실온에서도 형성할 수 있기 때문에, 유리 기판 위에 형성할 수 있거나, 또는 실리콘을 사용한 접적 회로 위에 형성할 수 있다. 또한, 기판의 대형화에도 대응할 수 있다. 따라서, 상술한 와이드 갭 반도체 중에서도 특히 산화물 반도체는 양산성이 높다는 장점을 갖는다. 또한, 트랜지스터의 성능(예를 들어, 전계 효과 이동도)을 항상시키기 위하여, 결정성의 산화물 반도체를 얻고자 하는 경우에도 250°C 내지 800°C의 가열 처리에 의하여 용이하게 결정성의 산화물 반도체를 얻을 수 있다.

[0130] 다음에, 도 6에 도시된 트랜지스터(113)의 구체적인 단면 구조에 대하여, 도 7a 내지 도 7c를 사용하여 설명한다.

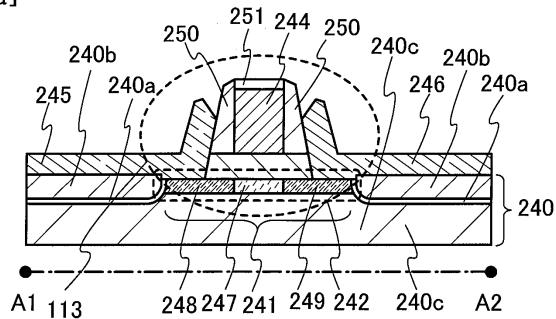

- [0131] 도 7a는 절연막(240) 및 트랜지스터(113)의 단면도이고, 도 7b는 절연막(240) 및 트랜지스터(113)의 상면도이다. 도 7b의 파선 A1-A2에 있어서의 단면도가, 도 7a에 상당한다. 또한, 도 7c는 도 7b의 파선 B1-B2에 있어서의 절연막(240) 및 트랜지스터(113)의 단면도이다.

- [0132] 트랜지스터(113)는, 게이트 전극(244)의 측부에 절연막을 갖는 사이드 월(250)이 제공되어 있고, 게이트 전극(244)의 상부에 절연막(251)이 제공되어 있다. 또한, 도전막(245) 및 도전막(246)은 그 일부가 사이드 월(250)에 접한다. 도전막(245) 및 도전막(246)은 반드시 사이드 월(250)에 접할 필요는 없지만, 사이드 월(250)에 접하도록 도전막(245) 및 도전막(246)을 형성함으로써, 도전막(245) 및 도전막(246)의 위치가 약간 어긋나 형성되어도 도전막(245) 및 도전막(246)과 산화물 반도체막(242)이 접하는 면적이 변동하는 것을 방지할 수 있다. 따라서, 도전막(245) 및 도전막(246)의 위치가 어긋나 형성되는 것으로 인한 트랜지스터(113)의 온 전류의 변동을 방지할 수 있다.

- [0133] 또한, 게이트 전극(244)의 상부에 위치하는 절연막(251)은 반드시 제공할 필요는 없지만, 절연막(251)을 제공함으로써 도전막(245) 및 도전막(246)의 위치가 어긋나 형성되어 게이트 전극(244)의 상부와 접촉되어도 도전막(245) 및 도전막(246)과 게이트 전극(244)이 도통하는 것을 방지할 수 있다.

- [0134] 절연막(240)에서는, 하층에 위치하는 제 3 산화 절연막(240c) 위에 제 1 산화 절연막(240a)과, 제 2 산화 절연막(240b)이 순서대로 적층되도록 제공된다. 또한, 제 1 산화 절연막(240a) 및 제 2 산화 절연막(240b)에는, 개구부(241)가 제공되어 있고, 상기 개구부(241)에는 트랜지스터(113)가 갖는 산화물 반도체막(242)이 제공되어 있다. 또한, 제 1 산화 절연막(240a)은 산화물 반도체막(242)의 단부에 접하도록 산화물 반도체막(242) 주위에 제공되어 있다. 또한, 제 2 산화 절연막(240b)은 제 1 산화 절연막(240a)을 개재하여 산화물 반도체막(242) 주위에 제공되어 있다. 제 3 산화 절연막(240c)은 산화물 반도체막(242) 아래에 제공되어 있다.

- [0135] 상기 구성에 의하여, 가열됨으로써 제 1 산화 절연막(240a)으로부터 방출된 산소가, 제 2 산화 절연막(240b)을 통과하는 것을 억제할 수 있기 때문에, 상기 산소가 제 1 영역(247)에서의 산화물 반도체막(242)의 단부(252)에 효율적으로 공급된다. 또한, 제 3 산화 절연막(240c)으로부터 방출된 산소는 산화물 반도체막(242)의 하부에 공급된다. 또한, 산화물 반도체를 채널 형성 영역에 갖는 트랜지스터(113)는, 산화물 반도체막(242)을 원하는 형상으로 에칭하기 위한 에칭 처리, 산화물 반도체막(242)의 단부의 감압 분위기에서의 노출 등에 의하여, 산화물 반도체막(242) 단부에 있어서 산소의 탈리로 인한 산소 결손이 형성되기 쉽다. 그리고, 산소 결손은 캐리어의 이동 경로가 되므로, 산화물 반도체막(242)의 단부에 산소 결손이 형성되면, 기생 채널이 생겨 트랜지스터(113)의 오프 전류가 높아진다. 그러나, 본 발명의 일 형태에서는, 상기 구성에 의하여 제 1 영역(247)에 있어서의 산화물 반도체막(242)의 단부(252)에 산소 결손이 형성되는 것을 방지하여 오프 전류를 저감시킬 수 있다.

- [0136] 또한, 도 6에 도시된 바와 같이, 용량 소자(112)는 절연막(240) 위의 도전막(253)과, 도전막(253) 위의 절연막(254)과, 절연막(254)을 개재하여 도전막(253)과 중첩되는 위치에 제공된 도전막(255)을 갖는다. 절연막(254)은 트랜지스터(113) 위에도 제공되어 있다. 또한, 도전막(253)과 도전막(255)은 전기적으로 접속되어 있어도 좋고, 또는 도전막(253)과 도전막(255)이 하나의 연속된 도전막으로 구성되어 있어도 좋다.

- [0137] 또한, 도 6에서는, 용량 소자(112)를 트랜지스터(113)와 함께 절연막(240) 위에 제공한 경우를 예시하였지만, 용량 소자(112)는 n채널형 트랜지스터(119) 및 p채널형 트랜지스터(118)와 함께 절연막(240) 아래에 제공되어도 좋다.

- [0138] 또한, 도 6에서는, 절연막(240)과 n채널형 트랜지스터(119) 및 p채널형 트랜지스터(118) 사이에 절연막(219)을 제공한 경우를 예시하였지만, 절연막(219)은 반드시 제공할 필요는 없다. 절연막(219)을 제공하지 않은 경우, 도전막(206), 도전막(207), 및 도전막(213)에 접하도록 절연막(240)이 제공된다.

- [0139] 또한, 도 6에 있어서 트랜지스터(113)는 산화물 반도체막(242)의 한쪽에서 게이트 전극(244)을 적어도 가지면 좋지만, 산화물 반도체막(242)을 개재하여 존재하는 한 쌍의 게이트 전극을 가져도 좋다.

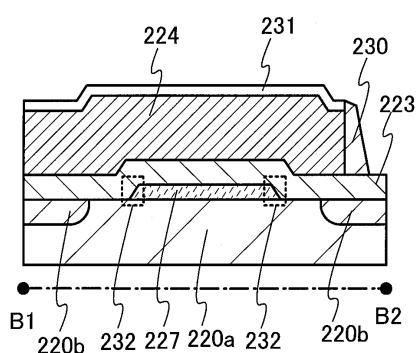

- [0140] 다음에, 트랜지스터(113)의 구성이 도 6에 도시된 기억 장치와 상이한, 본 발명의 일 형태에 따른 기억 장치의 구성에 대하여 설명한다. 도 8a 내지 도 8c는 트랜지스터(113)의 구성을 일례로서 도시한 것이다. 도 8a 내지 도 8c에서는, 제 1 산화 절연막(220a) 및 제 2 산화 절연막(220b)을 갖는 절연막(220) 위에 트랜지스터(113)가 제공되어 있다. 또한, 도 8a는 절연막(220) 및 트랜지스터(113)의 단면도이고, 도 8b는 절연막(220) 및 트랜지스터(113)의 상면도이다. 도 8b의 파선 A1-A2에 있어서의 단면도가, 도 8a에 상당한다. 또한, 도 8c는 도 8b의 파선 B1-B2에 있어서의 절연막(220) 및 트랜지스터(113)의 단면도이다.

- [0141] 제 1 산화 절연막(220a)은 가열됨으로써 산소의 일부가 탈리되는 산화 절연막을 사용하여 형성한다. 가열됨으로써 산소의 일부가 탈리되는 산화 절연막으로서는, 화학량론적 조성 비율을 만족시키는 산소보다 더 많은 산소를 함유한 절연막을 사용하는 것이 바람직하다. 제 1 산화 절연막(220a)으로서 산화 실리콘, 산화질화 실리콘, 질화산화 실리콘, 산화 갈륨, 산화 하프늄, 산화 이트륨 등을 사용할 수 있다.

- [0142] 제 2 산화 절연막(220b)은, 산소의 확산을 방지하는 산화 절연막으로 형성한다. 제 2 산화 절연막(220b)의 일례로서는, 산화 알루미늄, 산화질화 알루미늄 등이 있다. 또한, 산화 알루미늄은 화학량론적 조성 비율을 만족시키는 산소를 함유한 산화 알루미늄, 또는 화학량론적 조성 비율을 만족시키는 산소보다 많은 산소를 함유한 산화 알루미늄( $Al_{10_x}$ ,  $x$ 는  $3/2$  이상)으로 하는 것이 바람직하다. 또한, 산화질화 알루미늄은 화학량론적 조성 비율을 만족시키는 산소를 함유한 산화 알루미늄의 산소의 일부가 질소로 치환되어 있다.

- [0143] 트랜지스터(113)는, 절연막(220) 위에 위치하는 산화물 반도체막(222)과, 산화물 반도체막(222) 위의 게이트 절연막(223)과, 게이트 절연막(223)을 개재하여 산화물 반도체막(222)과 중첩되는 위치에 제공된 게이트 전극(224)과, 산화물 반도체막(222)에 접속된 도전막(225) 및 도전막(226)을 갖는다. 산화물 반도체막(222)은 게이트 전극(224)과 중첩되고, 적어도 일부가 채널 형성 영역으로서 기능하는 제 1 영역(227)과, 소스 또는 드레인으로서 기능하고, 제 1 영역(227)을 끼우는 제 2 영역(228) 및 제 2 영역(229)을 갖는다.

- [0144] 또한, 트랜지스터(113)는, 게이트 전극(224) 측부에 절연막을 갖는 사이드 월(230)이 제공되고, 게이트 전극(224) 상부에 절연막(231)이 제공되어 있다. 그리고, 도전막(225) 및 도전막(226)은 그 일부가 사이드 월(230)에 접한다. 도전막(225) 및 도전막(226)은 반드시 사이드 월(230)에 접할 필요는 없지만, 사이드 월(230)에 접하도록 도전막(225) 및 도전막(226)을 형성함으로써, 도전막(225) 및 도전막(226)의 위치가 약간 어긋나 형성되어도 도전막(225) 및 도전막(226)과 산화물 반도체막(222)이 접하는 면적이 변동하는 것을 방지할 수 있다. 따라서, 도전막(225) 및 도전막(226)의 위치가 어긋나 형성되는 것으로 인한 트랜지스터(113)의 온 전류의 변동을 방지할 수 있다.

- [0145] 또한, 게이트 전극(224)의 상부에 위치하는 절연막(231)은 반드시 제공할 필요는 없지만, 절연막(231)을 제공함으로써 도전막(225) 및 도전막(226)의 위치가 어긋나 형성되어 게이트 전극(224)의 상부와 접촉되어도 도전막(225) 및 도전막(226)과 게이트 전극(224)이 도통하는 것을 방지할 수 있다.

- [0146] 그리고, 절연막(220)은 제 1 산화 절연막(220a) 주위에 제 2 산화 절연막(220b)이 제공되어 있다. 또한, 산화물 반도체막(222)은 제 1 영역(227)에 있어서 상기 제 1 산화 절연막(220a)과 접하고, 제 2 영역(228) 및 제 2 영역(229)에 있어서 제 1 산화 절연막(220a) 및 제 2 산화 절연막(220b)에 접한다.

- [0147] 상기 구성에 의하여, 가열됨으로써 제 1 산화 절연막(220a)으로부터 방출된 산소가, 제 2 산화 절연막(220b)을 통과하는 것을 억제할 수 있기 때문에, 상기 산소가 제 1 영역(227)에서의 산화물 반도체막(222)의 단부(232)에 효율적으로 공급된다. 또한, 산화물 반도체를 채널 형성 영역에 갖는 트랜지스터(113)는, 산화물 반도체막(222)을 원하는 형상으로 에칭하기 위한 에칭 처리, 산화물 반도체막(222)의 단부의 감압 분위기에서의 노출 등에 의하여, 산화물 반도체막(222) 단부에 있어서 산소의 탈리로 인한 산소 결손이 형성되기 쉽다. 그리고, 산소 결손은 캐리어의 이동 경로가 되므로, 산화물 반도체막(222)의 단부에 산소 결손이 형성되면, 기생 채널이 생겨 트랜지스터(113)의 오프 전류가 높아진다. 그러나, 본 발명의 일 형태에서는, 상기 구성에 의하여 제 1 영역(227)에 있어서의 산화물 반도체막(222)의 단부(232)에 산소 결손이 형성되는 것을 방지하여 오프 전류를 저감시킬 수 있다.

- [0148] 또한, 도 8a 내지 도 8c에 있어서, 트랜지스터(113)는 산화물 반도체막(222)의 한쪽에 게이트 전극(224)을 적어도 가지면 좋지만, 산화물 반도체막(222)을 개재하여 존재하는 한 쌍의 게이트 전극을 가져도 좋다.

- [0149] 또한, 전자 공여체(도너)가 되는 수분 또는 수소 등의 불순물이 저감되고, 또 산소 결손이 저감됨으로써 고순도화된 산화물 반도체(purified OS)는, i형(진성 반도체) 또는 i형에 매우 가깝다. 따라서, 상기 산화물 반도체를 사용한 트랜지스터는 오프 전류가 현저히 낮은 특성을 갖는다. 또한, 산화물 반도체의 밴드 캡은 2eV 이상, 바람직하게는 2.5eV 이상, 더 바람직하게는 3eV 이상이다. 수분 또는 수소 등의 불순물 농도가 충분히 저감되고, 또 산소 결손이 저감됨으로써 고순도화된 산화물 반도체막을 사용함으로써, 트랜지스터의 오프 전류를 낮출 수 있다.

- [0150] 구체적으로는, 고순도화된 산화물 반도체막을 채널 형성 영역으로서 사용한 트랜지스터의 오프 전류가 낮은 것은 다양한 실험에 의하여 증명할 수 있다. 예를 들어, 채널 폭이  $1 \times 10^6 \mu\text{m}$ 이고, 채널 길이  $10 \mu\text{m}$ 인 소자인 경

우에도, 소스 전극과 드레인 전극간의 전압(드레인 전압)이 1V 내지 10V인 범위에서 오프 전류가 반도체 파라미터 애널라이저의 측정 한계 이하, 즉  $1 \times 10^{-13} \text{ A}$  이하라는 특성을 얻을 수 있다. 이 경우에는, 오프 전류를 트랜지스터의 채널 폭으로 나눈 값에 상당하는 오프 전류는  $100 \text{ zA}/\mu\text{m}$  이하인 것을 알 수 있다. 또한, 용량 소자와 트랜지스터를 접속시켜, 용량 소자에 유입 또는 용량 소자로부터 유출하는 전하를 상기 트랜지스터로 제어하는 회로를 사용하여, 오프 전류를 측정하였다. 상기 측정에서는 상기 트랜지스터에 고순도화된 산화물 반도체막을 채널 형성 영역에 사용하여, 용량 소자의 단위 시간당의 전하량의 추이로부터 상기 트랜지스터의 오프 전류를 측정하였다. 결과적으로, 트랜지스터의 소스 전극과 드레인 전극간의 전압이 3V인 경우에, 수십  $\text{yA}/\mu\text{m}$ 이라고 하는, 더 낮은 오프 전류가 얻어지는 것을 알 수 있었다. 따라서, 고순도화된 산화물 반도체막을 채널 형성 영역으로서 사용한 트랜지스터는, 결정성을 갖는 실리콘을 사용한 트랜지스터에 비하여 오프 전류가 현저히 작다.

[0151] 또한, 그 산화물 반도체로서는, 바람직하게는 In 또는 Zn을 포함하는 산화물을 사용하면 좋고, 보다 바람직하게는 In 및 Ga를 포함하는 산화물, 또는 In 및 Zn을 포함하는 산화물을 사용하면 좋다. 산화물 반도체막을 i형(진성)으로 하기 위하여, 이후에서 설명하는 탈수화 또는 탈수소화가 유효적이다. 또한, 산화물 반도체를 사용한 트랜지스터의 전기 특성의 편차를 저감하기 위한 스테빌라이저로서 그에 추가하여 갈륨(Ga)을 포함하는 것이 바람직하다. 또한, 스테빌라이저로서 주석(Sn)을 포함하는 것이 바람직하다. 또한, 스테빌라이저로서 하프늄(Hf)을 포함하는 것이 바람직하다. 또한, 스테빌라이저로서 알루미늄(Al)을 포함하는 것이 바람직하다.

[0152] 또한, 다른 스테빌라이저로서 란타노이드인, 란탄(La), 세륨(Ce), 프라세오디뮴(Pr), 네오디뮴(Nd), 사마륨(Sm), 유로퓸(Eu), 가돌리늄(Gd), 테르븀(Tb), 디스프로슘(Dy), 홀뮴(Ho), 에르븀(Er), 틀뮴(Tm), 이테르븀(Yb), 루테튬(Lu) 중 어느 한 종류 또는 복수 종류를 포함하여도 좋다.

[0153] 예를 들어, 산화물 반도체로서, 산화 인듐, 산화 주석, 산화 아연, 2원계 금속의 산화물인 In-Zn계 산화물, Sn-Zn계 산화물, Al-Zn계 산화물, Zn-Mg계 산화물, Sn-Mg계 산화물, In-Mg계 산화물, In-Ga계 산화물, 3원계 금속의 산화물인 In-Ga-Zn계 산화물(IGZO라고도 표기함), In-Al-Zn계 산화물, In-Sn-Zn계 산화물, Sn-Ga-Zn계 산화물, Al-Ga-Zn계 산화물, Sn-Al-Zn계 산화물, In-Hf-Zn계 산화물, In-La-Zn계 산화물, In-Ce-Zn계 산화물, In-Pr-Zn계 산화물, In-Nd-Zn계 산화물, In-Sm-Zn계 산화물, In-Eu-Zn계 산화물, In-Gd-Zn계 산화물, In-Tb-Zn계 산화물, In-Dy-Zn계 산화물, In-Ho-Zn계 산화물, In-Er-Zn계 산화물, In-Tm-Zn계 산화물, In-Yb-Zn계 산화물, In-Lu-Zn계 산화물, 4원계 금속의 산화물인 In-Sn-Ga-Zn계 산화물, In-Hf-Ga-Zn계 산화물, In-Al-Ga-Zn계 산화물, In-Sn-Al-Zn계 산화물, In-Sn-Hf-Zn계 산화물, In-Hf-Al-Zn계 산화물을 사용할 수 있다. 또한, 상기 산화물 반도체는 실리콘을 포함하여도 좋다.

[0154] 또한, 예를 들어, In-Ga-Zn계 산화물이란, In과 Ga와 Zn을 포함하는 산화물을 가리키고, In과 Ga와 Zn의 비율은 특별히 제한되지 않는다. 또한, In과 Ga와 Zn 이외의 금속 원소를 포함하여도 좋다. In-Ga-Zn계 산화물은 무전계 상태일 때 저항이 충분히 높고 오프 전류를 충분히 작게 할 수 있으며, 이동도도 높기 때문에 고체 활성장치, 또는 반도체 표시 장치에 사용하는 반도체 재료로서는 적합하다.

[0155] 또는, 산화물 반도체는 화학식  $\text{InM}_3(\text{ZnO})_m$  ( $m > 0$ )으로 표기되는 재료를 사용하여도 좋다. M은 Ga, Al, Mn 및 Co 중에서 선택된 하나 또는 복수의 금속 원소를 나타낸 것이다. 예를 들어, M으로서 Ga, Ga 및 Al, Ga 및 Fe, Ga 및 Ni, Ga 및 Mn, Ga 및 Co 등을 적용할 수 있다. 또한, 산화물 반도체로서,  $\text{In}_3\text{Sn}_5(\text{ZnO})_n$  또는 n은 정수임)로 표기되는 재료를 사용하여도 좋다. 또한, 상술한 조성은 결정 구조에서 도출되는 것이고, 어디까지나 일례에 불과한 것을 부기한다.

[0156] 예를 들어, 원자수 비율이  $\text{In:Ga:Zn}=1:1:1$  ( $=1/3:1/3:1/3$ ) 또는  $\text{In:Ga:Zn}=2:2:1$  ( $=2/5:2/5:1/5$ )인 In-Ga-Zn계 산화물이나 그 근방의 조성을 갖는 산화물을 사용할 수 있다. 또는, 원자수 비율이  $\text{In:Sn:Zn}=1:1:1$  ( $=1/3:1/3:1/3$ ),  $\text{In:Sn:Zn}=2:1:3$  ( $=1/3:1/6:1/2$ ) 또는  $\text{In:Sn:Zn}=2:1:5$  ( $=1/4:1/8:5/8$ )인 In-Sn-Zn계 산화물이나 그 근방의 조성을 갖는 산화물을 사용하면 좋다.

[0157] 그러나, 상술한 것에 한정되지 않고, 필요한 반도체 특성(이동도, 임계값, 편차 등)에 따라 적절한 조성의 것을 사용하면 좋다. 또한, 필요한 반도체 특성을 얻기 위하여 캐리어 밀도나 불순물 농도, 결함 밀도, 금속 원소와 산소의 원자수 비율, 원자간 결합 거리, 밀도 등을 적절한 것으로 하는 것이 바람직하다.

[0158] 또한, 예를 들어, In, Ga, Zn의 원자수 비율이  $\text{In:Ga:Zn}=a:b:c$  ( $a+b+c=1$ )인 산화물의 조성 비율이, 원자수 비율이  $\text{In:Ga:Zn}=A:B:C$  ( $A+B+C=1$ )인 산화물의 조성 비율의 근방이라는 것은,  $a, b, c$ 가,  $(a-A)^2 + (b-B)^2 + (c-C)^2 \leq r^2$  를 만족시키는 것을 말한다. r로서는, 예를 들어, 0.05로 하면 좋다. 다른 산화물도 마찬가지다.

- [0159] 또한, 산화물 반도체는, 아모퍼스(비정질)라도 좋고, 결정성을 가져도 좋다. 후자의 경우, 단결정이라도 좋고, 다결정이라도 좋으며, 일부분이 결정성을 갖는 구성이라도 좋고, 아모퍼스 중에 결정성을 갖는 부분을 포함하는 구조라도 좋고, 비아모퍼스라도 좋다. 일부분이 결정성을 갖는 구성의 일례로서 c축 배향하고, 또 ab면, 표면 또는 계면의 방향으로부터 보아 삼각형 또는 육각형의 원자 배열을 가지며, c축에 수직인 방향으로부터 보아 금속 원자가 층 형상으로 배열되거나 또는 금속 원자와 산소 원자가 층 형상으로 배열되고, ab면에 있어서는 a축 또는 b축의 방향이 상이한(c축을 중심으로 회전한) 결정(CAAC : C Axis Aligned Crystal이라고도 함)을 포함하는 산화물을 사용하여도 좋다.

- [0160] 아모퍼스 상태의 산화물 반도체는 비교적 용이하게 평탄한 표면을 얻을 수 있기 때문에, 이것을 사용하여 트랜지스터를 제작할 때의 계면 산란을 저감할 수 있고, 비교적 용이하게 비교적 높은 이동도를 얻을 수 있다.

- [0161] 또한, 결정성을 갖는 산화물 반도체는, 아모퍼스 상태의 산화물 반도체와 비교하여 별크내 결합을 저감할 수가 있으며, 표면의 평탄성을 높이면 아모퍼스 상태의 산화물 반도체 이상의 이동도를 얻을 수 있다. 표면의 평탄성을 높이기 위해서는 평탄한 표면 위에 산화물 반도체를 형성하는 것이 바람직하고, 구체적으로는, 평균 면 거칠기(Ra)가 1nm 이하, 바람직하게는 0.3nm 이하, 더 바람직하게는 0.1nm 이하의 표면 위에 형성하면 좋다.

- [0162] 또한, Ra는, JIS B0601에 의하여 정의되어 있는 중심선 평균 거칠기를 면에 대하여 적용할 수 있도록 3차원으로 확장한 것이며, “기준면부터 지정면까지의 편차의 절대값을 평균한 값”으로 표현할 수 있고, 이하의 수학식 2로 정의된다.

- [0163] [수학식 2]

- $$Ra = \frac{1}{S_0} \int_{y_1}^{y_2} \int_{x_1}^{x_2} |f(x, y) - Z_0| dx dy$$

- [0164] 또한, 수학식 2에서  $S_0$ 은 측정면(좌표  $(x_1, y_1)$ ,  $(x_1, y_2)$ ,  $(x_2, y_1)$ ,  $(x_2, y_2)$ )의 4점으로 연결된 사각형 영역)의 면적을 가리키고,  $Z_0$ 은 측정면의 평균 높이를 가리킨다. Ra는 원자간력 현미경(AFM: Atomic Force Microscope)으로 평가 가능하다.

- [0165] 또한, 예를 들어, 산화물 반도체막은 In(인듐), Ga(갈륨) 및 Zn(아연)을 포함하는 타깃을 사용한 스퍼터링법에 의하여 형성할 수 있다. In-Ga-Zn계 산화물 반도체막을 스퍼터링법으로 형성하는 경우, 바람직하게는, 원자수 비율이 In:Ga:Zn=1:1:1, 4:2:3, 3:1:2, 1:1:2, 2:1:3, 또는 3:1:4로 나타내어지는 In-Ga-Zn계 산화물의 타깃을 사용한다. 상술한 원자수 비율을 갖는 In-Ga-Zn계 산화물의 타깃을 사용하여 산화물 반도체막을 형성함으로써, 다결정 또는 CAAC이 형성되기 쉬워진다. 또한, In, Ga 및 Zn을 포함하는 타깃의 충전율은 90% 이상 100% 이하, 바람직하게는 95% 이상 100% 미만이다. 충전율이 높은 타깃을 사용함으로써, 형성한 산화물 반도체막은 치밀한 막이 된다.

- [0166] 또한, 산화물 반도체로서 In-Zn계 산화물의 재료를 사용하는 경우, 사용하는 타깃의 조성 비율은 원자수 비율로 In:Zn=50:1 내지 1:2(몰수비로 환산하면  $In_2O_3:ZnO=25:1$  내지 1:4), 바람직하게는 In:Zn=20:1 내지 1:1(몰수비)로 환산하면  $In_2O_3:ZnO=10:1$  내지 1:2), 더욱 바람직하게는 In:Zn=1.5:1 내지 15:1(몰수비로 환산하면  $In_2O_3:ZnO=3:4$  내지 15:2)로 한다. 예를 들어, In-Zn계 산화물인 산화물 반도체막의 형성에 사용하는 타깃은 원자수 비율이  $In:Zn:O=X:Y:Z$ 일 때,  $Z>1.5X+Y$ 로 한다. Zn의 비율을 상기 범위에 들어가게 함으로써, 이동도의 향상을 실현할 수 있다.

- [0167] 또한, 구체적으로는 감압 상태로 유지된 처리실 내에 기관을 유지하고, 처리실 내의 잔류 수분을 제거하면서 수소 및 수분이 제거된 스퍼터링 가스를 도입하고, 상기 타깃을 사용하여 산화물 반도체막을 형성하면 좋다. 형성할 때, 기관 온도를 100°C 이상 600°C 이하, 바람직하게는 200°C 이상 400°C 이하로 하여도 좋다. 기관을 가열하면서 형성함으로써, 형성된 산화물 반도체막에 포함되는 불순물 농도를 저감할 수 있다. 또한, 스퍼터링으로 인한 손상이 경감된다. 처리실 내의 잔류 수분을 제거하기 위해서는, 흡착형의 진공 펌프를 사용하는 것이 바람직하다. 예를 들어, 크라이오 펌프, 이온 펌프, 티타늄 서블리메이션(sublimation) 펌프를 사용하는 것이 바람직하다. 또한, 배기 수단으로서는, 터보 펌프에 콜드 트랩(cold trap)을 더한 것이라도 좋다. 크라이오 펌프를 사용하여 성막실을 배기하면, 예를 들어, 수소 원자, 물( $H_2O$ ) 등 수소 원자를 포함하는 화합물(보다 바람직하게는 탄소 원자를 포함하는 화합물도) 등이 배기되기 때문에, 상기 처리실에서 형성한 산화물 반도체막에 포함되는 불순물의 농도를 저감할 수 있다.

- [0169] 또한, 스퍼터링 등으로 형성된 산화물 반도체막 중에는, 불순물로서의 수분 또는 수소(수산기를 포함함)가 다양으로 함유되어 있는 경우가 있다. 수분 또는 수소는, 도너 준위를 형성하기 쉬우므로, 산화물 반도체에서는 불순물이다. 따라서, 본 발명의 일 형태에서는, 산화물 반도체막 중의 수분 또는 수소 등의 불순물을 저감(탈수화 또는 탈수소화)하기 위하여, 감압 분위기하, 질소나 희가스 등의 불활성 가스 분위기하, 산소 가스 분위기하, 또는 초건조 에어(CRDS(cavity ring down laser spectroscopy : 캐비티 링 다운 레이저 분광법) 방식의 이슬점 온도계를 사용하여 측정한 경우의 수분량이 20ppm(이슬점 환산으로 -55°C) 이하, 바람직하게는 1ppm 이하, 바람직하게는 10ppb 이하의 공기) 분위기하에서, 산화물 반도체막에 가열 처리를 실시한다.

- [0170] 산화물 반도체막에 가열 처리를 실시함으로써, 산화물 반도체막 중의 수분 또는 수소를 탈리시킬 수 있다. 구체적으로는, 250°C 이상 750°C 이하, 바람직하게는 400°C 이상 기판의 변형점 미만의 온도에서 가열 처리를 실시하면 좋다. 예를 들어, 500°C, 3분간 이상 6분간 이하 정도로 행하면 좋다. 가열 처리에 RTA법을 사용하면, 단시간에 탈수화 또는 탈수소화를 행할 수 있으므로, 유리 기판의 변형점을 넘는 온도로도 처리할 수 있다.

- [0171] 또한, 상기 가열 처리에 의하여 산화물 반도체막으로부터 산소가 탈리되고, 산화물 반도체막 중에 산소 결손이 형성되는 경우가 있다. 따라서, 본 발명의 일 형태에서는, 산화물 반도체막과 접하는 게이트 절연막 등의 절연막으로서, 산소를 함유하는 절연막을 사용한다. 그리고, 산소를 함유하는 절연막을 형성한 후, 가열 처리를 실시함으로써 상기 절연막으로부터 산화물 반도체막에 산소가 공여되도록 한다. 상기 구성에 의하여, 도너가 되는 산소 결손을 저감하고, 산화물 반도체막에 포함되는 산화물 반도체의 화학량론적 조성 비율을 만족시킬 수 있다. 반도체막에는, 화학량론적 조성 비율을 초과하는 양의 산소가 함유되어 있는 것이 바람직하다. 결과적으로, 산화물 반도체막을 i형에 가깝게 할 수 있고, 산소 결손으로 인하여 트랜지스터의 전기 특성의 편차를 경감하고, 전기 특성의 향상을 실현할 수 있다.

- [0172] 또한, 산소를 산화물 반도체막에 공여하기 위한 가열 처리는, 질소, 초건조 공기 또는 희가스(아르곤, 헬륨 등)의 분위기하에서, 바람직하게는 200°C 이상 400°C 이하, 예를 들어 250°C 이상 350°C 이하에서 행한다. 상기 가스는, 물의 함유량이 20ppm 이하, 바람직하게는 1ppm 이하, 보다 바람직하게는 10ppb 이하인 것이 바람직하다.

- [0173] 또한, c축 배향하고, 또 ab면, 표면 또는 계면의 방향으로부터 보아 삼각형 또는 육각형의 원자 배열을 갖고, c축에 수직인 방향으로부터 보아 금속 원자가 층 형상으로 배열되거나 또는 금속 원자와 산소 원자가 층 형상으로 배열되어 있고, ab면에 있어서는 a축 또는 b축의 방향이 상이한(c축을 중심으로 회전한) 결정(CAAC: C Axis Aligned Crystal)을 포함하는 산화물에 대하여, 이하에 설명한다.

- [0174] CAAC란 넓은 의미로 비단결정이며, 그 ab면에 수직인 방향으로부터 보아 삼각형, 육각형, 정삼각형 또는 정육각형의 원자 배열을 갖고, 또 c축 방향에 수직인 방향으로부터 보아 금속 원자가 층 형상으로 배열되거나 또는 금속 원자와 산소 원자가 층 형상으로 배열된 상(phase)을 포함하는 결정을 말한다.

- [0175] CAAC는 단결정이 아니지만, 비정질만으로 형성되는 것도 아니다. 또한, CAAC는 결정화한 부분(결정 부분)을 포함하지만, 하나의 결정 부분과 다른 결정 부분의 경계를 명확히 판별할 수 없는 경우도 있다.

- [0176] CAAC에 산소가 함유되는 경우, 산소의 일부는 질소로 치환되어도 좋다. 또한, CAAC를 구성하는 개개의 결정 부분의 c축은 일정 방향(예를 들어, CAAC가 형성되는 기판 면, CAAC의 표면 등에 수직인 방향)으로 일치되어도 좋다. 또는, CAAC를 구성하는 개개의 결정 부분의 ab면의 법선은 일정 방향(예를 들어, CAAC가 형성되는 기판 면, CAAC의 표면 등에 수직인 방향)을 향하여도 좋다.

- [0177] CAAC는 그 조성 등에 따라 도체, 반도체, 절연체일 수 있다. 또한, 그 조성 등에 따라 가시광에 대하여 투광성을 갖고 있거나 갖고 있지 않거나 한다.

- [0178] 이러한 CAAC의 예로서, 막 형상으로 형성되어 막 표면 또는 CAAC가 형성되는 기판면에 수직인 방향에서 관찰하면 삼각형 또는 육각형의 원자 배열이 확인되고, 또 그 막의 단면을 관찰하면 금속 원자 또는 금속 원자 및 산소 원자(또는 질소 원자)의 층 형상 배열이 확인되는 결정을 열거할 수도 있다.

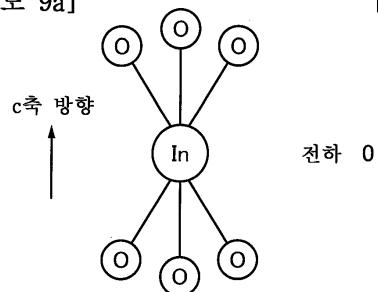

- [0179] CAAC에 포함되는 결정 구조의 일례에 대하여 도 9a 내지 도 11c를 사용하여 자세히 설명한다. 또한, 특별히 언급하지 않는 한, 도 9a 내지 도 11c는 위 방향을 c축 방향으로 하고, c축 방향과 직교하는 면을 ab면으로 한다. 또한, 단순히 상반부 및 하반부라고 하는 경우에는, ab면을 경계로 하였을 때의 상반부 및 하반부를 가리킨다. 또한, 도 9a 내지 도 9e에 있어서, 동그라미로 둘러싸인 0은 4배위 0를 나타내고, 이중 동그라미는 3배위 0를 나타낸다.

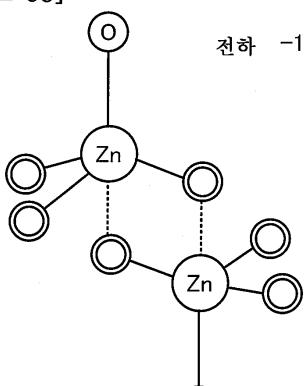

- [0180] 도 9a는 1개의 6배위 In과, In에 근접한 6개의 4배위 산소 원자(이하, 4배위 0)를 갖는 구조를 도시한 것이다. 여기서는, 금속 원자 1개에 대하여 근접한 산소 원자만을 도시한 구조를 소 그룹이라고 부른다. 도 9a의 구조는 팔면체 구조를 갖지만, 간편화를 위하여 평면 구조를 도시한 것이다. 또한, 도 9a의 상반부 및 하반부에는 각각 3개씩 4배위의 0가 있다. 도 9a에서 도시한 소 그룹은 전하가 0이다.

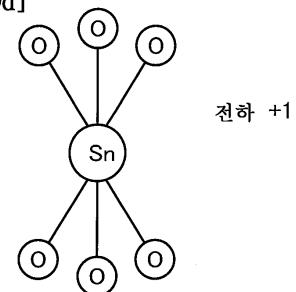

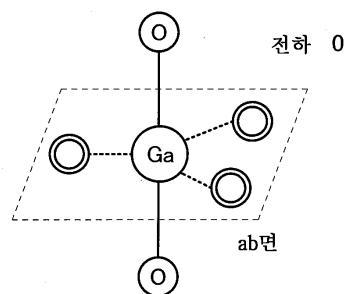

- [0181] 도 9b는 1개의 5배위의 Ga와, Ga에 근접한 3개의 3배위의 산소 원자(이하 3배위의 0)와, Ga에 근접한 2개의 4배위의 0를 갖는 구조를 도시한 것이다. 3배위의 0는 모두 ab면에 존재한다. 도 9b의 상반부 및 하반부에는 각각 1개씩 4배위의 0가 있다. 또한, In도 5배위를 갖기 때문에, 도 9b에 도시한 구조를 취할 수 있다. 도 9b에 도시한 소 그룹은 전하가 0이다.

- [0182] 도 9c는 1개의 4배위의 Zn과, Zn에 근접한 4개의 4배위의 0를 갖는 구조를 도시한 것이다. 도 9c의 상반부에는 1개의 4배위의 0가 있고, 하반부에는 3개의 4배위의 0가 있다. 또는, 도 9c의 상반부에 3개의 4배위의 0가 있고, 하반부에 1개의 4배위의 0가 있어도 좋다. 도 9c에서 도시한 소 그룹은 전하가 0이다.

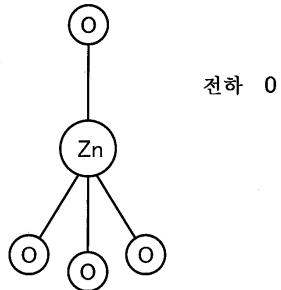

- [0183] 도 9d는 1개의 6배위의 Sn과, Sn에 근접한 6개의 4배위의 0를 갖는 구조를 도시한 것이다. 도 9d의 상반부에는 3개의 4배위의 0가 있고, 하반부에는 3개의 4배위의 0가 있다. 도 9d에 도시된 소 그룹은 전하가 +1이 된다.

- [0184] 도 9e는, 2개의 Zn을 포함하는 소 그룹을 도시한 것이다. 도 9e의 상반부에는 1개의 4배위의 0가 있고, 하반부에는 1개의 4배위의 0가 있다. 도 9e에 도시된 소 그룹은 전하가 -1이 된다.

- [0185] 여기서는, 복수의 소 그룹의 집합체를 중(中) 그룹이라고 부르고, 복수의 중 그룹의 집합체를 대(大) 그룹(유닛셀이라고도 함)이라고 부른다.

- [0186] 여기서, 이들의 소 그룹들이 결합하는 규칙에 대하여 설명한다. 도 9a에 도시된 6배위의 In의 상반부의 3개의 0는, 하측 방향으로 각각 3개의 근접 In을 갖고, 하반부의 3개의 0는, 상측 방향으로 각각 3개의 근접 In을 갖는다. 도 9b에 도시된 5배위의 Ga의 상반부의 1개의 0는 하측 방향으로 1개의 근접 Ga를 갖고, 하반부의 1개의 0는 상측 방향으로 1개의 근접 Ga를 갖는다. 도 9c에 도시된 4배위의 Zn의 상반부의 1개의 0는 하측 방향으로 하나의 근접 Zn을 갖고, 하반부의 3개의 0는 상측 방향으로 각각 3개의 근접 Zn을 갖는다. 이와 같이, 금속 원자의 상측 방향의 4배위 0의 개수와, 그 0의 하측 방향에 있는 근접 금속 원자의 개수는 동일하며, 마찬가지로 금속 원자의 하측 방향의 4배위 0의 개수와, 그 0의 상측 방향에 있는 근접 금속 원자의 개수는 동일하다. 0는 4배위이므로 하측 방향에 있는 근접 금속 원자의 개수와, 상측 방향에 있는 근접 금속 원자의 개수의 합은 4가 된다. 따라서, 금속 원자의 상측 방향에 있는 4배위 0의 개수와, 다른 금속 원자의 하측 방향에 있는 4배위 0의 개수의 합이 4일 때, 금속 원자를 갖는 2종류의 소 그룹들은 결합할 수 있다. 예를 들어, 6배위의 금속 원자(In 또는 Sn)가 하반부의 4배위의 0를 개재하여 결합하는 경우, 4배위의 0가 3개이기 때문에 5배위의 금속 원자(Ga 또는 In) 및 4배위의 금속 원자(Zn) 중 어느 것과 결합하게 된다.

- [0187] 배위수가 4, 5, 6인 금속 원자는 c축 방향에서 4배위의 0를 개재하여 결합한다. 또한, 그 외, 중 구조의 총 전하가 0이 되도록 복수의 소 그룹이 결합하여 중 그룹을 구성한다.

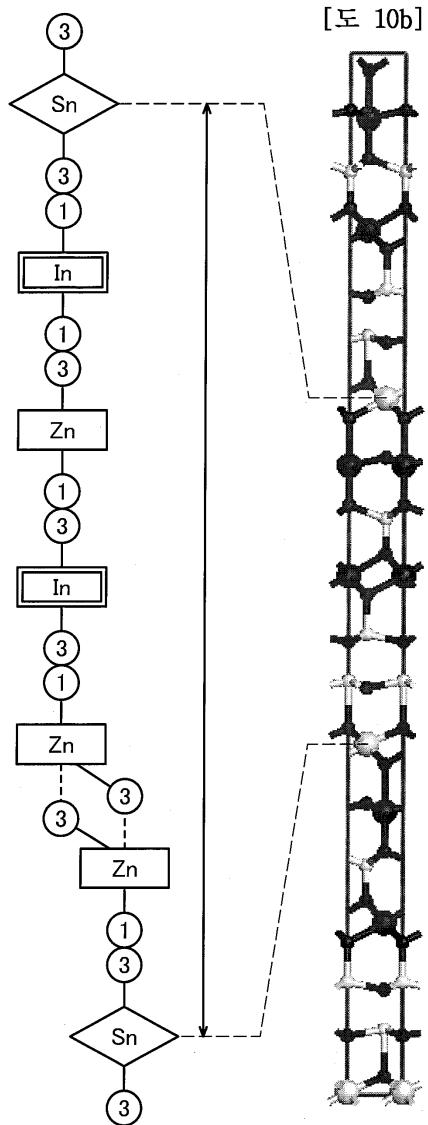

- [0188] 도 10a는 In-Sn-Zn계 산화물의 층 구조를 구성하는 중 그룹의 모델도를 도시한 것이다. 도 10b는, 3개의 중 그룹으로 구성되는 대 그룹을 도시한 것이다. 또한, 도 10c는 도 10b의 층 구조를 c축 방향으로부터 관찰한 경우의 원자 배열을 도시한 것이다.

- [0189] 도 10a에 있어서는, 간편화하기 위하여, 3배위의 0는 생략하고, 4배위의 0는 개수만 나타내며, 예를 들어, Sn의 상반부 및 하반부에는 각각 3개씩 4배위의 0가 있는 것을 동그라미의 3으로서 도시하였다. 마찬가지로, 도 10a에 있어서, In의 상반부 및 하반부에는 각각 1개씩 4배위의 0가 있고, 동그라미 1로서 나타내고 있다. 또한, 도 10a에 있어서, 하반부에는 1개의 4배위의 0가 있고, 상반부에는 3개의 4배위의 0가 있는 Zn과, 상반부에는 1개의 4배위의 0가 있고, 하반부에는 3개의 4배위의 0가 있는 Zn을 도시하였다.

- [0190] 도 10a에 있어서, In-Sn-Zn계 산화물의 층 구조를 구성하는 중 그룹은, 위로부터 순서대로 4배위의 0가 3개씩 상반부 및 하반부에 있는 Sn이, 4배위의 0가 1개씩 상반부 및 하반부에 있는 In과 결합하고, 그 In이, 상반부에 3개의 4배위의 0가 있는 Zn과 결합하고, 그 Zn의 하반부의 1개의 4배위의 0를 개재하여 4배위의 0가 3개씩 상반부 및 하반부에 있는 In과 결합하고, 그 In이, 상반부에 1개의 4배위의 0가 있는 Zn 2개로 이루어지는 소 그룹과 결합하고, 이 소 그룹의 하반부의 1개의 4배위의 0를 개재하여 4배위의 0가 3개씩 상반부 및 하반부에 있는 Sn과 결합하고 있는 구조이다. 복수의 상기 중 그룹이 결합하여 대 그룹을 구성한다.

- [0191] 여기서, 3배위의 0 및 4배위의 0의 경우, 결합 1개당의 전하는 각각 -0.667, -0.5로 생각할 수가 있다. 예를

들어, In(6배위 또는 5배위), Zn(4배위), Sn(5배위 또는 6배위)의 전하는 각각 +3, +2, +4이다. 따라서, Sn을 포함하는 소 그룹은 전하가 +1이 된다. 따라서, Sn을 포함하는 총 구조를 형성하기 위해서는, 전하 +1을 상쇄하는 전하 -1이 필요하다. 전하 -1을 취하는 구조로서, 도 9e에 도시된 바와 같이, 2개의 Zn을 포함하는 소 그룹을 들 수 있다. 예를 들어, Sn을 포함하는 소 그룹 1개에 대하여 2개의 Zn을 포함하는 소 그룹이 1개 있으면, 전하가 상쇄되기 때문에 총 전하를 0으로 할 수 있다.

[0192] 구체적으로, 도 10b에서 도시한 대 그룹이 반복됨으로써, In-Sn-Zn계 산화물의 결정( $In_2SnZn_3O_8$ )을 얻을 수 있다. 또한, 얻어지는 In-Sn-Zn계 산화물의 총 구조는,  $In_2SnZn_2O_7(ZnO)_m$ ( $m$ 은 0 또는 자연수)으로 하는 조성식으로 나타낼 수 있다.

[0193] 또한, 그 외에도 4원계 금속 산화물인 In-Sn-Ga-Zn계 산화물이나, 3원계 금속 산화물인 In-Ga-Zn계 산화물(IGZO라고도 표기함), In-Al-Zn계 산화물, Sn-Ga-Zn계 산화물, Al-Ga-Zn계 산화물, Sn-Al-Zn계 산화물, In-Hf-Zn계 산화물, In-La-Zn계 산화물, In-Ce-Zn계 산화물, In-Pr-Zn계 산화물, In-Nd-Zn계 산화물, In-Sm-Zn계 산화물, In-Eu-Zn계 산화물, In-Gd-Zn계 산화물, In-Tb-Zn계 산화물, In-Dy-Zn계 산화물, In-Ho-Zn계 산화물, In-Er-Zn계 산화물, In-Tm-Zn계 산화물, In-Yb-Zn계 산화물, In-Lu-Zn계 산화물이나, 2원계 금속 산화물인 In-Zn계 산화물, Sn-Zn계 산화물, Al-Zn계 산화물, Zn-Mg계 산화물, Sn-Mg계 산화물, In-Mg계 산화물, In-Ga계 산화물 등을 사용한 경우도 마찬가지이다.

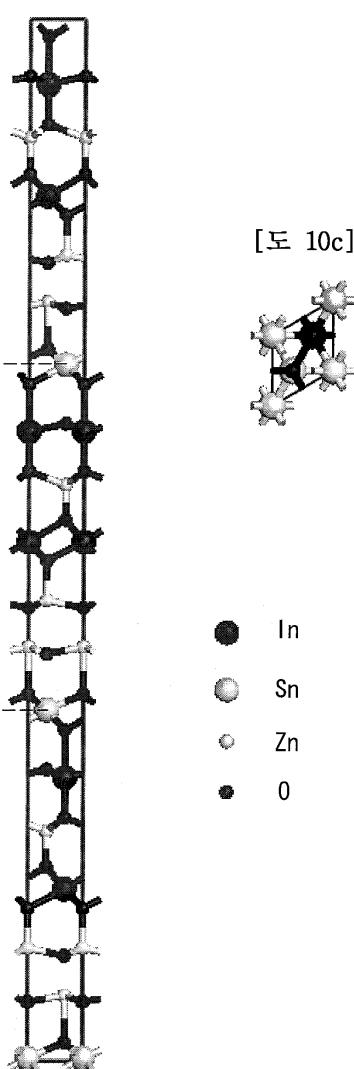

[0194] 예를 들어, 도 11a는 In-Ga-Zn계 산화물의 총 구조를 구성하는 중 그룹의 모델도를 도시한 것이다.

[0195] 도 11a에 있어서, In-Ga-Zn계 산화물의 총 구조를 구성하는 중 그룹은, 위로부터 순서대로 4배위의 0가 3개씩 상반부 및 하반부에 있는 In이, 4배위의 0가 1개 상반부에 있는 Zn과 결합하고, 그 Zn의 하반부의 3개의 4배위의 0를 개재하여 4배위의 0가 1개씩 상반부 및 하반부에 있는 Ga와 결합하고, 그 Ga의 하반부의 1개의 4배위의 0를 개재하여 4배위의 0가 3개씩 상반부 및 하반부에 있는 In과 결합하는 구성이다. 복수의 상기 중 그룹이 결합하여 대 그룹을 구성한다.

[0196] 도 11b는, 3개의 중 그룹으로 구성되는 대 그룹을 도시한 것이다. 또한, 도 11c는 도 11b의 총 구조를 c축 방향에서 관찰한 경우의 원자 배열을 도시한 것이다.

[0197] 여기서, In(6배위 또는 5배위), Zn(4배위), Ga(5배위)의 전하는, 각각 +3, +2, +3이기 때문에, In, Zn 및 Ga 중의 어느 것을 포함하는 소 그룹은, 전하가 0이 된다. 따라서, 이들 소 그룹을 조합한 것이라면 중 그룹의 총 전하는 항상 0이 된다.

[0198] 또한, In-Ga-Zn계 산화물의 총 구조를 구성하는 중 그룹은, 도 11a에 도시된 중 그룹에 한정되지 않고, In, Ga, Zn의 배열이 상이한 중 그룹을 조합한 대 그룹도 취할 수 있다.

[0199] 본 실시형태는, 상기 실시형태와 적절히 조합하여 실시할 수 있다.

[0200] (실시형태 4)

[0201] 본 발명의 일 형태에 따른 DCDC 컨버터는, 입력 전압에 대하여 큰 출력 전압이 얻어지는 승압형이라도 좋고, 입력 전압에 대하여 작은 출력 전압이 얻어지는 강압형이라도 좋다.

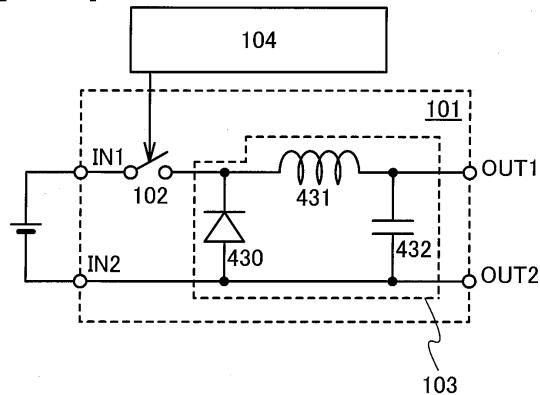

[0202] 도 12a는 본 발명의 일 형태에 따른 강압형의 DCDC 컨버터의 구성을 도시한 것이다. 도 12a에 도시된 DCDC 컨버터는, 정전압 생성부(103)가 다이오드(430), 코일(431), 용량 소자(432)를 갖는다. 또한, 도 12a에 도시된 DCDC 컨버터는, 입력 전압이 인가되는 입력 단자(IN1)와, 기준 전압이 인가되는 입력 단자(IN2)와, 출력 단자(OUT1)와, 출력 단자(OUT2)를 갖는다.

[0203] 스위칭 소자(102)는, 입력 단자(IN1)와 다이오드(430)의 음극 사이의 접속을 제어한다. 구체적으로는, 스위칭 소자(102)는 그 소스 및 드레인 중 한쪽이 입력 단자(IN1)에 접속되고, 그 소스 및 드레인 중 다른 쪽이 다이오드(430)의 음극에 접속되어 있다. 코일(431)이 갖는 한 쌍의 단자는, 한쪽이 다이오드(430)의 음극에 접속되고, 다른 쪽이 DCDC 컨버터의 출력 단자(OUT1)에 접속되어 있다. 입력 단자(IN2)는 다이오드(430)의 양극과 출력 단자(OUT2)에 접속되어 있다. 또한, 용량 소자(432)가 갖는 한 쌍의 전극은 한쪽이 출력 단자(OUT1)에 접속되고, 다른 쪽이 출력 단자(OUT2)에 접속되어 있다.

[0204] 도 12a에 도시된 DCDC 컨버터에서는, 스위칭 소자(102)가 온 상태가 되면, 입력 단자(IN1)와 출력 단자(OUT1) 사이에 전압이 생겨, 코일(431)에 전류가 흐른다. 코일(431)은 상기 전류가 흐름으로써 자화되는 동시에, 자기 유도에 의하여 전류의 흐름과는 반대 방향의 기전력이 생긴다. 그래서, 출력 단자(OUT1)에는 입력 단자(IN1)에

인가되는 입력 전압을 강압함으로써 얻어지는 전압이 인가된다. 즉, 용량 소자(432)가 갖는 한 쌍의 전극간에는 입력 단자(IN2)로부터 인가되는 기준 전압과, 입력 전압을 강압함으로써 얻어지는 전압의 차분에 상당하는 전압이 인가된다.

[0205] 이어서, 스위칭 소자(102)가 오프 상태가 되면, 입력 단자(IN1)와 출력 단자(OUT1) 사이에 형성되어 있던 전류의 경로가 차단된다. 코일(431)에서는, 상기 전류의 변화를 방해하는 방향, 즉, 스위칭 소자(102)가 온 상태일 때 생긴 기전력과는 반대 방향의 기전력이 생긴다. 그래서, 코일(431)을 흐르는 전류는 상기 기전력에 의하여 생긴 전압으로 유지된다. 즉, 스위칭 소자(102)가 오프 상태일 때에는 입력 단자(IN2) 또는 출력 단자(OUT2)와 출력 단자(OUT1) 사이에 코일(431)과 다이오드(430)를 통한 전류의 경로가 형성된다. 따라서, 용량 소자(432)가 갖는 한 쌍의 전극간에 인가된 전압은 어느 정도 유지된다.

[0206] 또한, 용량 소자(432)에 유지되는 전압은 출력 단자(OUT1)로부터 출력되는 출력 전압에 상당한다. 상기 동작에 있어서, 스위칭 소자(102)가 온 상태인 기간의 비율이 클수록, 용량 소자(432)에 유지되는 전압은 기준 전압과 입력 전압의 차분에 가깝게 된다. 따라서, 입력 전압에 더 가까운 크기의 출력 전압이 얻어지도록, 강압할 수 있다. 반대로, 스위칭 소자(102)가 오프인 기간의 비율이 클수록, 용량 소자(432)에 유지되는 전압은 기준 전압과의 차분이 작아진다. 따라서, 기준 전압에 더 가까운 크기의 출력 전압이 얻어지도록 강압할 수 있다.

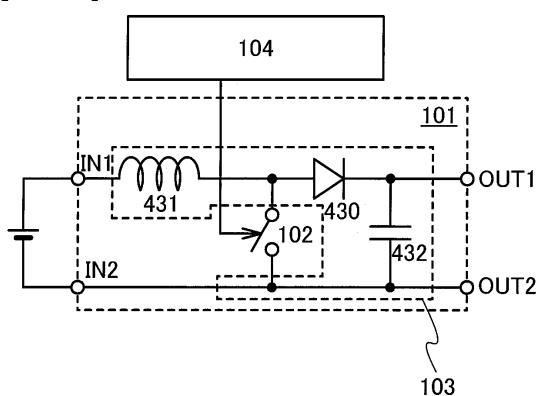

[0207] 다음에, 도 12b는 본 발명의 일 형태에 따른 승압형의 DCDC 컨버터의 구성을 도시한 것이다.

[0208] 또한, 도 12b에 도시된 DCDC 컨버터는, 정전압 생성부(103)가 다이오드(430), 코일(431), 용량 소자(432)를 갖는다. 또한, 도 12b에 도시된 DCDC 컨버터는, 입력 전압이 인가되는 입력 단자(IN1)와, 기준 전압이 인가되는 입력 단자(IN2)와, 출력 단자(OUT1)와, 출력 단자(OUT2)를 갖는다.

[0209] 코일(431)이 갖는 한 쌍의 단자는, 한쪽이 입력 단자(IN1)에 접속되고, 다른 쪽이 다이오드(430)의 양극에 접속된다. 스위칭 소자(102)는, 상기 코일(431)과 다이오드(430) 사이의 노드와, 입력 단자(IN2) 또는 출력 단자(OUT2) 사이의 접속을 제어한다. 구체적으로는, 스위칭 소자(102)는 그 소스 및 드레인 중 한쪽이 코일(431)과 다이오드(430) 사이의 노드에 접속되고, 그 소스 및 드레인 중 다른 쪽이 입력 단자(IN2) 및 출력 단자(OUT2)에 접속된다. 또한, 다이오드(430)의 음극은 출력 단자(OUT1)에 접속된다. 용량 소자(432)가 갖는 한 쌍의 전극은 한쪽이 출력 단자(OUT1)에 접속되고, 다른 쪽이 출력 단자(OUT2)에 접속된다.

[0210] 도 12b에 도시된 DCDC 컨버터에서는, 스위칭 소자(102)가 온 상태로 되면, 입력 단자(IN1)와 입력 단자(IN2) 사이에 생기는 전압에 의하여 코일(431)에 전류가 흐른다. 코일(431)은, 상기 전류가 흐름으로써 자화(磁化)된다. 또한, 코일(431)은 자기 유도에 의하여 전류의 흐름과는 반대 방향의 기전력이 생성되기 때문에, 상기 전류는 서서히 상승한다.

[0211] 이어서, 스위칭 소자(102)가 오프 상태가 되면, 입력 단자(IN1)와 입력 단자(IN2) 사이에 형성되어 있던 전류의 경로가 차단된다. 코일(431)에서는, 상기 전류의 변화를 방해하는 방향, 즉, 스위칭 소자(102)가 온 상태일 때 생긴 기전력과는 반대 방향의 기전력이 생긴다. 그래서, 코일(431)이 갖는 한 쌍의 단자간에는, 스위칭 소자(102)가 온 상태일 때에 코일(431)에 흐르고 있던 전류에 준한 크기의 전압이 생성된다. 그리고, 코일(431)을 흐르는 전류는, 단자간에 생성된 전압에 의하여 유지된다. 즉, 스위칭 소자(102)가 오프 상태일 때는 입력 단자(IN1)와 출력 단자(OUT1) 사이에 코일(431)과 다이오드(430)를 개재한 전류의 경로가 형성된다. 이 때, 출력 단자(OUT1)에는, 입력 단자(IN1)에 인가되는 입력 전압에, 코일(431)의 단자간에 생성된 전압이 가산된 전압이 인가되고, 이 전압이 출력 전압으로서 DCDC 컨버터로부터 출력된다. 상기 출력 단자(OUT1)의 전압과, 기준 전압의 차분에 상당하는 전압은 용량 소자(432)의 전극간에 있어서 유지된다.

[0212] 상기 동작에 있어서, 스위칭 소자(102)가 온 상태인 기간의 비율이 클수록, 코일(431)에 흐르는 전류가 높아진다. 그래서, 스위칭 소자(102)가 오프 상태가 되었을 때에 코일(431)의 단자간에 생기는 전압이 커지기 때문에, 출력 전압과 입력 전압의 차가 커지도록 승압할 수 있다. 반대로, 스위칭 소자(102)가 오프 상태인 기간의 비율이 클수록, 코일(431)에 흐르는 전류는 낮아진다. 그래서, 스위칭 소자(102)가 오프 상태가 되었을 때에 코일(431)의 단자간에 생기는 전압이 작아지기 때문에, 출력 전압과 입력 전압의 차가 작아지도록 승압할 수 있다.

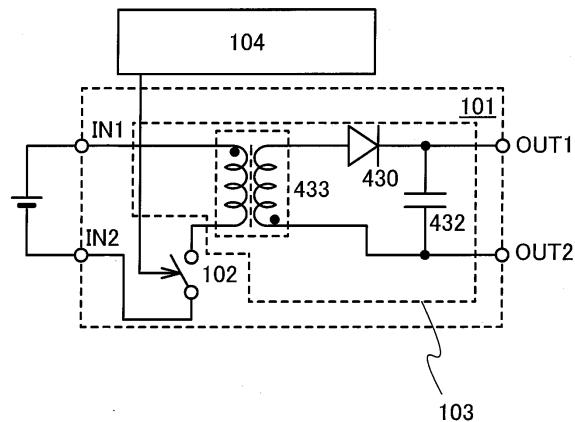

[0213] 다음에, 도 13a는 본 발명의 일 형태에 따른 플라이백형의 DCDC 컨버터의 구성을 도시한 것이다. 도 13a에 도시된 DCDC 컨버터는, 정전압 생성부(103)가 다이오드(430), 용량 소자(432), 트랜스(433)를 갖는다. 또한, 도 13a에 도시된 DCDC 컨버터는, 입력 전압이 인가되는 입력 단자(IN1)와, 기준 전압이 인가되는 입력 단자(IN2)와, 출력 단자(OUT1)와, 출력 단자(OUT2)를 갖는다.

- [0214] 트랜스(433)는, 그 중심에 공통의 코어가 제공된, 1차 코일과 2차 코일을 갖는다. 스위칭 소자(102)는 입력 단자(IN2)와 트랜스(433)의 1차 코일이 갖는 한쪽의 단자 사이의 접속을 제어한다. 구체적으로, 스위칭 소자(102)는 그 소스 및 드레인 중 한쪽이 입력 단자(IN2)에 접속되고, 그 소스 및 드레인 중 다른 쪽이 트랜스(433)의 1차 코일이 갖는 한쪽의 단자에 접속되어 있다. 또한, 트랜스(433)의 1차 코일이 갖는 다른 쪽의 단자는, 입력 단자(IN1)에 접속되어 있다.

- [0215] 또한, 트랜스(433)가 갖는 2차 코일은 한 쌍의 단자 중 어느 한쪽이 다이오드(430)의 양극에 접속되고, 다른 쪽의 단자가 출력 단자(OUT2)에 접속된다. 다이오드(430)의 음극은 출력 단자(OUT1)에 접속되어 있다. 용량 소자(432)가 갖는 한 쌍의 전극은 한쪽이 출력 단자(OUT1)에 접속되고, 다른 쪽이 출력 단자(OUT2)에 접속되어 있다.

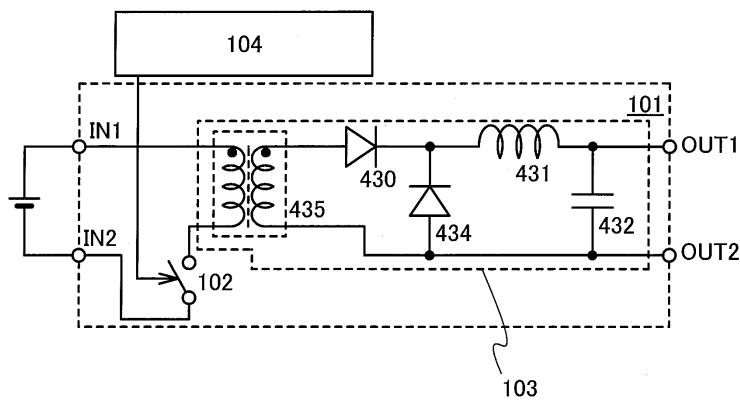

- [0216] 또한, 도 13b는 본 발명의 일 형태에 따른 포워드형의 DCDC 컨버터의 구성을 도시한 것이다. 도 13b에 도시된 DCDC 컨버터는, 정전압 생성부(103)가 다이오드(430), 다이오드(434), 코일(431), 용량 소자(432), 트랜스(435)를 갖는다. 또한, 도 13b에 도시된 DCDC 컨버터는, 입력 전압이 인가되는 입력 단자(IN1)와, 기준 전압이 인가되는 입력 단자(IN2)와, 출력 단자(OUT1)와, 출력 단자(OUT2)를 갖는다.

- [0217] 트랜스(435)는, 도 13a에 도시된 트랜스(433)와 마찬가지로 그 중심에 공통의 코어가 제공된, 1차 코일과 2차 코일을 갖는다. 다만, 트랜스(433)는 1차 코일과 2차 코일의 감기 시작점의 위치가 반대 측으로 배치되어 있는 한편, 트랜스(435)는 1차 코일과 2차 코일의 감기 시작점의 위치가 같은 측으로 배치되어 있다.

- [0218] 스위칭 소자(102)는 입력 단자(IN2)와 트랜스(435)의 1차 코일이 갖는 한쪽의 단자 사이의 접속을 제어한다. 구체적으로, 스위칭 소자(102)는 그 소스 및 드레인 중 한쪽이 입력 단자(IN2)에 접속되고, 그 소스 및 드레인 중 다른 쪽이 트랜스(435)의 1차 코일이 갖는 한쪽의 단자에 접속되어 있다. 또한, 트랜스(435)의 1차 코일이 갖는 다른 쪽의 단자는, 입력 단자(IN1)에 접속되어 있다.

- [0219] 또한, 트랜스(435)가 갖는 2차 코일은, 한 쌍의 단자 중 한쪽이 다이오드(430)의 양극에 접속되고, 다른 쪽의 단자가 출력 단자(OUT2)에 접속되어 있다. 다이오드(430)의 음극은, 다이오드(434)의 음극 및 코일(431)의 한쪽의 단자에 접속되어 있다. 다이오드(434)의 양극은, 출력 단자(OUT2)에 접속되어 있다. 코일(431)의 다른 쪽의 단자는, 출력 단자(OUT1)에 접속되어 있다. 용량 소자(432)가 갖는 한 쌍의 전극은, 한쪽이 출력 단자(OUT1)에 접속되고, 다른 쪽이 출력 단자(OUT2)에 접속되어 있다.

- [0220] 본 실시형태는 상기 실시형태와 적절히 조합하여 실시할 수 있다.

- [0221] (실시형태 5)

- [0222] 본 실시형태에서는, 본 발명의 일 형태에 따른 반도체 장치의 구성에 대하여 설명한다.

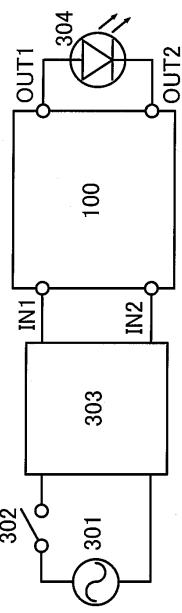

- [0223] 도 14a는 반도체 장치의 하나인 발광 장치의 일 형태를 나타낸 것이다. 도 14a에 도시된 발광 장치는, 교류 전원(301)과, 스위치(302)와, 정류 회로(303)와, DCDC 컨버터(100)와, 발광 소자(304)를 갖는다. 정류 회로(303) 및 DCDC 컨버터(100)가 전원 회로를 구성하고 있다.

- [0224] 구체적으로, 도 14a에 도시된 발광 장치에서는 교류 전원(301)으로부터의 교류 전압이 스위치(302)를 통하여 정류 회로(303)에 인가되어 정류된다. 정류됨으로써 얻어진 직류 전압은 DCDC 컨버터(100)에 입력되고, 그 크기가 조정되어 출력된다. DCDC 컨버터(100)의 상세한 구성 및 동작에 대해서는 상기 실시형태를 참조할 수 있다.

- [0225] 또한, DCDC 컨버터(100)로부터 출력된 전압이 발광 소자(304)에 인가됨으로써, 발광 소자(304)가 발광한다. 발광 소자(304)에는, 발광 다이오드(LED), 유기 발광 소자(OLED) 등 다양한 광원을 사용할 수 있다.

- [0226] 또한, 도 14a에서는, 전원으로서 교류 전원(301)을 사용하는 발광 장치의 구성을 도시하였지만, 본 발명은 이 구성에 한정되지 않는다. 전원으로서 교류 전원이 아니라 직류 전원을 사용하여도 좋다. 다만, 직류 전원을 사용하는 경우는 정류 회로(303)를 제공하지 않아도 좋다.

- [0227] 또한, 도 14a에서는, 전원인 교류 전원(301)을 갖는 발광 장치의 구성을 도시하지만, 본 발명의 일 형태에 따른 발광 장치는 반드시 전원을 그 구성 요소에 포함시킬 필요는 없다.

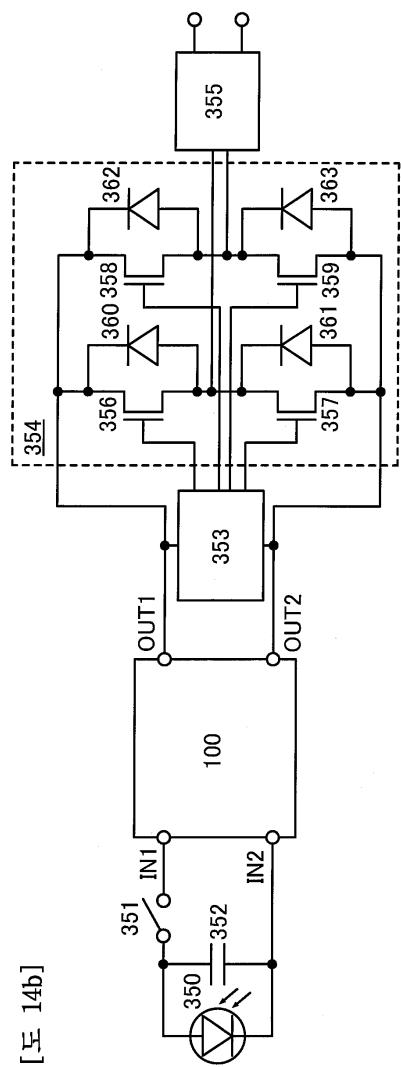

- [0228] 도 14b는 반도체 장치의 하나인 태양 전지의 일 형태를 도시한 것이다.

- [0229] 도 14b에 도시된 태양 전지는, 포토 다이오드(350)와, 스위치(351)와, 용량 소자(352)와, DCDC 컨버터(100)와, 펄스 폭 변조 회로(353)와, 인버터(354)와, 밴드 패스 필터(355)를 갖는다.

- [0230] 구체적으로, 도 14b에 도시된 태양 전지에서는, 포토 다이오드(350)에 광이 조사되면 전압이 생긴다. 상기 전압은 용량 소자(352)에 있어서 평활화된 후, 스위치(351)를 통하여 DCDC 컨버터(100)에 입력된다. 또한, 용량 소자(352)를 제공함으로써, 스위치(351)의 스위칭에 의하여 생기는 펄스상의 전류가 포토 다이오드(350)로 흘러드는 것을 방지할 수 있다.

- [0231] 그리고, DCDC 컨버터(100)에 입력된 전압은, DCDC 컨버터(100)에 있어서 그 크기가 조정된 후에 출력된다. DCDC 컨버터(100)의 상세한 구성 및 동작에 대해서는 상기 실시형태를 참조할 수 있다.

- [0232] DCDC 컨버터(100)의 출력 단자(OUT1) 및 출력 단자(OUT2)로부터 출력된 전압은 직류 전압이다. 인버터(354)는 DCDC 컨버터(100)로부터 출력된 직류 전압을 교류 전압으로 변환하여 출력한다. 도 14b에서는 인버터(354)가 4개의 트랜지스터(356) 내지 트랜지스터(359)와, 4개의 다이오드(360) 내지 다이오드(363)로 구성되어 있는 예를 도시하였다.

- [0233] 구체적으로, 트랜지스터(356)는 그 소스 및 드레인 중 한쪽이 DCDC 컨버터(100)의 출력 단자(OUT1)에 접속되고, 그 소스 및 드레인 중 다른 쪽이 트랜지스터(357)의 소스 및 드레인 중 한쪽에 접속되어 있다. 트랜지스터(357)의 소스 및 드레인 중 다른 쪽은, DCDC 컨버터(100)의 출력 단자(OUT2)에 접속되어 있다. 트랜지스터(358)는 그 소스 및 드레인 중 한쪽이 DCDC 컨버터(100)의 출력 단자(OUT1)에 접속되고, 그 소스 및 드레인 중 다른 쪽이 트랜지스터(359)의 소스 및 드레인 중 한쪽에 접속되어 있다. 트랜지스터(359)의 소스 및 드레인 중 다른 쪽은, DCDC 컨버터(100)의 출력 단자(OUT2)에 접속되어 있다. 다이오드(360) 내지 다이오드(363)는, 트랜지스터(356) 내지 트랜지스터(359)와 각각 병렬로 접속되어 있다. 구체적으로는, 트랜지스터(356) 내지 트랜지스터(359)의 소스 및 드레인 중 한쪽에 다이오드(360) 내지 다이오드(363)의 양극이 각각 접속되고, 트랜지스터(356) 내지 트랜지스터(359)의 소스 및 드레인 중 다른 쪽에 다이오드(360) 내지 다이오드(363)의 음극이 각각 접속되어 있다.

- [0234] 또한, 펄스 폭 변조 회로(353)에는 DCDC 컨버터(100)로부터 출력된 전압이 인가된다. 펄스 폭 변조 회로(353)는 상기 전압이 인가됨으로써 동작하고, 트랜지스터(356) 내지 트랜지스터(359)의 스위칭을 제어하는 신호를 생성한다.

- [0235] 펄스 폭 변조 회로(353)로부터의 상기 신호에 따라 트랜지스터(356) 내지 트랜지스터(359)가 스위칭을 행함으로써, 인버터(354)가 갖는, 트랜지스터(356)의 소스 및 드레인 중 다른 쪽과 트랜지스터(357)의 소스 및 드레인 중 한쪽이 접속되어 있는 노드와, 트랜지스터(358)의 소스 및 드레인 중 다른 쪽과 트랜지스터(359)의 소스 및 드레인 중 한쪽이 접속되어 있는 노드로부터, PWM 파형을 갖는 교류 전압이 출력된다.

- [0236] 그리고, 밴드 패스 필터(355)를 사용하여, 인버터(354)로부터 출력된 교류 전압의 고주파 성분을 제거함으로써, 정현파를 갖는 교류 전압을 얻을 수 있다.

- [0237] 본 실시형태는 상기 실시형태와 적절히 조합하여 실시할 수 있다.

- [0238] (실시예 1)

- [0239] 본 발명의 일 형태에 따른 DCDC 컨버터, 전원 회로, 또는 반도체 장치를 사용함으로써, 소비 전력이 낮은 전자 기기를 실현할 수 있다. 특히, 전력의 공급을 상시 받기 어려운 휴대용의 전자 기기의 경우, 본 발명의 일 형태에 따른 DCDC 컨버터, 전원 회로, 또는 반도체 장치를 그 구성 요소에 추가함으로써 연속 사용 시간이 길어지는 장점을 얻을 수 있다.

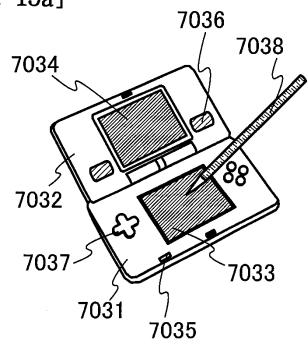

- [0240] 본 발명의 일 형태에 따른 반도체 장치는, 표시 장치, 퍼스널 컴퓨터, 기록 매체를 구비한 화상 재생 장치(대표적으로는 DVD: Digital Versatile Disc 등의 기록 매체를 재생하여, 그 화상을 표시할 수 있는 디스플레이를 갖는 장치)에 사용할 수 있다. 그 외, 본 발명의 일 형태에 따른 반도체 장치를 사용할 수 있는 전자 기기로서, 휴대 전화, 휴대형을 포함하는 게임기, 휴대 정보 단말, 전자 서적, 비디오 카메라, 디지털 스틸 카메라 등의 카메라, 고글형 디스플레이(헤드 장착형 디스플레이), 내비게이션 시스템, 음향 재생 장치(카 오디오, 디지털 오디오 콤포넌트 등), 복사기, 팩시밀리, 프린터, 프린터 복합기, 현금 자동 입출금기(ATM), 자동 판매기 등을 들 수 있다. 이들 전자 기기의 구체적인 예를 도 15a 내지 도 15f에 도시하였다.

- [0241] 도 15a는, 휴대형 게임기이며, 하우징(7031), 하우징(7032), 표시부(7033), 표시부(7034), 마이크로폰(7035), 스피커(7036), 조작 키(7037), 스타일러스(7038) 등을 갖는다. 본 발명의 일 형태에 따른 DCDC 컨버터, 전원 회로, 또는 반도체 장치는, 휴대형 게임기의 구동을 제어하기 위한 접속 회로에 사용할 수 있다. 휴대형 게임기의 구동을 제어하기 위한 접속 회로에 본 발명의 일 형태에 따른 DCDC 컨버터, 전원 회로, 또는 반도체 장치

를 사용함으로써, 소비 전력이 낮은 휴대형 게임기를 제공할 수 있다. 또한, 도 15a에서 도시한 휴대형 게임기는, 2개의 표시부로서 표시부(7033)와 표시부(7034)를 갖지만, 휴대형 게임기가 갖는 표시부의 개수는, 이것에 한정되지 않는다.

[0242] 도 15b는 휴대 전화이며, 하우징(7041), 표시부(7042), 음성 입력부(7043), 음성 출력부(7044), 조작 키(7045), 수광부(7046) 등을 갖는다. 수광부(7046)에 있어서 수신한 광을 전기 신호로 변환함으로써, 외부의 화상을 취득할 수 있다. 본 발명의 일 형태에 따른 DCDC 컨버터, 전원 회로, 또는 반도체 장치는, 휴대 전화의 구동을 제어하기 위한 집적 회로에 사용할 수 있다. 휴대 전화의 구동을 제어하기 위한 집적 회로에 본 발명의 일 형태에 따른 DCDC 컨버터, 전원 회로, 또는 반도체 장치를 사용함으로써, 소비 전력이 낮은 휴대 전화를 제공할 수 있다.

[0243] 도 15c는 휴대 정보 단말이며, 하우징(7051), 표시부(7052), 조작 키(7053) 등을 갖는다. 본 발명의 일 형태에 따른 DCDC 컨버터, 전원 회로, 또는 반도체 장치는, 휴대 정보 단말의 구동을 제어하기 위한 집적 회로에 사용할 수 있다. 휴대 정보 단말의 구동을 제어하기 위한 집적 회로에 본 발명의 일 형태에 따른 DCDC 컨버터, 전원 회로, 또는 반도체 장치를 사용함으로써, 소비 전력이 낮은 휴대 정보 단말을 제공할 수 있다.

[0244] 도 15d는 노트북형 퍼스널 컴퓨터이며, 하우징(7061), 화상 표시부(7062), 키보드(7063), 포인팅 디바이스(7064) 등을 갖는다. 본 발명의 일 형태에 따른 DCDC 컨버터, 전원 회로, 또는 반도체 장치는, 노트북형 퍼스널 컴퓨터의 구동을 제어하기 위한 집적 회로에 사용할 수 있다. 노트북형 퍼스널 컴퓨터의 구동을 제어하기 위한 집적 회로에 본 발명의 일 형태에 따른 DCDC 컨버터, 전원 회로, 또는 반도체 장치를 사용함으로써, 소비 전력이 낮은 노트북형 퍼스널 컴퓨터를 제공할 수 있다.

[0245] 도 15e는 탁상형 조명 장치이며, 하우징(7071), 광원(7072), 지지대(7073) 등을 갖는다. 본 발명의 일 형태에 따른 DCDC 컨버터, 전원 회로, 또는 반도체 장치는, 조명 장치의 구동을 제어하기 위한 집적 회로에 사용할 수 있다. 또한, 본 발명의 일 형태에 따른 반도체 장치의 하나인 발광 장치는, 광원(7072)과 그 동작을 제어하기 위한 구동 회로에 사용할 수 있다. 본 발명의 일 형태에 따른 DCDC 컨버터, 전원 회로, 또는 반도체 장치를 사용함으로써, 소비 전력이 낮은 조명 장치를 제공할 수 있다.

[0246] 도 15f는 설치형의 조명 장치이며, 하우징(7081), 광원(7082) 등을 갖는다. 본 발명의 일 형태에 따른 DCDC 컨버터, 전원 회로, 또는 반도체 장치는, 조명 장치의 구동을 제어하기 위한 집적 회로에 사용할 수 있다. 또한, 본 발명의 일 형태에 따른 반도체 장치의 하나인 발광 장치는, 광원(7082)과 그 동작을 제어하기 위한 구동 회로에 사용할 수 있다. 본 발명의 일 형태에 따른 DCDC 컨버터, 전원 회로, 또는 반도체 장치를 사용함으로써, 소비 전력이 낮은 조명 장치를 제공할 수 있다.

[0247] 본 실시예는, 상기 실시형태와 적절히 조합하여 실시할 수 있다.

### 부호의 설명

[0248] 100: DCDC 컨버터

101: 전력 변환 회로

102: 스위칭 소자

103: 정전압 생성부

104: 제어 회로

105: AD 컨버터

106: AD 컨버터

107: 신호 처리 회로

108: 펄스 변조 회로

109: 전원 제어 회로

110: 기억 장치

111: 기억 소자

- 112: 용량 소자

113: 트랜지스터

114: 단위 기억 회로

115: 논리 소자

115a: 논리 소자

115b: 논리 소자

116: 트랜지스터

117: 트랜지스터

118: p채널형 트랜지스터

119: n채널형 트랜지스터

120: p채널형 트랜지스터

121: n채널형 트랜지스터

130: 스위칭 소자

131: 제어 장치

132: ALU

133: 데이터 캐쉬

134: 명령 캐쉬

135: 프로그램 카운터

136: 명령 레지스터

137: 비휘발성 기억 장치

150: AD 컨버터

200: 기판

201: 절연막

203n: 반도체막

203p: 반도체막

204n: 게이트 절연막

204p: 게이트 절연막

205n: 게이트 전극

205p: 게이트 전극

206: 도전막

207: 도전막

208: 제 1 영역

209: 제 2 영역

210: 제 2 영역

211: 제 3 영역

212: 제 3 영역

- 213: 도전막

- 214: 제 1 영역

- 215: 제 2 영역

- 216: 제 2 영역

- 217: 제 3 영역

- 218: 제 3 영역

- 219: 절연막

- 220: 절연막

- 220a: 산화 절연막

- 220b: 산화 절연막

- 222: 산화물 반도체막

- 223: 게이트 절연막

- 224: 게이트 전극

- 225: 도전막

- 226: 도전막

- 227: 제 1 영역

- 228: 제 2 영역

- 229: 제 2 영역

- 230: 사이드 월

- 231: 절연막

- 232: 단부

- 240: 절연막

- 240a: 산화 절연막

- 240b: 산화 절연막

- 240c: 산화 절연막

- 241: 개구부

- 242: 산화물 반도체막

- 243: 게이트 절연막

- 244: 게이트 전극

- 245: 도전막

- 246: 도전막

- 247: 제 1 영역

- 248: 제 2 영역

- 249: 제 2 영역

- 250: 사이드 월

- 251: 절연막

- 252: 단부

253: 도전막

254: 절연막

255: 도전막

301: 교류 전원

302: 스위치

303: 정류 회로

304: 발광 소자

350: 포토 다이오드

351: 스위치

352: 용량 소자

353: 펄스 폭 변조 회로

354: 인버터

355: 밴드 패스 필터

356: 트랜지스터

357: 트랜지스터

358: 트랜지스터

359: 트랜지스터

360: 다이오드

363: 다이오드

430: 다이오드

431: 코일

432: 용량 소자

433: 트랜스

434: 다이오드

435: 트랜스

7031: 하우징

7032: 하우징

7033: 표시부

7034: 표시부

7035: 마이크로폰

7036: 스피커

7037: 조작 키

7038: 스타일러스

7041: 하우징

7042: 표시부

7043: 음성 입력부

7044: 음성 출력부

7045: 조작 키

7046: 수광부

7051: 하우징

7052: 표시부

7053: 조작 키

7061: 하우징

7062: 화상 표시부

7063: 키보드

7064: 포인팅 디바이스

7071: 하우징

7072: 광원

7073: 지지대

7081: 하우징

7082: 광원

## 도면

## 도면1

[도 1a]

[도 1b]

## 도면2

## 도면3

## 도면4

[도 4a]

[도 4b]

## 도면5

## 도면6

## 도면7

[도 7a]

[도 7b]

[도 7c]

## 도면8

[도 8a]

[도 8b]

[도 8c]

## 도면9

[도 9a]

[도 9d]

[도 9b]

[도 9e]

[도 9c]

## 도면10

[도 10a]

[도 10b]

[도 10c]

- In

- Sn

- Zn

- O

## 도면11

## 도면12

[도 12a]

[도 12b]

## 도면13

[도 13a]

[도 13b]

도면14

[도면 14a]

[도면 14b]

도면15

[도 15a]

[도 15b]

[도 15c]

[도 15d]

[도 15e]

[도 15f]

도면16